Overview The LC3 Computer A limited 3 address

- Slides: 19

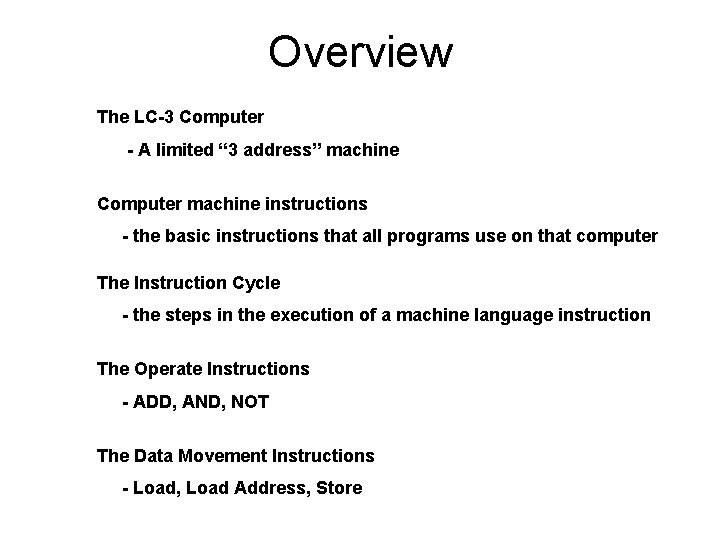

Overview The LC-3 Computer - A limited “ 3 address” machine Computer machine instructions - the basic instructions that all programs use on that computer The Instruction Cycle - the steps in the execution of a machine language instruction The Operate Instructions - ADD, AND, NOT The Data Movement Instructions - Load, Load Address, Store

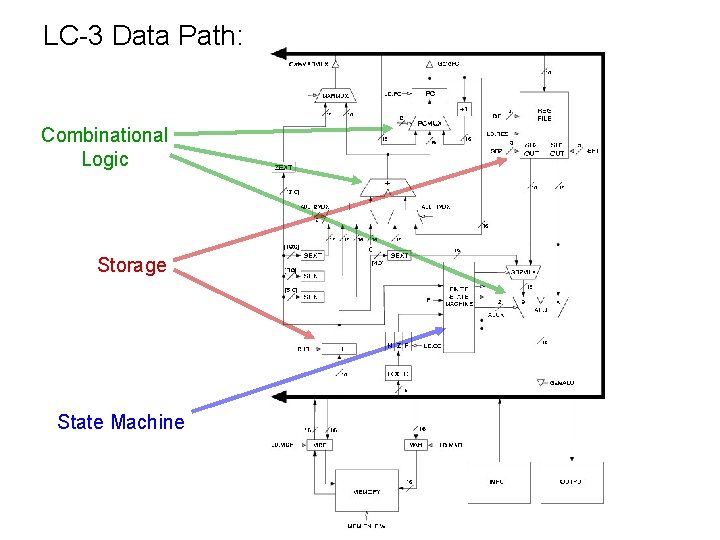

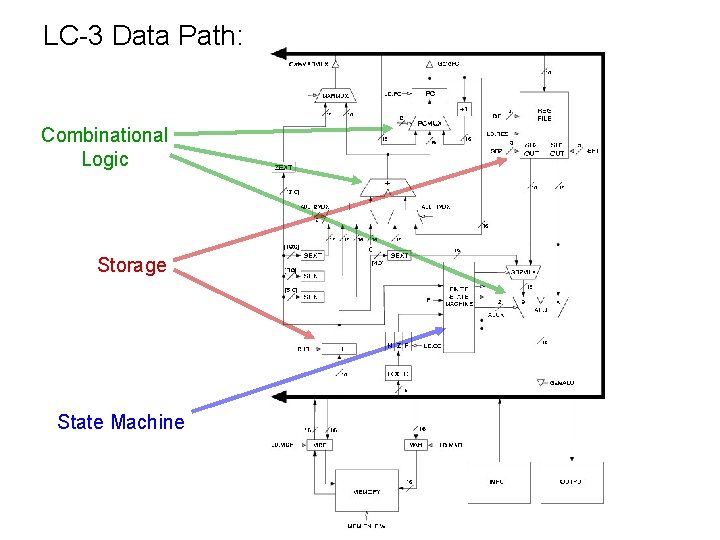

LC-3 Data Path: Combinational Logic Storage State Machine

Computer Machine Instruction Formats What is contained IN an instruction? • Specifies the operation to be performed • Where to get the operands • Where to put the result What are the major instruction types? • Operate (add, sub, mult, OR, AND, etc. ) • Data Movement (Load, Store) • Control (branch, jump to subroutine, etc. )

The LC-3 Instruction ADDRESSING MODES • Immediate (Operand is in the instruction) • Register (Operand is in one of the 8 registers) • PC-relative (Operand is “offset” from the (PC) ) • Base + Offset (Base relative) (Operand is “offset” from the contents of a register) • Indirect (The “Operand” actually points to the real address – rather than being the operand)

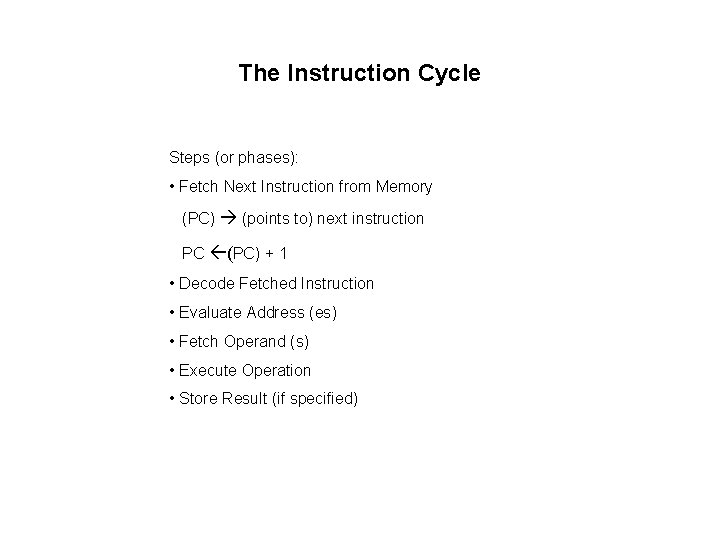

The Instruction Cycle Steps (or phases): • Fetch Next Instruction from Memory (PC) (points to) next instruction PC (PC) + 1 • Decode Fetched Instruction • Evaluate Address (es) • Fetch Operand (s) • Execute Operation • Store Result (if specified)

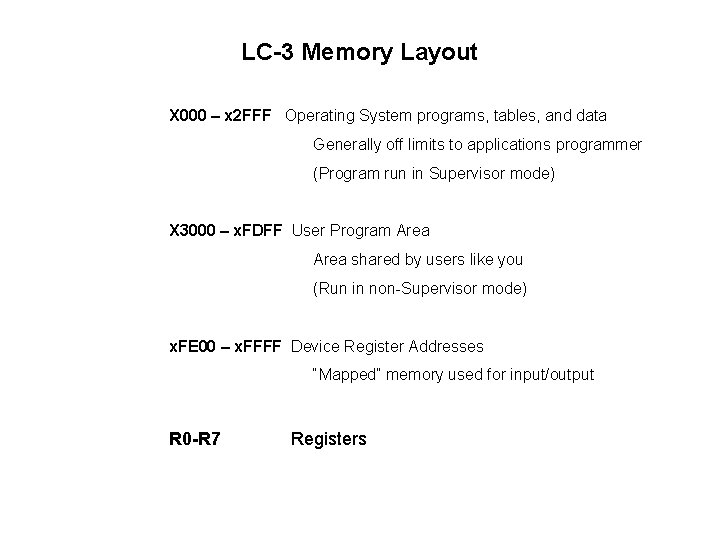

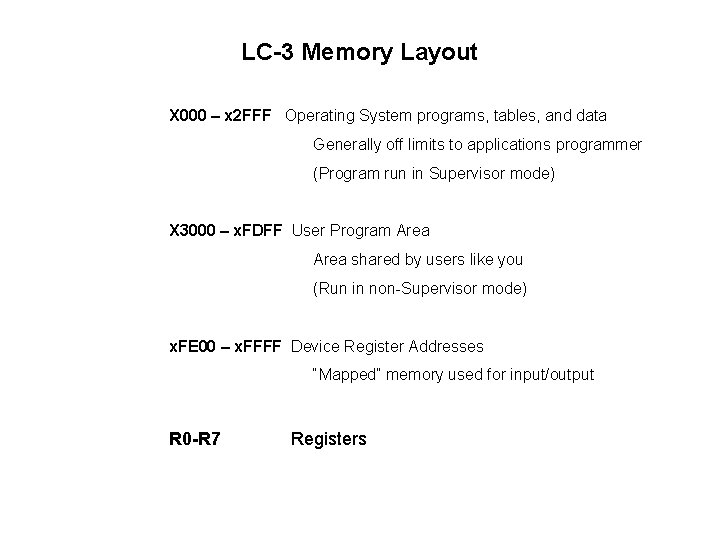

LC-3 Memory Layout X 000 – x 2 FFF Operating System programs, tables, and data Generally off limits to applications programmer (Program run in Supervisor mode) X 3000 – x. FDFF User Program Area shared by users like you (Run in non-Supervisor mode) x. FE 00 – x. FFFF Device Register Addresses “Mapped” memory used for input/output R 0 -R 7 Registers

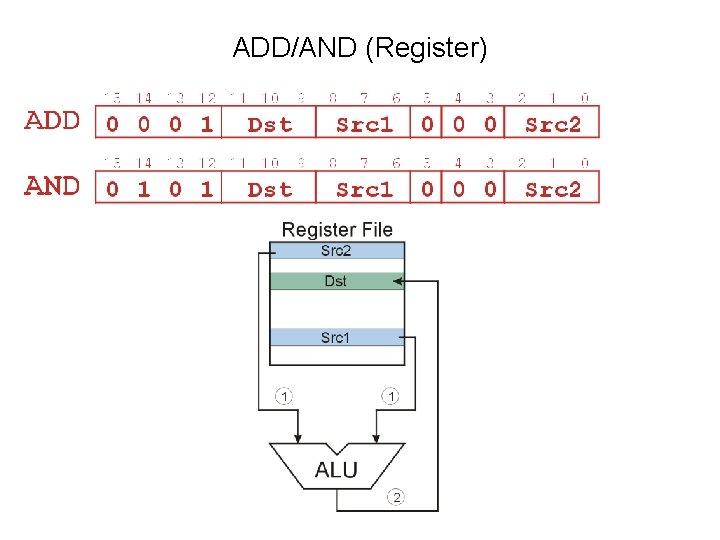

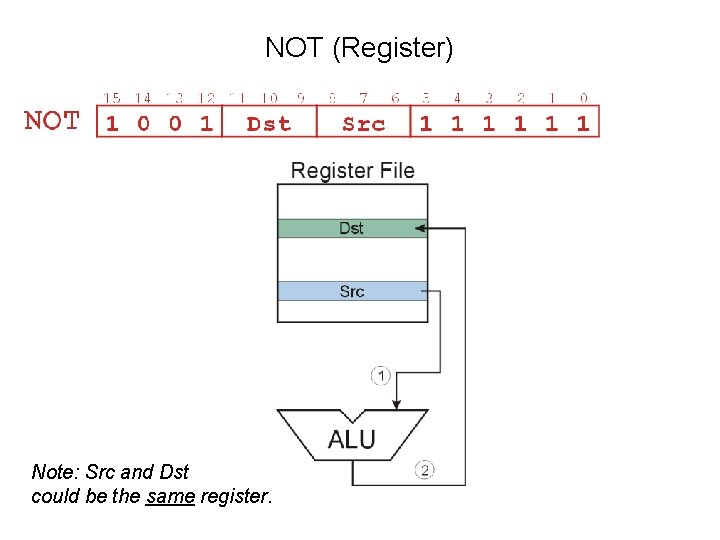

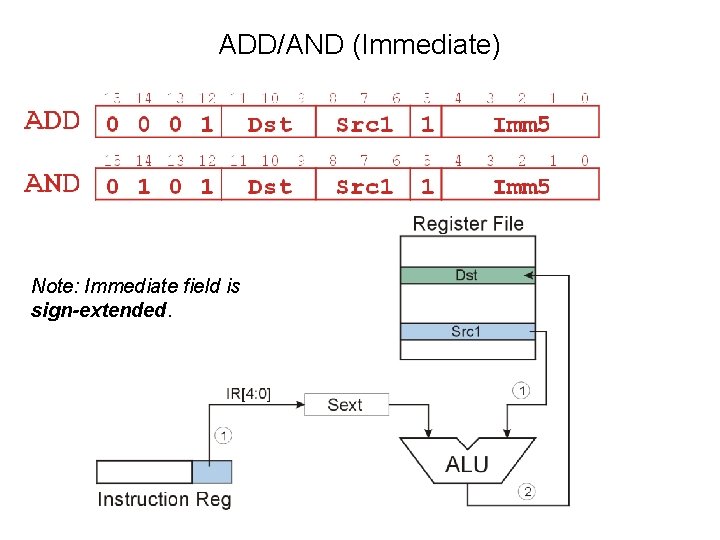

Operate Instructions • Only three operations: ADD, AND, NOT • Source and Destination operands are registers

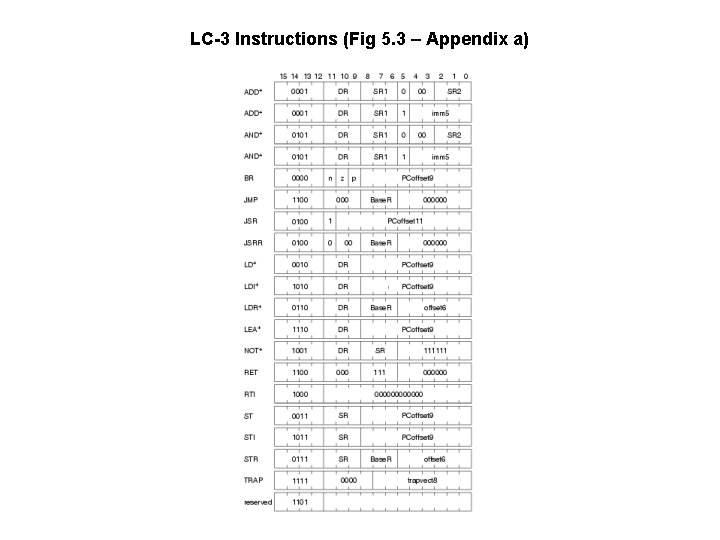

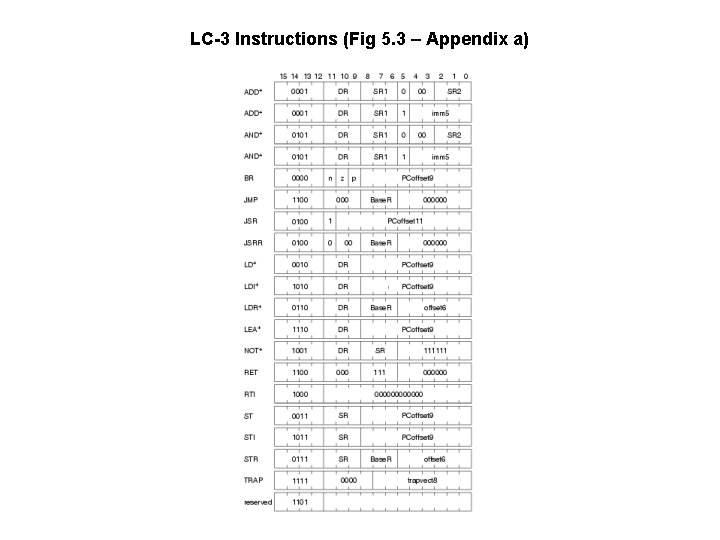

LC-3 Instructions (Fig 5. 3 – Appendix a)

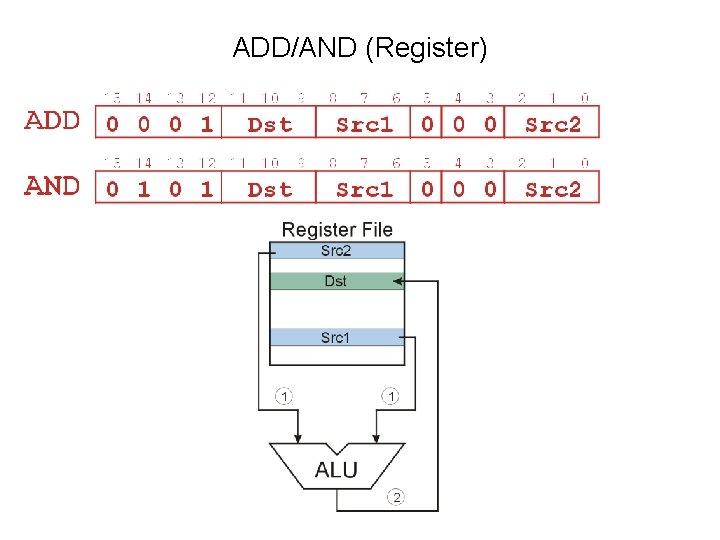

ADD/AND (Register)

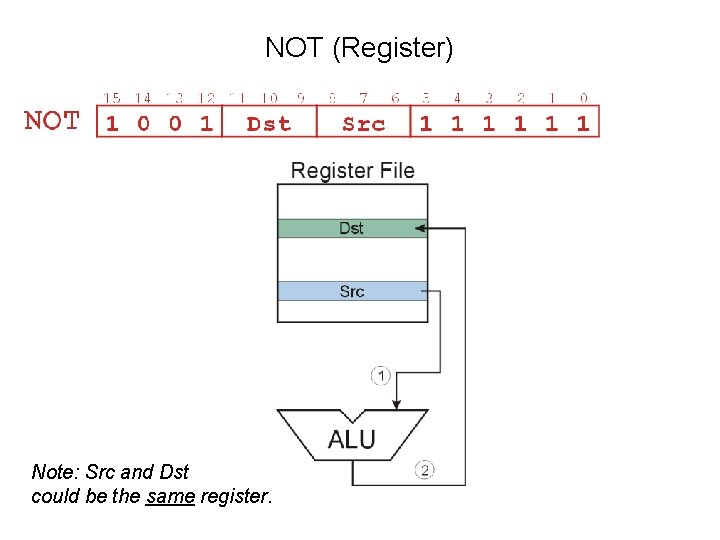

NOT (Register) Note: Src and Dst could be the same register.

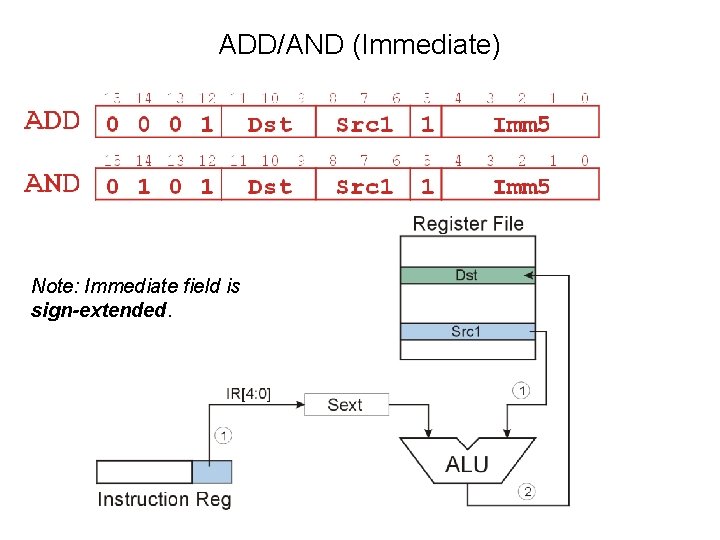

ADD/AND (Immediate) Note: Immediate field is sign-extended.

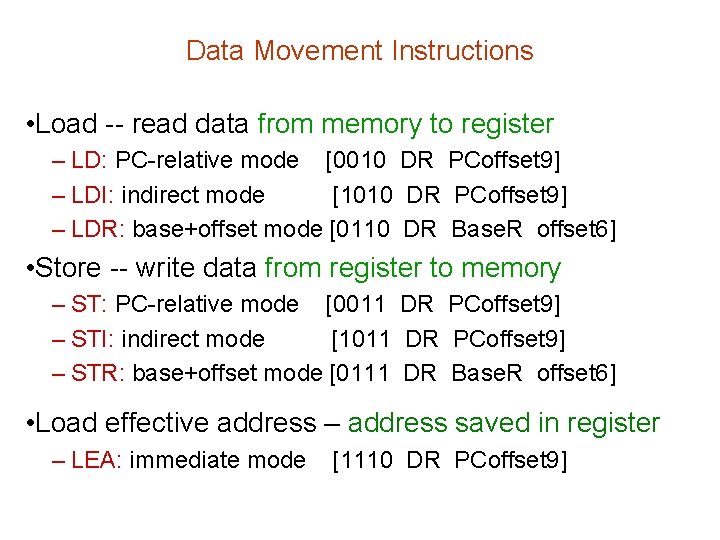

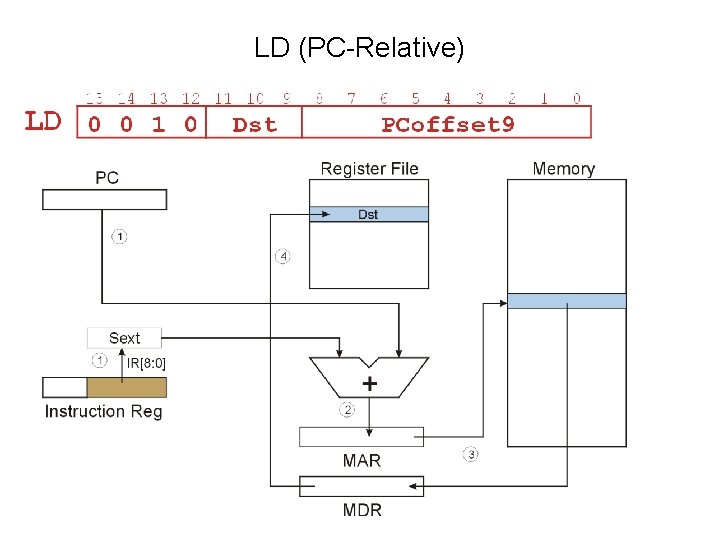

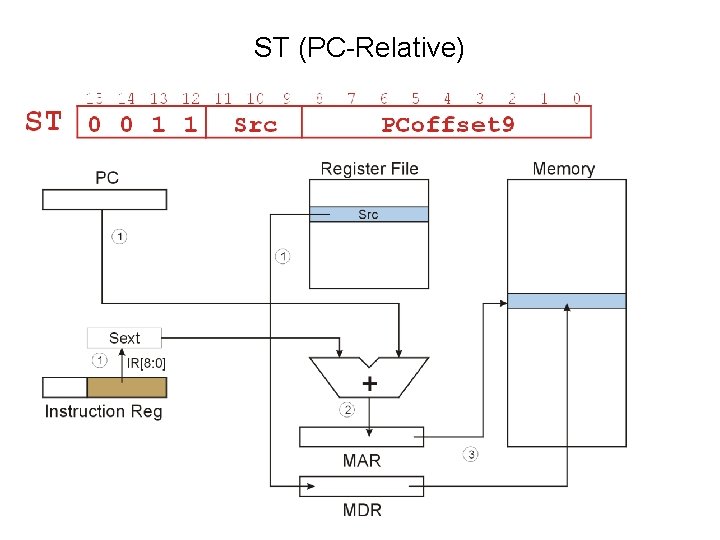

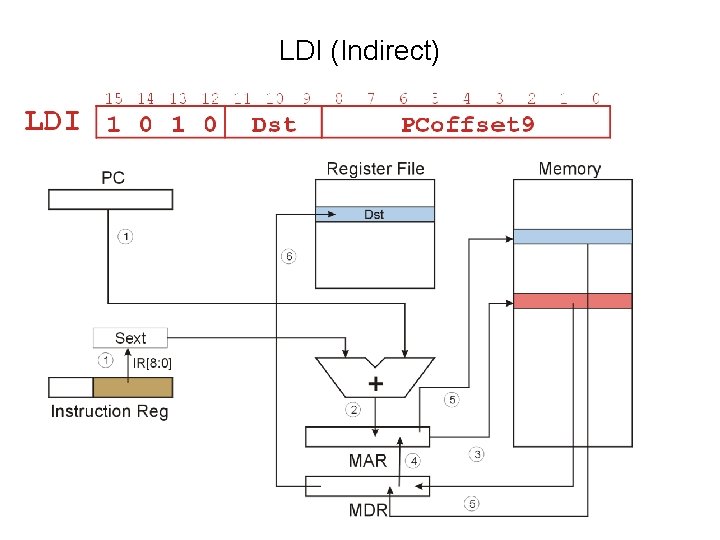

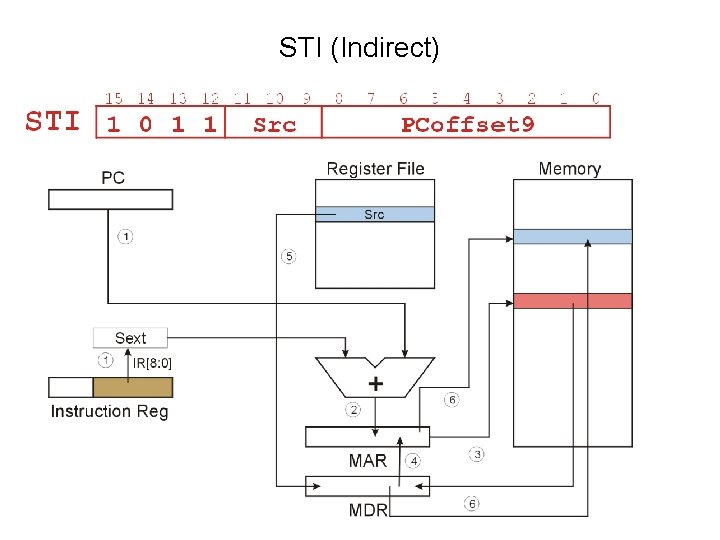

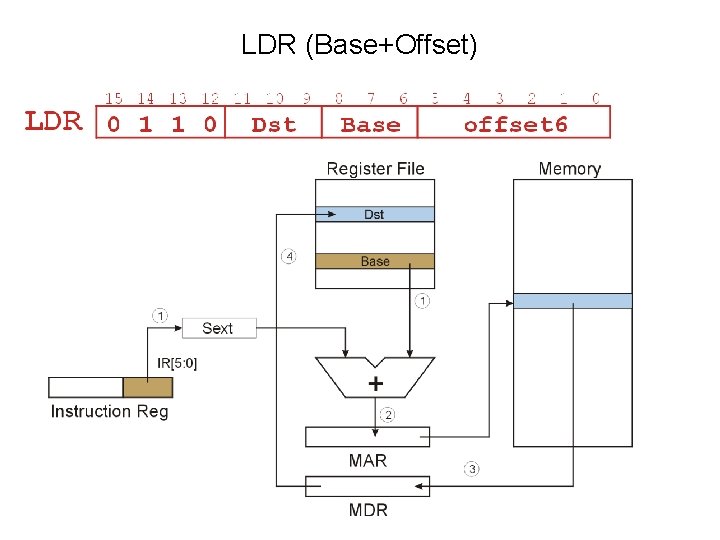

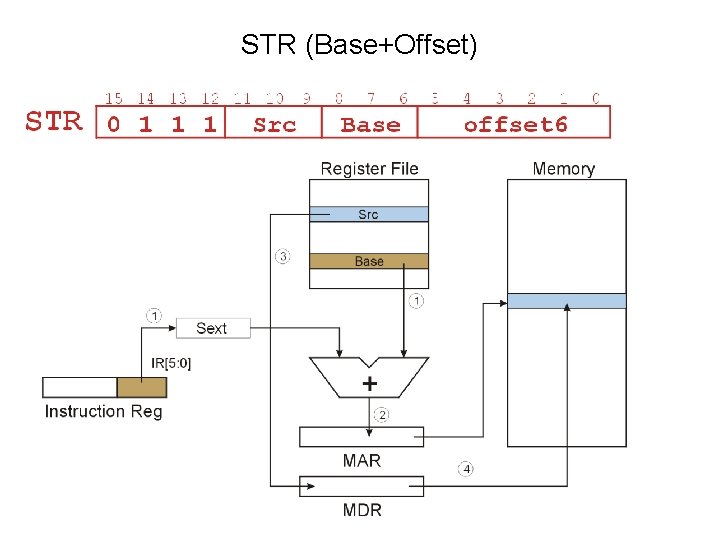

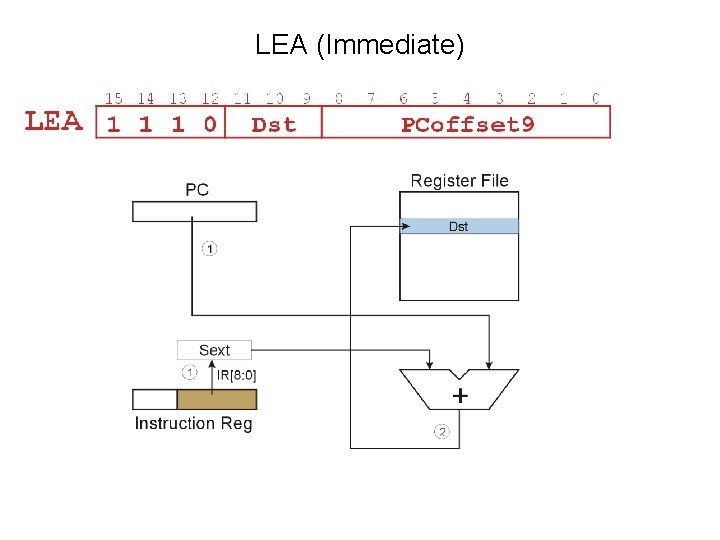

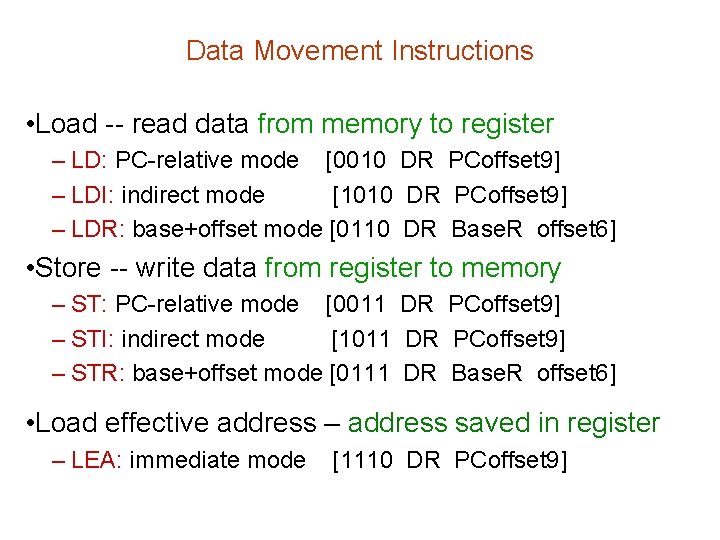

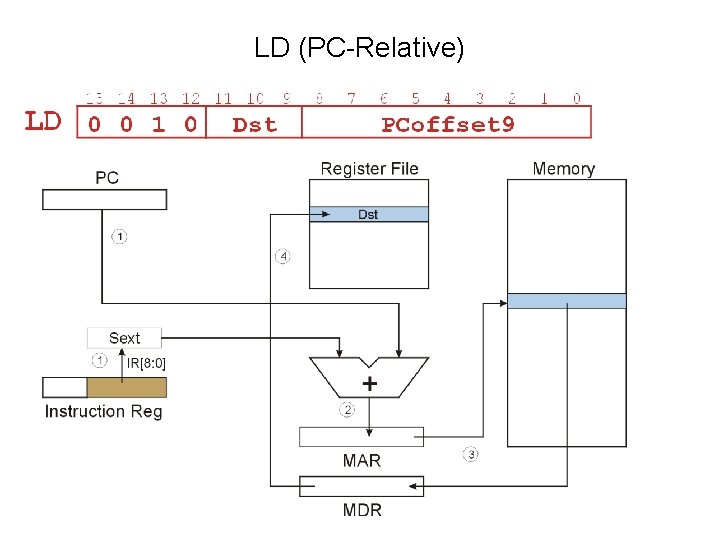

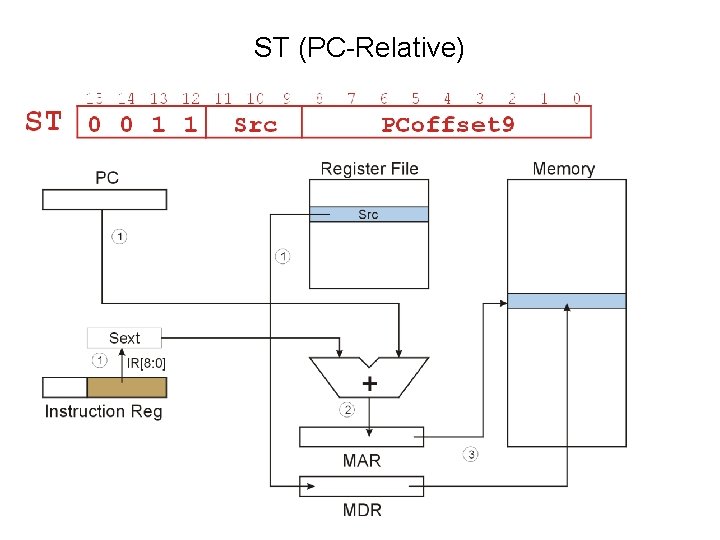

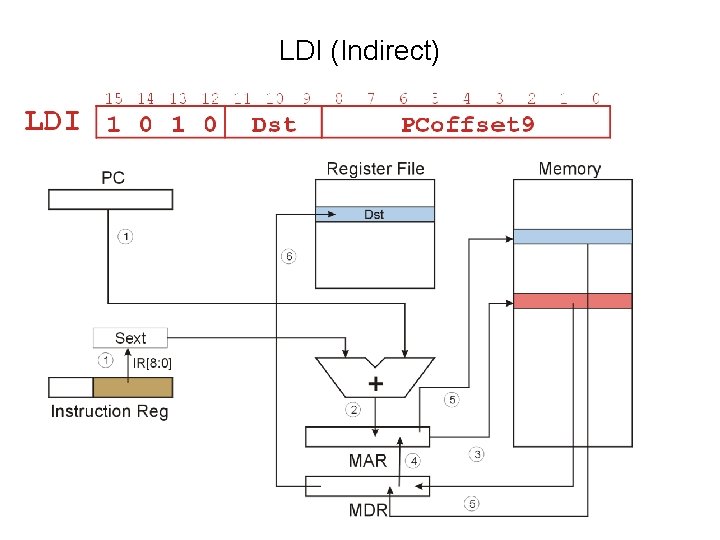

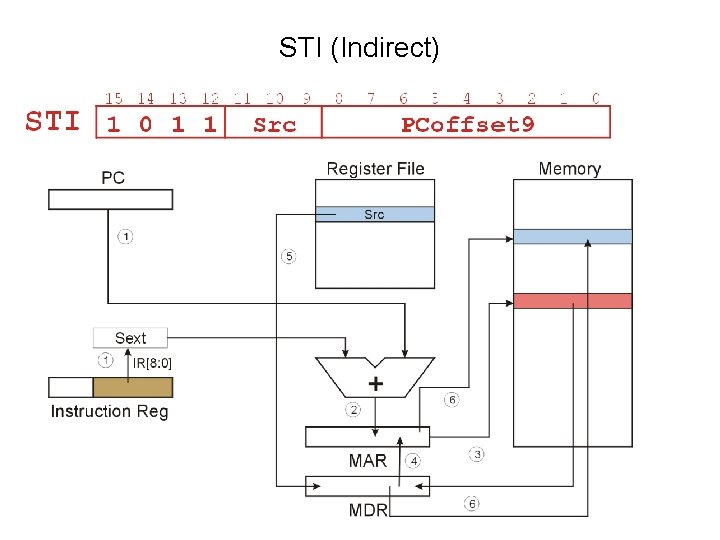

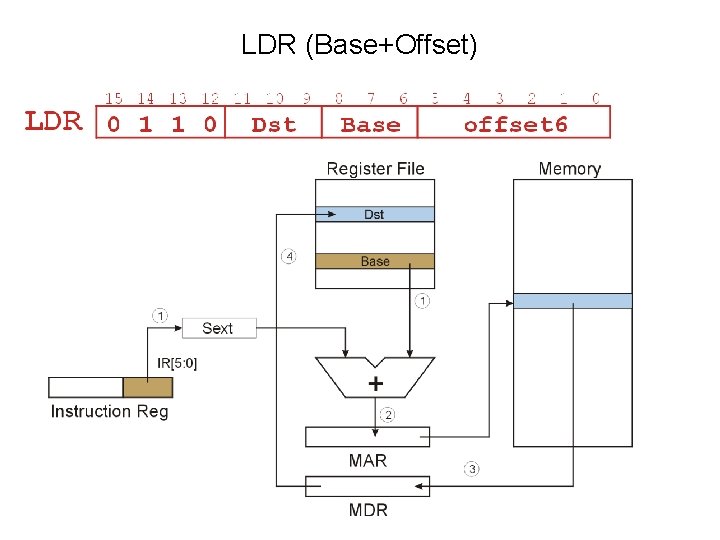

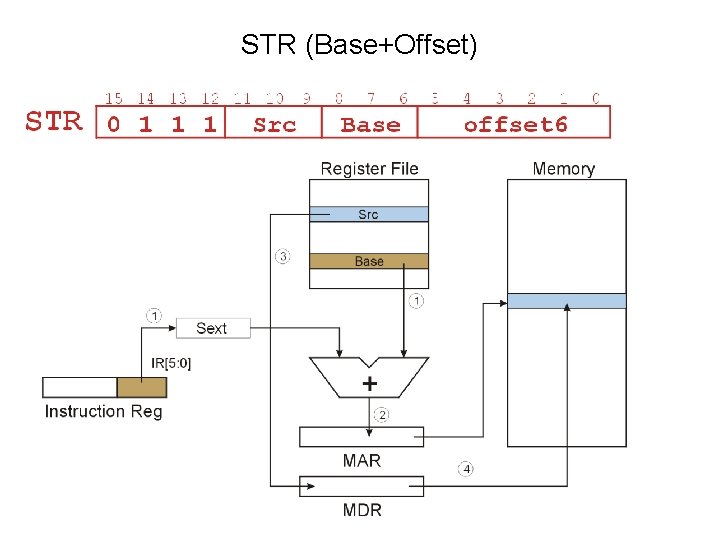

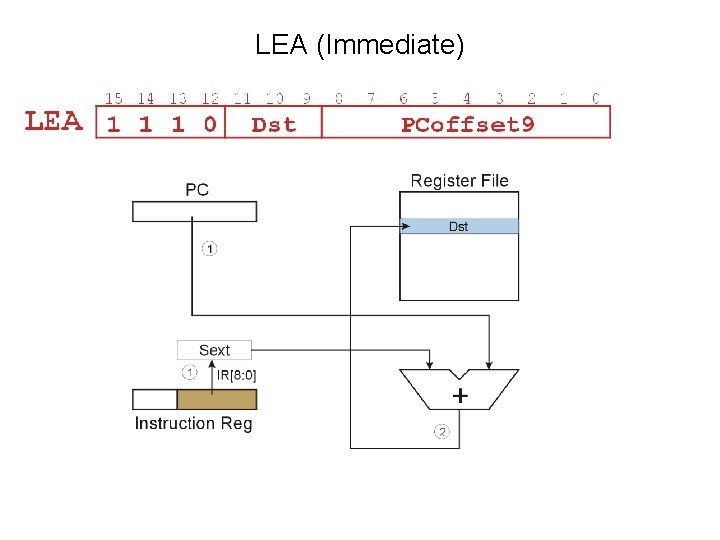

Data Movement Instructions • Load -- read data from memory to register – LD: PC-relative mode [0010 DR PCoffset 9] – LDI: indirect mode [1010 DR PCoffset 9] – LDR: base+offset mode [0110 DR Base. R offset 6] • Store -- write data from register to memory – ST: PC-relative mode [0011 DR PCoffset 9] – STI: indirect mode [1011 DR PCoffset 9] – STR: base+offset mode [0111 DR Base. R offset 6] • Load effective address – address saved in register – LEA: immediate mode [1110 DR PCoffset 9]

LD (PC-Relative)

ST (PC-Relative)

LDI (Indirect)

STI (Indirect)

LDR (Base+Offset)

STR (Base+Offset)

LEA (Immediate)