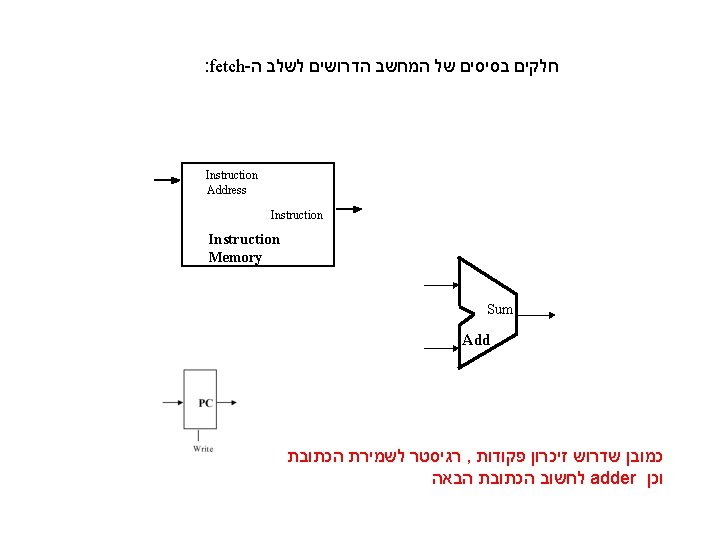

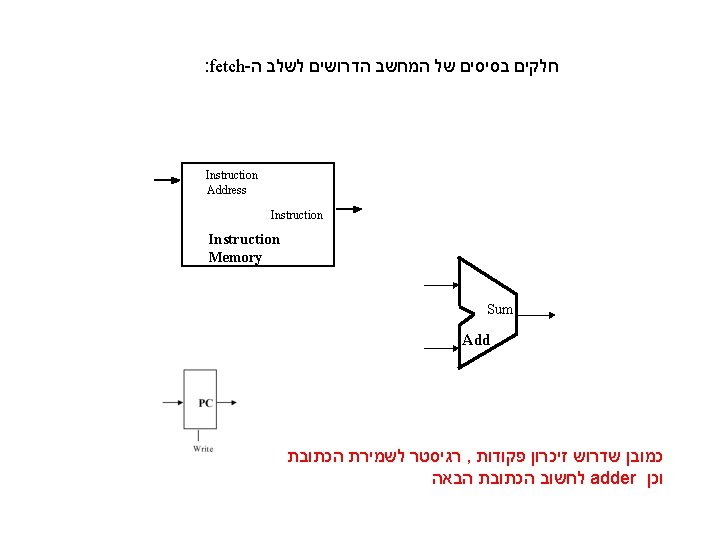

FETCH 4 PC Read address Instruction memory Add

![4 Adde r [31: 26] 6 PC Instruction Memory [25: 21]=Rs 5 [20: 16]=Rt 4 Adde r [31: 26] 6 PC Instruction Memory [25: 21]=Rs 5 [20: 16]=Rt](https://slidetodoc.com/presentation_image_h/31d41bd12f6b00c3c57a44f7785a0a6a/image-7.jpg)

![4 Adde r [31: 26] 6 PC Instruction Memory Reg File [25: 21]=Rs 5 4 Adde r [31: 26] 6 PC Instruction Memory Reg File [25: 21]=Rs 5](https://slidetodoc.com/presentation_image_h/31d41bd12f6b00c3c57a44f7785a0a6a/image-10.jpg)

![4 Adde r [31: 26] 6 PC Instruction Memory Reg File [25: 21]=Rs 5 4 Adde r [31: 26] 6 PC Instruction Memory Reg File [25: 21]=Rs 5](https://slidetodoc.com/presentation_image_h/31d41bd12f6b00c3c57a44f7785a0a6a/image-11.jpg)

![A CPU capable of R-type instructions only 4 Adde r [31: 26] 6 Reg. A CPU capable of R-type instructions only 4 Adde r [31: 26] 6 Reg.](https://slidetodoc.com/presentation_image_h/31d41bd12f6b00c3c57a44f7785a0a6a/image-13.jpg)

![A CPU capable of R-type instructions only Instruction Memory Reg File [25: 21]=Rs 5 A CPU capable of R-type instructions only Instruction Memory Reg File [25: 21]=Rs 5](https://slidetodoc.com/presentation_image_h/31d41bd12f6b00c3c57a44f7785a0a6a/image-14.jpg)

![A CPU capable of R-type instructions only 4 Adde r [31: 26] 6 Reg. A CPU capable of R-type instructions only 4 Adde r [31: 26] 6 Reg.](https://slidetodoc.com/presentation_image_h/31d41bd12f6b00c3c57a44f7785a0a6a/image-16.jpg)

![A CPU capable of lw instructions only 4 Adde r [31: 26] 6 add A CPU capable of lw instructions only 4 Adde r [31: 26] 6 add](https://slidetodoc.com/presentation_image_h/31d41bd12f6b00c3c57a44f7785a0a6a/image-18.jpg)

![4 Adde r [31: 26] 6 add Reg. Write=1 Reg File PC Instruction Memory 4 Adde r [31: 26] 6 add Reg. Write=1 Reg File PC Instruction Memory](https://slidetodoc.com/presentation_image_h/31d41bd12f6b00c3c57a44f7785a0a6a/image-19.jpg)

![A CPU capable of lw instructions only 4 Adde r [31: 26] 6 add A CPU capable of lw instructions only 4 Adde r [31: 26] 6 add](https://slidetodoc.com/presentation_image_h/31d41bd12f6b00c3c57a44f7785a0a6a/image-20.jpg)

![A CPU capable of R-type & lw instructions (principle) 4 Adde r [31: 26] A CPU capable of R-type & lw instructions (principle) 4 Adde r [31: 26]](https://slidetodoc.com/presentation_image_h/31d41bd12f6b00c3c57a44f7785a0a6a/image-22.jpg)

![A CPU capable of R-type & lw instructions 4 Adde r [31: 26] 6 A CPU capable of R-type & lw instructions 4 Adde r [31: 26] 6](https://slidetodoc.com/presentation_image_h/31d41bd12f6b00c3c57a44f7785a0a6a/image-23.jpg)

![Control 0 M u x Add 4 Instruction [31– 26] PC Instruction memory Instruction Control 0 M u x Add 4 Instruction [31– 26] PC Instruction memory Instruction](https://slidetodoc.com/presentation_image_h/31d41bd12f6b00c3c57a44f7785a0a6a/image-29.jpg)

![Jump Instruction [25– 0] 26 Shift left 2 Jump address [31– 0] 28 0 Jump Instruction [25– 0] 26 Shift left 2 Jump address [31– 0] 28 0](https://slidetodoc.com/presentation_image_h/31d41bd12f6b00c3c57a44f7785a0a6a/image-33.jpg)

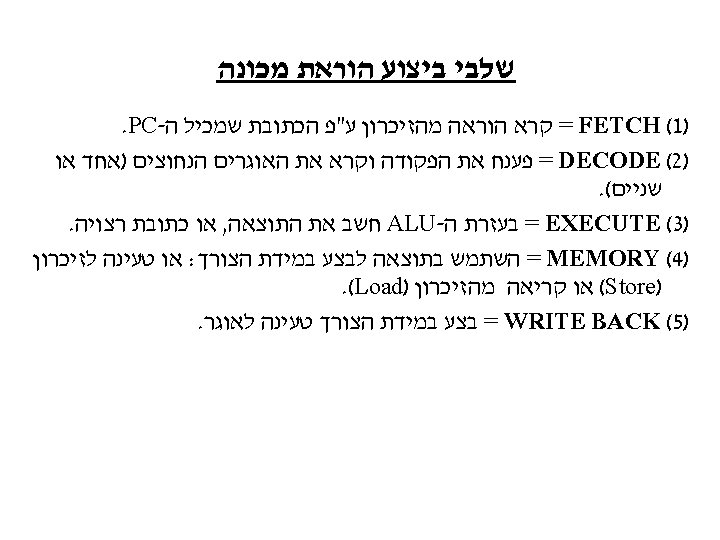

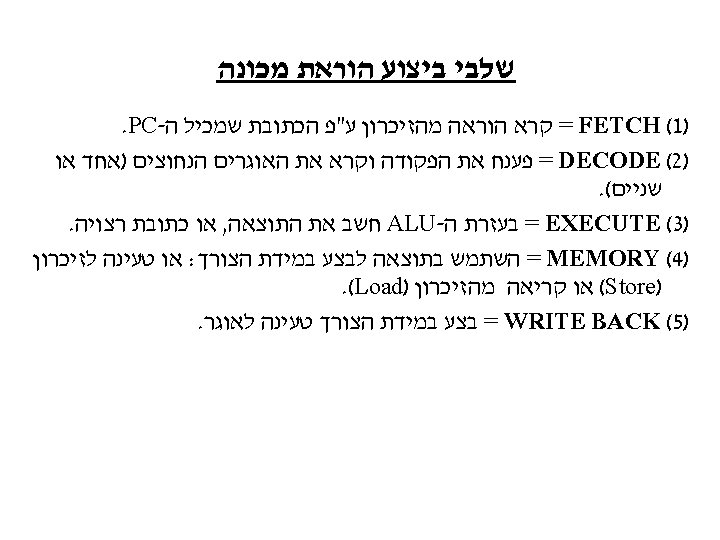

- Slides: 33

FETCH - שלב ה 4 PC Read address Instruction memory Add

![4 Adde r 31 26 6 PC Instruction Memory 25 21Rs 5 20 16Rt 4 Adde r [31: 26] 6 PC Instruction Memory [25: 21]=Rs 5 [20: 16]=Rt](https://slidetodoc.com/presentation_image_h/31d41bd12f6b00c3c57a44f7785a0a6a/image-7.jpg)

4 Adde r [31: 26] 6 PC Instruction Memory [25: 21]=Rs 5 [20: 16]=Rt 5 [15: 11]=Rd 5 ck A CPU capable of R-type instructions only [5: 0]=funct 6

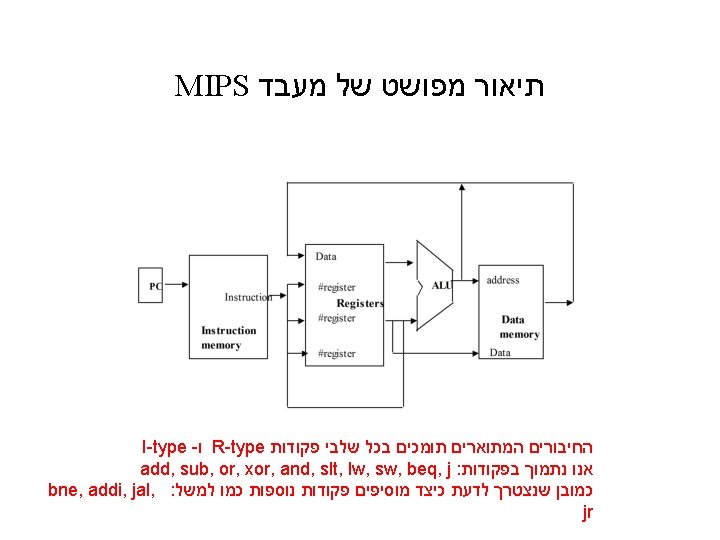

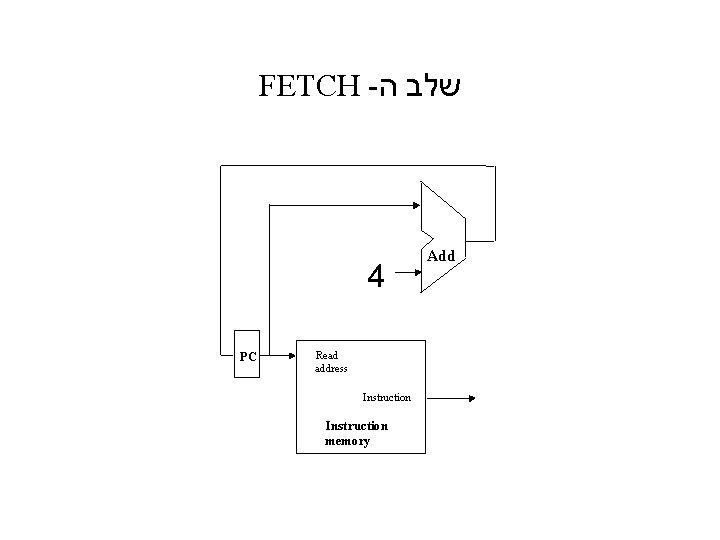

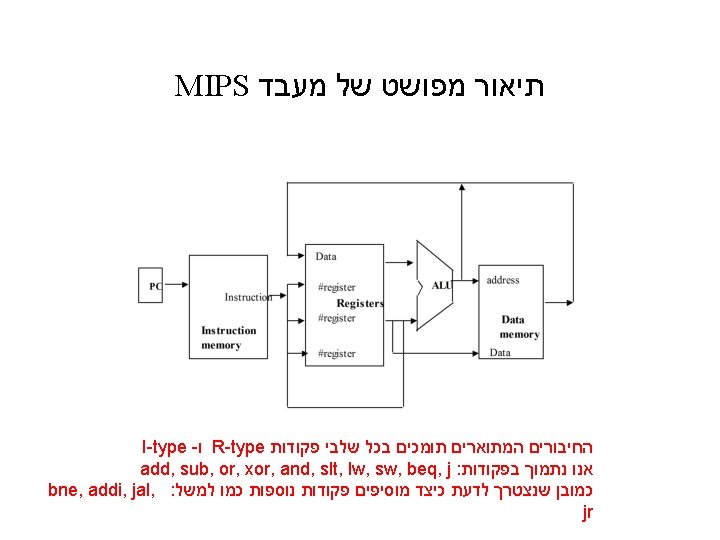

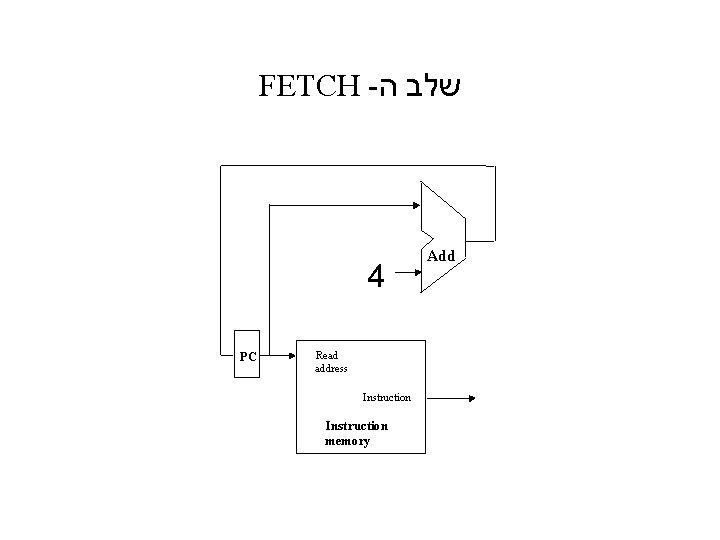

decode- יחידה זו דרושה לשלב ה. יחידת הרגיסטרים (write back- )ולשלב ה Read register 1 מספרי האוגרים Read register 2 Read data 1 Registers Write register Data Write Data Read data 2

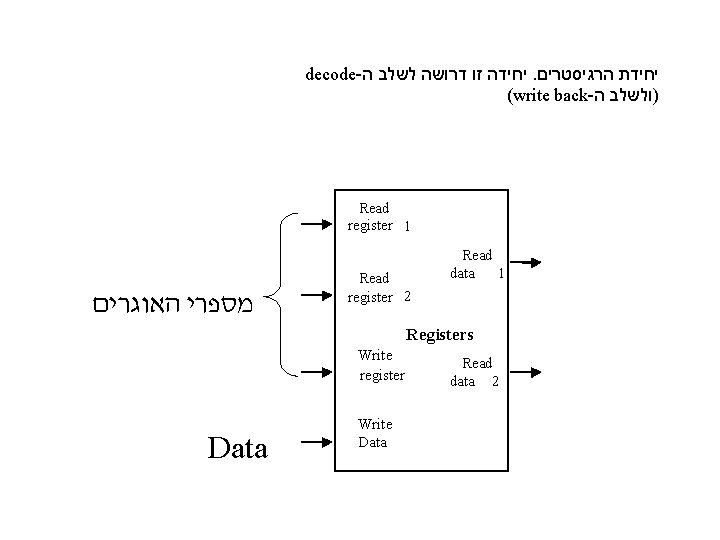

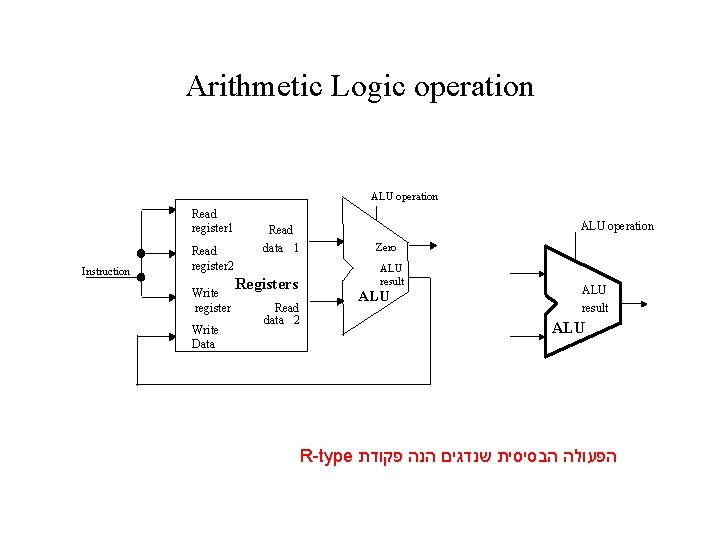

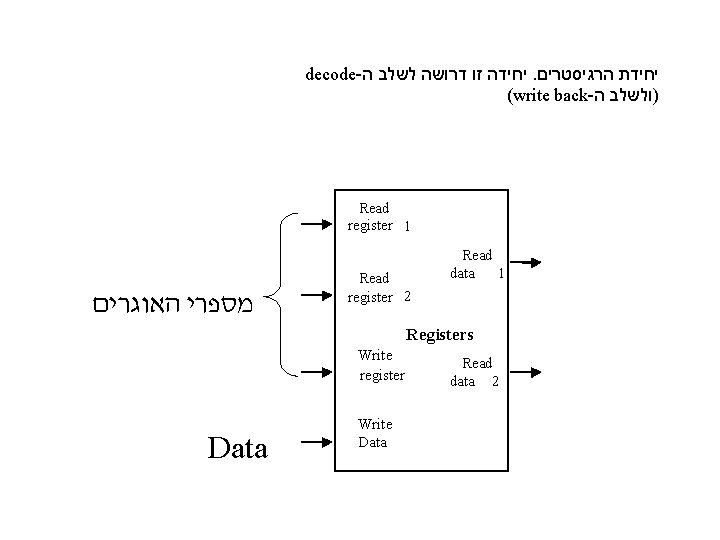

Arithmetic Logic operation ALU operation Read register 1 Instruction Read register 2 Write register Write Data Read data 1 Registers Read data 2 ALU operation Zero ALU result ALU R-type הפעולה הבסיסית שנדגים הנה פקודת

![4 Adde r 31 26 6 PC Instruction Memory Reg File 25 21Rs 5 4 Adde r [31: 26] 6 PC Instruction Memory Reg File [25: 21]=Rs 5](https://slidetodoc.com/presentation_image_h/31d41bd12f6b00c3c57a44f7785a0a6a/image-10.jpg)

4 Adde r [31: 26] 6 PC Instruction Memory Reg File [25: 21]=Rs 5 ALU [20: 16]=Rt 5 [15: 11]=Rd 5 ck [5: 0]=funct 6 ck A CPU capable of R-type instructions only

![4 Adde r 31 26 6 PC Instruction Memory Reg File 25 21Rs 5 4 Adde r [31: 26] 6 PC Instruction Memory Reg File [25: 21]=Rs 5](https://slidetodoc.com/presentation_image_h/31d41bd12f6b00c3c57a44f7785a0a6a/image-11.jpg)

4 Adde r [31: 26] 6 PC Instruction Memory Reg File [25: 21]=Rs 5 ALU [20: 16]=Rt 5 [15: 11]=Rd 5 ck [5: 0]=funct 6 ck A CPU capable of R-type instructions only

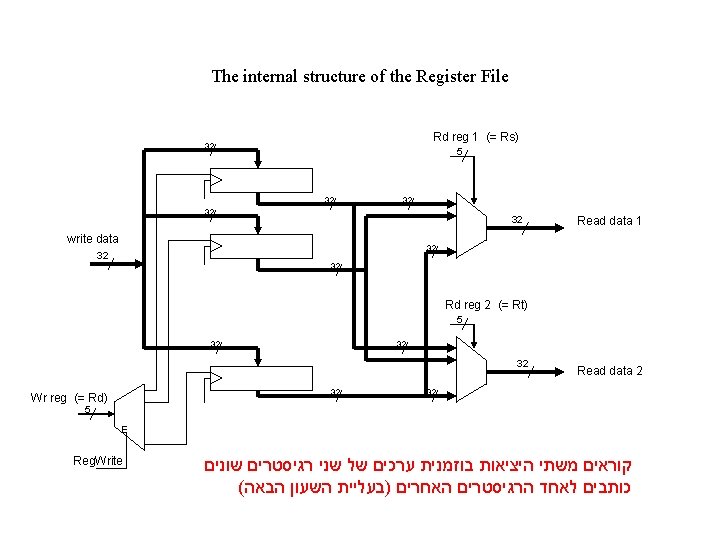

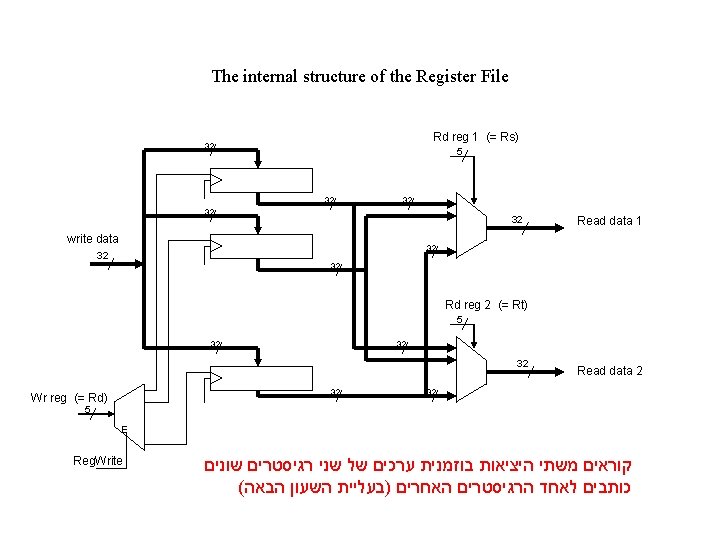

The internal structure of the Register File Rd reg 1 (= Rs) 32 5 32 32 write data Read data 1 32 32 32 Rd reg 2 (= Rt) 5 32 32 Wr reg (= Rd) Read data 2 32 5 E Reg. Write קוראים משתי היציאות בוזמנית ערכים של שני רגיסטרים שונים ( כותבים לאחד הרגיסטרים האחרים )בעליית השעון הבאה

![A CPU capable of Rtype instructions only 4 Adde r 31 26 6 Reg A CPU capable of R-type instructions only 4 Adde r [31: 26] 6 Reg.](https://slidetodoc.com/presentation_image_h/31d41bd12f6b00c3c57a44f7785a0a6a/image-13.jpg)

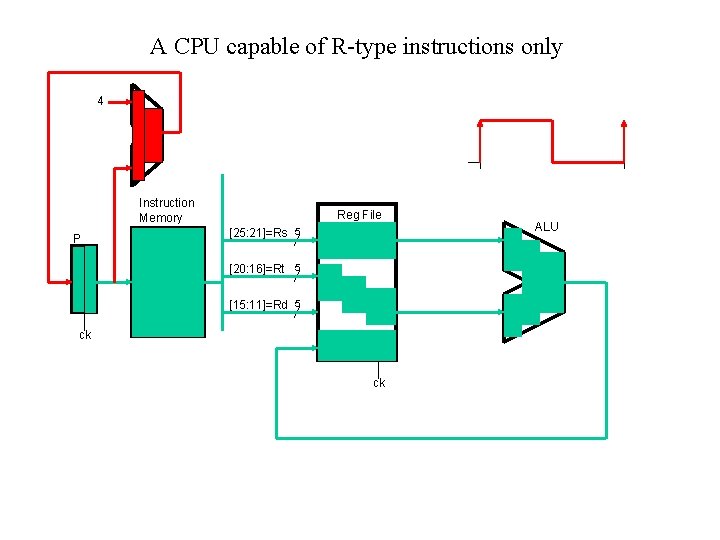

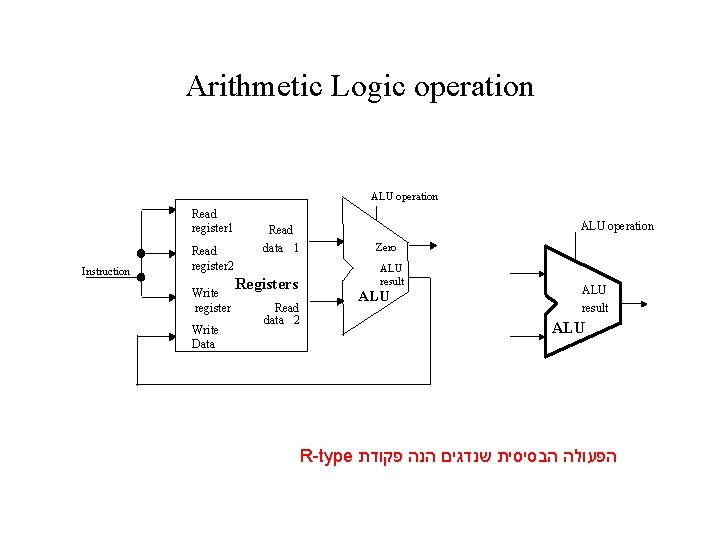

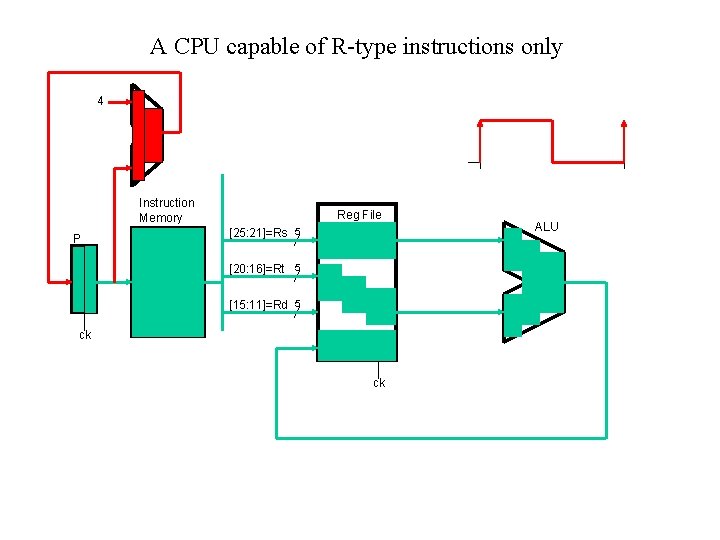

A CPU capable of R-type instructions only 4 Adde r [31: 26] 6 Reg. Write Reg File PC Instruction Memory [25: 21]=Rs 5 ALU [20: 16]=Rt 5 [15: 11]=Rd 5 ck ck

![A CPU capable of Rtype instructions only Instruction Memory Reg File 25 21Rs 5 A CPU capable of R-type instructions only Instruction Memory Reg File [25: 21]=Rs 5](https://slidetodoc.com/presentation_image_h/31d41bd12f6b00c3c57a44f7785a0a6a/image-14.jpg)

A CPU capable of R-type instructions only Instruction Memory Reg File [25: 21]=Rs 5 PC ALU [20: 16]=Rt 5 [15: 11]=Rd 5 ck ck

A CPU capable of R-type instructions only 4 Instruction Memory P C Reg File [25: 21]=Rs 5 [20: 16]=Rt 5 [15: 11]=Rd 5 ck ck ALU

![A CPU capable of Rtype instructions only 4 Adde r 31 26 6 Reg A CPU capable of R-type instructions only 4 Adde r [31: 26] 6 Reg.](https://slidetodoc.com/presentation_image_h/31d41bd12f6b00c3c57a44f7785a0a6a/image-16.jpg)

A CPU capable of R-type instructions only 4 Adde r [31: 26] 6 Reg. Write [5: 0]=funct 6 ALU control Reg File PC Instruction Memory [25: 21]=Rs 5 ALU [20: 16]=Rt 5 [15: 11]=Rd 5 ck ck

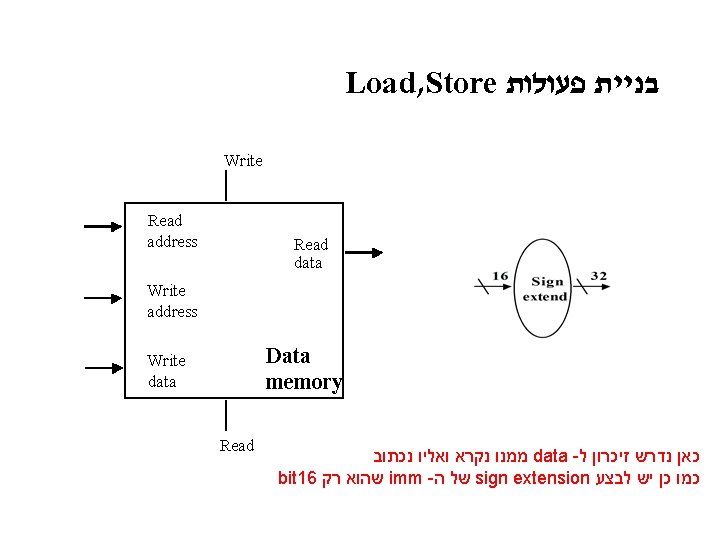

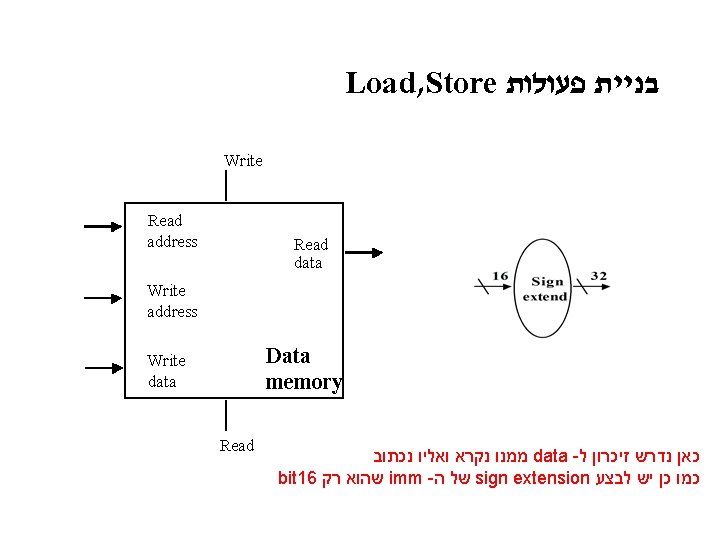

Load, Store בניית פעולות Write Read address Read data Write address Data memory Write data Read ממנו נקרא ואליו נכתוב data - כאן נדרש זיכרון ל bit 16 שהוא רק imm - של ה sign extension כמו כן יש לבצע

![A CPU capable of lw instructions only 4 Adde r 31 26 6 add A CPU capable of lw instructions only 4 Adde r [31: 26] 6 add](https://slidetodoc.com/presentation_image_h/31d41bd12f6b00c3c57a44f7785a0a6a/image-18.jpg)

A CPU capable of lw instructions only 4 Adde r [31: 26] 6 add Reg. Write=1 Reg File PC Instruction Memory [25: 21]=Rs 5 ALU [20: 16]=Rt 5 Address 5 ck ck [15: 0] Data Memory 16 Sext 16 ->32 D. Out

![4 Adde r 31 26 6 add Reg Write1 Reg File PC Instruction Memory 4 Adde r [31: 26] 6 add Reg. Write=1 Reg File PC Instruction Memory](https://slidetodoc.com/presentation_image_h/31d41bd12f6b00c3c57a44f7785a0a6a/image-19.jpg)

4 Adde r [31: 26] 6 add Reg. Write=1 Reg File PC Instruction Memory [25: 21]=Rs 5 ALU [20: 16]=Rt 5 Address 5 ck ck [15: 0] 16 Sext 16 ->32 A CPU capable of lw instructions only Data Memory D. Out

![A CPU capable of lw instructions only 4 Adde r 31 26 6 add A CPU capable of lw instructions only 4 Adde r [31: 26] 6 add](https://slidetodoc.com/presentation_image_h/31d41bd12f6b00c3c57a44f7785a0a6a/image-20.jpg)

A CPU capable of lw instructions only 4 Adde r [31: 26] 6 add Reg. Write=1 Reg File PC Instruction Memory [25: 21]=Rs 5 ALU [20: 16]=Rt 5 Address 5 ck ck [15: 0] Data Memory 16 Sext 16 ->32 D. Out

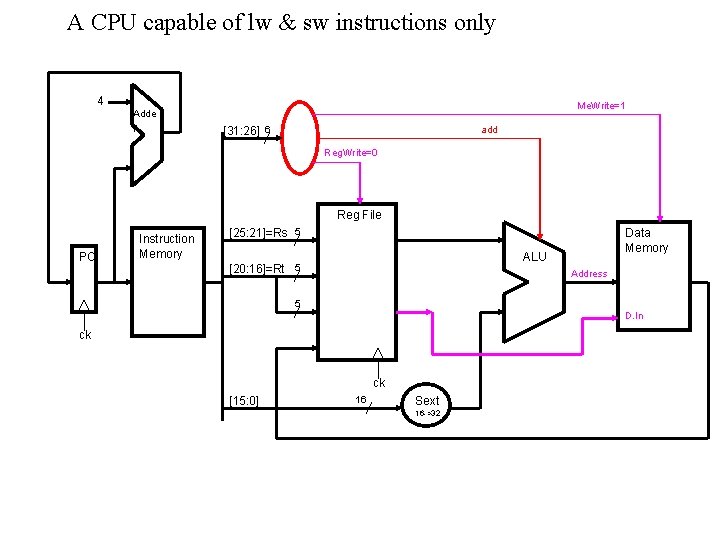

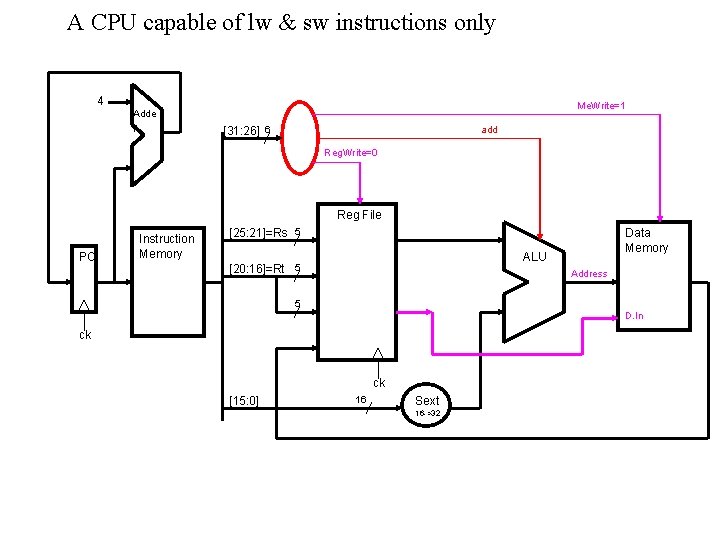

A CPU capable of lw & sw instructions only 4 Me. Write=1 Adde r [31: 26] 6 add Reg. Write=0 Reg File PC Instruction Memory [25: 21]=Rs 5 Data Memory ALU [20: 16]=Rt 5 Address 5 D. In ck ck [15: 0] 16 Sext 16 ->32

![A CPU capable of Rtype lw instructions principle 4 Adde r 31 26 A CPU capable of R-type & lw instructions (principle) 4 Adde r [31: 26]](https://slidetodoc.com/presentation_image_h/31d41bd12f6b00c3c57a44f7785a0a6a/image-22.jpg)

A CPU capable of R-type & lw instructions (principle) 4 Adde r [31: 26] 6 add Reg. Write [5: 0]=funct 6 ALU control Reg File PC Instruction Memory [25: 21]=Rs 5 ALU [20: 16]=Rt 5 Address [15: 11]=Rd 5 ck ck [15: 0] Data Memory 16 Sext 16 ->32

![A CPU capable of Rtype lw instructions 4 Adde r 31 26 6 A CPU capable of R-type & lw instructions 4 Adde r [31: 26] 6](https://slidetodoc.com/presentation_image_h/31d41bd12f6b00c3c57a44f7785a0a6a/image-23.jpg)

A CPU capable of R-type & lw instructions 4 Adde r [31: 26] 6 add Reg. Write [5: 0]=funct 6 ALU control Reg File PC Instruction Memory [25: 21]=Rs 5 ALU [20: 16]=Rt 5 Address 5 Rd ck [15: 0] Data Memory 16 ck Sext 16 ->32 D. Out

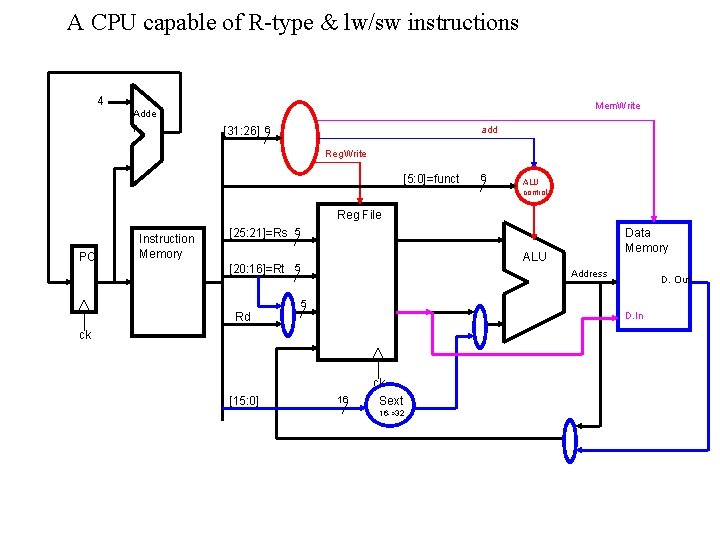

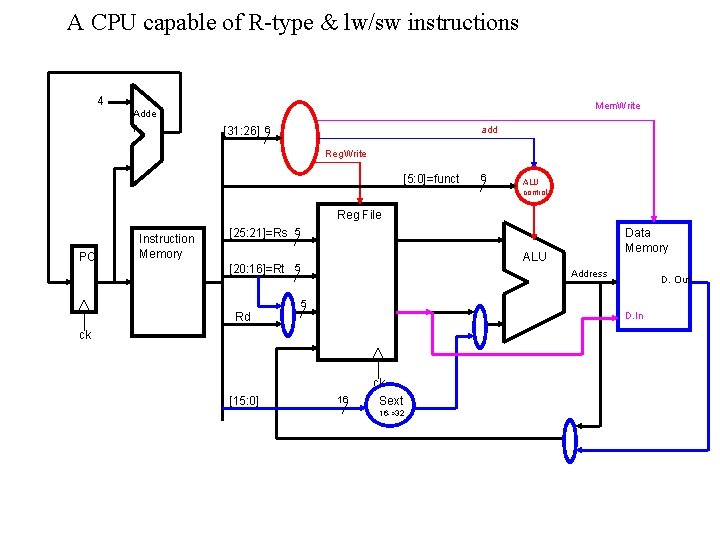

A CPU capable of R-type & lw/sw instructions 4 Mem. Write Adde r [31: 26] 6 add Reg. Write [5: 0]=funct 6 ALU control Reg File PC Instruction Memory [25: 21]=Rs 5 Data Memory ALU [20: 16]=Rt 5 Address D. Out 5 D. In Rd ck [15: 0] 16 ck Sext 16 ->32

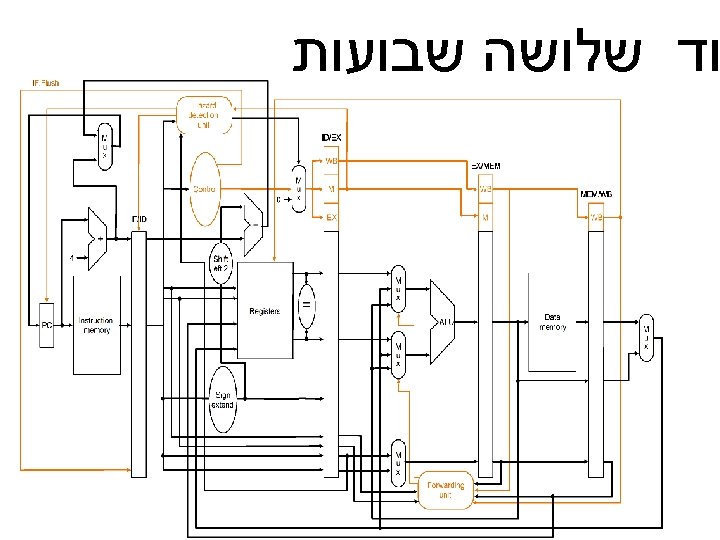

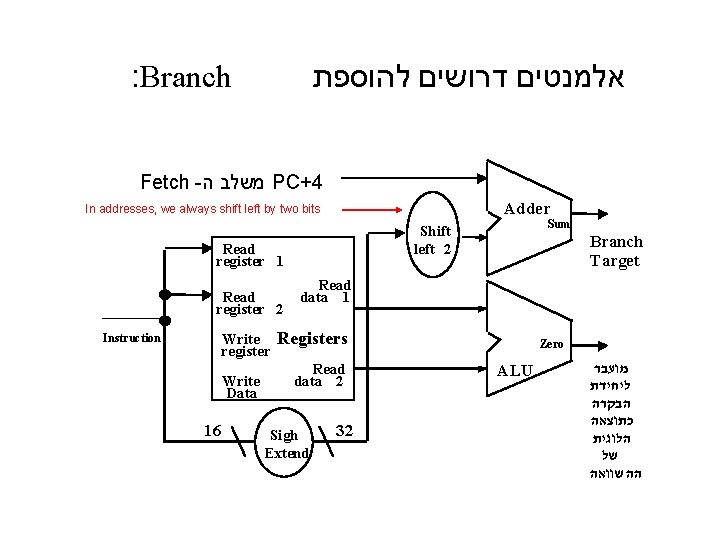

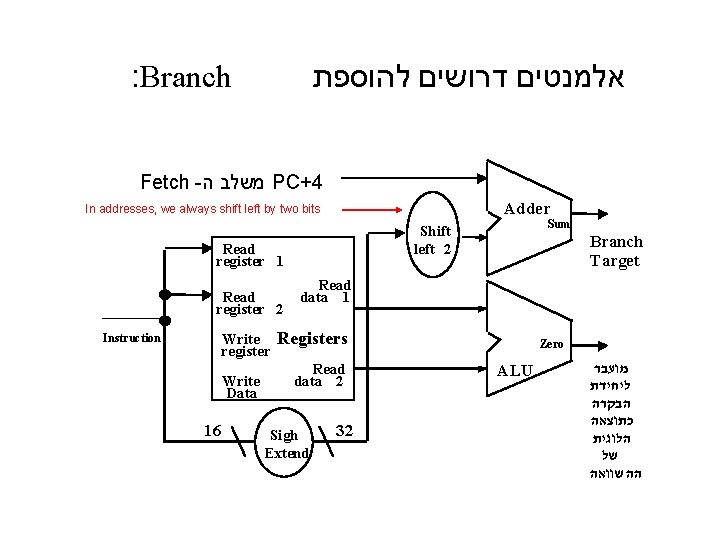

: Branch אלמנטים דרושים להוספת Fetch - משלב ה PC+4 Adder In addresses, we always shift left by two bits Read register 1 Read register 2 Instruction Write register Write Data 16 Sum Shift left 2 Branch Target Read data 1 Registers Read data 2 Sigh Extend 32 Zero ALU מועבר ליחידת הבקרה כתוצאה הלוגית של ההשוואה

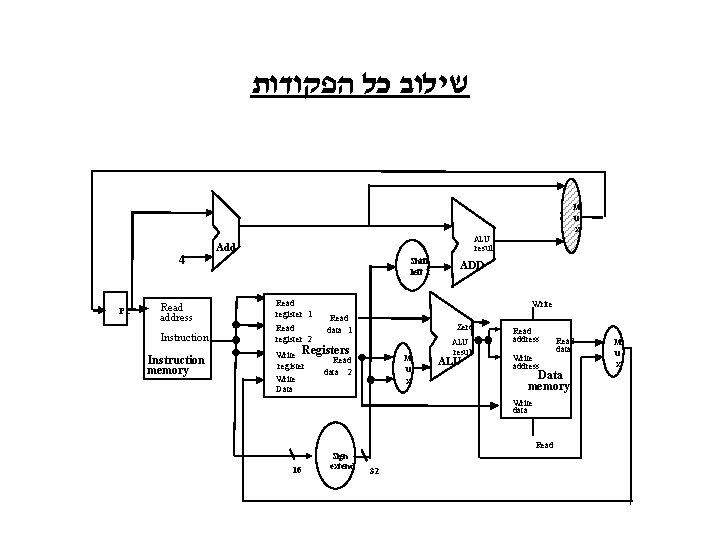

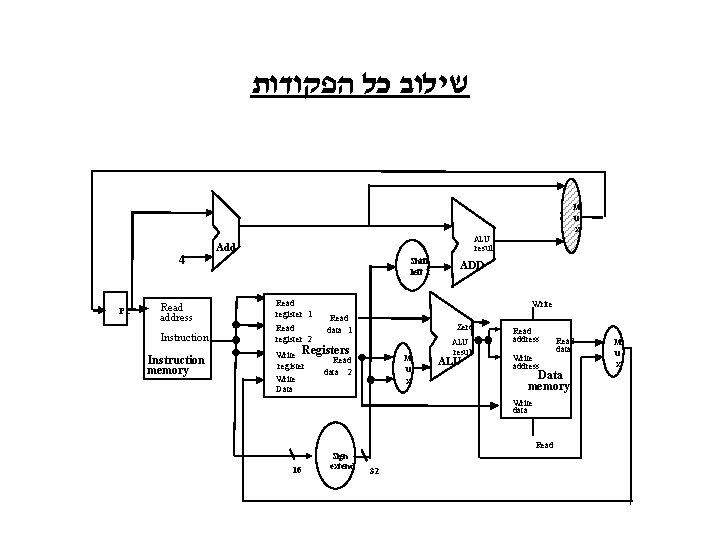

שילוב כל הפקודות M u x ALU Add result 4 PC Read address Instruction memory Shift left 2 Read register 1 Read register 2 Write Read data 1 Zero ALU Registers Write register Write Data ADD M u x Read data 2 result ALU Read address Write address Data memory Write data Read 16 Sign extend 32 Read data M u x

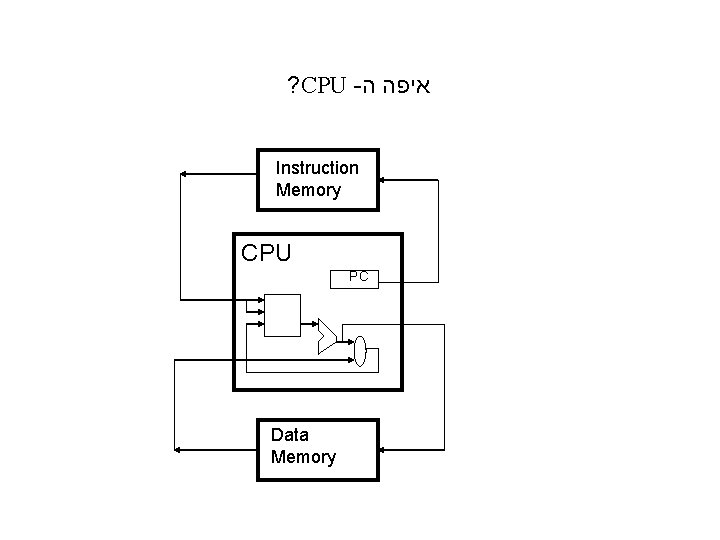

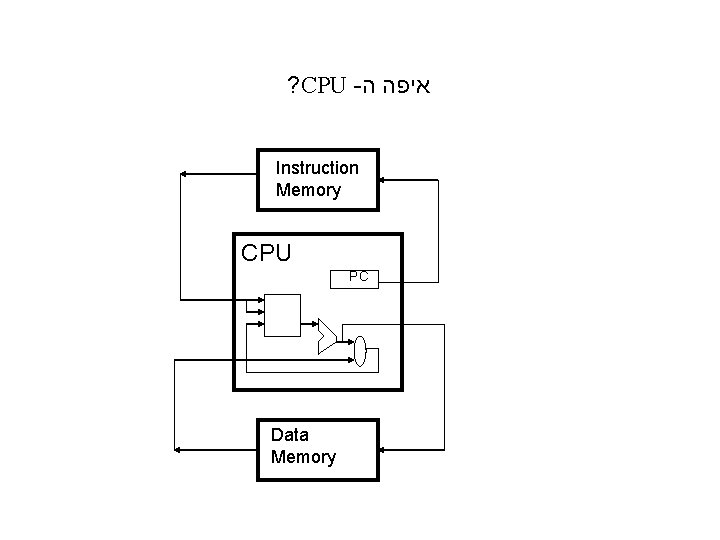

? CPU - איפה ה Instruction Memory CPU PC Data Memory

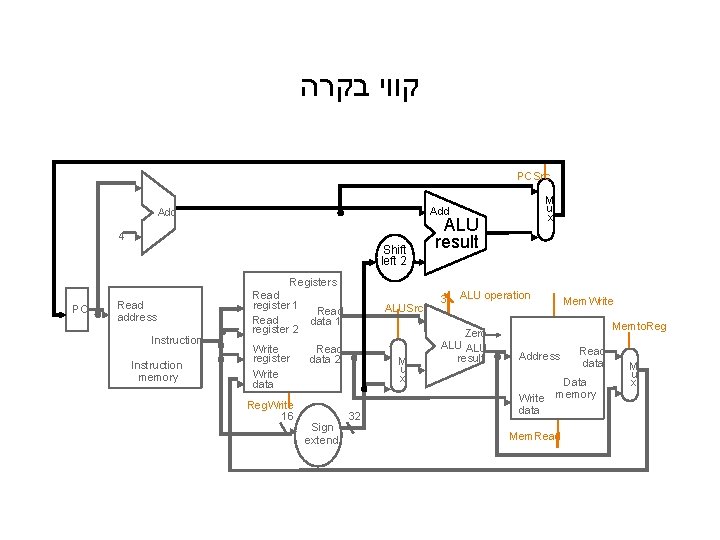

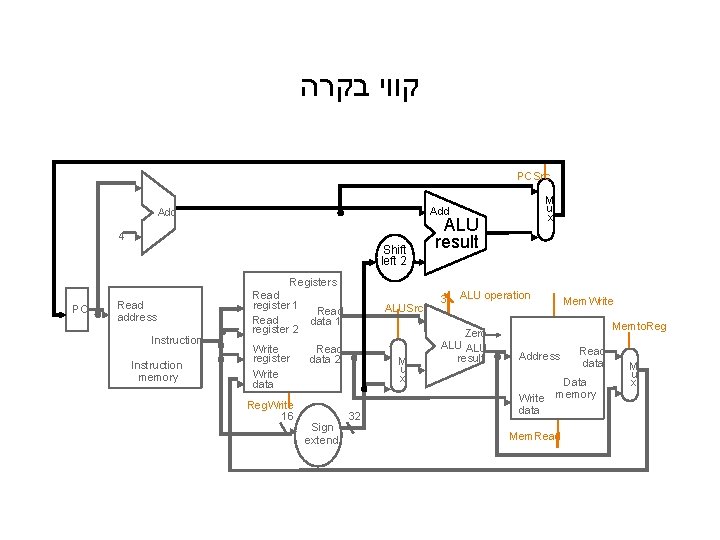

קווי בקרה PCSrc 4 Shift left 2 PC Read address Instruction memory M u x Add Registers Read register 1 Read data 1 register 2 Write register Write data Reg. Write 16 ALUSrc Read data 2 Sign extend M u x 32 ALU result 3 ALU operation Zero ALU result Mem Write Memto. Reg Address Write data Read data Data memory Mem. Read M u x

![Control 0 M u x Add 4 Instruction 31 26 PC Instruction memory Instruction Control 0 M u x Add 4 Instruction [31– 26] PC Instruction memory Instruction](https://slidetodoc.com/presentation_image_h/31d41bd12f6b00c3c57a44f7785a0a6a/image-29.jpg)

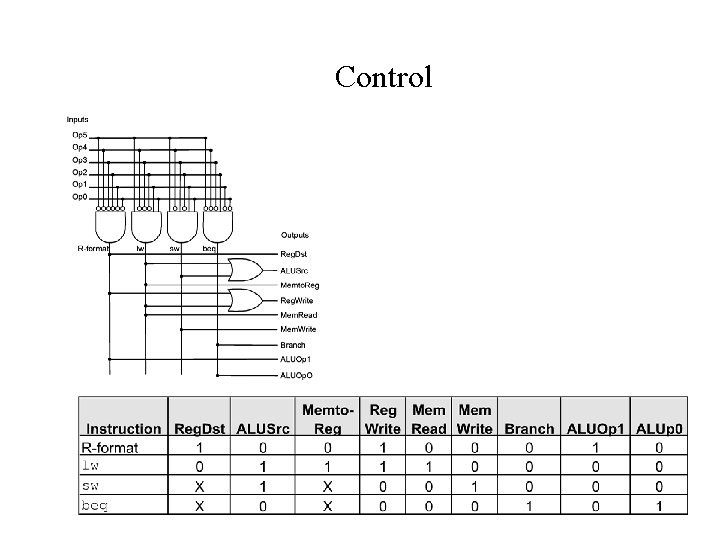

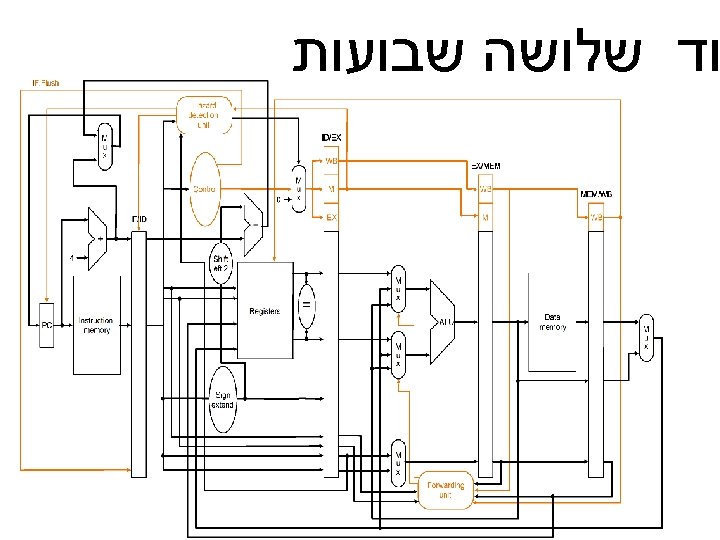

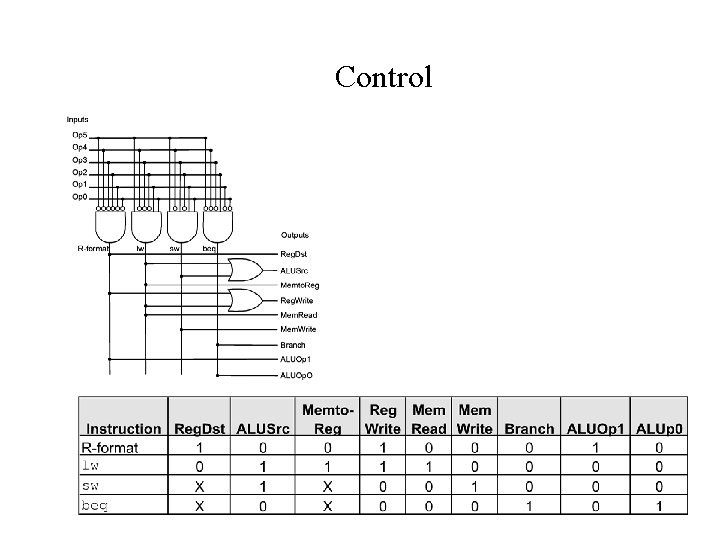

Control 0 M u x Add 4 Instruction [31– 26] PC Instruction memory Instruction [15– 11] Zero ALU result Address Read register 1 Instruction [20– 16] Instruction [31– 0] 1 Shift left 2 Reg. Dst Branch Mem. Read Memto. Reg Control ALUOp Mem. Write ALUSrc Reg. Write Instruction [25– 21] Read address ALU Add result 0 M u x 1 Read data 1 Read register 2 Registers Read Write data 2 register 0 M u x 1 Write data Instruction [15– 0] 16 Instruction [5– 0] Sign extend 32 ALU control d Rea a dat Data memory 1 M u x 0

Control

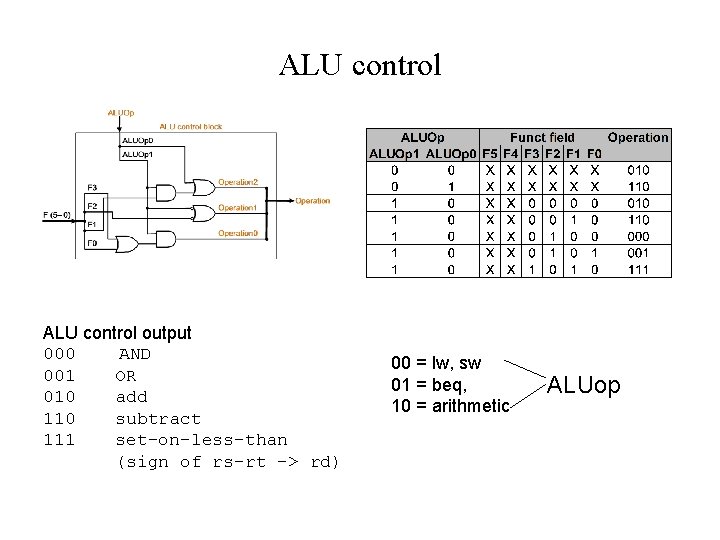

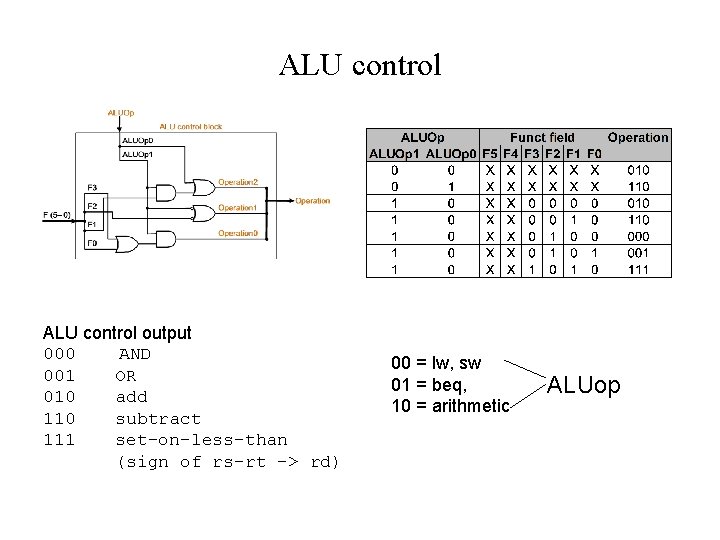

ALU control output 000 AND 001 OR 010 add 110 subtract 111 set-on-less-than (sign of rs-rt -> rd) 00 = lw, sw 01 = beq, 10 = arithmetic ALUop

![Jump Instruction 25 0 26 Shift left 2 Jump address 31 0 28 0 Jump Instruction [25– 0] 26 Shift left 2 Jump address [31– 0] 28 0](https://slidetodoc.com/presentation_image_h/31d41bd12f6b00c3c57a44f7785a0a6a/image-33.jpg)

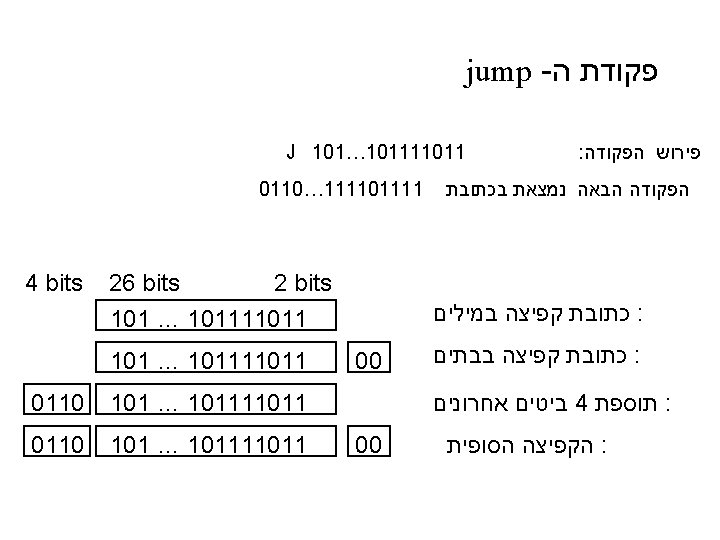

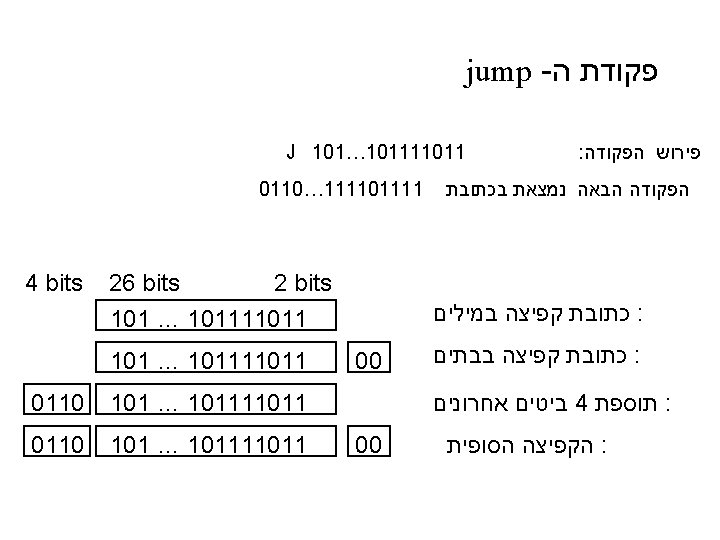

Jump Instruction [25– 0] 26 Shift left 2 Jump address [31– 0] 28 0 1 M u x ALU Add result 1 0 Zero ALU result Address PC+4 [31– 28] Add 4 Instruction [31– 26] PC Instruction [25– 21] Read address Read register 1 Instruction [20– 16] Instruction [31– 0] Instruction memory Control Instruction [15– 11] Shift left 2 Reg. Dst Jump Branch Mem. Read Memto. Reg ALUOp Mem. Write ALUSrc Reg Write 0 M u x 1 Read data 1 Read register 2 Registers Read Write data 2 register 0 M u x 1 Write data Instruction [15– 0] 16 Instruction [5– 0] Sign extend 32 ALU control Read data Data memory 1 M u x 0