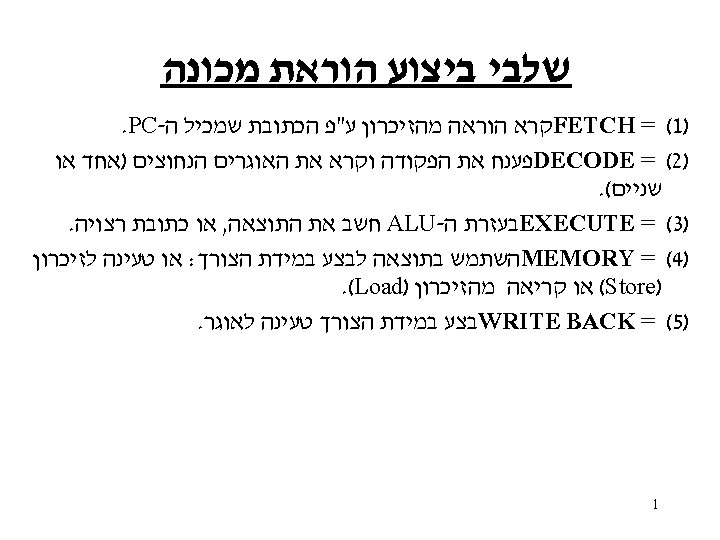

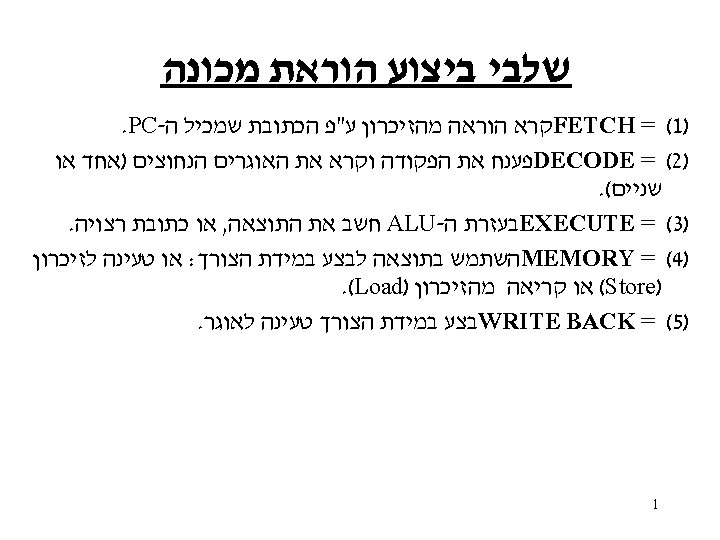

Instruction Address Instruction Memory Sum Add 2 FETCH

![Control 0 M u x Add 4 Instruction ]31– 26[ PC Instruction memory Instruction Control 0 M u x Add 4 Instruction ]31– 26[ PC Instruction memory Instruction](https://slidetodoc.com/presentation_image_h2/4e1cbbff47a5a4e551de0f3834c1e9a8/image-15.jpg)

- Slides: 17

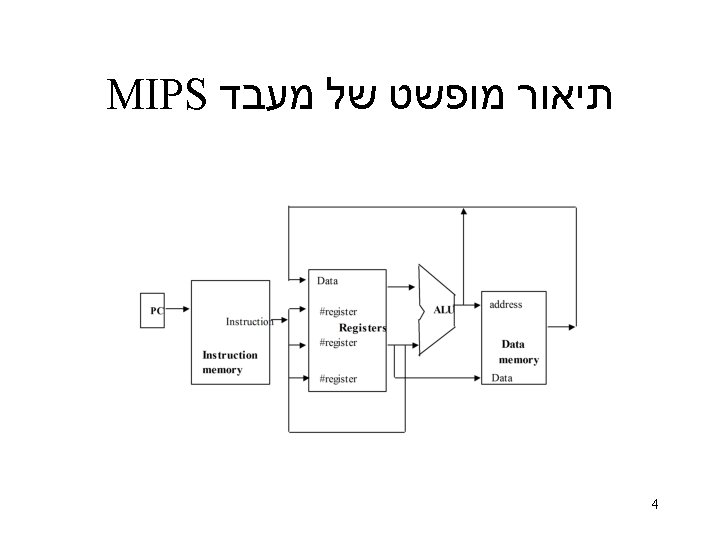

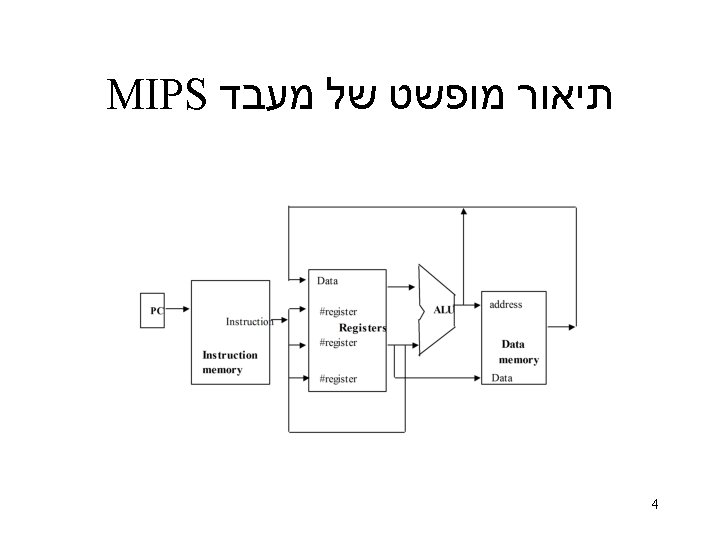

חלקים בסיסים של המחשב Instruction Address Instruction Memory Sum Add 2

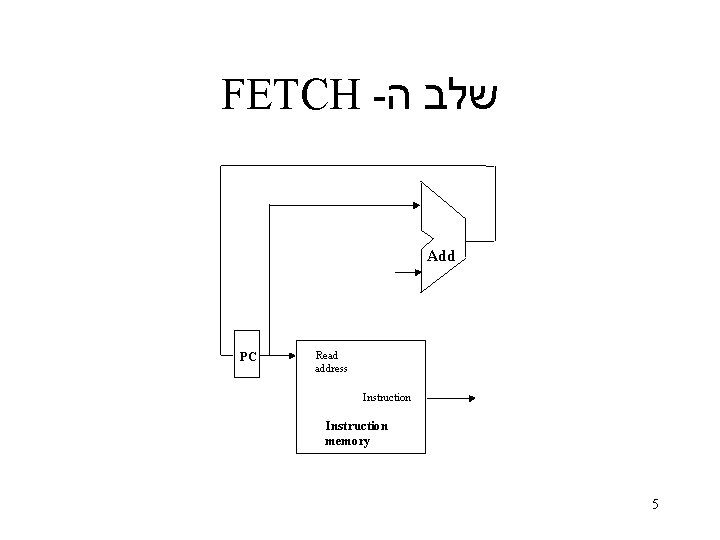

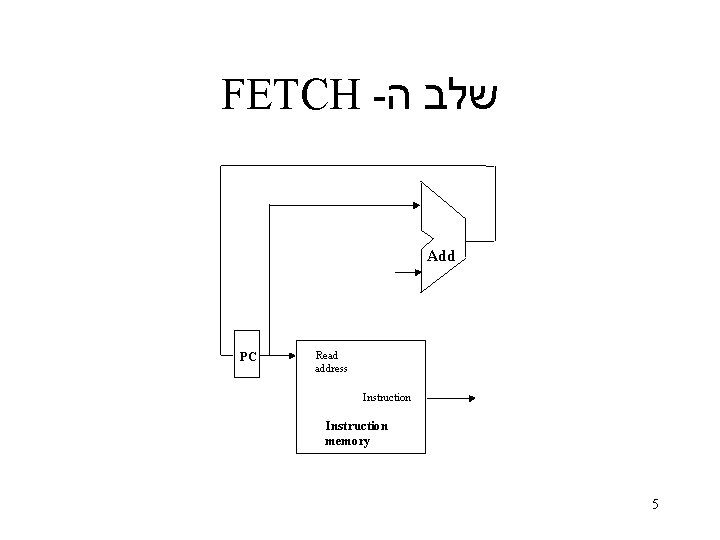

FETCH - שלב ה Add PC Read address Instruction memory 5

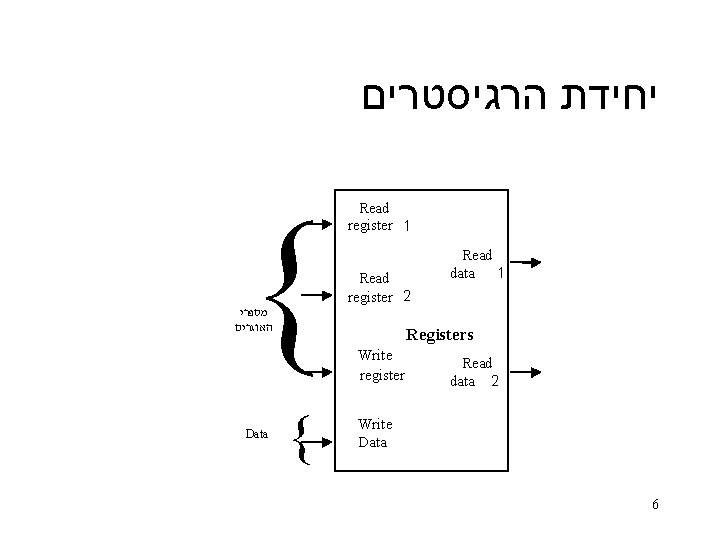

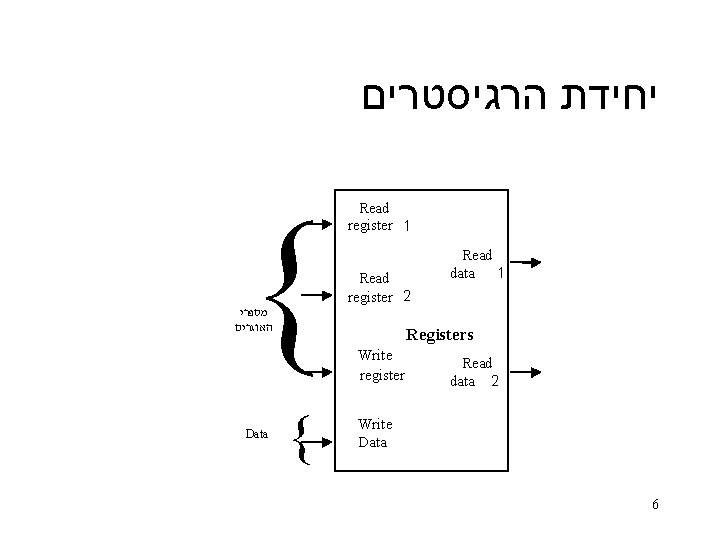

יחידת הרגיסטרים Read register 1 Read register 2 } מספרי האוגרים } Data Read data 1 Registers Write register Read data 2 Write Data 6

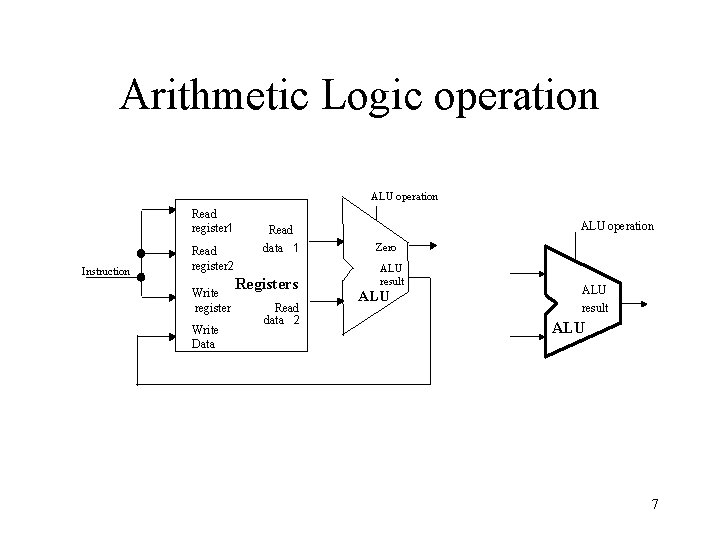

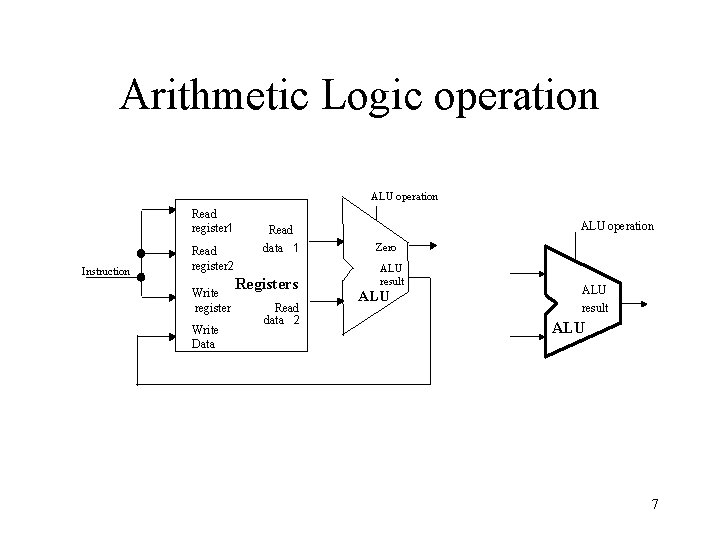

Arithmetic Logic operation ALU operation Read register 1 Instruction Read register 2 Write register Write Data Read data 1 Registers Read data 2 ALU operation Zero ALU result ALU 7

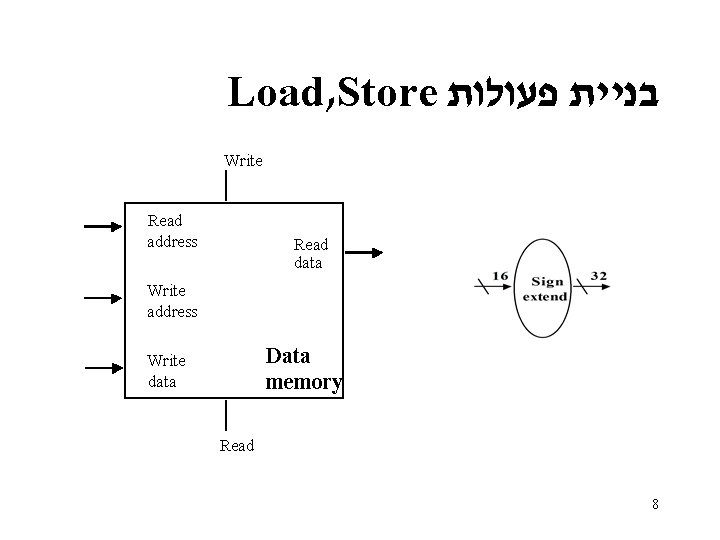

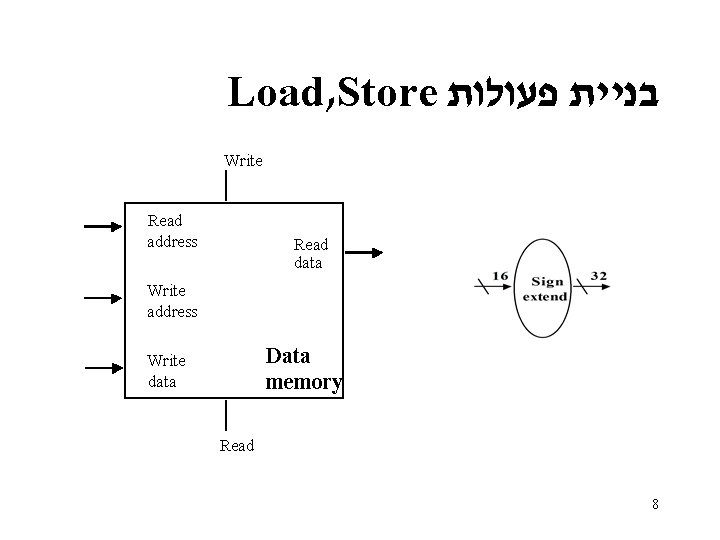

Load, Store בניית פעולות Write Read address Read data Write address Data memory Write data Read 8

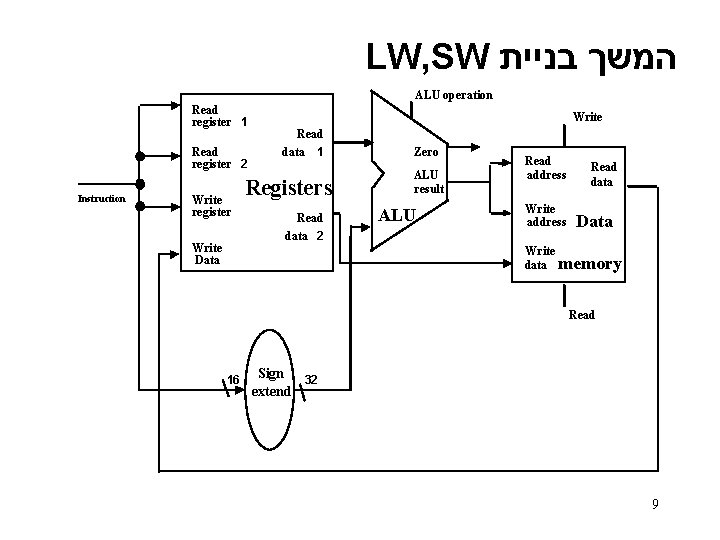

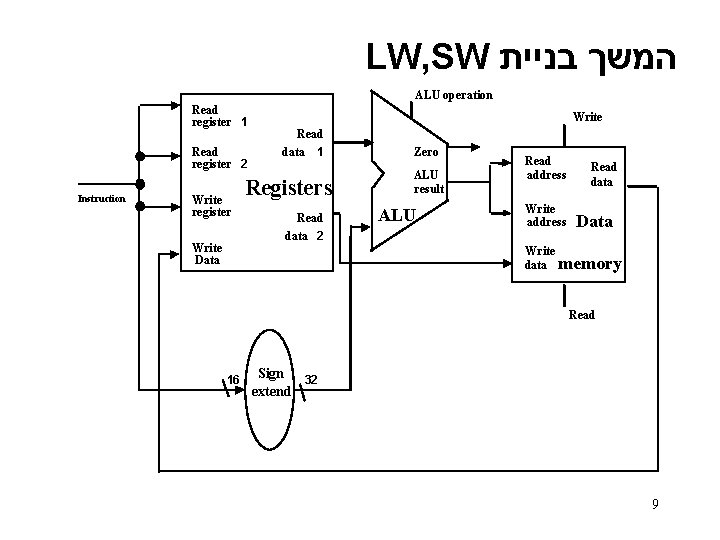

LW, SW המשך בניית ALU operation Read register 1 Read register 2 Instruction Write register Write Data Write Read data 1 Registers Read data 2 Zero ALU result ALU Read address Write address Read data Data Write data memory Read 16 Sign 32 extend 9

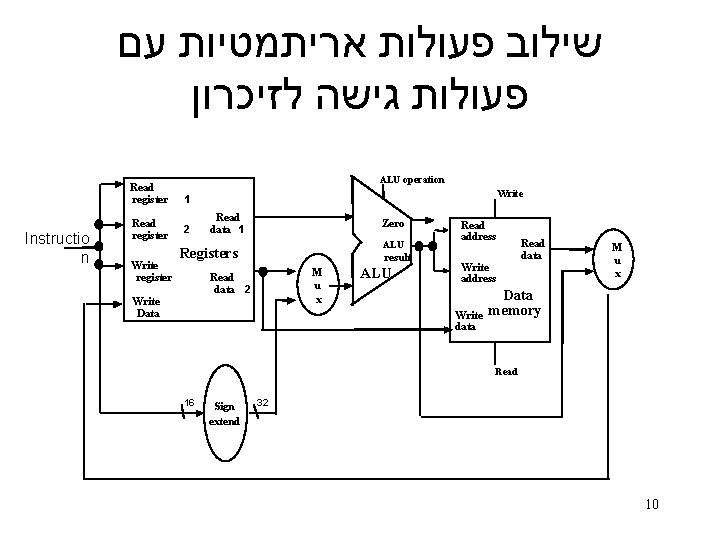

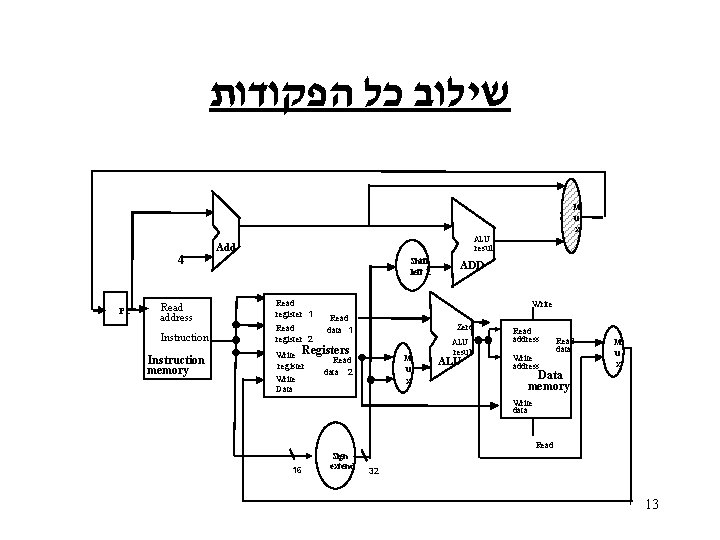

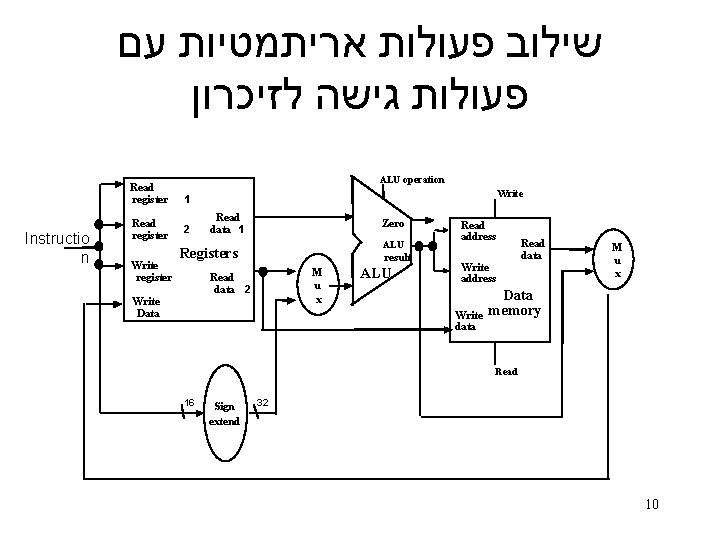

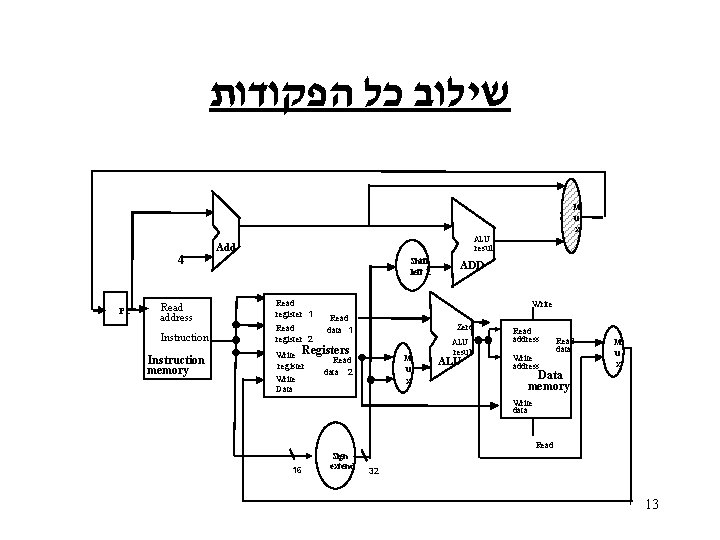

שילוב פעולות אריתמטיות עם פעולות גישה לזיכרון Read register Instructio n Read register Write register ALU operation Write 1 2 Read data 1 Zero ALU Registers result M u x Read data 2 Write Data ALU Read address Read data Write address Write data M u x Data memory Read 16 Sign extend 32 10

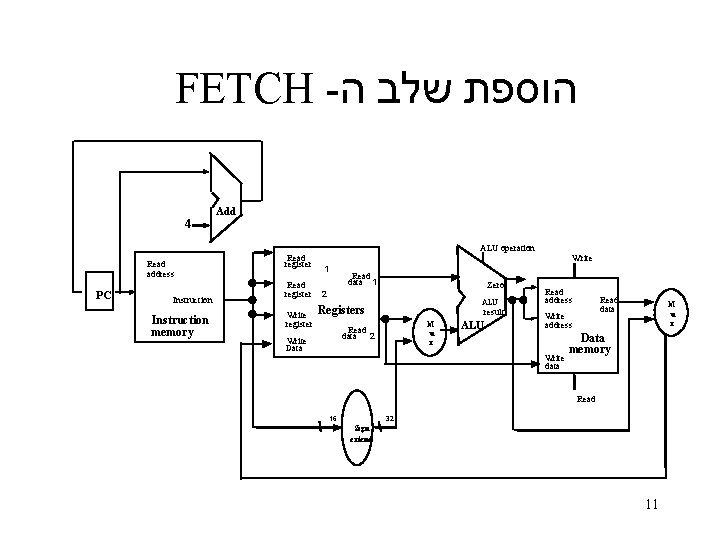

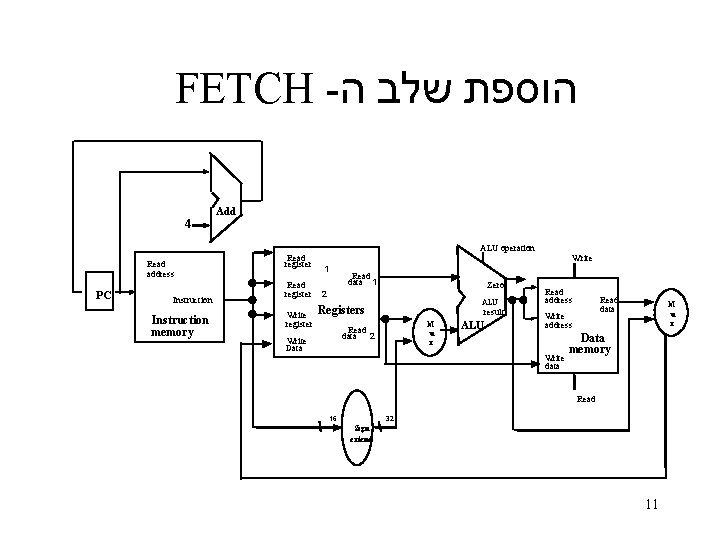

FETCH - הוספת שלב ה 4 Read address PC Instruction memory Add Read register Write register ALU operation 1 Read data 1 Zero 2 ALU Registers result M u x Read data 2 Write Data ALU Write Read address Read data Write address Write data M u x Data memory Read 16 32 Sign extend 11

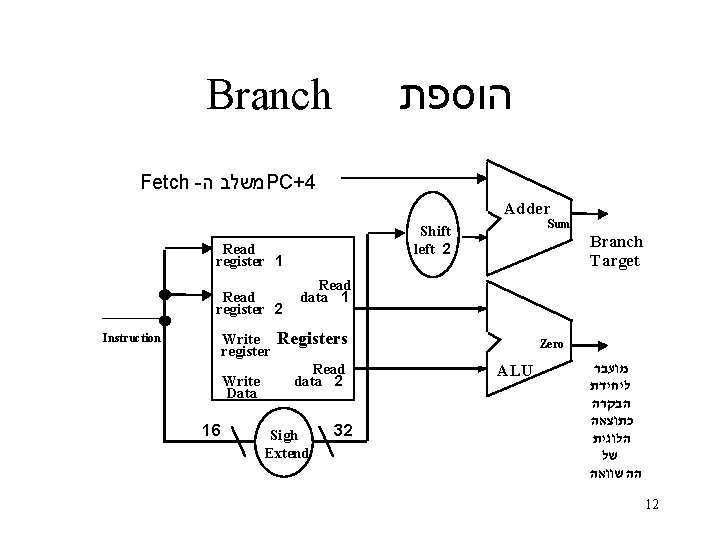

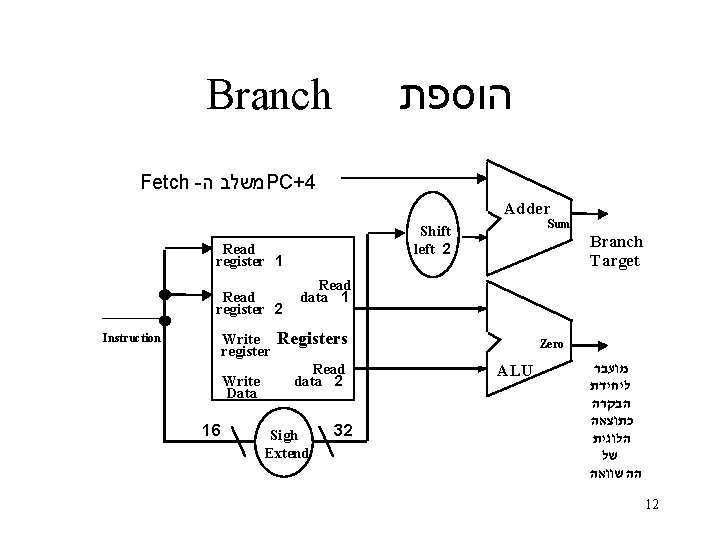

הוספת Branch Fetch - משלב ה PC+4 Adder Read register 1 Read register 2 Instruction Write register Write Data 16 Sum Shift left 2 Branch Target Read data 1 Registers Read data 2 Sigh Extend 32 Zero ALU מועבר ליחידת הבקרה כתוצאה הלוגית של ההשוואה 12

שילוב כל הפקודות M u x 4 PC Read address Instruction memory ALU Add result Shift left 2 Read register 1 Read register 2 Write Read data 1 Zero ALU Registers Write register Write Data ADD M u x Read data 2 result ALU Read address Write address Read data M u x Data memory Write data Read 16 Sign extend 32 13

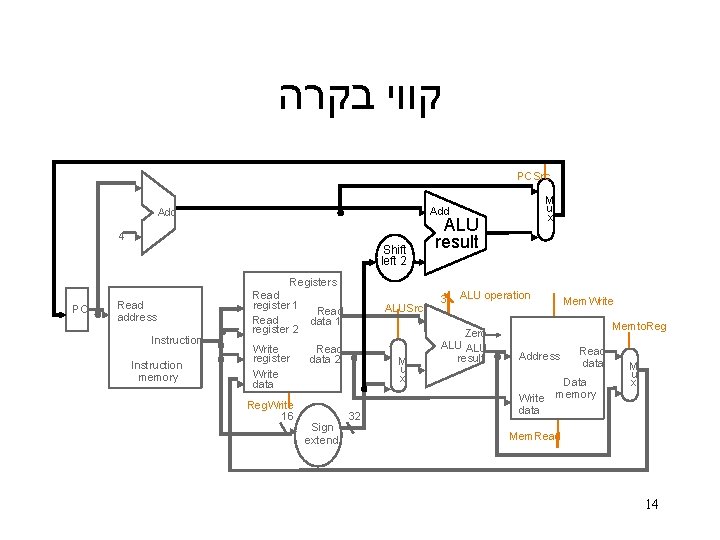

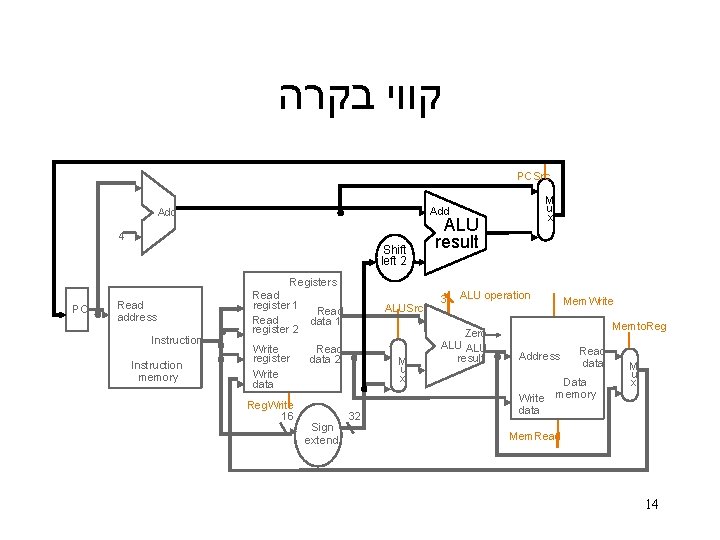

קווי בקרה PCSrc 4 Shift left 2 PC Read address Instruction memory M u x Add Registers Read register 1 Read data 1 register 2 Write register Write data Reg. Write 16 ALUSrc Read data 2 Sign extend M u x 32 ALU result 3 ALU operation Zero ALU result Mem Write Memto. Reg Address Write data Read data Data memory M u x Mem. Read 14

![Control 0 M u x Add 4 Instruction 31 26 PC Instruction memory Instruction Control 0 M u x Add 4 Instruction ]31– 26[ PC Instruction memory Instruction](https://slidetodoc.com/presentation_image_h2/4e1cbbff47a5a4e551de0f3834c1e9a8/image-15.jpg)

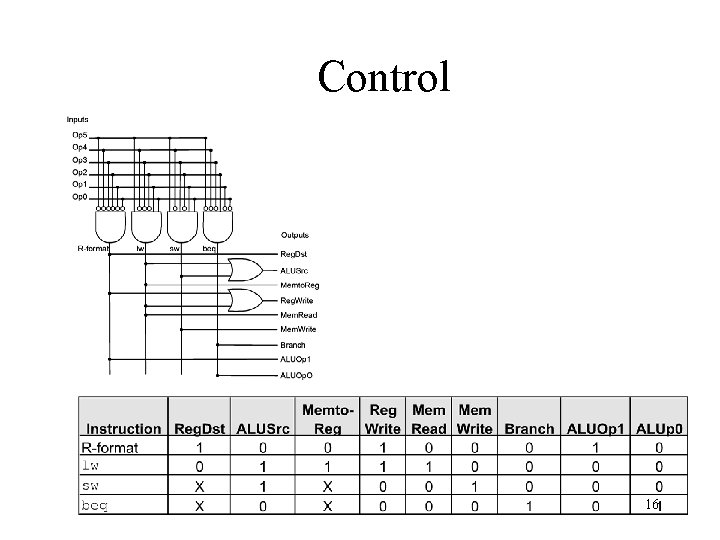

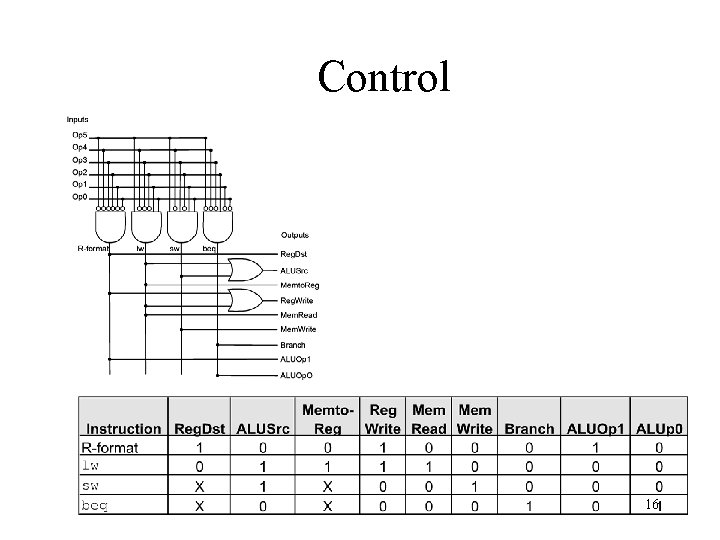

Control 0 M u x Add 4 Instruction ]31– 26[ PC Instruction memory Instruction ]15– 11[ Zero ALU result Address Read register 1 Instruction ]20– 16[ Instruction ]31– 0[ 1 Shift left 2 Reg. Dst Branch Mem. Read Memto. Reg Control ALUOp Mem. Write ALUSrc Reg. Write Instruction ]25– 21[ Read address ALU Add result 0 M u x 1 Read data 1 Read register 2 Registers Read Write data 2 register 0 M u x 1 Write data Instruction ]15– 0[ 16 Sign extend d Rea a dat Data memory 1 M u x 0 32 ALU control Instruction ]5– 0[ 15

Control 16

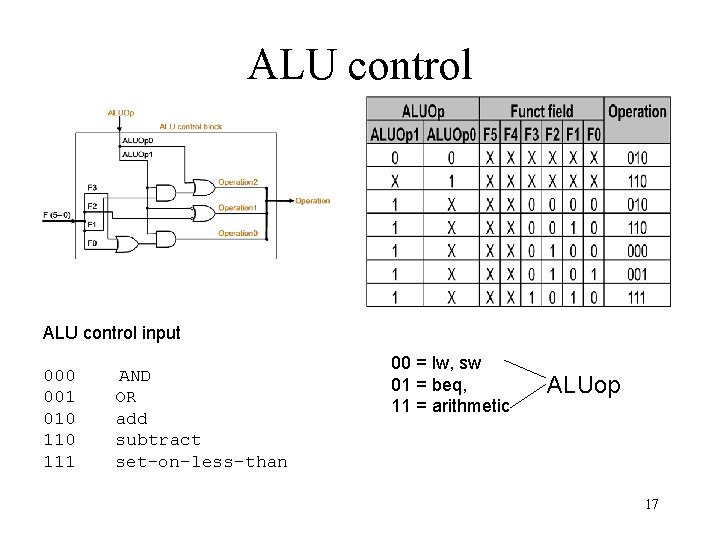

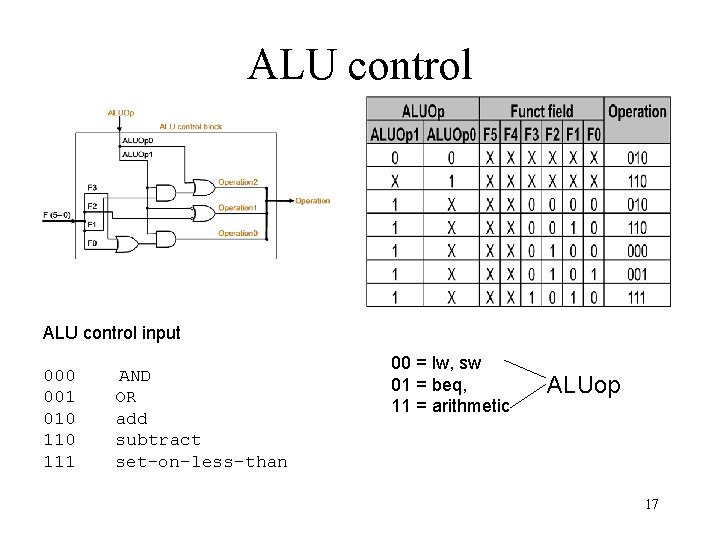

ALU control input 000 001 010 111 AND OR add subtract set-on-less-than 00 = lw, sw 01 = beq, 11 = arithmetic ALUop 17