Central Processing Unit Fetch Cycle FETCH Programming Counter

- Slides: 9

Central Processing Unit (Fetch Cycle)

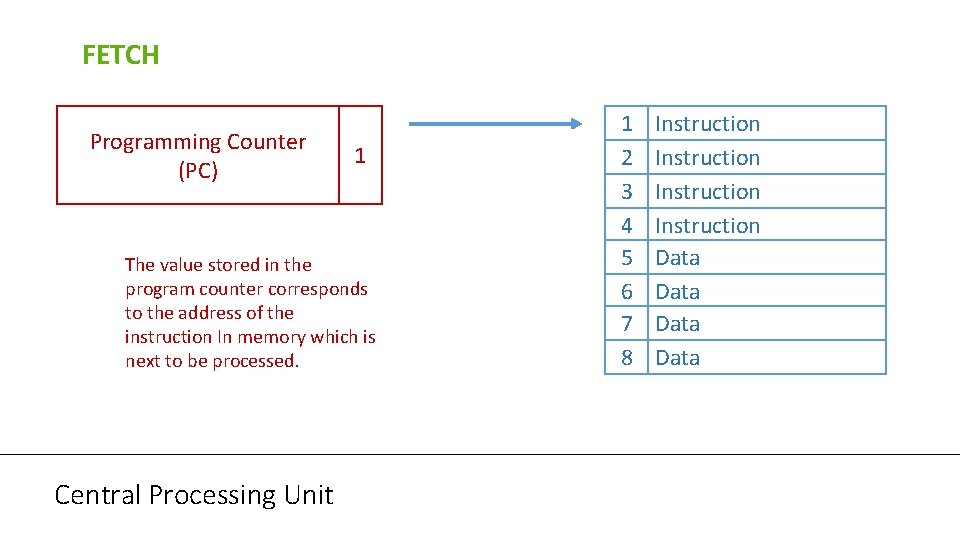

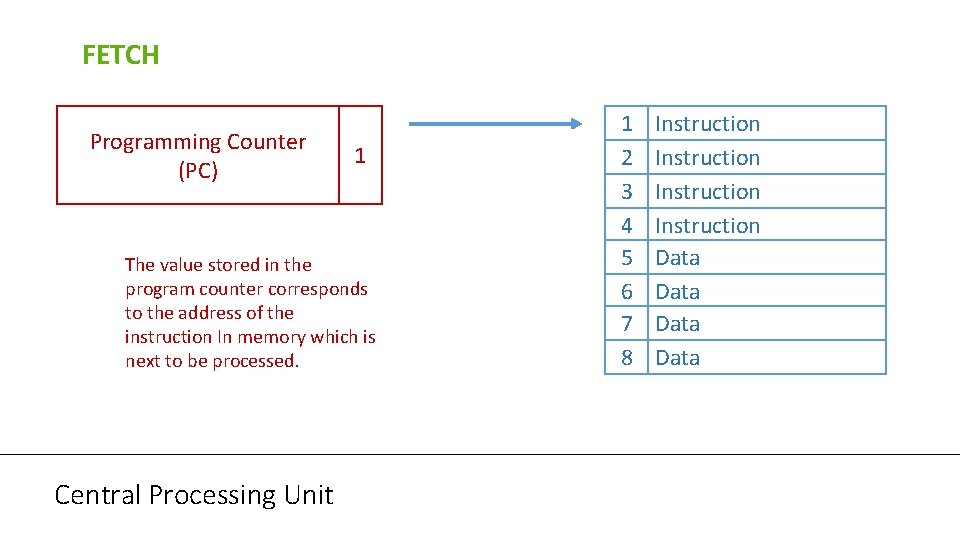

FETCH Programming Counter (PC) 1 The value stored in the program counter corresponds to the address of the instruction In memory which is next to be processed. Central Processing Unit 1 2 3 4 5 6 7 8 Instruction Data

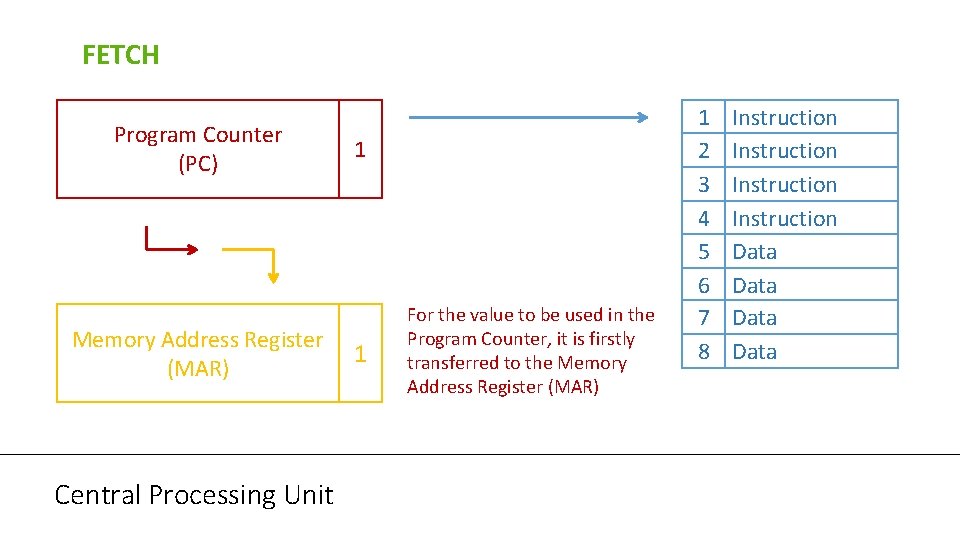

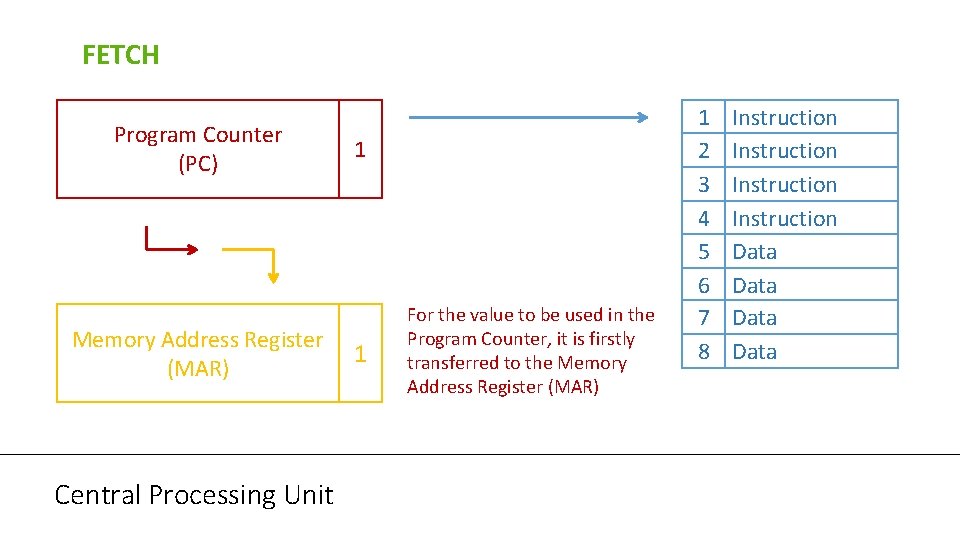

FETCH Program Counter (PC) Memory Address Register (MAR) Central Processing Unit 1 1 For the value to be used in the Program Counter, it is firstly transferred to the Memory Address Register (MAR) 1 2 3 4 5 6 7 8 Instruction Data

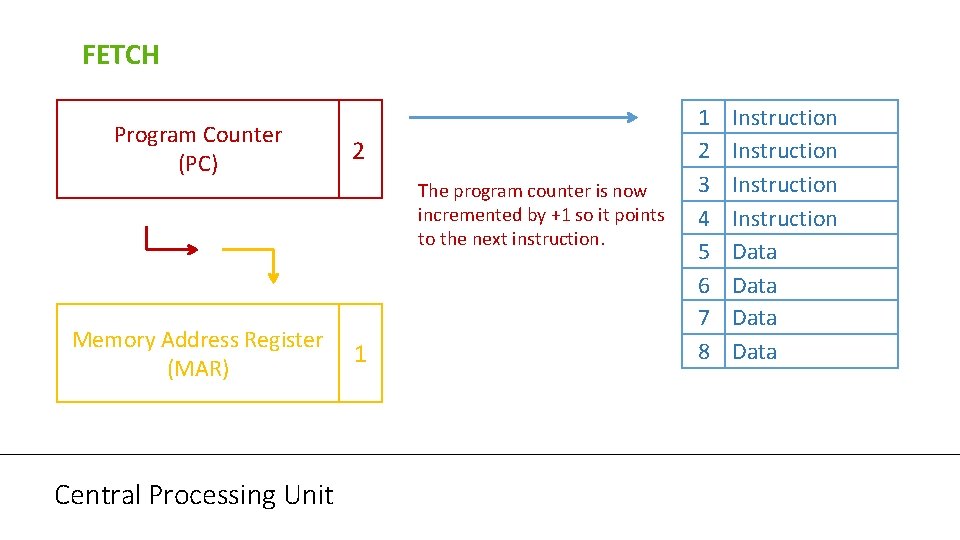

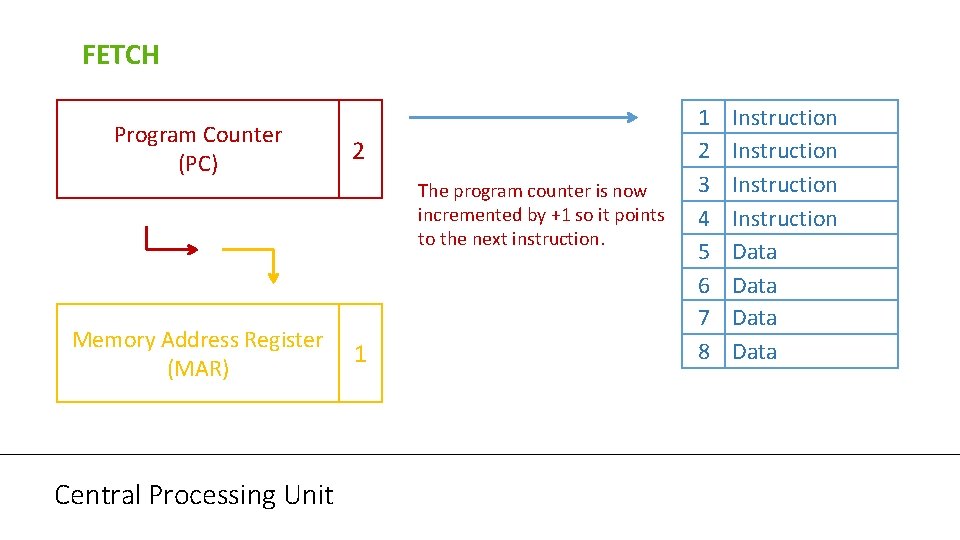

FETCH Program Counter (PC) 2 The program counter is now incremented by +1 so it points to the next instruction. Memory Address Register (MAR) Central Processing Unit 1 1 2 3 4 5 6 7 8 Instruction Data

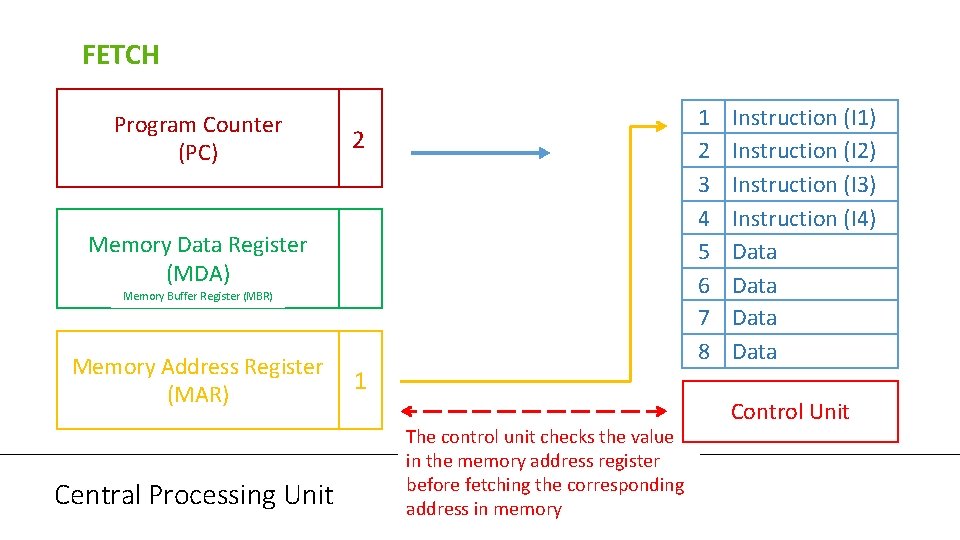

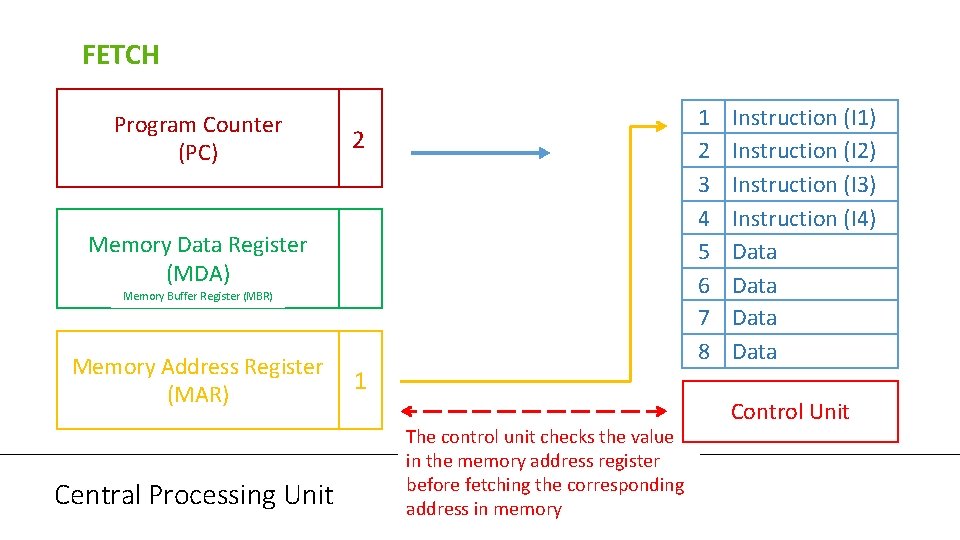

FETCH Program Counter (PC) 1 2 3 4 5 6 7 8 2 Memory Data Register (MDA) Memory Buffer Register (MBR) Memory Address Register (MAR) Central Processing Unit 1 The control unit checks the value in the memory address register before fetching the corresponding address in memory Instruction (I 1) Instruction (I 2) Instruction (I 3) Instruction (I 4) Data Control Unit

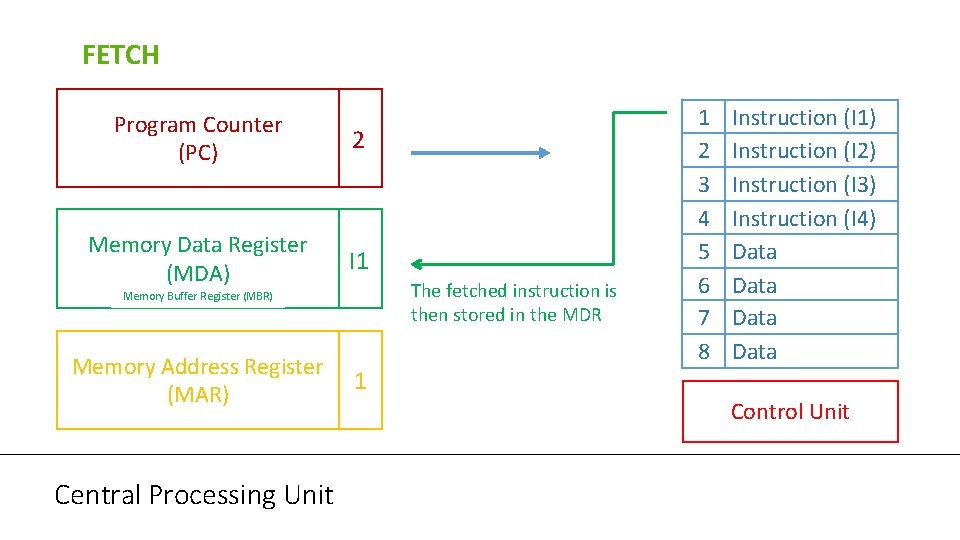

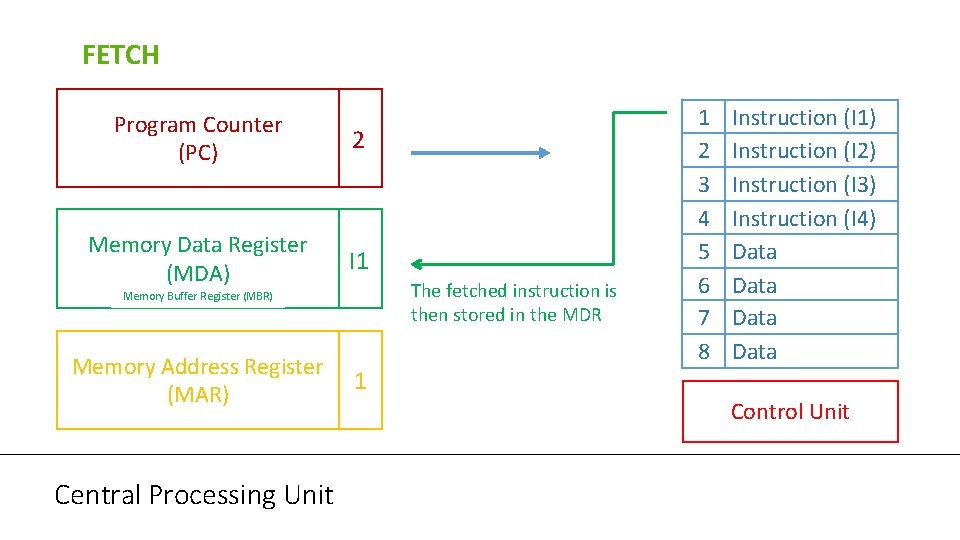

FETCH Program Counter (PC) 2 Memory Data Register (MDA) I 1 The fetched instruction is then stored in the MDR Memory Buffer Register (MBR) Memory Address Register (MAR) Central Processing Unit 1 1 2 3 4 5 6 7 8 Instruction (I 1) Instruction (I 2) Instruction (I 3) Instruction (I 4) Data Control Unit

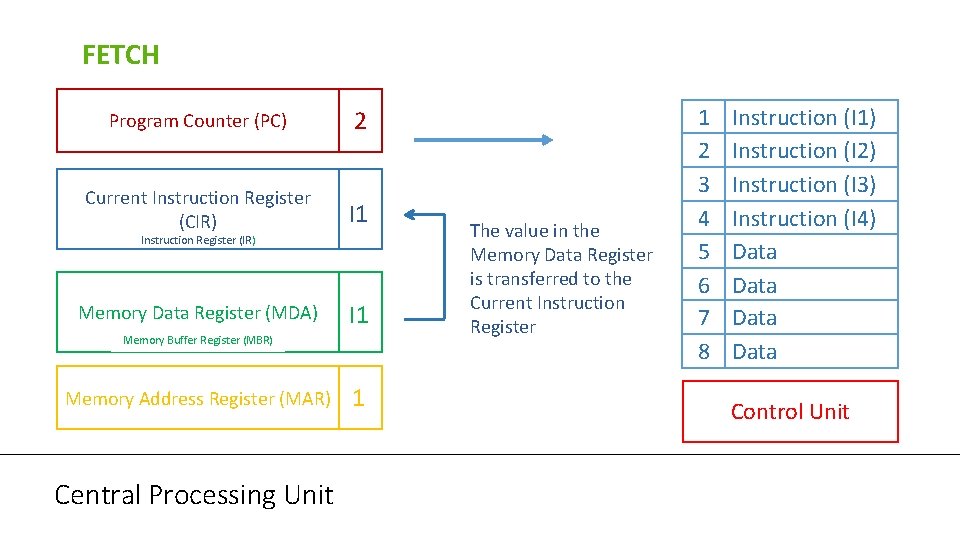

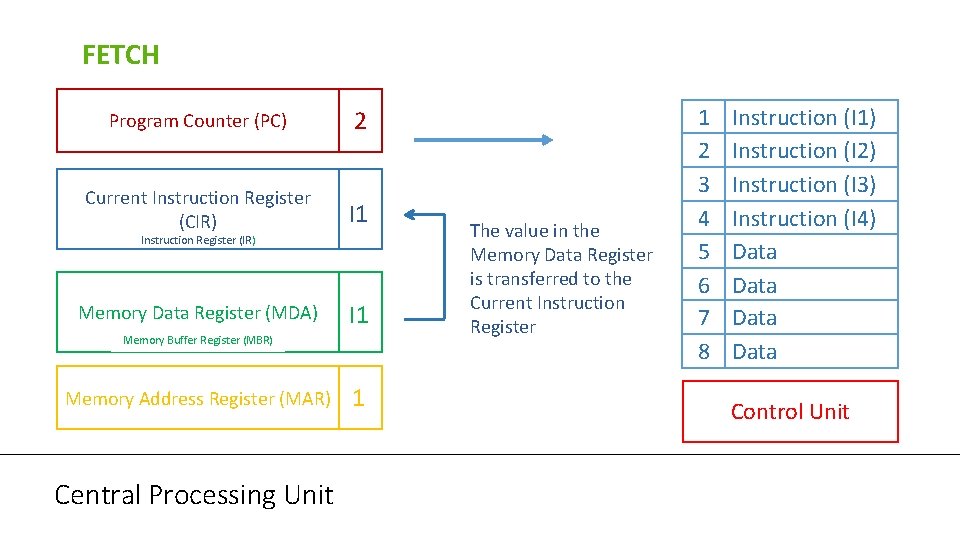

FETCH Program Counter (PC) 2 Current Instruction Register (CIR) I 1 Memory Data Register (MDA) I 1 Instruction Register (IR) Memory Buffer Register (MBR) Memory Address Register (MAR) Central Processing Unit 1 The value in the Memory Data Register is transferred to the Current Instruction Register 1 2 3 4 5 6 7 8 Instruction (I 1) Instruction (I 2) Instruction (I 3) Instruction (I 4) Data Control Unit

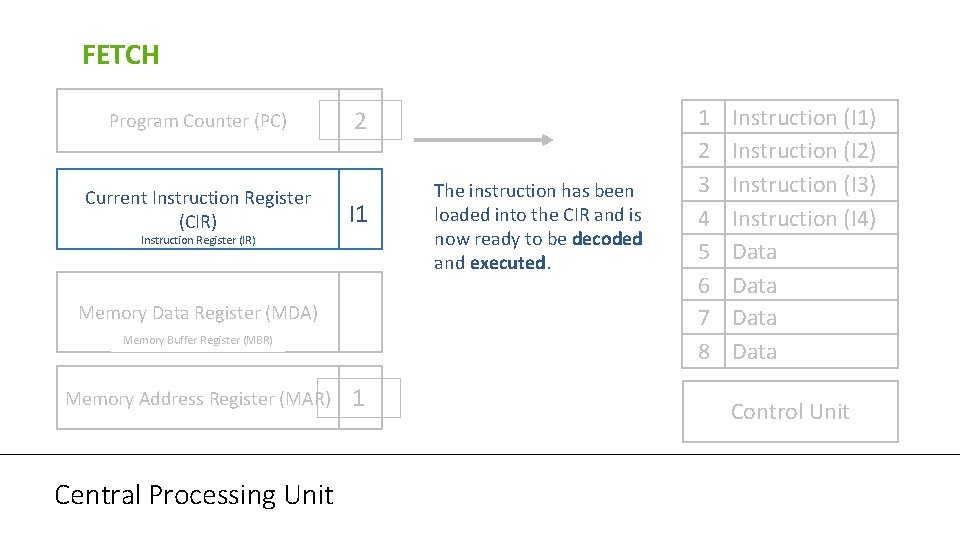

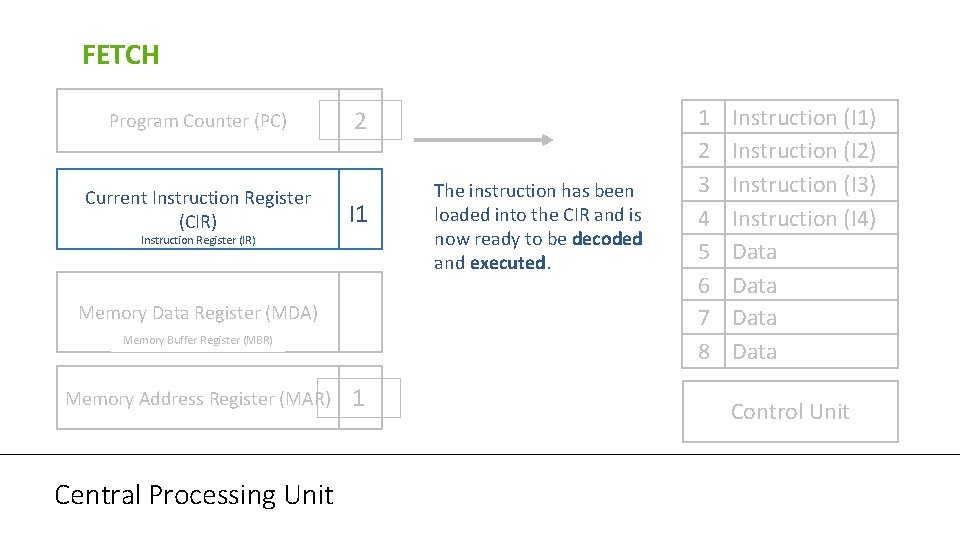

FETCH Program Counter (PC) Current Instruction Register (CIR) 2 I 1 Instruction Register (IR) Memory Data Register (MDA) Memory Buffer Register (MBR) Memory Address Register (MAR) Central Processing Unit 1 The instruction has been loaded into the CIR and is now ready to be decoded and executed. 1 2 3 4 5 6 7 8 Instruction (I 1) Instruction (I 2) Instruction (I 3) Instruction (I 4) Data Control Unit

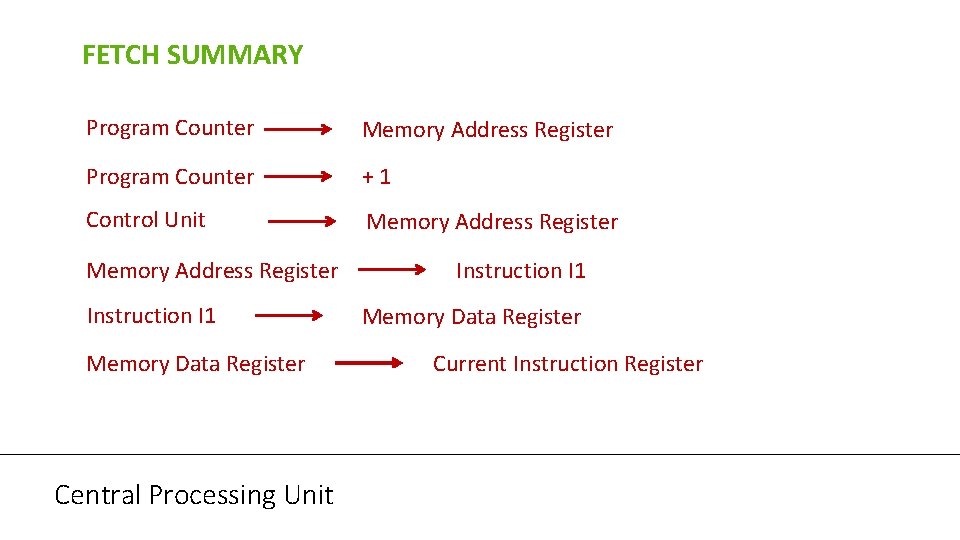

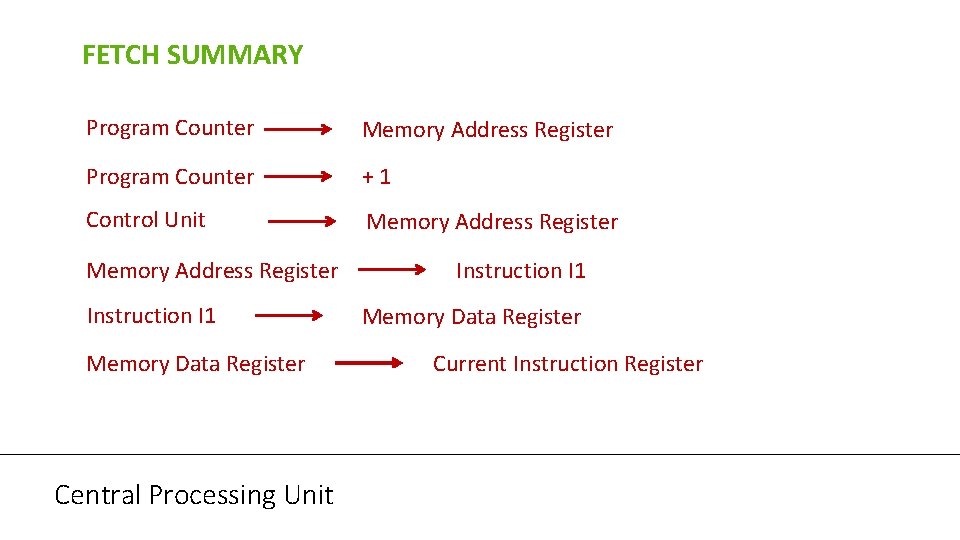

FETCH SUMMARY Program Counter Memory Address Register Program Counter +1 Control Unit Memory Address Register Instruction I 1 Memory Data Register Central Processing Unit Instruction I 1 Memory Data Register Current Instruction Register