ELEC 5270 0016270 001 Spring 2009 LowPower Design

![i(t) = C dv(t)/dt = [V – v(t)] /R dv(t) V – v(t) ─── i(t) = C dv(t)/dt = [V – v(t)] /R dv(t) V – v(t) ───](https://slidetodoc.com/presentation_image_h2/b6041af04cc30e37a9cd2bea983692c7/image-7.jpg)

![v(t) = i(t) Copyright Agrawal, 2007 = -t V [1 – exp( ── )] v(t) = i(t) Copyright Agrawal, 2007 = -t V [1 – exp( ── )]](https://slidetodoc.com/presentation_image_h2/b6041af04cc30e37a9cd2bea983692c7/image-8.jpg)

![isc, Rise Time and Capacitance Isc(t) = Copyright Agrawal, 2007 -t VDD[1 - exp(─────)] isc, Rise Time and Capacitance Isc(t) = Copyright Agrawal, 2007 -t VDD[1 - exp(─────)]](https://slidetodoc.com/presentation_image_h2/b6041af04cc30e37a9cd2bea983692c7/image-22.jpg)

- Slides: 42

ELEC 5270 -001/6270 -001 Spring 2009 Low-Power Design of Electronic Circuits Power Dissipation of CMOS Circuits Vishwani D. Agrawal James J. Danaher Professor Dept. of Electrical and Computer Engineering Auburn University, Auburn, AL 36849 vagrawal@eng. auburn. edu http: //www. eng. auburn. edu/~vagrawal/COURSE/E 6270_Spr 09/course. html Copyright Agrawal, 2007 ELEC 5270/6270 Spring 09, Lecture 4 1

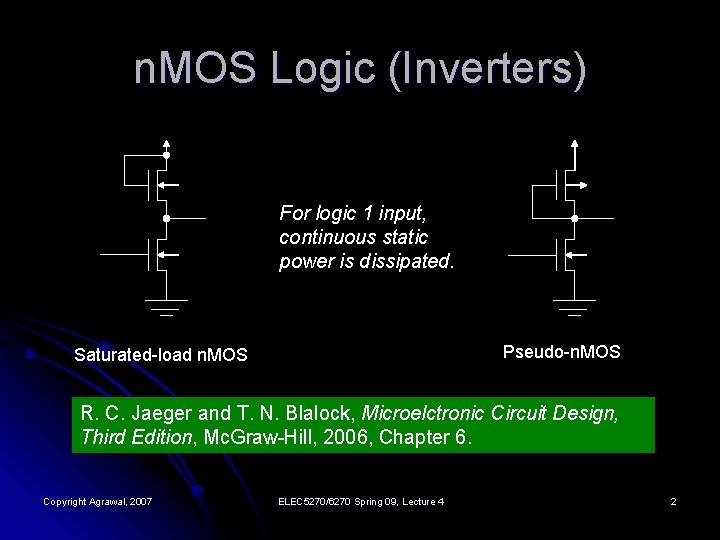

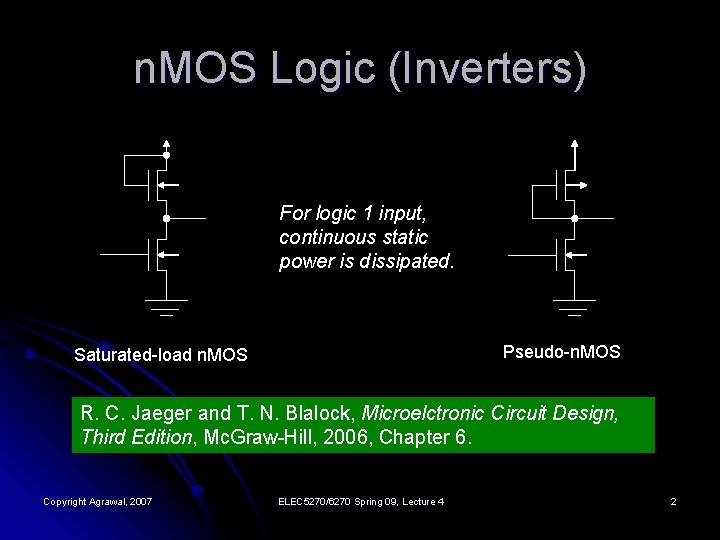

n. MOS Logic (Inverters) For logic 1 input, continuous static power is dissipated. Pseudo-n. MOS Saturated-load n. MOS R. C. Jaeger and T. N. Blalock, Microelctronic Circuit Design, Third Edition, Mc. Graw-Hill, 2006, Chapter 6. Copyright Agrawal, 2007 ELEC 5270/6270 Spring 09, Lecture 4 2

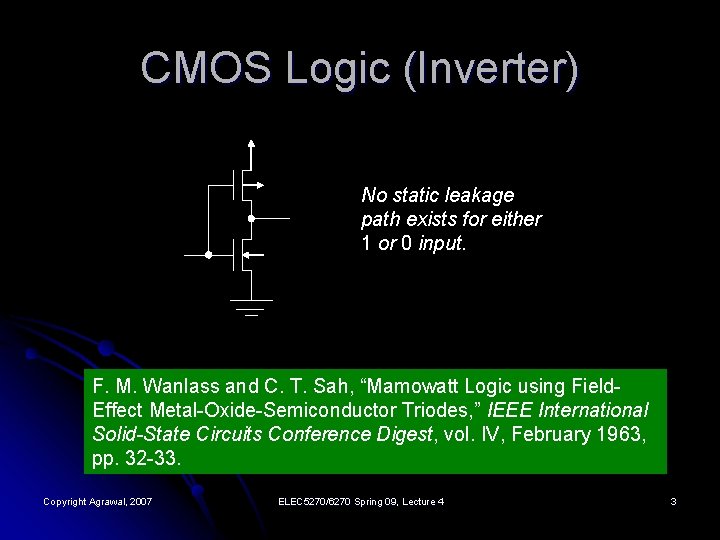

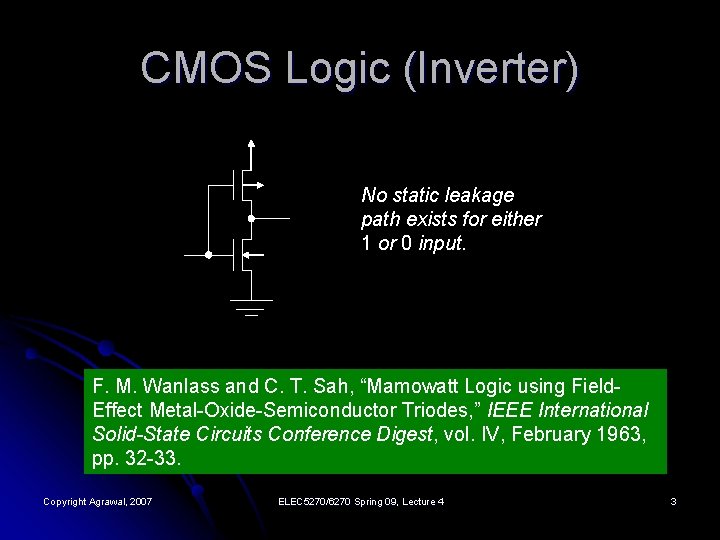

CMOS Logic (Inverter) No static leakage path exists for either 1 or 0 input. F. M. Wanlass and C. T. Sah, “Mamowatt Logic using Field. Effect Metal-Oxide-Semiconductor Triodes, ” IEEE International Solid-State Circuits Conference Digest, vol. IV, February 1963, pp. 32 -33. Copyright Agrawal, 2007 ELEC 5270/6270 Spring 09, Lecture 4 3

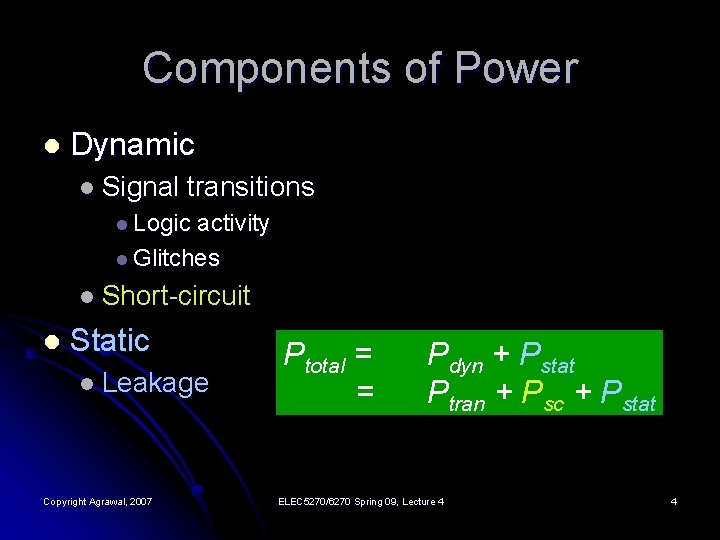

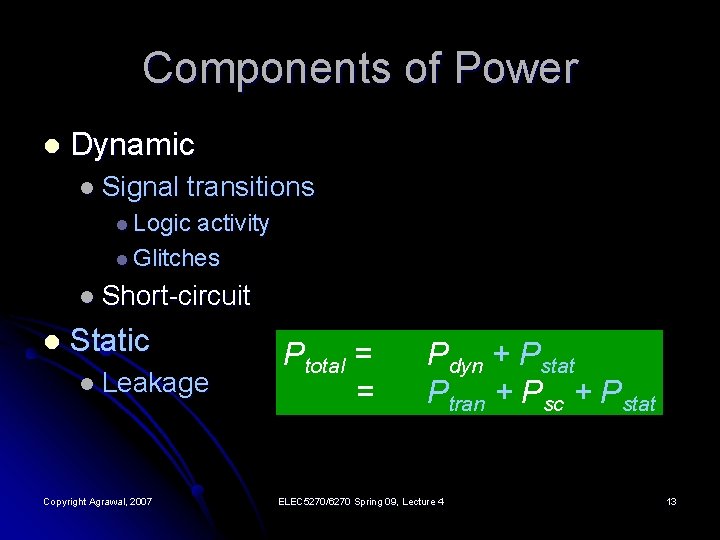

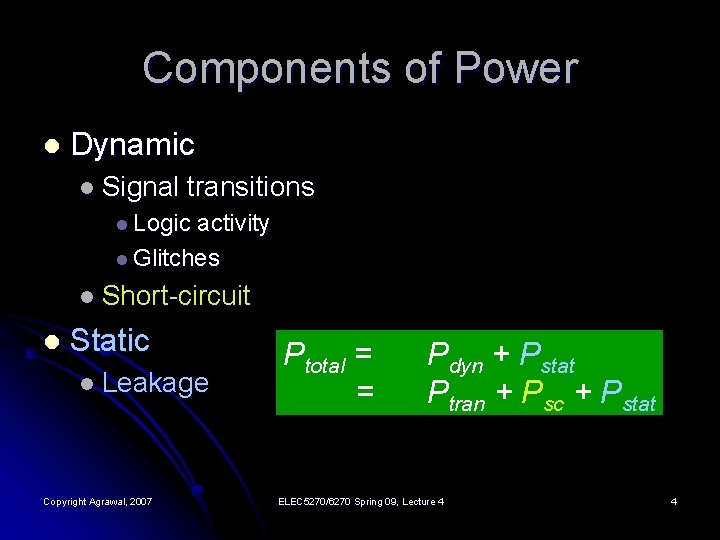

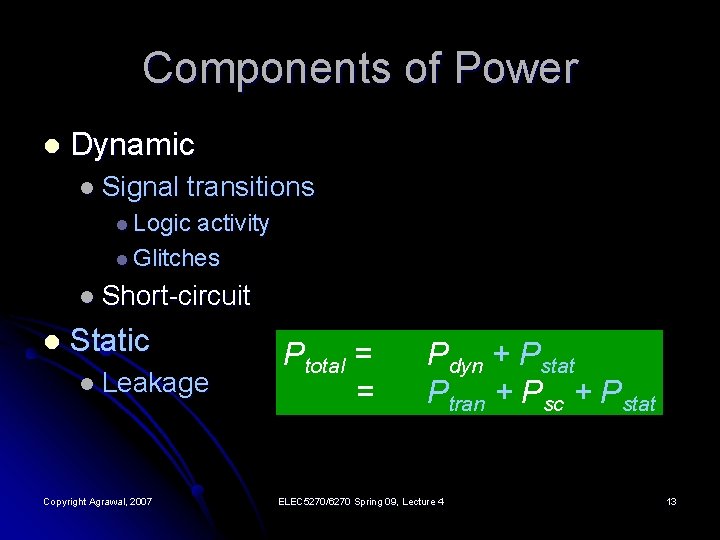

Components of Power l Dynamic l Signal transitions l Logic activity l Glitches l Short-circuit l Static l Leakage Copyright Agrawal, 2007 Ptotal = = Pdyn + Pstat Ptran + Psc + Pstat ELEC 5270/6270 Spring 09, Lecture 4 4

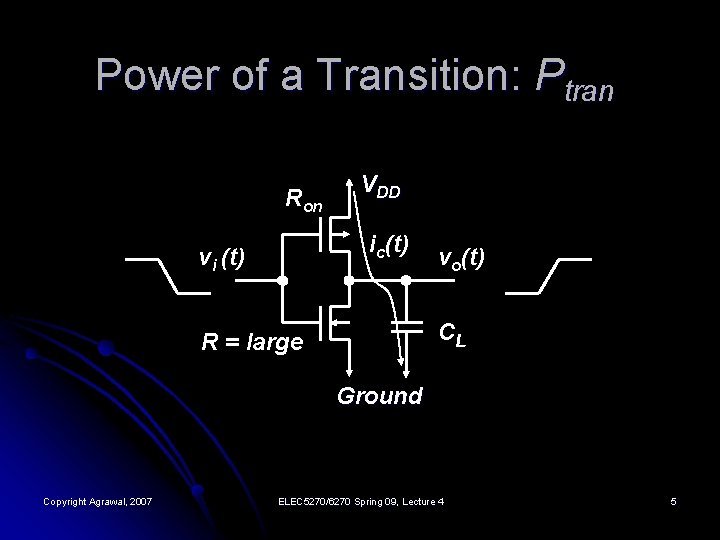

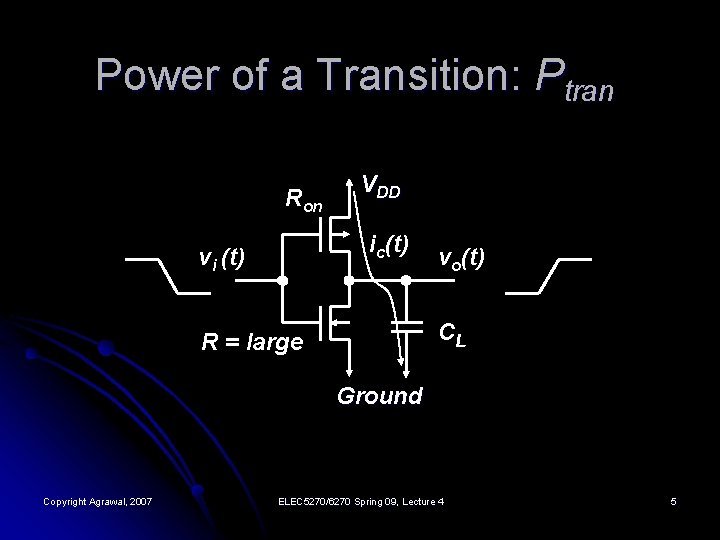

Power of a Transition: Ptran Ron VDD ic(t) vi (t) vo(t) CL R = large Ground Copyright Agrawal, 2007 ELEC 5270/6270 Spring 09, Lecture 4 5

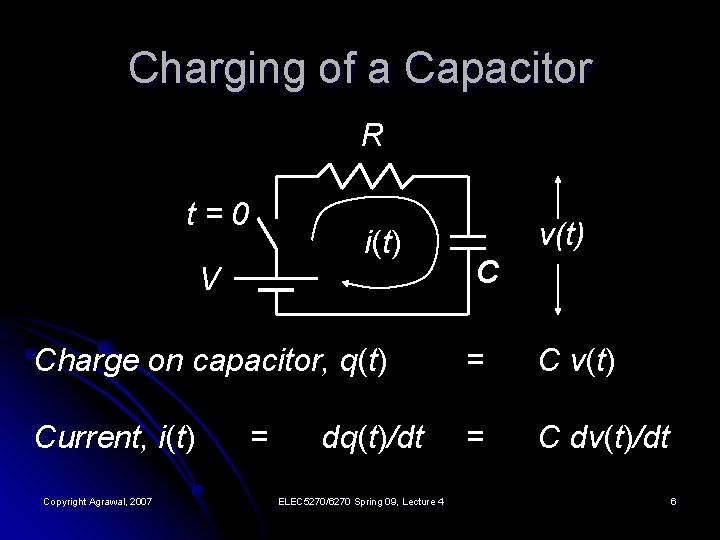

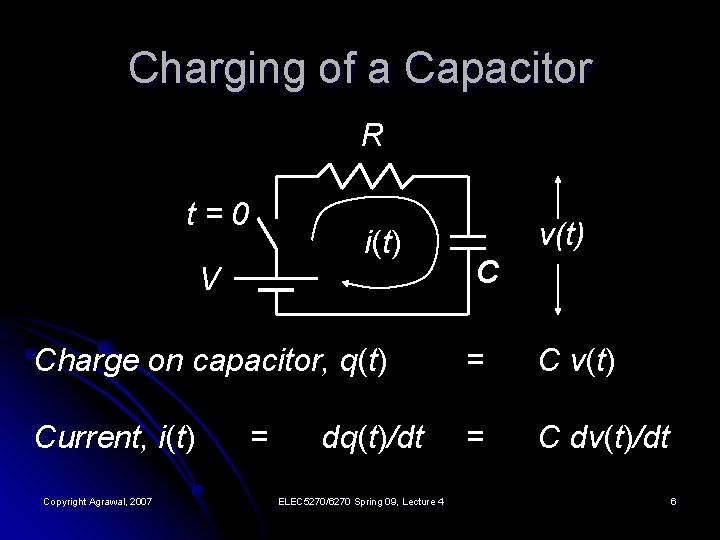

Charging of a Capacitor R t=0 i(t) V v(t) C Charge on capacitor, q(t) = C v(t) Current, i(t) = C dv(t)/dt Copyright Agrawal, 2007 = dq(t)/dt ELEC 5270/6270 Spring 09, Lecture 4 6

![it C dvtdt V vt R dvt V vt i(t) = C dv(t)/dt = [V – v(t)] /R dv(t) V – v(t) ───](https://slidetodoc.com/presentation_image_h2/b6041af04cc30e37a9cd2bea983692c7/image-7.jpg)

i(t) = C dv(t)/dt = [V – v(t)] /R dv(t) V – v(t) ─── = ───── dt RC dv(t) dt ∫ ───── = ∫ ──── V – v(t) RC -t ln [V – v(t)] = ── + A RC Initial condition, t = 0, v(t) = 0 → A = ln V -t v(t) = V [1 – exp(───)] RC Copyright Agrawal, 2007 ELEC 5270/6270 Spring 09, Lecture 4 7

![vt it Copyright Agrawal 2007 t V 1 exp v(t) = i(t) Copyright Agrawal, 2007 = -t V [1 – exp( ── )]](https://slidetodoc.com/presentation_image_h2/b6041af04cc30e37a9cd2bea983692c7/image-8.jpg)

v(t) = i(t) Copyright Agrawal, 2007 = -t V [1 – exp( ── )] RC dv(t) C ─── dt = ELEC 5270/6270 Spring 09, Lecture 4 V -t ── exp( ── ) R RC 8

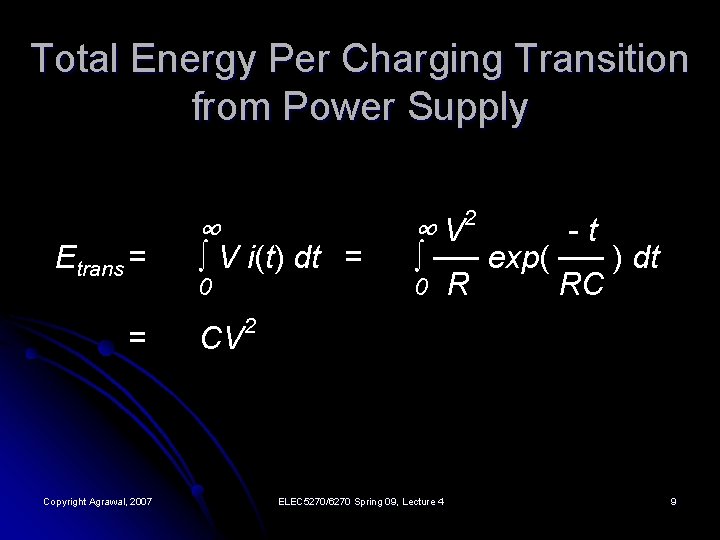

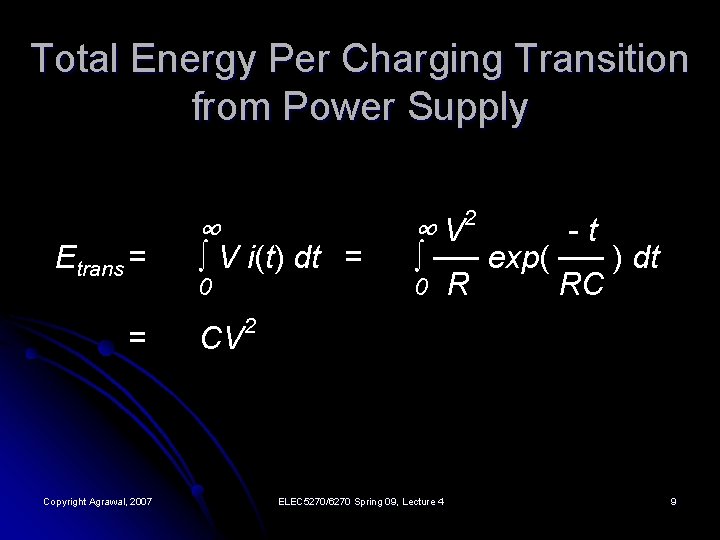

Total Energy Per Charging Transition from Power Supply Etrans = = Copyright Agrawal, 2007 ∞ ∫ V i(t) dt = 0 CV ∞V 2 -t ∫ ── exp( ── ) dt 0 R RC 2 ELEC 5270/6270 Spring 09, Lecture 4 9

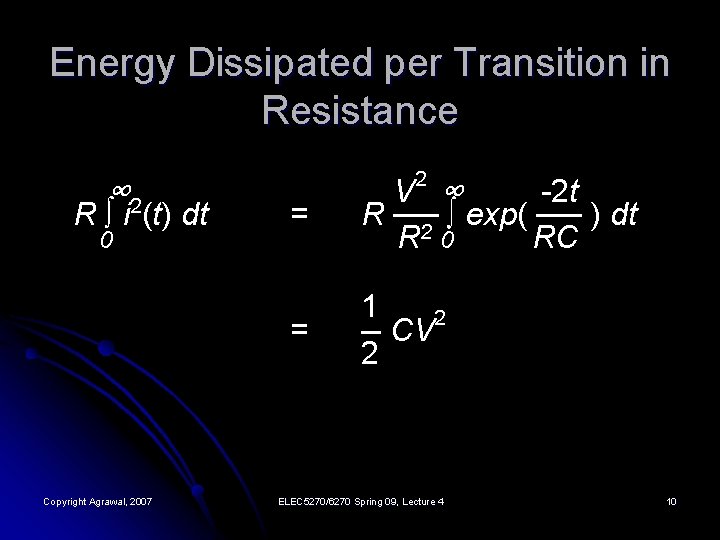

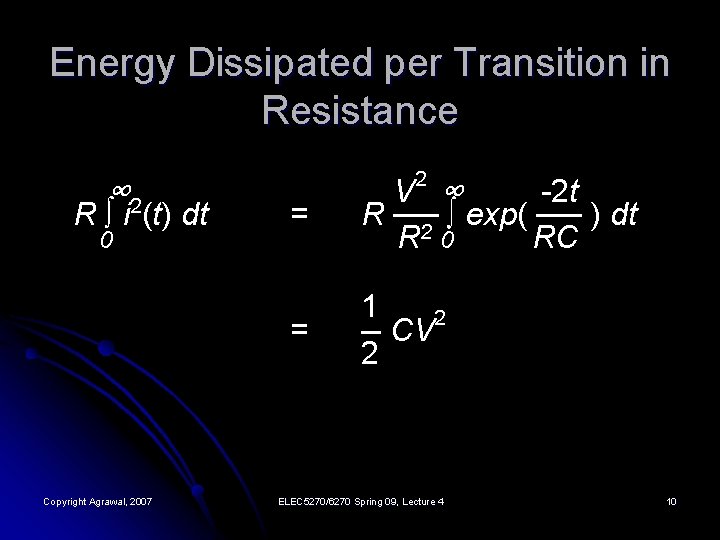

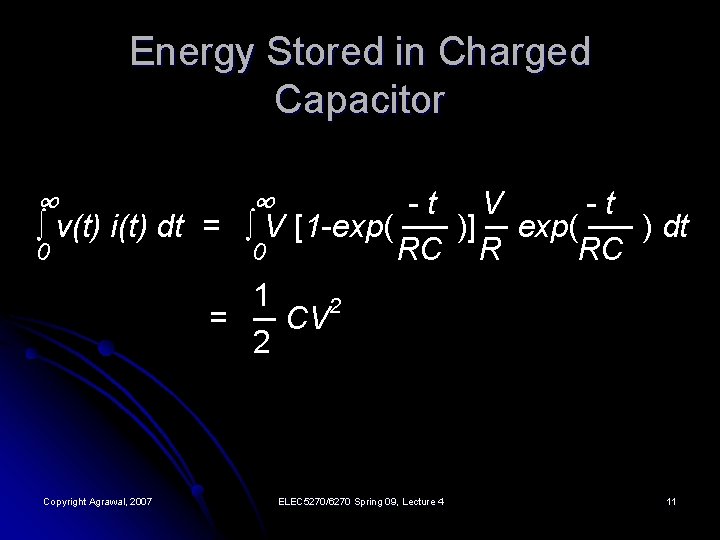

Energy Dissipated per Transition in Resistance ∞ 2 R ∫ i (t) dt 0 Copyright Agrawal, 2007 = V ∞ -2 t R ── ∫ exp( ── ) dt 2 R 0 RC = 1 2 ─ CV 2 2 ELEC 5270/6270 Spring 09, Lecture 4 10

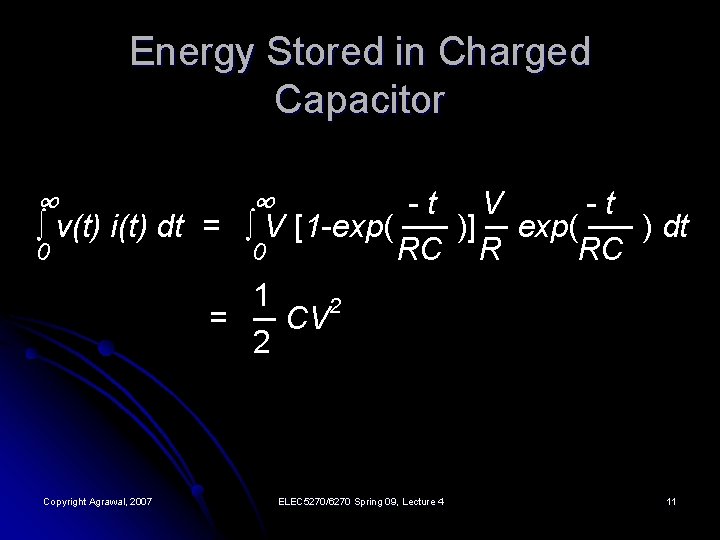

Energy Stored in Charged Capacitor ∞ ∞ -t V -t ∫ v(t) i(t) dt = ∫ V [1 -exp( ── )] ─ exp( ── ) dt 0 0 RC R RC 1 2 = ─ CV 2 Copyright Agrawal, 2007 ELEC 5270/6270 Spring 09, Lecture 4 11

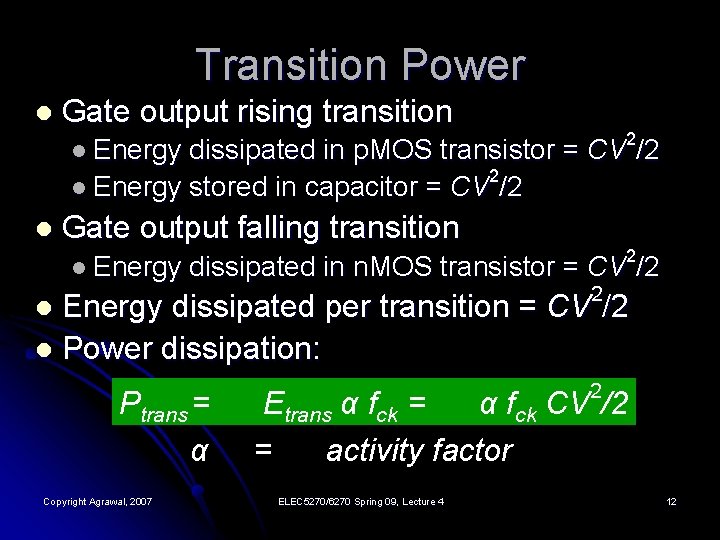

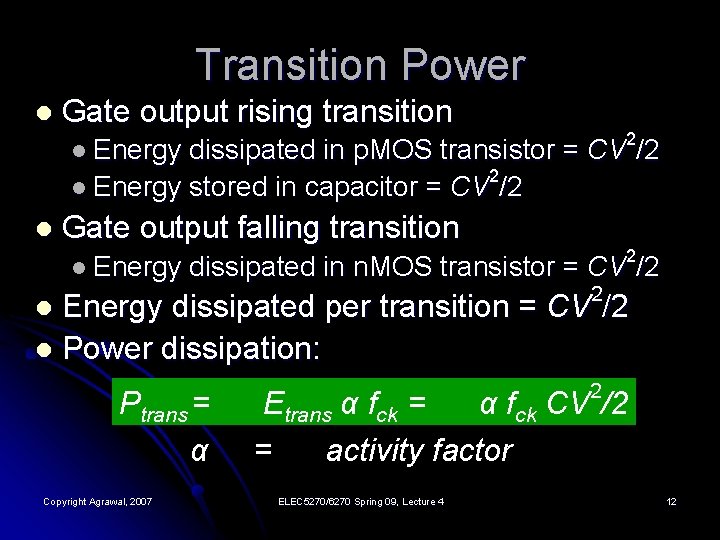

Transition Power l Gate output rising transition dissipated in p. MOS transistor = CV 2/2 2 l Energy stored in capacitor = CV /2 l Energy l Gate output falling transition l Energy dissipated in n. MOS transistor = CV 2/2 2 Energy dissipated per transition = CV /2 l Power dissipation: l Ptrans = α Copyright Agrawal, 2007 2 Etrans α fck = α fck CV /2 = activity factor ELEC 5270/6270 Spring 09, Lecture 4 12

Components of Power l Dynamic l Signal transitions l Logic activity l Glitches l Short-circuit l Static l Leakage Copyright Agrawal, 2007 Ptotal = = Pdyn + Pstat Ptran + Psc + Pstat ELEC 5270/6270 Spring 09, Lecture 4 13

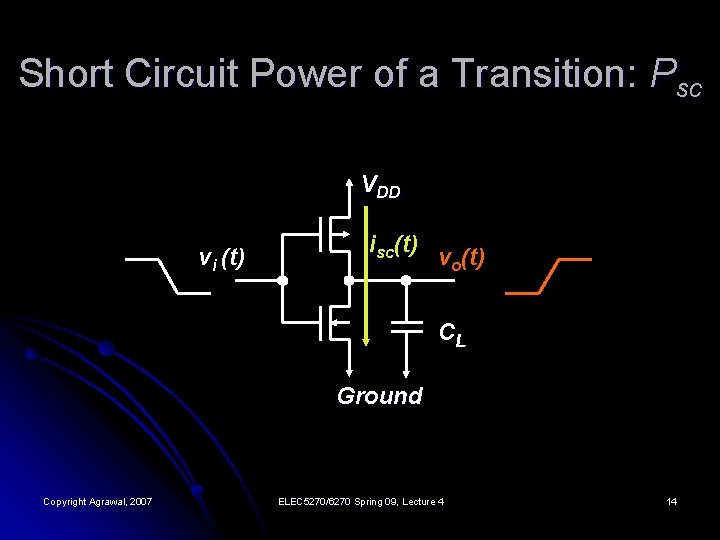

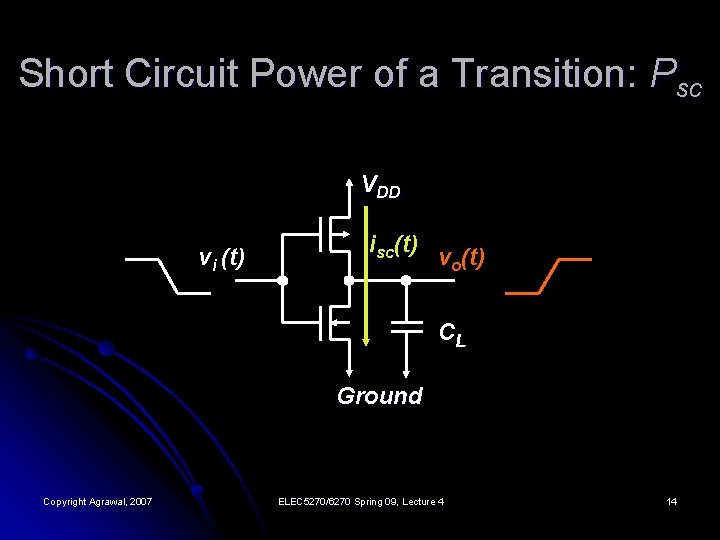

Short Circuit Power of a Transition: Psc VDD vi (t) isc(t) vo(t) CL Ground Copyright Agrawal, 2007 ELEC 5270/6270 Spring 09, Lecture 4 14

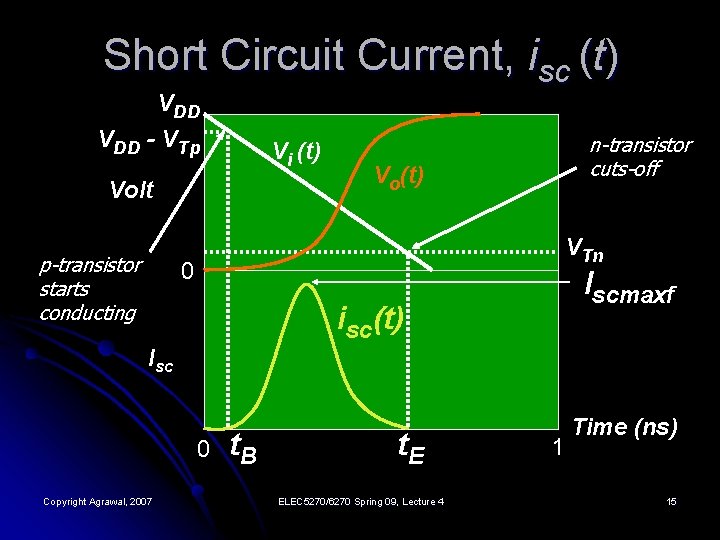

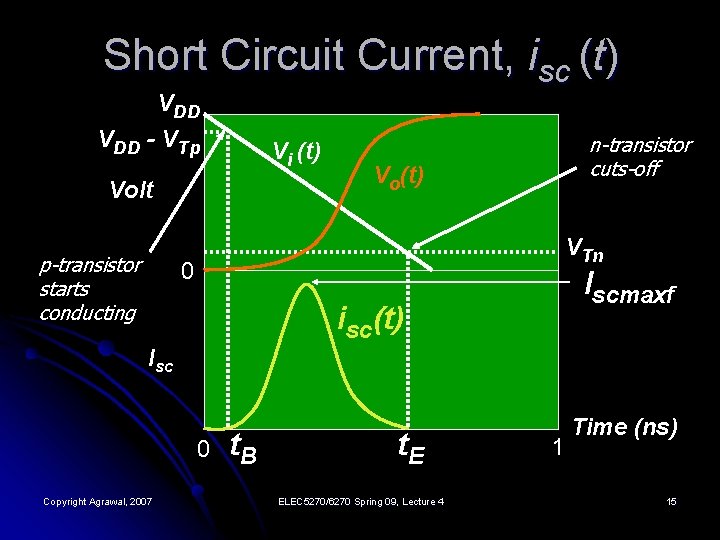

Short Circuit Current, isc (t) VDD - VTp Vi (t) Volt p-transistor starts conducting n-transistor cuts-off Vo(t) VTn 0 Iscmaxf isc(t) Isc 0 Copyright Agrawal, 2007 t. B t. E ELEC 5270/6270 Spring 09, Lecture 4 1 Time (ns) 15

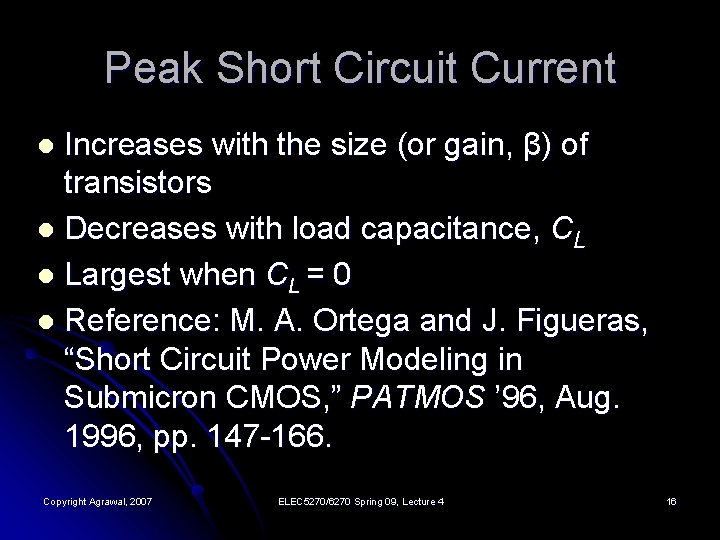

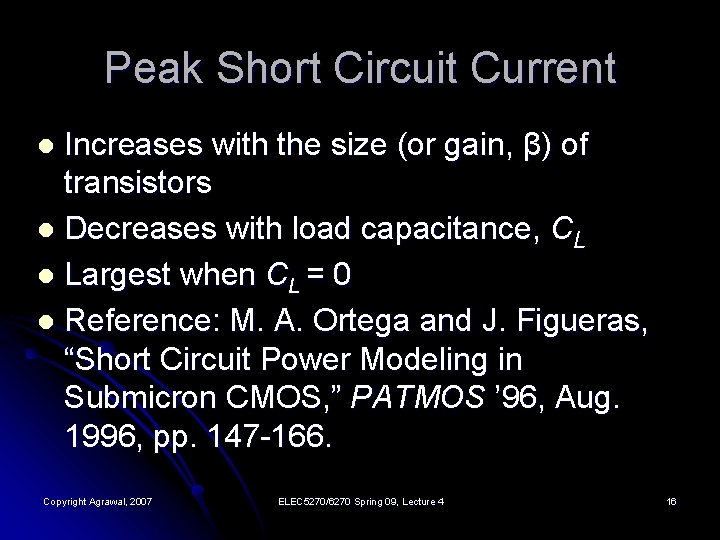

Peak Short Circuit Current Increases with the size (or gain, β) of transistors l Decreases with load capacitance, CL l Largest when CL = 0 l Reference: M. A. Ortega and J. Figueras, “Short Circuit Power Modeling in Submicron CMOS, ” PATMOS ’ 96, Aug. 1996, pp. 147 -166. l Copyright Agrawal, 2007 ELEC 5270/6270 Spring 09, Lecture 4 16

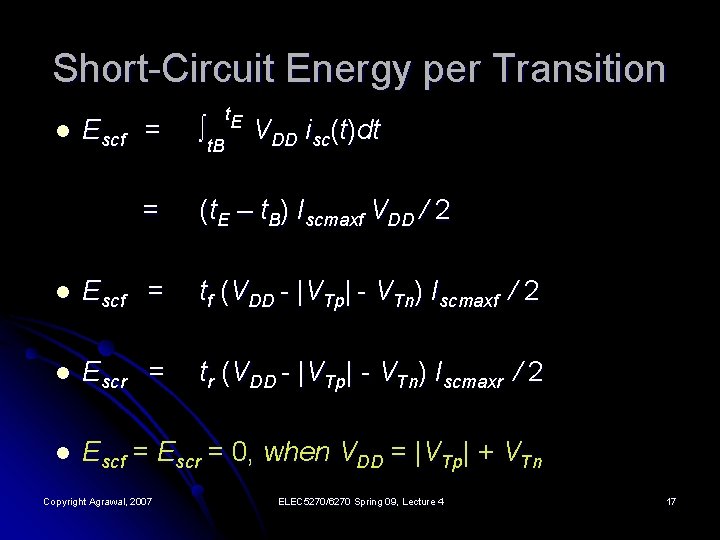

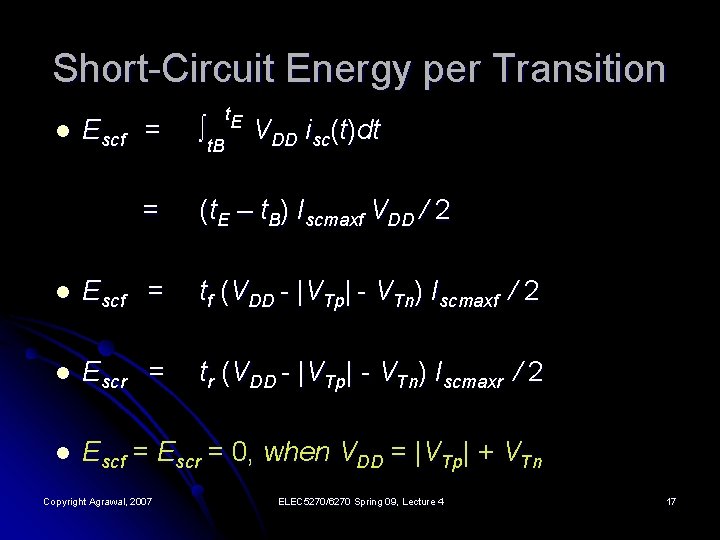

Short-Circuit Energy per Transition l Escf = = t. E ∫t. B VDD isc(t)dt (t. E – t. B) Iscmaxf VDD / 2 l Escf = tf (VDD - |VTp| - VTn) Iscmaxf / 2 l Escr = tr (VDD - |VTp| - VTn) Iscmaxr / 2 l Escf = Escr = 0, when VDD = |VTp| + VTn Copyright Agrawal, 2007 ELEC 5270/6270 Spring 09, Lecture 4 17

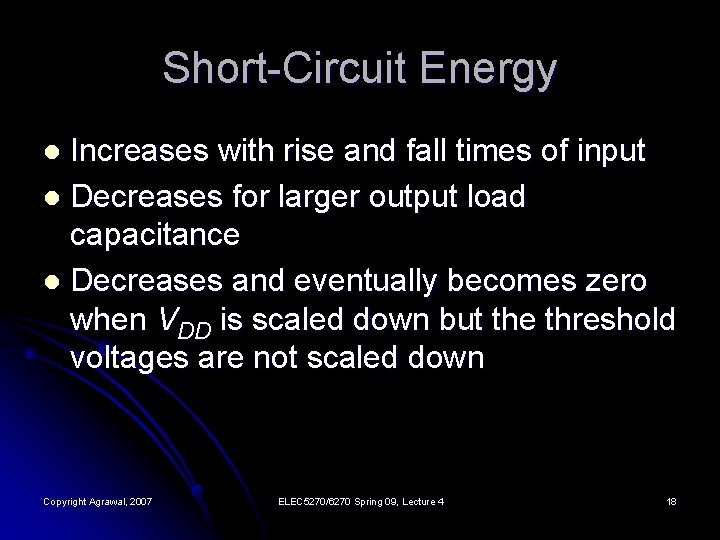

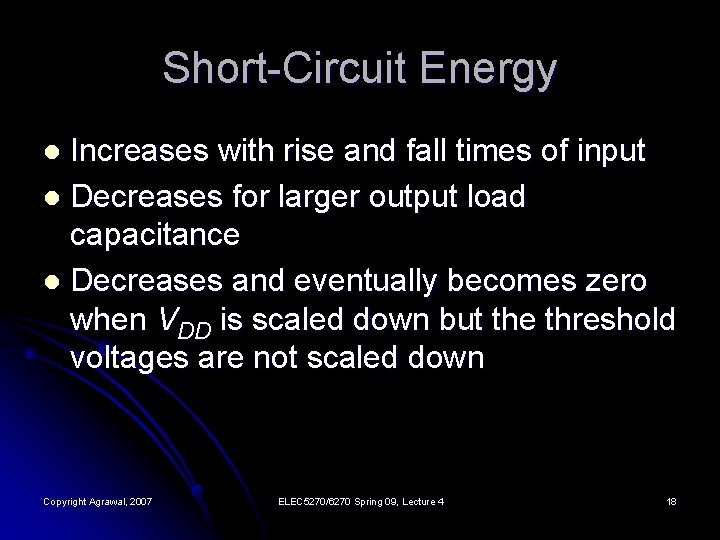

Short-Circuit Energy Increases with rise and fall times of input l Decreases for larger output load capacitance l Decreases and eventually becomes zero when VDD is scaled down but the threshold voltages are not scaled down l Copyright Agrawal, 2007 ELEC 5270/6270 Spring 09, Lecture 4 18

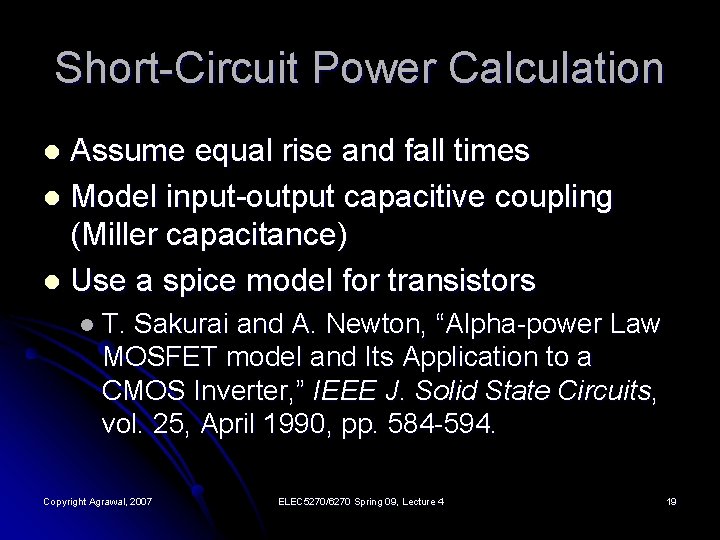

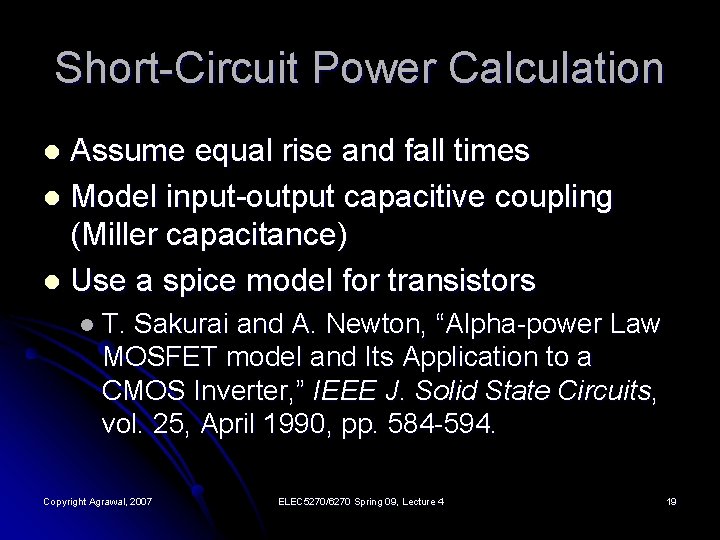

Short-Circuit Power Calculation Assume equal rise and fall times l Model input-output capacitive coupling (Miller capacitance) l Use a spice model for transistors l l T. Sakurai and A. Newton, “Alpha-power Law MOSFET model and Its Application to a CMOS Inverter, ” IEEE J. Solid State Circuits, vol. 25, April 1990, pp. 584 -594. Copyright Agrawal, 2007 ELEC 5270/6270 Spring 09, Lecture 4 19

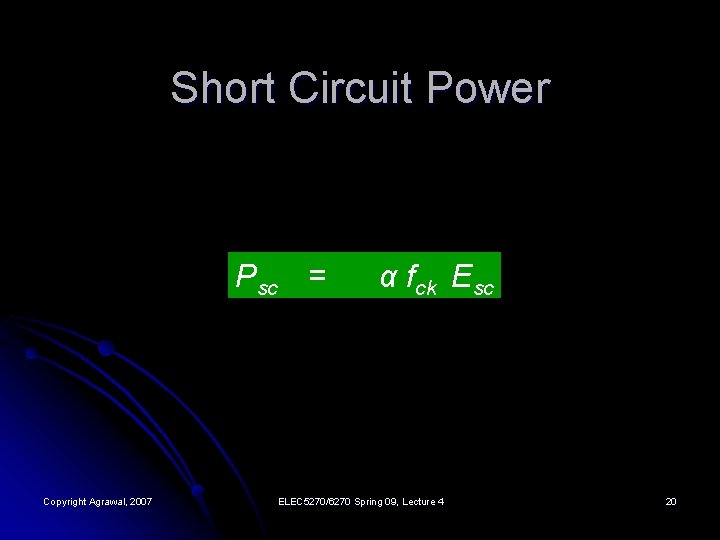

Short Circuit Power Psc = Copyright Agrawal, 2007 α fck Esc ELEC 5270/6270 Spring 09, Lecture 4 20

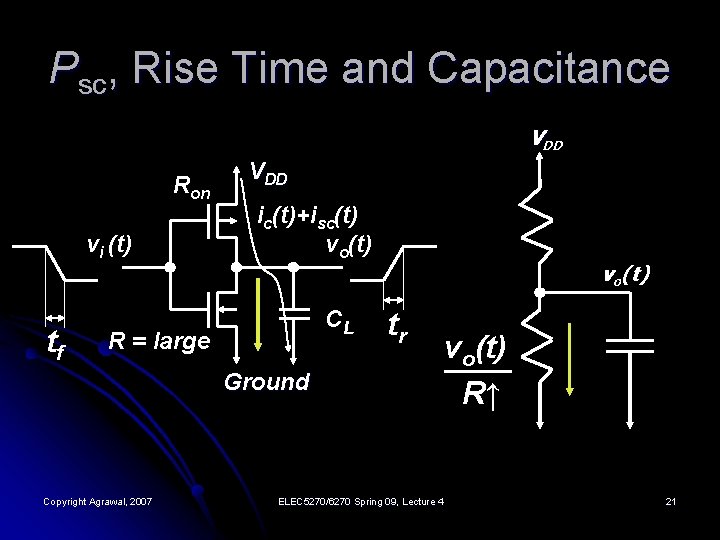

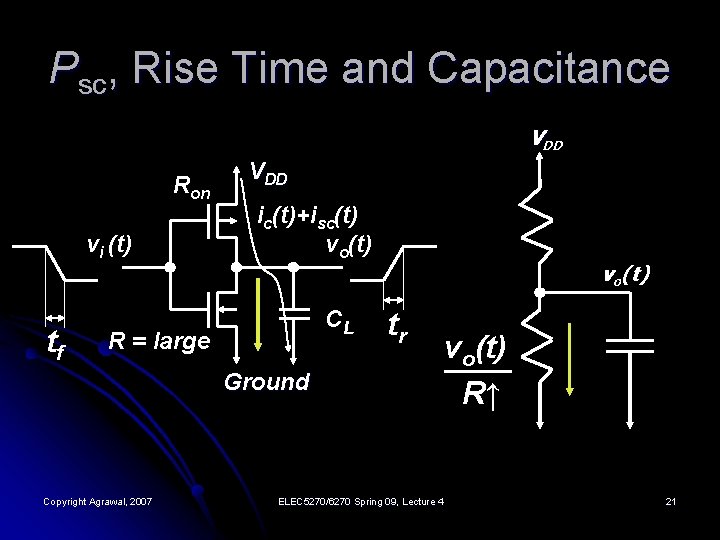

Psc, Rise Time and Capacitance VDD Ron vi (t) tf VDD ic(t)+isc(t) vo(t) CL R = large Ground Copyright Agrawal, 2007 vo(t) tr vo(t) ─── R↑ ELEC 5270/6270 Spring 09, Lecture 4 21

![isc Rise Time and Capacitance Isct Copyright Agrawal 2007 t VDD1 exp isc, Rise Time and Capacitance Isc(t) = Copyright Agrawal, 2007 -t VDD[1 - exp(─────)]](https://slidetodoc.com/presentation_image_h2/b6041af04cc30e37a9cd2bea983692c7/image-22.jpg)

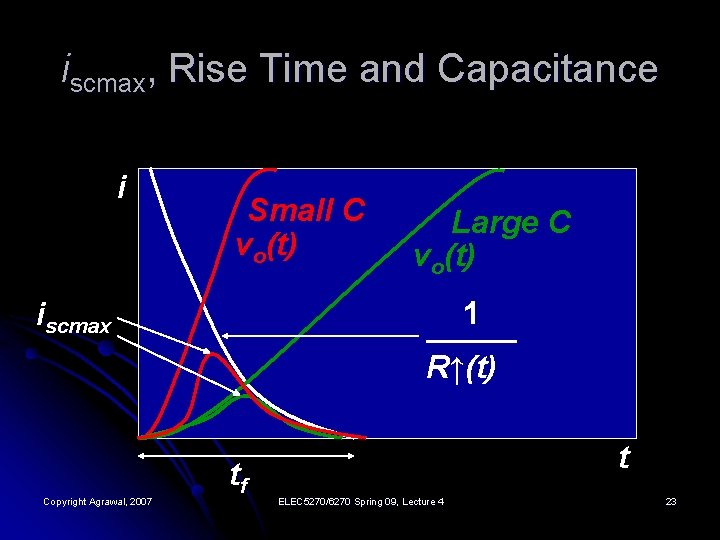

isc, Rise Time and Capacitance Isc(t) = Copyright Agrawal, 2007 -t VDD[1 - exp(─────)] vo(t) R↓(t) C ──── = ─────── R↑(t) ELEC 5270/6270 Spring 09, Lecture 4 22

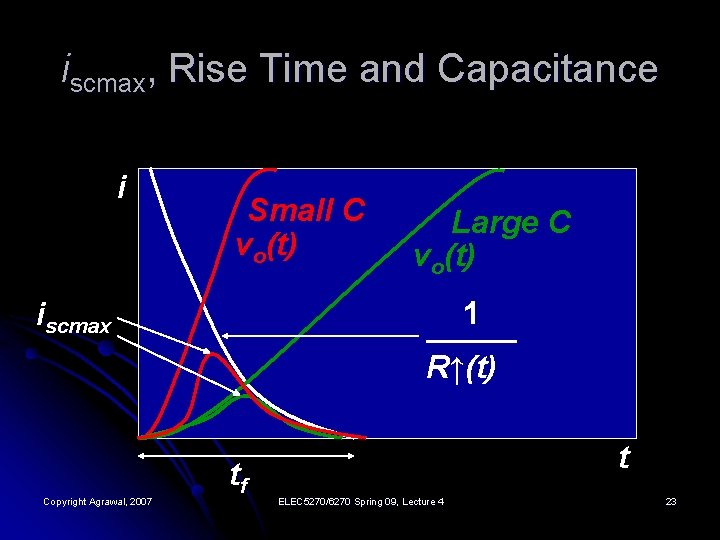

iscmax, Rise Time and Capacitance i Small C vo(t) 1 ──── R↑(t) iscmax Copyright Agrawal, 2007 Large C vo(t) tf t ELEC 5270/6270 Spring 09, Lecture 4 23

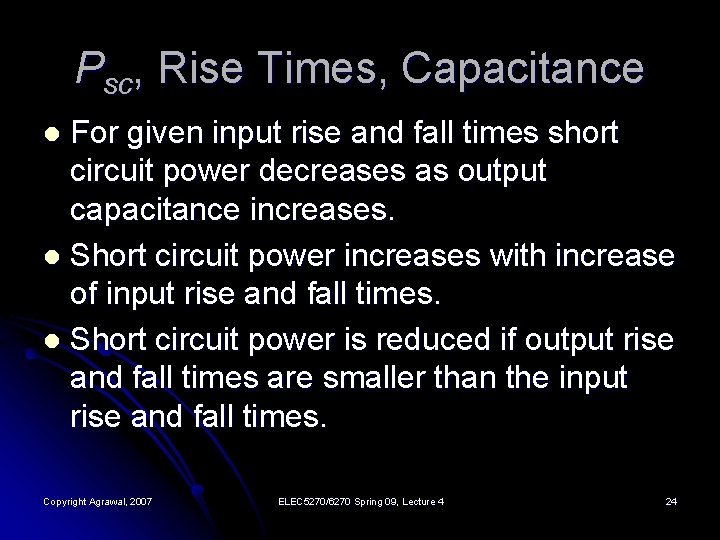

Psc, Rise Times, Capacitance For given input rise and fall times short circuit power decreases as output capacitance increases. l Short circuit power increases with increase of input rise and fall times. l Short circuit power is reduced if output rise and fall times are smaller than the input rise and fall times. l Copyright Agrawal, 2007 ELEC 5270/6270 Spring 09, Lecture 4 24

Summary: Short-Circuit Power l l Short-circuit power is consumed by each transition (increases with input transition time). Reduction requires that gate output transition should not be faster than the input transition (faster gates can consume more short-circuit power). Increasing the output load capacitance reduces short-circuit power. Scaling down of supply voltage with respect to threshold voltages reduces short-circuit power; completely eliminated when VDD ≤ |Vtp| + Vtn. Copyright Agrawal, 2007 ELEC 5270/6270 Spring 09, Lecture 4 25

Components of Power l Dynamic l Signal transitions l Logic activity l Glitches l Short-circuit l Static l Leakage Copyright Agrawal, 2007 ELEC 5270/6270 Spring 09, Lecture 4 26

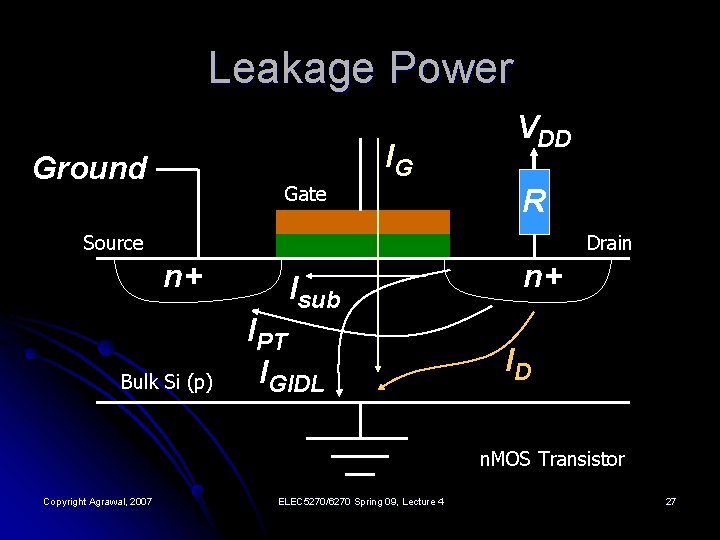

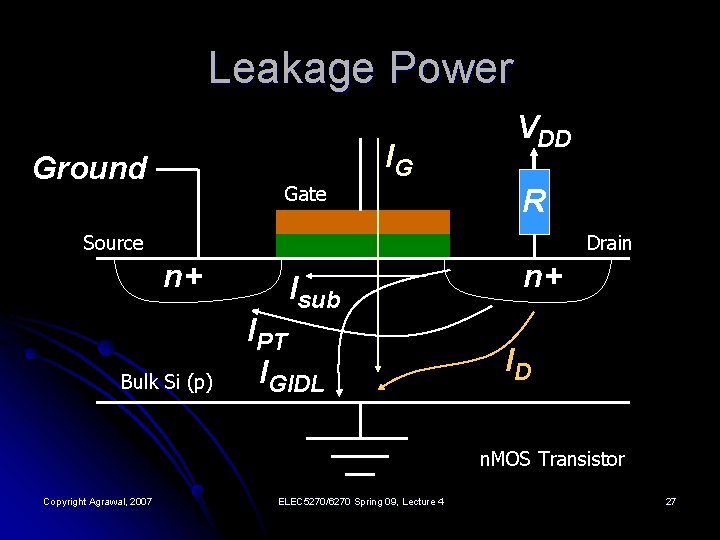

Leakage Power IG Ground Gate VDD R Source Drain n+ Bulk Si (p) Isub IPT IGIDL n+ ID n. MOS Transistor Copyright Agrawal, 2007 ELEC 5270/6270 Spring 09, Lecture 4 27

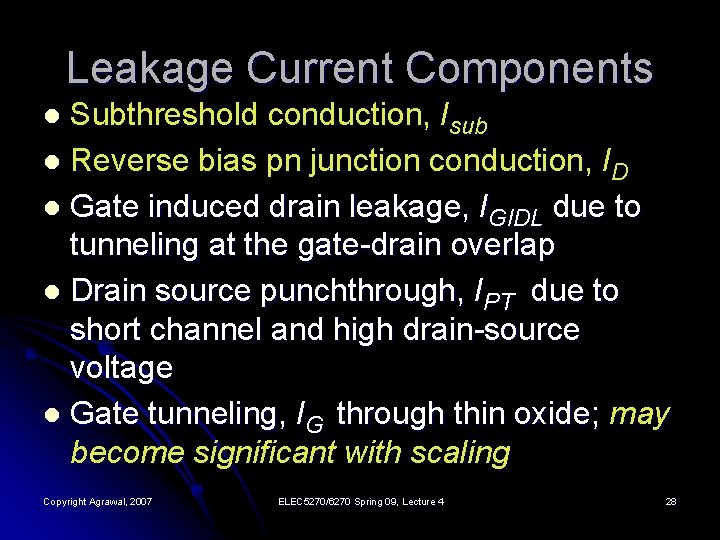

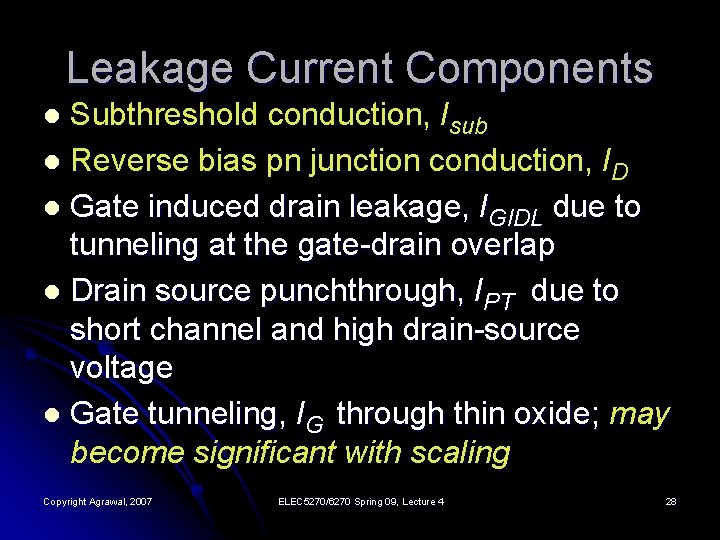

Leakage Current Components Subthreshold conduction, Isub l Reverse bias pn junction conduction, ID l Gate induced drain leakage, IGIDL due to tunneling at the gate-drain overlap l Drain source punchthrough, IPT due to short channel and high drain-source voltage l Gate tunneling, IG through thin oxide; may become significant with scaling l Copyright Agrawal, 2007 ELEC 5270/6270 Spring 09, Lecture 4 28

Subthreshold Current Isub = μ 0 Cox (W/L) Vt 2 exp{(VGS –VTH ) / n. Vt } μ 0: carrier surface mobility Cox: gate oxide capacitance per unit area L: channel length W: gate width Vt = k. T/q: thermal voltage n: a technology parameter Copyright Agrawal, 2007 ELEC 5270/6270 Spring 09, Lecture 4 29

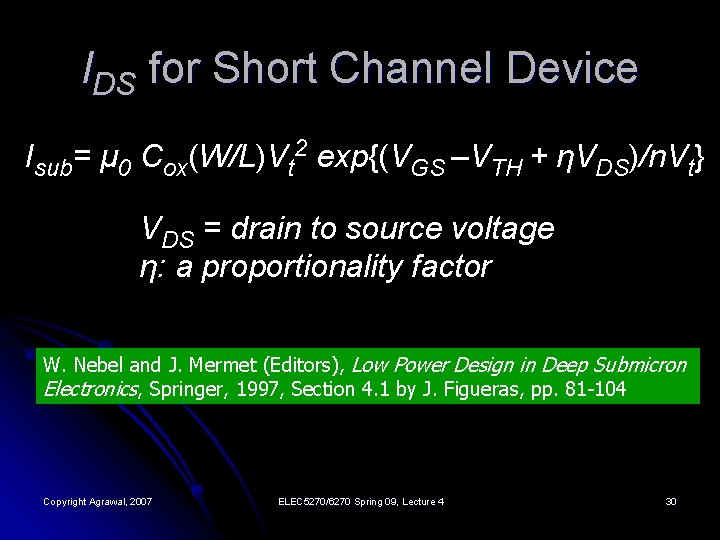

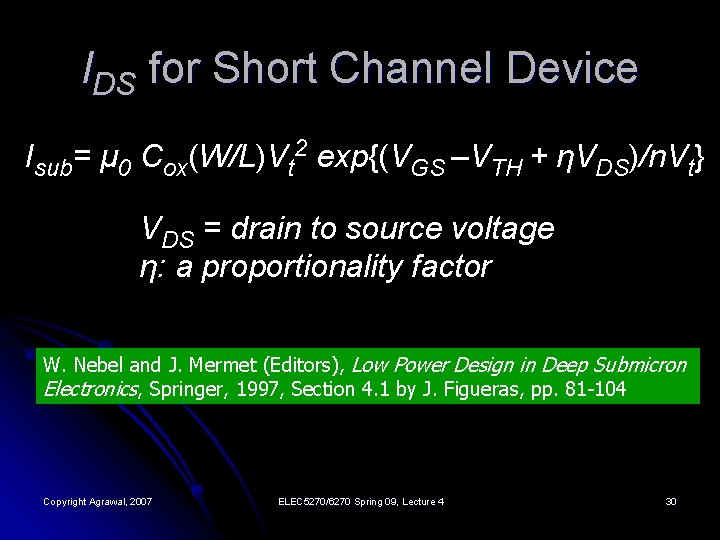

IDS for Short Channel Device Isub= μ 0 Cox(W/L)Vt 2 exp{(VGS –VTH + ηVDS)/n. Vt} VDS = drain to source voltage η: a proportionality factor W. Nebel and J. Mermet (Editors), Low Power Design in Deep Submicron Electronics, Springer, 1997, Section 4. 1 by J. Figueras, pp. 81 -104 Copyright Agrawal, 2007 ELEC 5270/6270 Spring 09, Lecture 4 30

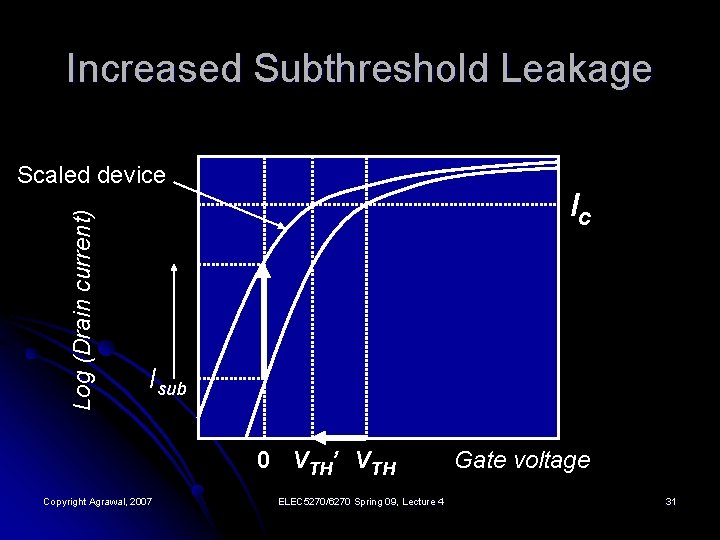

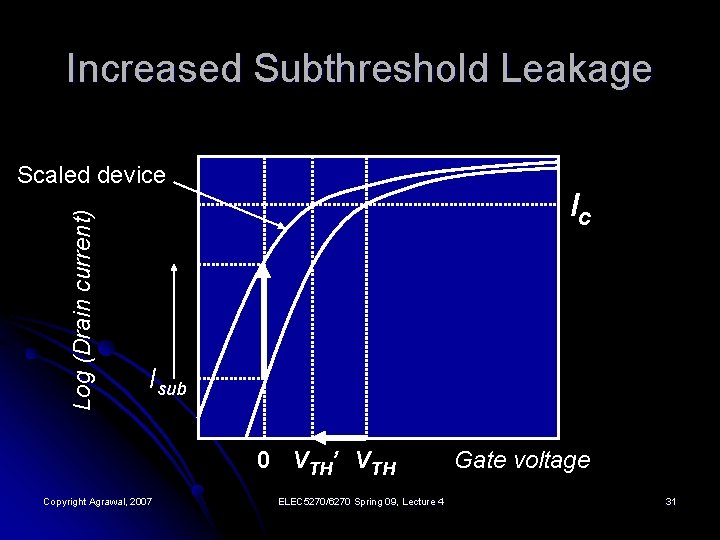

Increased Subthreshold Leakage Log (Drain current) Scaled device Ic Isub 0 VTH’ VTH Copyright Agrawal, 2007 ELEC 5270/6270 Spring 09, Lecture 4 Gate voltage 31

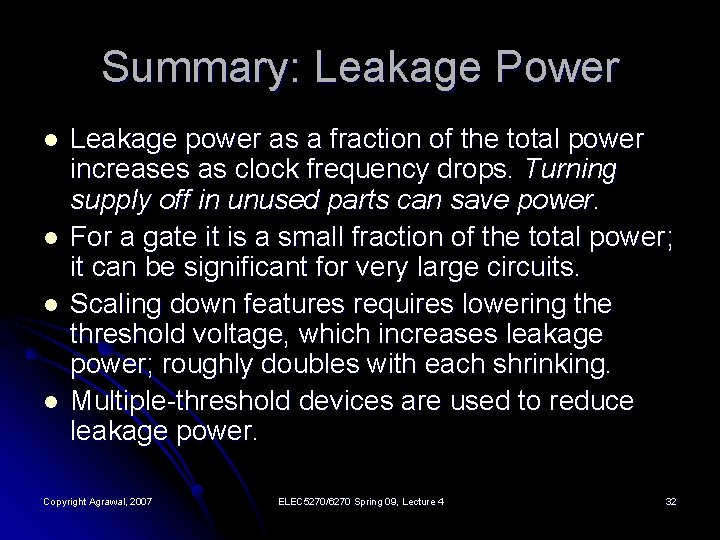

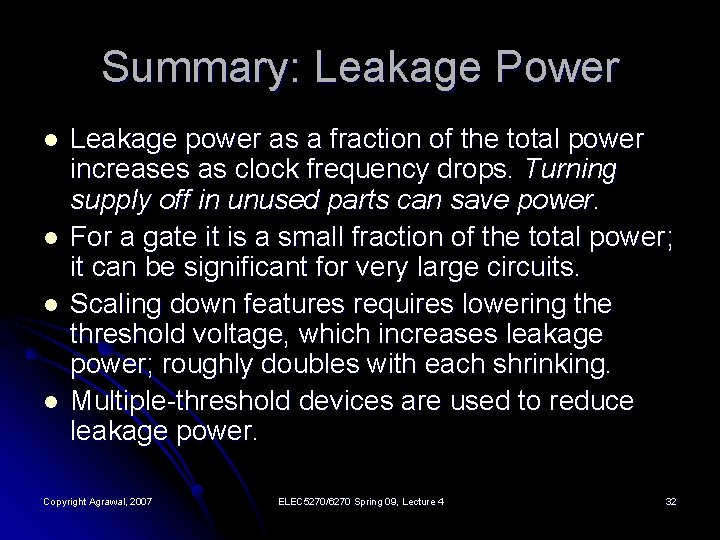

Summary: Leakage Power l l Leakage power as a fraction of the total power increases as clock frequency drops. Turning supply off in unused parts can save power. For a gate it is a small fraction of the total power; it can be significant for very large circuits. Scaling down features requires lowering the threshold voltage, which increases leakage power; roughly doubles with each shrinking. Multiple-threshold devices are used to reduce leakage power. Copyright Agrawal, 2007 ELEC 5270/6270 Spring 09, Lecture 4 32

Technology Scaling down 0. 7 micron by factors 2 and 4 leads to 0. 35 and 0. 17 micron technologies l Constant electric field assumed l Copyright Agrawal, 2007 ELEC 5270/6270 Spring 09, Lecture 4 33

Constant Electric Field Scaling B. Davari, R. H. Dennard and G. G. Shahidi, “CMOS Scaling for High Performance and Low Power—The Next Ten Years, ” Proc. IEEE, April 1995, pp. 595 -606. l Other forms of scaling are referred to as constant-voltage and quasi-constantvoltage. l Copyright Agrawal, 2007 ELEC 5270/6270 Spring 09, Lecture 4 34

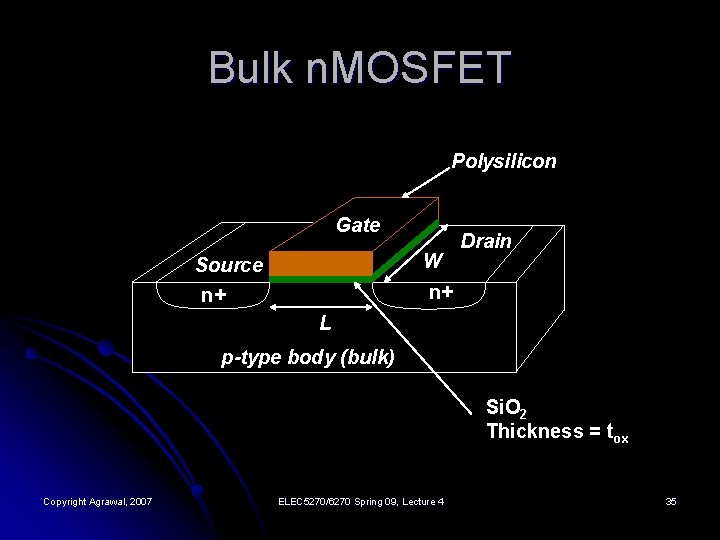

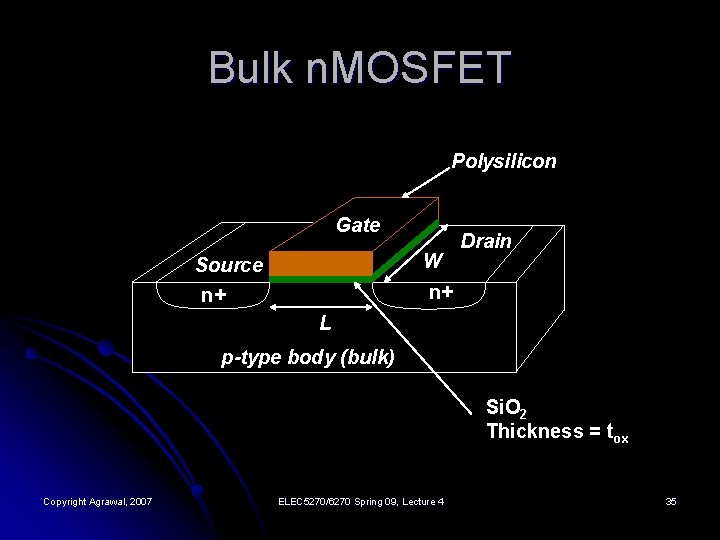

Bulk n. MOSFET Polysilicon Gate W Source Drain n+ n+ L p-type body (bulk) Si. O 2 Thickness = tox Copyright Agrawal, 2007 ELEC 5270/6270 Spring 09, Lecture 4 35

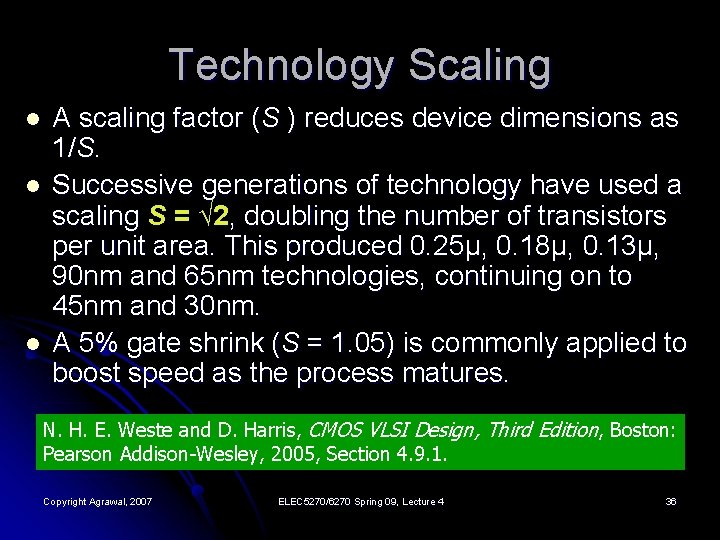

Technology Scaling l l l A scaling factor (S ) reduces device dimensions as 1/S. Successive generations of technology have used a scaling S = √ 2, doubling the number of transistors per unit area. This produced 0. 25μ, 0. 18μ, 0. 13μ, 90 nm and 65 nm technologies, continuing on to 45 nm and 30 nm. A 5% gate shrink (S = 1. 05) is commonly applied to boost speed as the process matures. N. H. E. Weste and D. Harris, CMOS VLSI Design, Third Edition, Boston: Pearson Addison-Wesley, 2005, Section 4. 9. 1. Copyright Agrawal, 2007 ELEC 5270/6270 Spring 09, Lecture 4 36

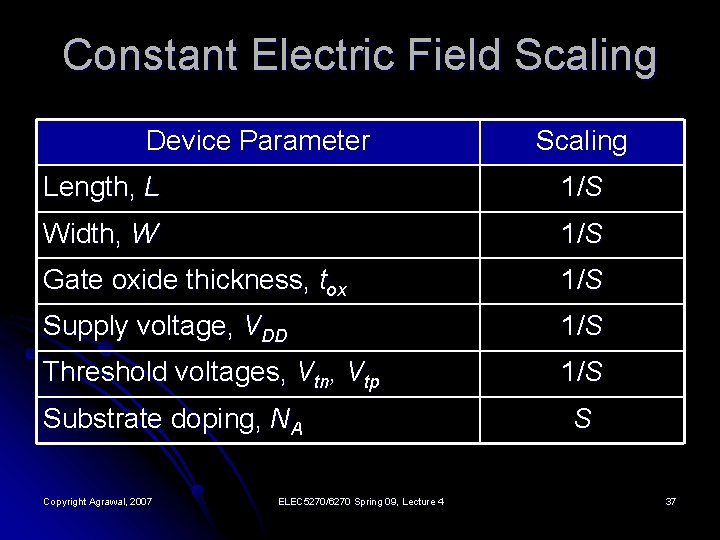

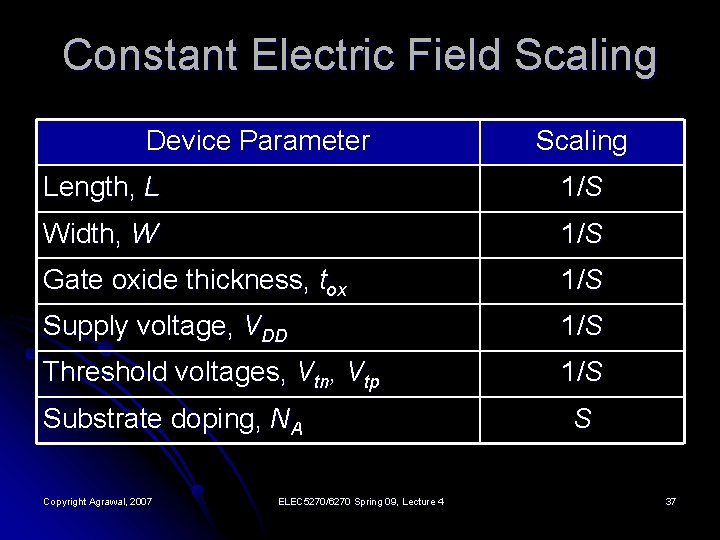

Constant Electric Field Scaling Device Parameter Scaling Length, L 1/S Width, W 1/S Gate oxide thickness, tox 1/S Supply voltage, VDD 1/S Threshold voltages, Vtn, Vtp 1/S Substrate doping, NA Copyright Agrawal, 2007 ELEC 5270/6270 Spring 09, Lecture 4 S 37

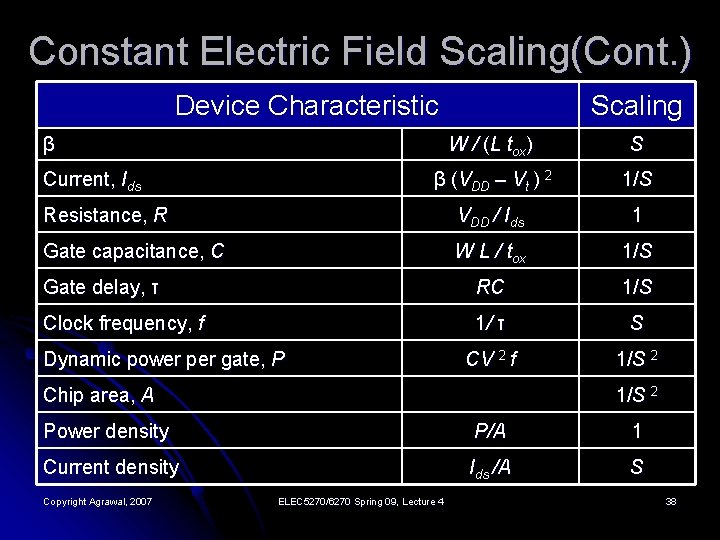

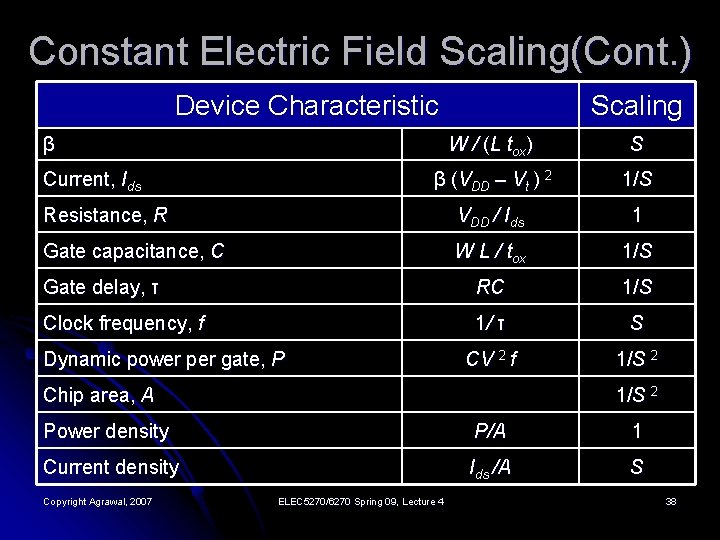

Constant Electric Field Scaling(Cont. ) Device Characteristic β Scaling W / (L tox) S β (VDD – Vt ) 2 1/S Resistance, R VDD / Ids 1 Gate capacitance, C W L / tox 1/S Gate delay, τ RC 1/S Clock frequency, f 1/ τ S CV 2 f 1/S 2 Current, Ids Dynamic power per gate, P Chip area, A 1/S 2 Power density P/A 1 Current density Ids /A S Copyright Agrawal, 2007 ELEC 5270/6270 Spring 09, Lecture 4 38

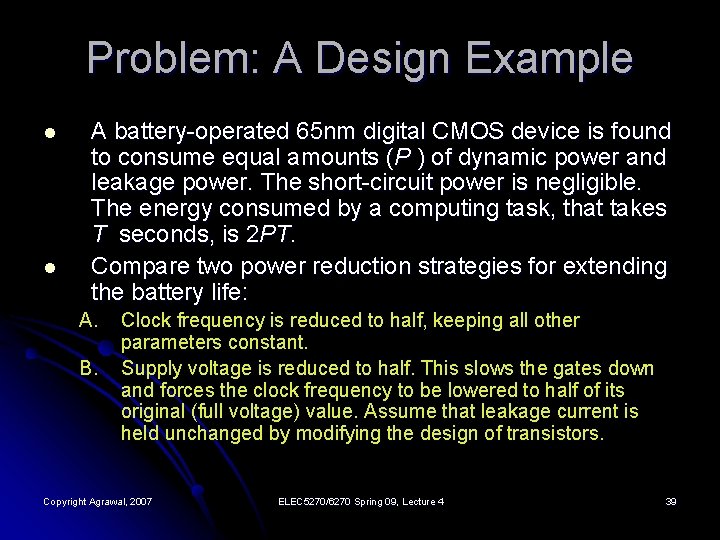

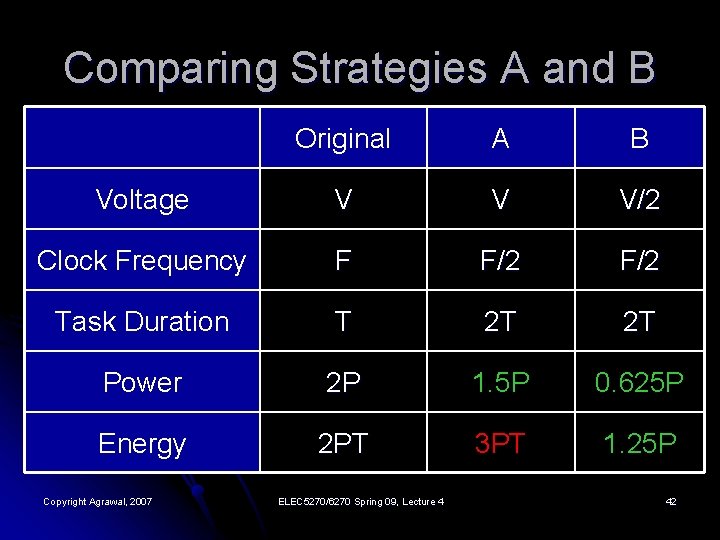

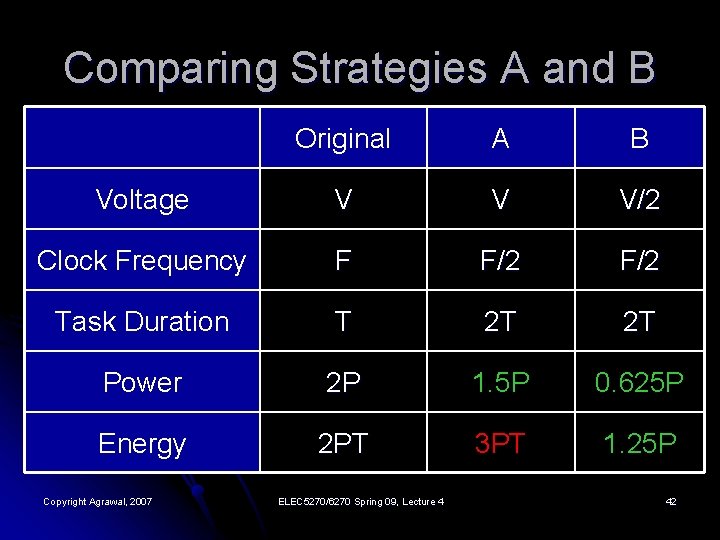

Problem: A Design Example l l A battery-operated 65 nm digital CMOS device is found to consume equal amounts (P ) of dynamic power and leakage power. The short-circuit power is negligible. The energy consumed by a computing task, that takes T seconds, is 2 PT. Compare two power reduction strategies for extending the battery life: A. B. Clock frequency is reduced to half, keeping all other parameters constant. Supply voltage is reduced to half. This slows the gates down and forces the clock frequency to be lowered to half of its original (full voltage) value. Assume that leakage current is held unchanged by modifying the design of transistors. Copyright Agrawal, 2007 ELEC 5270/6270 Spring 09, Lecture 4 39

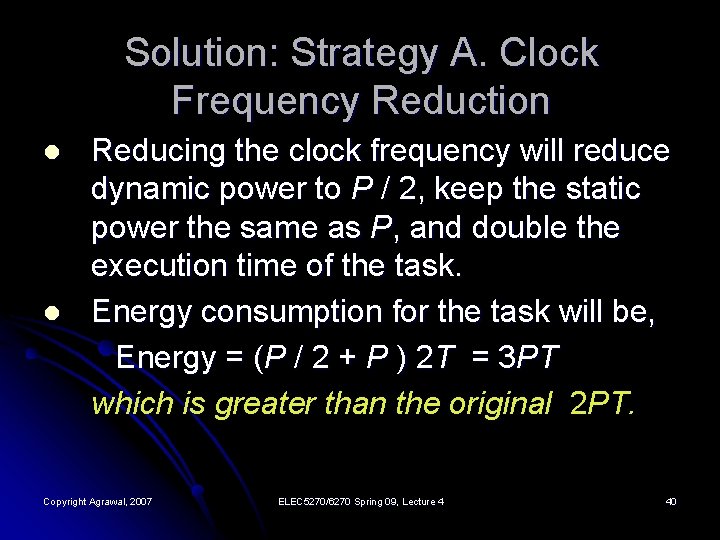

Solution: Strategy A. Clock Frequency Reduction l l Reducing the clock frequency will reduce dynamic power to P / 2, keep the static power the same as P, and double the execution time of the task. Energy consumption for the task will be, Energy = (P / 2 + P ) 2 T = 3 PT which is greater than the original 2 PT. Copyright Agrawal, 2007 ELEC 5270/6270 Spring 09, Lecture 4 40

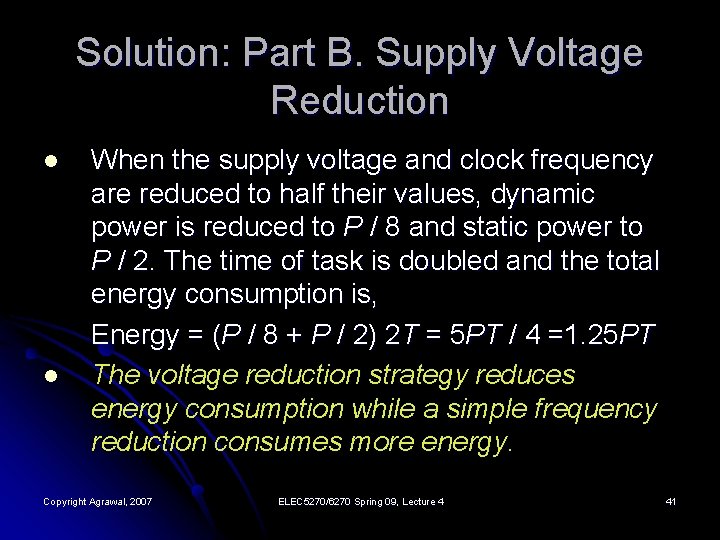

Solution: Part B. Supply Voltage Reduction l l When the supply voltage and clock frequency are reduced to half their values, dynamic power is reduced to P / 8 and static power to P / 2. The time of task is doubled and the total energy consumption is, Energy = (P / 8 + P / 2) 2 T = 5 PT / 4 =1. 25 PT The voltage reduction strategy reduces energy consumption while a simple frequency reduction consumes more energy. Copyright Agrawal, 2007 ELEC 5270/6270 Spring 09, Lecture 4 41

Comparing Strategies A and B Original A B Voltage V V V/2 Clock Frequency F F/2 Task Duration T 2 T 2 T Power 2 P 1. 5 P 0. 625 P Energy 2 PT 3 PT 1. 25 P Copyright Agrawal, 2007 ELEC 5270/6270 Spring 09, Lecture 4 42