CAPITOLUL 7 Tematic Prezentare general Multiplexoare logice Decodificatoare

- Slides: 43

CAPITOLUL 7

Tematică Ø Prezentare generală Ø Multiplexoare logice Ø Decodificatoare logice Ø Sumatoare binare Ø Codificatoare de priorităţi Ø Comparatoare Ø Generatoare bit de paritate 11/3/2020 BLPC curs 2008 -2009 2

Multiplexoare logice 11/3/2020 BLPC curs 2009 -2010 3

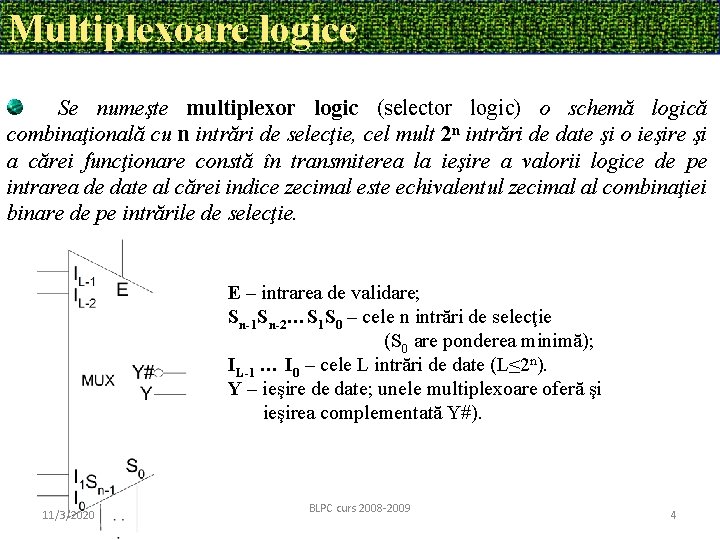

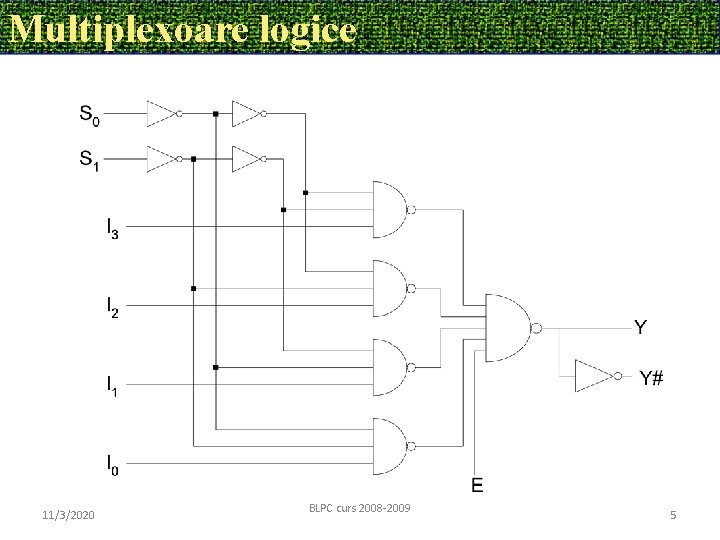

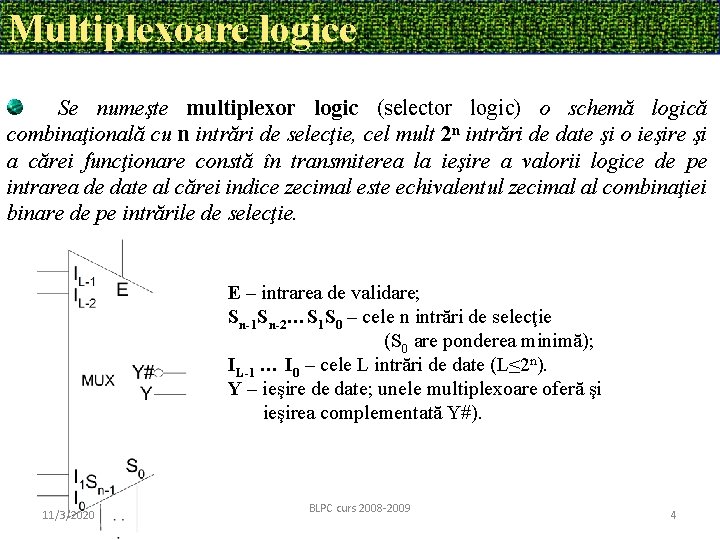

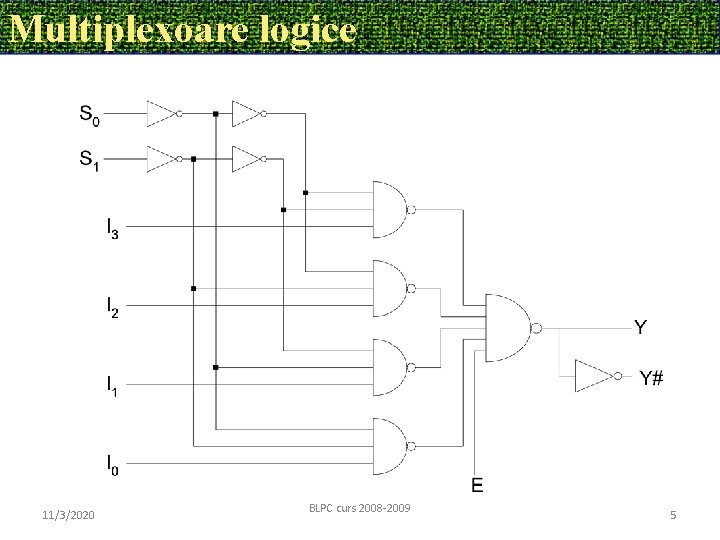

Multiplexoare logice Se numeşte multiplexor logic (selector logic) o schemă logică combinaţională cu n intrări de selecţie, cel mult 2 n intrări de date şi o ieşire şi a cărei funcţionare constă în transmiterea la ieşire a valorii logice de pe intrarea de date al cărei indice zecimal este echivalentul zecimal al combinaţiei binare de pe intrările de selecţie. E – intrarea de validare; Sn-1 Sn-2…S 1 S 0 – cele n intrări de selecţie (S 0 are ponderea minimă); IL-1 … I 0 – cele L intrări de date (L≤ 2 n). Y – ieşire de date; unele multiplexoare oferă şi ieşirea complementată Y#). 11/3/2020 BLPC curs 2008 -2009 4

Multiplexoare logice 11/3/2020 BLPC curs 2008 -2009 5

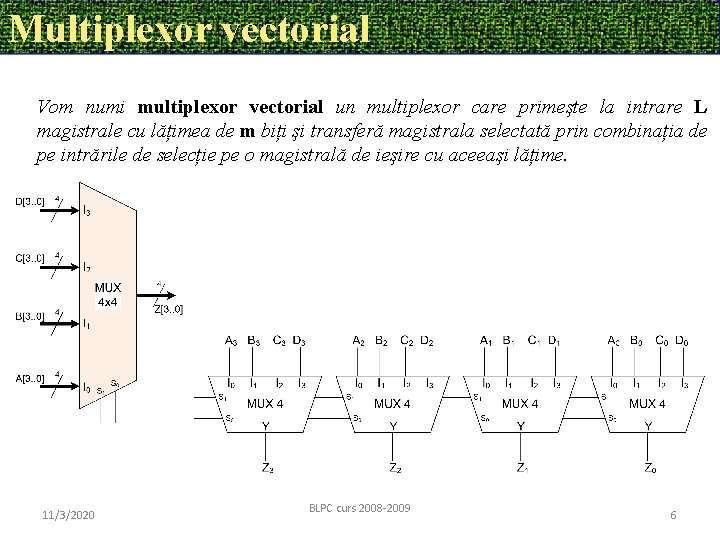

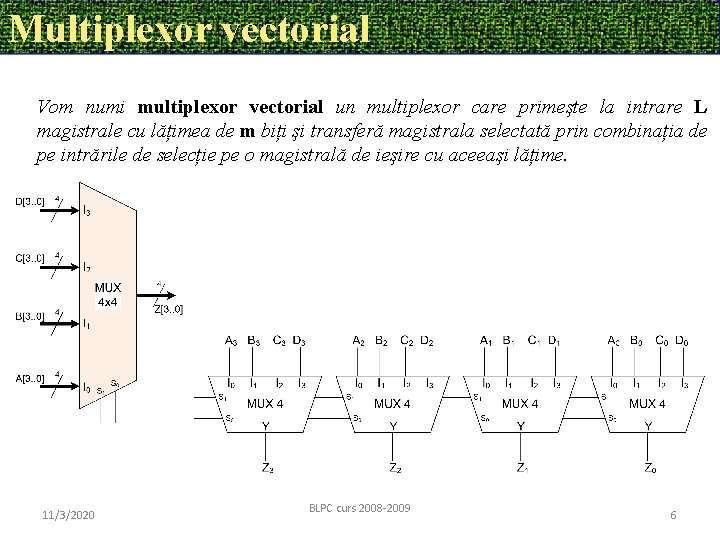

Multiplexor vectorial Vom numi multiplexor vectorial un multiplexor care primeşte la intrare L magistrale cu lățimea de m biți şi transferă magistrala selectată prin combinația de pe intrările de selecție pe o magistrală de ieşire cu aceeaşi lățime. 11/3/2020 BLPC curs 2008 -2009 6

Decodificatoare logice 11/3/2020 BLPC curs 2007 -2008 7

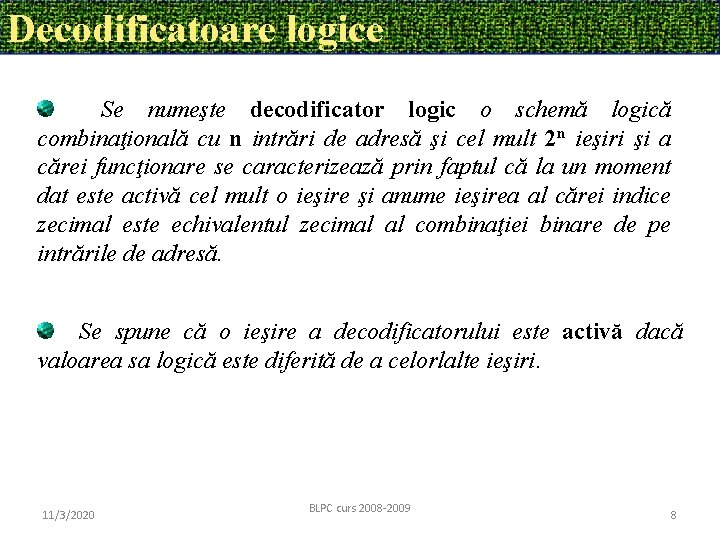

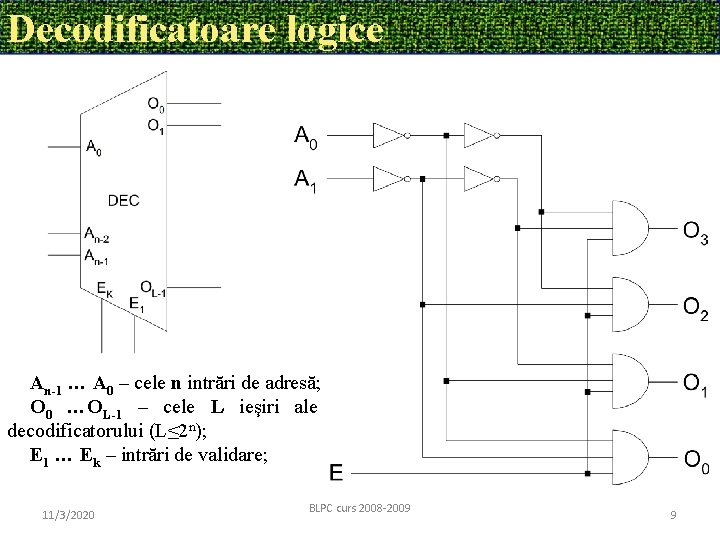

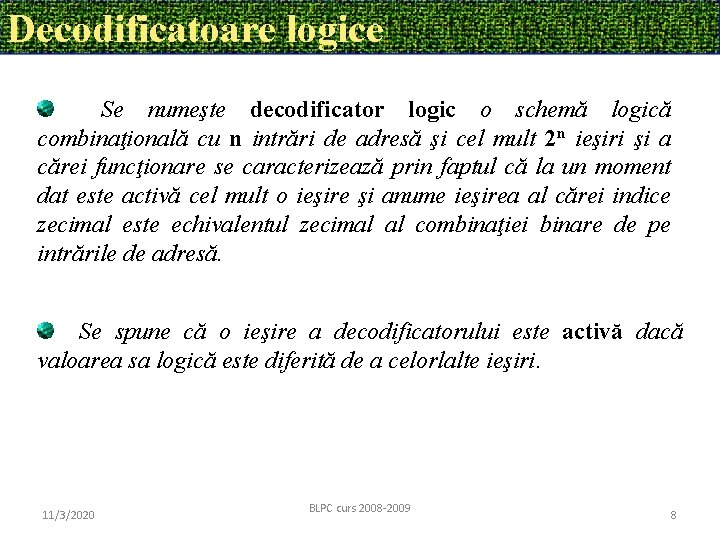

Decodificatoare logice Se numeşte decodificator logic o schemă logică combinaţională cu n intrări de adresă şi cel mult 2 n ieşiri şi a cărei funcţionare se caracterizează prin faptul că la un moment dat este activă cel mult o ieşire şi anume ieşirea al cărei indice zecimal este echivalentul zecimal al combinaţiei binare de pe intrările de adresă. Se spune că o ieşire a decodificatorului este activă dacă valoarea sa logică este diferită de a celorlalte ieşiri. 11/3/2020 BLPC curs 2008 -2009 8

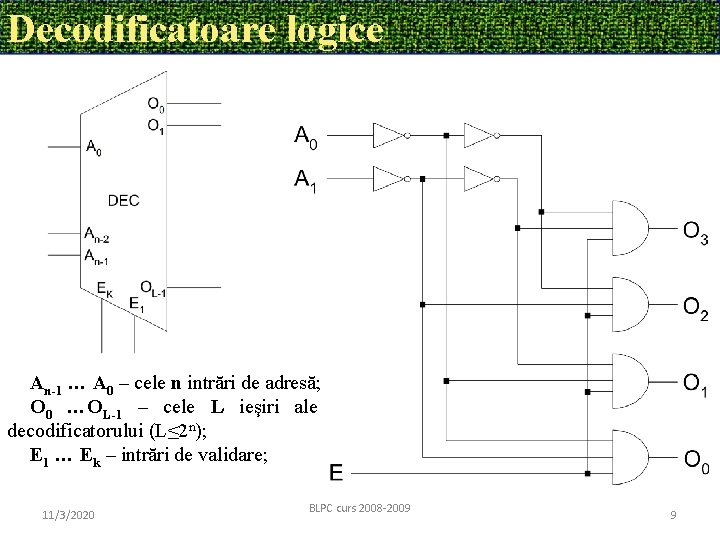

Decodificatoare logice An-1 … A 0 – cele n intrări de adresă; O 0 …OL-1 – cele L ieşiri ale decodificatorului (L≤ 2 n); E 1 … Ek – intrări de validare; 11/3/2020 BLPC curs 2008 -2009 9

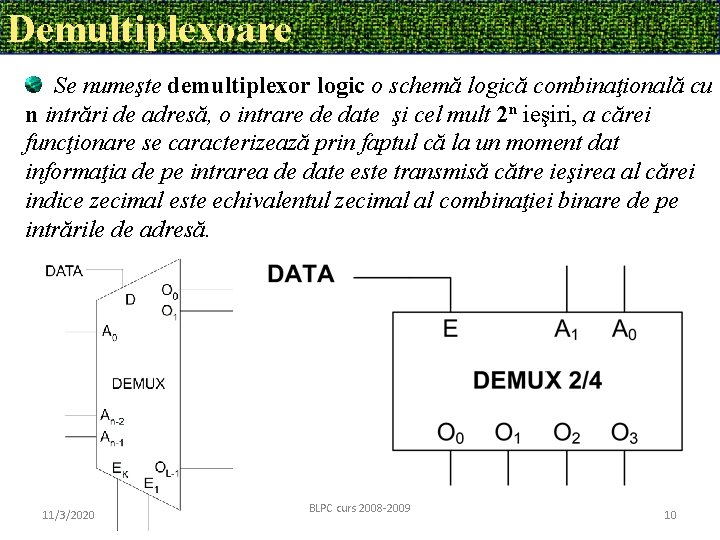

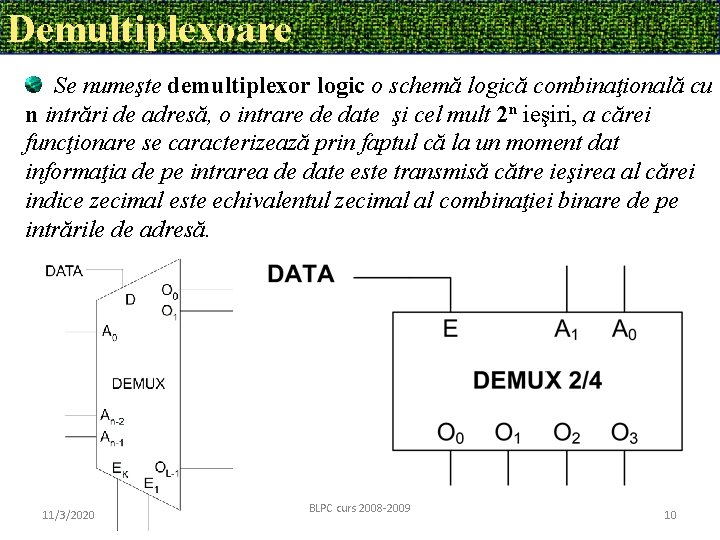

Demultiplexoare Se numeşte demultiplexor logic o schemă logică combinaţională cu n intrări de adresă, o intrare de date şi cel mult 2 n ieşiri, a cărei funcţionare se caracterizează prin faptul că la un moment dat informaţia de pe intrarea de date este transmisă către ieşirea al cărei indice zecimal este echivalentul zecimal al combinaţiei binare de pe intrările de adresă. 11/3/2020 BLPC curs 2008 -2009 10

Sumatoare binare 11/3/2020 11

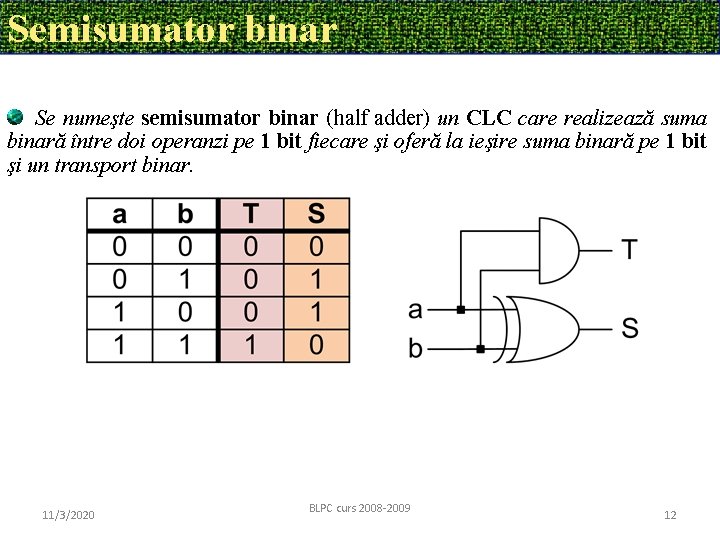

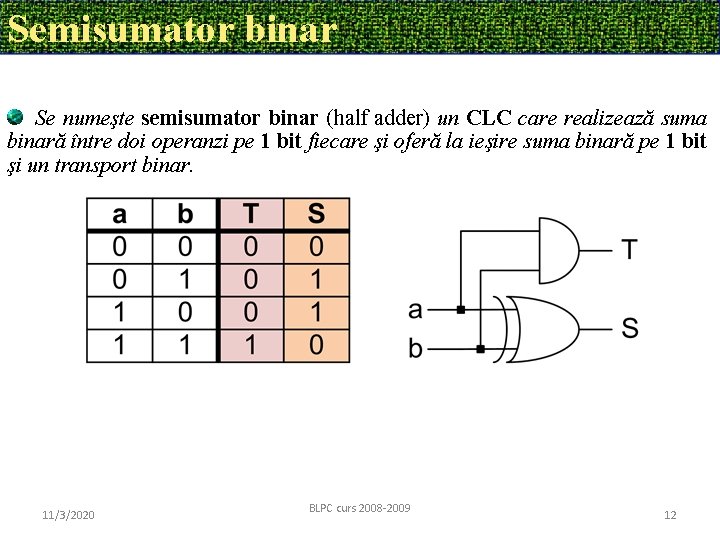

Semisumator binar Se numeşte semisumator binar (half adder) un CLC care realizează suma binară între doi operanzi pe 1 bit fiecare şi oferă la ieşire suma binară pe 1 bit şi un transport binar. 11/3/2020 BLPC curs 2008 -2009 12

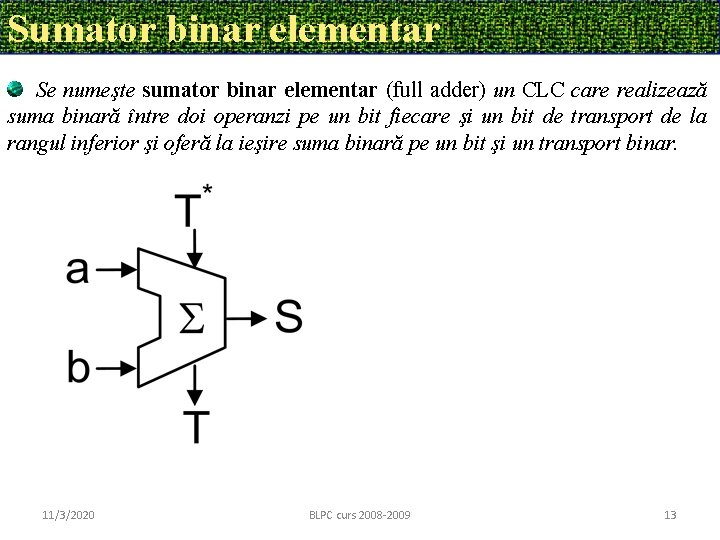

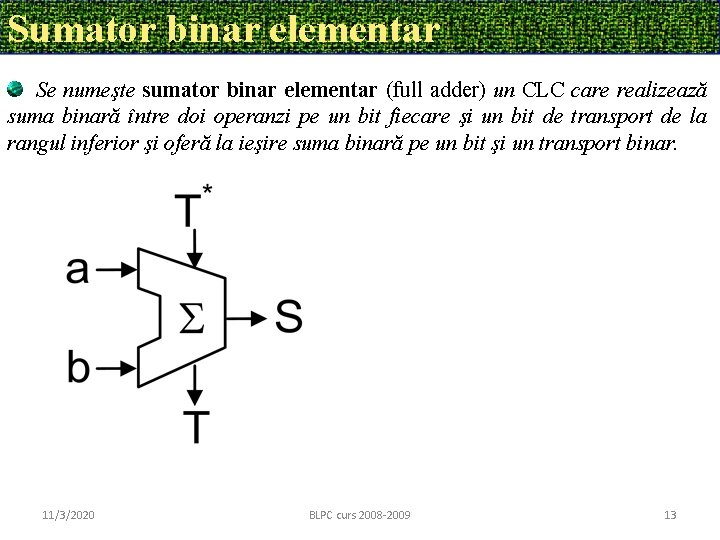

Sumator binar elementar Se numeşte sumator binar elementar (full adder) un CLC care realizează suma binară între doi operanzi pe un bit fiecare şi un bit de transport de la rangul inferior şi oferă la ieşire suma binară pe un bit şi un transport binar. 11/3/2020 BLPC curs 2008 -2009 13

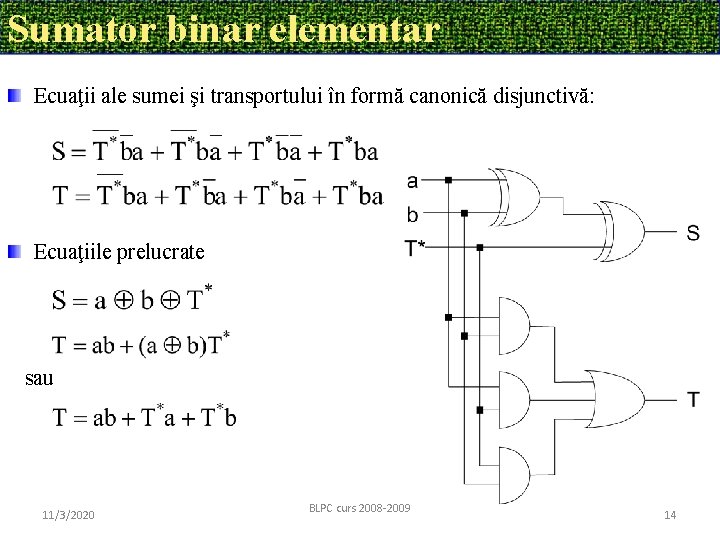

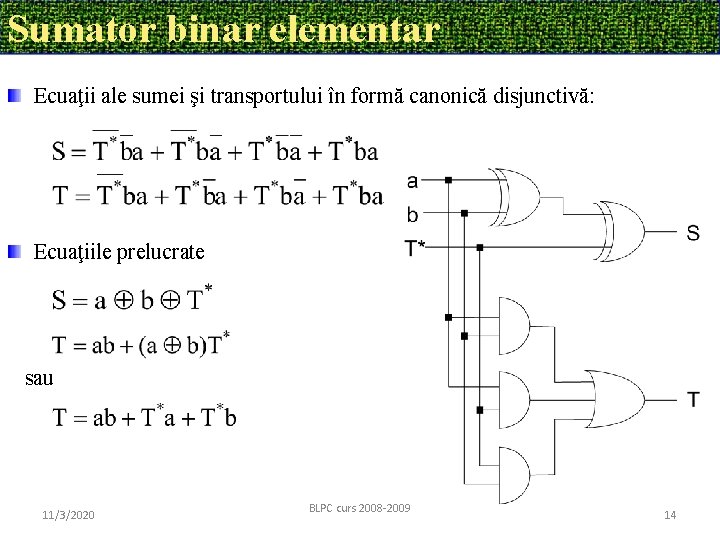

Sumator binar elementar Ecuaţii ale sumei şi transportului în formă canonică disjunctivă: Ecuaţiile prelucrate sau 11/3/2020 BLPC curs 2008 -2009 14

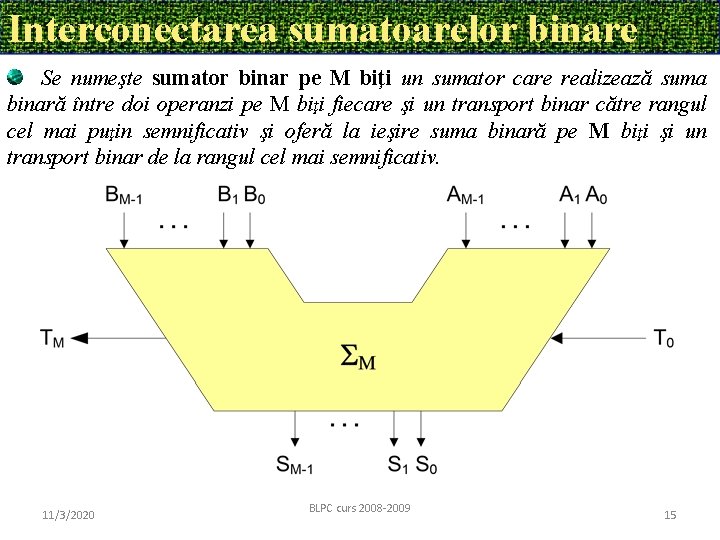

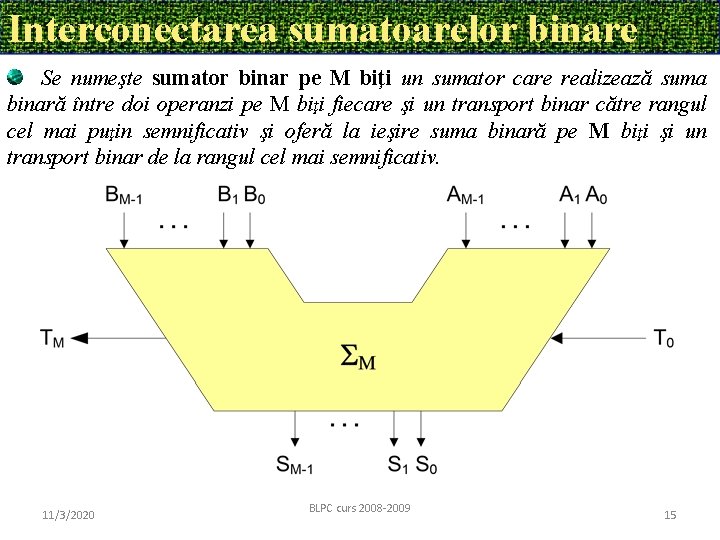

Interconectarea sumatoarelor binare Se numeşte sumator binar pe M biţi un sumator care realizează suma binară între doi operanzi pe M biţi fiecare şi un transport binar către rangul cel mai puţin semnificativ şi oferă la ieşire suma binară pe M biţi şi un transport binar de la rangul cel mai semnificativ. 11/3/2020 BLPC curs 2008 -2009 15

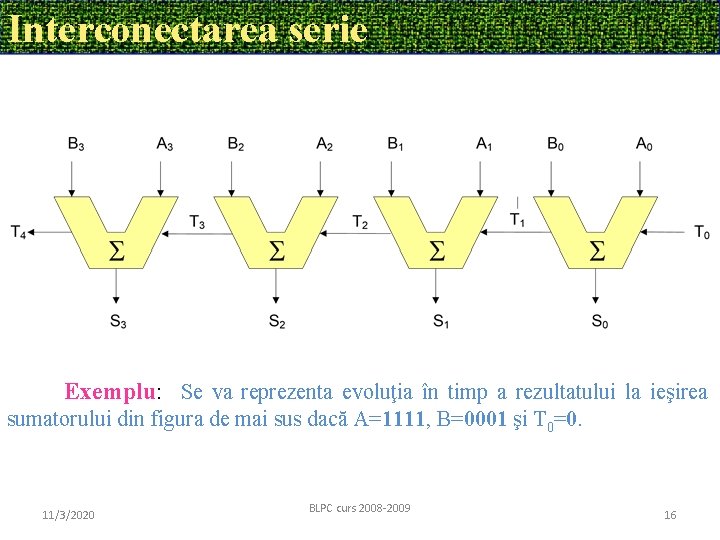

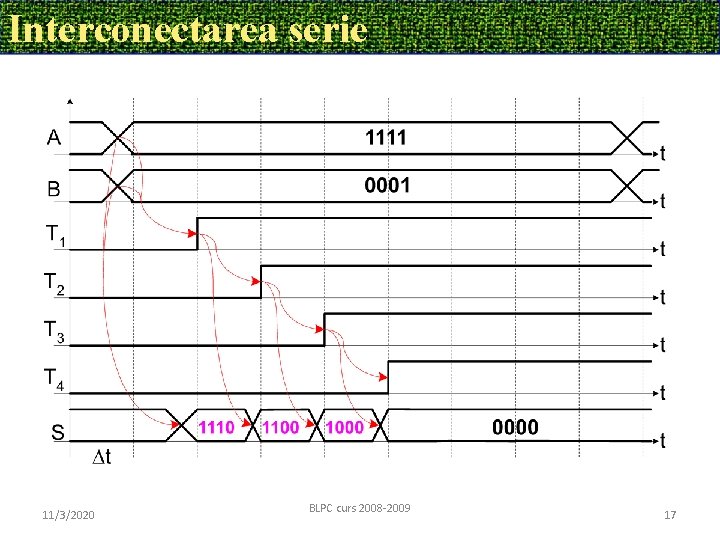

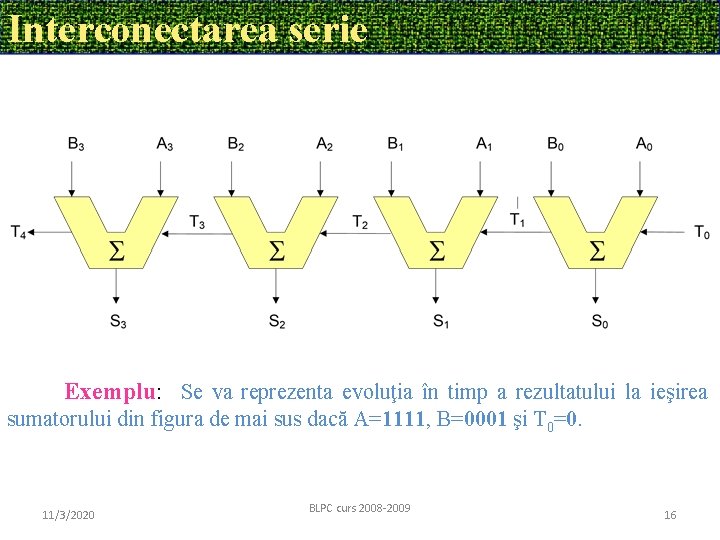

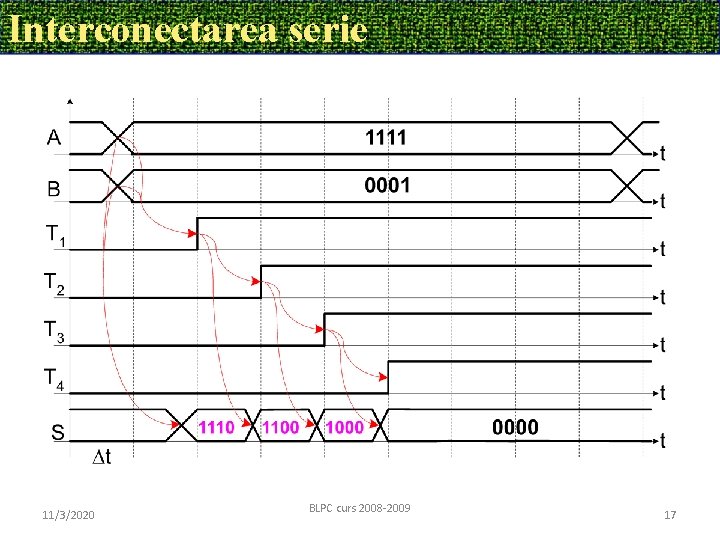

Interconectarea serie Exemplu: Se va reprezenta evoluţia în timp a rezultatului la ieşirea sumatorului din figura de mai sus dacă A=1111, B=0001 şi T 0=0. 11/3/2020 BLPC curs 2008 -2009 16

Interconectarea serie 11/3/2020 BLPC curs 2008 -2009 17

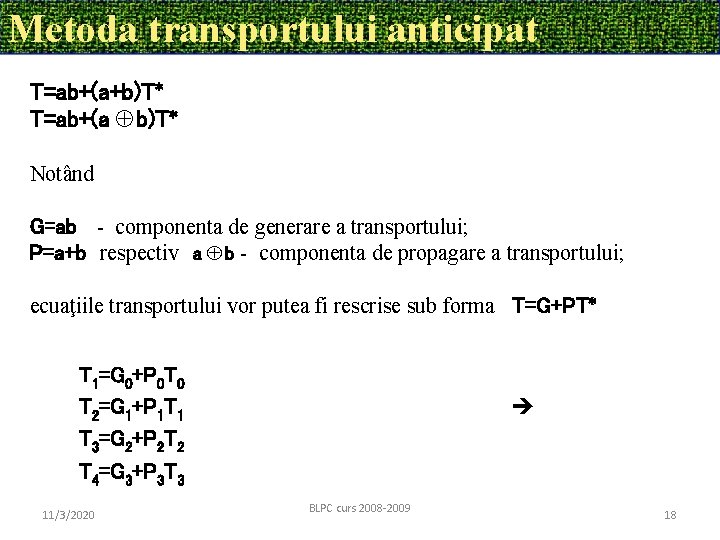

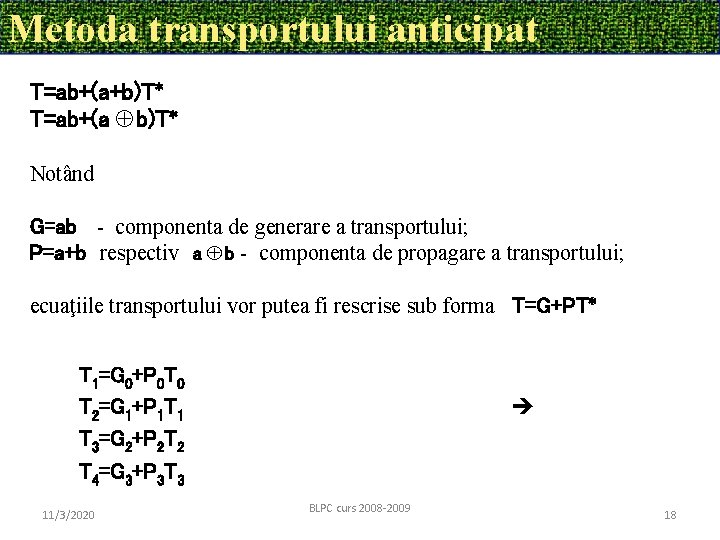

Metoda transportului anticipat T=ab+(a+b)T* T=ab+(a b)T* Notând G=ab - componenta de generare a transportului; P=a+b respectiv a b - componenta de propagare a transportului; ecuaţiile transportului vor putea fi rescrise sub forma T=G+PT* T 1=G 0+P 0 T 0 T 2=G 1+P 1 T 1 T 3=G 2+P 2 T 2 T 4=G 3+P 3 T 3 11/3/2020 BLPC curs 2008 -2009 18

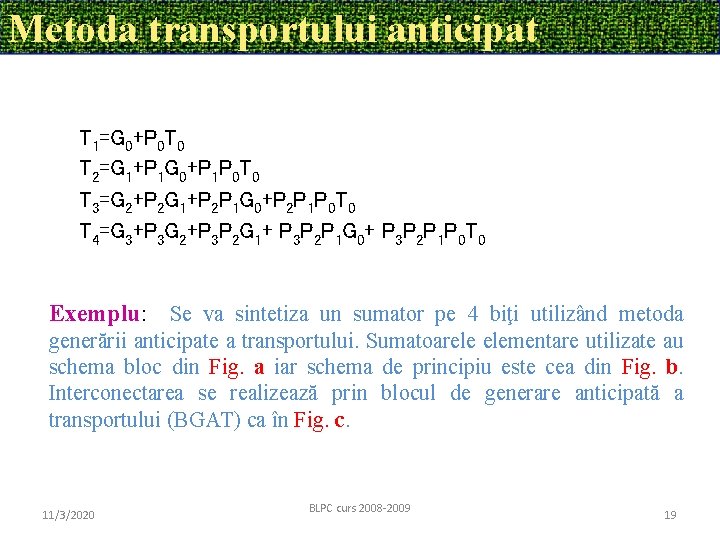

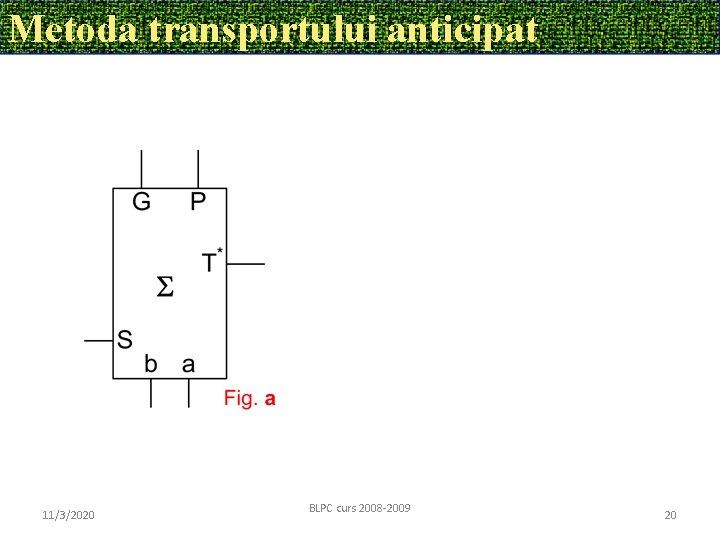

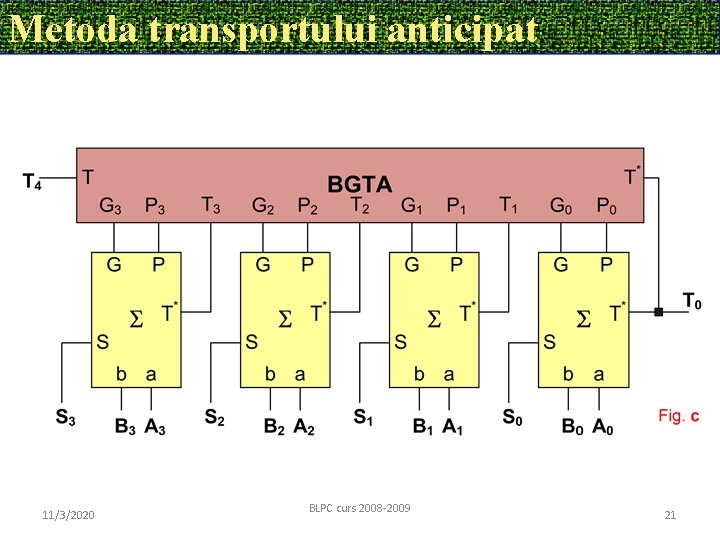

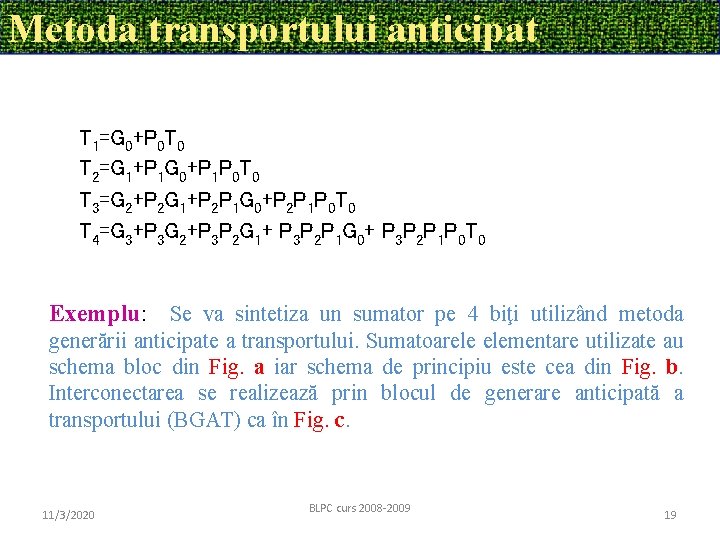

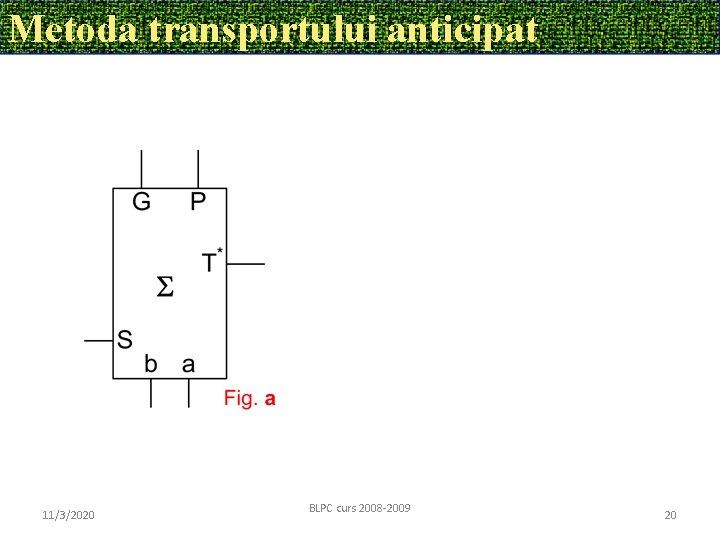

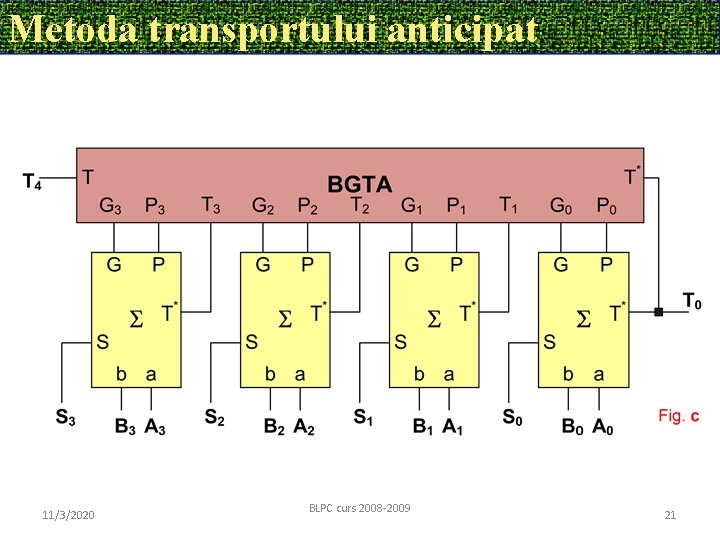

Metoda transportului anticipat T 1=G 0+P 0 T 0 T 2=G 1+P 1 G 0+P 1 P 0 T 0 T 3=G 2+P 2 G 1+P 2 P 1 G 0+P 2 P 1 P 0 T 0 T 4=G 3+P 3 G 2+P 3 P 2 G 1+ P 3 P 2 P 1 G 0+ P 3 P 2 P 1 P 0 T 0 Exemplu: Se va sintetiza un sumator pe 4 biţi utilizând metoda generării anticipate a transportului. Sumatoarele elementare utilizate au schema bloc din Fig. a iar schema de principiu este cea din Fig. b. Interconectarea se realizează prin blocul de generare anticipată a transportului (BGAT) ca în Fig. c. 11/3/2020 BLPC curs 2008 -2009 19

Metoda transportului anticipat 11/3/2020 BLPC curs 2008 -2009 20

Metoda transportului anticipat 11/3/2020 BLPC curs 2008 -2009 21

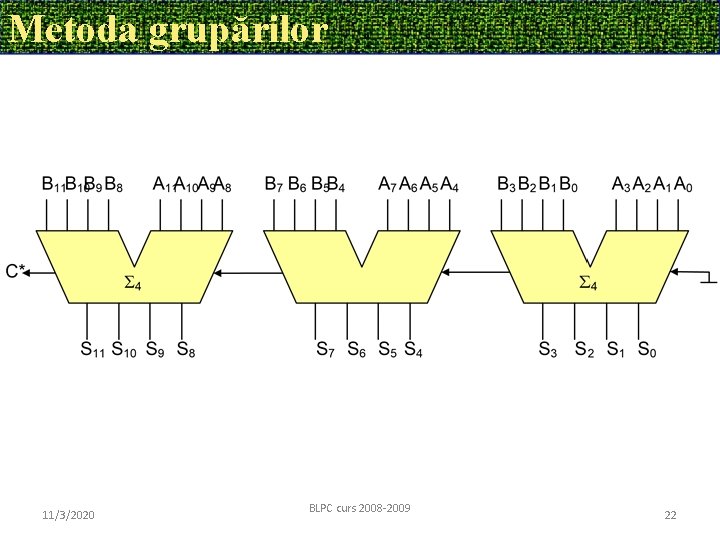

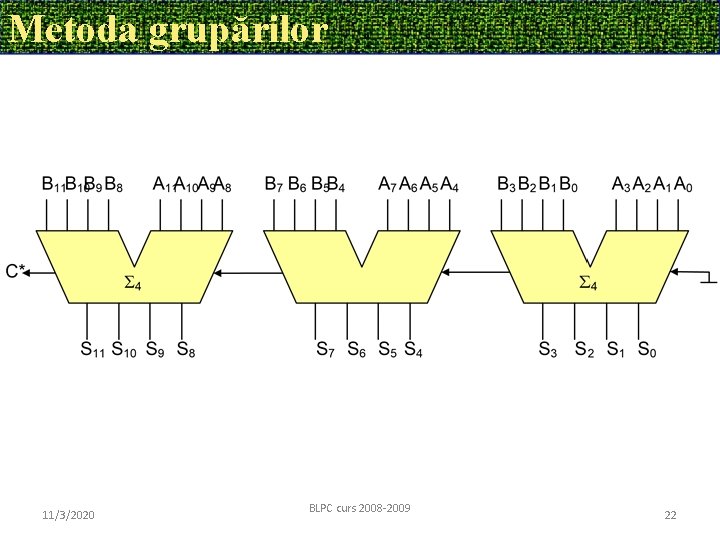

Metoda grupărilor 11/3/2020 BLPC curs 2008 -2009 22

Codificatoare de prioritate 11/3/2020 23

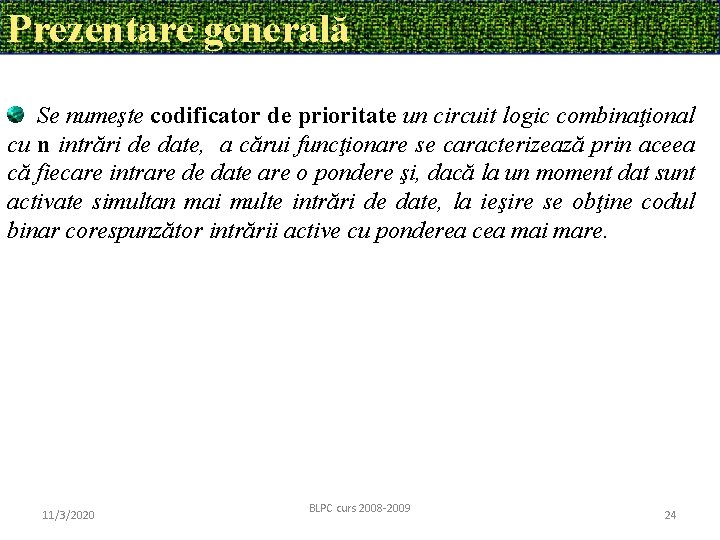

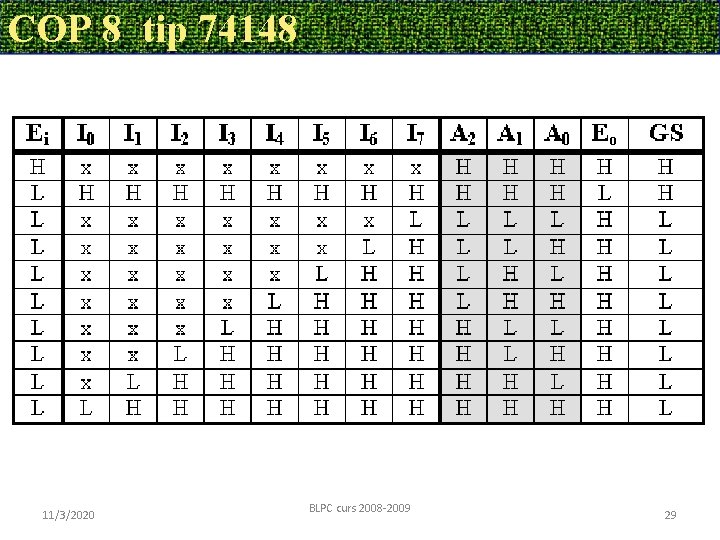

Prezentare generală Se numeşte codificator de prioritate un circuit logic combinaţional cu n intrări de date, a cărui funcţionare se caracterizează prin aceea că fiecare intrare de date are o pondere şi, dacă la un moment dat sunt activate simultan mai multe intrări de date, la ieşire se obţine codul binar corespunzător intrării active cu ponderea cea mai mare. 11/3/2020 BLPC curs 2008 -2009 24

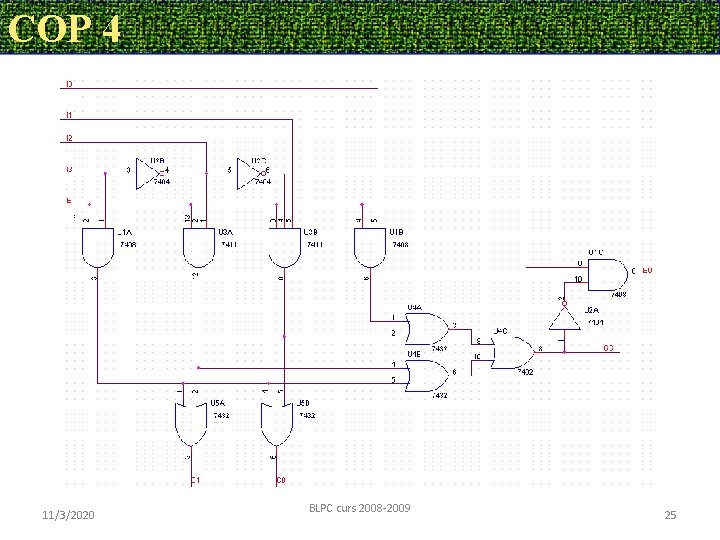

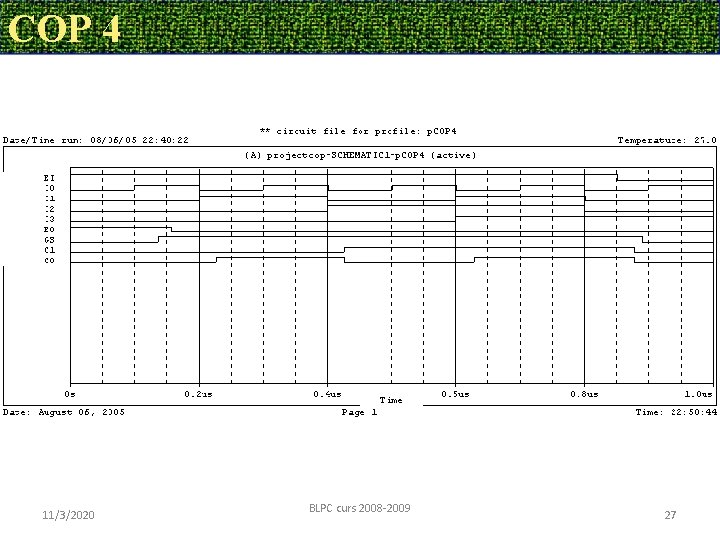

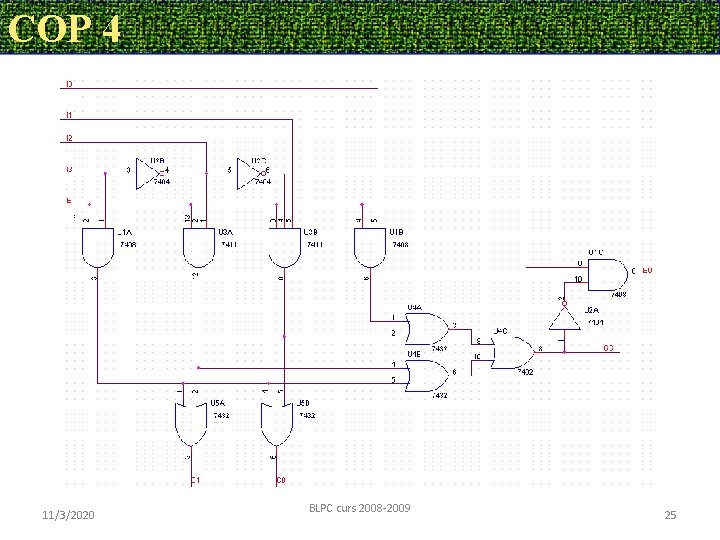

COP 4 11/3/2020 BLPC curs 2008 -2009 25

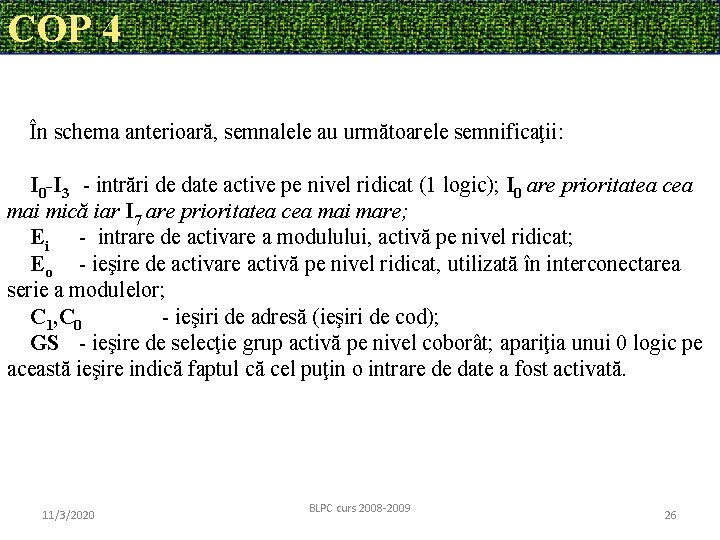

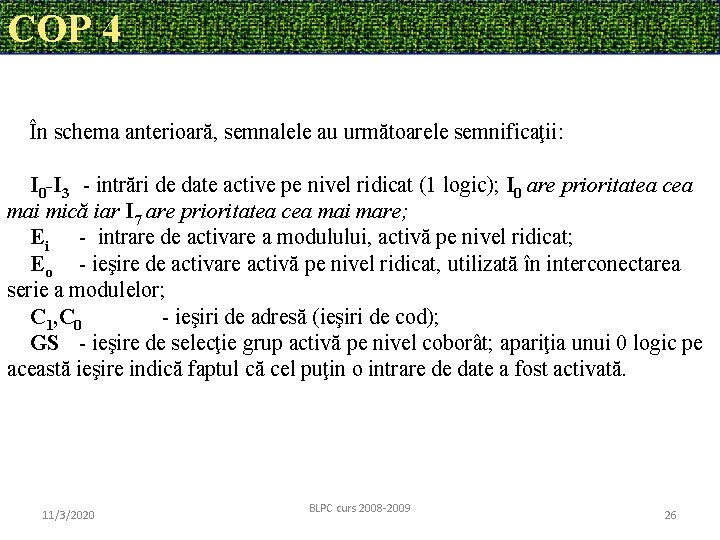

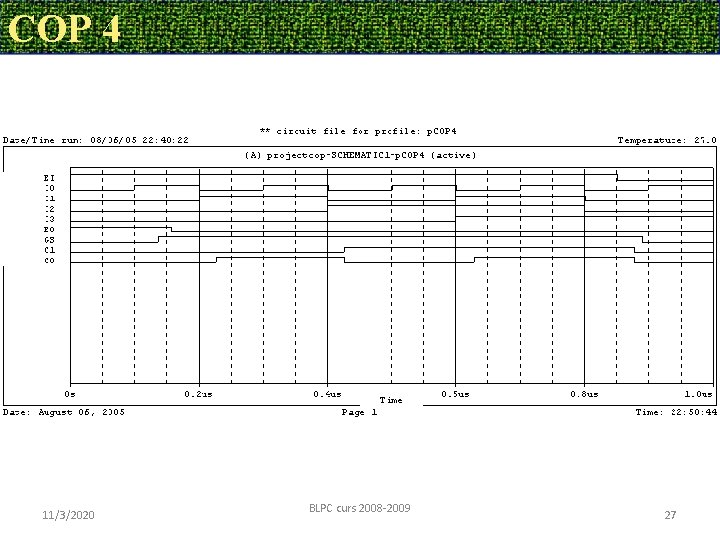

COP 4 În schema anterioară, semnalele au următoarele semnificaţii: I 0 -I 3 - intrări de date active pe nivel ridicat (1 logic); I 0 are prioritatea cea mai mică iar I 7 are prioritatea cea mai mare; Ei - intrare de activare a modulului, activă pe nivel ridicat; Eo - ieşire de activare activă pe nivel ridicat, utilizată în interconectarea serie a modulelor; C 1, C 0 - ieşiri de adresă (ieşiri de cod); GS - ieşire de selecţie grup activă pe nivel coborât; apariţia unui 0 logic pe această ieşire indică faptul că cel puţin o intrare de date a fost activată. 11/3/2020 BLPC curs 2008 -2009 26

COP 4 11/3/2020 BLPC curs 2008 -2009 27

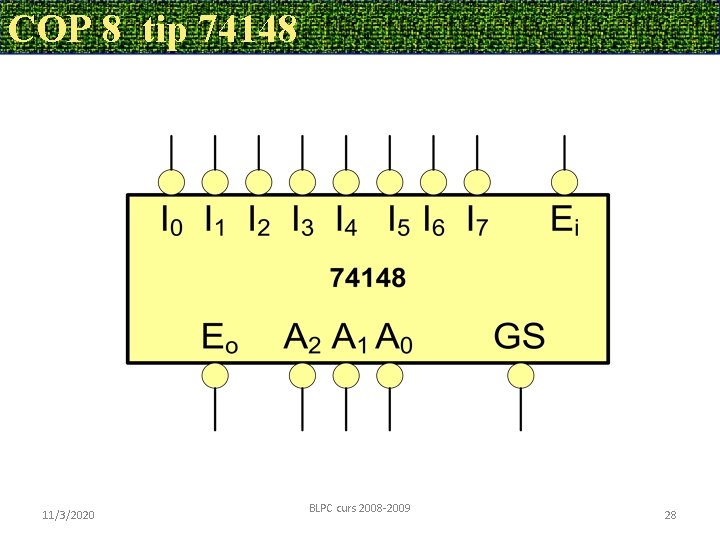

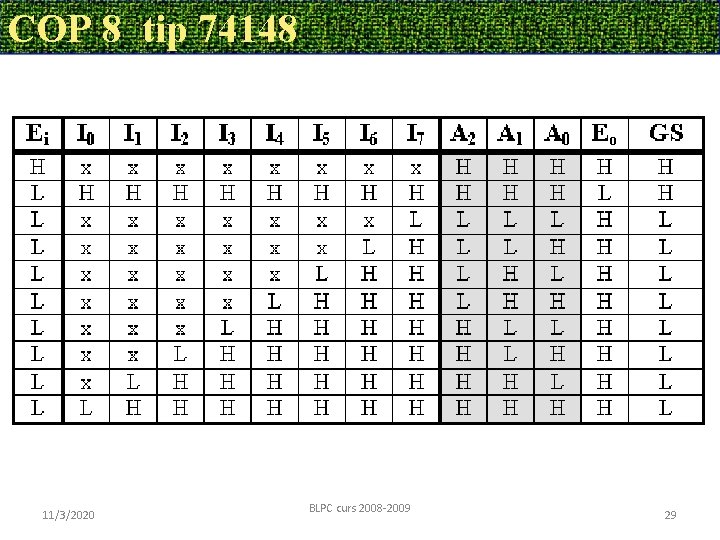

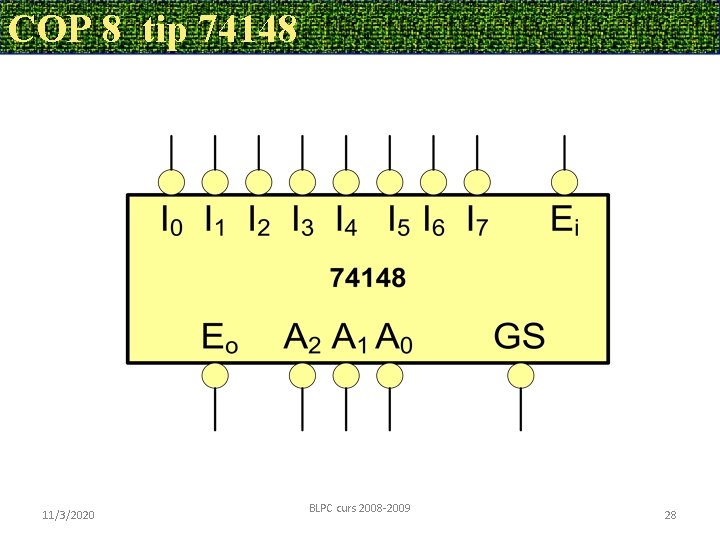

COP 8 tip 74148 11/3/2020 BLPC curs 2008 -2009 28

COP 8 tip 74148 11/3/2020 BLPC curs 2008 -2009 29

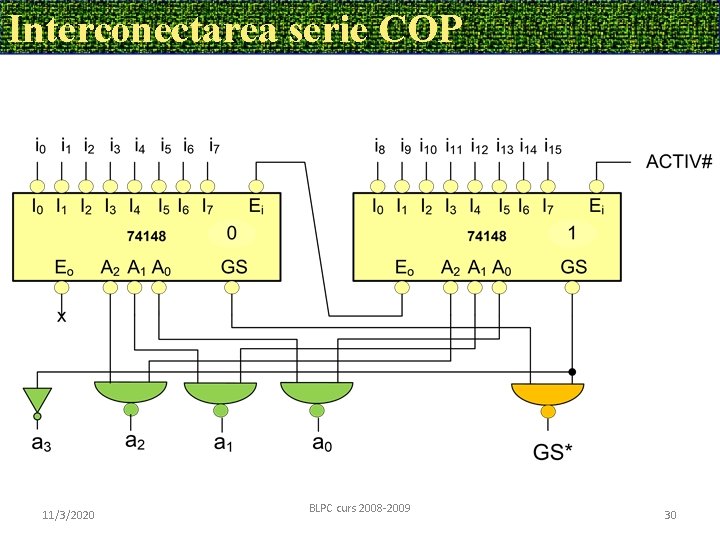

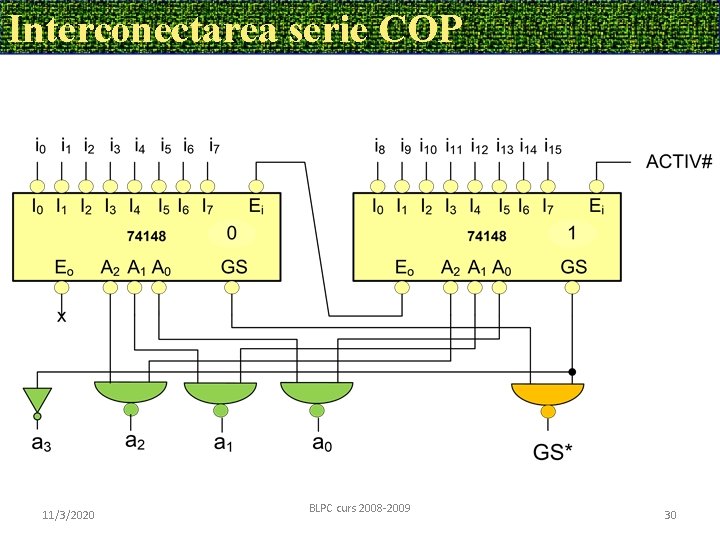

Interconectarea serie COP 11/3/2020 BLPC curs 2008 -2009 30

Comparatoare 11/3/2020 31

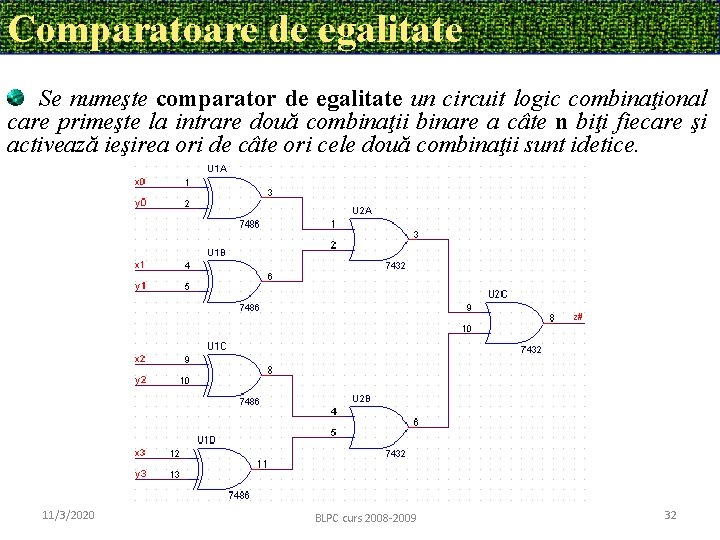

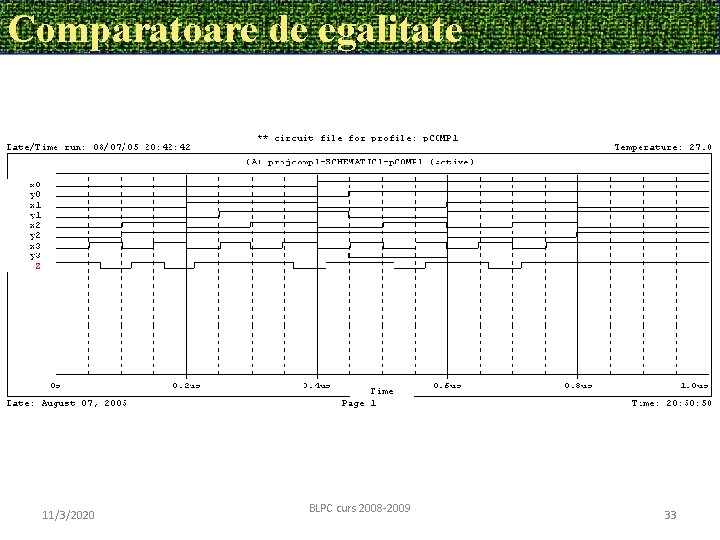

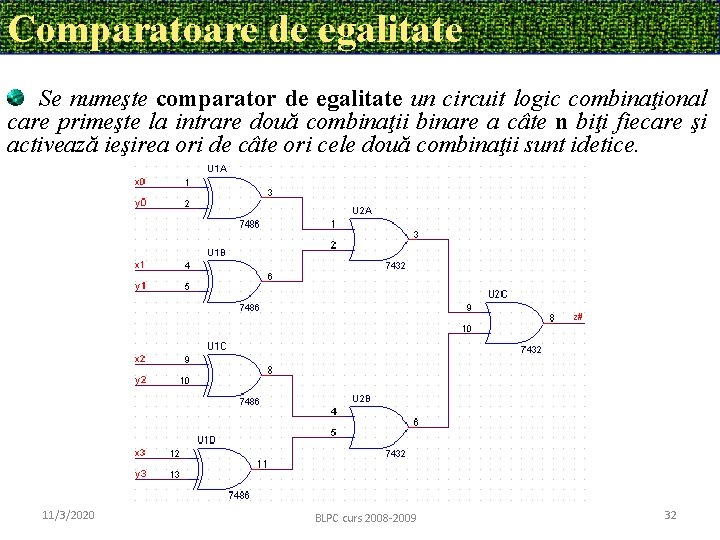

Comparatoare de egalitate Se numeşte comparator de egalitate un circuit logic combinaţional care primeşte la intrare două combinaţii binare a câte n biţi fiecare şi activează ieşirea ori de câte ori cele două combinaţii sunt idetice. 11/3/2020 BLPC curs 2008 -2009 32

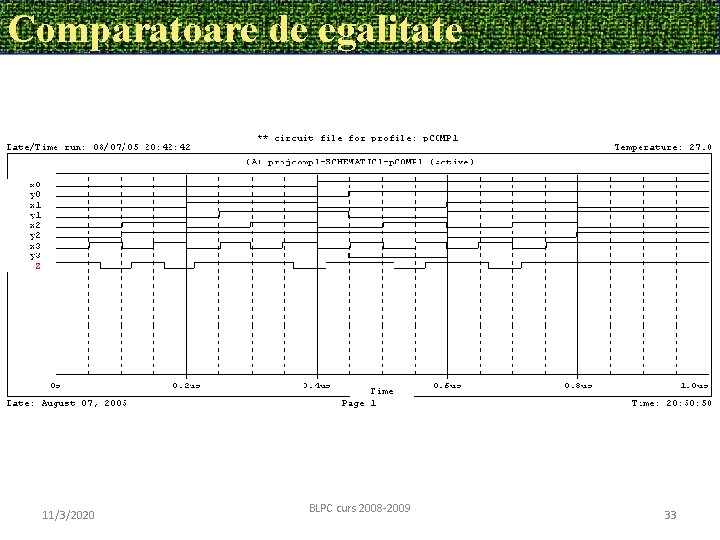

Comparatoare de egalitate 11/3/2020 BLPC curs 2008 -2009 33

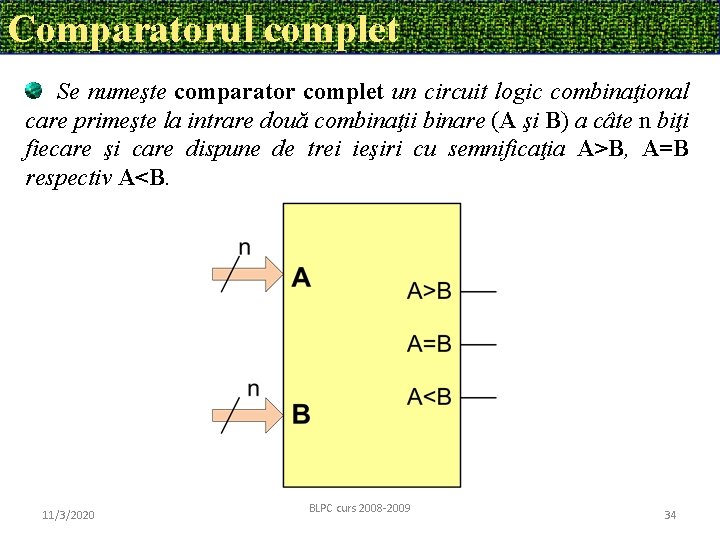

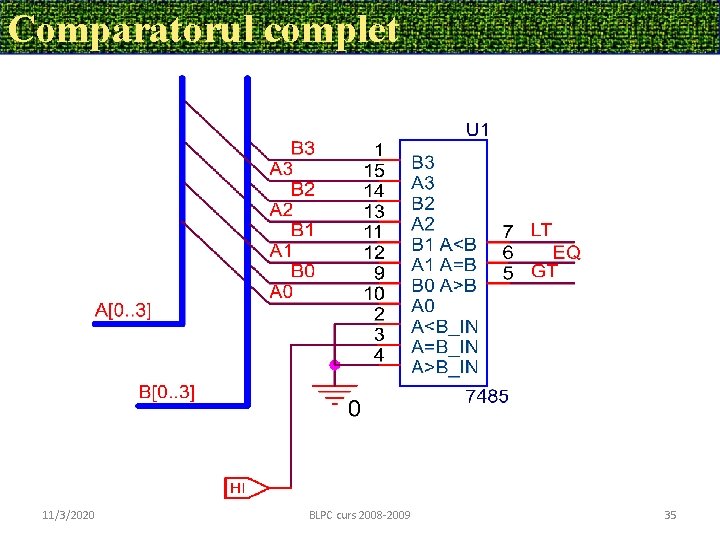

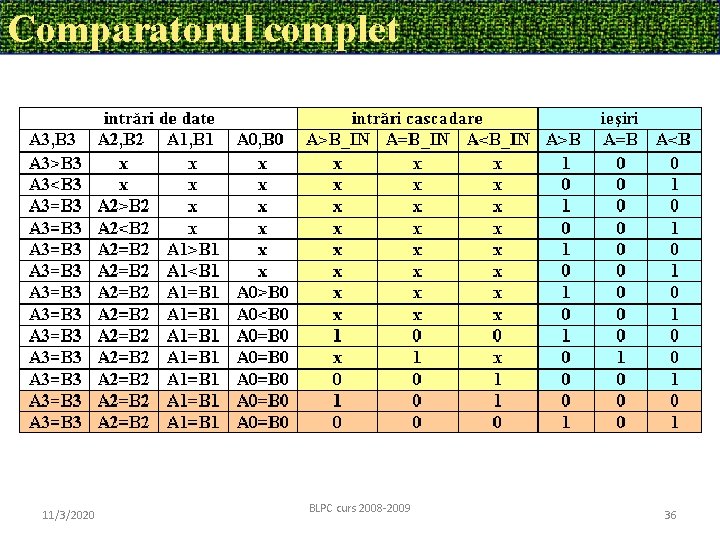

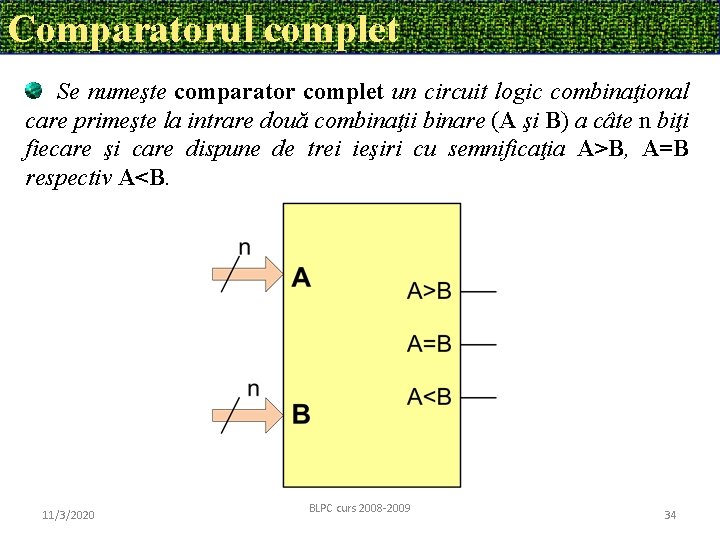

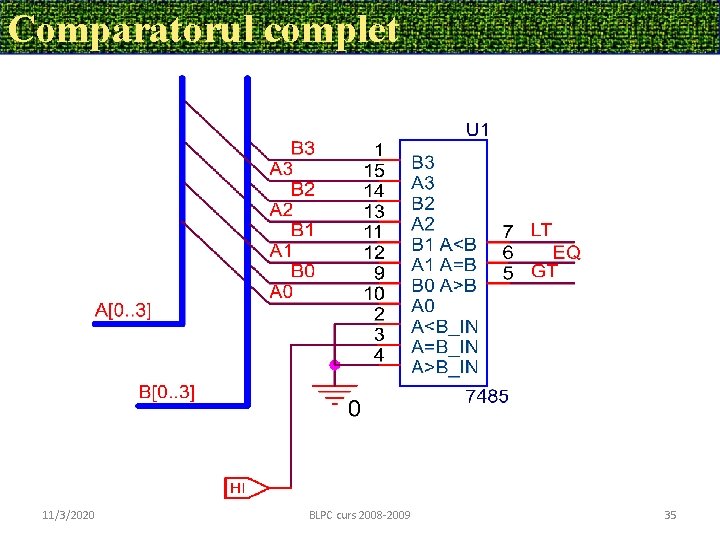

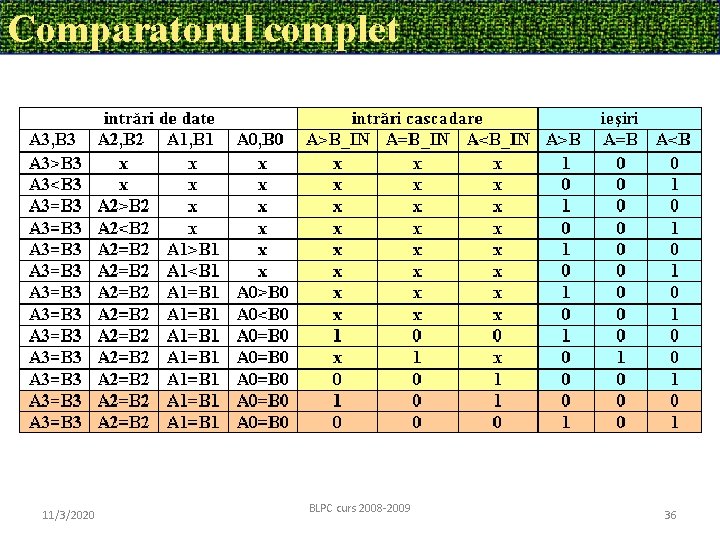

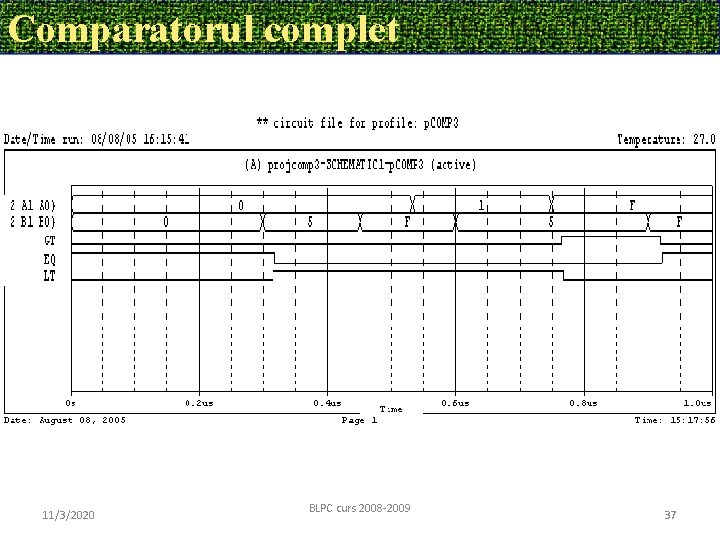

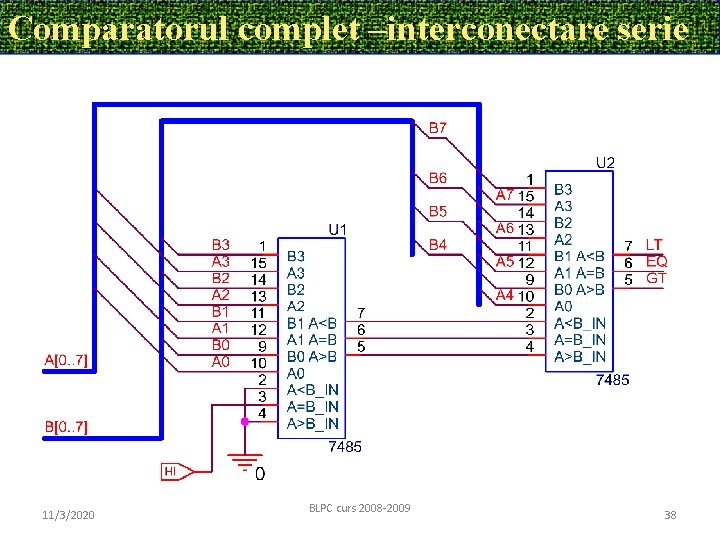

Comparatorul complet Se numeşte comparator complet un circuit logic combinaţional care primeşte la intrare două combinaţii binare (A şi B) a câte n biţi fiecare şi care dispune de trei ieşiri cu semnificaţia A>B, A=B respectiv A<B. 11/3/2020 BLPC curs 2008 -2009 34

Comparatorul complet 11/3/2020 BLPC curs 2008 -2009 35

Comparatorul complet 11/3/2020 BLPC curs 2008 -2009 36

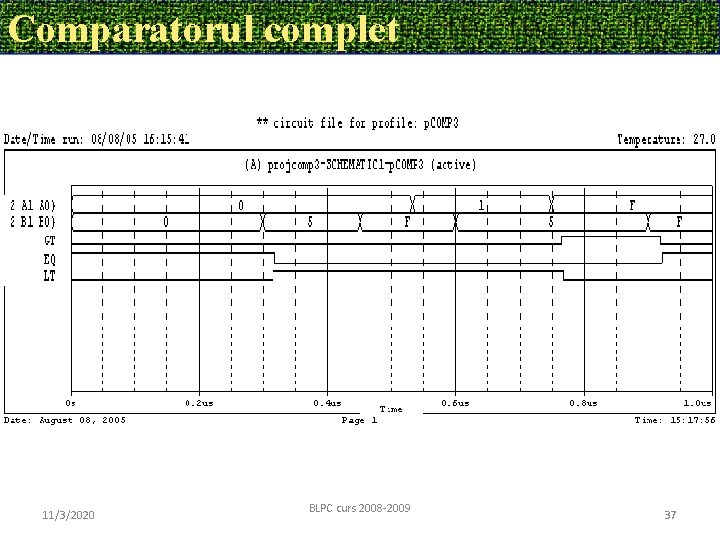

Comparatorul complet 11/3/2020 BLPC curs 2008 -2009 37

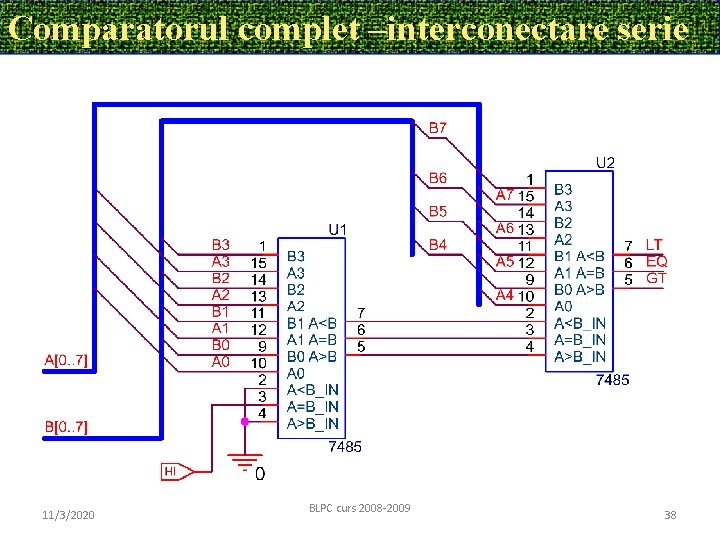

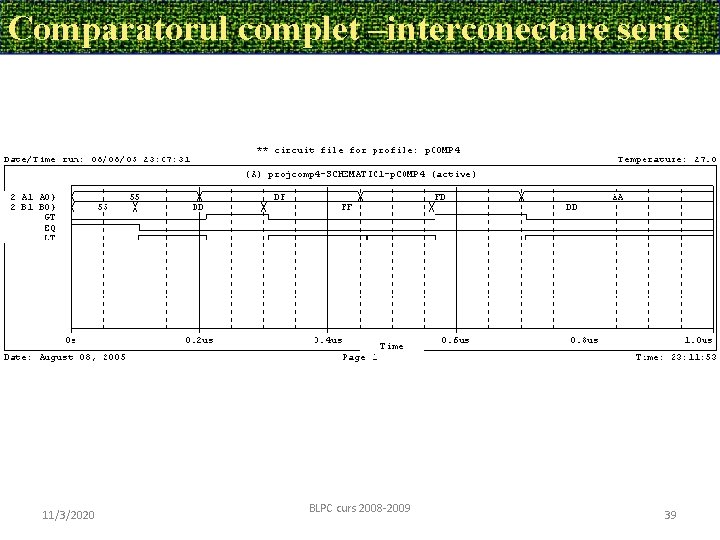

Comparatorul complet –interconectare serie 11/3/2020 BLPC curs 2008 -2009 38

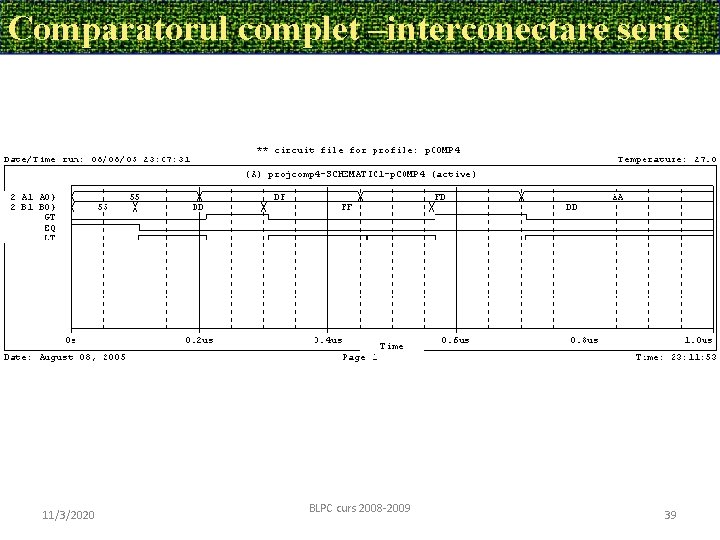

Comparatorul complet –interconectare serie 11/3/2020 BLPC curs 2008 -2009 39

Generatoare de bit de paritate 11/3/2020 BLPC curs 2007 -2008 40

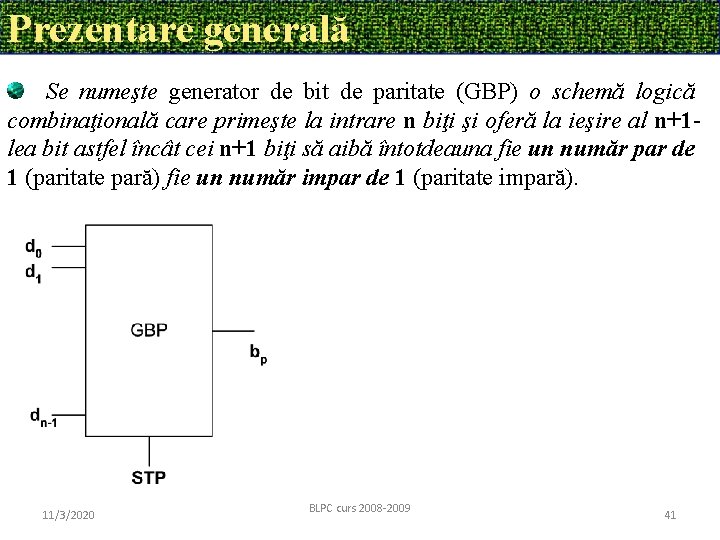

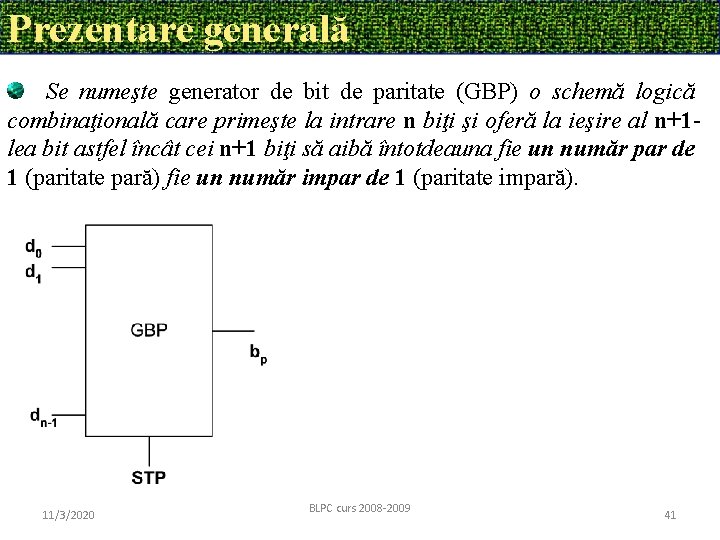

Prezentare generală Se numeşte generator de bit de paritate (GBP) o schemă logică combinaţională care primeşte la intrare n biţi şi oferă la ieşire al n+1 lea bit astfel încât cei n+1 biţi să aibă întotdeauna fie un număr par de 1 (paritate pară) fie un număr impar de 1 (paritate impară). 11/3/2020 BLPC curs 2008 -2009 41

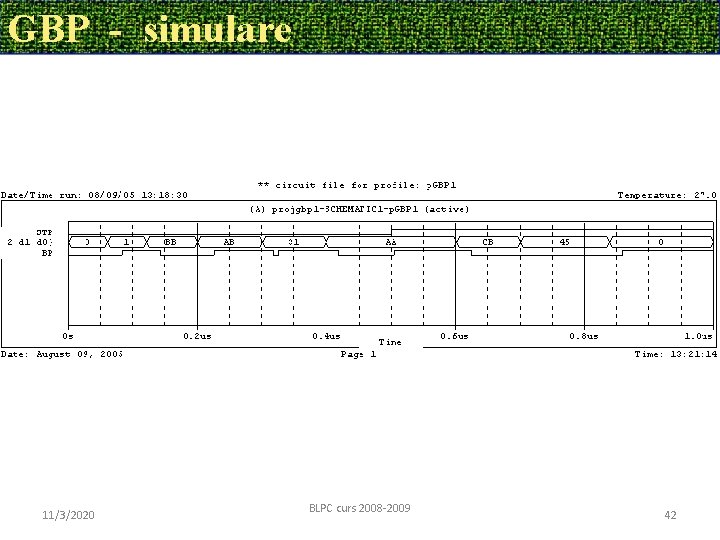

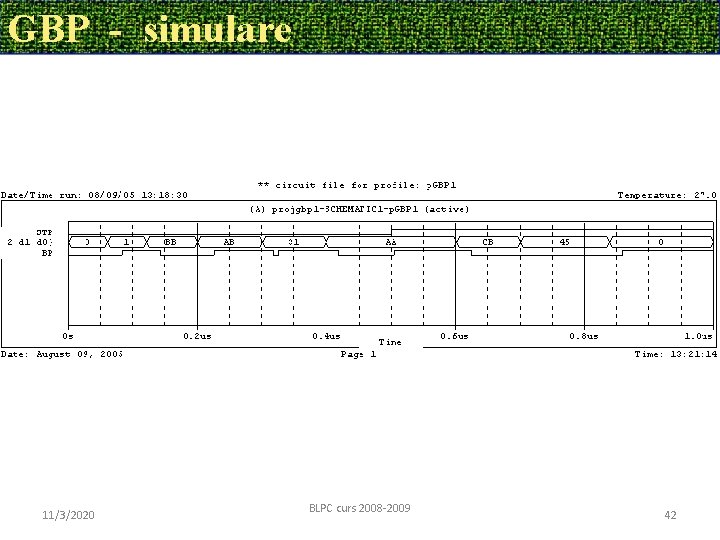

GBP - simulare 11/3/2020 BLPC curs 2008 -2009 42

Întrebări ? 11/3/2020 BLPC curs 2008 -2009 43