The ICARUS readout system 4 3 D Imaging

- Slides: 24

The ICARUS read-out system 4 3 D Imaging in the ICARUS LAr-TPC 4 Layout, optimization and performance of front -end electronics (analogue + digital) 4 Self-triggering and zero-suppression 4 DAQ software, on-line display and monitoring

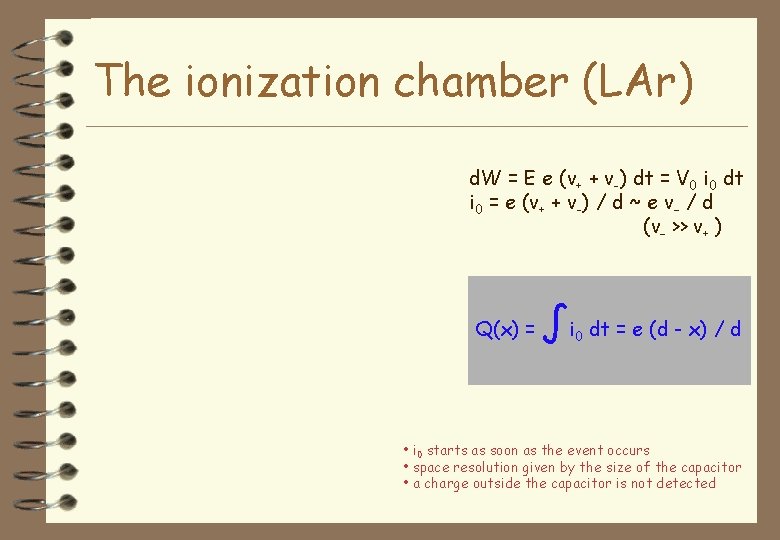

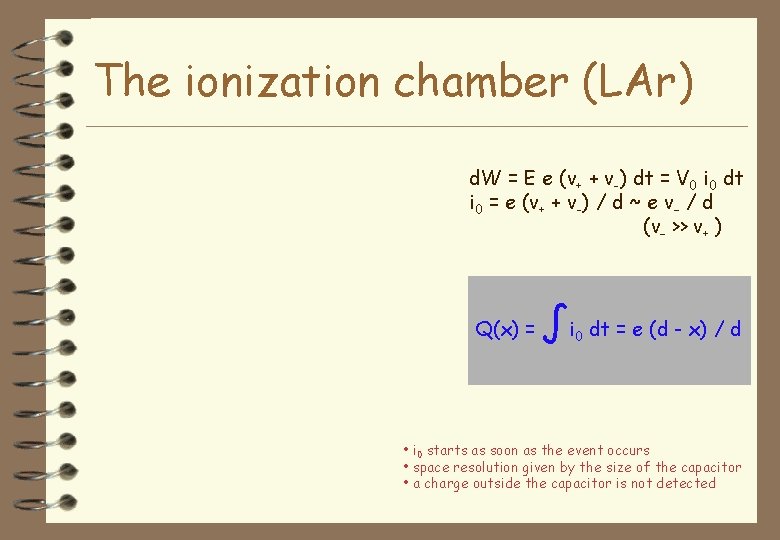

The ionization chamber (LAr) d. W = E e (v+ + v-) dt = V 0 i 0 dt i 0 = e (v+ + v-) / d ~ e v– / d (v– >> v+ ) Q(x) = ∫i 0 dt = e (d - x) / d • i 0 starts as soon as the event occurs • space resolution given by the size of the capacitor • a charge outside the capacitor is not detected

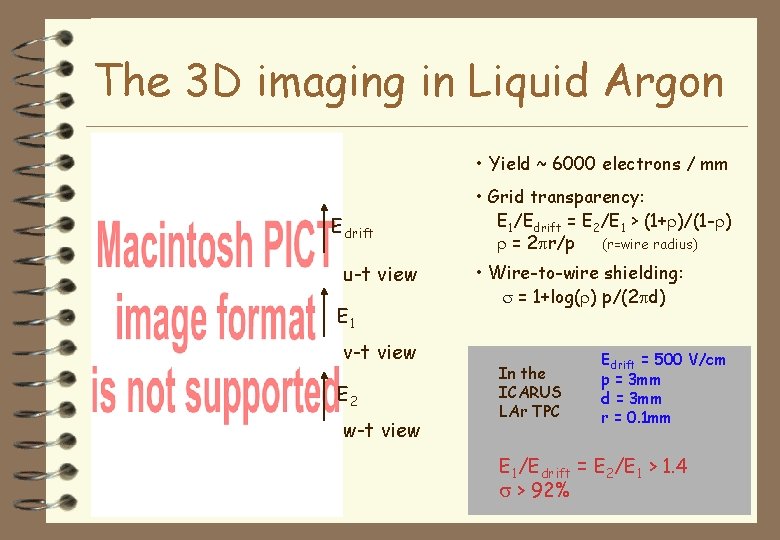

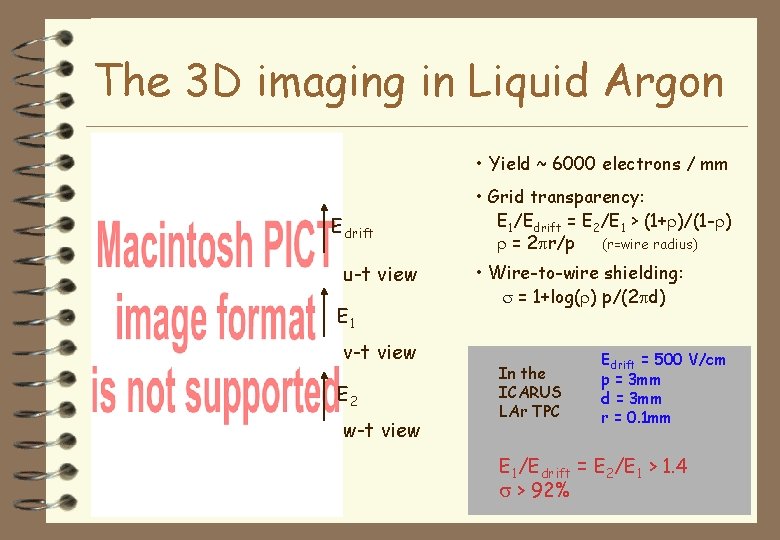

The 3 D imaging in Liquid Argon • Yield ~ 6000 electrons / mm Edrift u-t view E 1 v-t view E 2 w-t view • Grid transparency: E 1/Edrift = E 2/E 1 > (1+r)/(1 -r) r = 2 pr/p (r=wire radius) • Wire-to-wire shielding: s = 1+log(r) p/(2 pd) In the ICARUS LAr TPC Edrift = 500 V/cm p = 3 mm d = 3 mm r = 0. 1 mm E 1/Edrift = E 2/E 1 > 1. 4 s > 92%

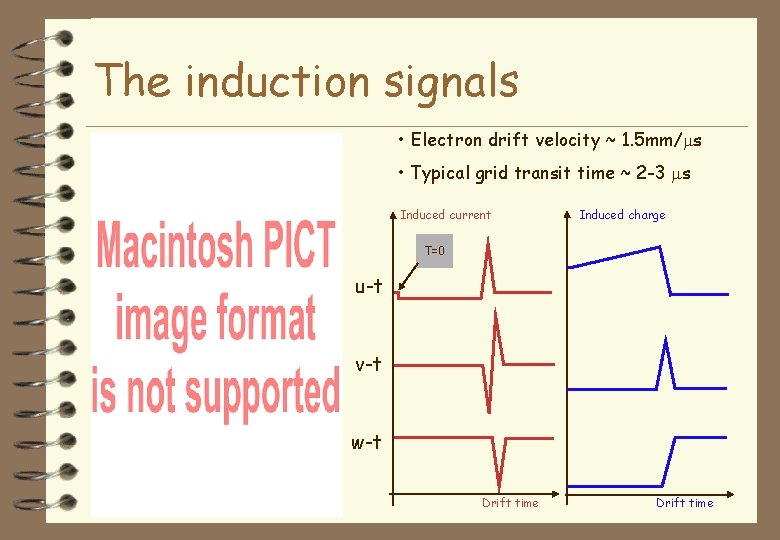

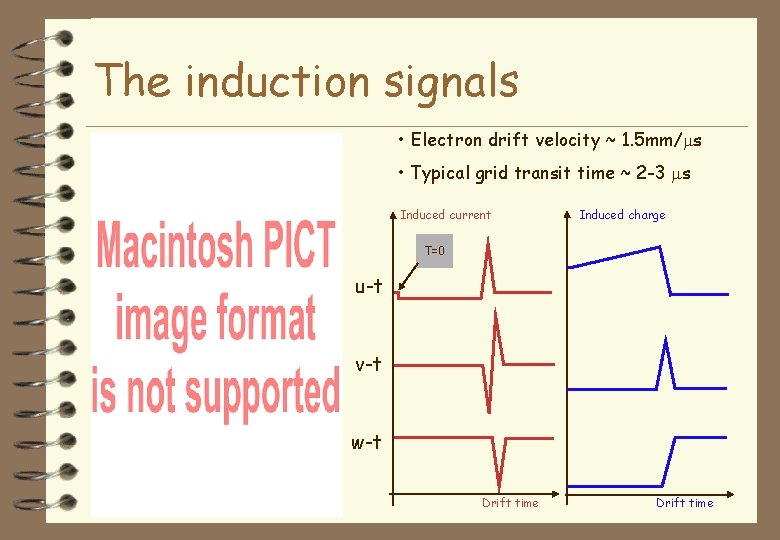

The induction signals • Electron drift velocity ~ 1. 5 mm/ms • Typical grid transit time ~ 2 -3 ms Induced current Induced charge T=0 u-t v-t w-t Drift time

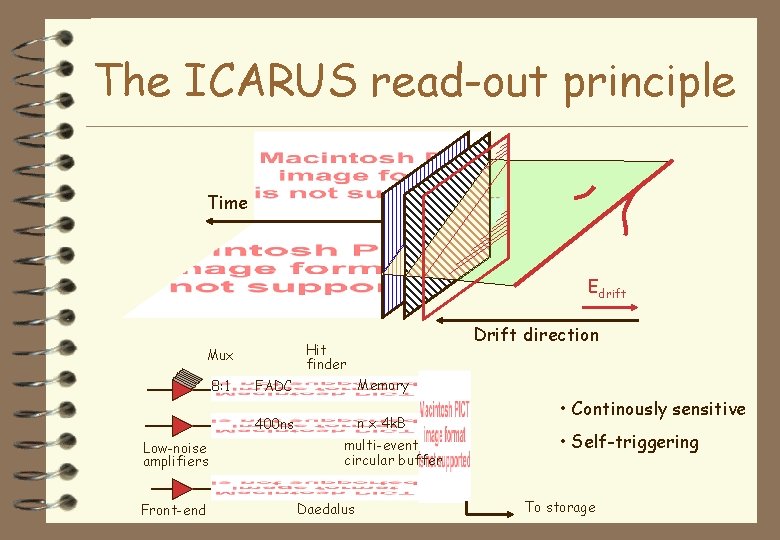

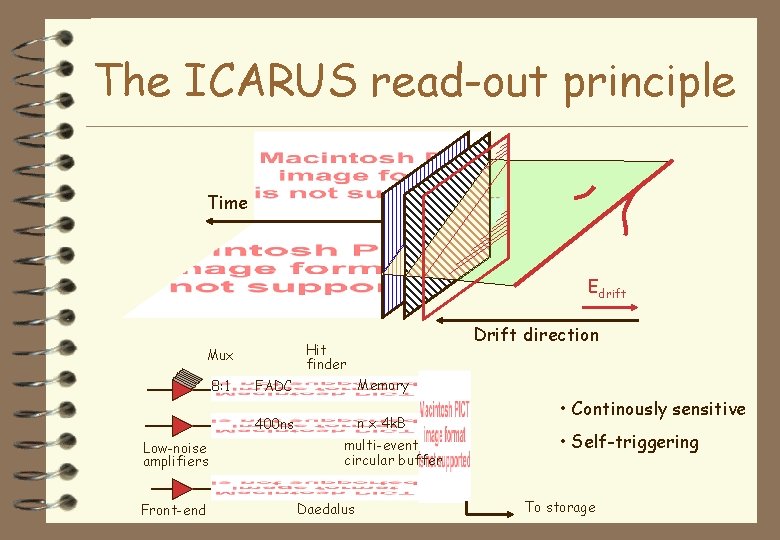

The ICARUS read-out principle Time Edrift Mux 8: 1 Low-noise amplifiers Front-end Drift direction Hit finder FADC Memory 400 ns n x 4 k. B multi-event circular buffer Daedalus • Continously sensitive • Self-triggering To storage

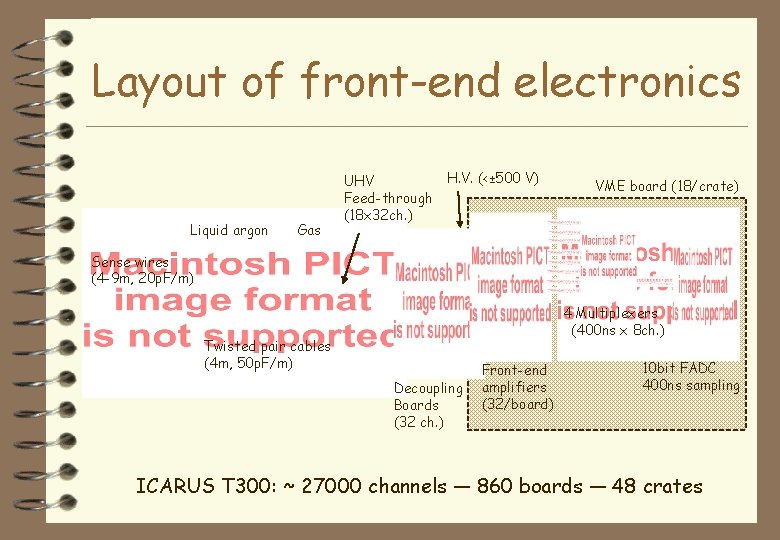

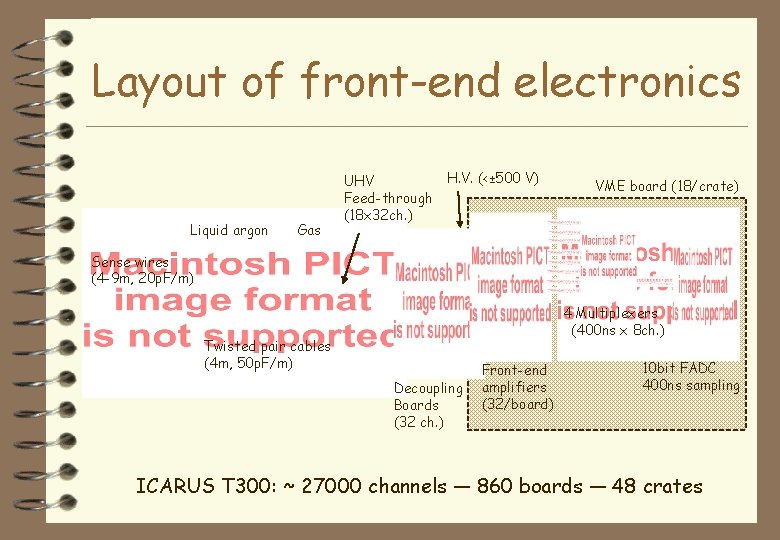

Layout of front-end electronics Liquid argon Gas UHV Feed-through (18 x 32 ch. ) H. V. (<± 500 V) VME board (18/crate) Sense wires (4 -9 m, 20 p. F/m) 4 Multiplexers (400 ns x 8 ch. ) Twisted pair cables (4 m, 50 p. F/m) Decoupling Boards (32 ch. ) Front-end amplifiers (32/board) 10 bit FADC 400 ns sampling ICARUS T 300: ~ 27000 channels — 860 boards — 48 crates

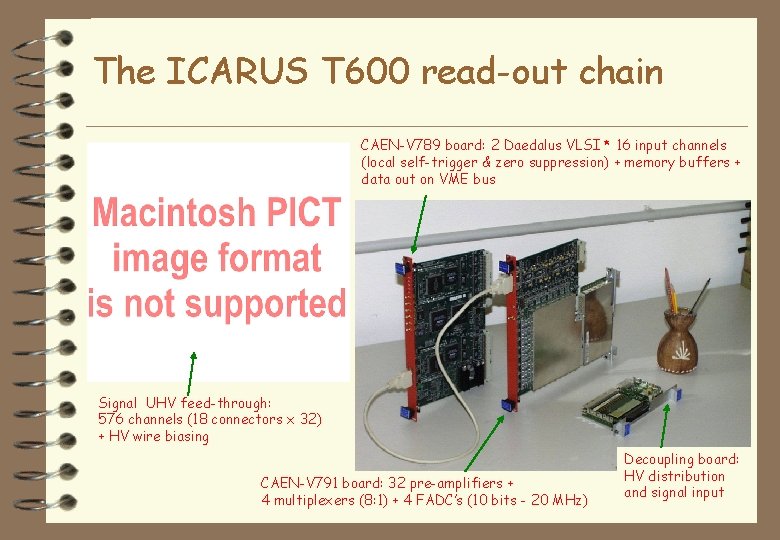

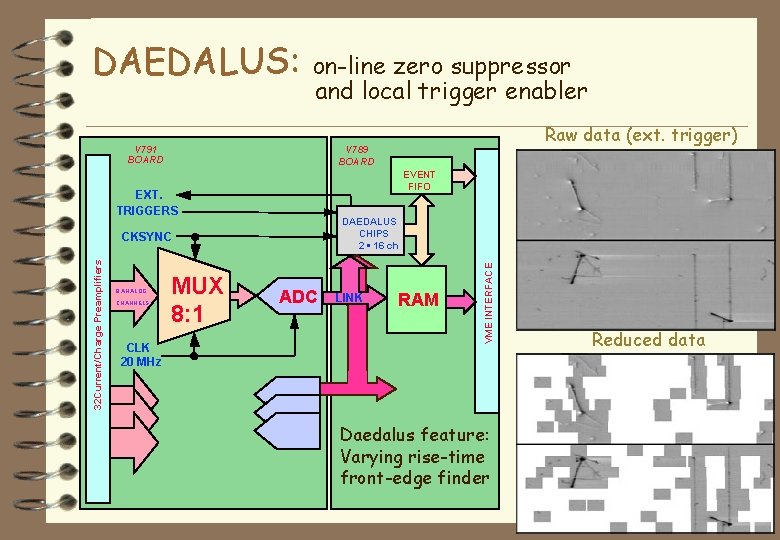

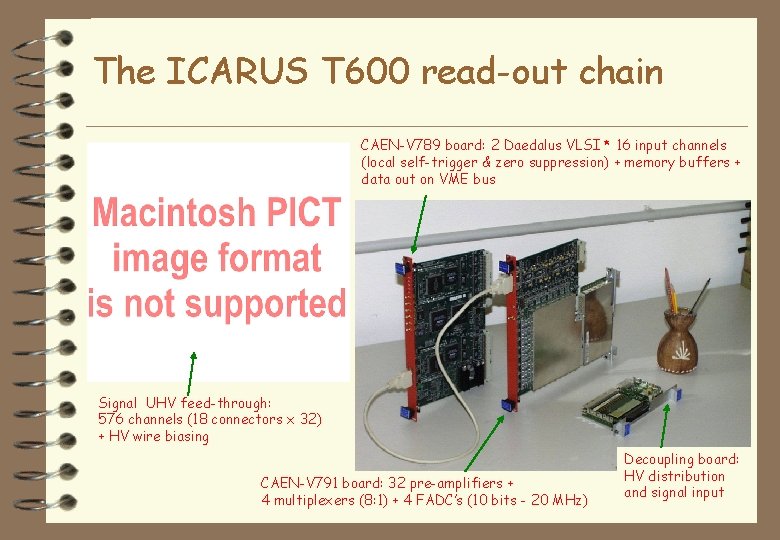

The ICARUS T 600 read-out chain CAEN-V 789 board: 2 Daedalus VLSI * 16 input channels (local self-trigger & zero suppression) + memory buffers + data out on VME bus Signal UHV feed-through: 576 channels (18 connectors x 32) + HV wire biasing CAEN-V 791 board: 32 pre-amplifiers + 4 multiplexers (8: 1) + 4 FADC’s (10 bits - 20 MHz) Decoupling board: HV distribution and signal input

The T 600 electronic racks

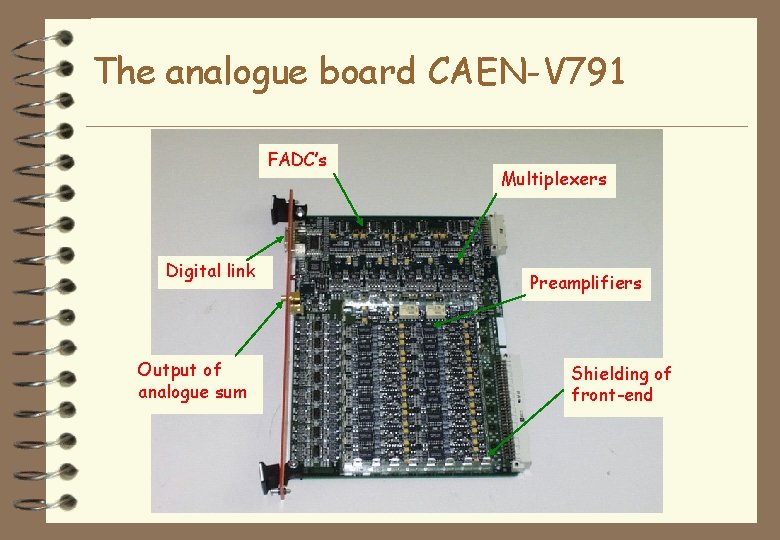

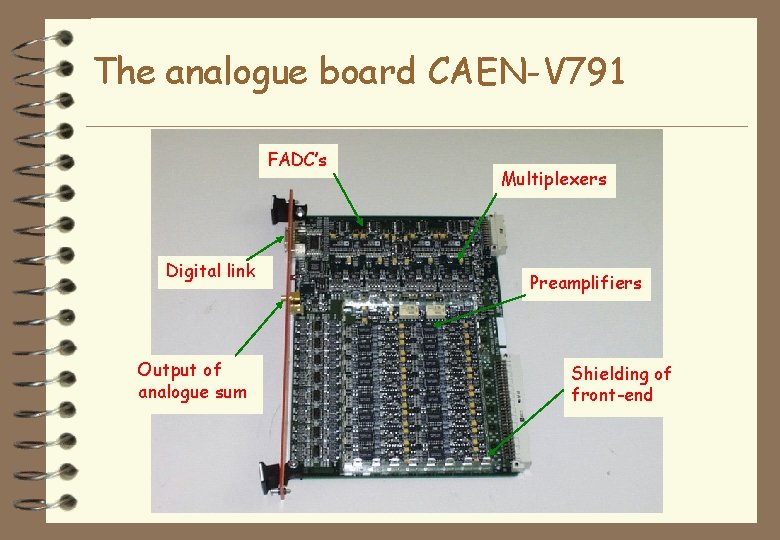

The analogue board CAEN-V 791 FADC’s Digital link Output of analogue sum Multiplexers Preamplifiers Shielding of front-end

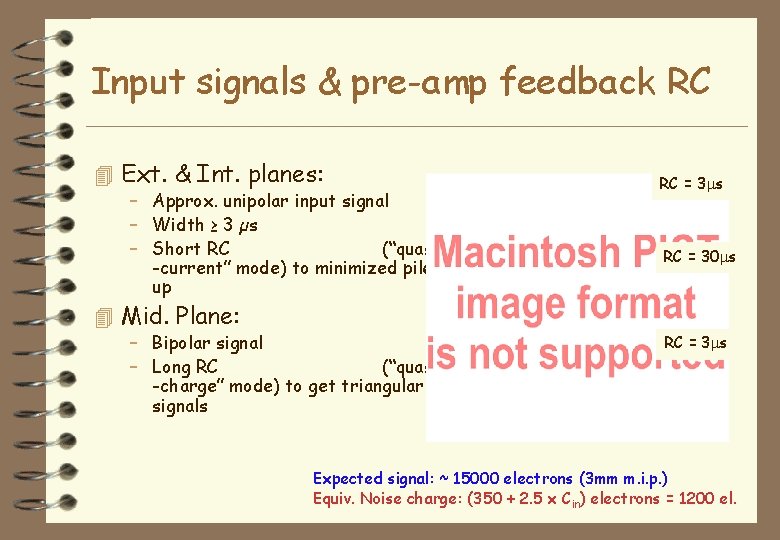

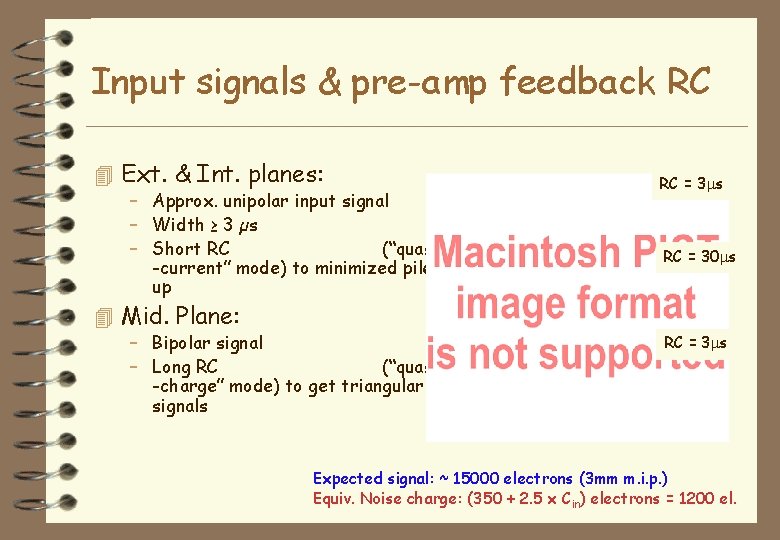

Input signals & pre-amp feedback RC 4 Ext. & Int. planes: – Approx. unipolar input signal – Width ≥ 3 µs – Short RC (“quasi -current” mode) to minimized pileup 4 Mid. Plane: – Bipolar signal – Long RC (“quasi -charge” mode) to get triangular signals RC = 3 ms RC = 30 ms RC = 3 ms Expected signal: ~ 15000 electrons (3 mm m. i. p. ) Equiv. Noise charge: (350 + 2. 5 x Cin) electrons = 1200 el.

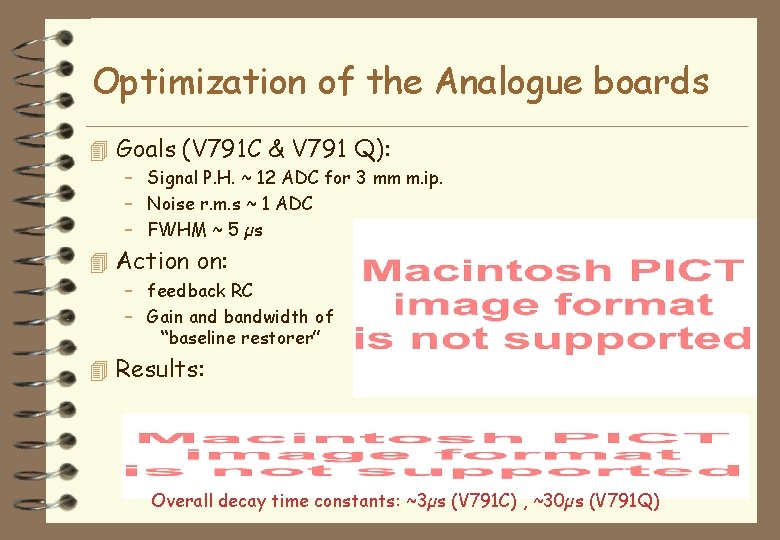

Optimization of the Analogue boards 4 Goals (V 791 C & V 791 Q): – Signal P. H. ~ 12 ADC for 3 mm m. ip. – Noise r. m. s ~ 1 ADC – FWHM ~ 5 µs 4 Action on: – feedback RC – Gain and bandwidth of “baseline restorer” 4 Results: Overall decay time constants: ~3µs (V 791 C) , ~30µs (V 791 Q)

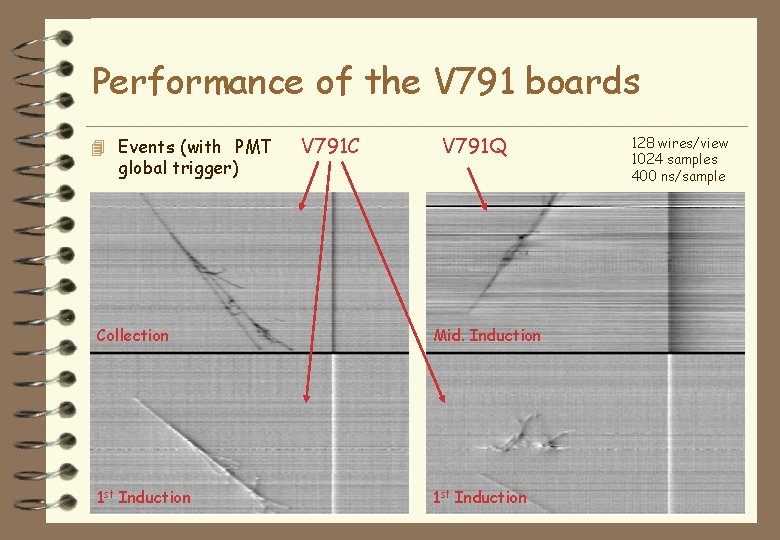

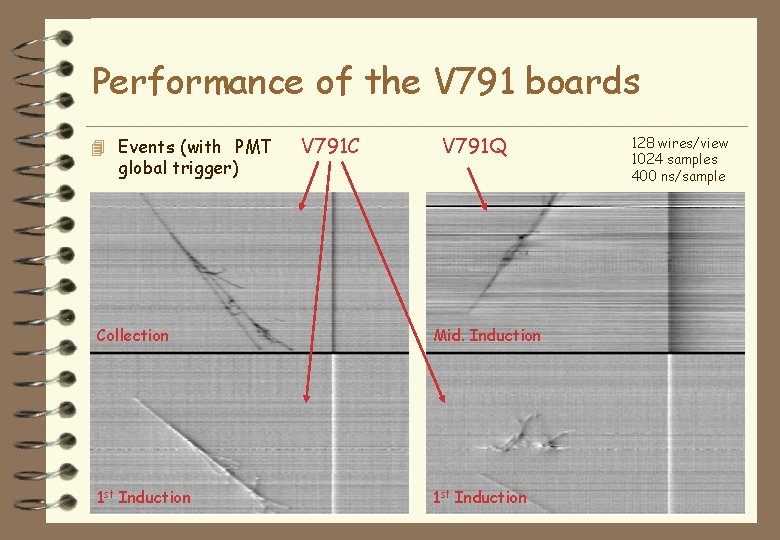

Performance of the V 791 boards 4 Events (with PMT global trigger) V 791 C V 791 Q Collection Mid. Induction 1 st Induction 128 wires/view 1024 samples 400 ns/sample

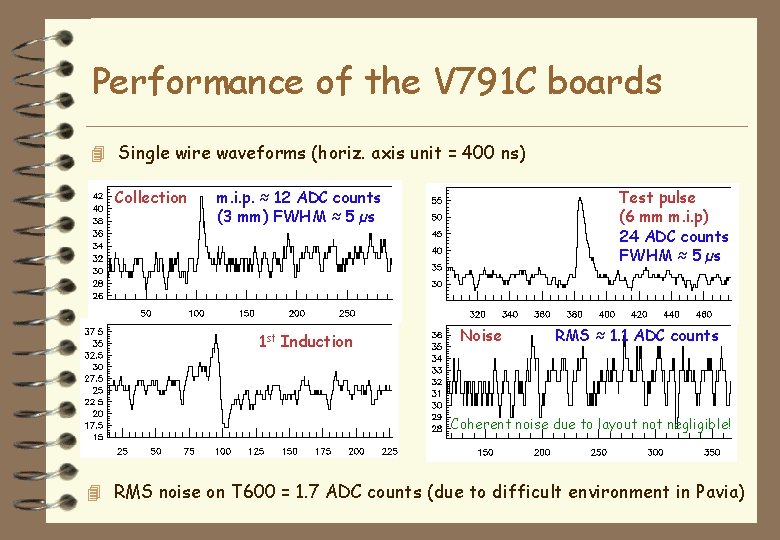

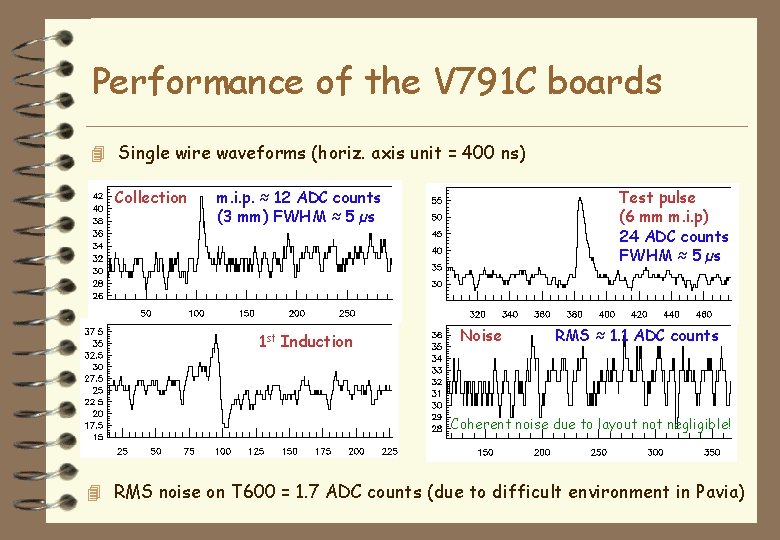

Performance of the V 791 C boards 4 Single wire waveforms (horiz. axis unit = 400 ns) Collection m. i. p. ≈ 12 ADC counts (3 mm) FWHM ≈ 5 µs 1 st Induction Test pulse (6 mm m. i. p) 24 ADC counts FWHM ≈ 5 µs Noise RMS ≈ 1. 1 ADC counts Coherent noise due to layout not negligible! 4 RMS noise on T 600 = 1. 7 ADC counts (due to difficult environment in Pavia)

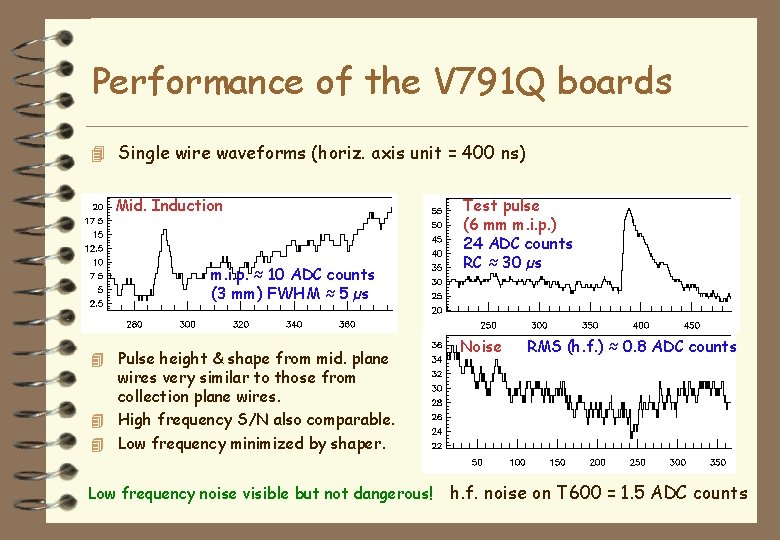

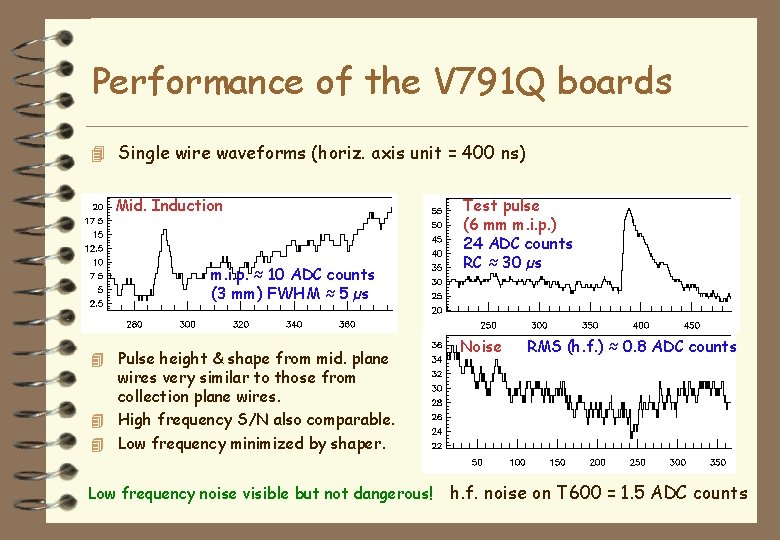

Performance of the V 791 Q boards 4 Single wire waveforms (horiz. axis unit = 400 ns) Mid. Induction m. i. p. ≈ 10 ADC counts (3 mm) FWHM ≈ 5 µs 4 Pulse height & shape from mid. plane Test pulse (6 mm m. i. p. ) 24 ADC counts RC ≈ 30 µs Noise RMS (h. f. ) ≈ 0. 8 ADC counts wires very similar to those from collection plane wires. 4 High frequency S/N also comparable. 4 Low frequency minimized by shaper. Low frequency noise visible but not dangerous! h. f. noise on T 600 = 1. 5 ADC counts

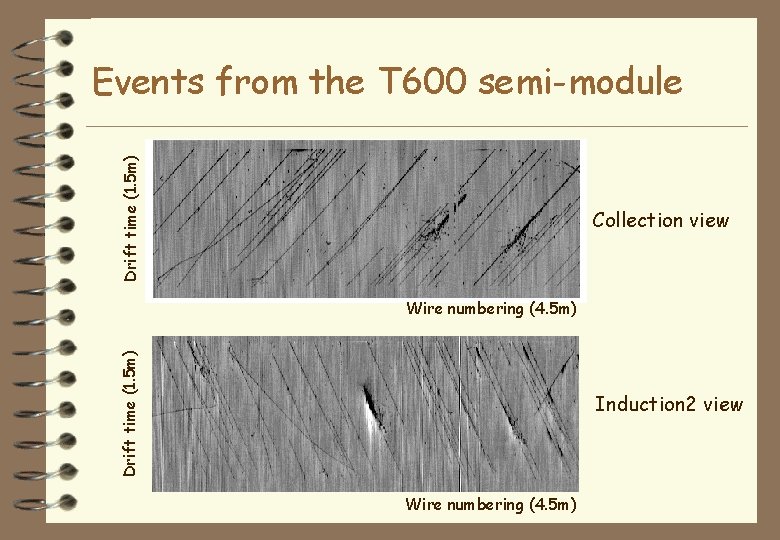

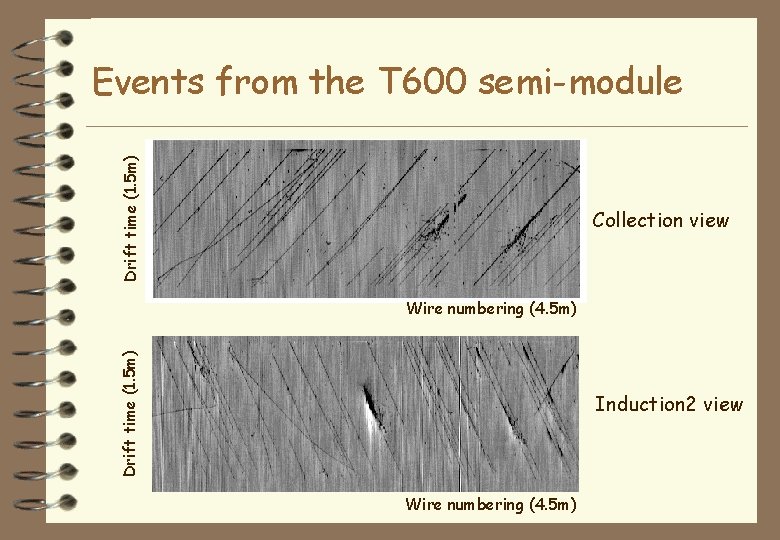

Drift time (1. 5 m) Events from the T 600 semi-module Collection view Drift time (1. 5 m) Wire numbering (4. 5 m) Induction 2 view Wire numbering (4. 5 m)

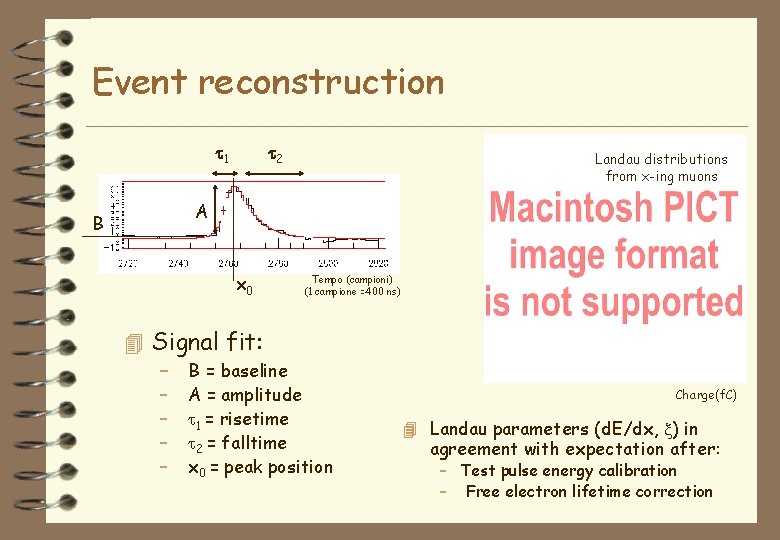

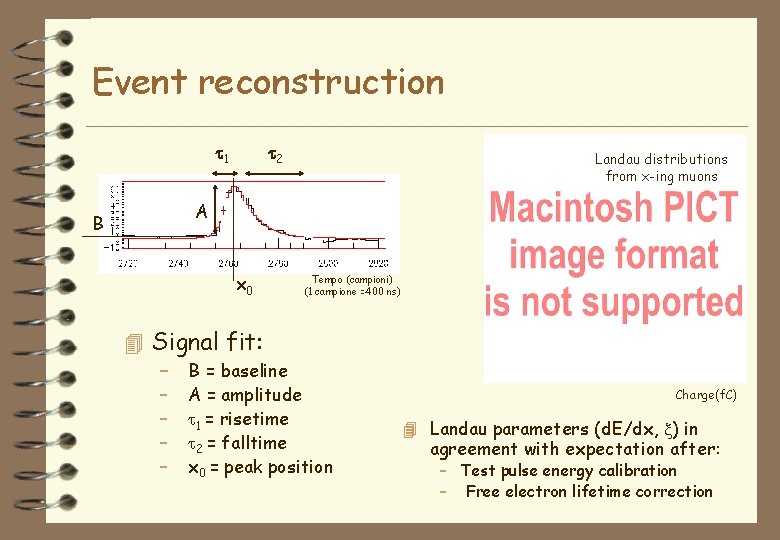

Event reconstruction 1 2 Landau distributions from x-ing muons A B x 0 Tempo (campioni) (1 campione =400 ns) 4 Signal fit: – B = baseline – – A = amplitude t 1 = risetime t 2 = falltime x 0 = peak position Charge(f. C) 4 Landau parameters (d. E/dx, x) in agreement with expectation after: – Test pulse energy calibration – Free electron lifetime correction

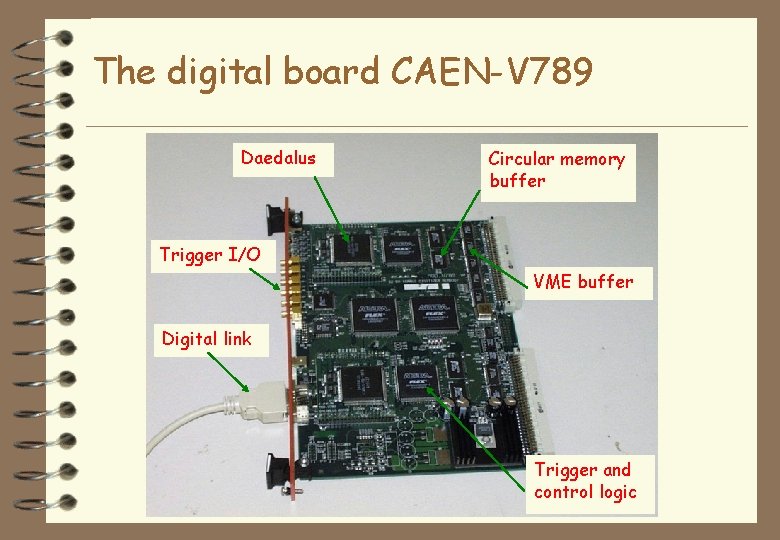

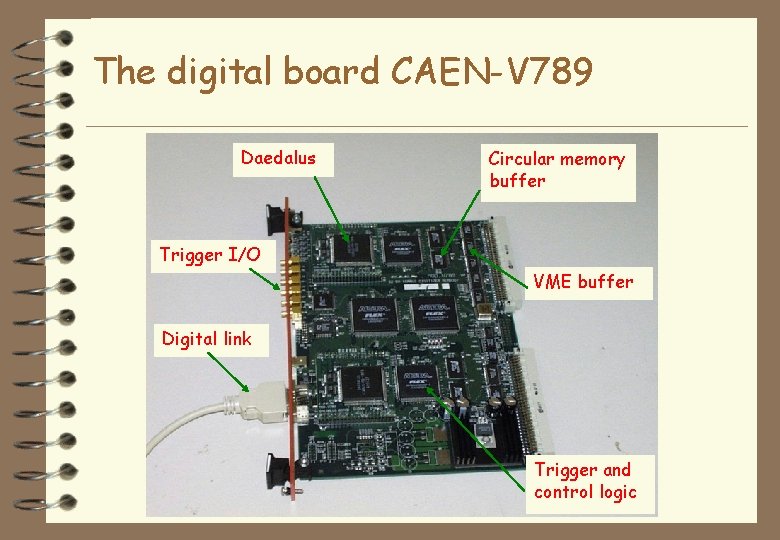

The digital board CAEN-V 789 Daedalus Circular memory buffer Trigger I/O VME buffer Digital link Trigger and control logic

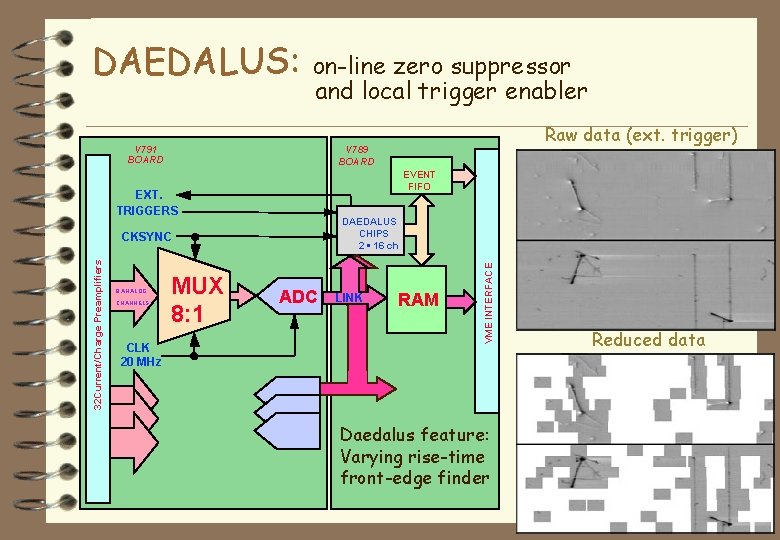

DAEDALUS: on-line zero suppressor and local trigger enabler V 791 BOARD EVENT FIFO EXT. TRIGGERS 32 Current/Charge Preamplifiers CHANNELS CLK 20 MHz MUX 8: 1 ADC LINK RAM VME INTERFACE DAEDALUS CHIPS 2 • 16 ch CKSYNC 8 ANALOG Raw data (ext. trigger) V 789 BOARD Daedalus feature: Varying rise-time front-edge finder Reduced data

Zero-Suppression Algorithm Hitfinder + Tile. Building Daedalus: detects signal Rising-Edge, Falling-Edge, Width… and generates a hitfound signal Trigger. Logic: handles a 16 channels group and builds a data tile around the hit Present Performance on T 300 Raw. Data: Efficiency= 97% Collection 90% Induction 1 & 2 False Detections= 20% Studies underway for improvement of algorithm (promising…)

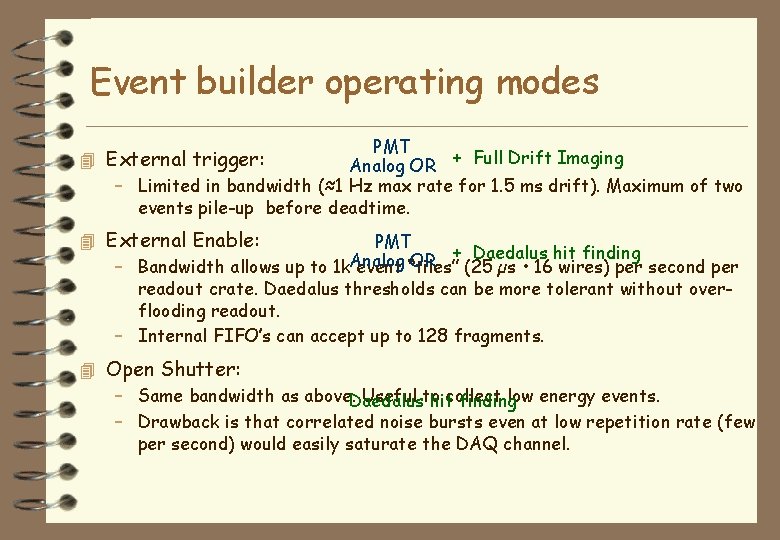

Event builder operating modes PMT 4 External trigger: Analog OR + Full Drift Imaging – Limited in bandwidth (≈1 Hz max rate for 1. 5 ms drift). Maximum of two events pile-up before deadtime. 4 External Enable: PMT + Daedalus hit finding Analog OR – Bandwidth allows up to 1 k event “tiles” (25 µs • 16 wires) per second per readout crate. Daedalus thresholds can be more tolerant without overflooding readout. – Internal FIFO’s can accept up to 128 fragments. 4 Open Shutter: – Same bandwidth as above. Daedalus Useful to low energy events. hitcollect finding – Drawback is that correlated noise bursts even at low repetition rate (few per second) would easily saturate the DAQ channel.

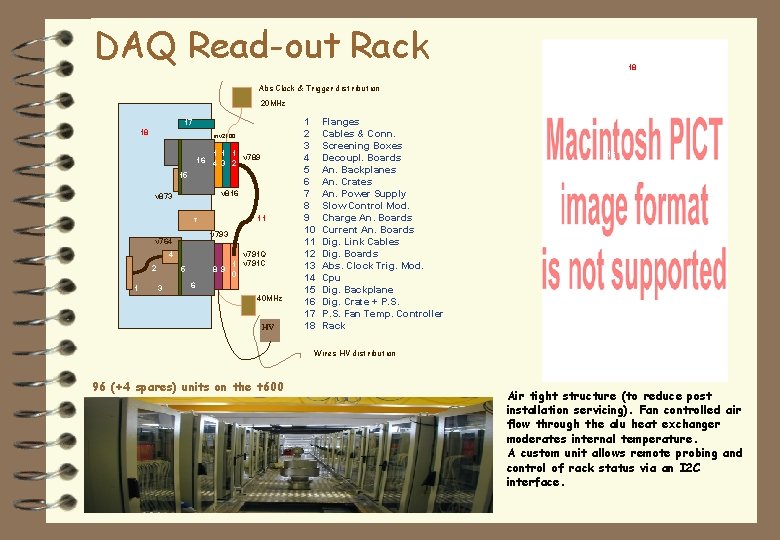

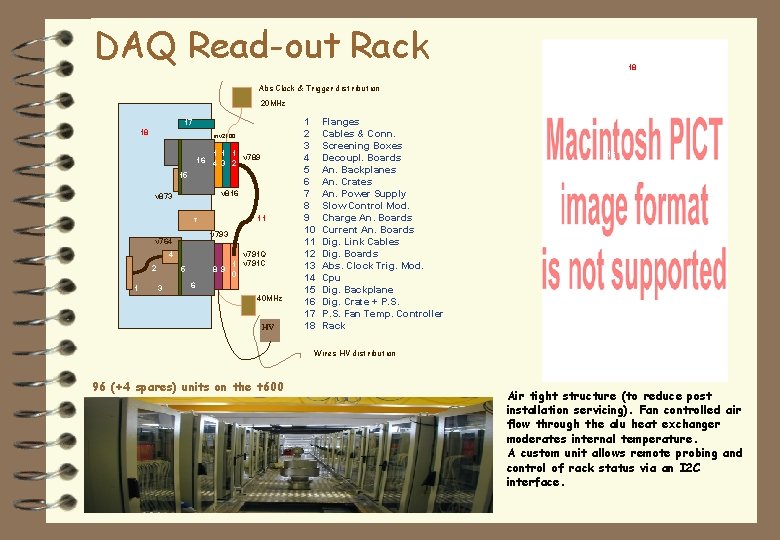

DAQ Read-out Rack 18 17 Abs Clock & Trigger distribution 20 MHz 17 18 mv 2100 16 1 1 1 v 789 43 2 15 v 816 v 873 11 7 v 793 v 764 4 2 1 5 3 89 v 791 Q 1 v 791 C 0 6 40 MHz HV 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 Flanges Cables & Conn. Screening Boxes Decoupl. Boards An. Backplanes An. Crates An. Power Supply Slow Control Mod. Charge An. Boards Current An. Boards Dig. Link Cables Dig. Boards Abs. Clock Trig. Mod. Cpu Dig. Backplane Dig. Crate + P. S. Fan Temp. Controller Rack 16 7 6 Wires HV distribution 96 (+4 spares) units on the t 600 Air tight structure (to reduce post installation servicing). Fan controlled air flow through the alu heat exchanger moderates internal temperature. A custom unit allows remote probing and control of rack status via an I 2 C interface.

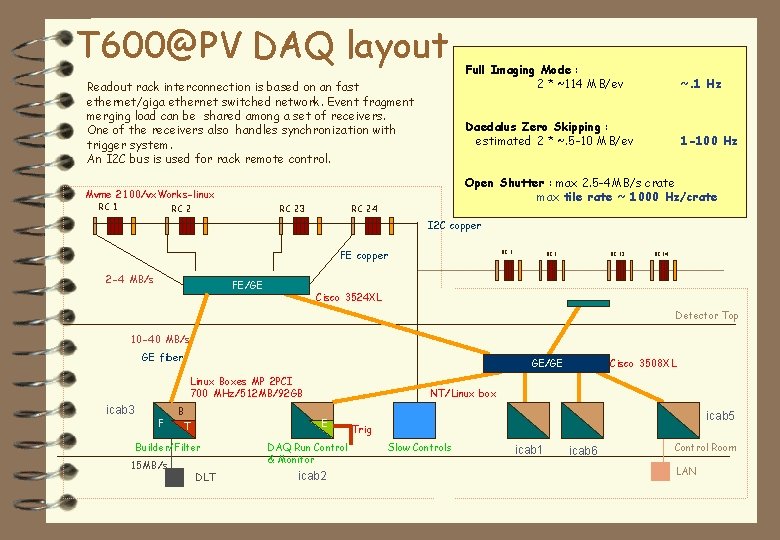

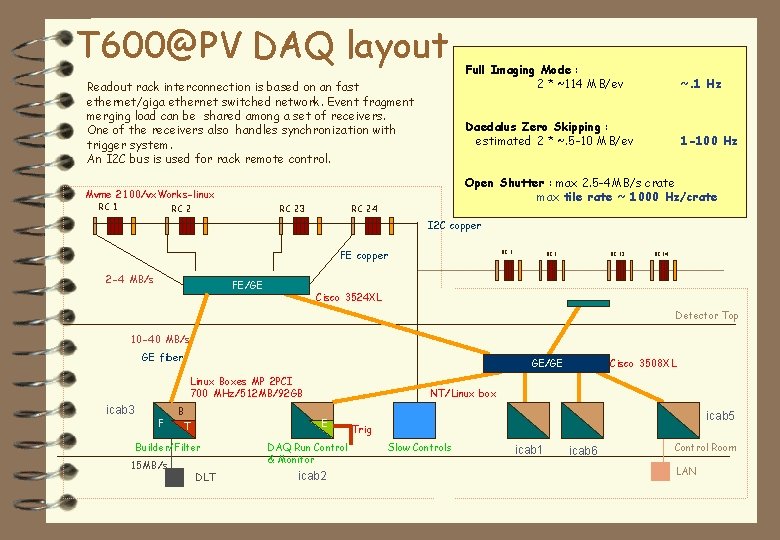

T 600@PV DAQ layout Readout rack interconnection is based on an fast ethernet/giga ethernet switched network. Event fragment merging load can be shared among a set of receivers. One of the receivers also handles synchronization with trigger system. An I 2 C bus is used for rack remote control. RC 23 ~. 1 Hz Daedalus Zero Skipping : estimated 2 * ~. 5 -10 MB/ev 1 -100 Hz Open Shutter : max 2. 5 -4 MB/s crate max tile rate ~ 1000 Hz/crate Mvme 2100/vx. Works-linux RC 1 Full Imaging Mode : 2 * ~114 MB/ev RC 24 I 2 C copper FE copper 2 -4 MB/s FE/GE RC 1 RC 23 RC 24 Cisco 3524 XL Detector Top 10 -40 MB/s GE fiber GE/GE Linux Boxes MP 2 PCI 700 MHz/512 MB/92 GB icab 3 F B T 15 MB/s NT/Linux box E Builder/Filter DLT Cisco 3508 XL DAQ Run Control & Monitor icab 2 icab 5 Trig Slow Controls icab 1 icab 6 Control Room LAN

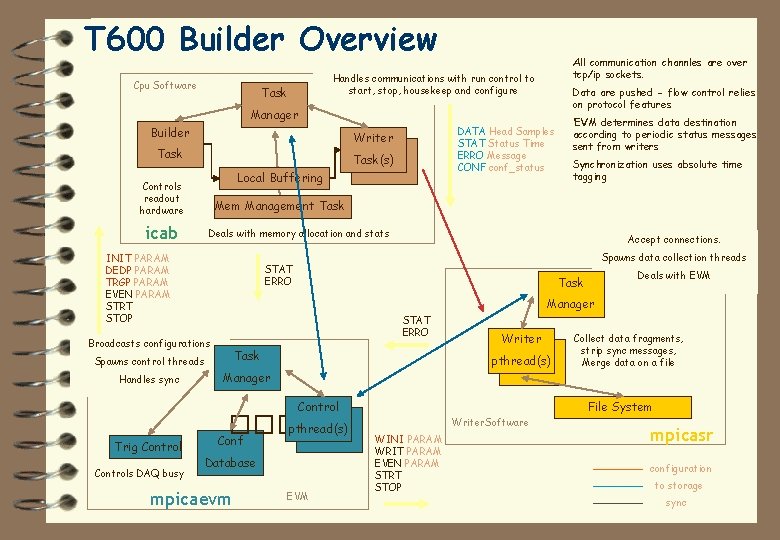

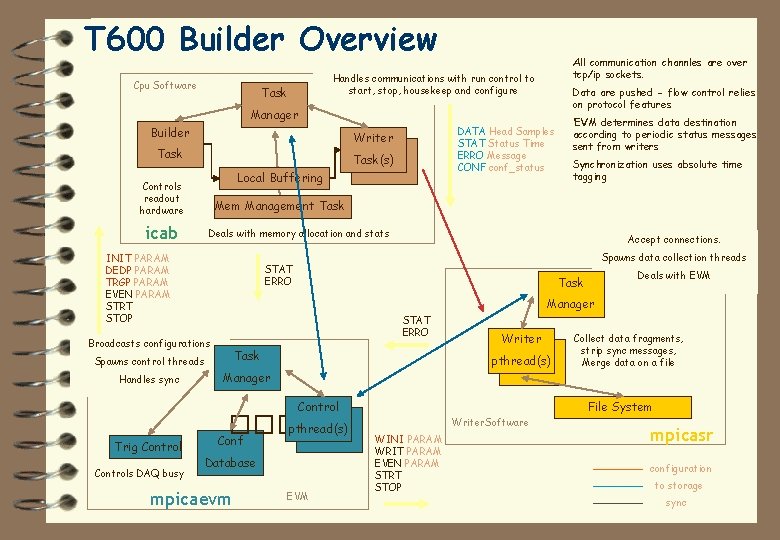

T 600 Builder Overview Cpu Software All communication channles are over tcp/ip sockets. Handles communications with run control to start, stop, housekeep and configure Task Data are pushed - flow control relies on protocol features Manager Builder Writer Task(s) Local Buffering Controls readout hardware icab DATA Head Samples STAT Status Time ERRO Message CONF conf_status Deals with memory allocation and stats Accept connections. Spawns data collection threads STAT ERRO Deals with EVM Task Manager STAT ERRO Broadcasts configurations Spawns control threads Task Handles sync Manager Writer pthread(s) Control ���pthread(s) Controls DAQ busy Synchronization uses absolute time tagging Mem Management Task INIT PARAM DEDP PARAM TRGP PARAM EVEN PARAM STRT STOP Trig Control ’EVM determines data destination according to periodic status messages sent from writers Conf Database mpicaevm EVM Collect data fragments, strip sync messages, Merge data on a file File System Writer. Software WINI PARAM WRIT PARAM EVEN PARAM STRT STOP mpicasr configuration to storage sync

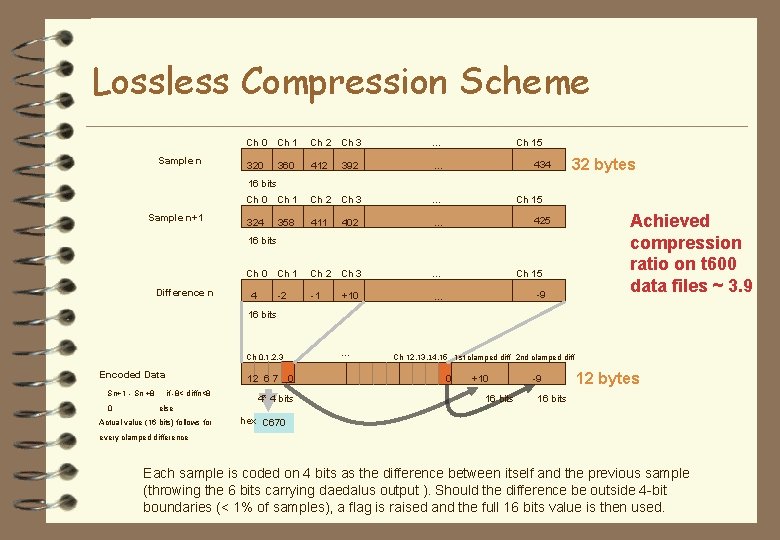

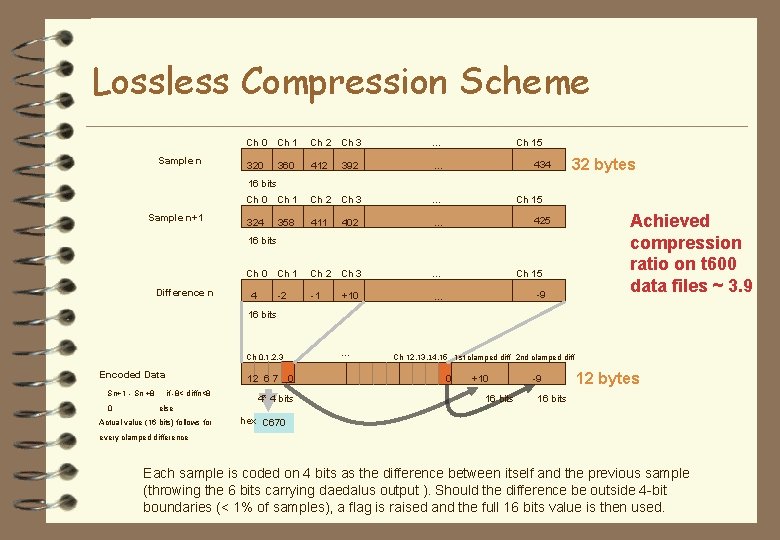

Lossless Compression Scheme Sample n Ch 0 Ch 1 Ch 2 Ch 3 … 320 412 … 360 392 Ch 15 434 32 bytes 16 bits Sample n+1 Ch 0 Ch 1 Ch 2 Ch 3 … 324 411 … 358 402 Ch 15 425 16 bits Ch 0 Ch 1 Difference n 4 -2 Ch 3 … -1 … +10 Ch 15 -9 Achieved compression ratio on t 600 data files ~ 3. 9 16 bits Ch 0, 1, 2, 3 Encoded Data Sn+1 - Sn +8 0 12 6 7 0 if -8< diffn<8 else Actual value (16 bits) follows for 4* 4 bits … Ch 12, 13, 14, 15 … 1 st clamped diff 2 nd clamped diff 0 +10 16 bits -9 12 bytes 16 bits hex C 670 every clamped difference Each sample is coded on 4 bits as the difference between itself and the previous sample (throwing the 6 bits carrying daedalus output ). Should the difference be outside 4 -bit boundaries (< 1% of samples), a flag is raised and the full 16 bits value is then used.