HCAL TPG and Readout CMS HCAL Readout Status

![HCAL FE/DAQ Overview Trigger Primitives DAQ DATA SLINK 64 [1 Gbit/s] CAL REGIONAL TRIGGER HCAL FE/DAQ Overview Trigger Primitives DAQ DATA SLINK 64 [1 Gbit/s] CAL REGIONAL TRIGGER](https://slidetodoc.com/presentation_image_h/22061a8d495384afc2e154fd18a833d8/image-4.jpg)

- Slides: 18

HCAL TPG and Readout CMS HCAL Readout Status CERN Tullio Grassi, Drew Baden University of Maryland Jim Rohlf Boston University CMS/CERN. Nov, 2001 HCAL Tri. DAS 1

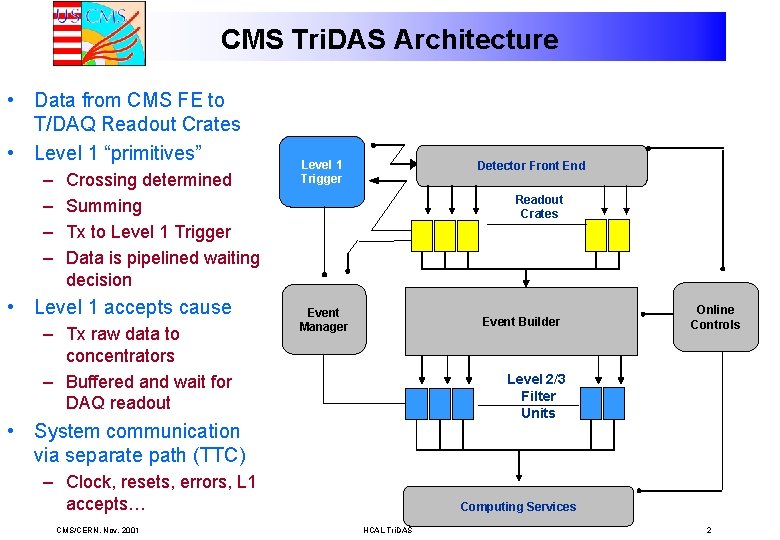

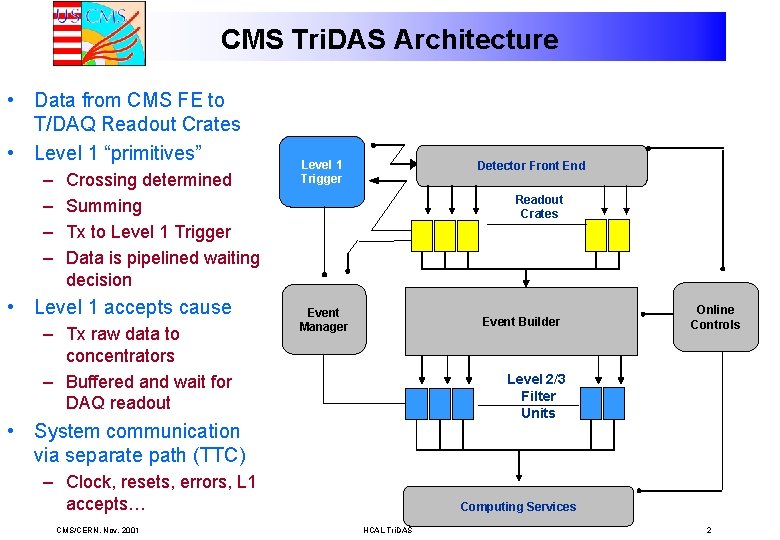

CMS Tri. DAS Architecture • Data from CMS FE to T/DAQ Readout Crates • Level 1 “primitives” – – Crossing determined Summing Tx to Level 1 Trigger Data is pipelined waiting decision • Level 1 accepts cause – Tx raw data to concentrators – Buffered and wait for DAQ readout Level 1 Trigger Detector Front End Readout Crates Event Manager Event Builder Level 2/3 Filter Units • System communication via separate path (TTC) – Clock, resets, errors, L 1 accepts… CMS/CERN. Nov, 2001 Online Controls Computing Services HCAL Tri. DAS 2

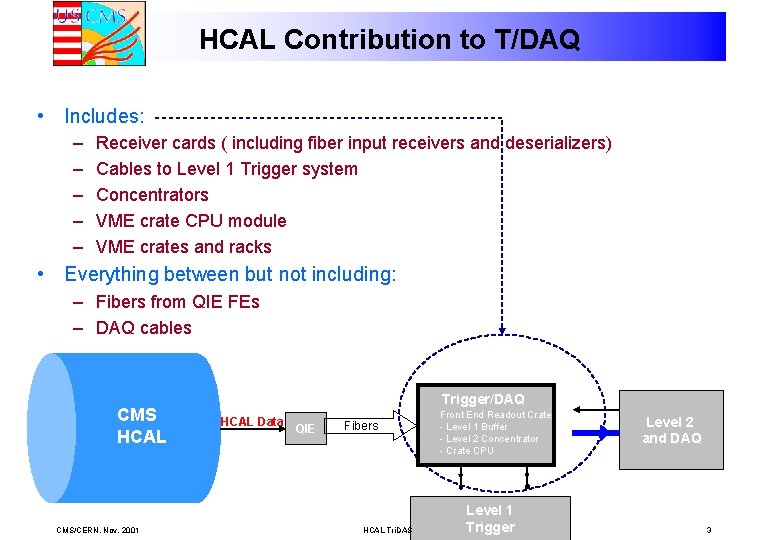

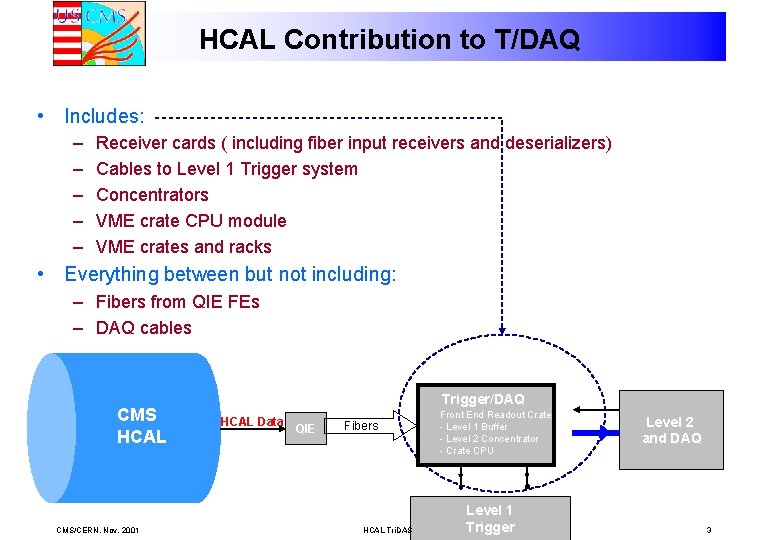

HCAL Contribution to T/DAQ • Includes: – – – Receiver cards ( including fiber input receivers and deserializers) Cables to Level 1 Trigger system Concentrators VME crate CPU module VME crates and racks • Everything between but not including: – Fibers from QIE FEs – DAQ cables CMS HCAL CMS/CERN. Nov, 2001 Trigger/DAQ HCAL Data QIE Fibers HCAL Tri. DAS Front End Readout Crate - Level 1 Buffer - Level 2 Concentrator - Crate CPU Level 1 Trigger Level 2 and DAQ 3

![HCAL FEDAQ Overview Trigger Primitives DAQ DATA SLINK 64 1 Gbits CAL REGIONAL TRIGGER HCAL FE/DAQ Overview Trigger Primitives DAQ DATA SLINK 64 [1 Gbit/s] CAL REGIONAL TRIGGER](https://slidetodoc.com/presentation_image_h/22061a8d495384afc2e154fd18a833d8/image-4.jpg)

HCAL FE/DAQ Overview Trigger Primitives DAQ DATA SLINK 64 [1 Gbit/s] CAL REGIONAL TRIGGER DAQ RUI C P U D C C H T R QIE QIE QIE 18 HTRs per Readout Crate Shield Wall GOL CCA QIE CCA HPD Fibers at 1. 6 Gb/s 3 QIE-channels per fiber GOL CCA (On detector) 32 bits @ 40 MHz H T R 16 bits @ 80 MHz TTC FRONT-END RBX Readout Box H T R READ-OUT Crate (in UXA) FE MODULE CMS/CERN. Nov, 2001 HCAL Tri. DAS 4

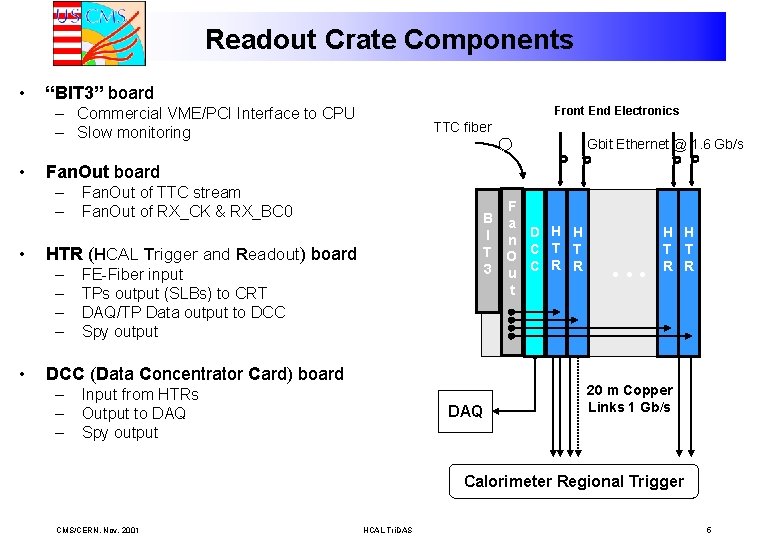

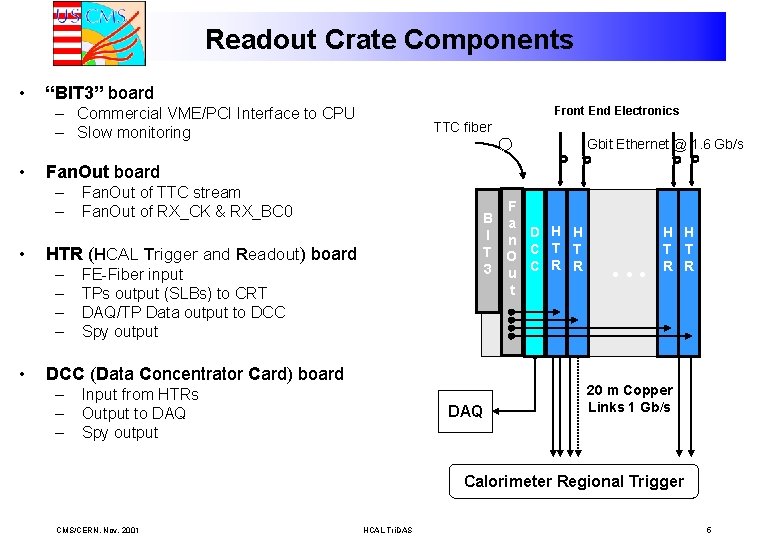

Readout Crate Components • “BIT 3” board – Commercial VME/PCI Interface to CPU – Slow monitoring • TTC fiber Gbit Ethernet @ 1. 6 Gb/s Fan. Out board – – • Fan. Out of TTC stream Fan. Out of RX_CK & RX_BC 0 F B a I n D H H T O C T T 3 u C R R t HTR (HCAL Trigger and Readout) board D C C • Front End Electronics – – FE-Fiber input TPs output (SLBs) to CRT DAQ/TP Data output to DCC Spy output DCC (Data Concentrator Card) board – – – Input from HTRs Output to DAQ Spy output DAQ . . . H H T T R R 20 m Copper Links 1 Gb/s Calorimeter Regional Trigger CMS/CERN. Nov, 2001 HCAL Tri. DAS 5

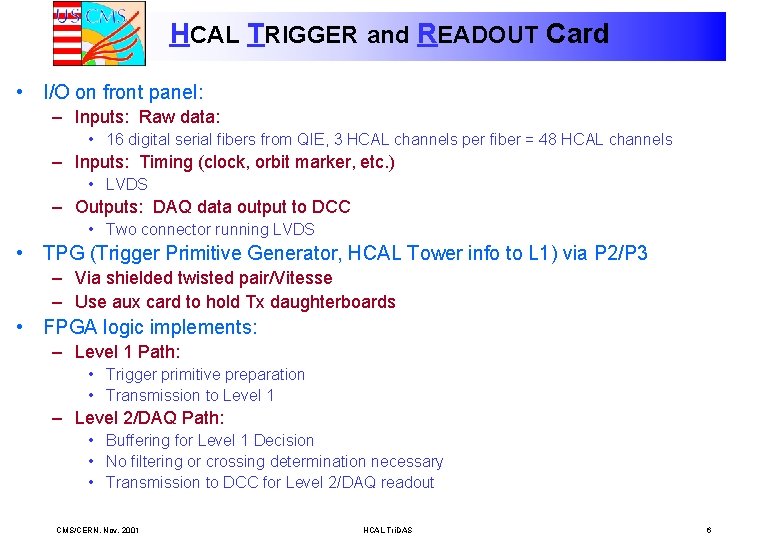

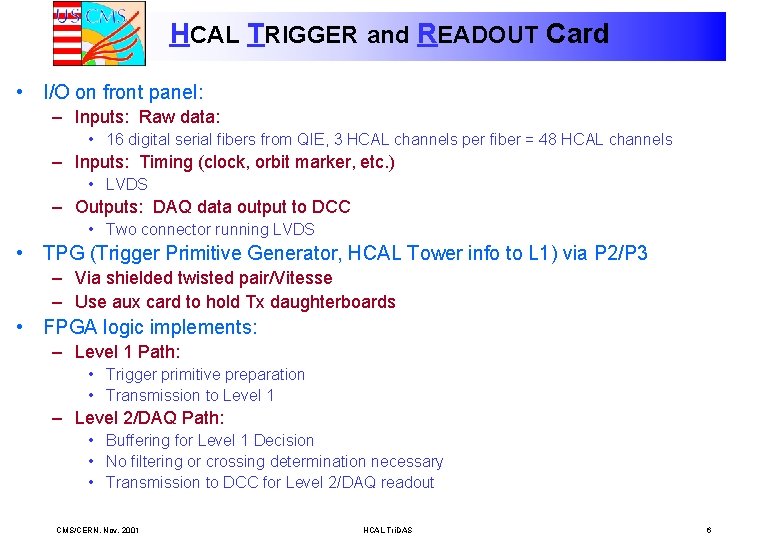

HCAL TRIGGER and READOUT Card • I/O on front panel: – Inputs: Raw data: • 16 digital serial fibers from QIE, 3 HCAL channels per fiber = 48 HCAL channels – Inputs: Timing (clock, orbit marker, etc. ) • LVDS – Outputs: DAQ data output to DCC • Two connector running LVDS • TPG (Trigger Primitive Generator, HCAL Tower info to L 1) via P 2/P 3 – Via shielded twisted pair/Vitesse – Use aux card to hold Tx daughterboards • FPGA logic implements: – Level 1 Path: • Trigger primitive preparation • Transmission to Level 1 – Level 2/DAQ Path: • Buffering for Level 1 Decision • No filtering or crossing determination necessary • Transmission to DCC for Level 2/DAQ readout CMS/CERN. Nov, 2001 HCAL Tri. DAS 6

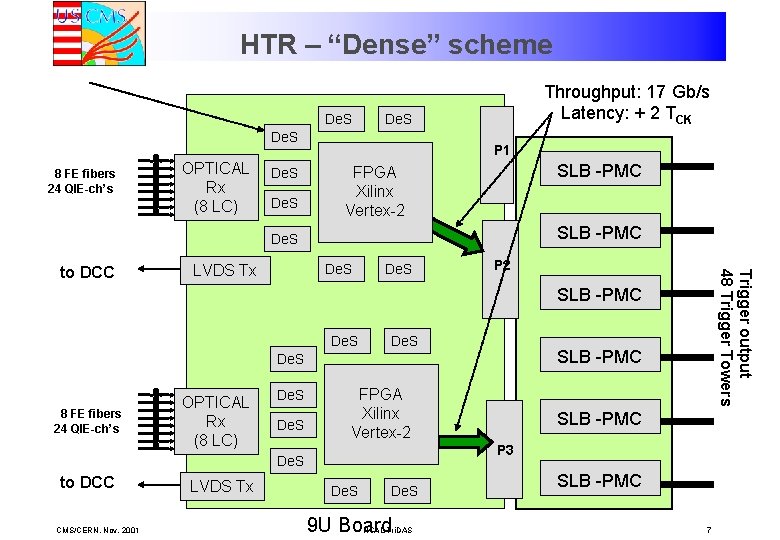

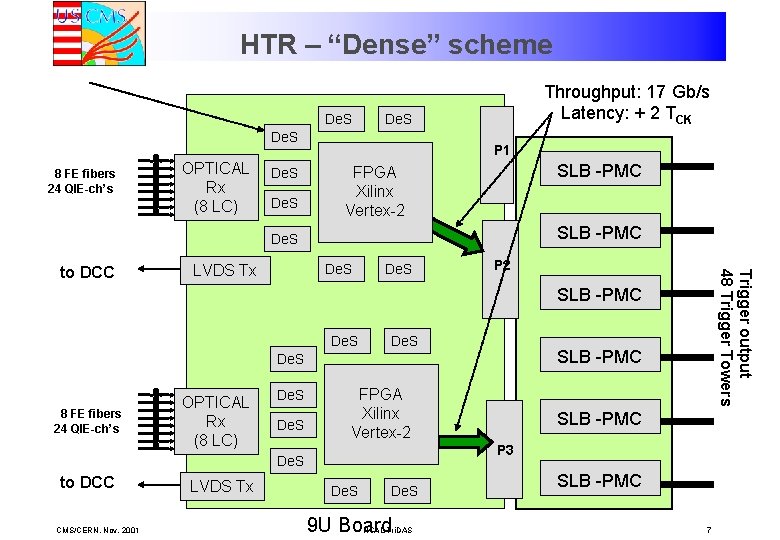

HTR – “Dense” scheme De. S 8 FE fibers 24 QIE-ch’s OPTICAL Rx (8 LC) De. S Throughput: 17 Gb/s Latency: + 2 TCK P 1 SLB -PMC FPGA Xilinx Vertex-2 SLB -PMC De. S LVDS Tx De. S P 2 Trigger output 48 Trigger Towers to DCC SLB -PMC De. S 8 FE fibers 24 QIE-ch’s OPTICAL Rx (8 LC) De. S FPGA Xilinx Vertex-2 P 3 De. S to DCC CMS/CERN. Nov, 2001 LVDS Tx SLB -PMC De. S 9 U Board HCAL Tri. DAS SLB -PMC 7

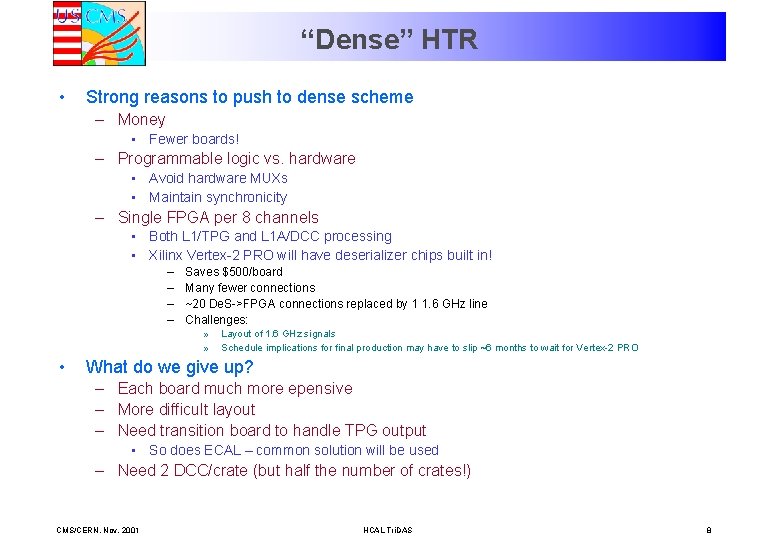

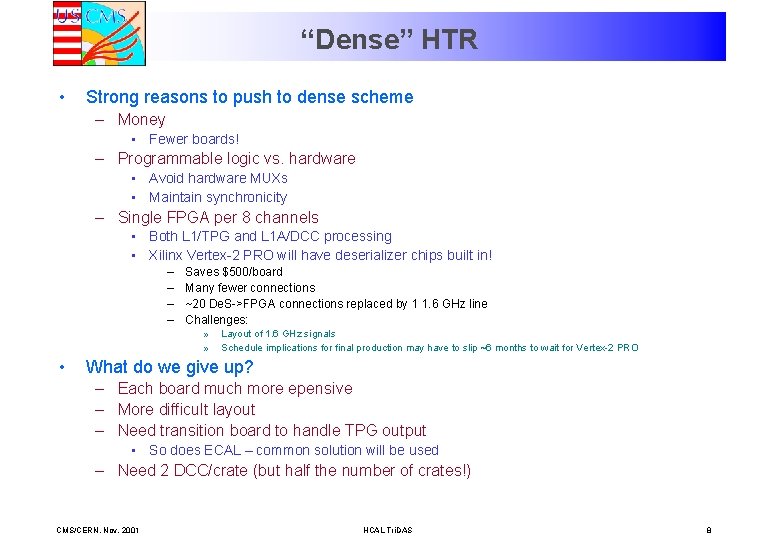

“Dense” HTR • Strong reasons to push to dense scheme – Money • Fewer boards! – Programmable logic vs. hardware • Avoid hardware MUXs • Maintain synchronicity – Single FPGA per 8 channels • Both L 1/TPG and L 1 A/DCC processing • Xilinx Vertex-2 PRO will have deserializer chips built in! – – Saves $500/board Many fewer connections ~20 De. S->FPGA connections replaced by 1 1. 6 GHz line Challenges: » » • Layout of 1. 6 GHz signals Schedule implications for final production may have to slip ~6 months to wait for Vertex-2 PRO What do we give up? – Each board much more epensive – More difficult layout – Need transition board to handle TPG output • So does ECAL – common solution will be used – Need 2 DCC/crate (but half the number of crates!) CMS/CERN. Nov, 2001 HCAL Tri. DAS 8

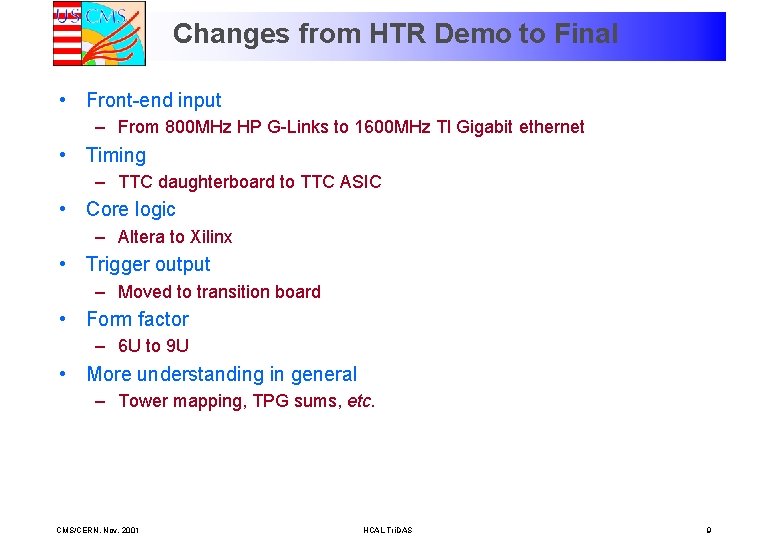

Changes from HTR Demo to Final • Front-end input – From 800 MHz HP G-Links to 1600 MHz TI Gigabit ethernet • Timing – TTC daughterboard to TTC ASIC • Core logic – Altera to Xilinx • Trigger output – Moved to transition board • Form factor – 6 U to 9 U • More understanding in general – Tower mapping, TPG sums, etc. CMS/CERN. Nov, 2001 HCAL Tri. DAS 9

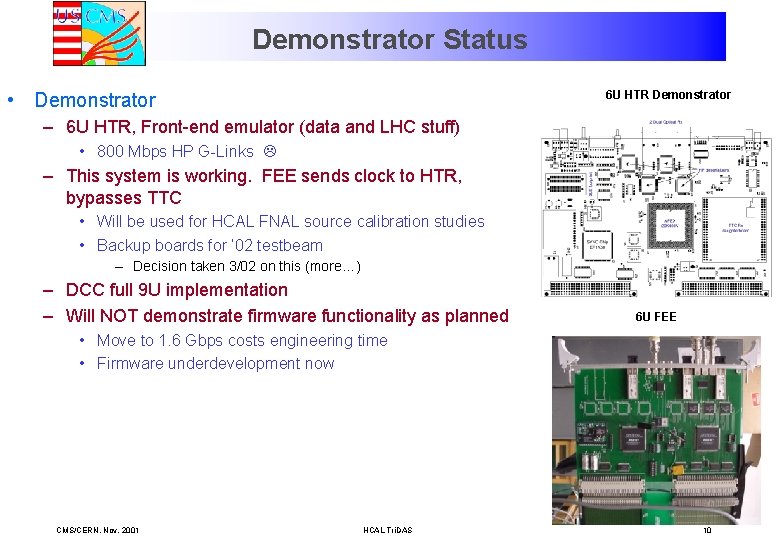

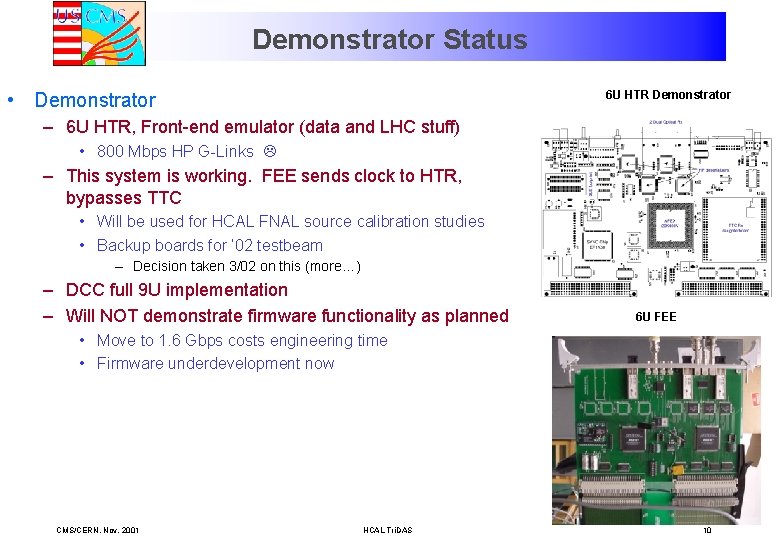

Demonstrator Status 6 U HTR Demonstrator • Demonstrator – 6 U HTR, Front-end emulator (data and LHC stuff) • 800 Mbps HP G-Links – This system is working. FEE sends clock to HTR, bypasses TTC • Will be used for HCAL FNAL source calibration studies • Backup boards for ’ 02 testbeam – Decision taken 3/02 on this (more…) – DCC full 9 U implementation – Will NOT demonstrate firmware functionality as planned 6 U FEE • Move to 1. 6 Gbps costs engineering time • Firmware underdevelopment now CMS/CERN. Nov, 2001 HCAL Tri. DAS 10

Status • Front-end emulator HTR demonstrator DCC S-Link CPU – Successful operation of each individual link • Integration underway - Tullio goes to Boston next week • Pre-prototype board layout – Complete, board is now being stuffed – Will have only 1 FPGA with full complement of associated parts • Will use the TI Deserializers – not the Vertex 2 PRO – Internal use only • Prototype layout – Should be complete in November • Some changes from pre-prototype, but minor • Maryland activity is in prep for source tests and 9 U board design – Preparation for testbeam summer 02 not yet started – Trying hard to meet March 02 deadline for decision on which HTR to use for testbeam • Energy filters still undefined CMS/CERN. Nov, 2001 HCAL Tri. DAS 11

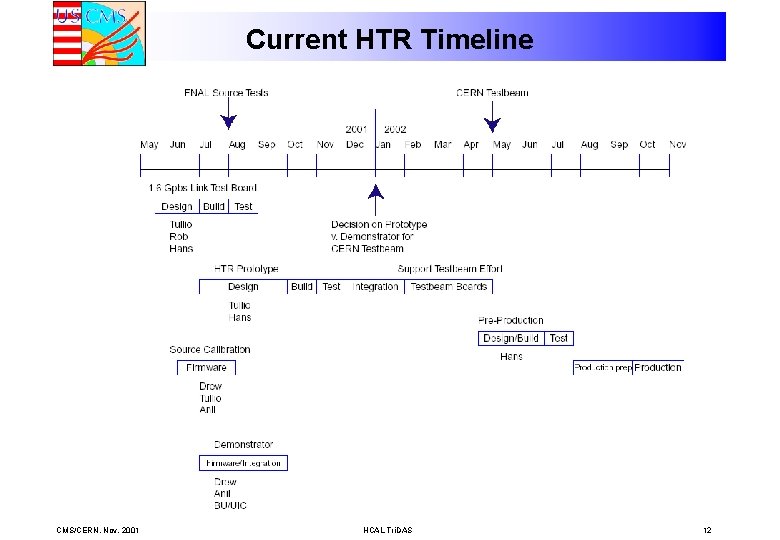

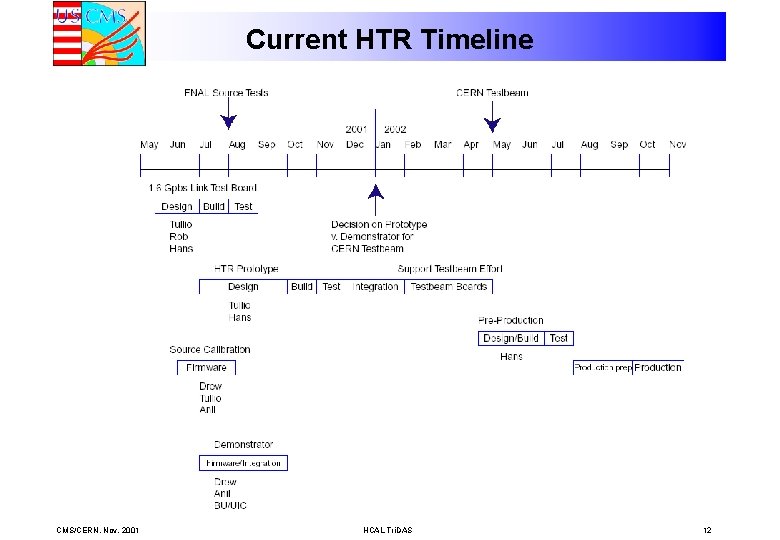

Current HTR Timeline CMS/CERN. Nov, 2001 HCAL Tri. DAS 12

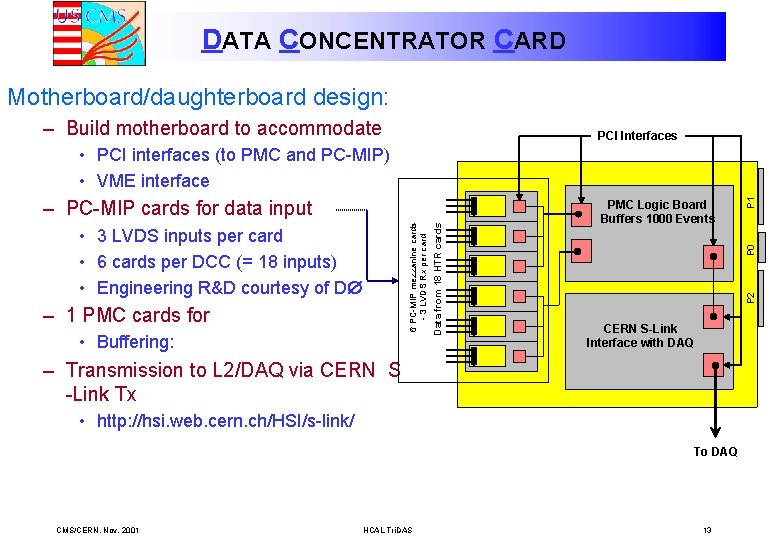

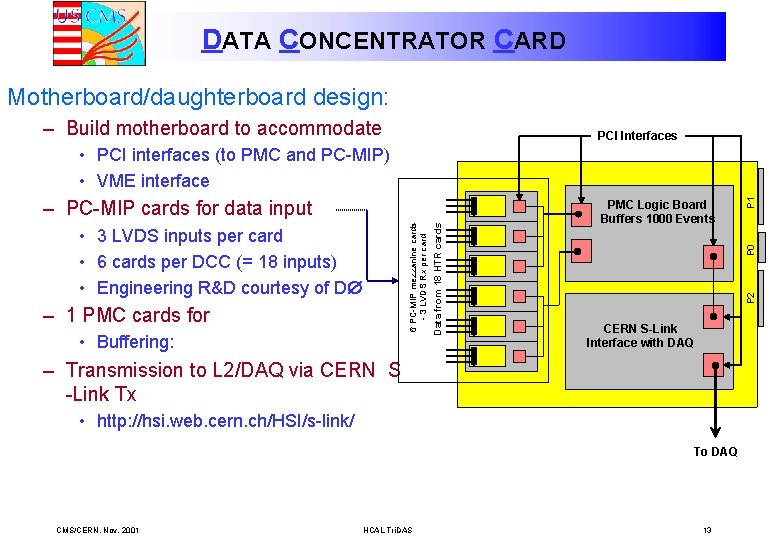

DATA CONCENTRATOR CARD Motherboard/daughterboard design: – Build motherboard to accommodate PCI Interfaces – 1 PMC cards for • Buffering: P 0 PMC Logic Board Buffers 1000 Events P 2 • 3 LVDS inputs per card • 6 cards per DCC (= 18 inputs) • Engineering R&D courtesy of D Data from 18 HTR cards 6 PC-MIP mezzanine cards - 3 LVDS Rx per card – PC-MIP cards for data input CERN S-Link Interface with DAQ – Transmission to L 2/DAQ via CERN S -Link Tx • http: //hsi. web. cern. ch/HSI/s-link/ To DAQ CMS/CERN. Nov, 2001 HCAL Tri. DAS P 1 • PCI interfaces (to PMC and PC-MIP) • VME interface 13

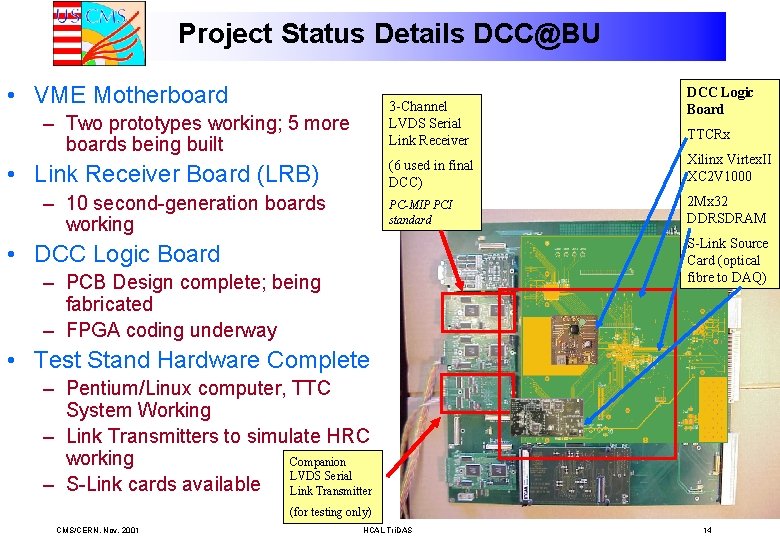

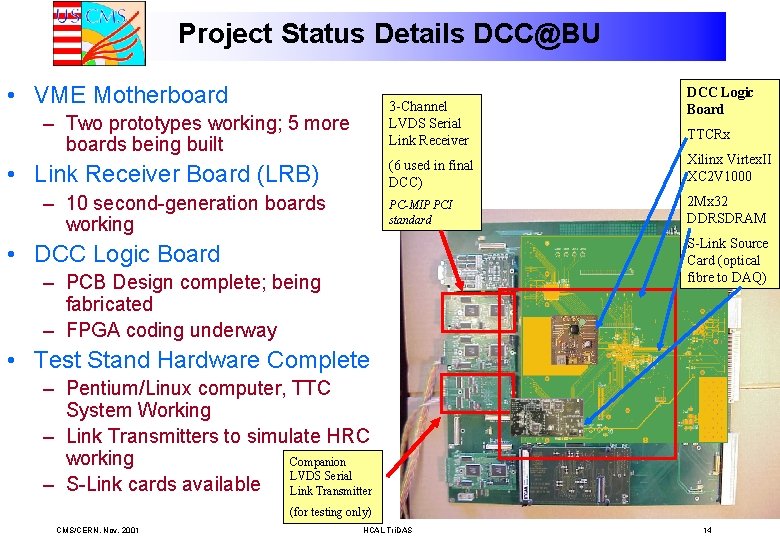

Project Status Details DCC@BU • VME Motherboard 3 -Channel LVDS Serial Link Receiver – Two prototypes working; 5 more boards being built (6 used in final DCC) • Link Receiver Board (LRB) – 10 second-generation boards working PC-MIP PCI standard DCC Logic Board TTCRx Xilinx Virtex. II XC 2 V 1000 2 Mx 32 DDRSDRAM S-Link Source Card (optical fibre to DAQ) • DCC Logic Board – PCB Design complete; being fabricated – FPGA coding underway • Test Stand Hardware Complete – Pentium/Linux computer, TTC System Working – Link Transmitters to simulate HRC working Companion LVDS Serial – S-Link cards available Link Transmitter (for testing only) CMS/CERN. Nov, 2001 HCAL Tri. DAS 14

HCAL TIMING FANOUT Module • Fanout of TTC info: – Both TTC channels fanout to each HTR and DCC – Separate fanout of clock/BC 0 for TPG synchronization • “da. Silva” scheme • Single width VME module CMS/CERN. Nov, 2001 HCAL Tri. DAS 15

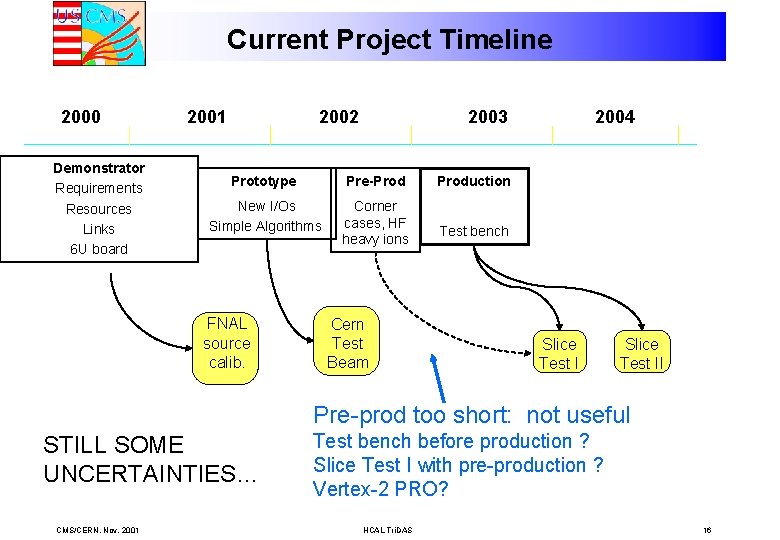

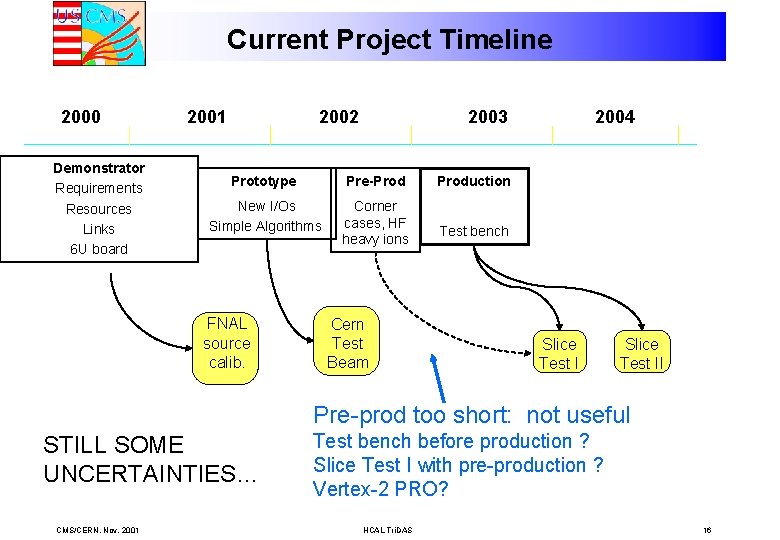

Current Project Timeline 2000 Demonstrator Requirements Resources Links 6 U board 2001 2002 2003 Prototype Pre-Prod New I/Os Simple Algorithms Corner cases, HF heavy ions FNAL source calib. Cern Test Beam 2004 Production Test bench Slice Test II Pre-prod too short: not useful STILL SOME UNCERTAINTIES… CMS/CERN. Nov, 2001 Test bench before production ? Slice Test I with pre-production ? Vertex-2 PRO? HCAL Tri. DAS 16

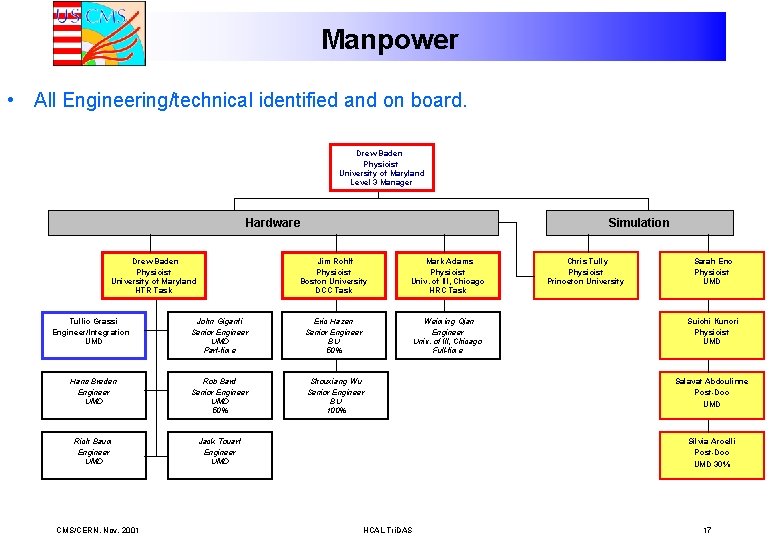

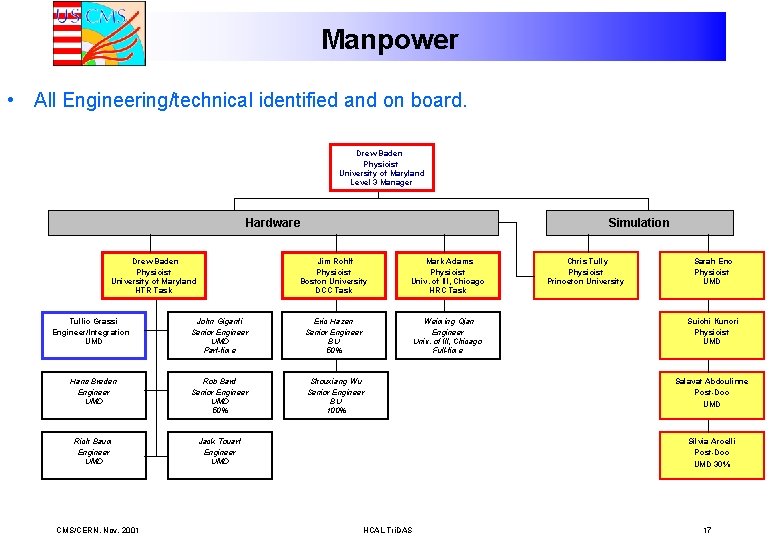

Manpower • All Engineering/technical identified and on board. Drew Baden Physicist University of Maryland Level 3 Manager Hardware Drew Baden Physicist University of Maryland HTR Task Simulation Jim Rohlf Physicist Boston University DCC Task Mark Adams Physicist Univ. of Ill, Chicago HRC Task John Giganti Senior Engineer UMD Part-time Eric Hazen Senior Engineer BU 50% Weiming Qian Engineer Univ. of Ill, Chicago Full-time Hans Breden Engineer UMD Rob Bard Senior Engineer UMD 50% Shouxiang Wu Senior Engineer BU 100% Rich Baum Engineer UMD Jack Touart Engineer UMD Tullio Grassi Engineer/Integration UMD CMS/CERN. Nov, 2001 Chris Tully Physicist Princeton University Sarah Eno Physicist UMD Suichi Kunori Physicist UMD Salavat Abdoulinne Post-Doc UMD Silvia Arcelli Post-Doc UMD 30% HCAL Tri. DAS 17

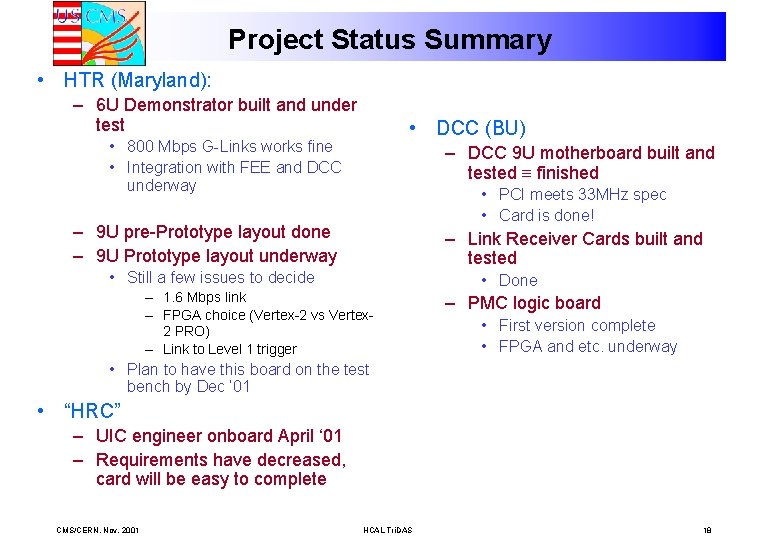

Project Status Summary • HTR (Maryland): – 6 U Demonstrator built and under test • DCC (BU) • 800 Mbps G-Links works fine • Integration with FEE and DCC underway – DCC 9 U motherboard built and tested finished • PCI meets 33 MHz spec • Card is done! – 9 U pre-Prototype layout done – 9 U Prototype layout underway – Link Receiver Cards built and tested • Still a few issues to decide – 1. 6 Mbps link – FPGA choice (Vertex-2 vs Vertex 2 PRO) – Link to Level 1 trigger • Done – PMC logic board • First version complete • FPGA and etc. underway • Plan to have this board on the test bench by Dec ’ 01 • “HRC” – UIC engineer onboard April ‘ 01 – Requirements have decreased, card will be easy to complete CMS/CERN. Nov, 2001 HCAL Tri. DAS 18