Raunarsko projektovanje elektronskih kola Simulacija elektronskih kola Postdiplomske

![Entity, sintaksa entity_name is [generics] [ports] [declarations (types, constants, signals)] [definitions (functions, procedures)] [begin Entity, sintaksa entity_name is [generics] [ports] [declarations (types, constants, signals)] [definitions (functions, procedures)] [begin](https://slidetodoc.com/presentation_image_h2/911241d46073b6051f3588afb6d9b140/image-41.jpg)

![Lab 1 DE 2 -70 FPGA pins Onal SW[0] PIN_AA 23 a SW[1] PIN_AB Lab 1 DE 2 -70 FPGA pins Onal SW[0] PIN_AA 23 a SW[1] PIN_AB](https://slidetodoc.com/presentation_image_h2/911241d46073b6051f3588afb6d9b140/image-54.jpg)

![Napredni dizajn Primjer realizacije FIR filtra: gdje su: y[n] izlaz x(n-i) je ulaz u Napredni dizajn Primjer realizacije FIR filtra: gdje su: y[n] izlaz x(n-i) je ulaz u](https://slidetodoc.com/presentation_image_h2/911241d46073b6051f3588afb6d9b140/image-193.jpg)

- Slides: 195

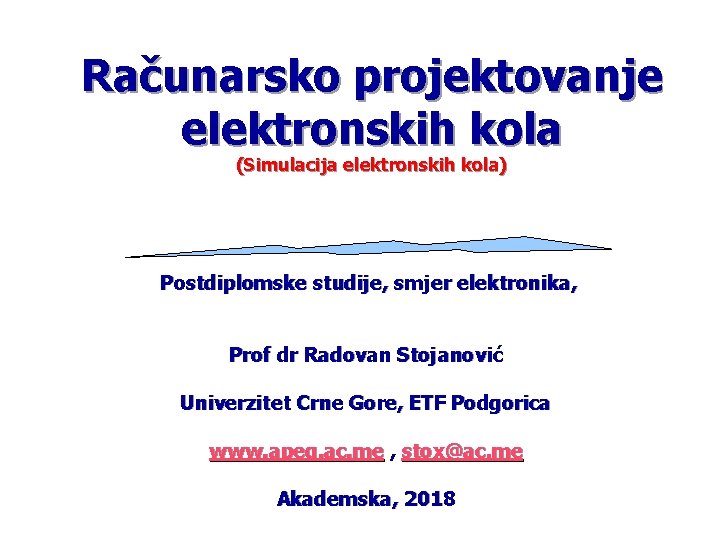

Računarsko projektovanje elektronskih kola (Simulacija elektronskih kola) Postdiplomske studije, smjer elektronika, Prof dr Radovan Stojanović Univerzitet Crne Gore, ETF Podgorica www. apeg. ac. me , stox@ac. me Akademska, 2018

1. U V O D – – – Opis kursa. Zašto automatizovani dizajn (AD)? AD methodologija.

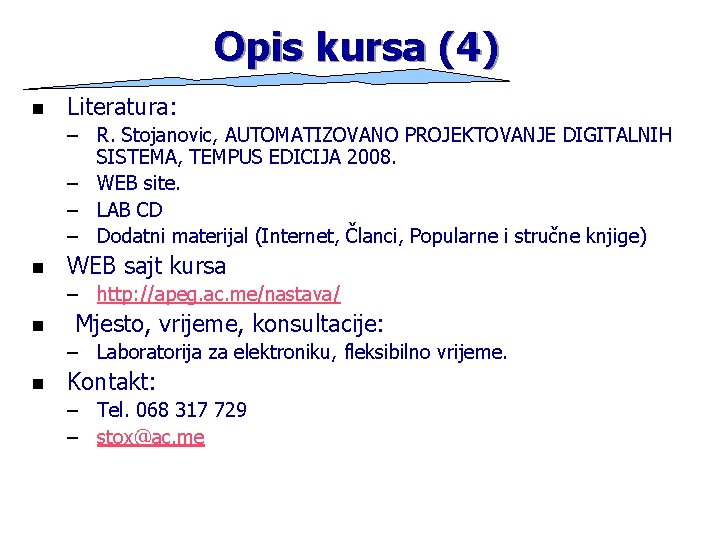

Opis kursa (1) Ø Ciljevi: ü Upoznavanje sa osnovnim principima i tehnikama automatizovanog dizajna i simulacije elektronskih kola i hardverskih sistema za različite namjene (elektronika, telekomunikacija, računari itd). ü Razumijevanje nivoa apstrakcije. ü Upoznavanje i ovladavanje sa elementima HDL-a (Hardware description language) kao i osnovnim CAD (Computer aided design) alatima za opis, simulaciju i sintezu digitalnih elektronskih kola. ü Upoznavanje i ovladavanje sa izabranim softverima i alatima za simulaciju analognih elektronskih kola. ü Praktično projektovanje digitalnih elektronskih kola i sistema u FPGA tehnologiji.

Opis kursa (2) Ø Metodologija nastave: ü Teorijsko-praktičnog tipa: predavanja, prezentacije, lab vježbe, domaći, praktični problemi, seminarski, lektira. Ø Metodologija provjere znanja: o o o Pohadjanje nastave, aktivnosti na času (5%). Laboratorija (10 %). Domaći zadaci (5%). Kolokvijum I (25%) Kolokvijum II (25%) Zavrsni ispit (30%)

Opis kursa (3) n Metodologija ocjenjivanja: – >= 90%: A. – >= 80%, < 90%: B. – >= 70%, < 80%: C. – >= 60%, < 70%: D. – >= 50%, < 60%: E. n n n – < 50%: F. Kredit: – 6 ECTS poena Softverski alati u procesu nastave: – Altera Quartus II Ver 9. 1 (web free) ili jedna od zadnjih Hardverski alati u procesu nastave: – EP 1 C 6 Cyclone family i DGII education board

Opis kursa (4) n Literatura: – R. Stojanovic, AUTOMATIZOVANO PROJEKTOVANJE DIGITALNIH SISTEMA, TEMPUS EDICIJA 2008. – WEB site. – LAB CD – Dodatni materijal (Internet, Članci, Popularne i stručne knjige) n WEB sajt kursa – http: //apeg. ac. me/nastava/ n Mjesto, vrijeme, konsultacije: – Laboratorija za elektroniku, fleksibilno vrijeme. n Kontakt: – Tel. 068 317 729 – stox@ac. me

Lektira Na našem jeziku i engleskom (VHDL): – http: //es. elfak. ni. ac. rs/am/Materijal/Predavanja/AMS 201 0. pdf – http: //www. elektronika. ftn. uns. ac. rs/images/file/2 godina /ume/Vezbe/zbirka. VHDL. pdf – https: //www. fer. unizg. hr/_download/repository/labosivhdl-1. pdf – http: //ftn. mrdnise. com/fajlovi/4 Book. MIT_code_from_examples_Jul 08425. pdf

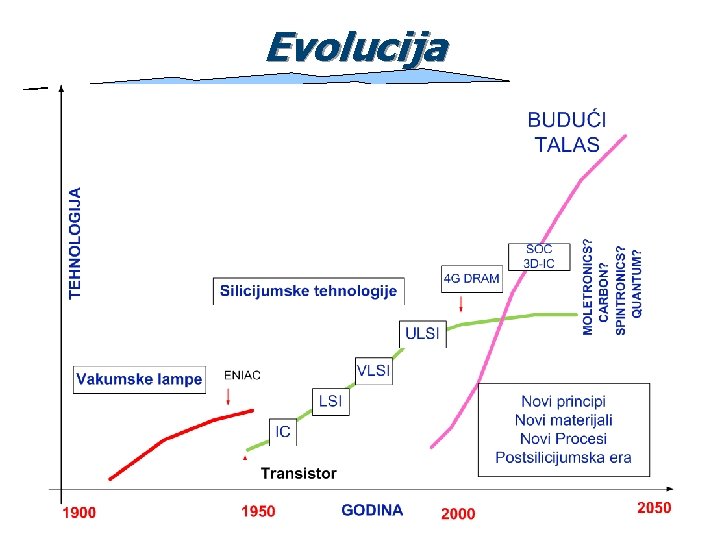

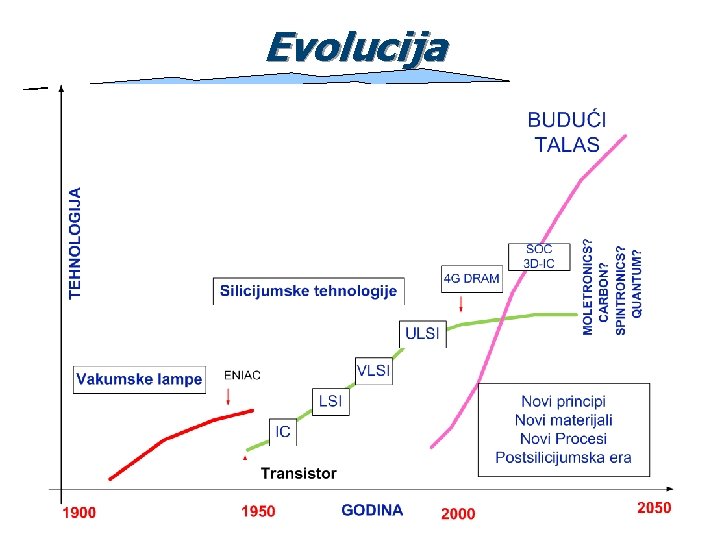

Evolucija

Integarcija Jack Kilby, TI, 1959 konstruiše prvo integrisano kolo (IC). Robert Noyce Fairchild Intel, 1959, razvija prvo pravo IC.

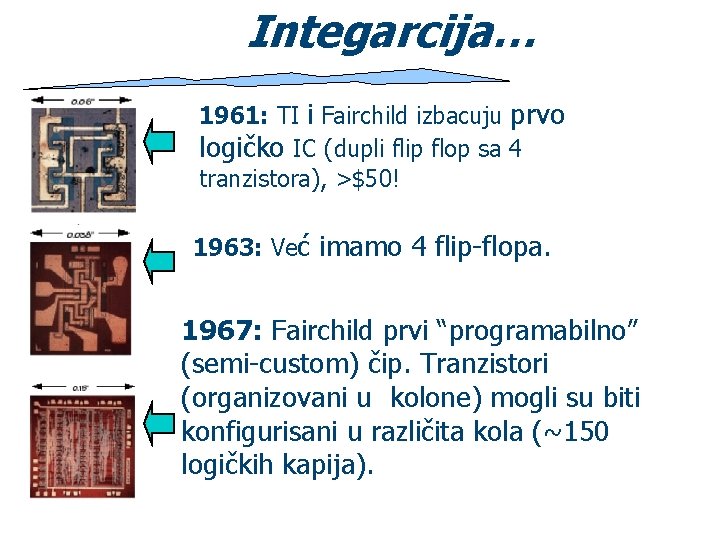

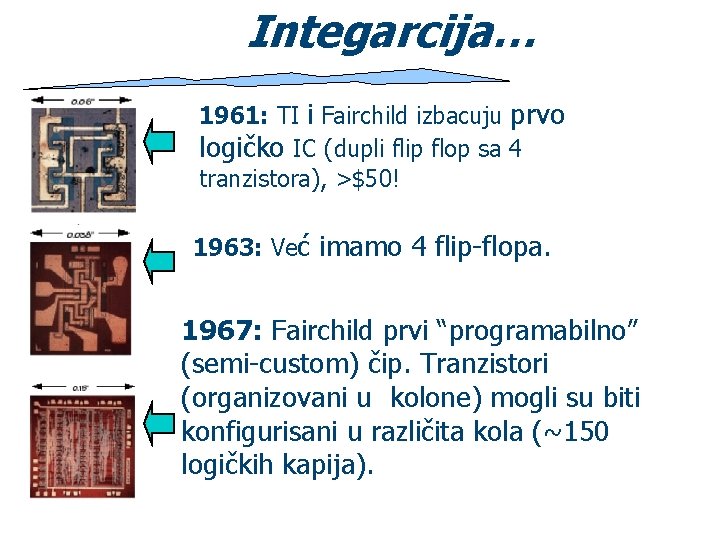

Integarcija… 1961: TI i Fairchild izbacuju prvo logičko IC (dupli flip flop sa 4 tranzistora), >$50! 1963: Već imamo 4 flip-flopa. 1967: Fairchild prvi “programabilno” (semi-custom) čip. Tranzistori (organizovani u kolone) mogli su biti konfigurisani u različita kola (~150 logičkih kapija).

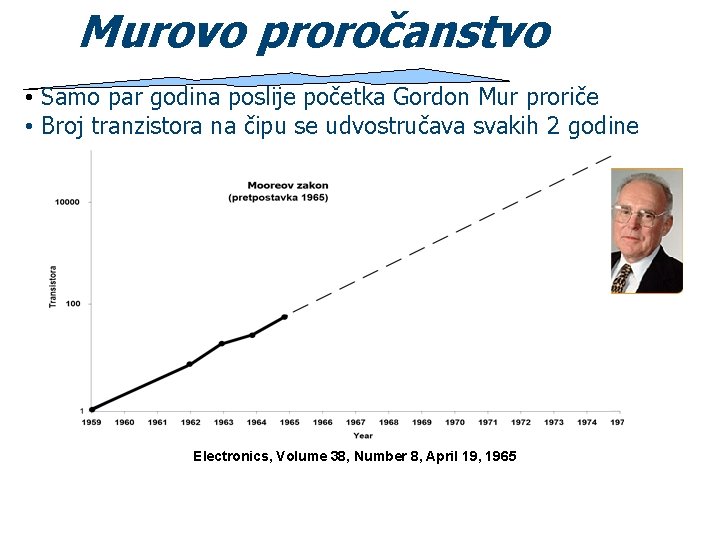

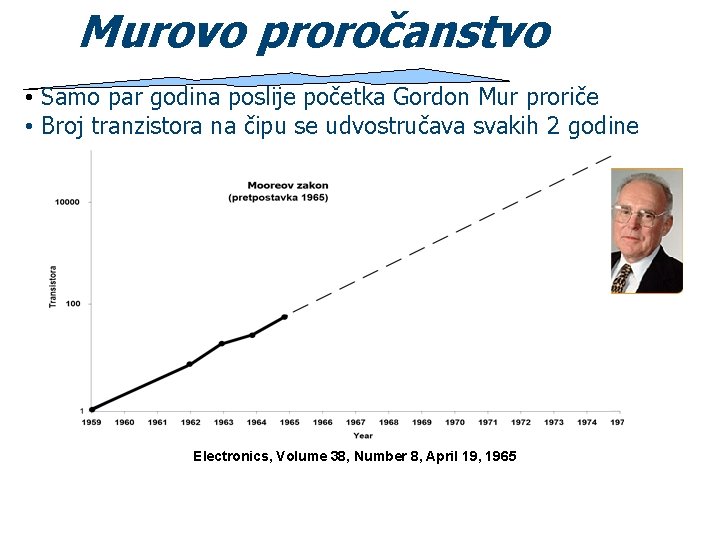

Murovo proročanstvo • Samo par godina poslije početka Gordon Mur proriče • Broj tranzistora na čipu se udvostručava svakih 2 godine Electronics, Volume 38, Number 8, April 19, 1965

Murovo proročanstvo… 1968: Prvi operacioni pojačavač, početak integrisane analogne ere 1968: Noyce and Moore leave Fairchild to form Intel. 1970: Intel, 1 k bit RAM, 1103. 1971: Ted Hoff u Intelu projektuje prvi microprocessor, 4004, 4 -bit buss, 108 KHz, 2300 transistora, 10 um process.

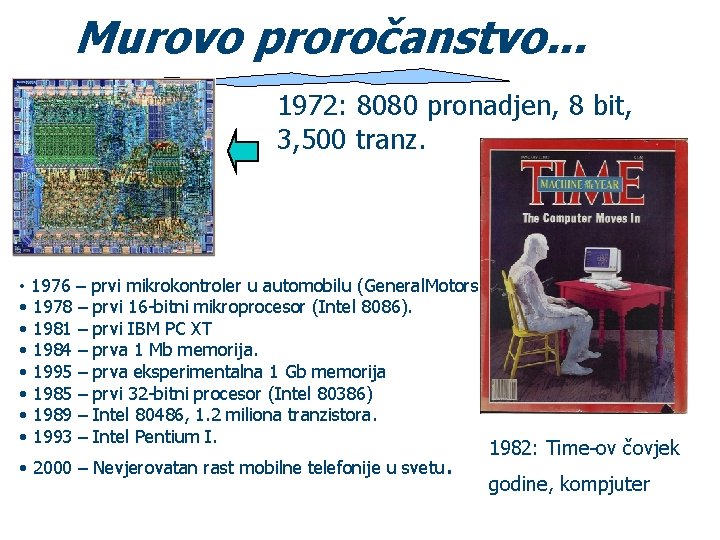

Murovo proročanstvo. . . 1972: 8080 pronadjen, 8 bit, 3, 500 tranz. • 1976 – prvi mikrokontroler u automobilu (General. Motors) • 1978 – prvi 16 -bitni mikroprocesor (Intel 8086). • 1981 – prvi IBM PC XT • 1984 – prva 1 Mb memorija. • 1995 – prva eksperimentalna 1 Gb memorija • 1985 – prvi 32 -bitni procesor (Intel 80386) • 1989 – Intel 80486, 1. 2 miliona tranzistora. • 1993 – Intel Pentium I. • 2000 – Nevjerovatan rast mobilne telefonije u svetu. 1982: Time-ov čovjek godine, kompjuter

Kontraverza “I think there is a world market for maybe five computers” IBM Chairman Thomas Watson, 1943 “ 640, 000 bytes of memory ought to be enough for anybody”, Bill Gates, 1981. “The Internet will catastrophically collapse in 1996”, Robert Metcalfe

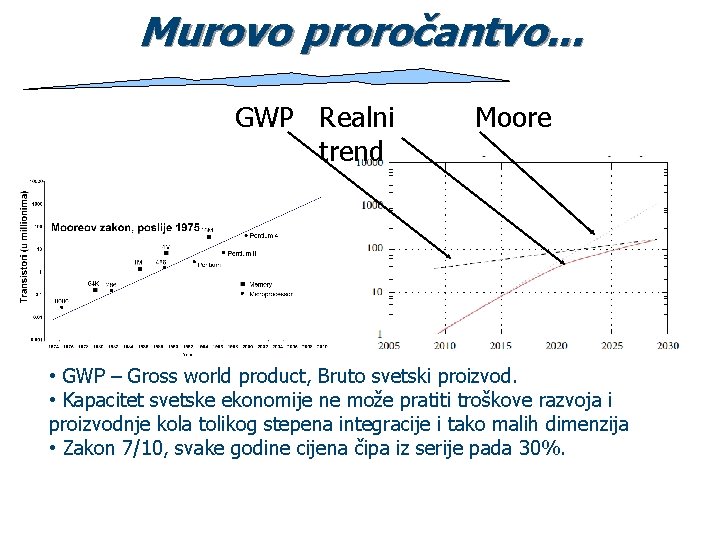

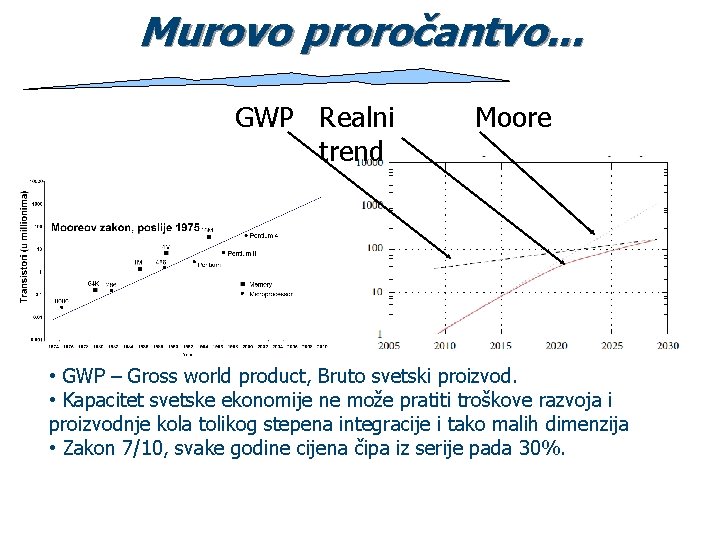

Murovo proročantvo. . . GWP Realni trend Moore • GWP – Gross world product, Bruto svetski proizvod. • Kapacitet svetske ekonomije ne može pratiti troškove razvoja i proizvodnje kola tolikog stepena integracije i tako malih dimenzija • Zakon 7/10, svake godine cijena čipa iz serije pada 30%.

EDA • EDA – Electronic Design Automation. • Ili “Mašina pravi mašinu”. • Jednostavno projektovanje pomoću računara, proračuni svih bitnih parametara, simulacija, verifikacija, korekcija rada i mnogi drugi zahtjevi se obavljaju pomoću računara. • Samo na taj način Mooreov zakon je mogao biti ostvariv. • Prvi pentium kada je bio projektovan iznajmljen je hangar za potrebe crtanje. • EDA se primjenjuje podjednako na ANALOGNI, DIGITALNI, RF i MJEŠOVITI dizajn. • Danas pentium core staje na jedan CD. • DA je prisutna i u drugim disciplinama, gradjevinarstvu, mašinstvu (CAD) itd.

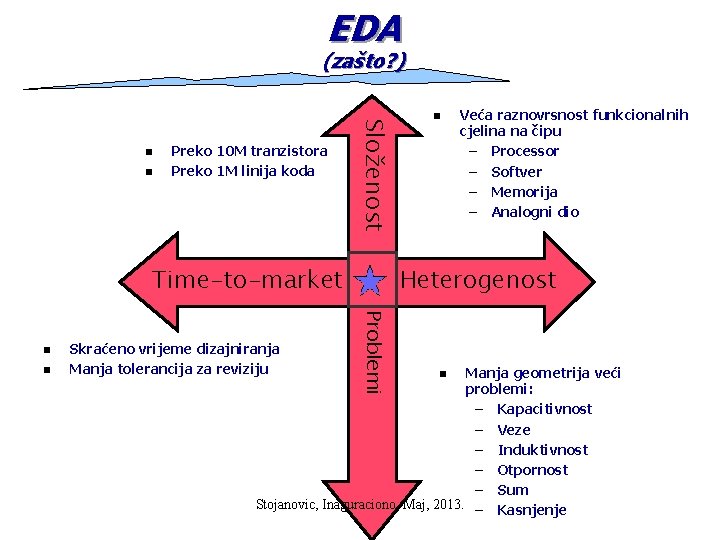

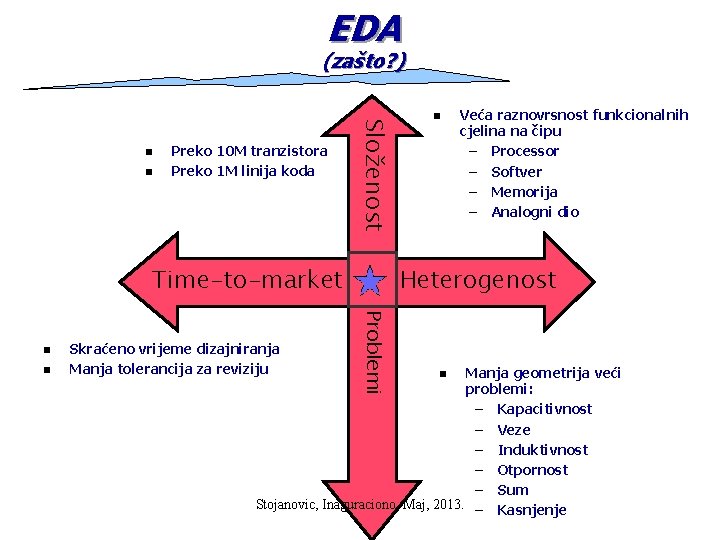

EDA (zašto? ) n Preko 10 M tranzistora Preko 1 M linija koda Složenost n Time-to-market n Skraćeno vrijeme dizajniranja Manja tolerancija za reviziju Veća raznovrsnost funkcionalnih cjelina na čipu – Processor – Softver – Memorija – Analogni dio Heterogenost Problemi n n Manja geometrija veći problemi: – Kapacitivnost – Veze – Induktivnost – Otpornost – Sum Stojanovic, Inaguraciono, Maj, 2013. – Kasnjenje n

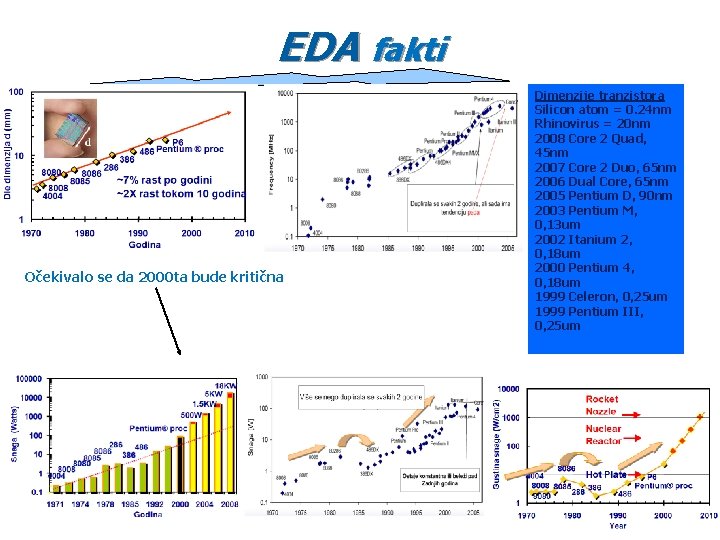

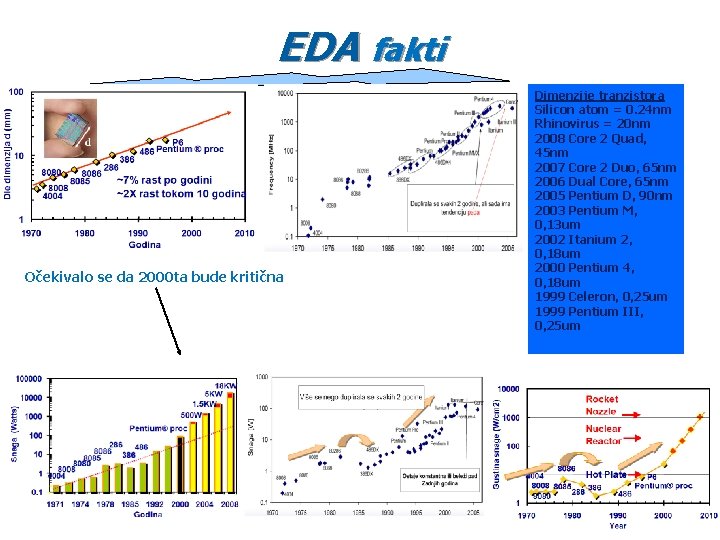

EDA fakti Očekivalo se da 2000 ta bude kritična Dimenzije tranzistora Silicon atom = 0. 24 nm Rhinovirus = 20 nm 2008 Core 2 Quad, 45 nm 2007 Core 2 Duo, 65 nm 2006 Dual Core, 65 nm 2005 Pentium D, 90 nm 2003 Pentium M, 0, 13 um 2002 Itanium 2, 0, 18 um 2000 Pentium 4, 0, 18 um 1999 Celeron, 0, 25 um 1999 Pentium III, 0, 25 um

Zašto AD? (1) – – AD = Automatized design (Design Automatization) Svjedoci smo prave “eksplozije” elektronske tehnologije. Elektronski čipovi postaju sve složeniji i sve manjih dimenzija. Cjelokupan uredjaj treba biti realizovan na jednom čipu, system on chip. – Put od ideje do realizacije proizvoda mora biti što kraći. Neki od čipova visoke koncetracije

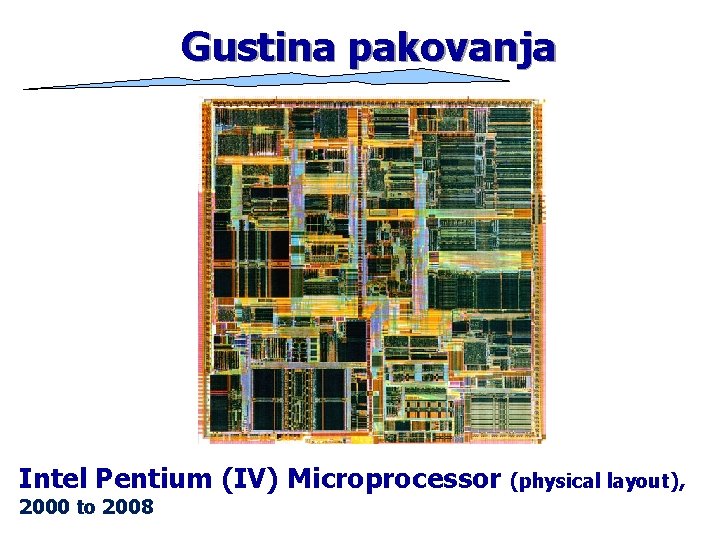

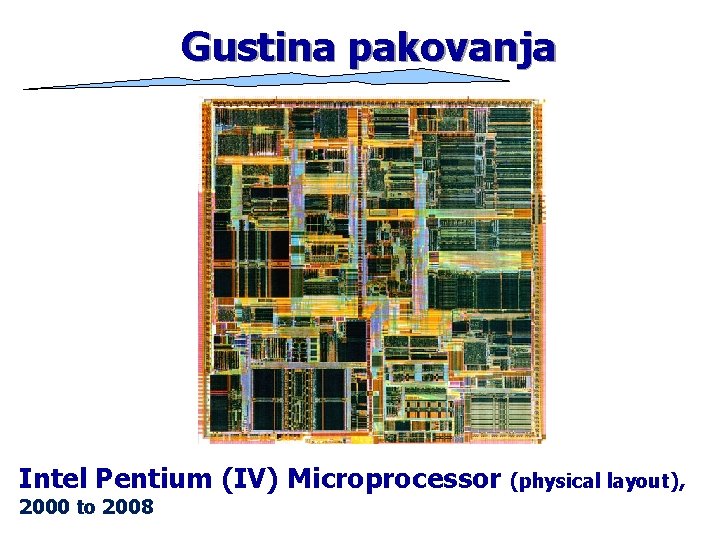

Gustina pakovanja Intel Pentium (IV) Microprocessor 2000 to 2008 (physical layout),

Ekonomski aspekti EDA

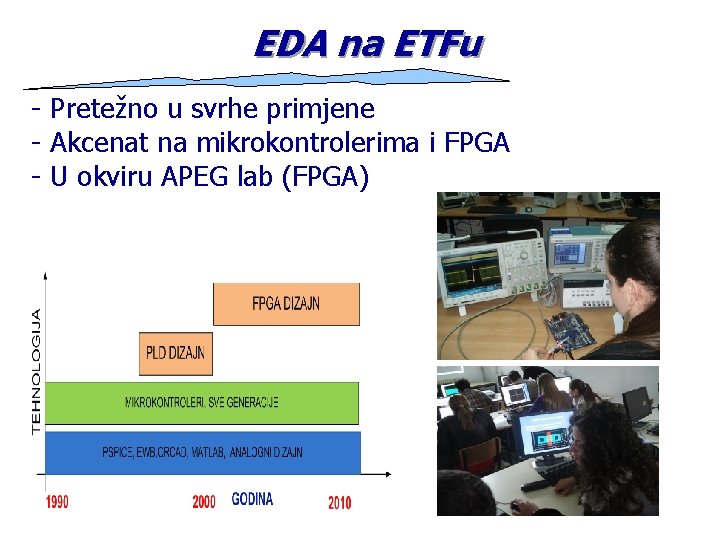

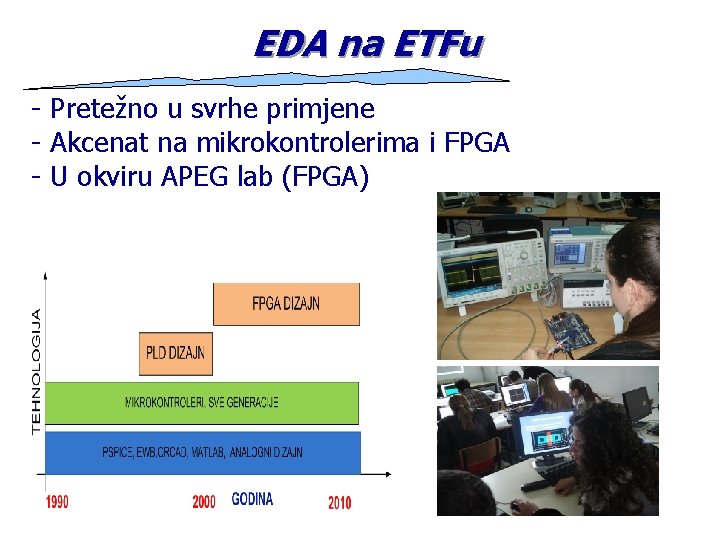

EDA na ETFu - Pretežno u svrhe primjene - Akcenat na mikrokontrolerima i FPGA - U okviru APEG lab (FPGA)

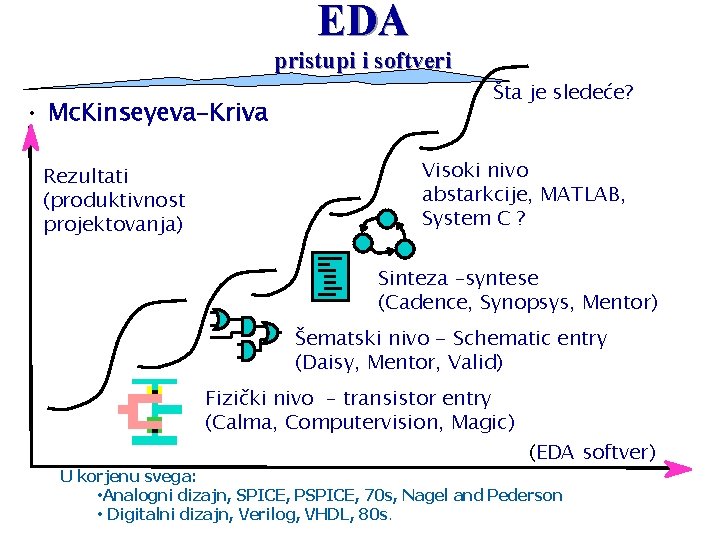

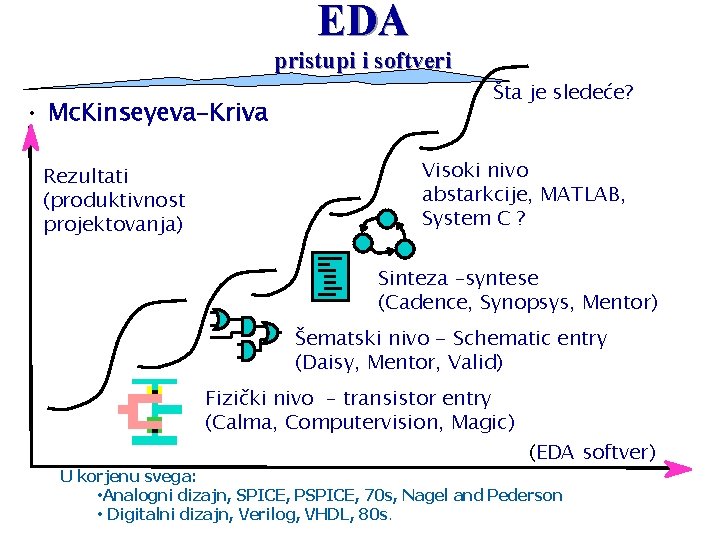

EDA pristupi i softveri • Mc. Kinseyeva-Kriva Rezultati (produktivnost projektovanja) Šta je sledeće? Visoki nivo abstarkcije, MATLAB, System C ? Sinteza –syntese (Cadence, Synopsys, Mentor) Šematski nivo - Schematic entry (Daisy, Mentor, Valid) Fizički nivo – transistor entry (Calma, Computervision, Magic) (EDA softver) U korjenu svega: • Analogni dizajn, SPICE, PSPICE, 70 s, Nagel and Pederson • Digitalni dizajn, Verilog, VHDL, 80 s.

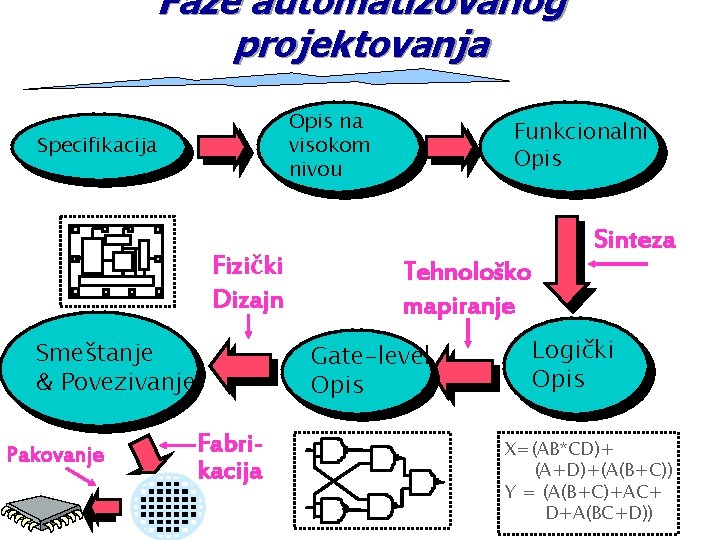

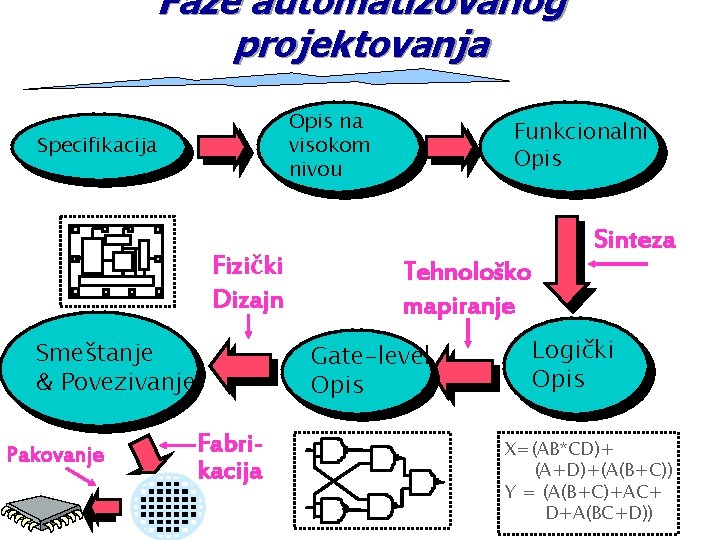

Faze automatizovanog projektovanja Opis na visokom nivou Specifikacija Fizički Dizajn Smeštanje & Povezivanje Pakovanje Funkcionalni Opis Sinteza Tehnološko mapiranje Gate-level Opis Fabrikacija Logički Opis X=(AB*CD)+ (A+D)+(A(B+C)) Y = (A(B+C)+AC+ D+A(BC+D))

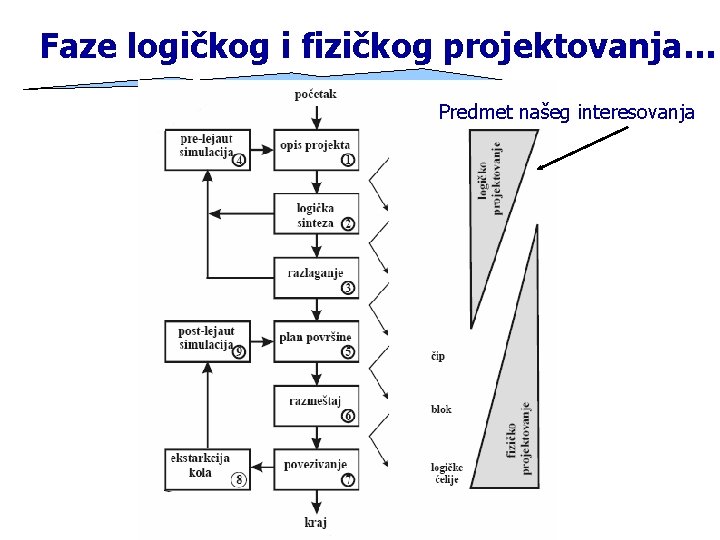

Faze logičkog i fizičkog projektovanja… Predmet našeg interesovanja

Tok projektovanja - “Design flow” 1 Design Entry direktno šema ili unošenje programa (koda), VHDL, and/or Verilog. Implementation Analiza, simulacija, tajmming. 2 3 Download direktno u čipove, pomoću ISP ili programatora XC 4000

“Design flow…” – naši primjeri FPGA kolo za racunanje kvadratnog korjena FPGA VGA kontroler Od ideje do realizacije, radovi studenata

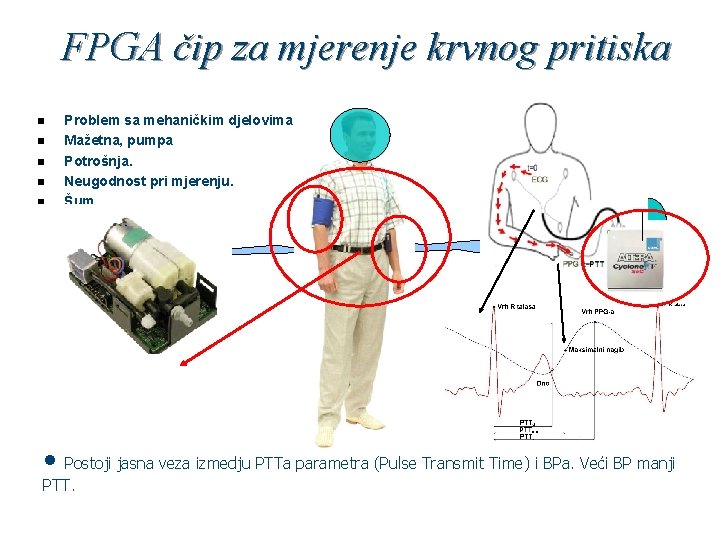

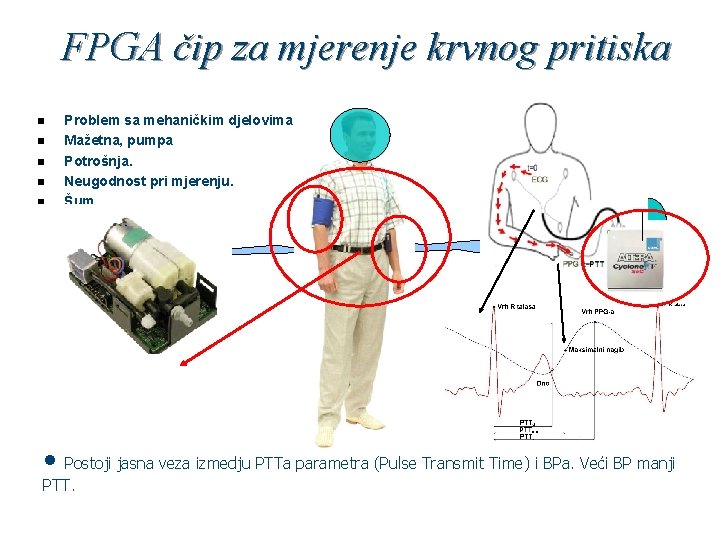

FPGA čip za mjerenje krvnog pritiska n n n • Problem sa mehaničkim djelovima, Mažetna, pumpa Potrošnja. Neugodnost pri mjerenju. Šum Postoji jasna veza izmedju PTTa parametra (Pulse Transmit Time) i BPa. Veći BP manji PTT.

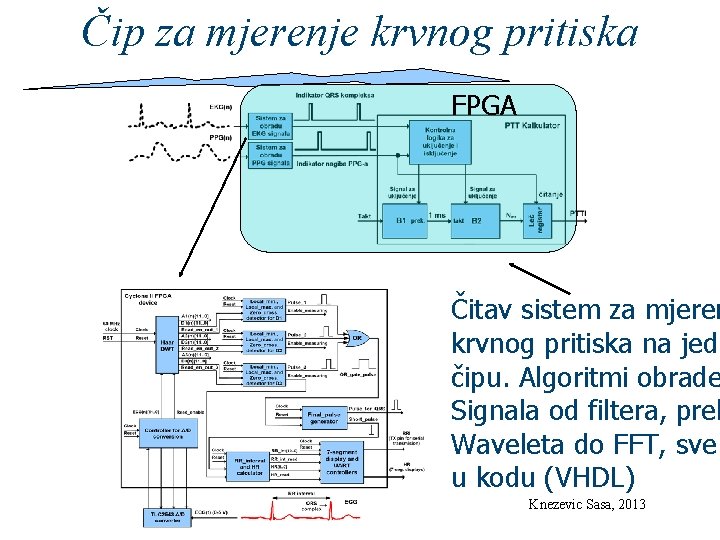

Čip za mjerenje krvnog pritiska FPGA Čitav sistem za mjeren krvnog pritiska na jedn čipu. Algoritmi obrade Signala od filtera, prek Waveleta do FFT, sve u kodu (VHDL) Knezevic Sasa, 2013

2. VHDL

Osnove • Šta je VHDL? • • • VHDL je internacionalni IEEE standardizovan jezik (IEEE 1076 -1993) za opis elektronskog hardvera. VHDL je akronim za VHSIC (Very High Speed Integrated Circuit) Hardware Description Language VHDL je jezik visokog nivoa abstrakcije (slično C-u, Paskalu, itd) • VHDL filozofija Maximalno tačan i pouzdan dizajn uz najmanju cijenu koštanja u najkraćem roku razvijanja.

Istorija • Ideja 1980. • 1981 prve konkretne aktivnosti. • U julu 1983 IBM i Texas Instruments potpisali Ugovor o razvijanju VHDL-a • U avgustu 1985 završena VHDL version 7. 2. • U decembru 1987 VHDL postaje IEEE standard 1076 -1987 i 1988 ANSI standard. • U septembru 1993 VHDL je re-standardizovan, VHDL-1993.

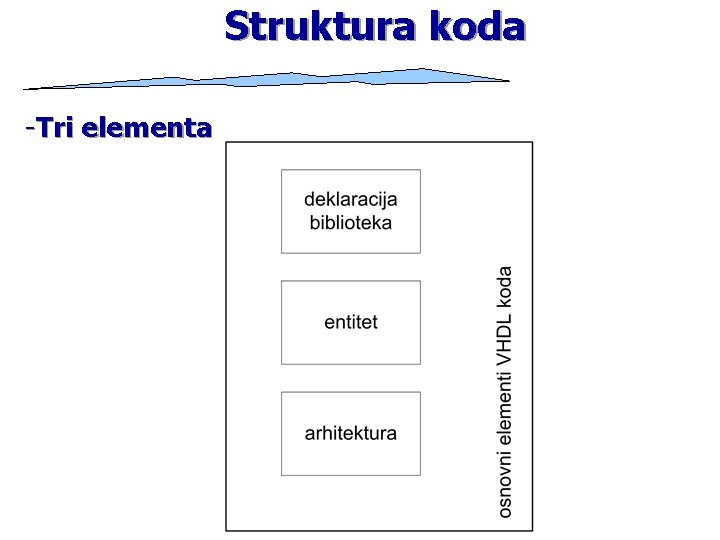

Struktura koda -Tri elementa

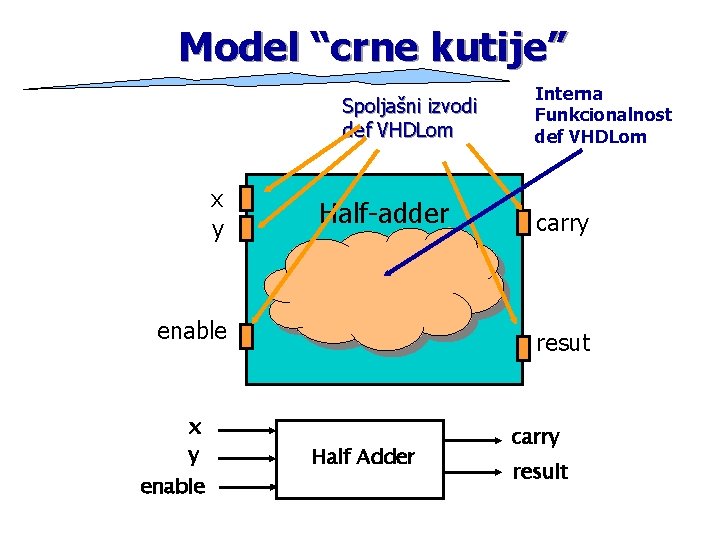

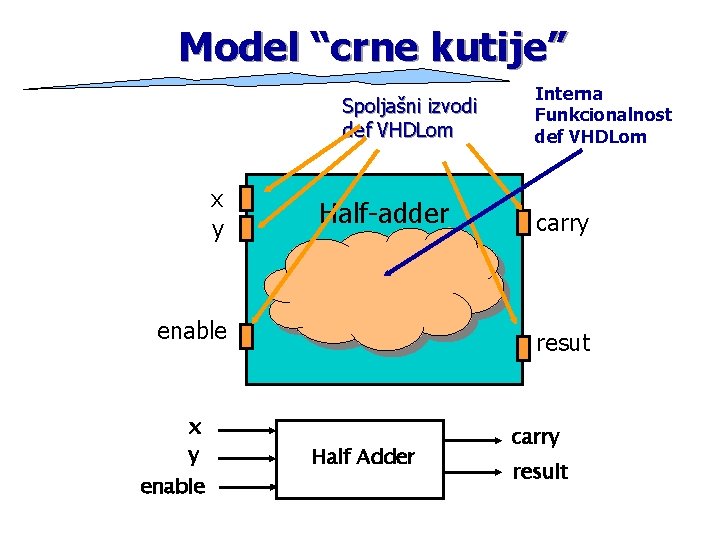

Model “crne kutije” Spoljašni izvodi def VHDLom x y Half-adder enable x y enable Interna Funkcionalnost def VHDLom carry resut Half Adder carry result

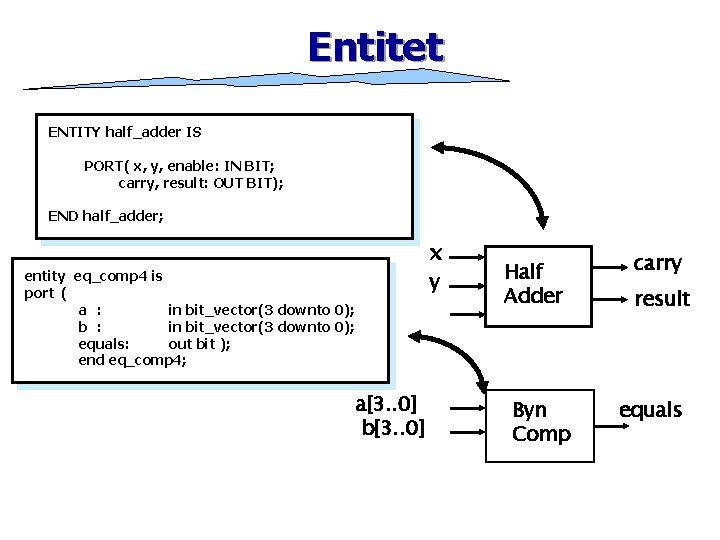

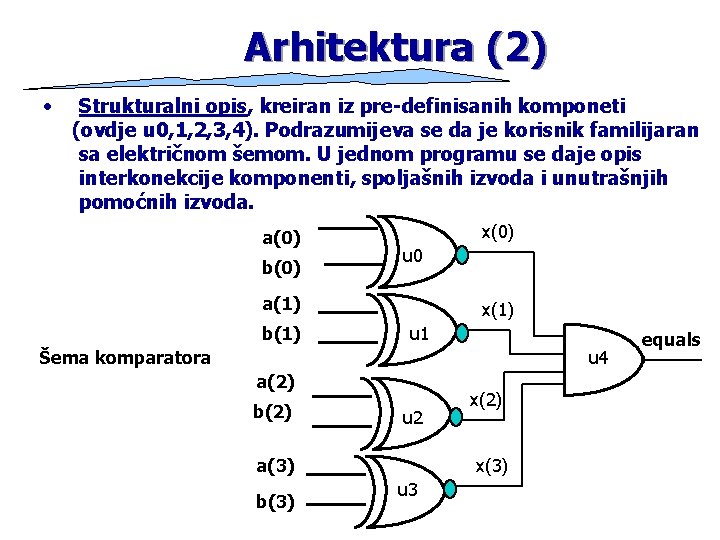

Entitet ENTITY half_adder IS PORT( x, y, enable: IN BIT; carry, result: OUT BIT); END half_adder; entity eq_comp 4 is port ( a : in bit_vector(3 downto 0); b : in bit_vector(3 downto 0); equals: out bit ); end eq_comp 4; a[3. . 0] b[3. . 0] x y Half Adder Byn Comp carry result equals

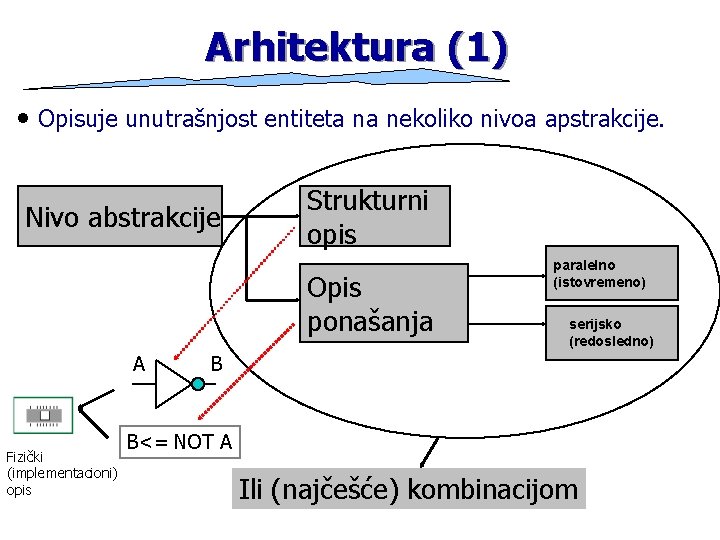

Arhitektura (1) • Opisuje unutrašnjost entiteta na nekoliko nivoa apstrakcije. Nivo abstrakcije Strukturni opis Opis ponašanja A Fizički (implementacioni) opis paralelno (istovremeno) serijsko (redosledno) B B<= NOT A Ili (najčešće) kombinacijom

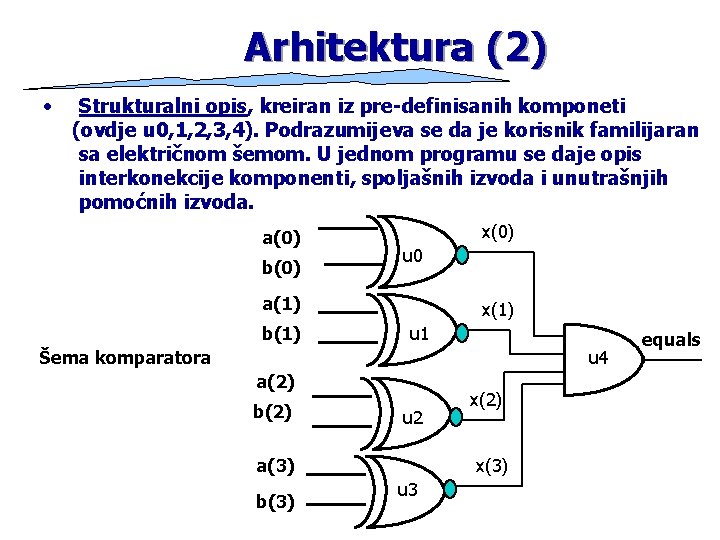

Arhitektura (2) • Strukturalni opis, kreiran iz pre-definisanih komponeti (ovdje u 0, 1, 2, 3, 4). Podrazumijeva se da je korisnik familijaran sa električnom šemom. U jednom programu se daje opis interkonekcije komponenti, spoljašnih izvoda i unutrašnjih pomoćnih izvoda. a(0) b(0) x(0) u 0 a(1) b(1) x(1) u 1 Šema komparatora u 4 a(2) b(2) u 2 a(3) b(3) x(2) x(3) u 3 equals

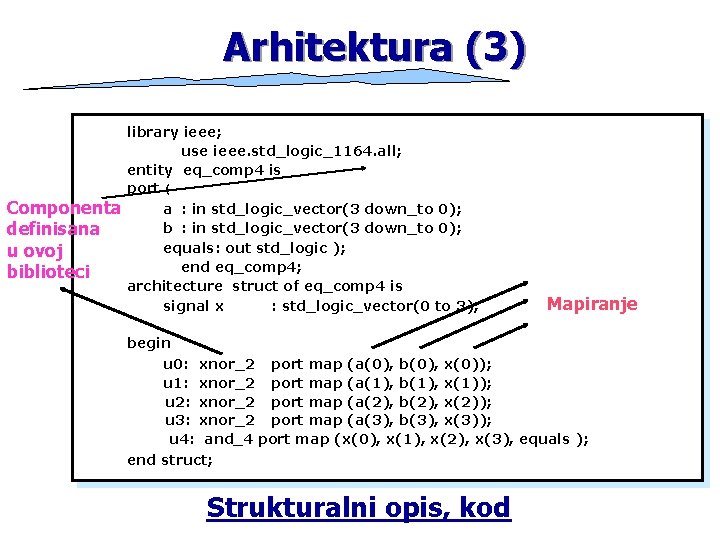

Arhitektura (3) Componenta definisana u ovoj biblioteci library ieee; use ieee. std_logic_1164. all; entity eq_comp 4 is port ( a : in std_logic_vector(3 down_to 0); b : in std_logic_vector(3 down_to 0); equals: out std_logic ); end eq_comp 4; architecture struct of eq_comp 4 is signal x : std_logic_vector(0 to 3); Mapiranje begin u 0: xnor_2 port map (a(0), b(0), x(0)); u 1: xnor_2 port map (a(1), b(1), x(1)); u 2: xnor_2 port map (a(2), b(2), x(2)); u 3: xnor_2 port map (a(3), b(3), x(3)); u 4: and_4 port map (x(0), x(1), x(2), x(3), equals ); end struct; Strukturalni opis, kod

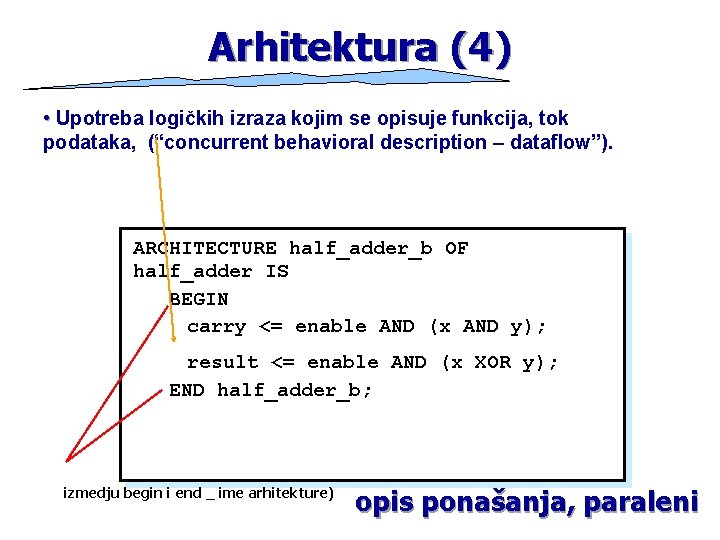

Arhitektura (4) • Upotreba logičkih izraza kojim se opisuje funkcija, tok podataka, (“concurrent behavioral description – dataflow”). ARCHITECTURE half_adder_b OF half_adder IS BEGIN carry <= enable AND (x AND y); result <= enable AND (x XOR y); END half_adder_b; izmedju begin i end _ ime arhitekture) opis ponašanja, paraleni

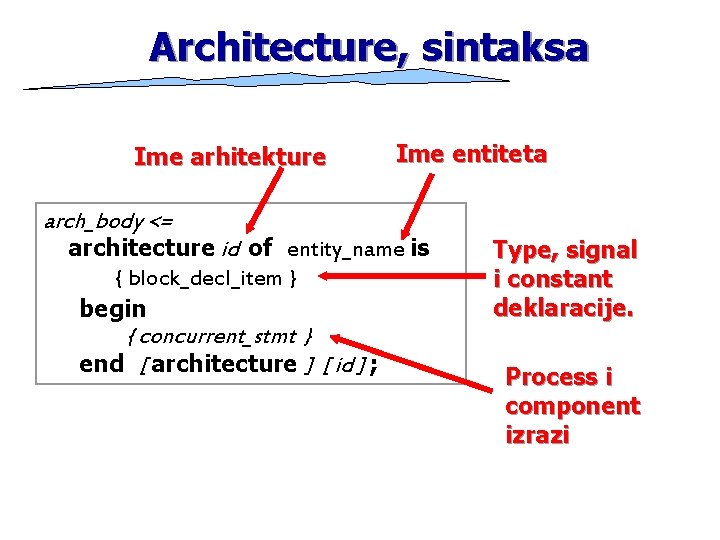

Arhitektura (5) • U formi izraza koji se redosledno izvršavaju, (“sequential behavioral”). Ti izrazi mogu biti i konstrukcije kao što su “if”, “case”, “loop”, “for”, and “while”. Sve se odigrava unutar “process” sekvence, može biti više procesa. ARCHITECTURE half_adder_a OF half_adder IS BEGIN PROCESS (x, y, enable) BEGIN IF enable = ‘ 1’ THEN result <= x XOR y; carry <= x AND y; ELSE carry <= ‘ 0’; result <= ‘ 0’; END IF; END PROCESS; END half_adder_a; opis ponašanja, serijski

![Entity sintaksa entityname is generics ports declarations types constants signals definitions functions procedures begin Entity, sintaksa entity_name is [generics] [ports] [declarations (types, constants, signals)] [definitions (functions, procedures)] [begin](https://slidetodoc.com/presentation_image_h2/911241d46073b6051f3588afb6d9b140/image-41.jpg)

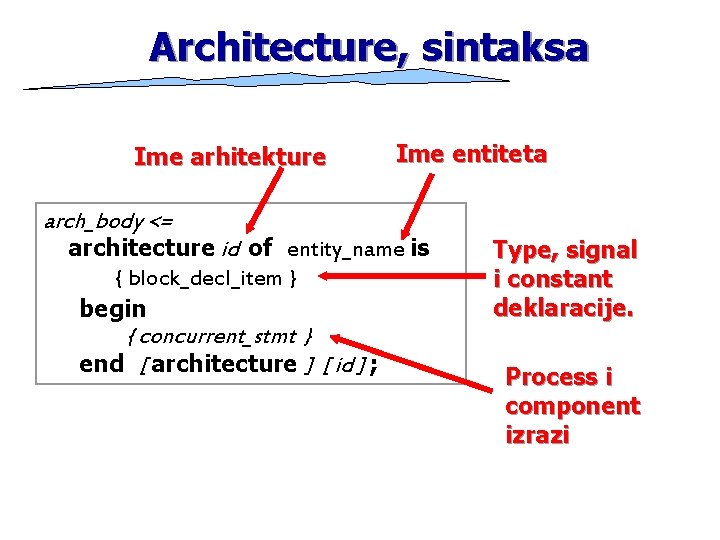

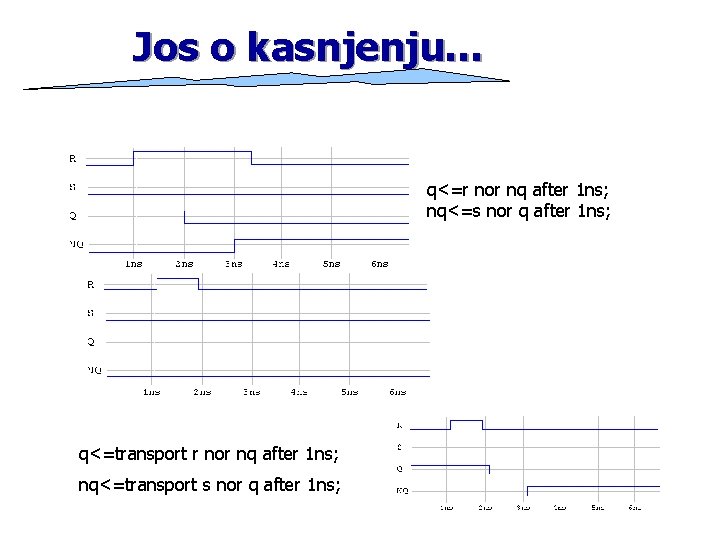

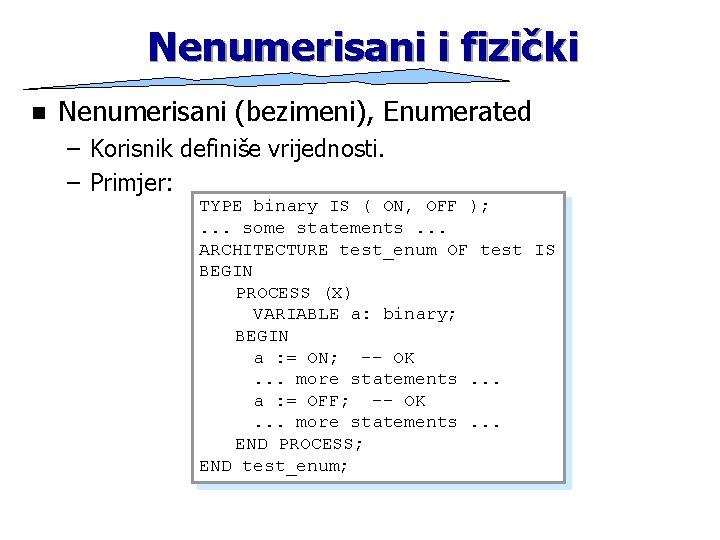

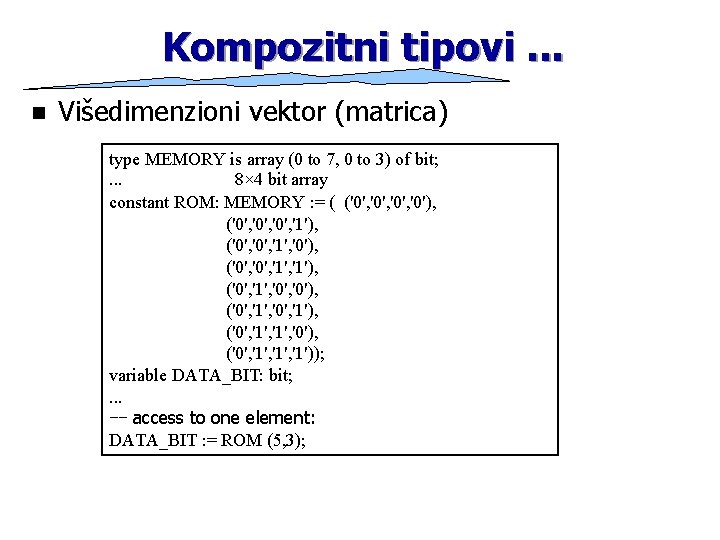

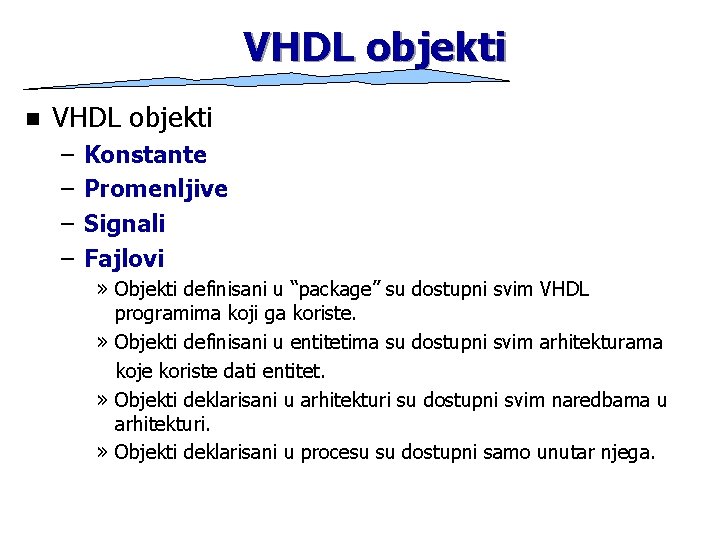

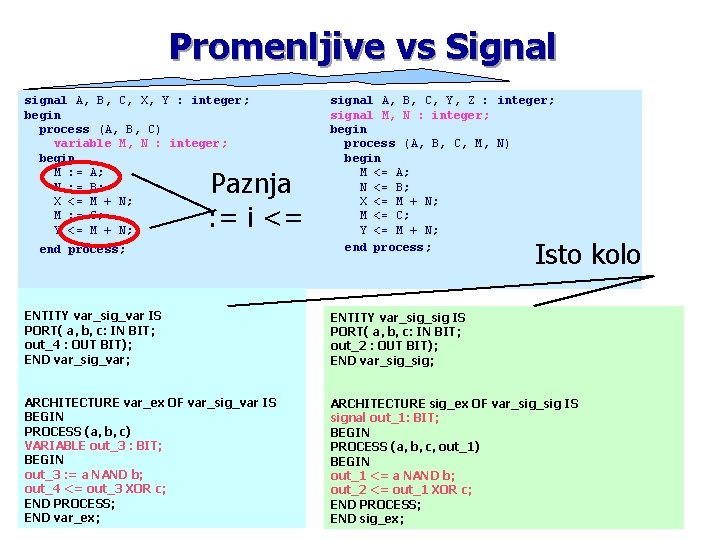

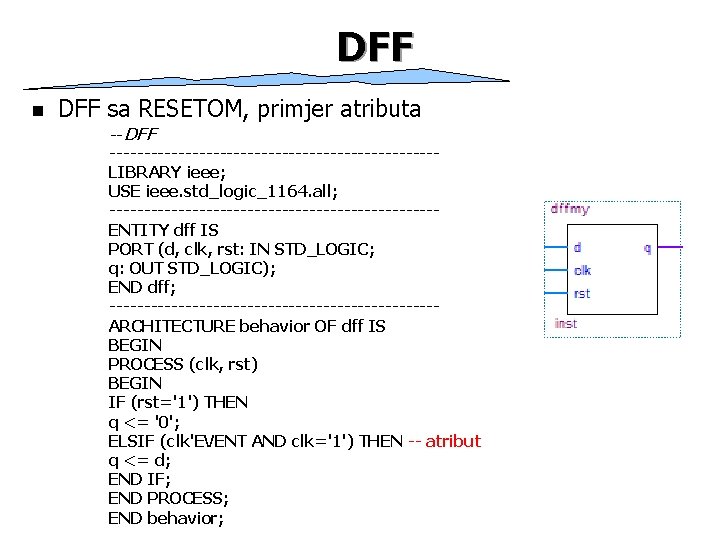

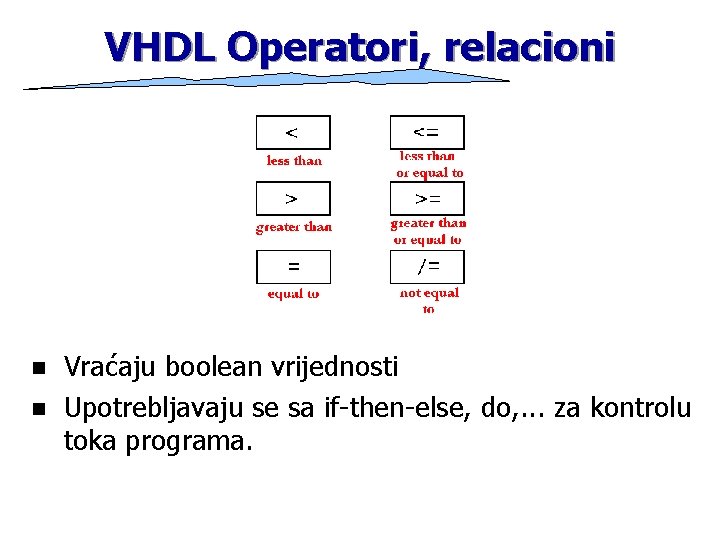

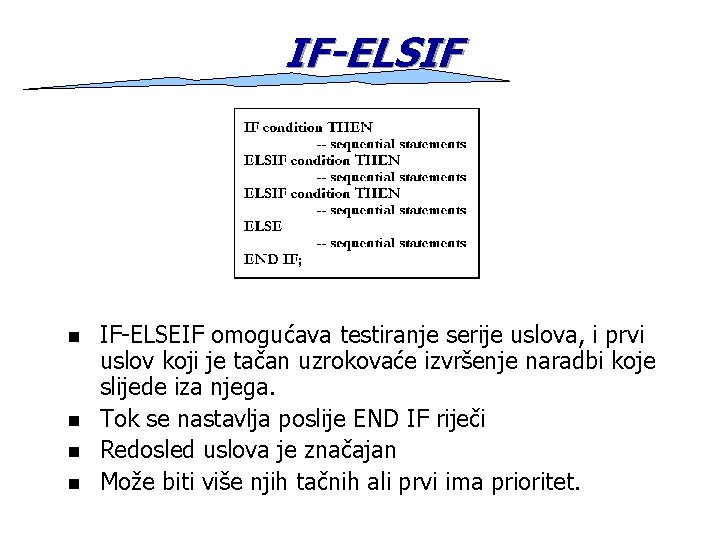

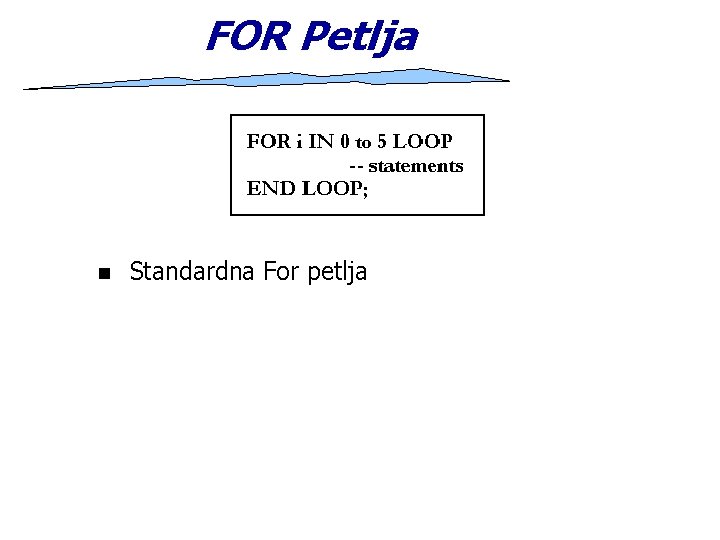

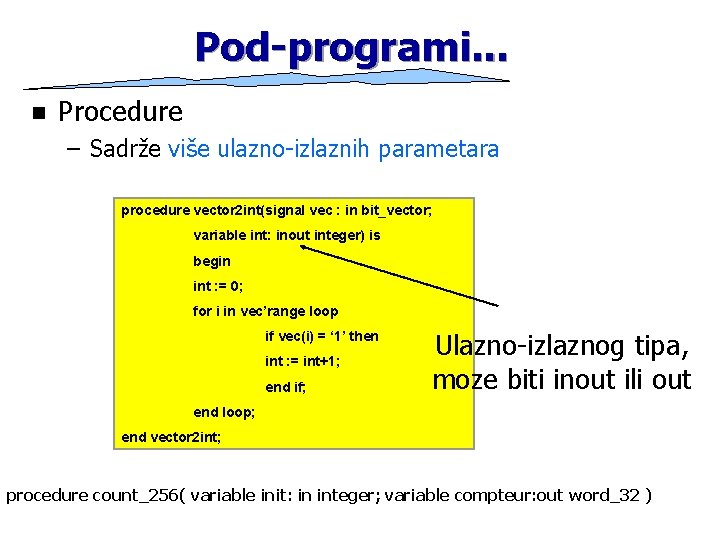

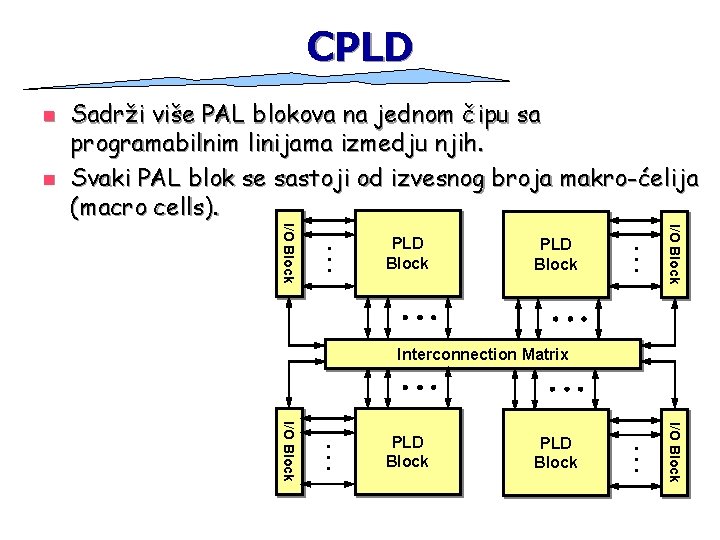

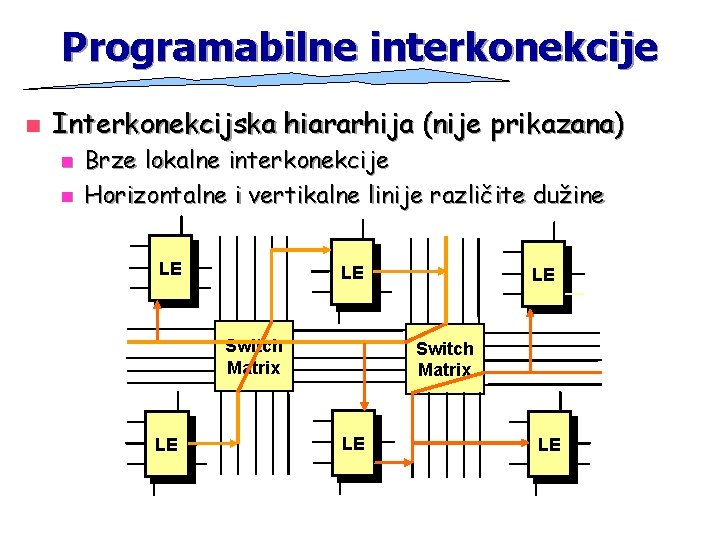

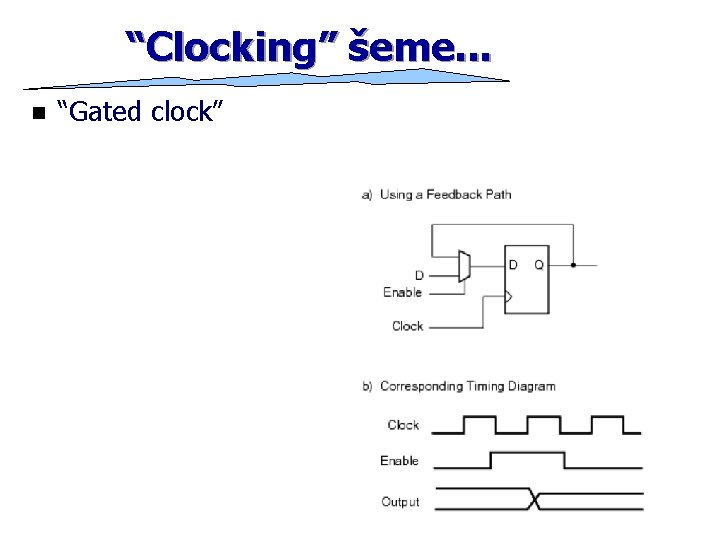

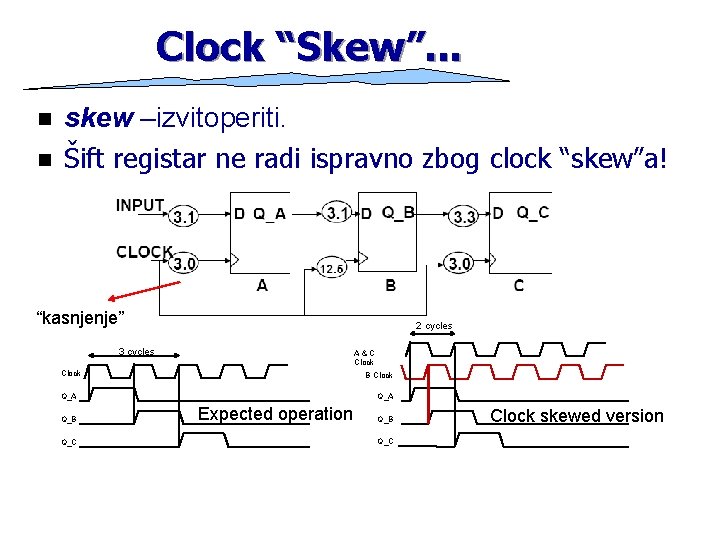

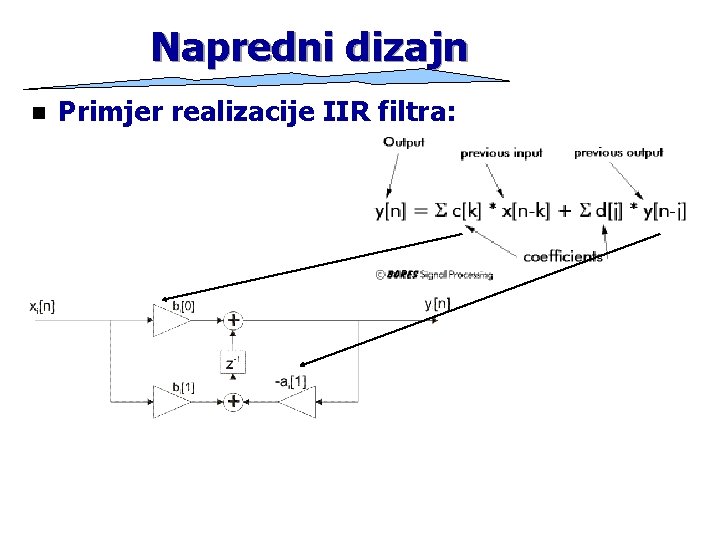

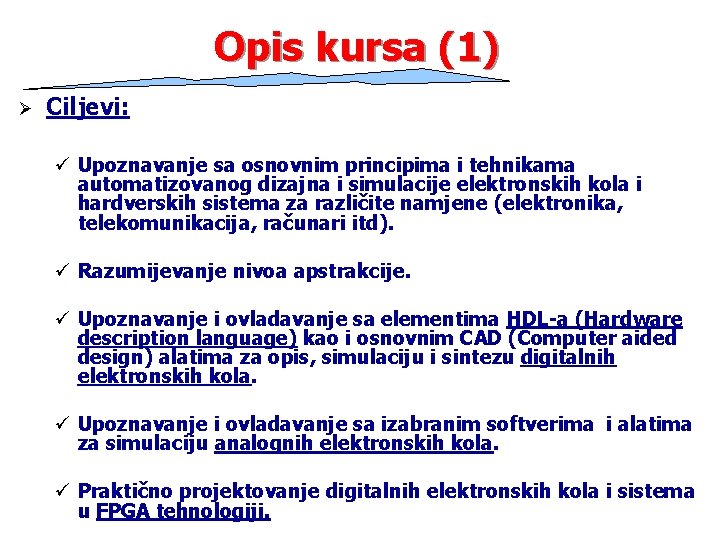

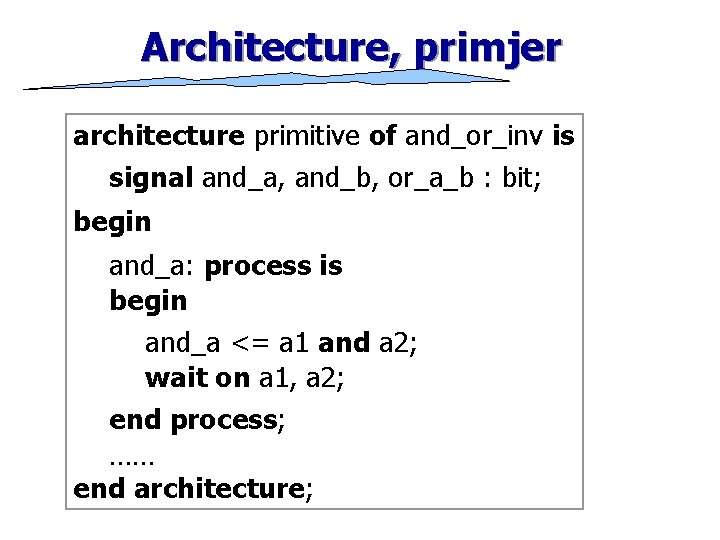

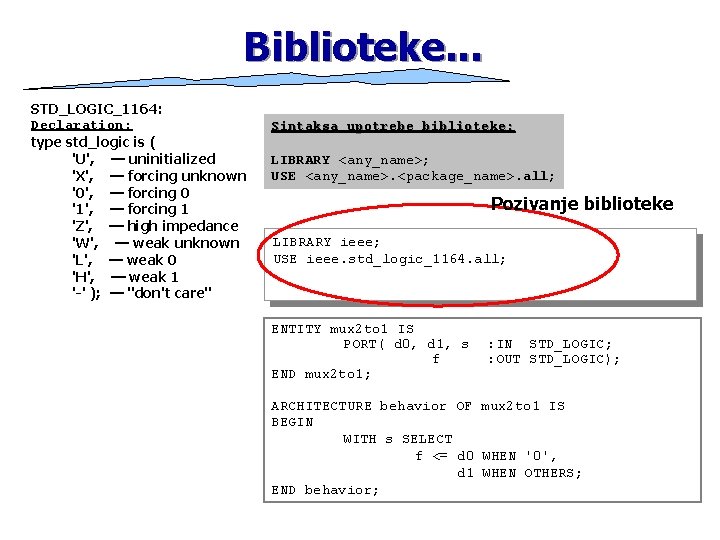

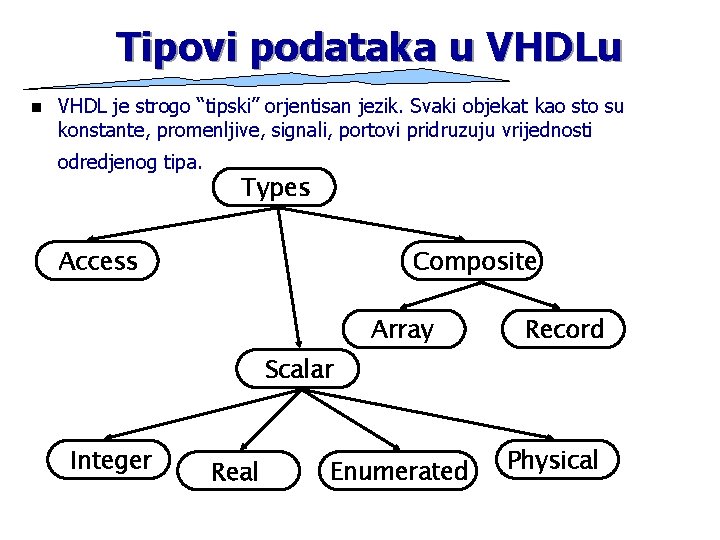

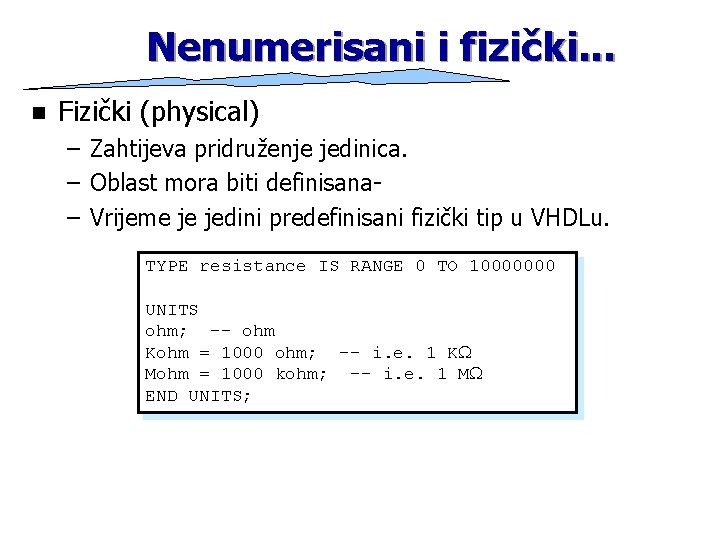

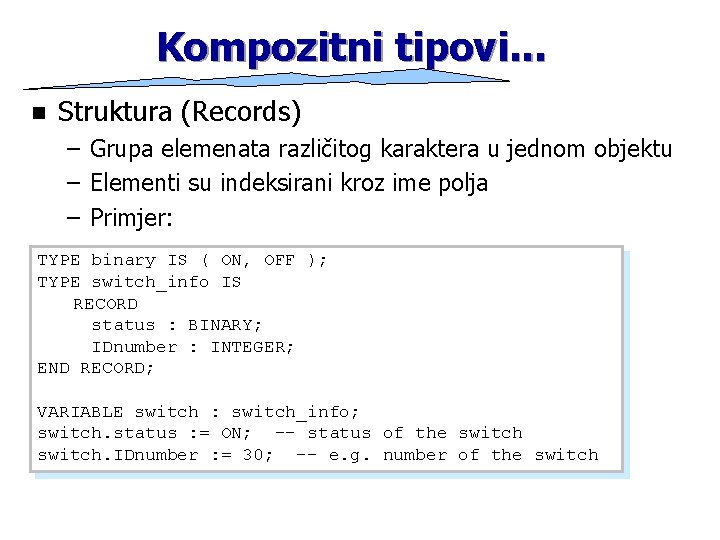

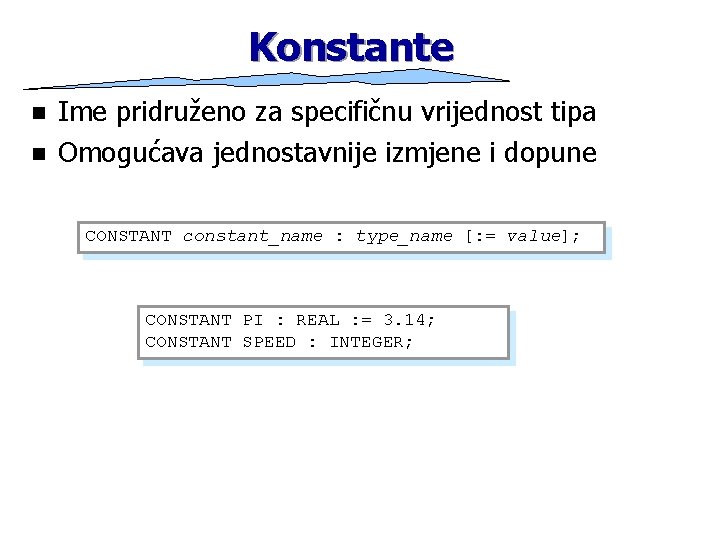

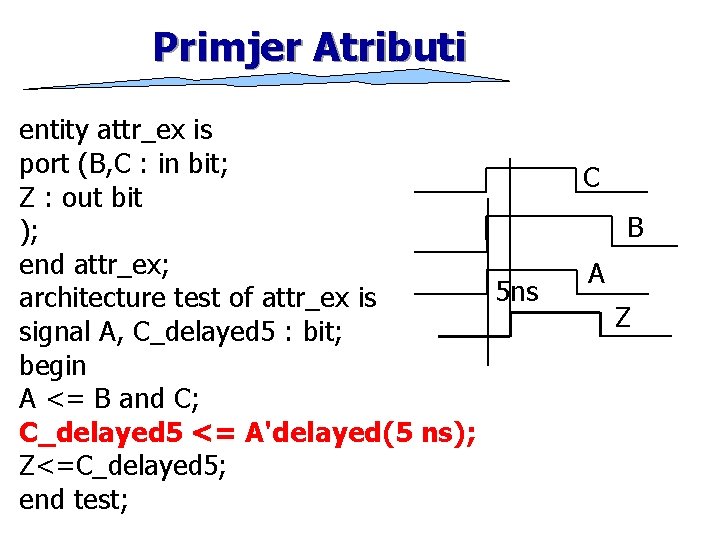

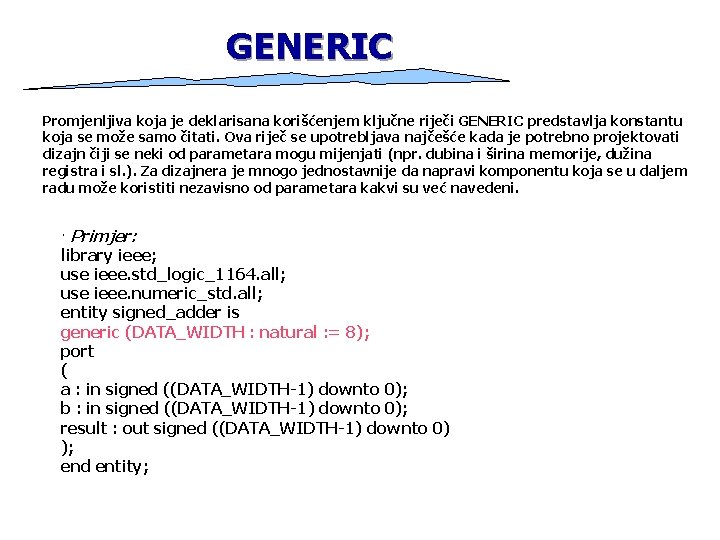

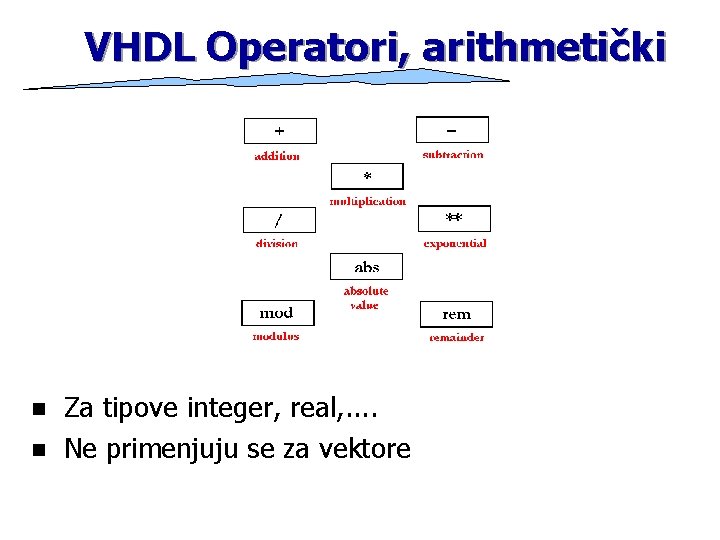

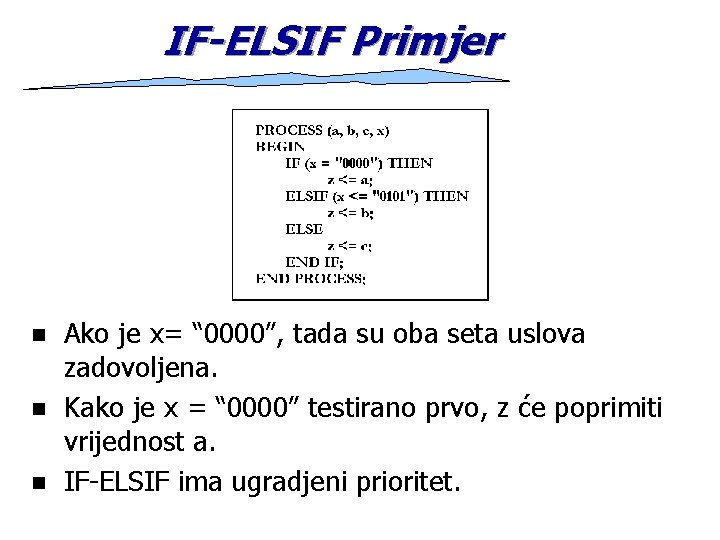

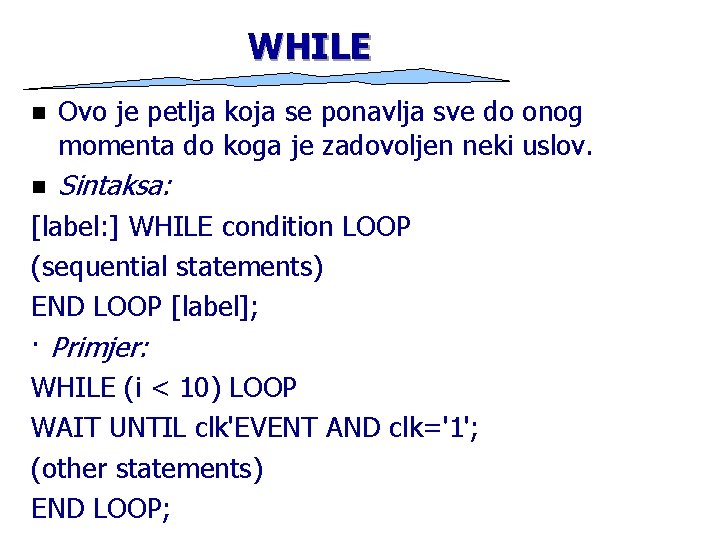

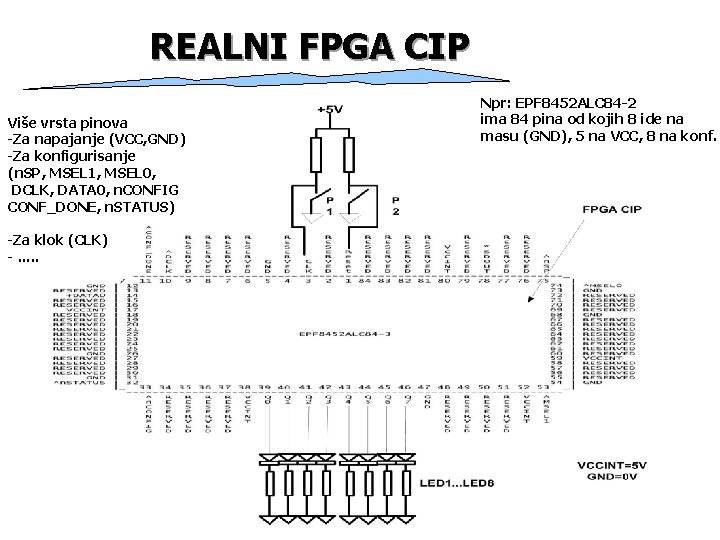

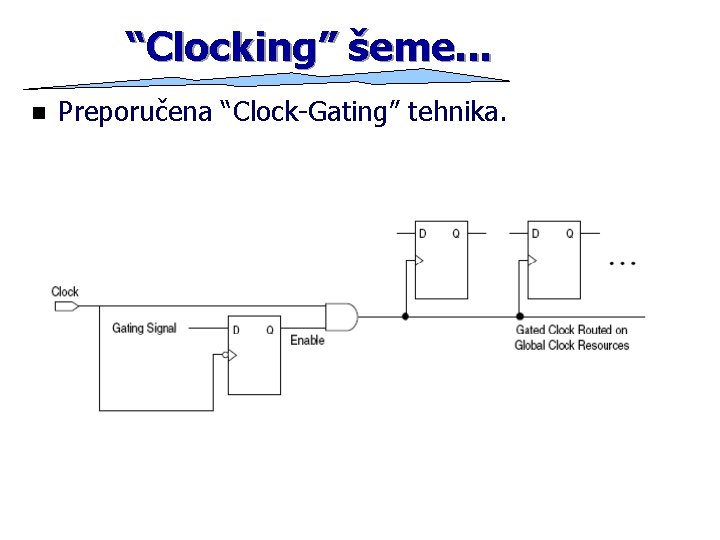

Entity, sintaksa entity_name is [generics] [ports] [declarations (types, constants, signals)] [definitions (functions, procedures)] [begin statements] – ne upotrebljava se end [entity_name]; Sintaksa u širem smislu entity program_rom is port ( address : in bit_vector (14 downto 0) ; data : out bit_vector (7 downto 0) ; enable : in bit ); subtype instruction_byte is bit_vector (7 downto 0); type program is array (0 to 2**14 -1) of instruction_byte; end entity program_rom; Samo type deklaracija, signal deklaracija i konstante, ne variable.

Architecture, sintaksa Ime arhitekture arch_body <= Ime entiteta architecture id of entity_name is { block_decl_item } begin { concurrent_stmt } end [ architecture ] [ id ] ; Type, signal i constant deklaracije. Process i component izrazi

Architecture, primjer architecture primitive of and_or_inv is signal and_a, and_b, or_a_b : bit; begin and_a: process is begin and_a <= a 1 and a 2; wait on a 1, a 2; end process; …… end architecture;

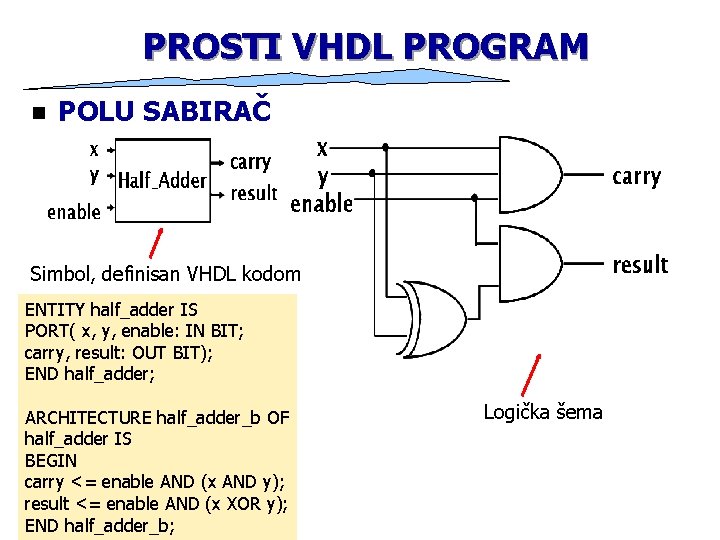

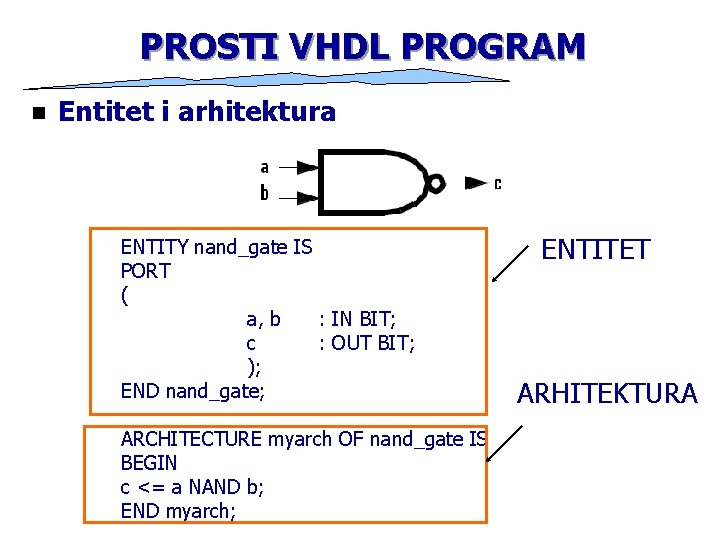

PROSTI VHDL PROGRAM n Entitet i arhitektura ENTITY nand_gate IS PORT ( a, b : IN BIT; c : OUT BIT; ); END nand_gate; ARCHITECTURE myarch OF nand_gate IS BEGIN c <= a NAND b; END myarch; ENTITET ARHITEKTURA

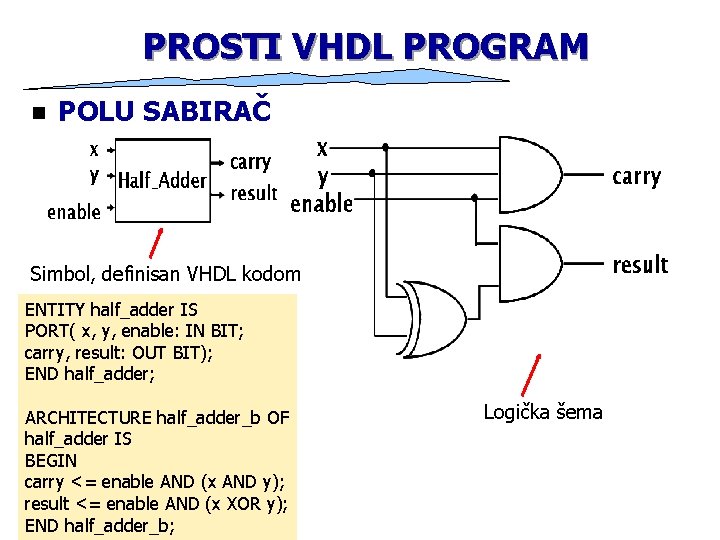

PROSTI VHDL PROGRAM n POLU SABIRAČ Simbol, definisan VHDL kodom ENTITY half_adder IS PORT( x, y, enable: IN BIT; carry, result: OUT BIT); END half_adder; ARCHITECTURE half_adder_b OF half_adder IS BEGIN carry <= enable AND (x AND y); result <= enable AND (x XOR y); END half_adder_b; Logička šema

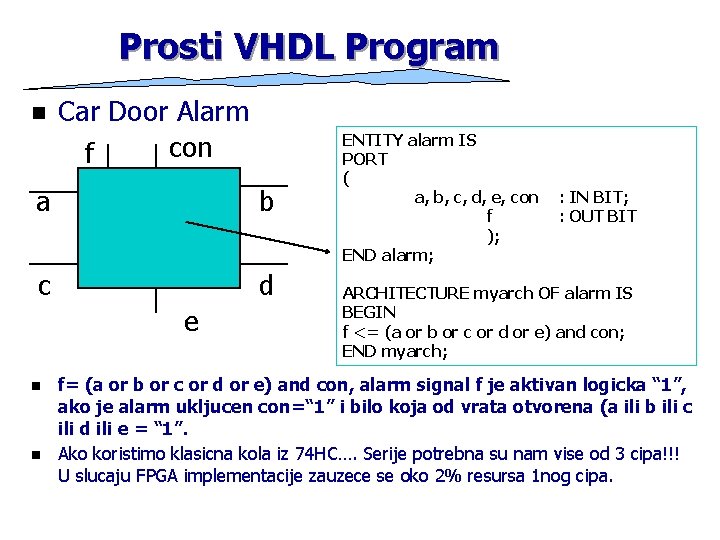

Prosti VHDL Program n Car Door Alarm con f a b c d e n n ENTITY alarm IS PORT ( a, b, c, d, e, con f ); END alarm; : IN BIT; : OUT BIT ARCHITECTURE myarch OF alarm IS BEGIN f <= (a or b or c or d or e) and con; END myarch; f= (a or b or c or d or e) and con, alarm signal f je aktivan logicka “ 1”, ako je alarm ukljucen con=“ 1” i bilo koja od vrata otvorena (a ili b ili c ili d ili e = “ 1”. Ako koristimo klasicna kola iz 74 HC…. Serije potrebna su nam vise od 3 cipa!!! U slucaju FPGA implementacije zauzece se oko 2% resursa 1 nog cipa.

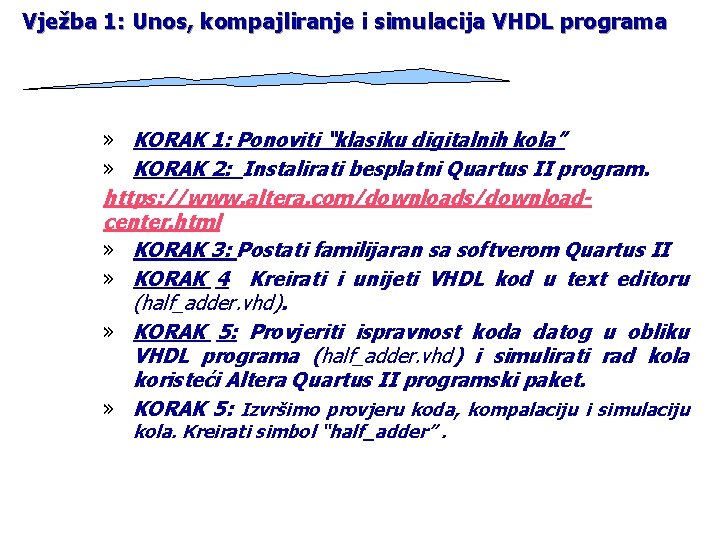

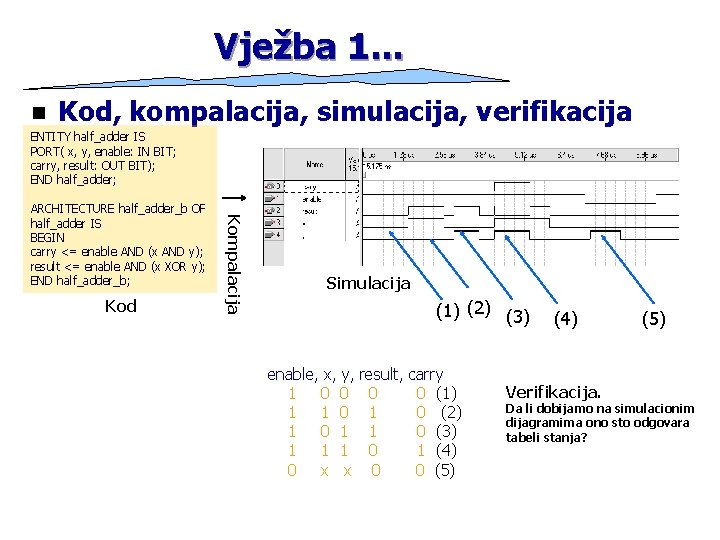

Vježba 1: Unos, kompajliranje i simulacija VHDL programa » KORAK 1: Ponoviti “klasiku digitalnih kola” » KORAK 2: Instalirati besplatni Quartus II program. https: //www. altera. com/downloads/downloadcenter. html » KORAK 3: Postati familijaran sa softverom Quartus II » KORAK 4 Kreirati i unijeti VHDL kod u text editoru (half_adder. vhd). » KORAK 5: Provjeriti ispravnost koda datog u obliku VHDL programa (half_adder. vhd) i simulirati rad kola koristeći Altera Quartus II programski paket. » KORAK 5: Izvršimo provjeru koda, kompalaciju i simulaciju kola. Kreirati simbol “half_adder”.

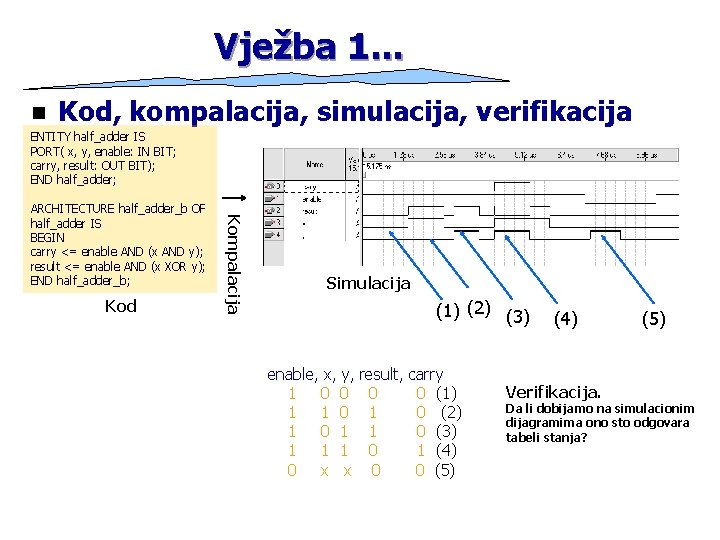

Vježba 1. . . n Kod, kompalacija, simulacija, verifikacija ENTITY half_adder IS PORT( x, y, enable: IN BIT; carry, result: OUT BIT); END half_adder; Kod Kompalacija ARCHITECTURE half_adder_b OF half_adder IS BEGIN carry <= enable AND (x AND y); result <= enable AND (x XOR y); END half_adder_b; Simulacija (1) (2) (3) enable, x, y, 1 0 0 1 1 0 x x result, 0 1 1 0 0 carry 0 (1) 0 (2) 0 (3) 1 (4) 0 (5) (4) Verifikacija. (5) Da li dobijamo na simulacionim dijagramima ono sto odgovara tabeli stanja?

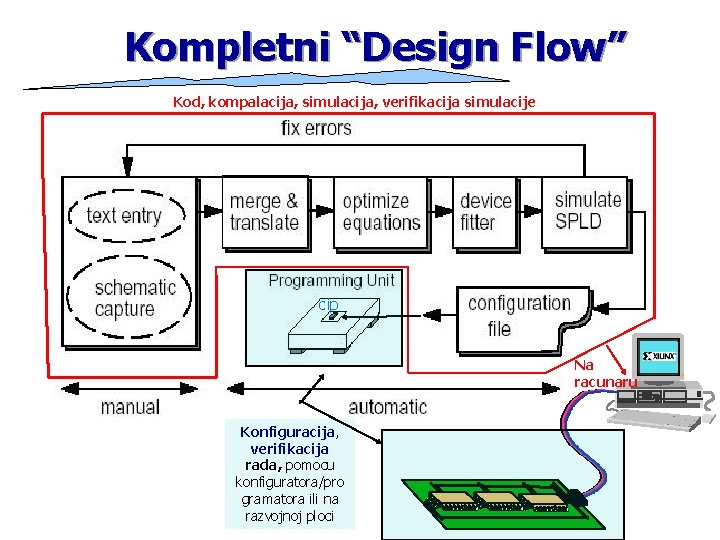

Kompletni “Design Flow” Kod, kompalacija, simulacija, verifikacija simulacije cip Na racunaru Konfiguracija, verifikacija rada, pomocu konfiguratora/pro gramatora ili na razvojnoj ploci

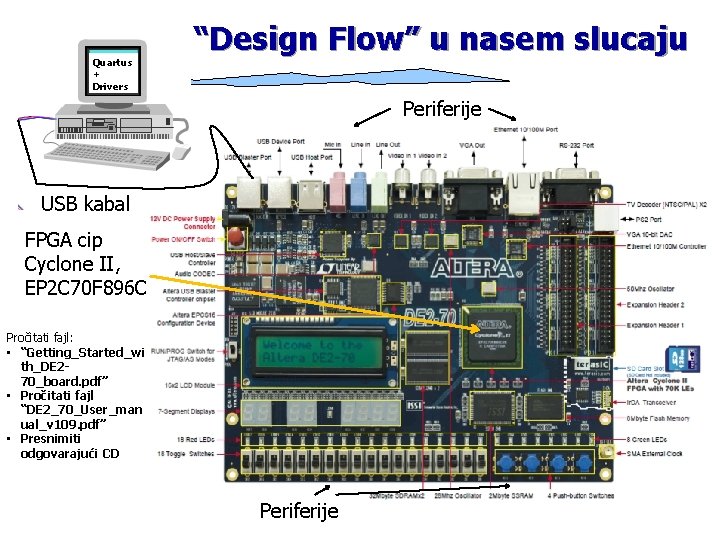

Quartus + Drivers “Design Flow” u nasem slucaju Periferije DC adapter USB kabal FPGA cip Cyclone II, EP 2 C 70 F 896 C Pročitati fajl: • “Getting_Started_wi th_DE 270_board. pdf” • Pročitati fajl “DE 2_70_User_man ual_v 109. pdf” • Presnimiti odgovarajući CD Periferije

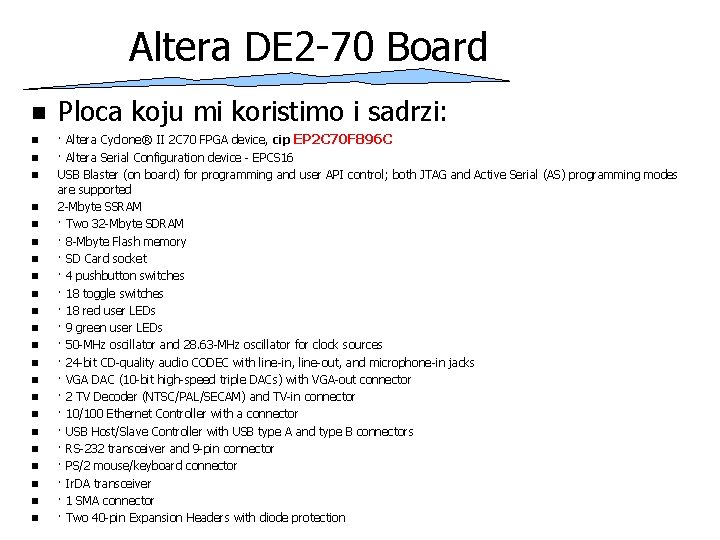

Altera DE 2 -70 Board n n n n n n Ploca koju mi koristimo i sadrzi: · Altera Cyclone® II 2 C 70 FPGA device, cip EP 2 C 70 F 896 C · Altera Serial Configuration device - EPCS 16 USB Blaster (on board) for programming and user API control; both JTAG and Active Serial (AS) programming modes are supported 2 -Mbyte SSRAM · Two 32 -Mbyte SDRAM · 8 -Mbyte Flash memory · SD Card socket · 4 pushbutton switches · 18 toggle switches · 18 red user LEDs · 9 green user LEDs · 50 -MHz oscillator and 28. 63 -MHz oscillator for clock sources · 24 -bit CD-quality audio CODEC with line-in, line-out, and microphone-in jacks · VGA DAC (10 -bit high-speed triple DACs) with VGA-out connector · 2 TV Decoder (NTSC/PAL/SECAM) and TV-in connector · 10/100 Ethernet Controller with a connector · USB Host/Slave Controller with USB type A and type B connectors · RS-232 transceiver and 9 -pin connector · PS/2 mouse/keyboard connector · Ir. DA transceiver · 1 SMA connector · Two 40 -pin Expansion Headers with diode protection

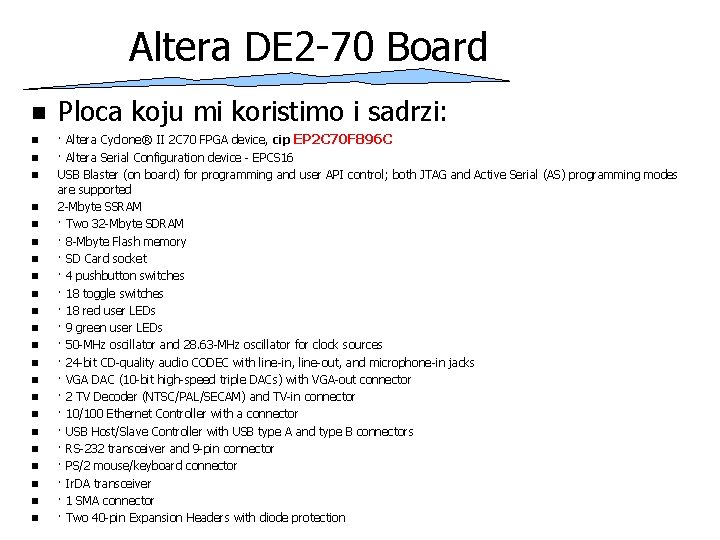

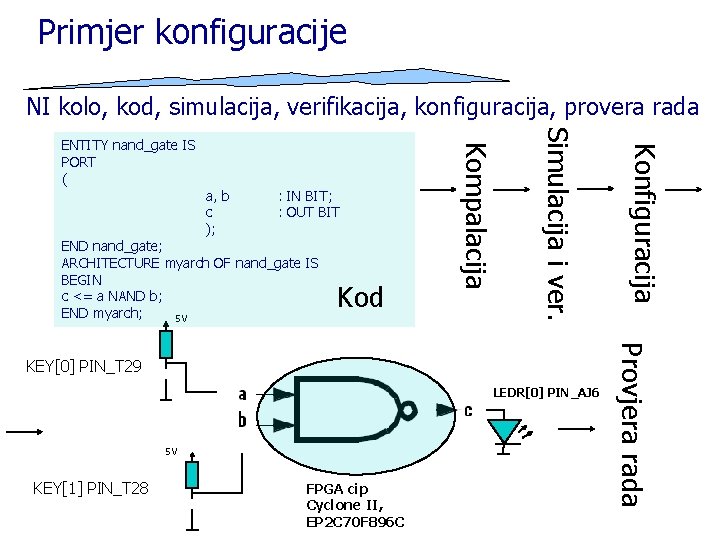

Primjer konfiguracije NI kolo, kod, simulacija, verifikacija, konfiguracija, provera rada END nand_gate; ARCHITECTURE myarch OF nand_gate IS BEGIN c <= a NAND b; END myarch; 5 V Kod LEDR[0] PIN_AJ 6 5 V KEY[1] PIN_T 28 FPGA cip Cyclone II, EP 2 C 70 F 896 C Provjera rada KEY[0] PIN_T 29 Konfiguracija : IN BIT; : OUT BIT Simulacija i ver. a, b c ); Kompalacija ENTITY nand_gate IS PORT (

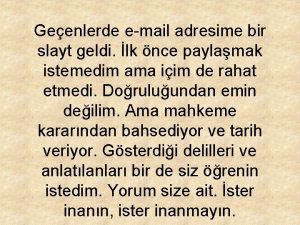

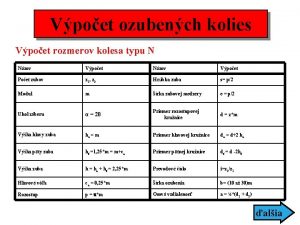

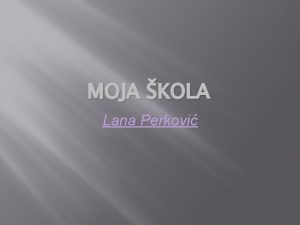

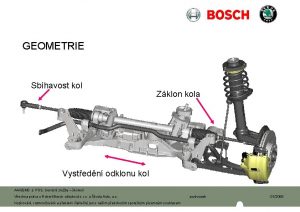

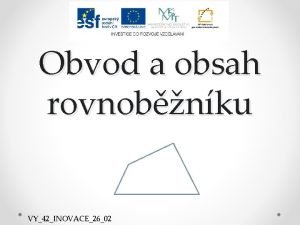

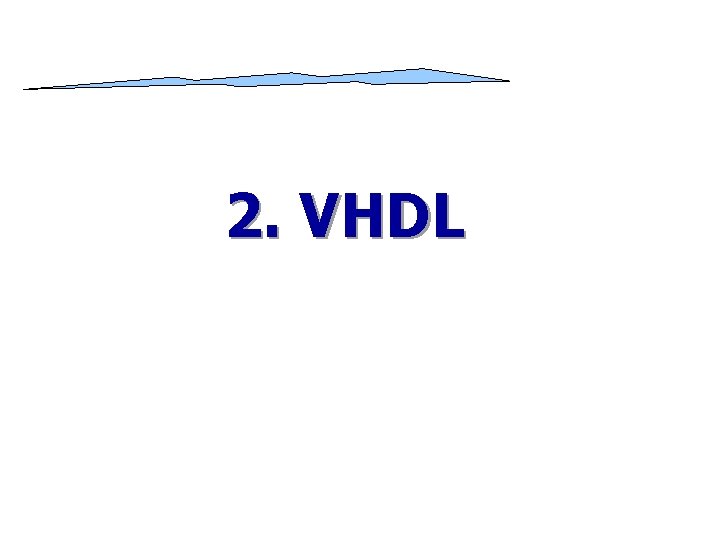

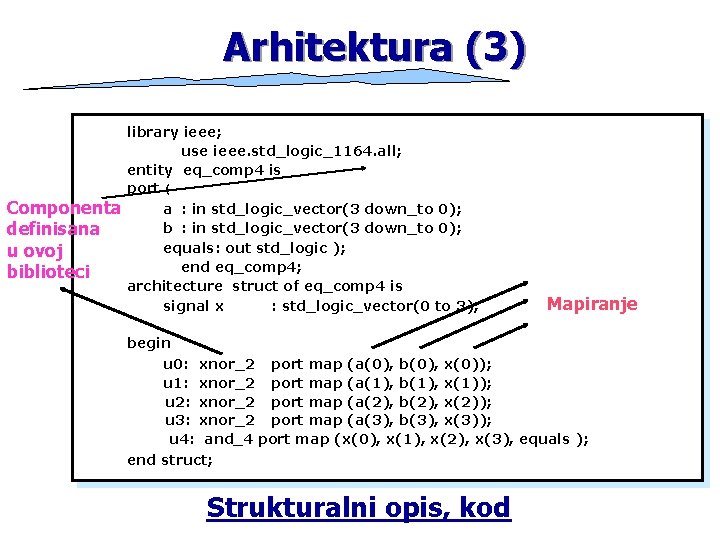

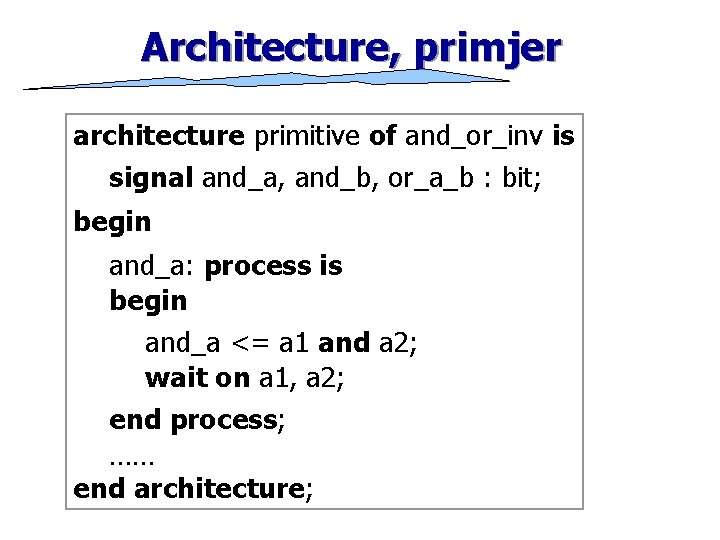

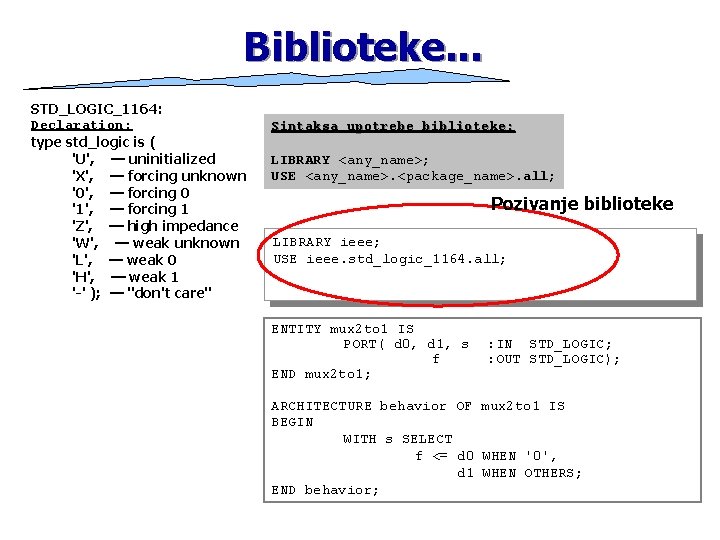

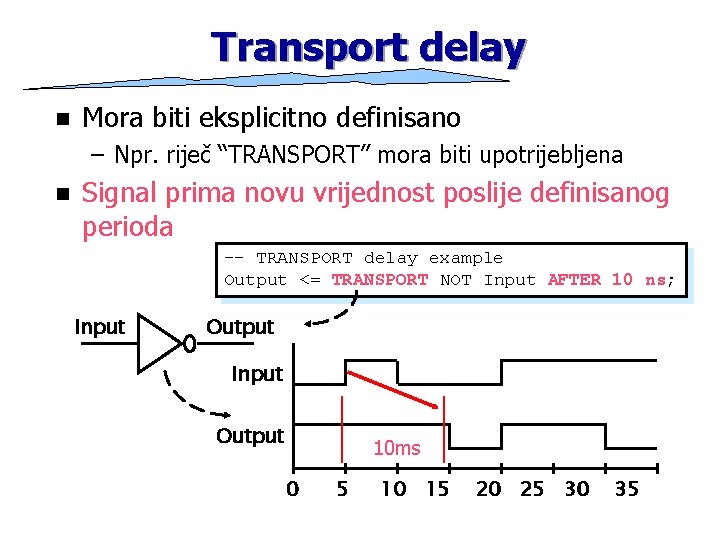

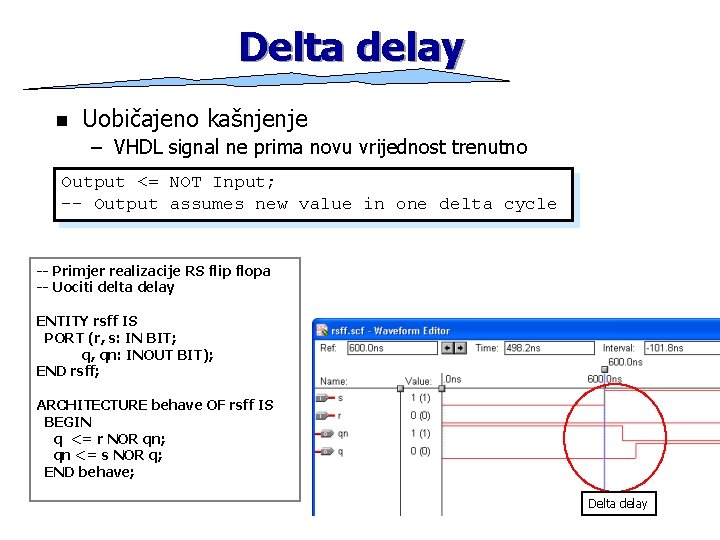

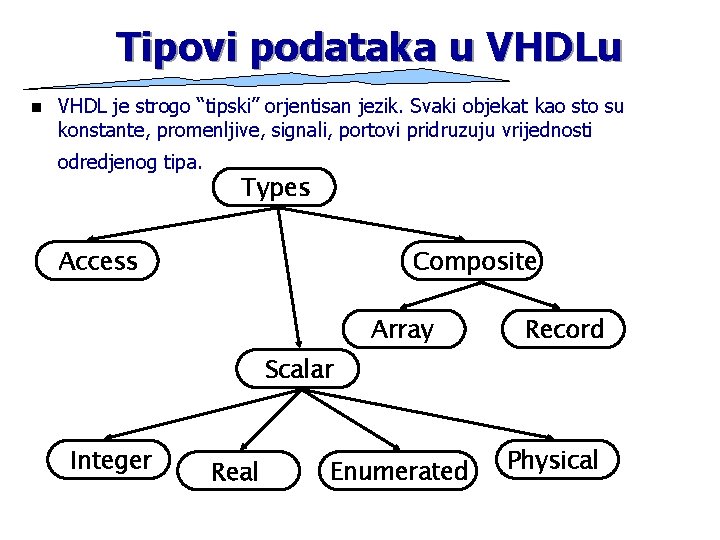

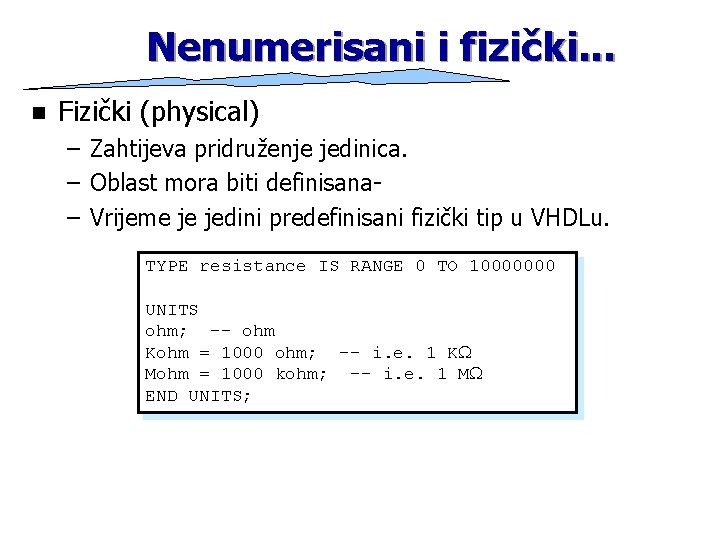

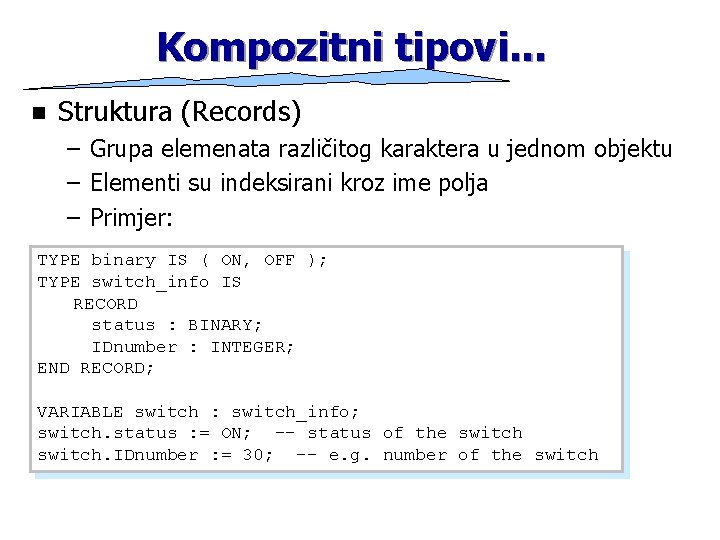

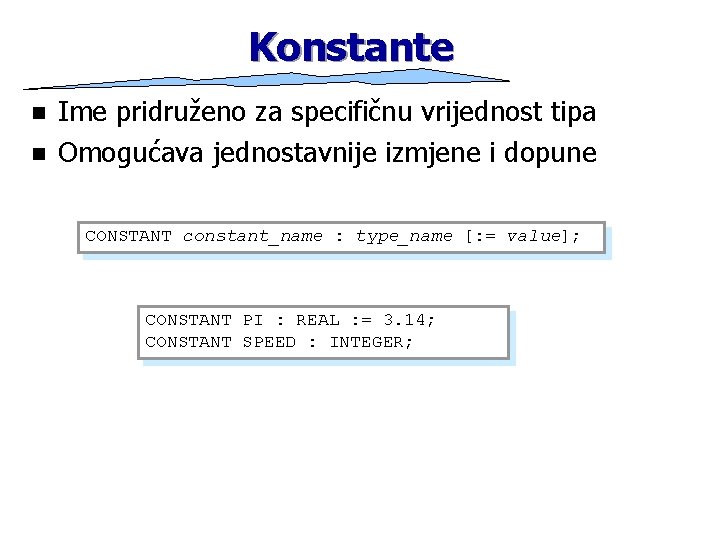

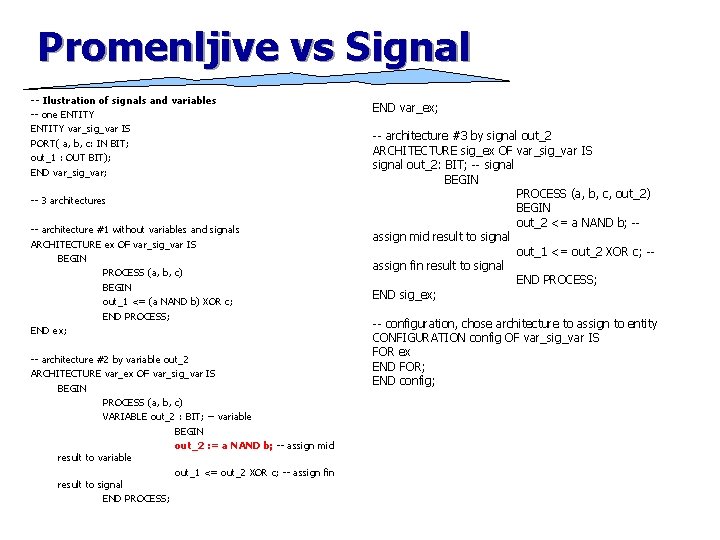

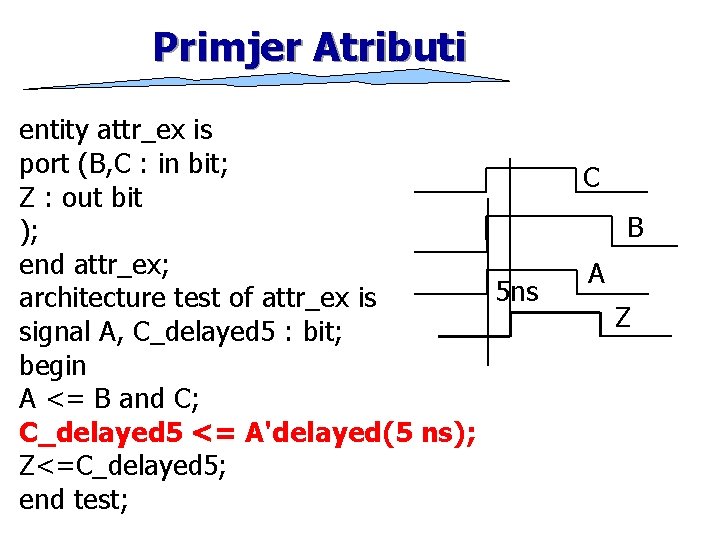

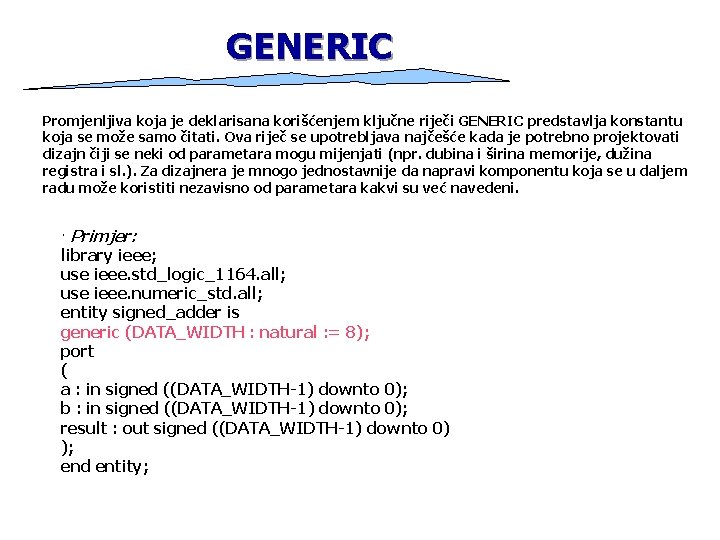

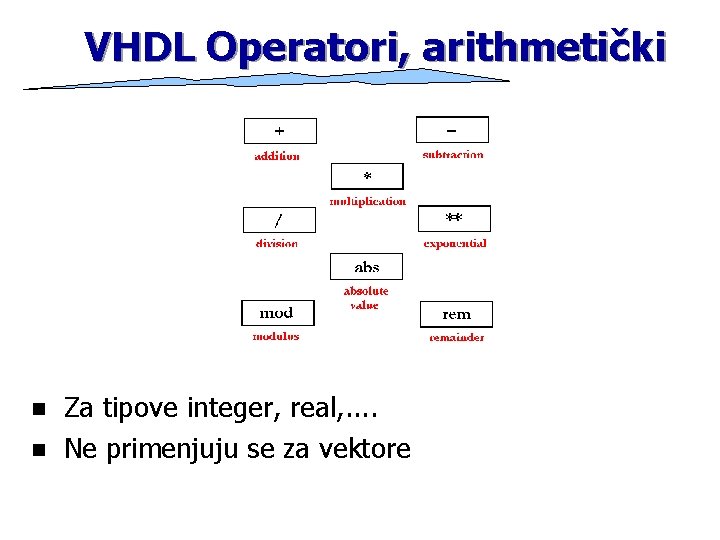

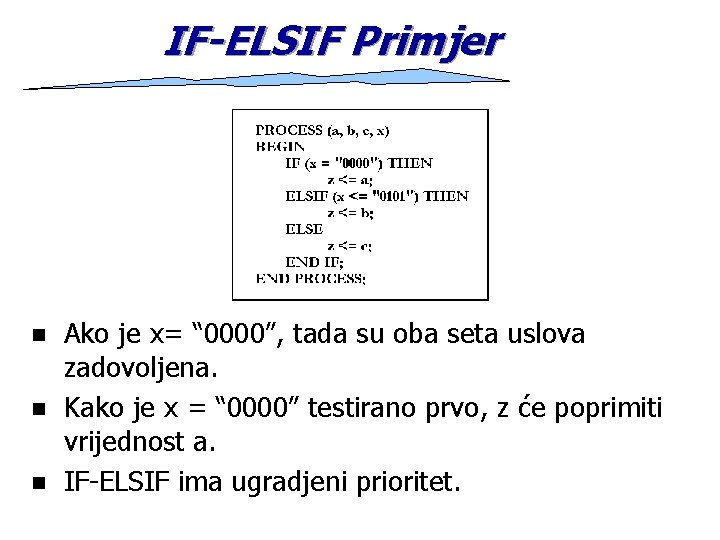

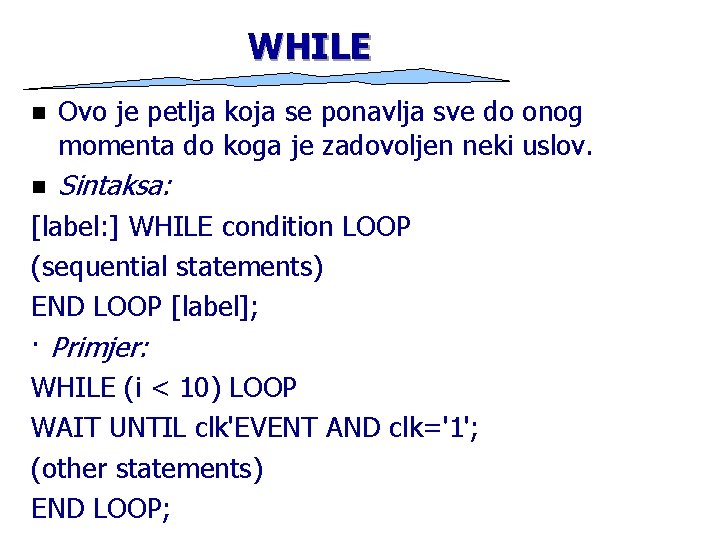

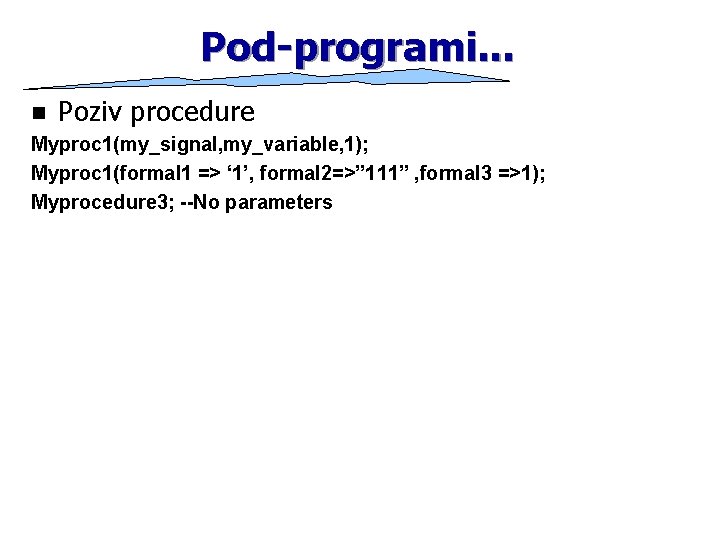

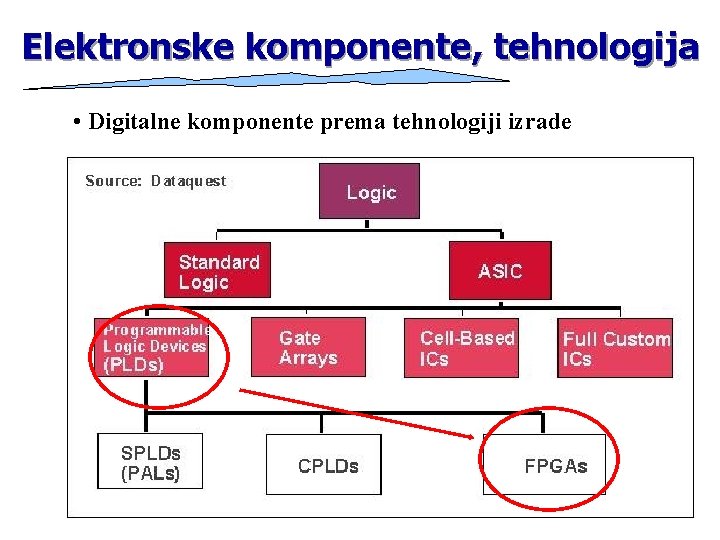

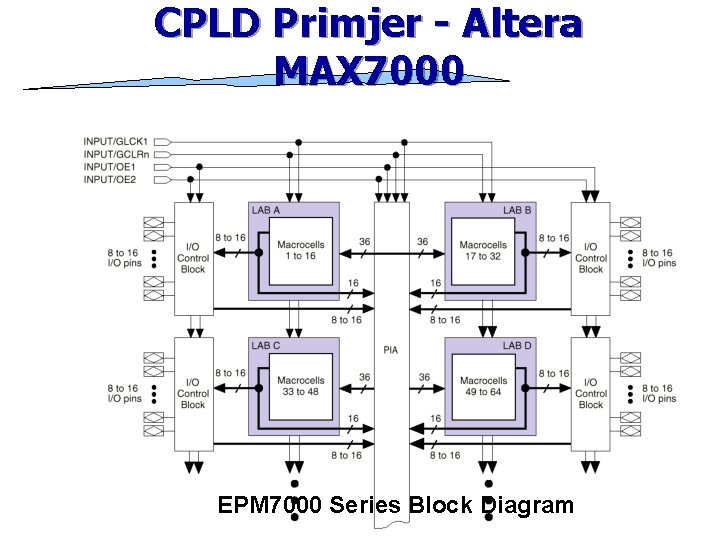

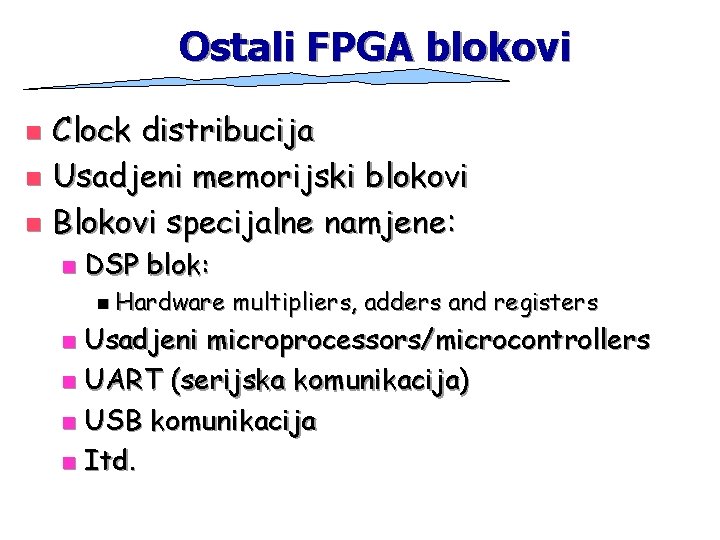

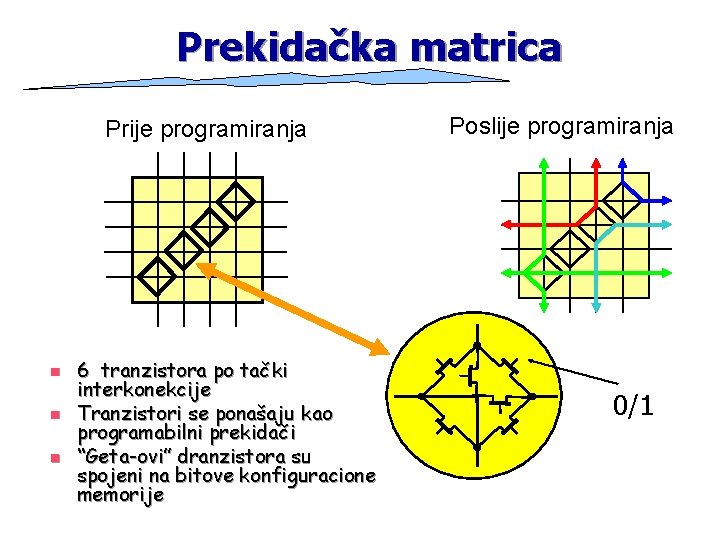

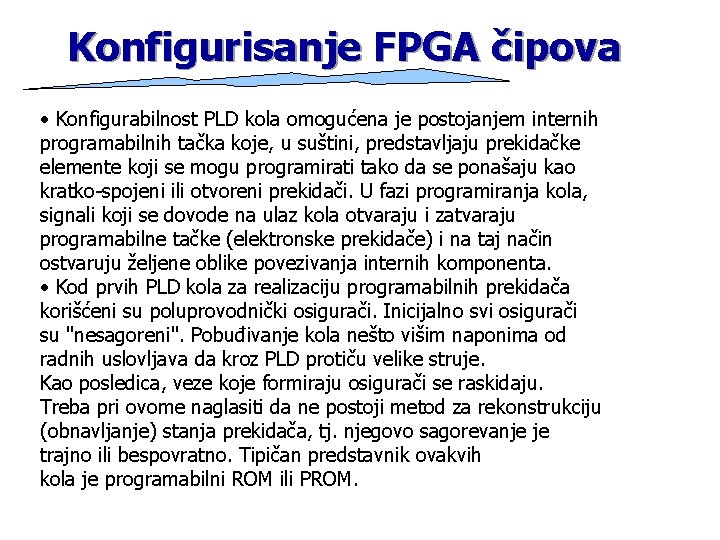

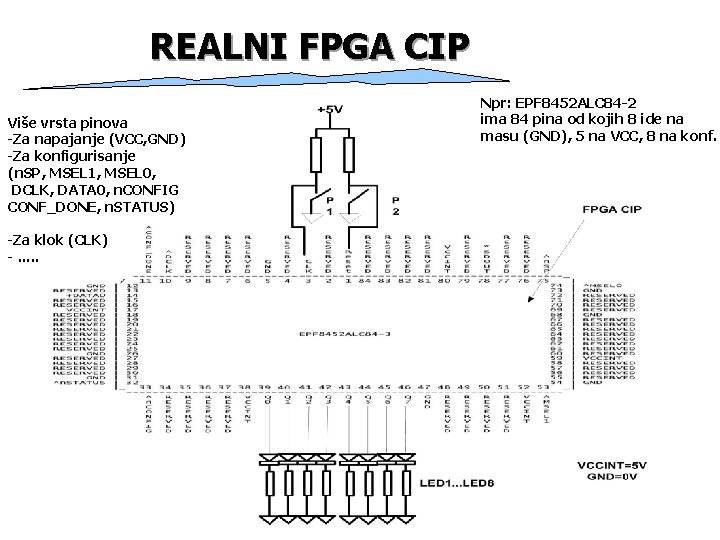

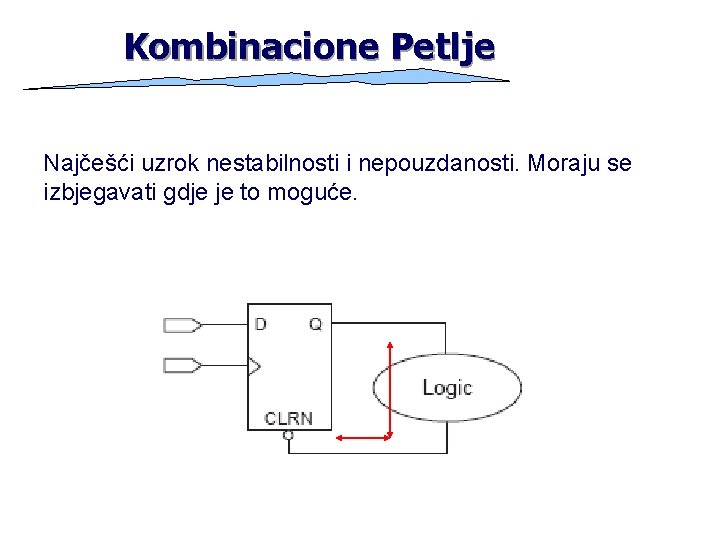

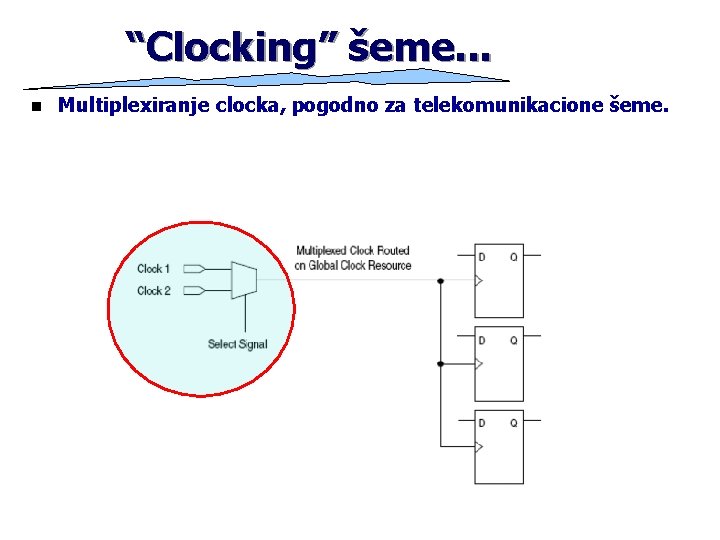

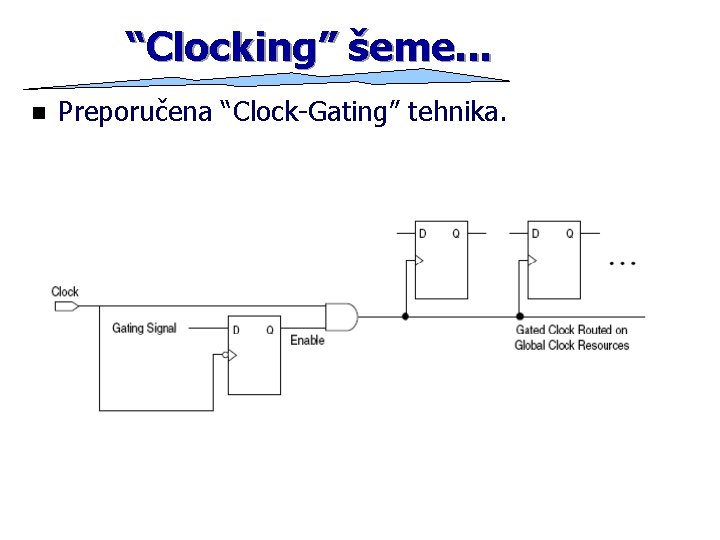

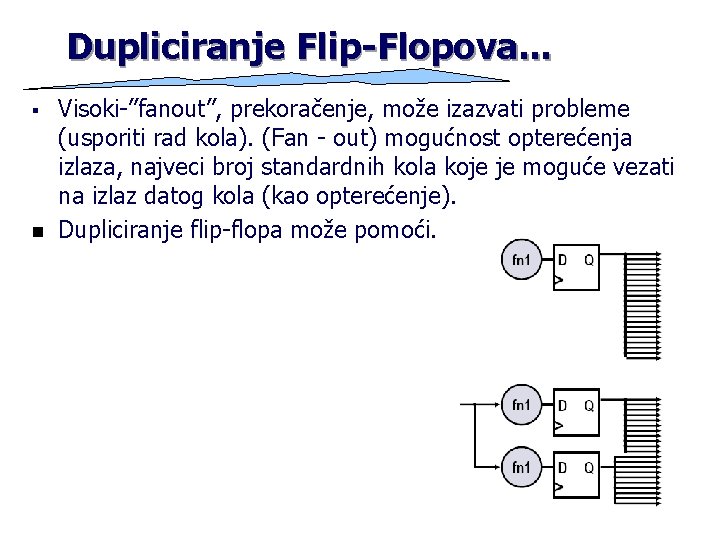

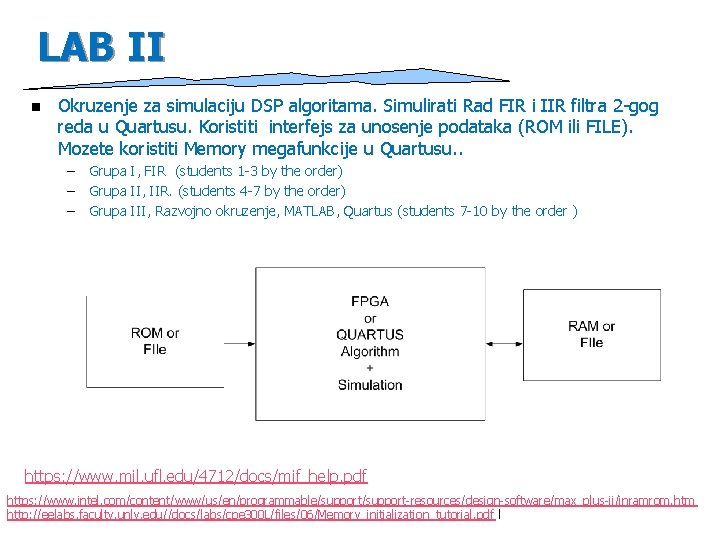

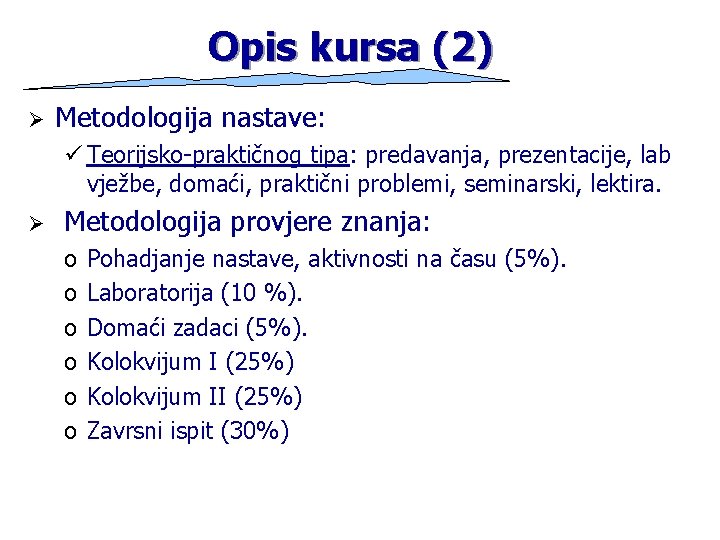

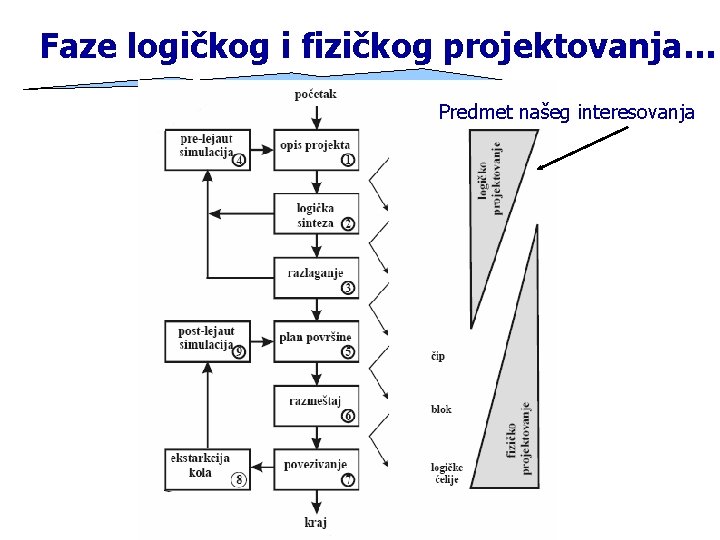

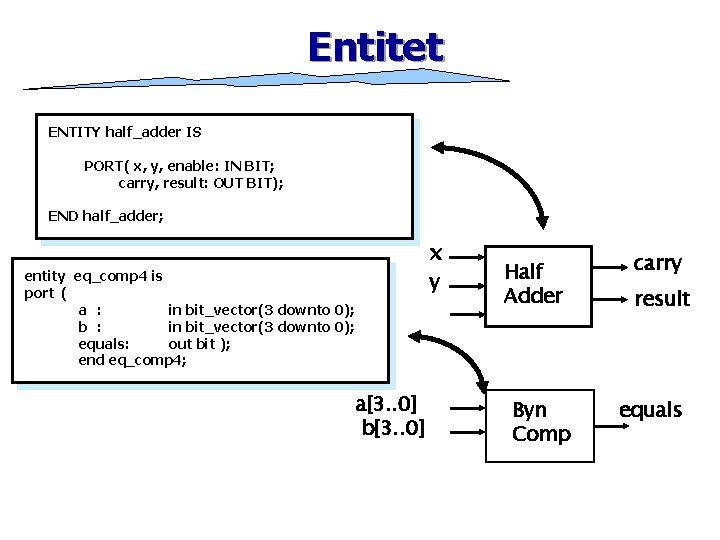

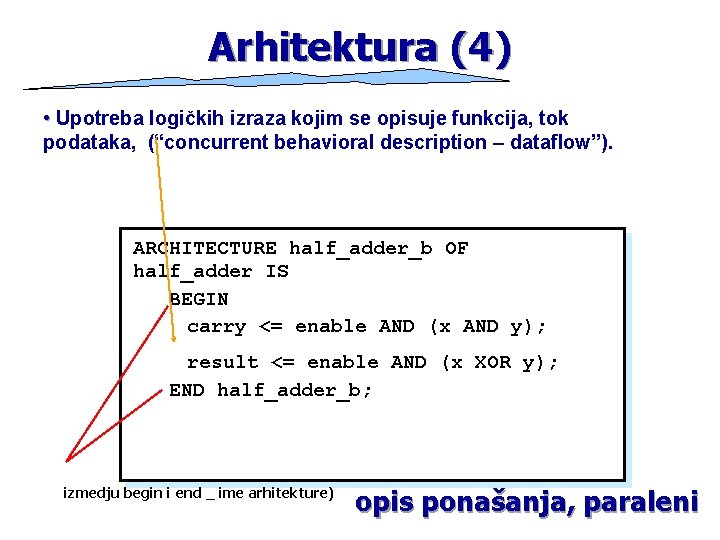

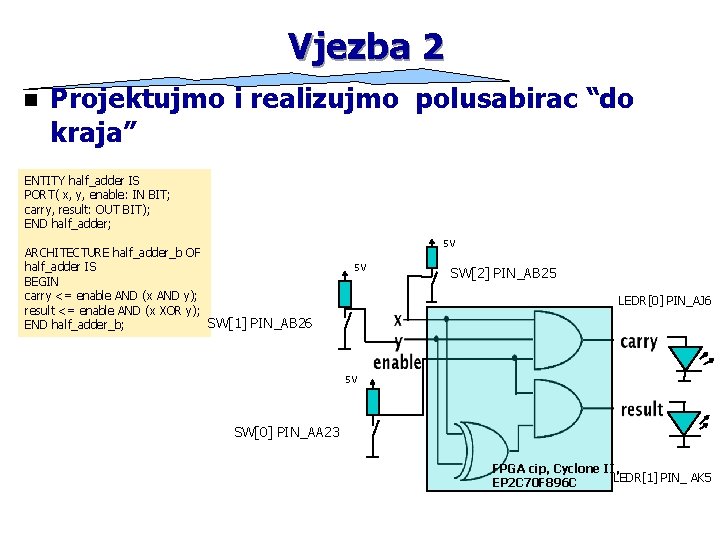

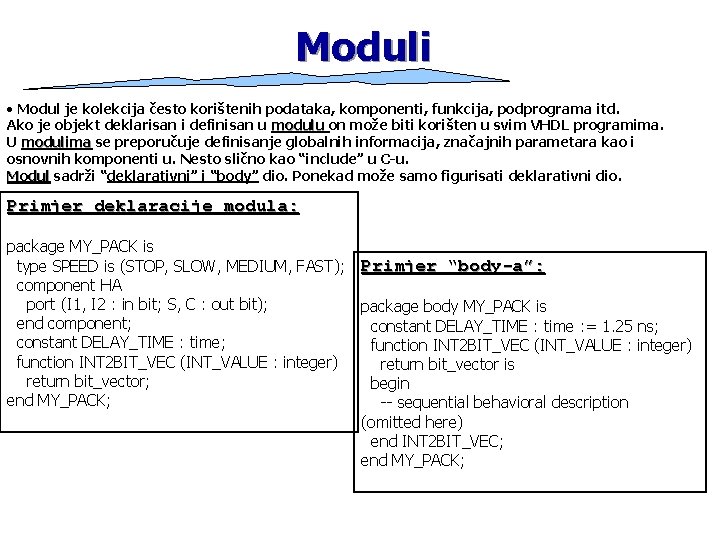

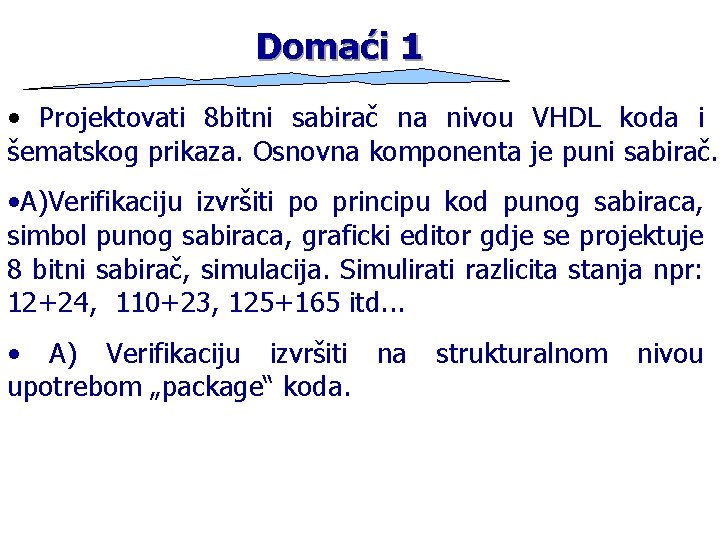

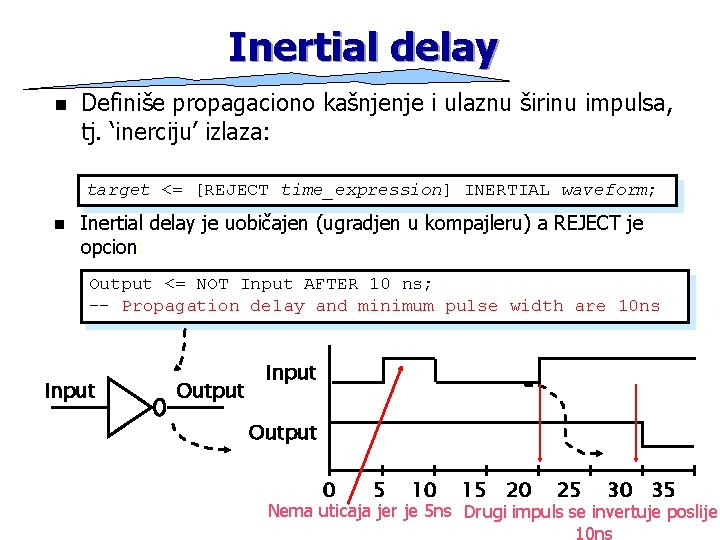

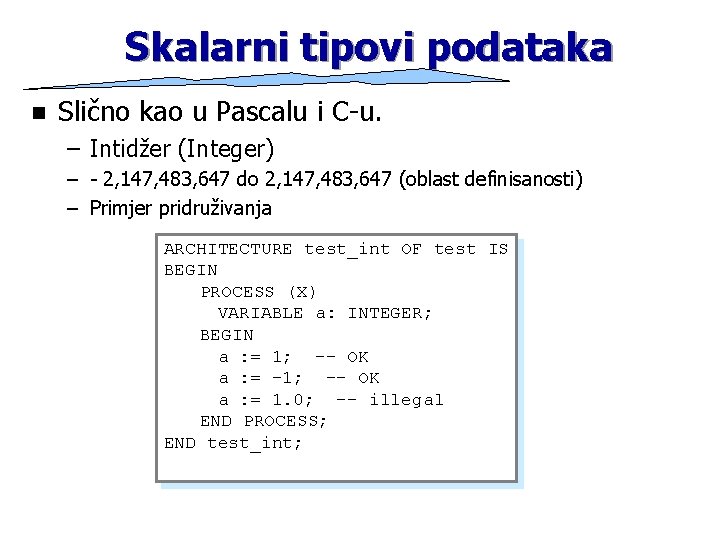

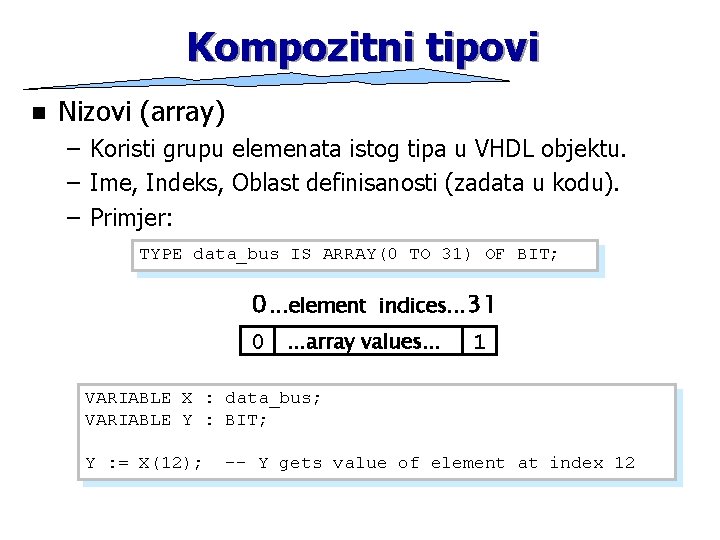

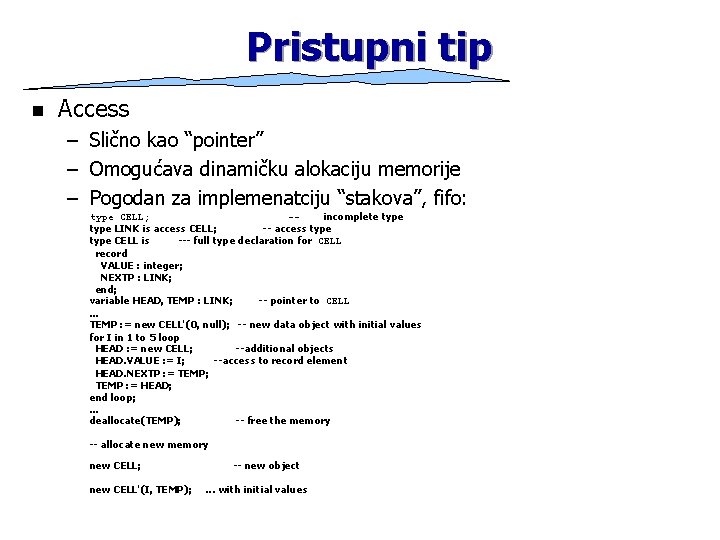

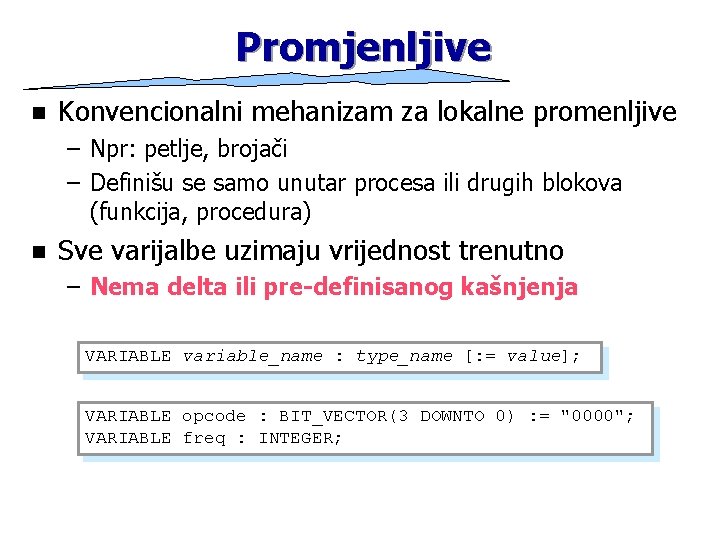

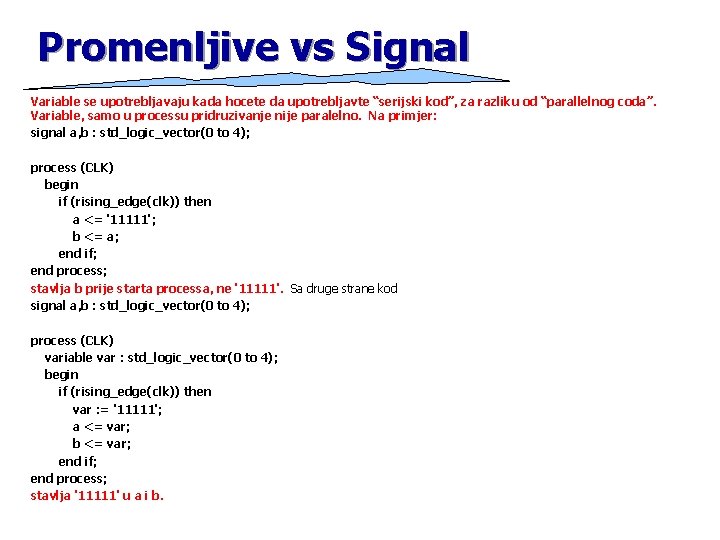

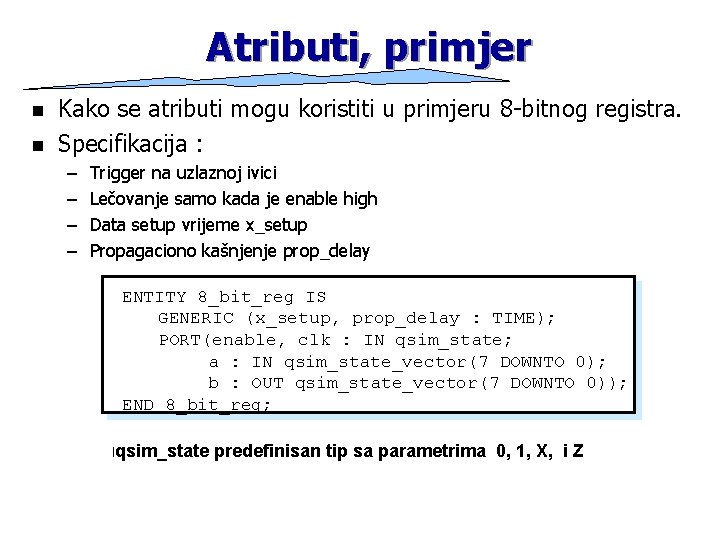

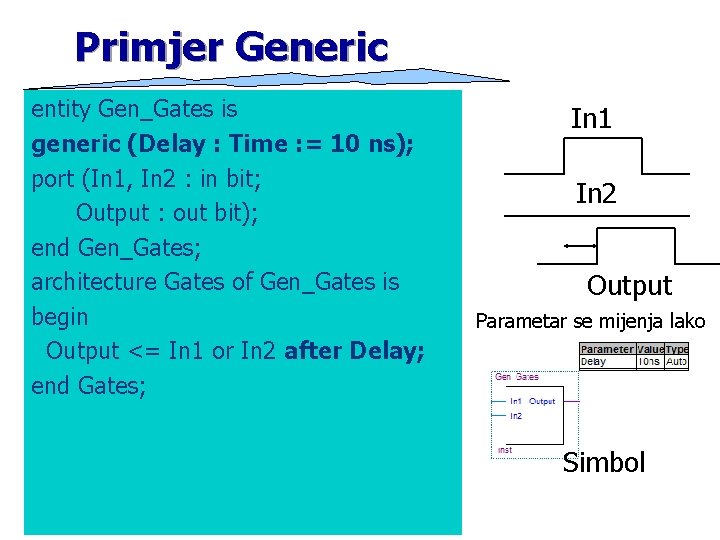

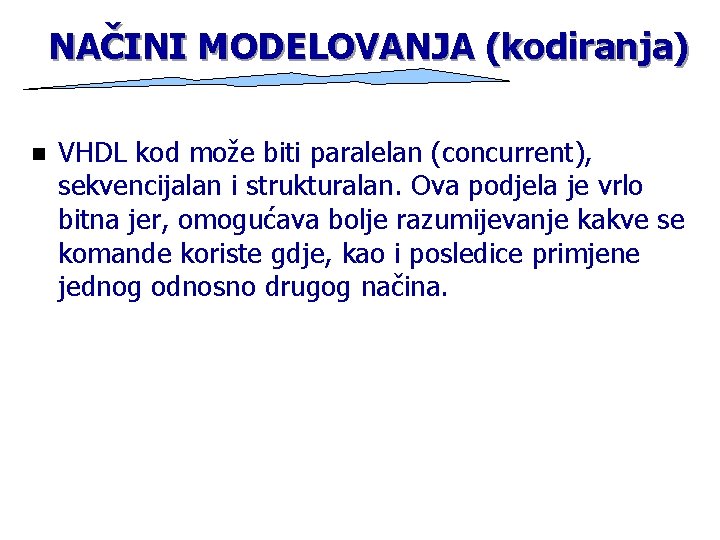

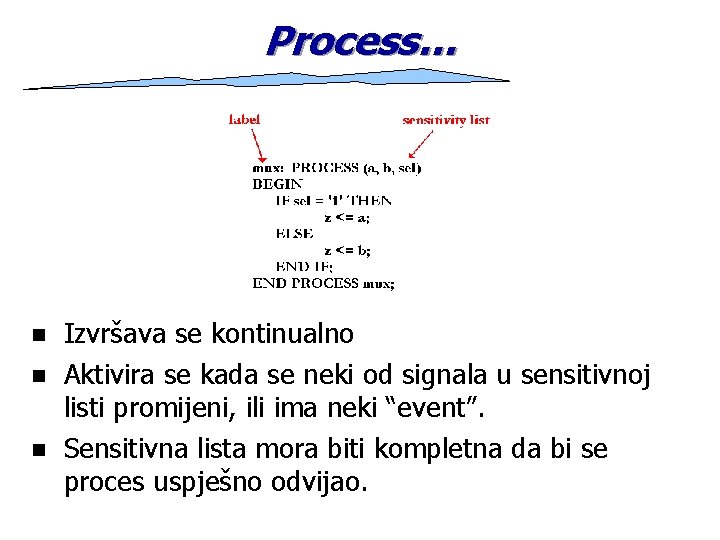

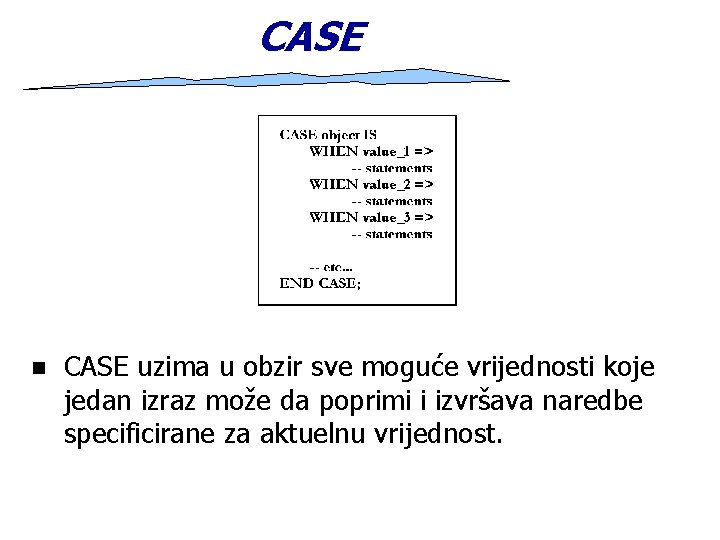

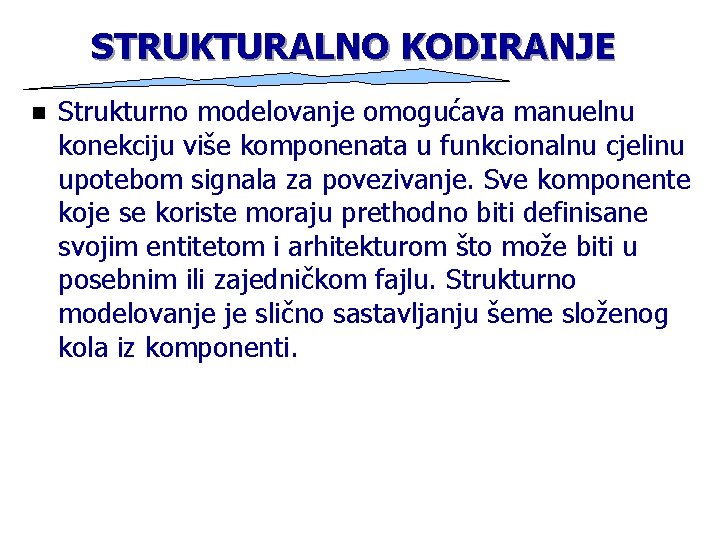

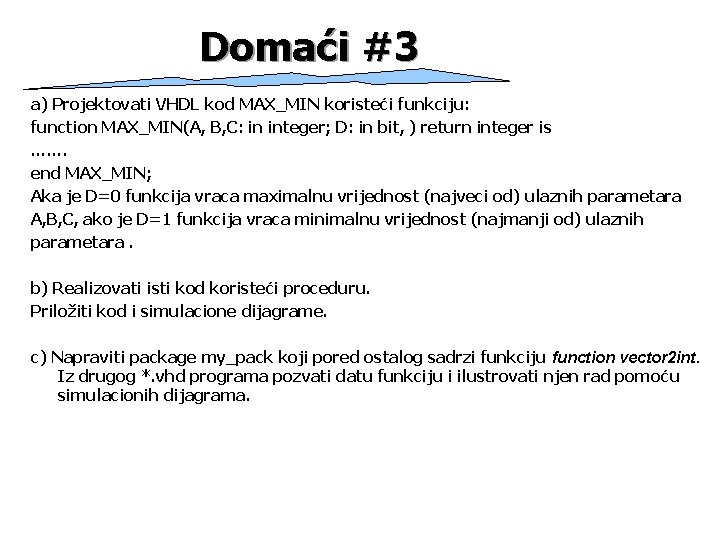

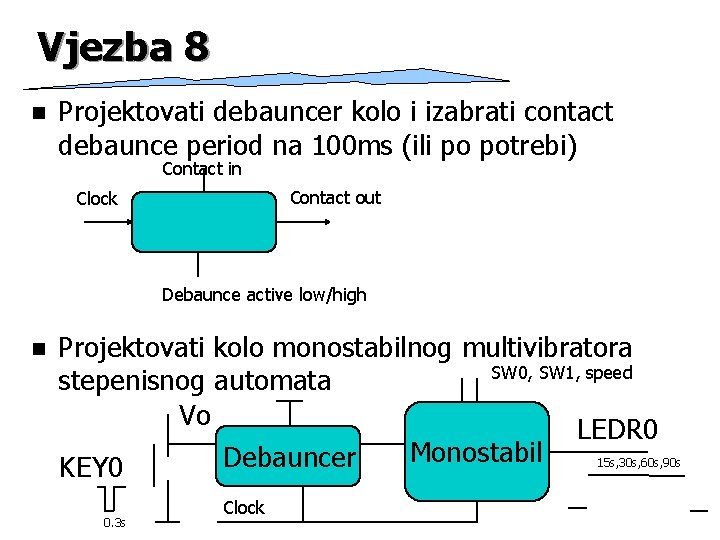

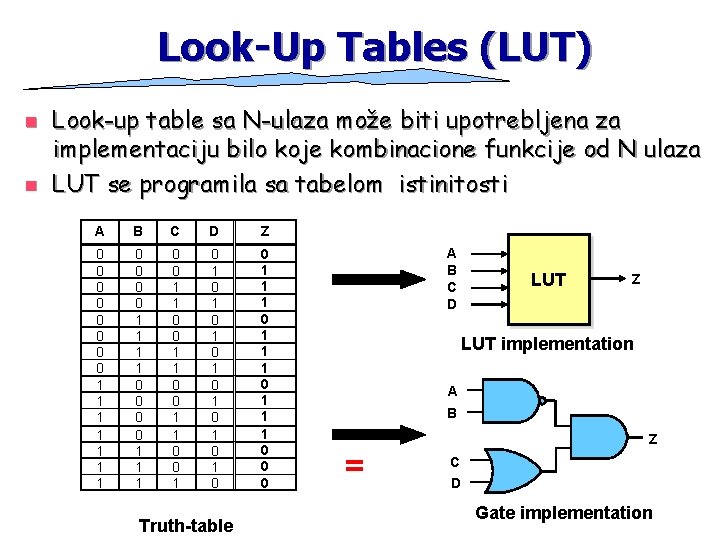

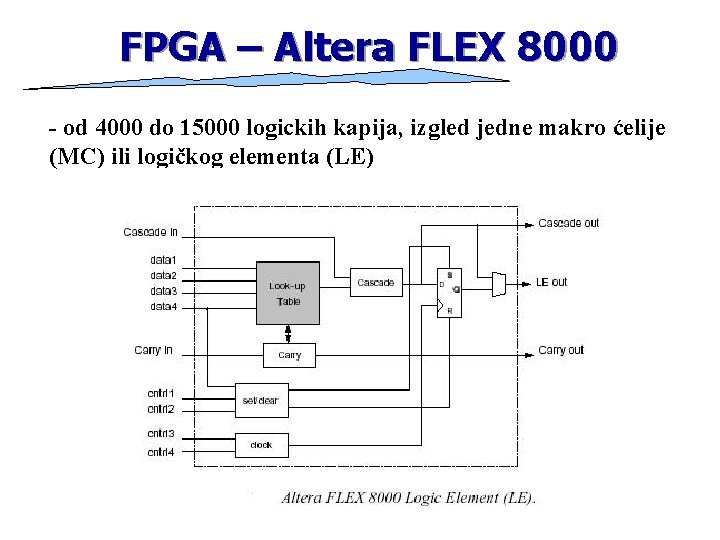

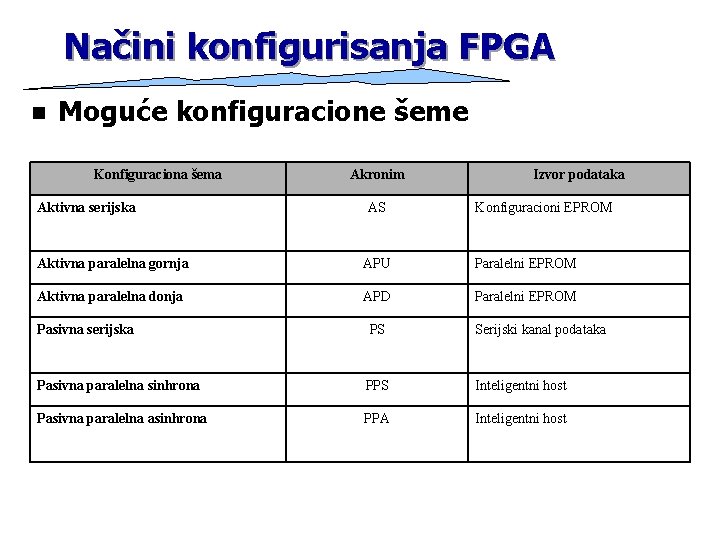

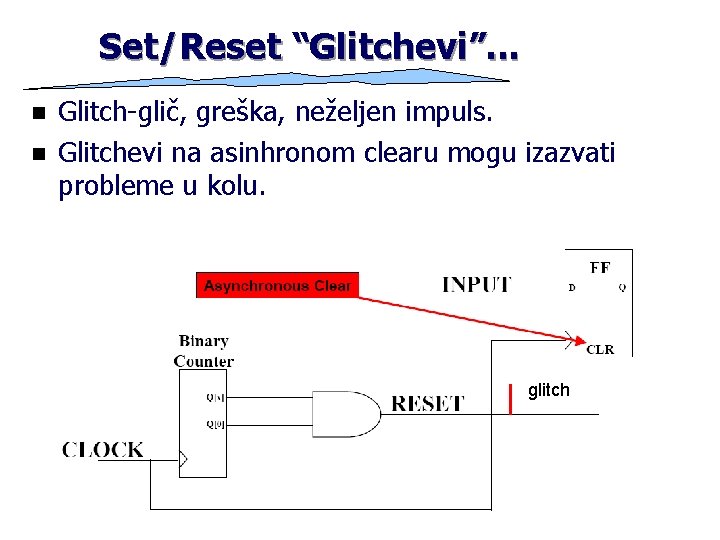

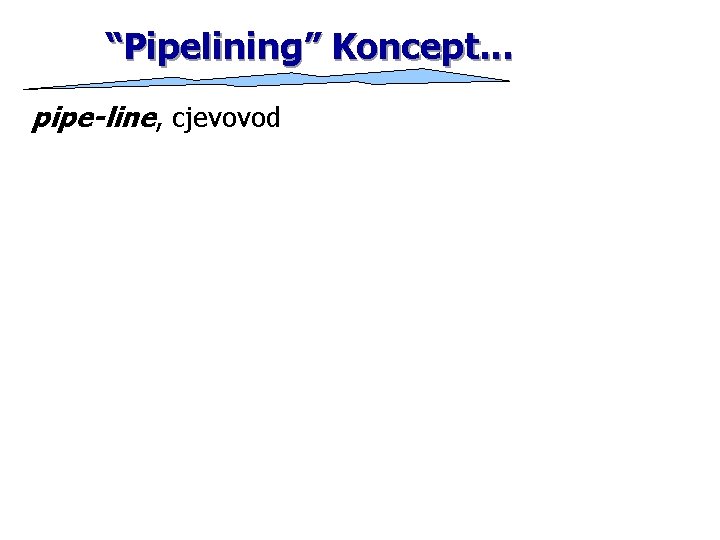

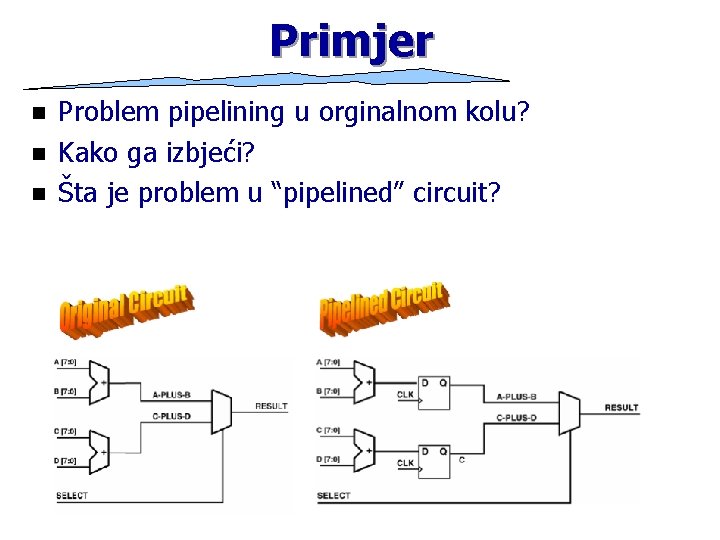

Vjezba 2 n Projektujmo i realizujmo polusabirac “do kraja” ENTITY half_adder IS PORT( x, y, enable: IN BIT; carry, result: OUT BIT); END half_adder; ARCHITECTURE half_adder_b OF half_adder IS BEGIN carry <= enable AND (x AND y); result <= enable AND (x XOR y); SW[1] PIN_AB 26 END half_adder_b; 5 V 5 V SW[2] PIN_AB 25 LEDR[0] PIN_AJ 6 5 V SW[0] PIN_AA 23 FPGA cip, Cyclone II, LEDR[1] PIN_ AK 5 EP 2 C 70 F 896 C

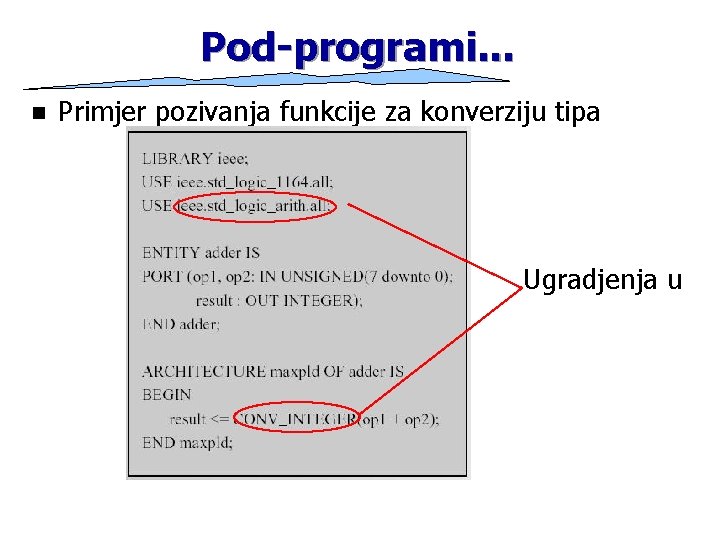

![Lab 1 DE 2 70 FPGA pins Onal SW0 PINAA 23 a SW1 PINAB Lab 1 DE 2 -70 FPGA pins Onal SW[0] PIN_AA 23 a SW[1] PIN_AB](https://slidetodoc.com/presentation_image_h2/911241d46073b6051f3588afb6d9b140/image-54.jpg)

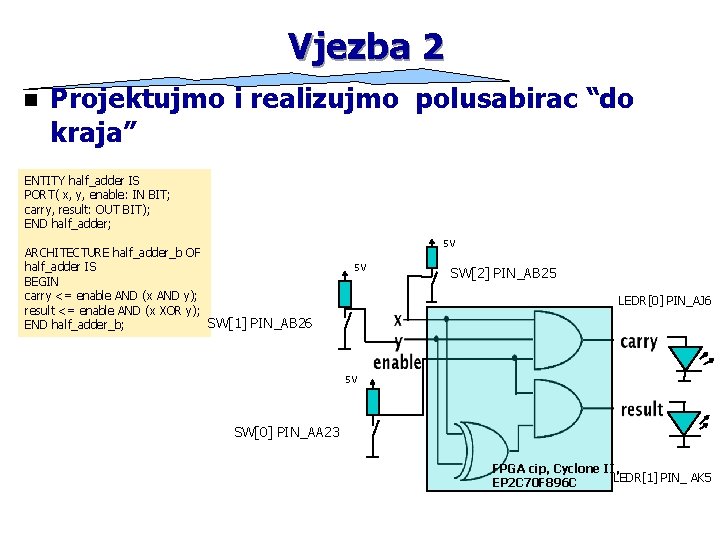

Lab 1 DE 2 -70 FPGA pins Onal SW[0] PIN_AA 23 a SW[1] PIN_AB 26 b SW[2] PIN_AB 25 c SW[3] PIN_AC 27 d SW[4] PIN_AC 26 e SW[5] PIN_AC 24 11 LEDR[0] PIN_AJ 6 ao LEDR[1] PIN_AK 5 onal a b c d e Alarm Hocemo da konstruisemo kolo (cip) koji je alarm otvorenosti vrata automobila Naime, izlaz “ao” koji je vezan na LEDR[1] na ploci se automatski aktivira ako su bilo koja od 5 vrata “a…e” otvorena (pri otvaranju se akticira odgowarajuci Sw[1]…Sw[5]. Normalno ako je “onal” SW[0] ukljucen, [to idicira LEDR[0]; Step 1: Napravimo VHDL cod alarma Step 2: Dodijelimo cip Step 3: Dodijelimo pinove Step 4: Provjerimo funkcionalnost na ploci ao l 1 ENTITY alarm IS PORT ( a, b, c, d, e, onal : IN BIT; ao, l 1 : OUT BIT ); END alarm; ARCHITECTURE myarch OF alarm IS BEGIN ao<= (a or b or c or d or e) and onal; l 1<=not(not onal); END myarch; LEDR(0. . ) Vcc Sw(0. . )

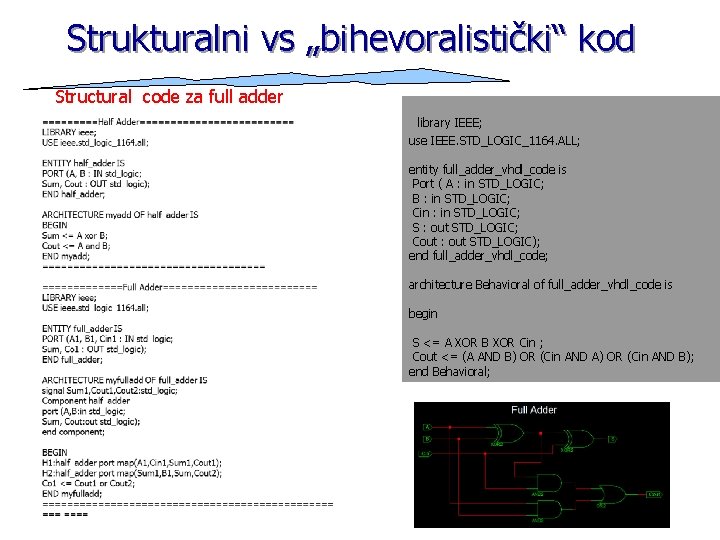

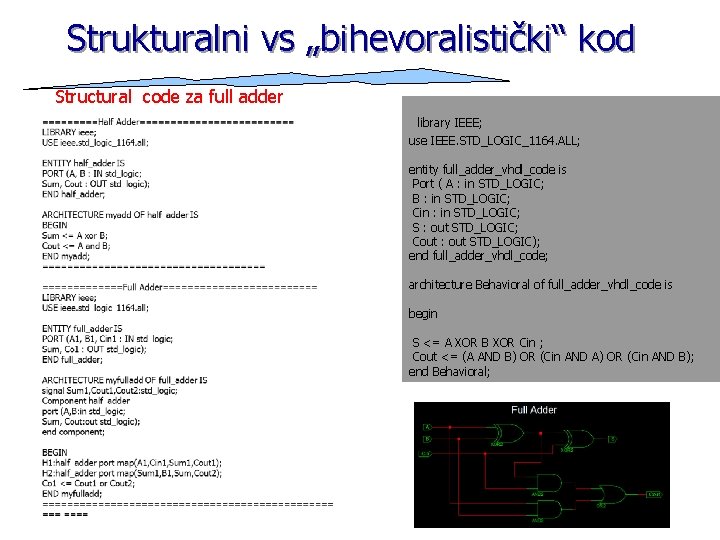

Strukturalni vs „bihevoralistički“ kod Structural code za full adder library IEEE; use IEEE. STD_LOGIC_1164. ALL; entity full_adder_vhdl_code is Port ( A : in STD_LOGIC; B : in STD_LOGIC; Cin : in STD_LOGIC; S : out STD_LOGIC; Cout : out STD_LOGIC); end full_adder_vhdl_code; architecture Behavioral of full_adder_vhdl_code is begin S <= A XOR B XOR Cin ; Cout <= (A AND B) OR (Cin AND A) OR (Cin AND B); end Behavioral;

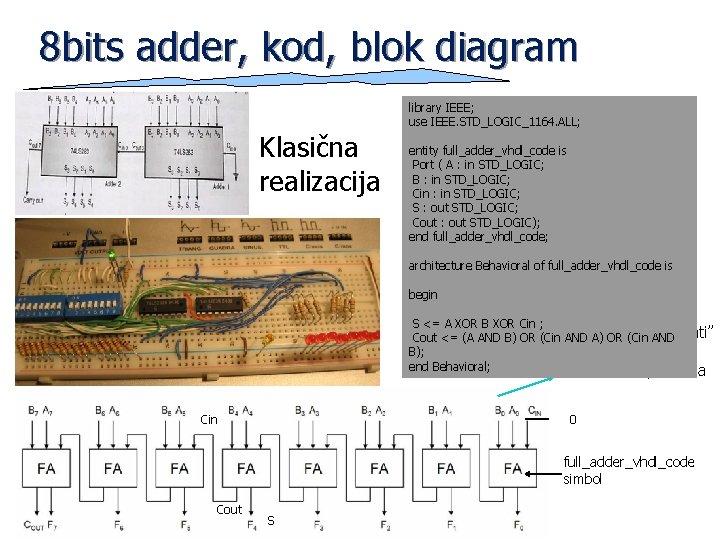

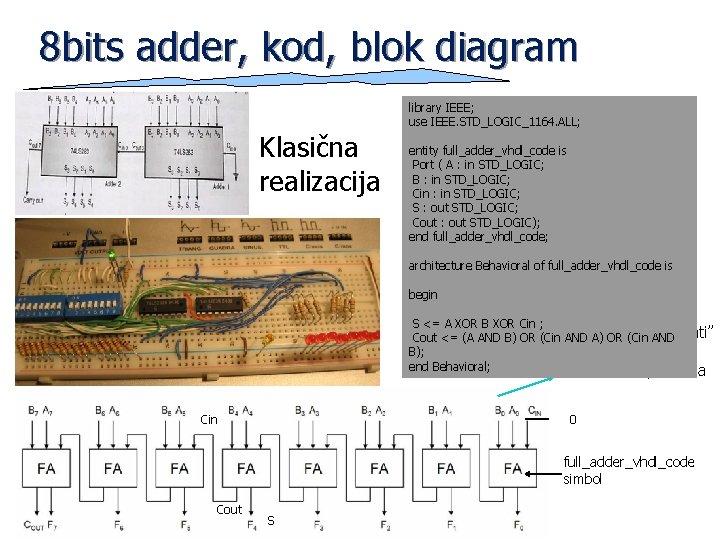

8 bits adder, kod, blok diagram library IEEE; use IEEE. STD_LOGIC_1164. ALL; Klasična realizacija entity full_adder_vhdl_code is Port ( A : in STD_LOGIC; B : in STD_LOGIC; Cin : in STD_LOGIC; S : out STD_LOGIC; Cout : out STD_LOGIC); end full_adder_vhdl_code; architecture Behavioral of full_adder_vhdl_code is begin S <= A XOR B XOR Cin ; se. OR moze “strpati” Cout <= (A AND B) OR (Cin Sve AND A) (Cin AND B); u VHDL cip i to da end Behavioral; ne zauzima prostora Cin 0 full_adder_vhdl_code simbol Cout S

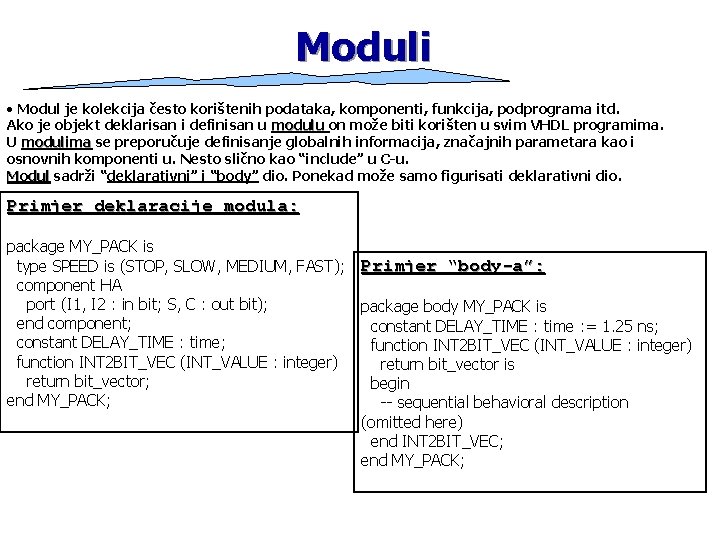

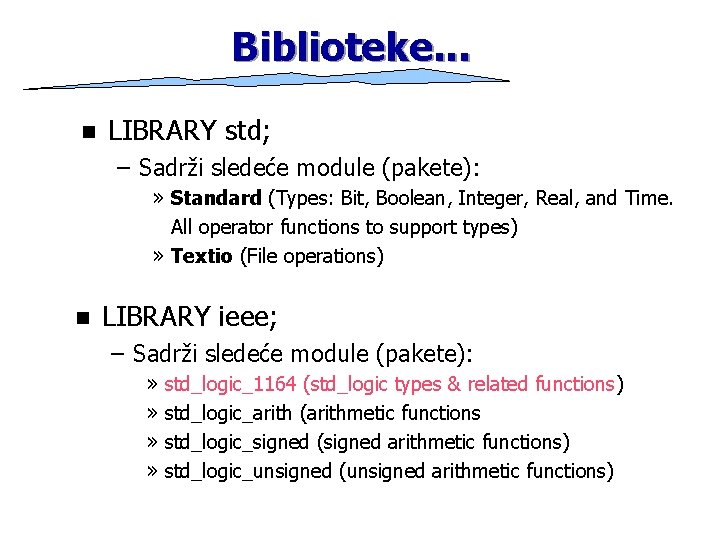

Moduli • Modul je kolekcija često korištenih podataka, komponenti, funkcija, podprograma itd. Ako je objekt deklarisan i definisan u modulu on može biti korišten u svim VHDL programima. U modulima se preporučuje definisanje globalnih informacija, značajnih parametara kao i osnovnih komponenti u. Nesto slično kao “include” u C-u. Modul sadrži “deklarativni” i “body” dio. Ponekad može samo figurisati deklarativni dio. Primjer deklaracije modula: package MY_PACK is type SPEED is (STOP, SLOW, MEDIUM, FAST); Primjer “body-a”: component HA port (I 1, I 2 : in bit; S, C : out bit); package body MY_PACK is end component; constant DELAY_TIME : time : = 1. 25 ns; constant DELAY_TIME : time; function INT 2 BIT_VEC (INT_VALUE : integer) return bit_vector is return bit_vector; begin end MY_PACK; -- sequential behavioral description (omitted here) end INT 2 BIT_VEC; end MY_PACK;

Moduli, primjer LIBRARY ieee; USE ieee. std_logic_1164. all; ENTITY mux 2 to 1 IS PORT (d 0, d 1, s : IN STD_LOGIC; f : OUT STD_LOGIC); END mux 2 to 1; ARCHITECTURE Logic. Func OF mux 2 to 1 IS BEGIN f <= (d 0 AND (NOT s)) OR (d 1 AND s); END Logic. Func; LIBRARY ieee; USE ieee. std_logic_1164. all; PACKAGE mux 2 to 1_package IS COMPONENT mux 2 to 1 PORT (d 0, d 1, s : IN STD_LOGIC; f : OUT STD_LOGIC); END COMPONENT; END mux 2 to 1_package; Fajl#1 u radnom direktrorijumu, mora biti kompajliran (mux 2 to 1. vhd) k 1 LIBRARY ieee; USE ieee. std_logic_1164. all; USE work. mux 2 to 1_package. all; ENTITY mux 4 to 1 IS PORT(w 0, w 1, w 2, w 3, sel 0, sel 1 : IN STD_LOGIC; f : OUT STD_LOGIC); END mux 4 to 1; ARCHITECTURE structure OF mux 4 to 1 IS SIGNAL I 1, I 2 : STD_LOGIC; BEGIN u 1: mux 2 to 1 PORT MAP(w 0, w 1, sel 0, I 1); u 2: mux 2 to 1 PORT MAP(w 2, w 3, sel 0, I 2); u 3: mux 2 to 1 PORT MAP(I 1, I 2, sel 1, f); END structure; Fajl#2, trenutni projekat (mux 4 to 1. vhd) NAPOMENA: Pri kompajliranju mux 4 to 1. vhd kao projekta u Qurtusu II, nije dovoljno ukključiti package sa USE work. mux 2 to 1_package. all; već treba mux 2 to 1. vhd dodati projektu sa Project-> Add/Remove files in Project…

Biblioteke n n Sadrže modul ili kolekciju modula Biblioteke proizvodjača – Standard Package – IEEE developed packages – Altera Component packages n Radne Biblioteke – Work. xx

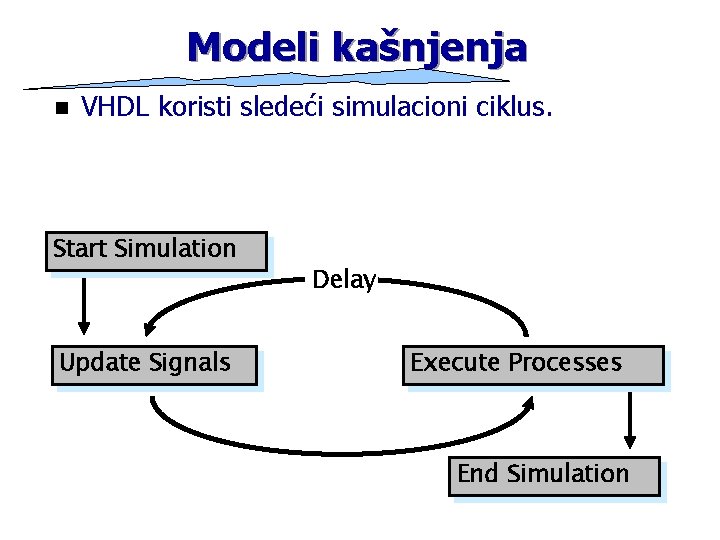

Biblioteke. . . n LIBRARY std; – Sadrži sledeće module (pakete): » Standard (Types: Bit, Boolean, Integer, Real, and Time. All operator functions to support types) » Textio (File operations) n LIBRARY ieee; – Sadrži sledeće module (pakete): » » std_logic_1164 (std_logic types & related functions) std_logic_arith (arithmetic functions std_logic_signed (signed arithmetic functions) std_logic_unsigned (unsigned arithmetic functions)

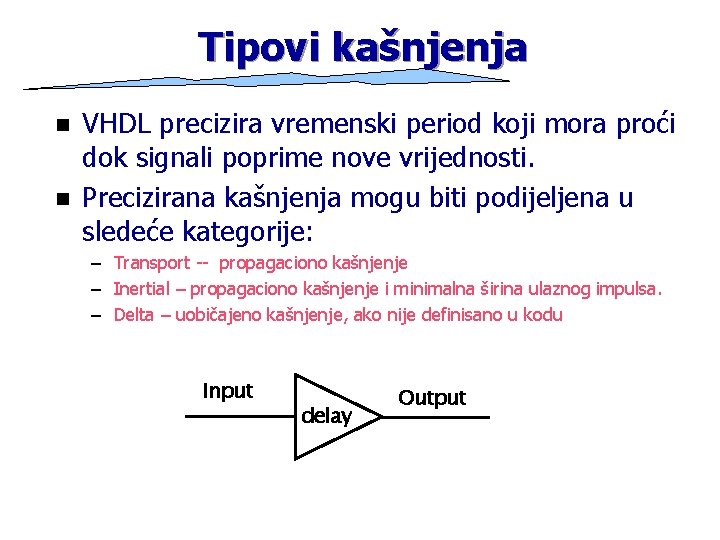

Biblioteke. . . STD_LOGIC_1164: Declaration: type std_logic is ( 'U', -- uninitialized 'X', -- forcing unknown '0', -- forcing 0 '1', -- forcing 1 'Z', -- high impedance 'W', -- weak unknown 'L', -- weak 0 'H', -- weak 1 '-' ); -- "don't care" Sintaksa upotrebe biblioteke: LIBRARY <any_name>; USE <any_name>. <package_name>. all; Pozivanje biblioteke LIBRARY ieee; USE ieee. std_logic_1164. all; ENTITY mux 2 to 1 IS PORT( d 0, d 1, s f END mux 2 to 1; : IN STD_LOGIC; : OUT STD_LOGIC); ARCHITECTURE behavior OF mux 2 to 1 IS BEGIN WITH s SELECT f <= d 0 WHEN '0', d 1 WHEN OTHERS; END behavior;

Ideja sistem integracije Veza izmedju hiararhijskih nivoa u projektu

Domaći 1 • Projektovati 8 bitni sabirač na nivou VHDL koda i šematskog prikaza. Osnovna komponenta je puni sabirač. • A)Verifikaciju izvršiti po principu kod punog sabiraca, simbol punog sabiraca, graficki editor gdje se projektuje 8 bitni sabirač, simulacija. Simulirati razlicita stanja npr: 12+24, 110+23, 125+165 itd. . . • A) Verifikaciju izvršiti na upotrebom „package“ koda. strukturalnom nivou

Modeli kašnjenja n VHDL koristi sledeći simulacioni ciklus. Start Simulation Update Signals Delay Execute Processes End Simulation

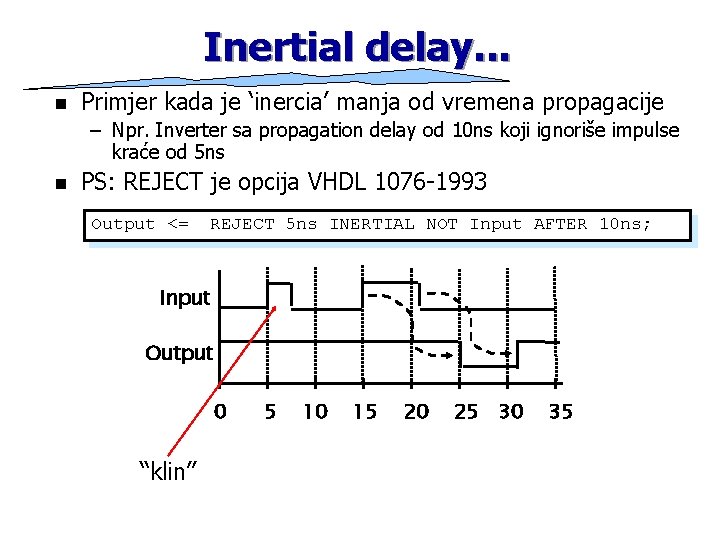

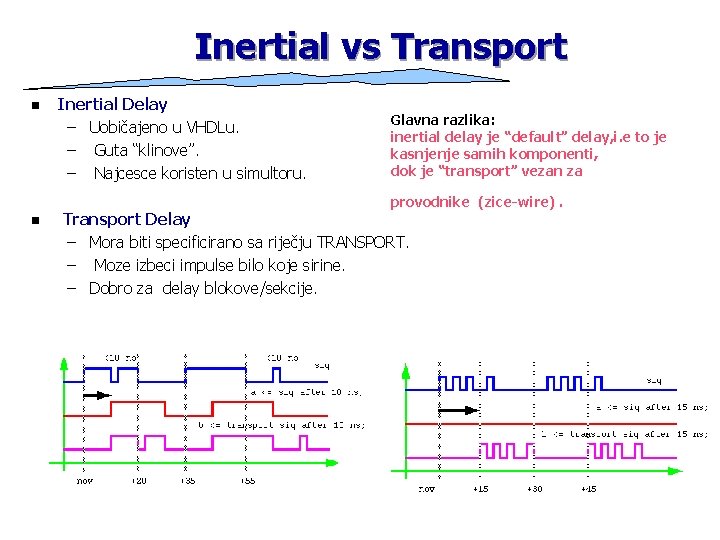

Tipovi kašnjenja n n VHDL precizira vremenski period koji mora proći dok signali poprime nove vrijednosti. Precizirana kašnjenja mogu biti podijeljena u sledeće kategorije: – Transport -- propagaciono kašnjenje – Inertial – propagaciono kašnjenje i minimalna širina ulaznog impulsa. – Delta – uobičajeno kašnjenje, ako nije definisano u kodu Input delay Output

Transport delay n Mora biti eksplicitno definisano – Npr. riječ “TRANSPORT” mora biti upotrijebljena n Signal prima novu vrijednost poslije definisanog perioda -- TRANSPORT delay example Output <= TRANSPORT NOT Input AFTER 10 ns; Input Output 10 ms 0 5 10 15 20 25 30 35

Inertial delay n Definiše propagaciono kašnjenje i ulaznu širinu impulsa, tj. ‘inerciju’ izlaza: target <= [REJECT time_expression] INERTIAL waveform; n Inertial delay je uobičajen (ugradjen u kompajleru) a REJECT je opcion: Output <= NOT Input AFTER 10 ns; -- Propagation delay and minimum pulse width are 10 ns Input Output 0 5 10 15 20 25 30 35 Nema uticaja jer je 5 ns Drugi impuls se invertuje poslije 10 ns

Inertial delay. . . n Primjer kada je ‘inercia’ manja od vremena propagacije – Npr. Inverter sa propagation delay od 10 ns koji ignoriše impulse kraće od 5 ns n PS: REJECT je opcija VHDL 1076 -1993 Output <= REJECT 5 ns INERTIAL NOT Input AFTER 10 ns; Input Output 0 “klin” 5 10 15 20 25 30 35

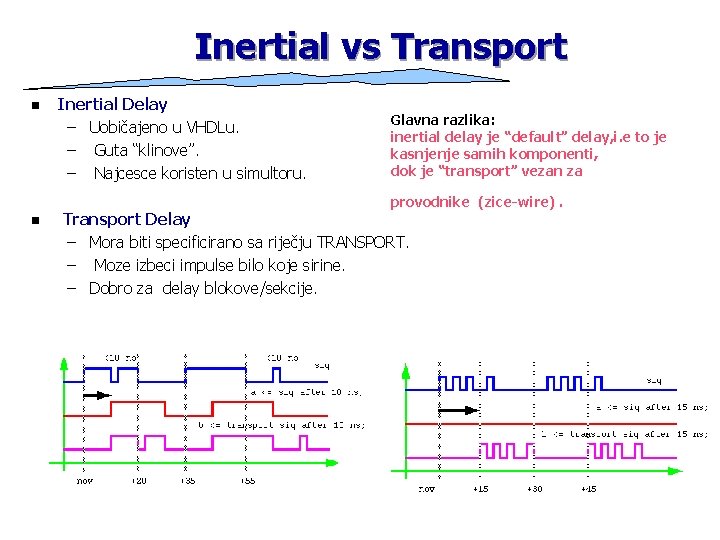

Inertial vs Transport n Inertial Delay – Uobičajeno u VHDLu. – Guta “klinove”. – Najcesce koristen u simultoru. Glavna razlika: inertial delay je “default” delay, i. e to je kasnjenje samih komponenti, dok je “transport” vezan za provodnike (zice-wire). n Transport Delay – Mora biti specificirano sa riječju TRANSPORT. – Moze izbeci impulse bilo koje sirine. – Dobro za delay blokove/sekcije.

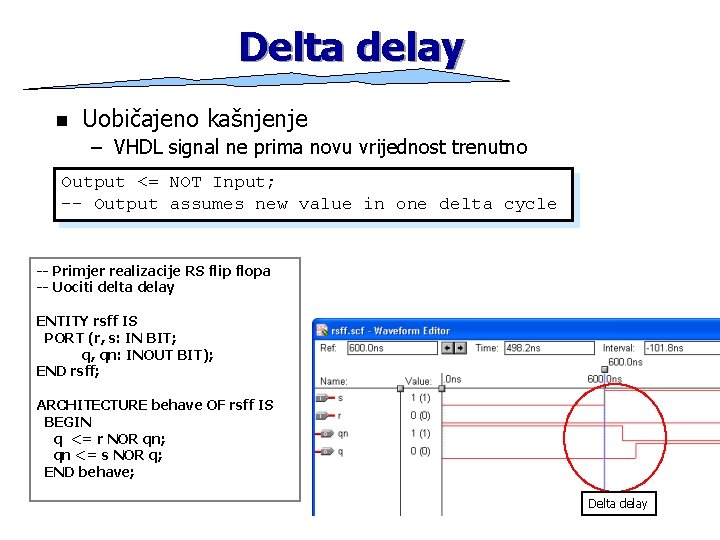

Delta delay n Uobičajeno kašnjenje – VHDL signal ne prima novu vrijednost trenutno Output <= NOT Input; -- Output assumes new value in one delta cycle -- Primjer realizacije RS flip flopa -- Uociti delta delay ENTITY rsff IS PORT (r, s: IN BIT; q, qn: INOUT BIT); END rsff; ARCHITECTURE behave OF rsff IS BEGIN q <= r NOR qn; qn <= s NOR q; END behave; Delta delay

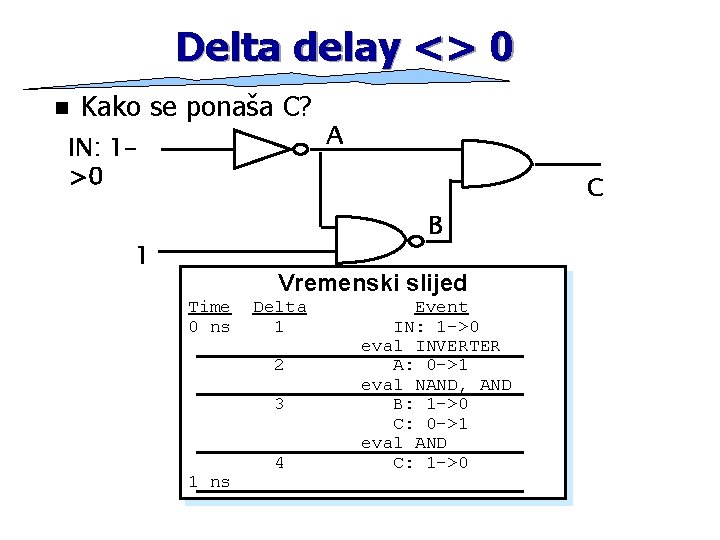

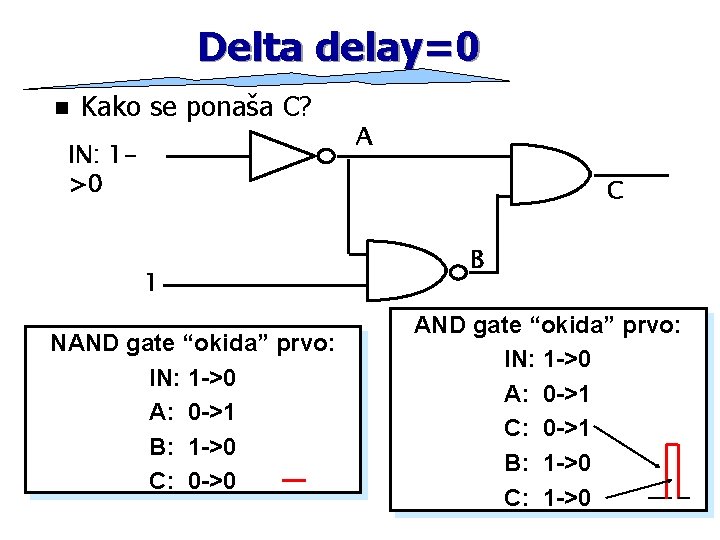

Delta delay=0 n Kako se ponaša C? IN: 1>0 A C 1 NAND gate “okida” prvo: IN: 1 ->0 A: 0 ->1 B: 1 ->0 C: 0 ->0 B AND gate “okida” prvo: IN: 1 ->0 A: 0 ->1 C: 0 ->1 B: 1 ->0 C: 1 ->0

Delta delay <> 0 n Kako se ponaša C? IN: 1>0 A C B 1 Vremenski slijed Time 0 ns Delta 1 2 3 1 ns 4 Event IN: 1 ->0 eval INVERTER A: 0 ->1 eval NAND, AND B: 1 ->0 C: 0 ->1 eval AND C: 1 ->0

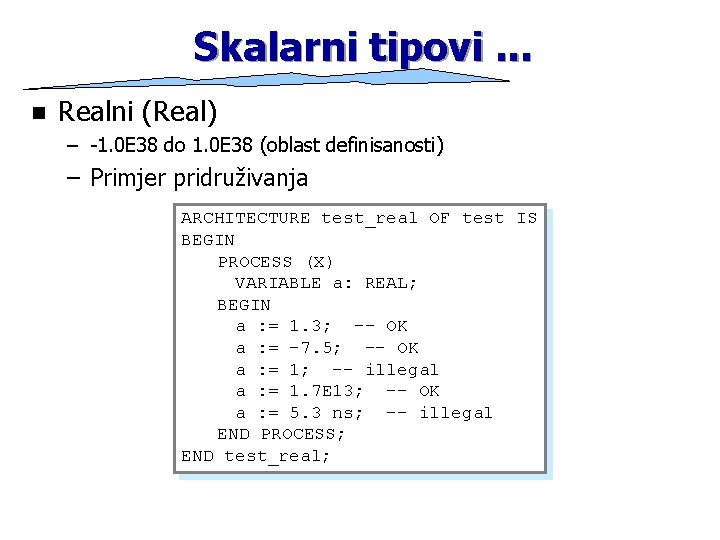

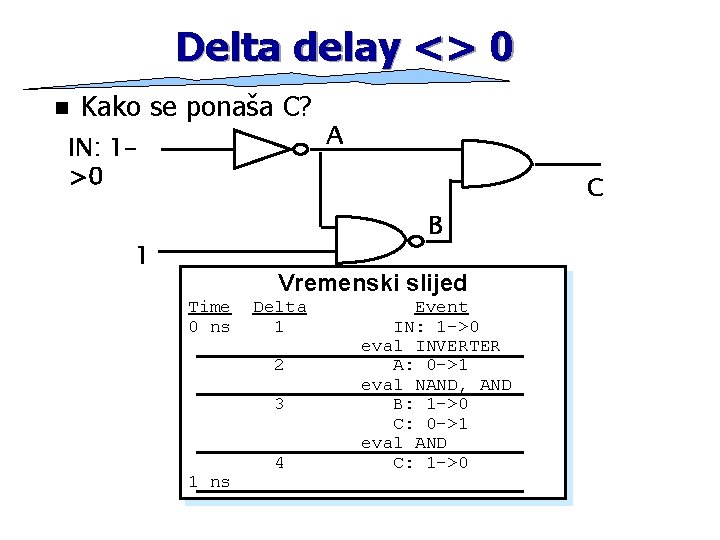

Jos o kasnjenju… q<=r nor nq after 1 ns; nq<=s nor q after 1 ns; q<=transport r nor nq after 1 ns; nq<=transport s nor q after 1 ns;

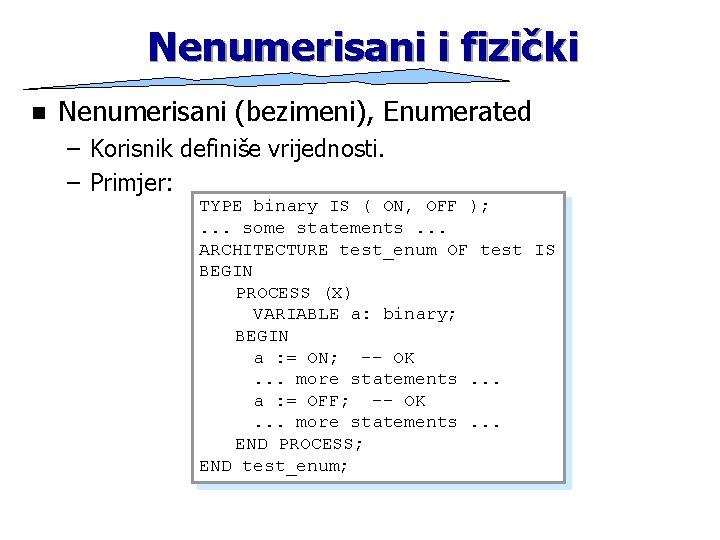

Tipovi podataka u VHDLu n VHDL je strogo “tipski” orjentisan jezik. Svaki objekat kao sto su konstante, promenljive, signali, portovi pridruzuju vrijednosti odredjenog tipa. Types Access Composite Array Record Scalar Integer Real Enumerated Physical

Skalarni tipovi podataka n Slično kao u Pascalu i C-u. – Intidžer (Integer) – - 2, 147, 483, 647 do 2, 147, 483, 647 (oblast definisanosti) – Primjer pridruživanja ARCHITECTURE test_int OF test IS BEGIN PROCESS (X) VARIABLE a: INTEGER; BEGIN a : = 1; -- OK a : = -1; -- OK a : = 1. 0; -- illegal END PROCESS; END test_int;

Skalarni tipovi. . . n Realni (Real) – -1. 0 E 38 do 1. 0 E 38 (oblast definisanosti) – Primjer pridruživanja ARCHITECTURE test_real OF test IS BEGIN PROCESS (X) VARIABLE a: REAL; BEGIN a : = 1. 3; -- OK a : = -7. 5; -- OK a : = 1; -- illegal a : = 1. 7 E 13; -- OK a : = 5. 3 ns; -- illegal END PROCESS; END test_real;

Nenumerisani i fizički n Nenumerisani (bezimeni), Enumerated – Korisnik definiše vrijednosti. – Primjer: TYPE binary IS ( ON, OFF ); . . . some statements. . . ARCHITECTURE test_enum OF test IS BEGIN PROCESS (X) VARIABLE a: binary; BEGIN a : = ON; -- OK. . . more statements. . . a : = OFF; -- OK. . . more statements. . . END PROCESS; END test_enum;

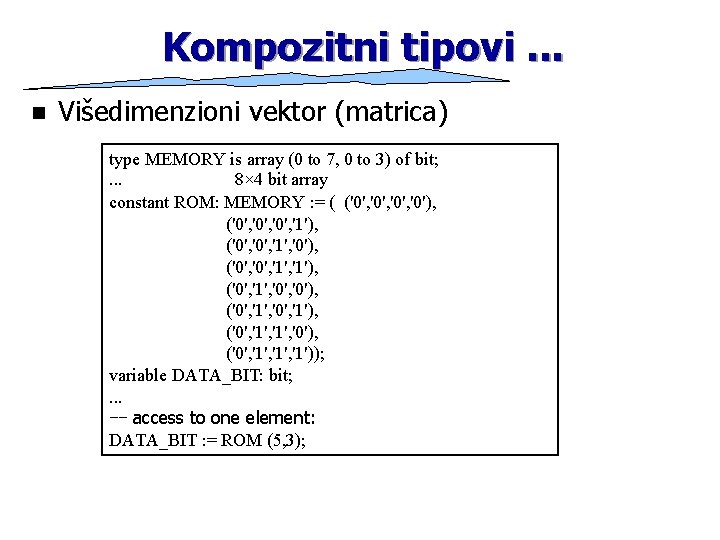

Nenumerisani i fizički. . . n Fizički (physical) – Zahtijeva pridruženje jedinica. – Oblast mora biti definisana– Vrijeme je jedini predefinisani fizički tip u VHDLu. TYPE resistance IS RANGE 0 TO 10000000 UNITS ohm; -- ohm Kohm = 1000 ohm; -- i. e. 1 K Mohm = 1000 kohm; -- i. e. 1 M END UNITS;

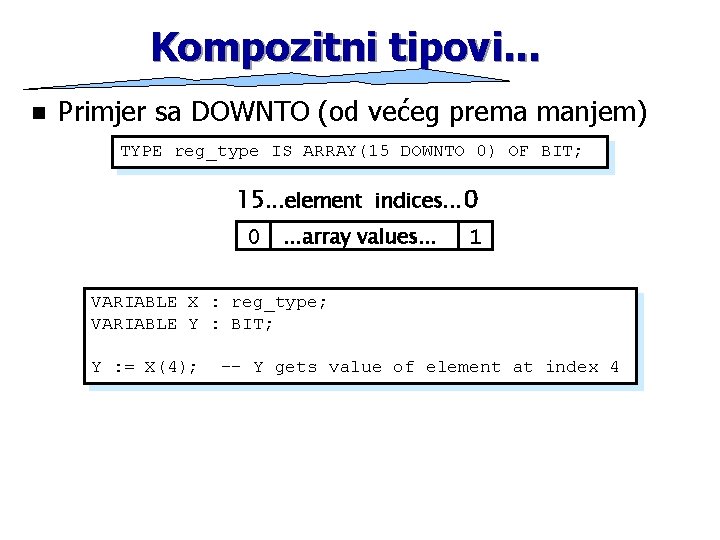

Kompozitni tipovi n Nizovi (array) – Koristi grupu elemenata istog tipa u VHDL objektu. – Ime, Indeks, Oblast definisanosti (zadata u kodu). – Primjer: TYPE data_bus IS ARRAY(0 TO 31) OF BIT; 0. . . element indices. . . 31 0. . . array values. . . 1 VARIABLE X : data_bus; VARIABLE Y : BIT; Y : = X(12); -- Y gets value of element at index 12

Kompozitni tipovi. . . n Primjer sa DOWNTO (od većeg prema manjem) TYPE reg_type IS ARRAY(15 DOWNTO 0) OF BIT; 15. . . element indices. . . 0 0. . . array values. . . 1 VARIABLE X : reg_type; VARIABLE Y : BIT; Y : = X(4); -- Y gets value of element at index 4

Kompozitni tipovi. . . n Višedimenzioni vektor (matrica) type MEMORY is array (0 to 7, 0 to 3) of bit; . . . 8× 4 bit array constant ROM: MEMORY : = ( ('0', '0'), ('0', '1'), ('0', '1', '0'), ('0', '1', '0', '1'), ('0', '1', '0'), ('0', '1', '1')); variable DATA_BIT: bit; . . . -- access to one element: DATA_BIT : = ROM (5, 3);

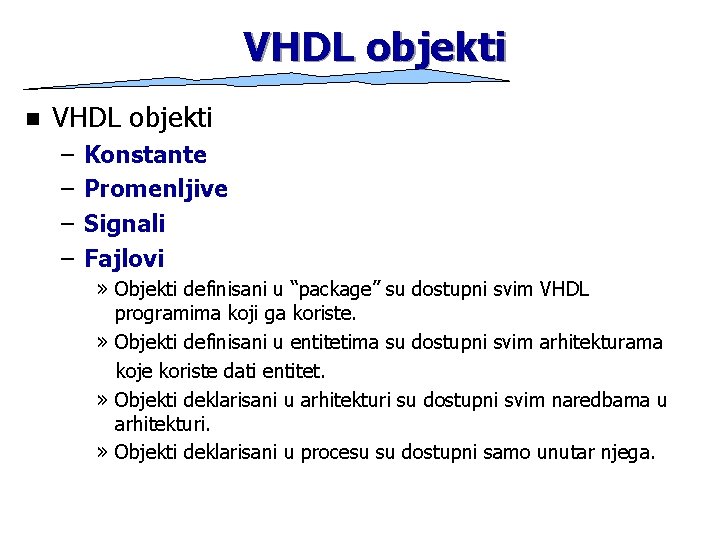

Kompozitni tipovi. . . n Struktura (Records) – Grupa elemenata različitog karaktera u jednom objektu – Elementi su indeksirani kroz ime polja – Primjer: TYPE binary IS ( ON, OFF ); TYPE switch_info IS RECORD status : BINARY; IDnumber : INTEGER; END RECORD; VARIABLE switch : switch_info; switch. status : = ON; -- status of the switch. IDnumber : = 30; -- e. g. number of the switch

Pristupni tip n Access – Slično kao “pointer” – Omogućava dinamičku alokaciju memorije – Pogodan za implemenatciju “stakova”, fifo: type CELL; -incomplete type LINK is access CELL; -- access type CELL is --- full type declaration for CELL record VALUE : integer; NEXTP : LINK; end; variable HEAD, TEMP : LINK; -- pointer to CELL. . . TEMP : = new CELL'(0, null); -- new data object with initial values for I in 1 to 5 loop HEAD : = new CELL; --additional objects HEAD. VALUE : = I; --access to record element HEAD. NEXTP : = TEMP; TEMP : = HEAD; end loop; . . . deallocate(TEMP); -- free the memory -- allocate new memory new CELL; new CELL'(I, TEMP); -- new object. . . with initial values

Pod-tipovi n Subtypes – Omogućava korisniku da definiše sopstvena ograničenja. – Može sadržavati definisane tipove ali u modifikovanom opsegu SUBTYPE name IS base_type RANGE <user range>; SUBTYPE first_ten IS INTEGER RANGE 0 TO 9;

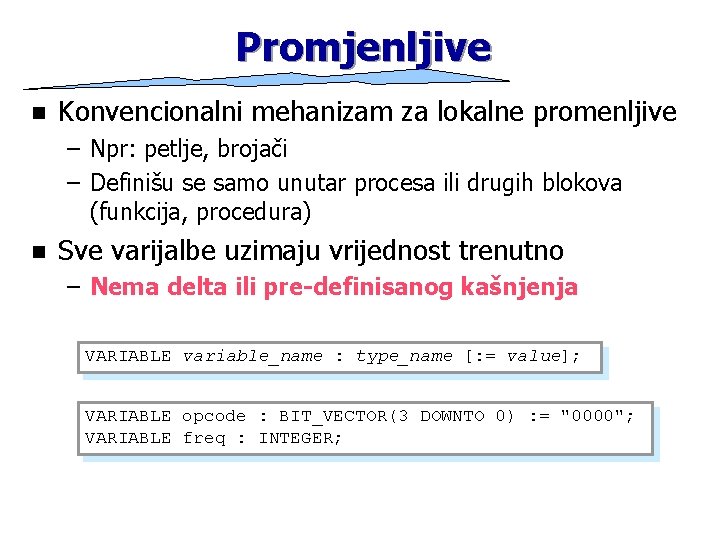

VHDL objekti n VHDL objekti – – Konstante Promenljive Signali Fajlovi » Objekti definisani u “package” su dostupni svim VHDL programima koji ga koriste. » Objekti definisani u entitetima su dostupni svim arhitekturama koje koriste dati entitet. » Objekti deklarisani u arhitekturi su dostupni svim naredbama u arhitekturi. » Objekti deklarisani u procesu su dostupni samo unutar njega.

Konstante n n Ime pridruženo za specifičnu vrijednost tipa Omogućava jednostavnije izmjene i dopune CONSTANT constant_name : type_name [: = value]; CONSTANT PI : REAL : = 3. 14; CONSTANT SPEED : INTEGER;

Promjenljive n Konvencionalni mehanizam za lokalne promenljive – Npr: petlje, brojači – Definišu se samo unutar procesa ili drugih blokova (funkcija, procedura) n Sve varijalbe uzimaju vrijednost trenutno – Nema delta ili pre-definisanog kašnjenja VARIABLE variable_name : type_name [: = value]; VARIABLE opcode : BIT_VECTOR(3 DOWNTO 0) : = "0000"; VARIABLE freq : INTEGER;

Signali n n Služe za komunikaciju izmedju VHDL komponenti Realni fizički signali (žice) Podrazumijevaju kašnjenje pridruživanju. Glavna razlika izmedju promenljivih i signala je pridruženo kašnjenje. SIGNAL signal_name : type_name [: = value]; SIGNAL brdy : BIT; brdy <= ‘ 0’ AFTER 5 ns, ‘ 1’ AFTER 10 ns;

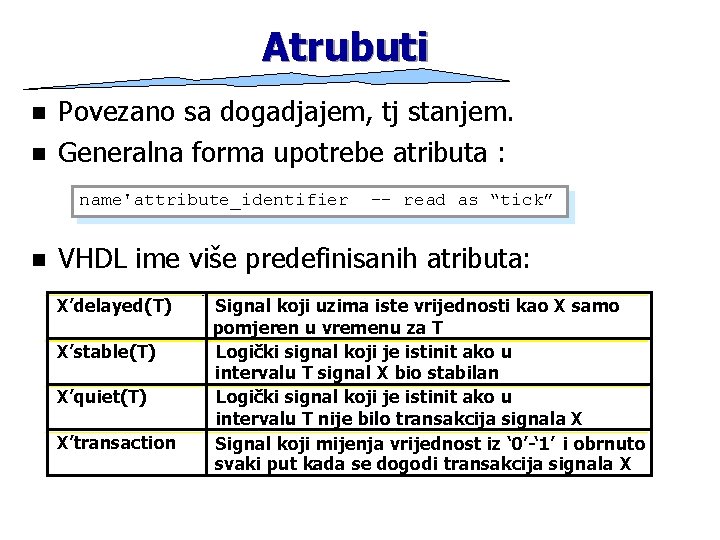

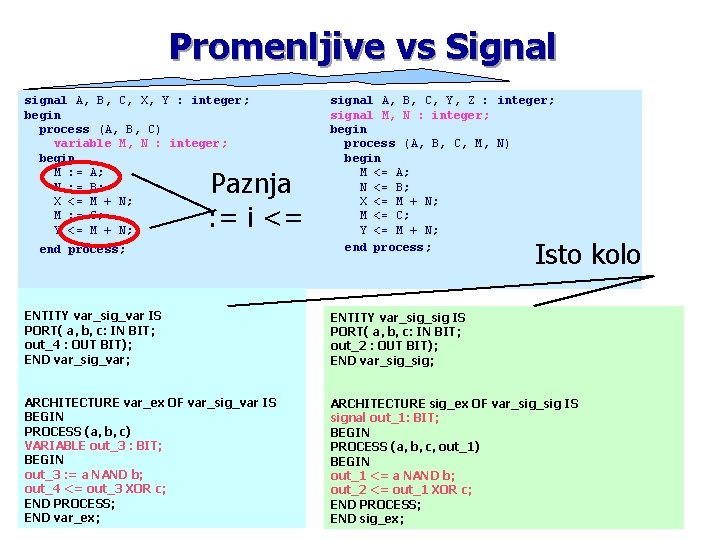

Promenljive vs Signal signal A, B, C, X, Y : integer; begin process (A, B, C) variable M, N : integer; begin M : = A; N : = B; X <= M + N; M : = C; Y <= M + N; Paznja : = i <= end process; signal A, B, C, Y, Z : integer; signal M, N : integer; begin process (A, B, C, M, N) begin M <= A; N <= B; X <= M + N; M <= C; Y <= M + N; end process; Isto kolo ENTITY var_sig_var IS PORT( a, b, c: IN BIT; out_4 : OUT BIT); END var_sig_var; ENTITY var_sig IS PORT( a, b, c: IN BIT; out_2 : OUT BIT); END var_sig; ARCHITECTURE var_ex OF var_sig_var IS BEGIN PROCESS (a, b, c) VARIABLE out_3 : BIT; BEGIN out_3 : = a NAND b; out_4 <= out_3 XOR c; END PROCESS; END var_ex; ARCHITECTURE sig_ex OF var_sig IS signal out_1: BIT; BEGIN PROCESS (a, b, c, out_1) BEGIN out_1 <= a NAND b; out_2 <= out_1 XOR c; END PROCESS; END sig_ex;

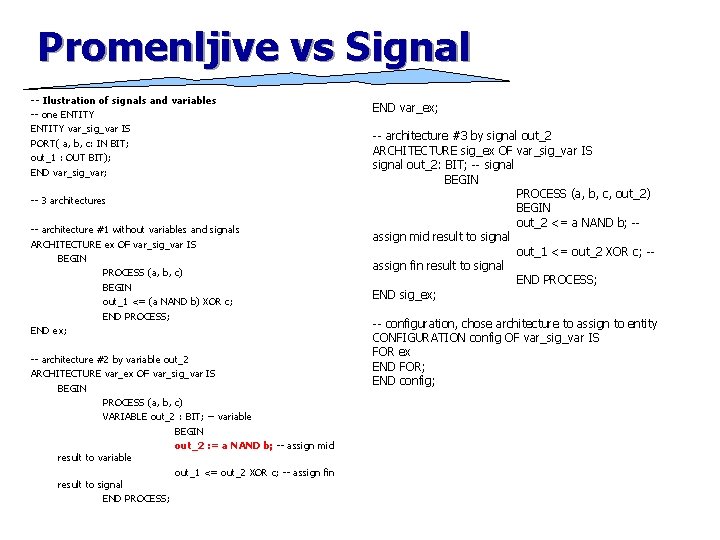

Promenljive vs Signal -- Ilustration of signals and variables -- one ENTITY var_sig_var IS PORT( a, b, c: IN BIT; out_1 : OUT BIT); END var_sig_var; -- 3 architectures -- architecture #1 without variables and signals ARCHITECTURE ex OF var_sig_var IS BEGIN PROCESS (a, b, c) BEGIN out_1 <= (a NAND b) XOR c; END PROCESS; END ex; -- architecture #2 by variable out_2 ARCHITECTURE var_ex OF var_sig_var IS BEGIN PROCESS (a, b, c) VARIABLE out_2 : BIT; -- variable BEGIN out_2 : = a NAND b; -- assign mid result to variable out_1 <= out_2 XOR c; -- assign fin result to signal END PROCESS; END var_ex; -- architecture #3 by signal out_2 ARCHITECTURE sig_ex OF var_sig_var IS signal out_2: BIT; -- signal BEGIN PROCESS (a, b, c, out_2) BEGIN out_2 <= a NAND b; -assign mid result to signal out_1 <= out_2 XOR c; -assign fin result to signal END PROCESS; END sig_ex; -- configuration, chose architecture to assign to entity CONFIGURATION config OF var_sig_var IS FOR ex END FOR; END config;

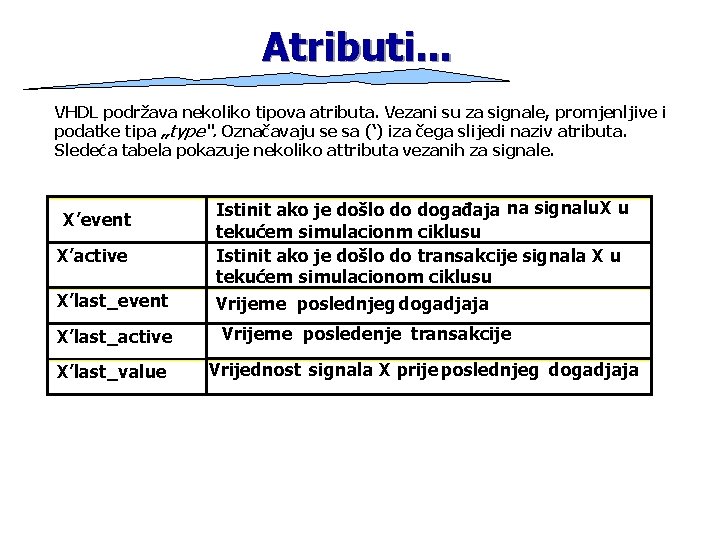

Promenljive vs Signal Variable se upotrebljavaju kada hocete da upotrebljavte “serijski kod”, za razliku od “parallelnog coda”. Variable, samo u processu pridruzivanje nije paralelno. Na primjer: signal a, b : std_logic_vector(0 to 4); process (CLK) begin if (rising_edge(clk)) then a <= '11111'; b <= a; end if; end process; stavlja b prije starta processa, ne '11111'. Sa druge strane kod signal a, b : std_logic_vector(0 to 4); process (CLK) variable var : std_logic_vector(0 to 4); begin if (rising_edge(clk)) then var : = '11111'; a <= var; b <= var; end if; end process; stavlja '11111' u a i b.

Atrubuti n n Povezano sa dogadjajem, tj stanjem. Generalna forma upotrebe atributa : name'attribute_identifier n -- read as “tick” VHDL ime više predefinisanih atributa: X’delayed(T) X’stable(T) X’quiet(T) X’transaction Signal koji uzima iste vrijednosti kao X samo pomjeren u vremenu za T Logički signal koji je istinit ako u intervalu T signal X bio stabilan Logički signal koji je istinit ako u intervalu T nije bilo transakcija signala X Signal koji mijenja vrijednost iz ‘ 0’-‘ 1’ i obrnuto svaki put kada se dogodi transakcija signala X

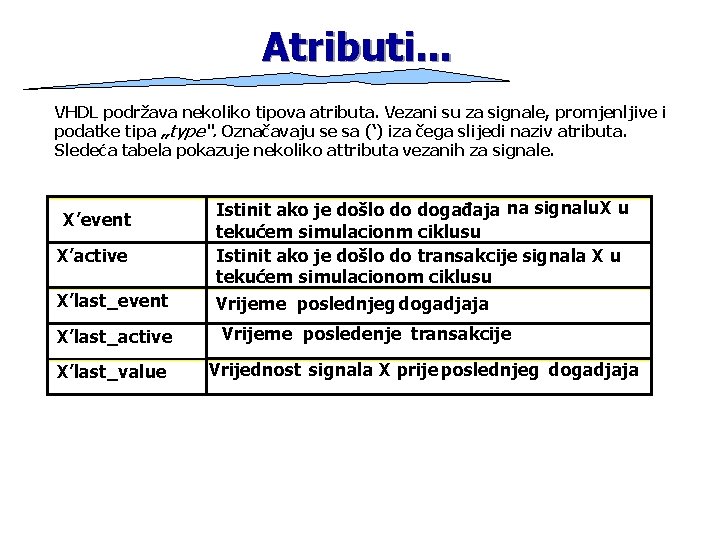

Atributi. . . VHDL podržava nekoliko tipova atributa. Vezani su za signale, promjenljive i podatke tipa „type“. Označavaju se sa (‘) iza čega slijedi naziv atributa. Sledeća tabela pokazuje nekoliko attributa vezanih za signale. X’event X’active X’last_event X’last_active X’last_value Istinit ako je došlo do događaja na signalu. X u tekućem simulacionm ciklusu Istinit ako je došlo do transakcije signala X u tekućem simulacionom ciklusu Vrijeme poslednjeg dogadjaja Vrijeme posledenje transakcije Vrijednost signala X prije poslednjeg dogadjaja

Primjer Atributi entity attr_ex is port (B, C : in bit; Z : out bit ); end attr_ex; 5 ns architecture test of attr_ex is signal A, C_delayed 5 : bit; begin A <= B and C; C_delayed 5 <= A'delayed(5 ns); Z<=C_delayed 5; end test; C B A Z

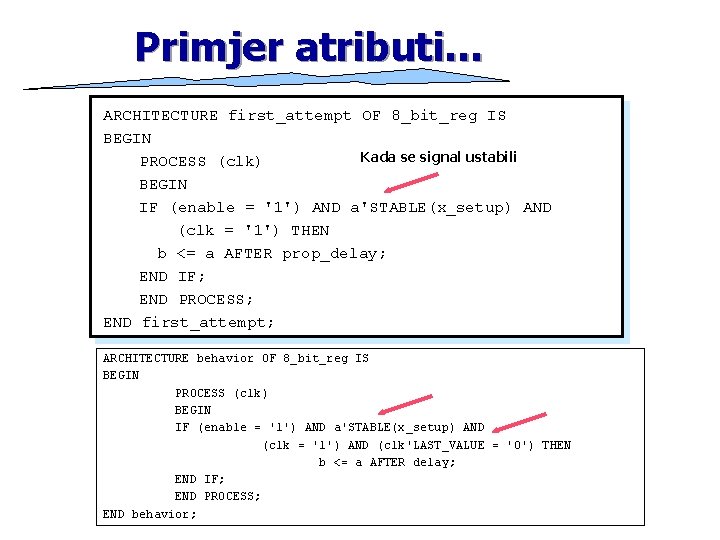

Atributi, primjer n n Kako se atributi mogu koristiti u primjeru 8 -bitnog registra. Specifikacija : – – Trigger na uzlaznoj ivici Lečovanje samo kada je enable high Data setup vrijeme x_setup Propagaciono kašnjenje prop_delay ENTITY 8_bit_reg IS GENERIC (x_setup, prop_delay : TIME); PORT(enable, clk : IN qsim_state; a : IN qsim_state_vector(7 DOWNTO 0); b : OUT qsim_state_vector(7 DOWNTO 0)); END 8_bit_reg; lqsim_state predefinisan tip sa parametrima 0, 1, X, i Z

Primjer atributi… ARCHITECTURE first_attempt OF 8_bit_reg IS BEGIN Kada se signal ustabili PROCESS (clk) BEGIN IF (enable = '1') AND a'STABLE(x_setup) AND (clk = '1') THEN b <= a AFTER prop_delay; END IF; END PROCESS; END first_attempt; ARCHITECTURE behavior OF 8_bit_reg IS BEGIN PROCESS (clk) BEGIN IF (enable = '1') AND a'STABLE(x_setup) AND (clk = '1') AND (clk'LAST_VALUE = '0') THEN b <= a AFTER delay; END IF; END PROCESS; END behavior;

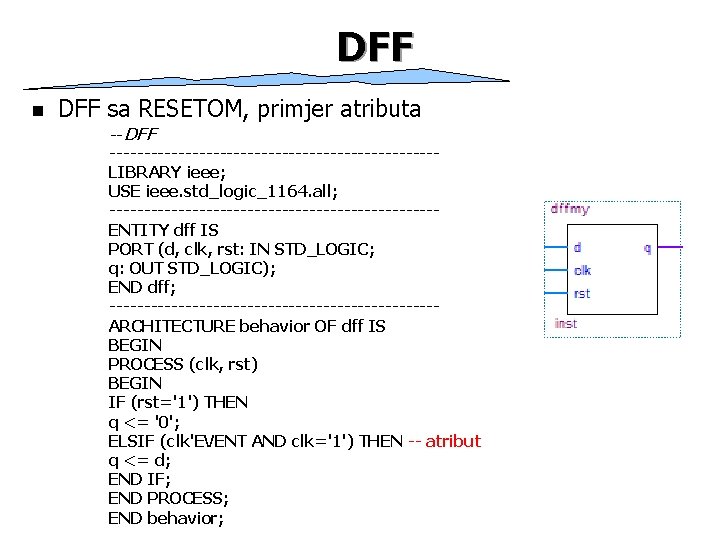

DFF n DFF sa RESETOM, primjer atributa -- DFF ------------------------LIBRARY ieee; USE ieee. std_logic_1164. all; ------------------------ENTITY dff IS PORT (d, clk, rst: IN STD_LOGIC; q: OUT STD_LOGIC); END dff; ------------------------ARCHITECTURE behavior OF dff IS BEGIN PROCESS (clk, rst) BEGIN IF (rst='1') THEN q <= '0'; ELSIF (clk'EVENT AND clk='1') THEN -- atribut q <= d; END IF; END PROCESS; END behavior;

GENERIC Promjenljiva koja je deklarisana korišćenjem ključne riječi GENERIC predstavlja konstantu koja se može samo čitati. Ova riječ se upotrebljava najčešće kada je potrebno projektovati dizajn čiji se neki od parametara mogu mijenjati (npr. dubina i širina memorije, dužina registra i sl. ). Za dizajnera je mnogo jednostavnije da napravi komponentu koja se u daljem radu može koristiti nezavisno od parametara kakvi su već navedeni. · Primjer: library ieee; use ieee. std_logic_1164. all; use ieee. numeric_std. all; entity signed_adder is generic (DATA_WIDTH : natural : = 8); port ( a : in signed ((DATA_WIDTH-1) downto 0); b : in signed ((DATA_WIDTH-1) downto 0); result : out signed ((DATA_WIDTH-1) downto 0) ); end entity;

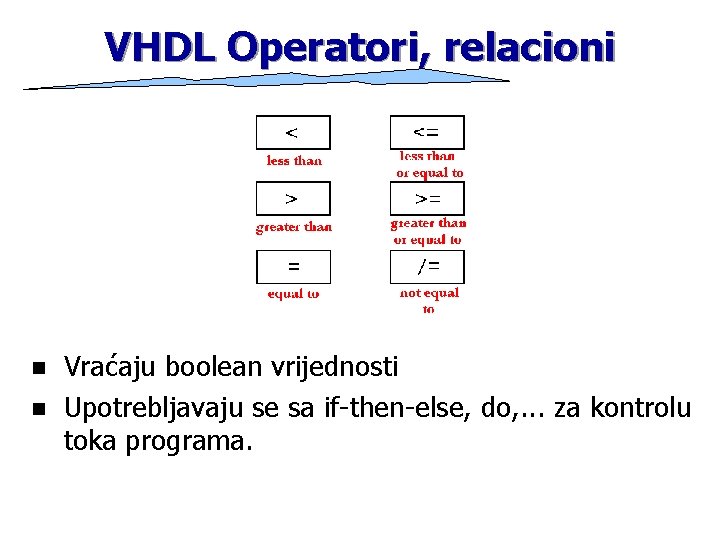

Primjer Generic entity Gen_Gates is generic (Delay : Time : = 10 ns); port (In 1, In 2 : in bit; Output : out bit); end Gen_Gates; architecture Gates of Gen_Gates is begin Output <= In 1 or In 2 after Delay; end Gates; In 1 In 2 Output Parametar se mijenja lako Simbol

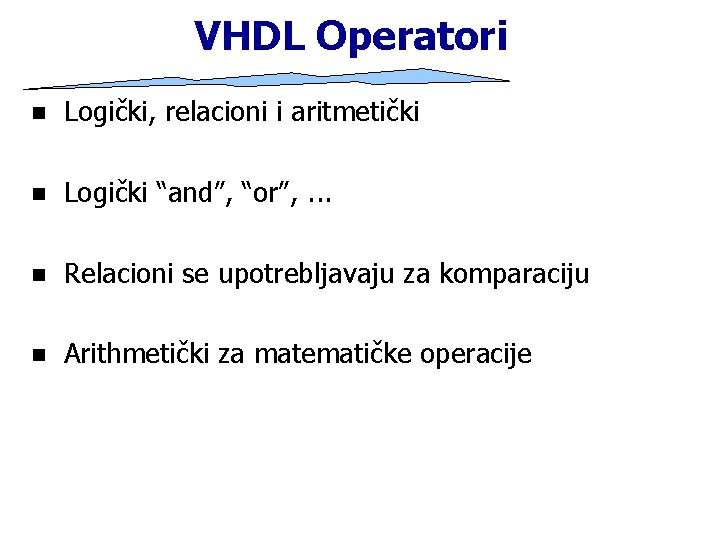

VHDL Operatori n Logički, relacioni i aritmetički n Logički “and”, “or”, . . . n Relacioni se upotrebljavaju za komparaciju n Arithmetički za matematičke operacije

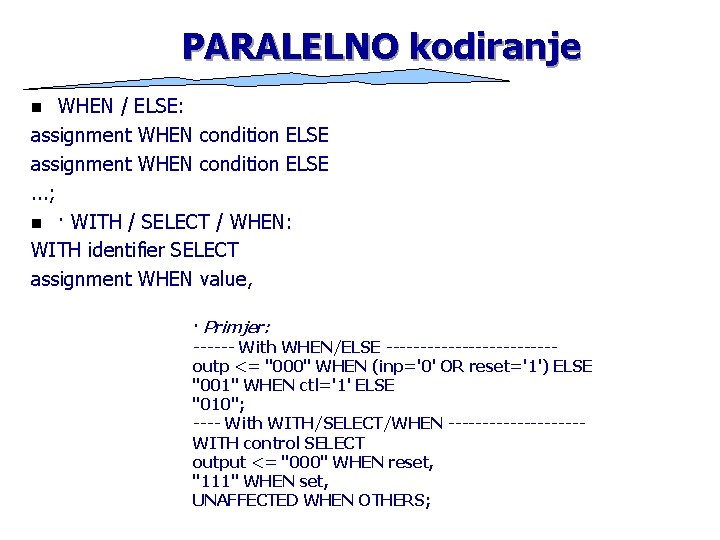

VHDL Operatori, relacioni n n Vraćaju boolean vrijednosti Upotrebljavaju se sa if-then-else, do, . . . za kontrolu toka programa.

VHDL Operatori, arithmetički n n Za tipove integer, real, . . Ne primenjuju se za vektore

NAČINI MODELOVANJA (kodiranja) n VHDL kod može biti paralelan (concurrent), sekvencijalan i strukturalan. Ova podjela je vrlo bitna jer, omogućava bolje razumijevanje kakve se komande koriste gdje, kao i posledice primjene jednog odnosno drugog načina.

PARALELNO kodiranje WHEN / ELSE: assignment WHEN condition ELSE. . . ; n · WITH / SELECT / WHEN: WITH identifier SELECT assignment WHEN value, n · Primjer: ------ With WHEN/ELSE ------------outp <= "000" WHEN (inp='0' OR reset='1') ELSE "001" WHEN ctl='1' ELSE "010"; ---- With WITH/SELECT/WHEN ----------WITH control SELECT output <= "000" WHEN reset, "111" WHEN set, UNAFFECTED WHEN OTHERS;

Sekvencijalno modelovanje n n n Processes If-then-else Case For While

Process n Sekvencijalno izvršenje naredbi n Sintaksa: Opciono label, ključna riječ “PROCESS”, i sensitivna lista

Process… n n n Izvršava se kontinualno Aktivira se kada se neki od signala u sensitivnoj listi promijeni, ili ima neki “event”. Sensitivna lista mora biti kompletna da bi se proces uspješno odvijao.

IF n n “if” testira uslov, i izvršava različit set komandi u zavisnosti od rezultata. Dvije forme if-then i the if-then-else

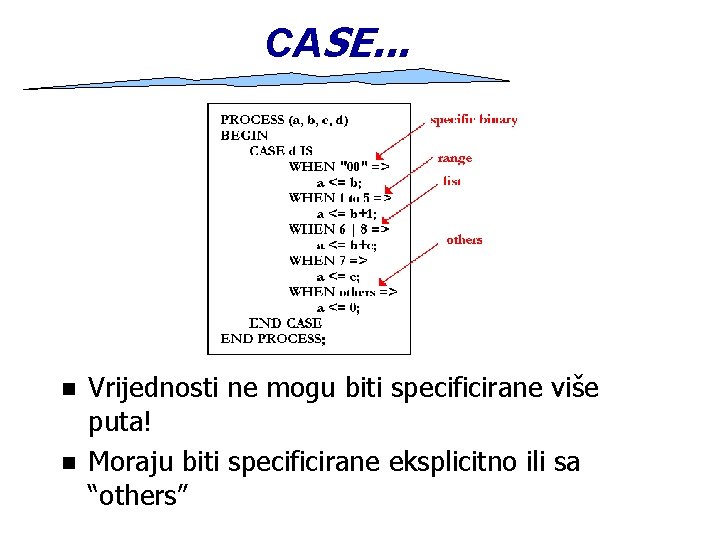

IF-ELSIF n n IF-ELSEIF omogućava testiranje serije uslova, i prvi uslov koji je tačan uzrokovaće izvršenje naradbi koje slijede iza njega. Tok se nastavlja poslije END IF riječi Redosled uslova je značajan Može biti više njih tačnih ali prvi ima prioritet.

IF-ELSIF Primjer n n n Ako je x= “ 0000”, tada su oba seta uslova zadovoljena. Kako je x = “ 0000” testirano prvo, z će poprimiti vrijednost a. IF-ELSIF ima ugradjeni prioritet.

CASE n CASE uzima u obzir sve moguće vrijednosti koje jedan izraz može da poprimi i izvršava naredbe specificirane za aktuelnu vrijednost.

CASE. . . n n Vrijednosti ne mogu biti specificirane više puta! Moraju biti specificirane eksplicitno ili sa “others”

FOR Petlja n Standardna For petlja

WHILE n Ovo je petlja koja se ponavlja sve do onog momenta do koga je zadovoljen neki uslov. n Sintaksa: [label: ] WHILE condition LOOP (sequential statements) END LOOP [label]; · Primjer: WHILE (i < 10) LOOP WAIT UNTIL clk'EVENT AND clk='1'; (other statements) END LOOP;

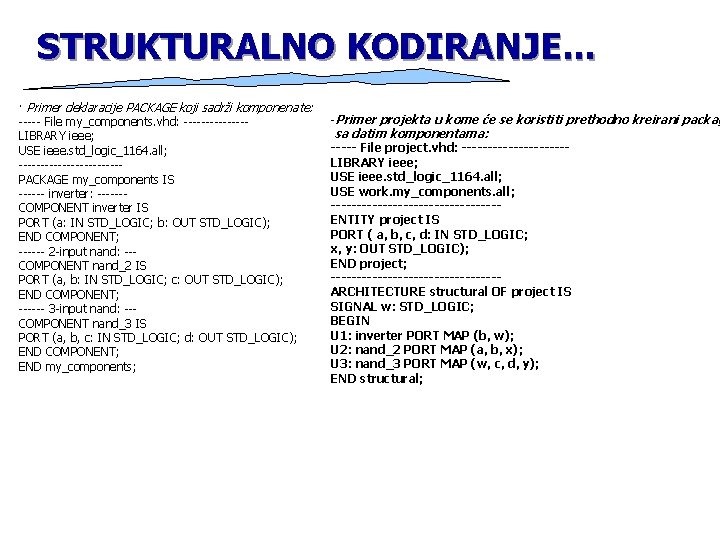

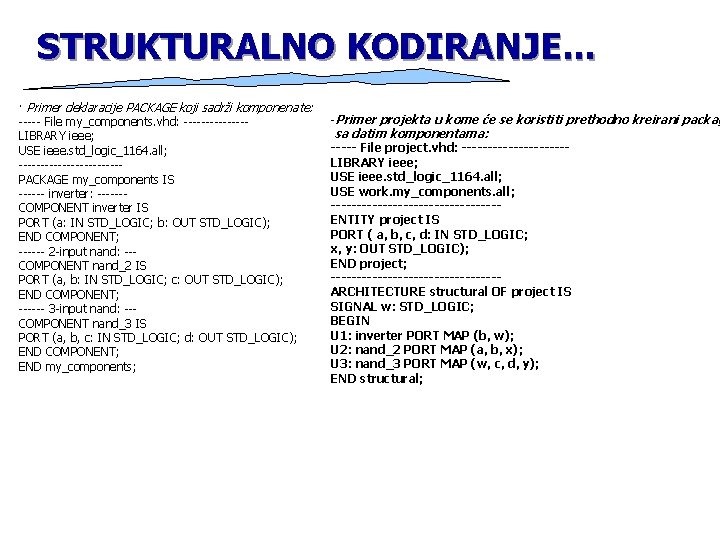

STRUKTURALNO KODIRANJE n Strukturno modelovanje omogućava manuelnu konekciju više komponenata u funkcionalnu cjelinu upotebom signala za povezivanje. Sve komponente koje se koriste moraju prethodno biti definisane svojim entitetom i arhitekturom što može biti u posebnim ili zajedničkom fajlu. Strukturno modelovanje je slično sastavljanju šeme složenog kola iz komponenti.

STRUKTURALNO KODIRANJE. . . n COMPONENT – Sintaksa deklaracije komponente: COMPONENT component_name IS PORT ( port_name : signal_mode signal_type; . . . ); END COMPONENT; - Sintaksa povezivanja komponente: label: component_name PORT MAP (port_list);

STRUKTURALNO KODIRANJE. . . · Primer deklaracije PACKAGE koji sadrži komponenate: ----- File my_components. vhd: -------LIBRARY ieee; USE ieee. std_logic_1164. all; ------------PACKAGE my_components IS ------ inverter: ------COMPONENT inverter IS PORT (a: IN STD_LOGIC; b: OUT STD_LOGIC); END COMPONENT; ------ 2 -input nand: --COMPONENT nand_2 IS PORT (a, b: IN STD_LOGIC; c: OUT STD_LOGIC); END COMPONENT; ------ 3 -input nand: --COMPONENT nand_3 IS PORT (a, b, c: IN STD_LOGIC; d: OUT STD_LOGIC); END COMPONENT; END my_components; -Primer projekta u kome će se koristiti prethodno kreirani packag sa datim komponentama: ----- File project. vhd: ----------LIBRARY ieee; USE ieee. std_logic_1164. all; USE work. my_components. all; ----------------ENTITY project IS PORT ( a, b, c, d: IN STD_LOGIC; x, y: OUT STD_LOGIC); END project; ----------------ARCHITECTURE structural OF project IS SIGNAL w: STD_LOGIC; BEGIN U 1: inverter PORT MAP (b, w); U 2: nand_2 PORT MAP (a, b, x); U 3: nand_3 PORT MAP (w, c, d, y); END structural;

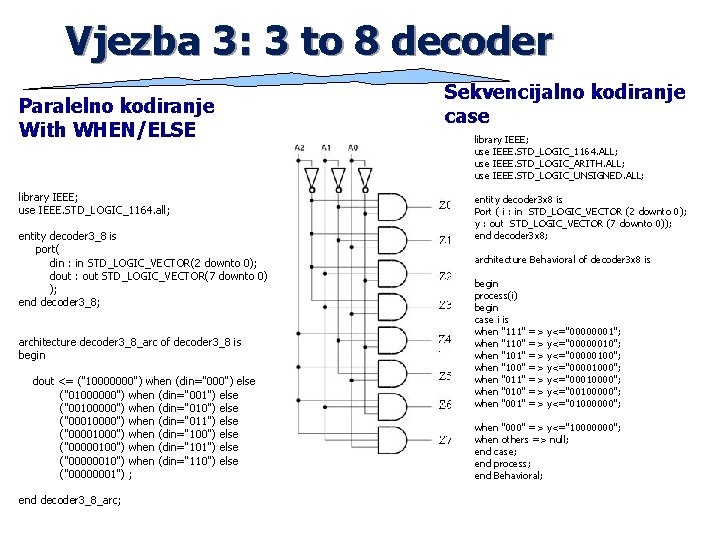

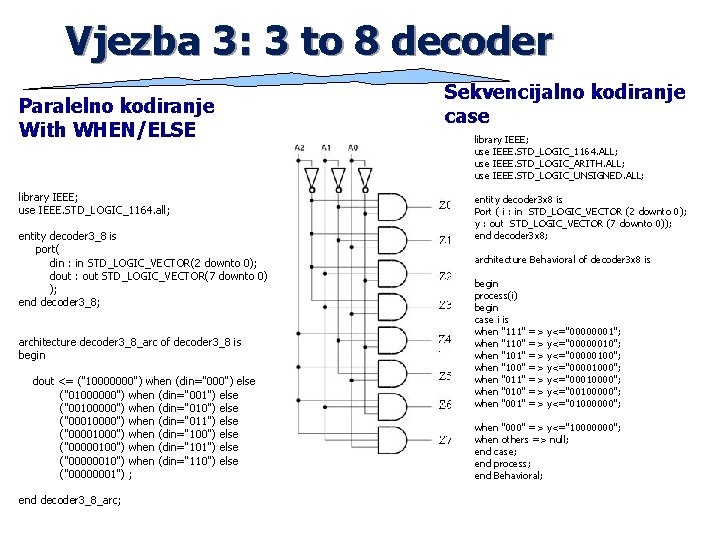

Vjezba 3: 3 to 8 decoder Paralelno kodiranje With WHEN/ELSE library IEEE; use IEEE. STD_LOGIC_1164. all; entity decoder 3_8 is port( din : in STD_LOGIC_VECTOR(2 downto 0); dout : out STD_LOGIC_VECTOR(7 downto 0) ); end decoder 3_8; architecture decoder 3_8_arc of decoder 3_8 is begin dout <= ("10000000") when (din="000") else ("01000000") when (din="001") else ("00100000") when (din="010") else ("00010000") when (din="011") else ("00001000") when (din="100") else ("00000100") when (din="101") else ("00000010") when (din="110") else ("00000001") ; end decoder 3_8_arc; Sekvencijalno kodiranje case library IEEE; use IEEE. STD_LOGIC_1164. ALL; use IEEE. STD_LOGIC_ARITH. ALL; use IEEE. STD_LOGIC_UNSIGNED. ALL; entity decoder 3 x 8 is Port ( i : in STD_LOGIC_VECTOR (2 downto 0); y : out STD_LOGIC_VECTOR (7 downto 0)); end decoder 3 x 8; architecture Behavioral of decoder 3 x 8 is begin process(i) begin case i is when "111" when "110" when "101" when "100" when "011" when "010" when "001" => => y<="00000001"; y<="00000010"; y<="00000100"; y<="00001000"; y<="00010000"; y<="00100000"; y<="01000000"; when "000" => y<="10000000"; when others => null; end case; end process; end Behavioral;

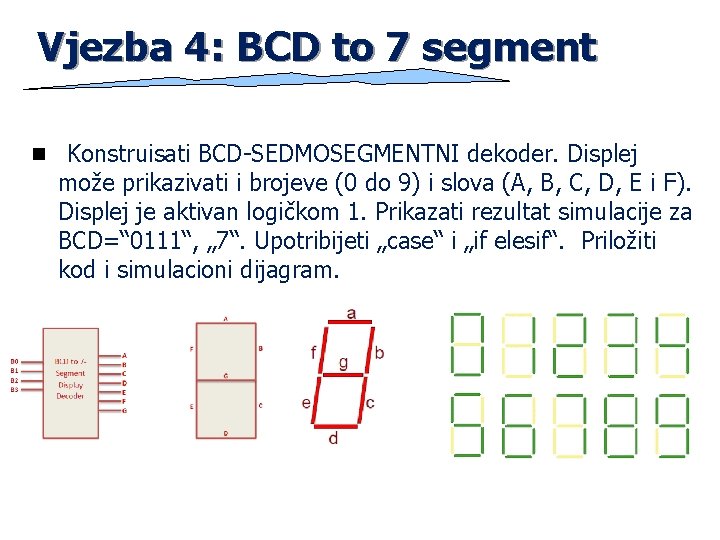

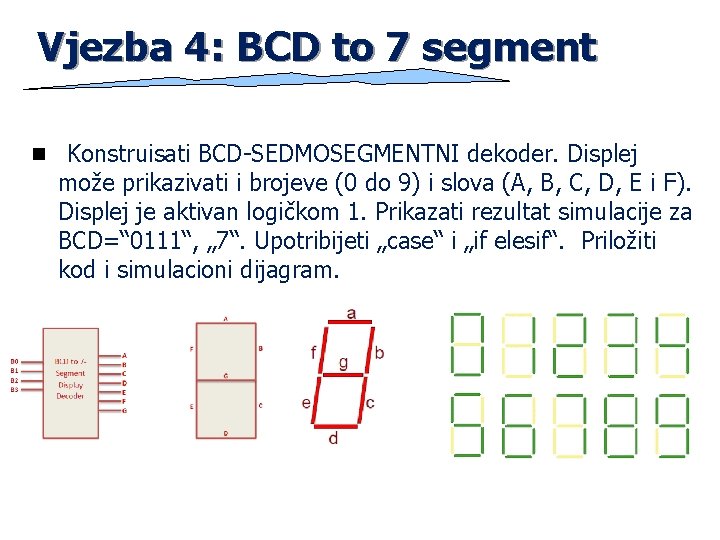

Vjezba 4: BCD to 7 segment n Konstruisati BCD-SEDMOSEGMENTNI dekoder. Displej može prikazivati i brojeve (0 do 9) i slova (A, B, C, D, E i F). Displej je aktivan logičkom 1. Prikazati rezultat simulacije za BCD=“ 0111“, „ 7“. Upotribijeti „case“ i „if elesif“. Priložiti kod i simulacioni dijagram.

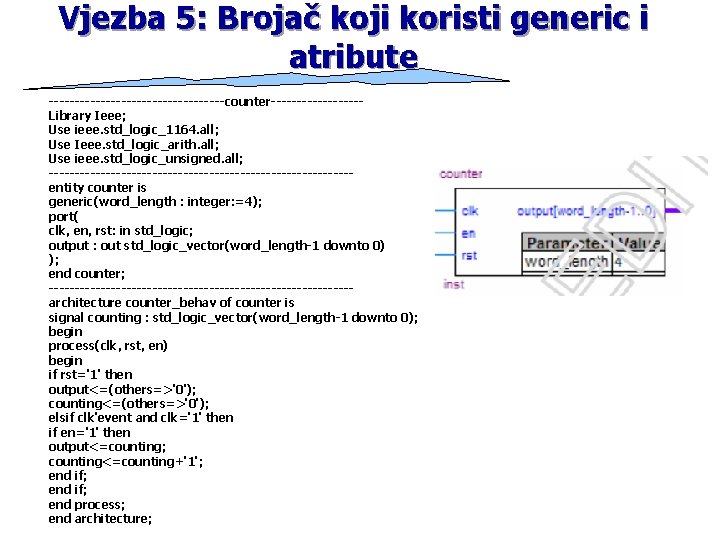

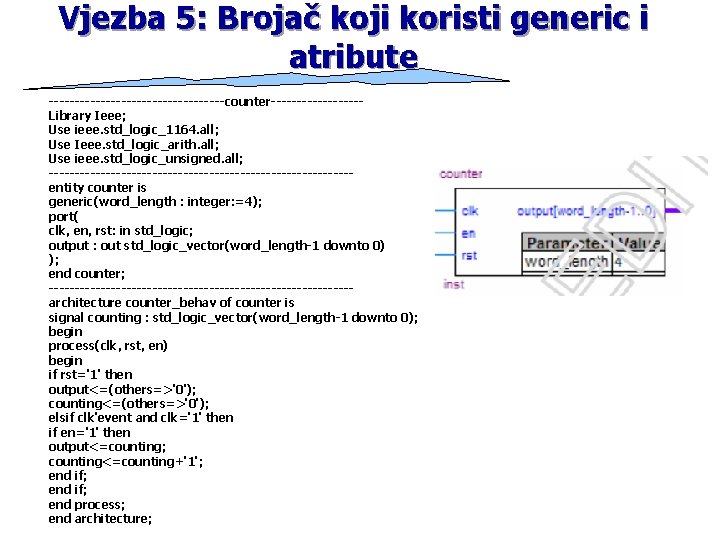

Vjezba 5: Brojač koji koristi generic i atribute -----------------counter---------Library Ieee; Use ieee. std_logic_1164. all; Use Ieee. std_logic_arith. all; Use ieee. std_logic_unsigned. all; -----------------------------entity counter is generic(word_length : integer: =4); port( clk, en, rst: in std_logic; output : out std_logic_vector(word_length-1 downto 0) ); end counter; -----------------------------architecture counter_behav of counter is signal counting : std_logic_vector(word_length-1 downto 0); begin process(clk, rst, en) begin if rst='1' then output<=(others=>'0'); counting<=(others=>'0'); elsif clk'event and clk='1' then if en='1' then output<=counting; counting<=counting+'1'; end if; end process; end architecture;

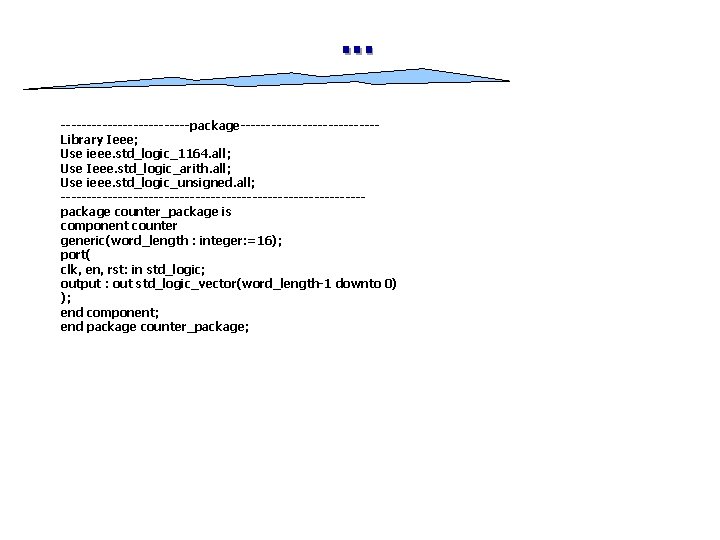

. . . -------------package-------------Library Ieee; Use ieee. std_logic_1164. all; Use Ieee. std_logic_arith. all; Use ieee. std_logic_unsigned. all; -----------------------------package counter_package is component counter generic(word_length : integer: =16); port( clk, en, rst: in std_logic; output : out std_logic_vector(word_length-1 downto 0) ); end component; end package counter_package;

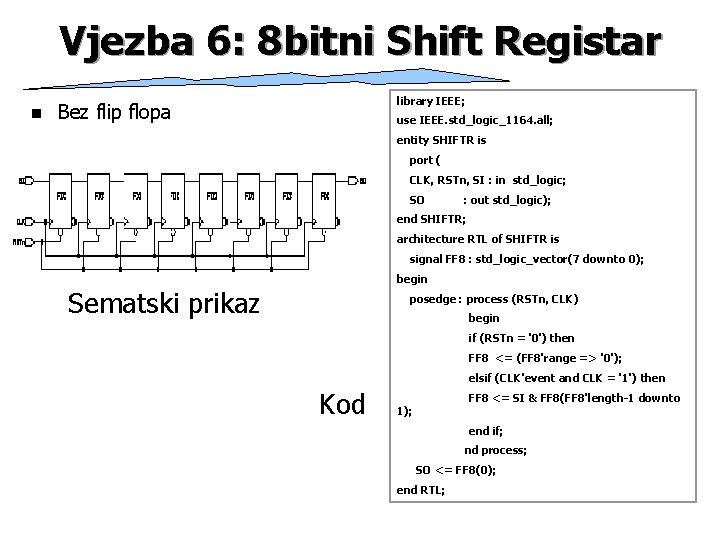

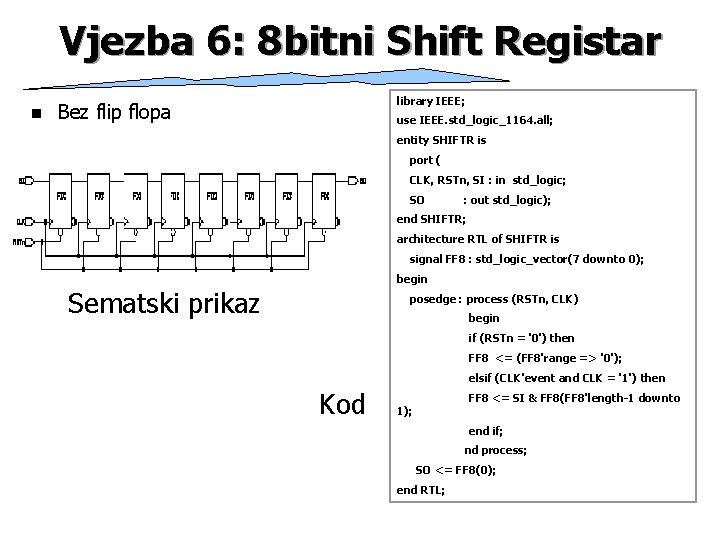

Vjezba 6: 8 bitni Shift Registar n library IEEE; Bez flip flopa use IEEE. std_logic_1164. all; entity SHIFTR is port ( CLK, RSTn, SI : in std_logic; SO : out std_logic); end SHIFTR; architecture RTL of SHIFTR is signal FF 8 : std_logic_vector(7 downto 0); begin Sematski prikaz posedge : process (RSTn, CLK) begin if (RSTn = '0') then FF 8 <= (FF 8'range => '0'); elsif (CLK'event and CLK = '1') then Kod FF 8 <= SI & FF 8(FF 8'length-1 downto 1); end if; nd process; SO <= FF 8(0); end RTL;

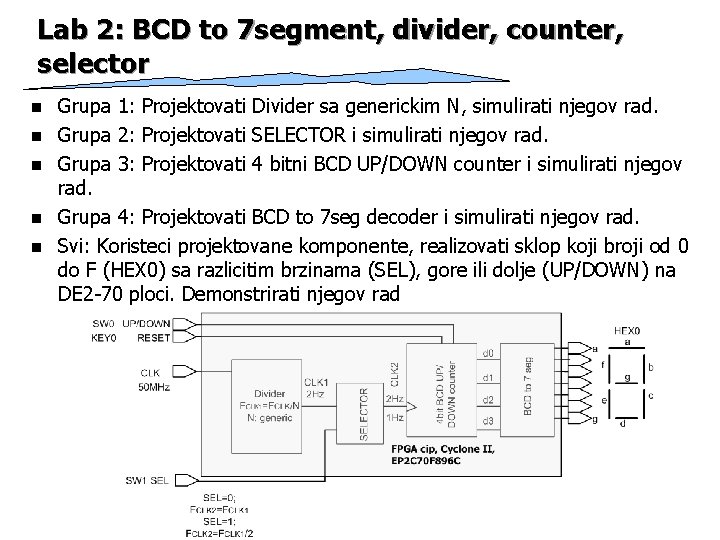

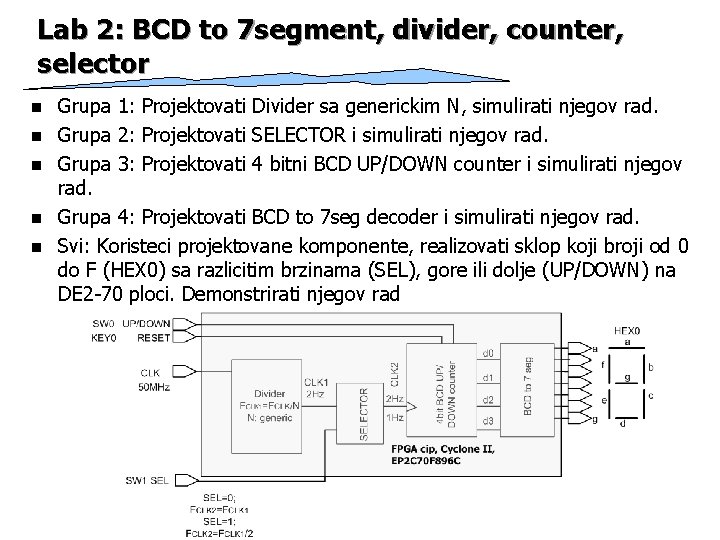

Lab 2: BCD to 7 segment, divider, counter, selector n n n Grupa 1: Projektovati Divider sa generickim N, simulirati njegov rad. Grupa 2: Projektovati SELECTOR i simulirati njegov rad. Grupa 3: Projektovati 4 bitni BCD UP/DOWN counter i simulirati njegov rad. Grupa 4: Projektovati BCD to 7 seg decoder i simulirati njegov rad. Svi: Koristeci projektovane komponente, realizovati sklop koji broji od 0 do F (HEX 0) sa razlicitim brzinama (SEL), gore ili dolje (UP/DOWN) na DE 2 -70 ploci. Demonstrirati njegov rad

Domaći #2 a) b) c) Simulirati rad ring brojaca koji se pogoni klokom od 1 s (J 1 zatvoren, slika 1). Simulirati rad Jonson brojaca koji se pogoni klokom od 1 s (J 1 otvoren, slika 1) Kolo realizovati na DE 2 -70 ploci. J 1 se realizuje digitalno (slika 2). D 0 slika 2 D 1 D 3 J 1 0 2 1 Clk=1 s 3 not slika 1

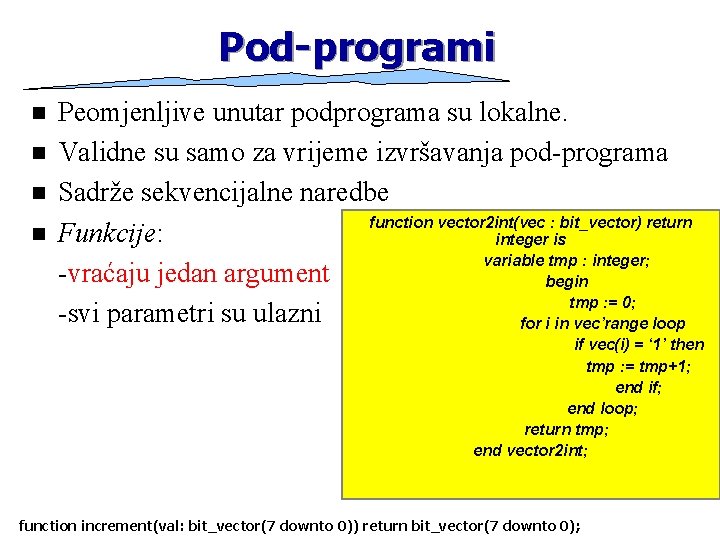

Podprogrami n U VHDLu postoje dva tipa podprograma: procedure i funkcije. Moraju imati deklaraciju i definiciju. Slicno kao u Cu. Omogucavaju preglednost programa, medjutim treba biti pazljiv pri radu sa njima. Ne zaboravite ovo je hardverski jezik.

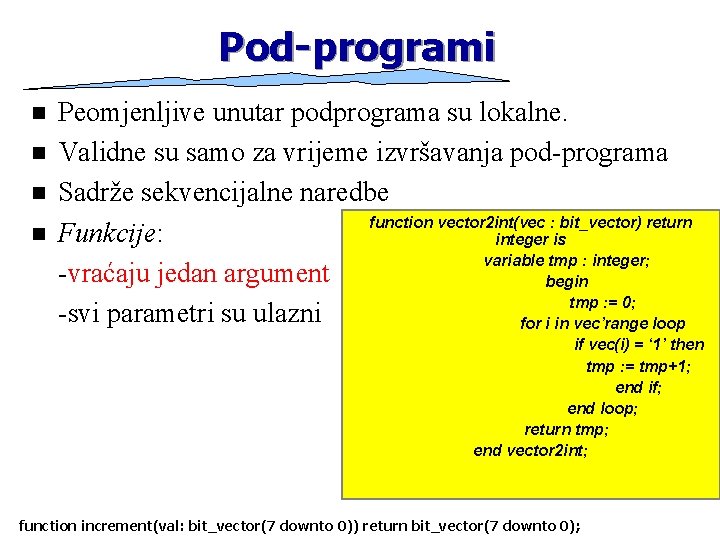

Pod-programi n n Peomjenljive unutar podprograma su lokalne. Validne su samo za vrijeme izvršavanja pod-programa Sadrže sekvencijalne naredbe function vector 2 int(vec : bit_vector) return Funkcije: integer is variable tmp : integer; -vraćaju jedan argument begin tmp : = 0; -svi parametri su ulazni for i in vec’range loop if vec(i) = ‘ 1’ then tmp : = tmp+1; end if; end loop; return tmp; end vector 2 int; function increment(val: bit_vector(7 downto 0)) return bit_vector(7 downto 0);

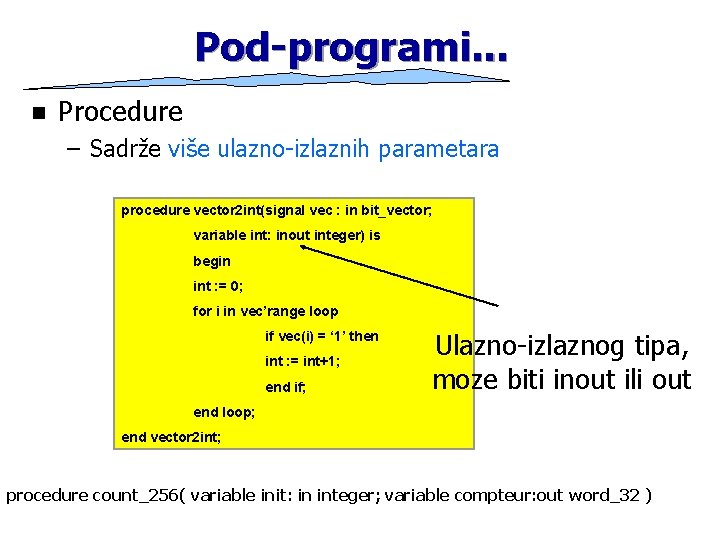

Pod-programi. . . n Procedure – Sadrže više ulazno-izlaznih parametara procedure vector 2 int(signal vec : in bit_vector; variable int: inout integer) is begin int : = 0; for i in vec’range loop if vec(i) = ‘ 1’ then int : = int+1; end if; Ulazno-izlaznog tipa, moze biti inout ili out end loop; end vector 2 int; procedure count_256( variable init: in integer; variable compteur: out word_32 )

Pod-programi. . . n Poziv procedure Myproc 1(my_signal, my_variable, 1); Myproc 1(formal 1 => ‘ 1’, formal 2=>” 111” , formal 3 =>1); Myprocedure 3; --No parameters

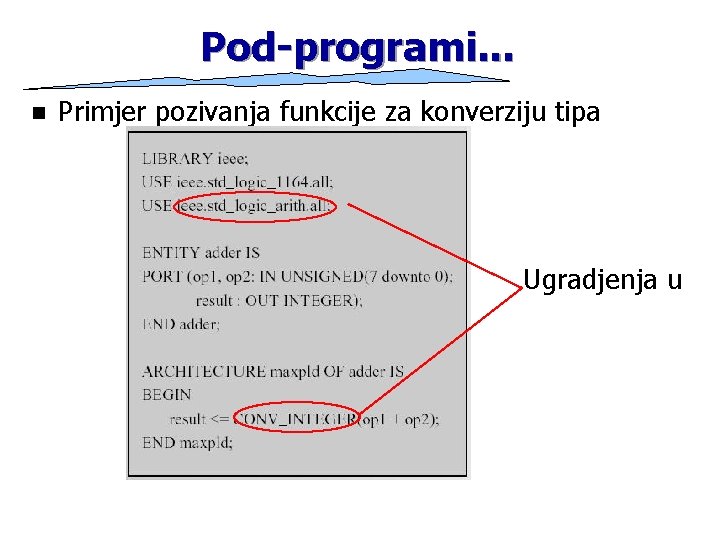

Pod-programi. . . n Primjer pozivanja funkcije za konverziju tipa Ugradjenja u

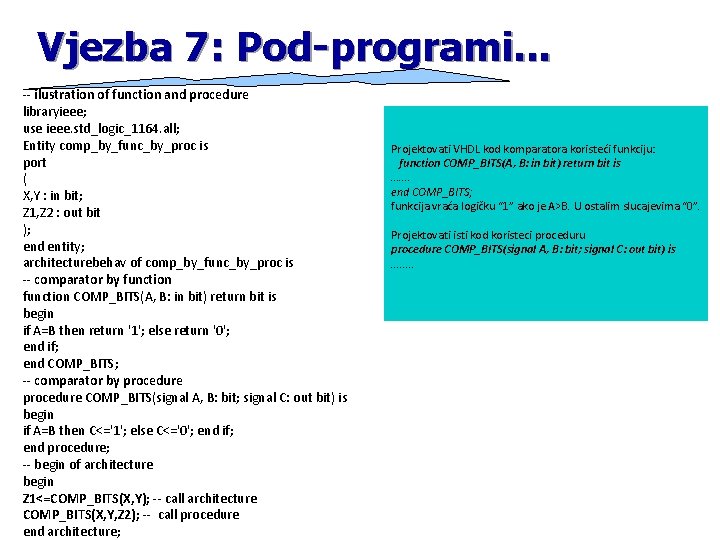

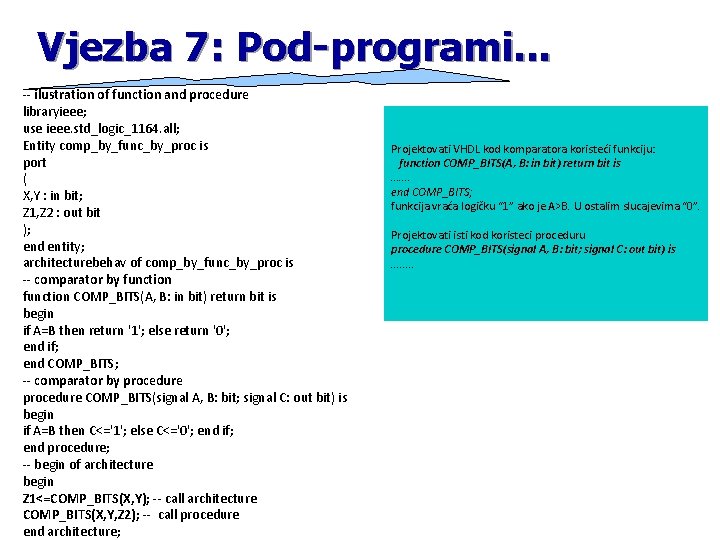

Vjezba 7: Pod-programi. . . -- ilustration of function and procedure libraryieee; use ieee. std_logic_1164. all; Entity comp_by_func_by_proc is port ( X, Y : in bit; Z 1, Z 2 : out bit ); end entity; architecturebehav of comp_by_func_by_proc is -- comparator by function COMP_BITS(A, B: in bit) return bit is begin if A=B then return '1'; else return '0'; end if; end COMP_BITS; -- comparator by procedure COMP_BITS(signal A, B: bit; signal C: out bit) is begin if A=B then C<='1'; else C<='0'; end if; end procedure; -- begin of architecture begin Z 1<=COMP_BITS(X, Y); -- call architecture COMP_BITS(X, Y, Z 2); -- call procedure end architecture; Projektovati VHDL kod komparatora koristeći funkciju: function COMP_BITS(A, B: in bit) return bit is ……. end COMP_BITS; funkcija vraća logičku “ 1” ako je A>B. U ostalim slucajevima “ 0”. Projektovati isti kod koristeci proceduru procedure COMP_BITS(signal A, B: bit; signal C: out bit) is. . . .

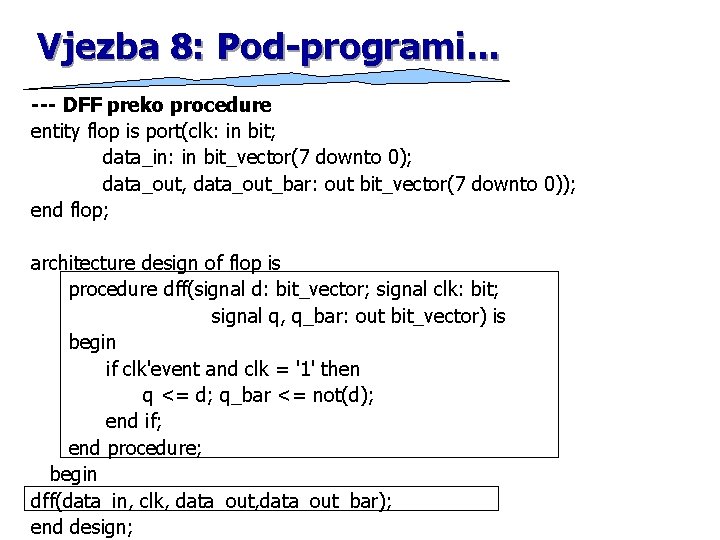

Vjezba 8: Pod-programi. . . --- DFF preko procedure entity flop is port(clk: in bit; data_in: in bit_vector(7 downto 0); data_out, data_out_bar: out bit_vector(7 downto 0)); end flop; architecture design of flop is procedure dff(signal d: bit_vector; signal clk: bit; signal q, q_bar: out bit_vector) is begin if clk'event and clk = '1' then q <= d; q_bar <= not(d); end if; end procedure; begin dff(data_in, clk, data_out_bar); end design;

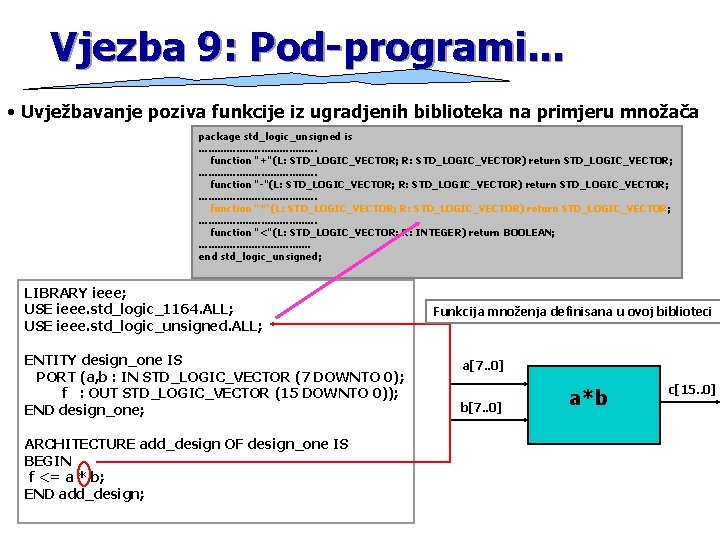

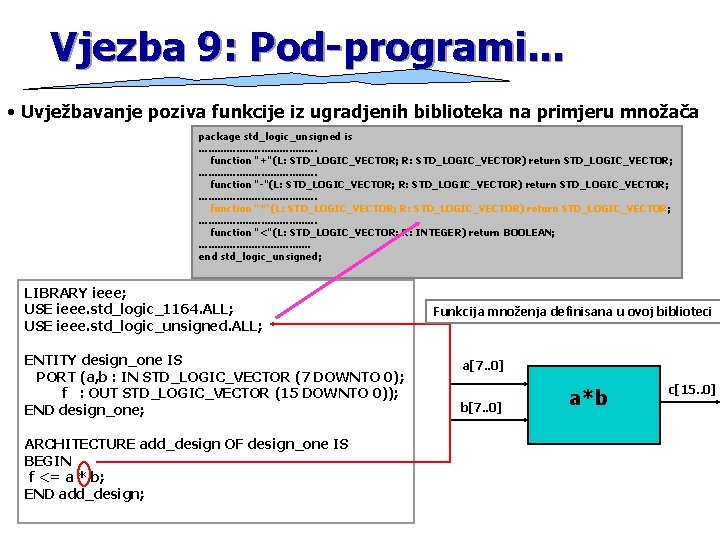

Vjezba 9: Pod-programi. . . • Uvježbavanje poziva funkcije iz ugradjenih biblioteka na primjeru množača package std_logic_unsigned is. . . . . function "+"(L: STD_LOGIC_VECTOR; R: STD_LOGIC_VECTOR) return STD_LOGIC_VECTOR; . . function "-"(L: STD_LOGIC_VECTOR; R: STD_LOGIC_VECTOR) return STD_LOGIC_VECTOR; . . function "*"(L: STD_LOGIC_VECTOR; R: STD_LOGIC_VECTOR) return STD_LOGIC_VECTOR; . . function "<"(L: STD_LOGIC_VECTOR; R: INTEGER) return BOOLEAN; . . end std_logic_unsigned; LIBRARY ieee; USE ieee. std_logic_1164. ALL; USE ieee. std_logic_unsigned. ALL; ENTITY design_one IS PORT (a, b : IN STD_LOGIC_VECTOR (7 DOWNTO 0); f : OUT STD_LOGIC_VECTOR (15 DOWNTO 0)); END design_one; ARCHITECTURE add_design OF design_one IS BEGIN f <= a * b; END add_design; Funkcija množenja definisana u ovoj biblioteci a[7. . 0] b[7. . 0] a*b c[15. . 0]

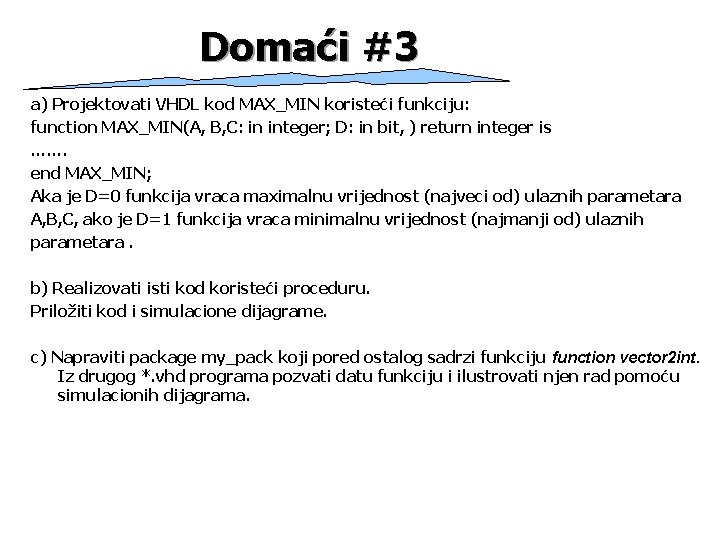

Domaći #3 a) Projektovati VHDL kod MAX_MIN koristeći funkciju: function MAX_MIN(A, B, C: in integer; D: in bit, ) return integer is ……. end MAX_MIN; Aka je D=0 funkcija vraca maximalnu vrijednost (najveci od) ulaznih parametara A, B, C, ako je D=1 funkcija vraca minimalnu vrijednost (najmanji od) ulaznih parametara. b) Realizovati isti kod koristeći proceduru. Priložiti kod i simulacione dijagrame. c) Napraviti package my_pack koji pored ostalog sadrzi funkciju function vector 2 int. Iz drugog *. vhd programa pozvati datu funkciju i ilustrovati njen rad pomoću simulacionih dijagrama.

Domaći #3… d) Projektovati VHDL kod koji će polu-sabirač realizovati pomoću funkcije ADD_BITS(X, Y) tako da se izlazni signali mogu izraziti preko ulaznih u formi. . . RESULT<=ADD_BITS(X, Y); CARRY<=X AND Y; . . . Funkcija ADD_BITS ima oblik function ADD_BITS(A, B: in bit) return bit is begin return(A XOR B) end ADD_BITS; Isti kod realizovati preko procedure ADD_BITS(signal A, B: bit; signal q: out bit) is begin q<=A XOR B; end procedure; #3 State Machine Detektor binarne sekvence “ 1110101101” Priložiti VHDL kog i simulacione dijagrame.

Domaći #4… State Machine: Procitati (lektira): https: //www. allaboutcircuits. com/technical-articles/implementing-a-finite-state -machine-in-vhdl/ https: //www. xilinx. com/support/documentation/university/Vivado. Teaching/HDL-Design/2015 x/VHDL/docs-pdf/lab 10. pdf https: //www. altera. com/support-resources/design-examples/designsoftware/vhdl/vhd-state-machine. html Zadatak: Projektovati i simulirati kod “detektora binarne sekvence “ 1110101101”. Priložiti VHDL kog i simulacione dijagrame.

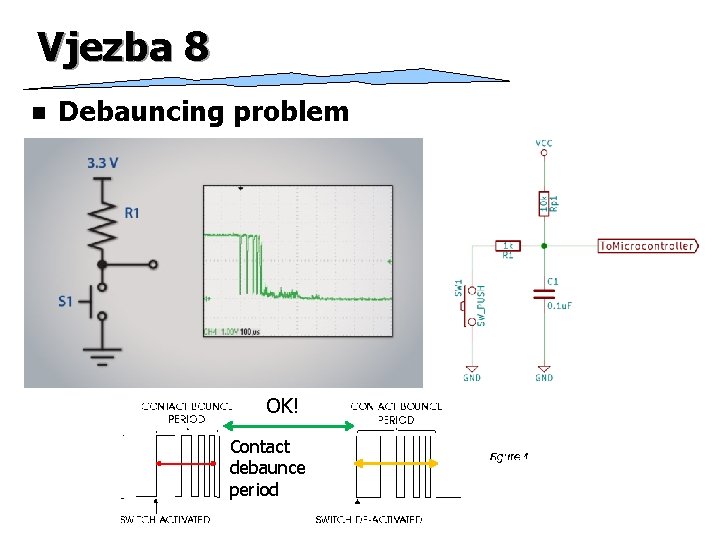

Vjezba 8 n Debauncing problem OK! Contact debaunce period

Vjezba 8 n Projektovati debauncer kolo i izabrati contact debaunce period na 100 ms (ili po potrebi) Contact in Contact out Clock Debaunce active low/high n Projektovati kolo monostabilnog multivibratora SW 0, SW 1, speed stepenisnog automata Vo LEDR 0 Monostabil Debauncer 15 s, 30 s, 60 s, 90 s KEY 0 0. 3 s Clock

PLD - FPGA Programabilna logička kola (PLD – Programmable Logic Devices) Lokalno Programibilne Sekvencijalne mreže (FPGA - Field Programmable Gate Array)

Sadržaj • Pregled digitalnih elektronskih komponenata prema teh. izrade. • Standardna logika vs programabilna (PLD) - Mjesto PLDs u elektronskoj industriji - Vrste PLD • FPGA - Konfigurisanje FPGA čipova • FPGA “Design Flow” • Važniji proizvodjači FPGA • Konfigurisanje FPGA čipova • Dizajn primjer • Proizvodjači FPGA čipova

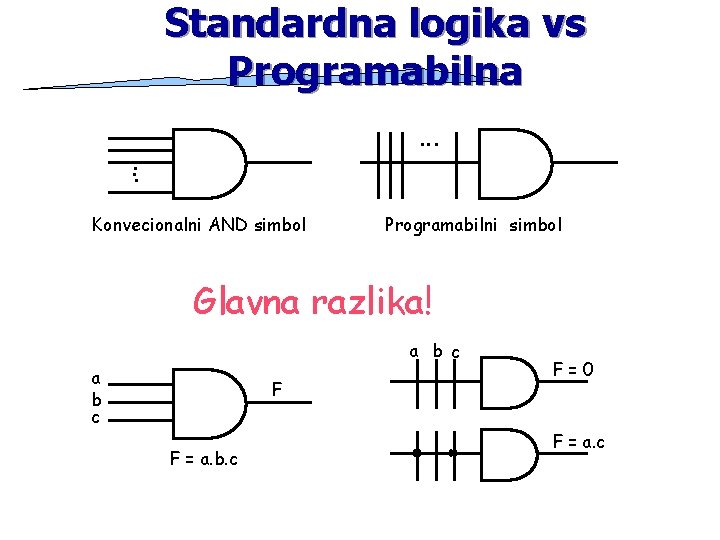

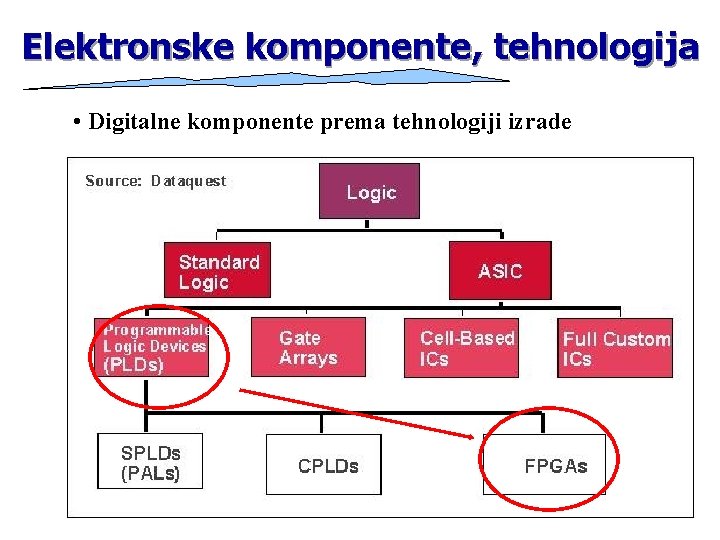

Elektronske komponente, tehnologija • Digitalne komponente prema tehnologiji izrade

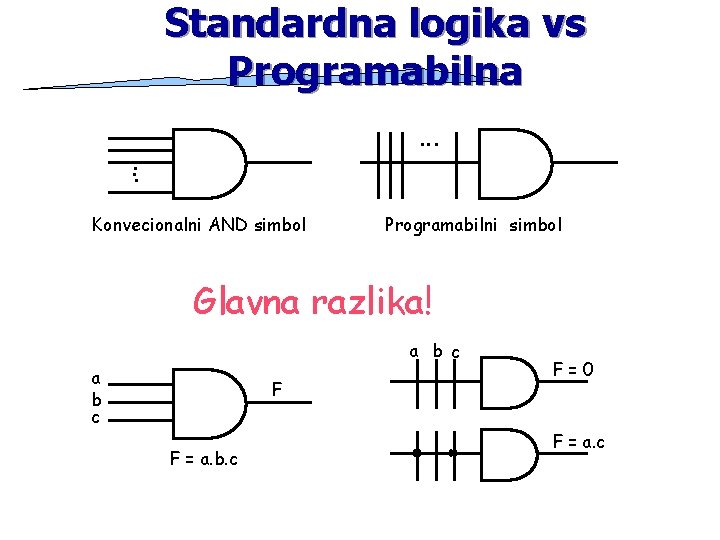

Standardna logika vs Programabilna. . . Konvecionalni AND simbol Programabilni simbol Glavna razlika! a b c F F = a. b. c F=0 F = a. c

Mjesto PLDs u elektronskoj industriji LDs su ključne komponente elektronskih sistema: n n n Processor Memory Logic PLD Prednosti: Brz i jeftin razvoj, idealne za proto-tipove, mogućnost višestruke upotrebe i raznovrsne implementacije: Mane: dimenzije, skupe za serijsku proizvodnju, veća potrošnja, veće kašnjenje.

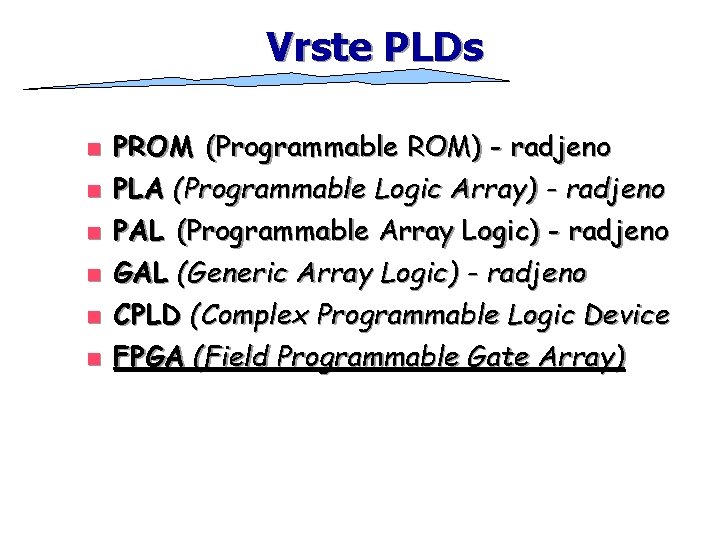

Vrste PLDs n n n PROM (Programmable ROM) - radjeno PLA (Programmable Logic Array) - radjeno PAL (Programmable Array Logic) - radjeno GAL (Generic Array Logic) - radjeno CPLD (Complex Programmable Logic Device FPGA (Field Programmable Gate Array)

CPLD n n Sadrži više PAL blokova na jednom čipu sa programabilnim linijama izmedju njih. Svaki PAL blok se sastoji od izvesnog broja makro-ćelija (macro cells). PLD Block • • • I/O Block PLD Block I/O Block • • • Interconnection Matrix I/O Block • • • PLD Block

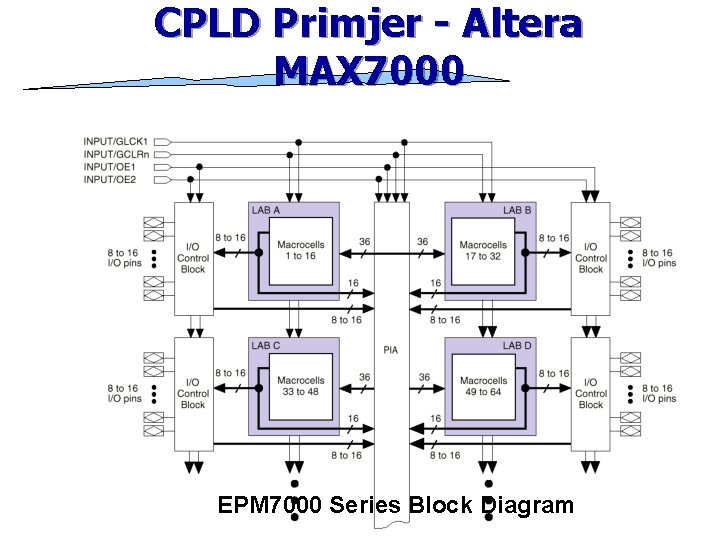

CPLD Primjer - Altera MAX 7000 EPM 7000 Series Block Diagram

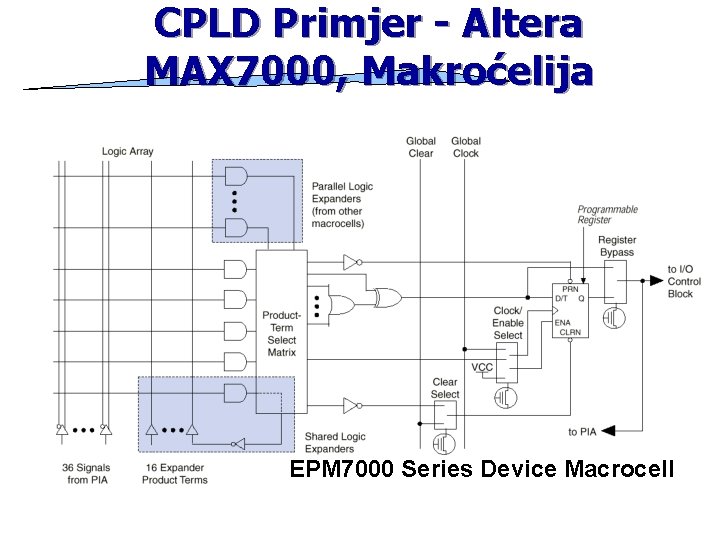

CPLD Primjer - Altera MAX 7000, Makroćelija EPM 7000 Series Device Macrocell

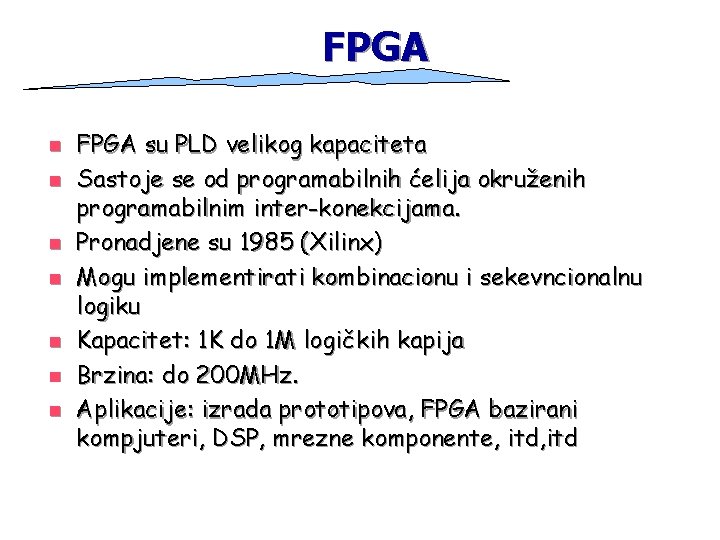

FPGA n n n n FPGA su PLD velikog kapaciteta Sastoje se od programabilnih ćelija okruženih programabilnim inter-konekcijama. Pronadjene su 1985 (Xilinx) Mogu implementirati kombinacionu i sekevncionalnu logiku Kapacitet: 1 K do 1 M logičkih kapija Brzina: do 200 MHz. Aplikacije: izrada prototipova, FPGA bazirani kompjuteri, DSP, mrezne komponente, itd

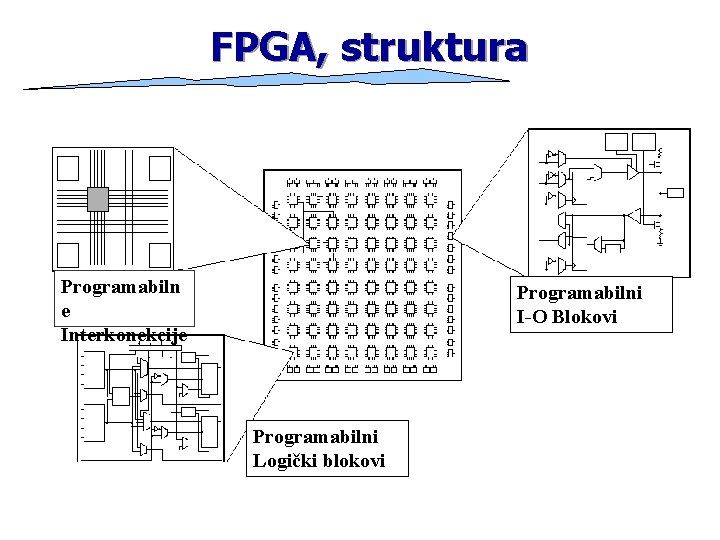

FPGA, struktura Programabiln e Interkonekcije Programabilni I-O Blokovi Programabilni Logički blokovi

Ostali FPGA blokovi Clock distribucija n Usadjeni memorijski blokovi n Blokovi specijalne namjene: n n DSP blok: n Hardware multipliers, adders and registers Usadjeni microprocessors/microcontrollers n UART (serijska komunikacija) n USB komunikacija n Itd. n

FPGA – Osnovni logički elemenat n n n LUT služe za implementaciju kombinacione logike. Registri za implementaciju sekvencijalne logike. Ostala logika (nije prikazana): n n Carry logika za aritmetičke funkcije Proširena logika za funkcije koje zahtijevaju više od 4 ulaza Select Out A B C D LUT D Clock Q

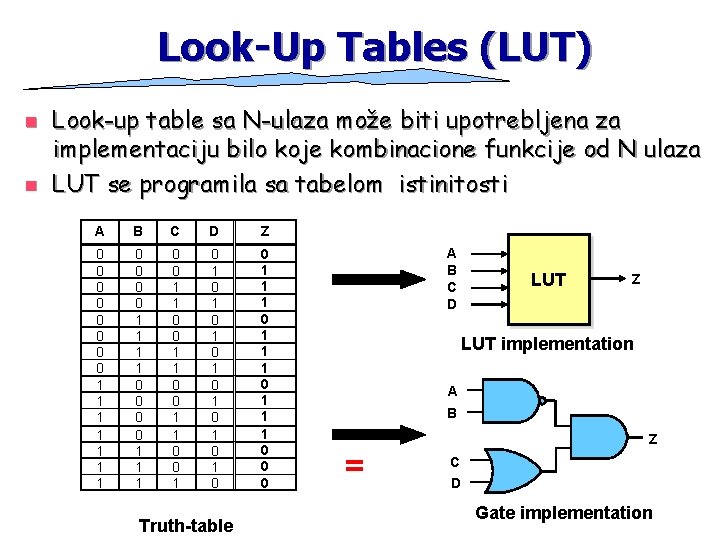

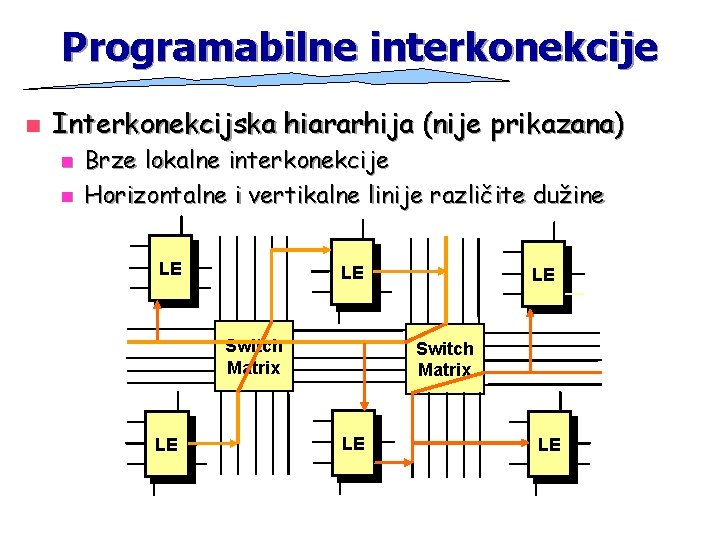

Look-Up Tables (LUT) n n Look-up table sa N-ulaza može biti upotrebljena za implementaciju bilo koje kombinacione funkcije od N ulaza LUT se programila sa tabelom istinitosti A B C D Z 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 0 0 1 1 0 0 1 0 1 0 0 1 1 1 0 0 0 Truth-table A B C D LUT Z LUT implementation A B = Z C D Gate implementation

LUT Implementacija n n n Primjer: 3 -input LUT Bazirana na multipleksorima (prekidačkim tranzistorima) Sadržaj LUT smješten u ćelijama konfiguracione memorije Configuration memory X 1 X 2 0/1 0/1 0/1 cells X 1 0 0 X 2 0 0 X 3 0 1 F/F 1/0 1/1 …………. 0/1 X 3 F=/X 1/X 2/X 3 or /X 1/X 2 X 3 itd. . F=/X 1/X 2/X 3 F

Programabilne interkonekcije n Interkonekcijska hiararhija (nije prikazana) n n Brze lokalne interkonekcije Horizontalne i vertikalne linije različite dužine LE LE Switch Matrix LE LE

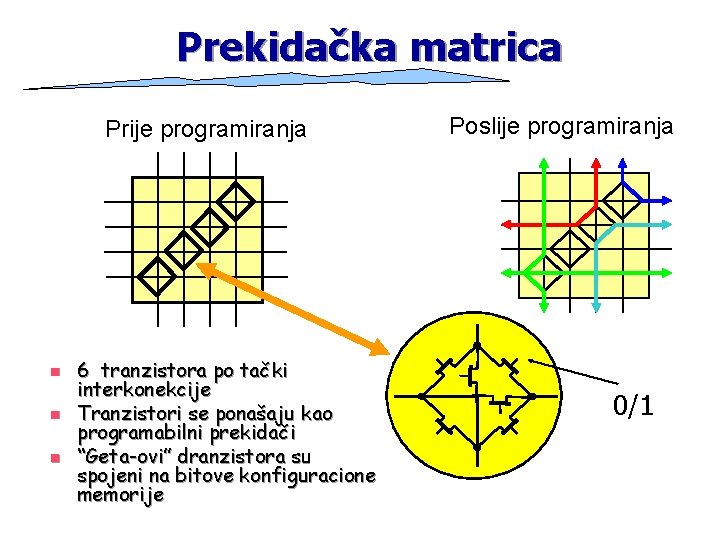

Prekidačka matrica Prije programiranja n n n 6 tranzistora po tački interkonekcije Tranzistori se ponašaju kao programabilni prekidači “Geta-ovi” dranzistora su spojeni na bitove konfiguracione memorije Poslije programiranja 0/1

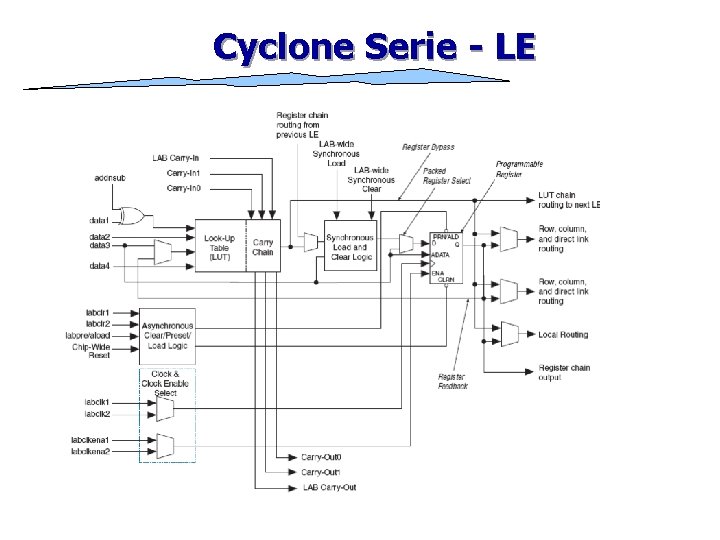

FPGA – Altera FLEX 8000 - od 4000 do 15000 logickih kapija, izgled jedne makro ćelije (MC) ili logičkog elementa (LE)

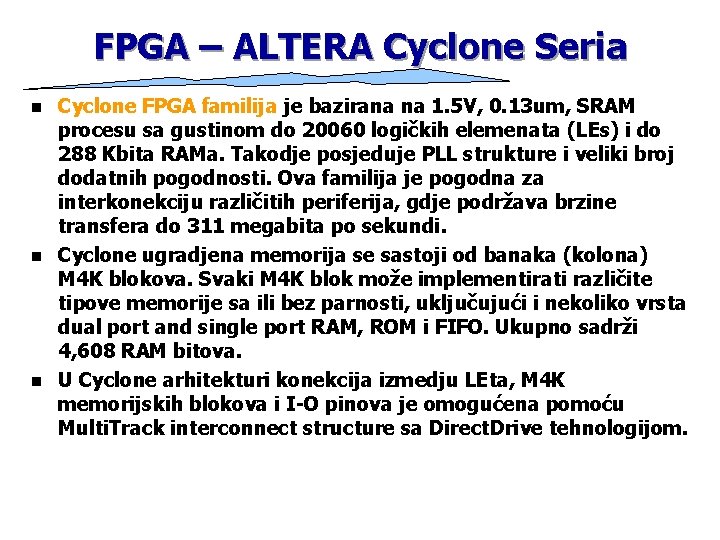

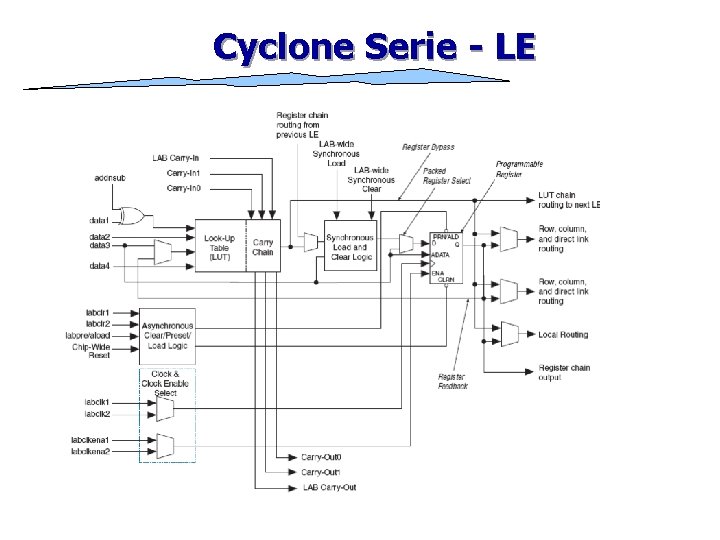

FPGA – ALTERA Cyclone Seria n n n Cyclone FPGA familija je bazirana na 1. 5 V, 0. 13 um, SRAM procesu sa gustinom do 20060 logičkih elemenata (LEs) i do 288 Kbita RAMa. Takodje posjeduje PLL strukture i veliki broj dodatnih pogodnosti. Ova familija je pogodna za interkonekciju različitih periferija, gdje podržava brzine transfera do 311 megabita po sekundi. Cyclone ugradjena memorija se sastoji od banaka (kolona) M 4 K blokova. Svaki M 4 K blok može implementirati različite tipove memorije sa ili bez parnosti, uključujući i nekoliko vrsta dual port and single port RAM, ROM i FIFO. Ukupno sadrži 4, 608 RAM bitova. U Cyclone arhitekturi konekcija izmedju LEta, M 4 K memorijskih blokova i I-O pinova je omogućena pomoću Multi. Track interconnect structure sa Direct. Drive tehnologijom.

Cyclone Serie - LE

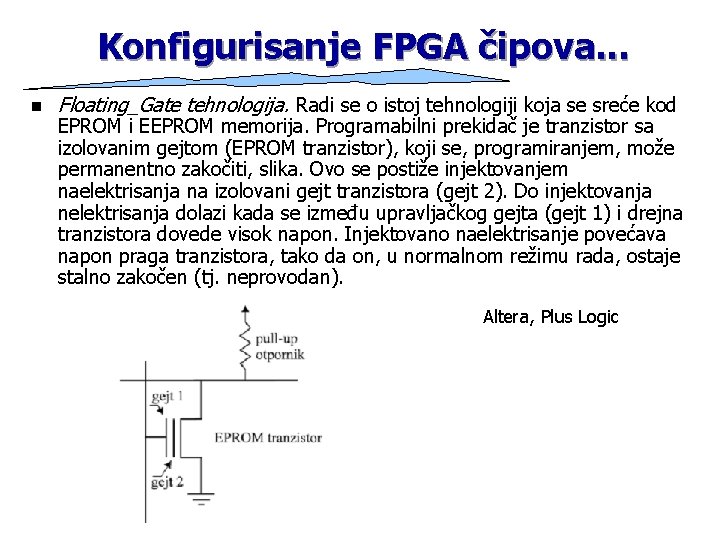

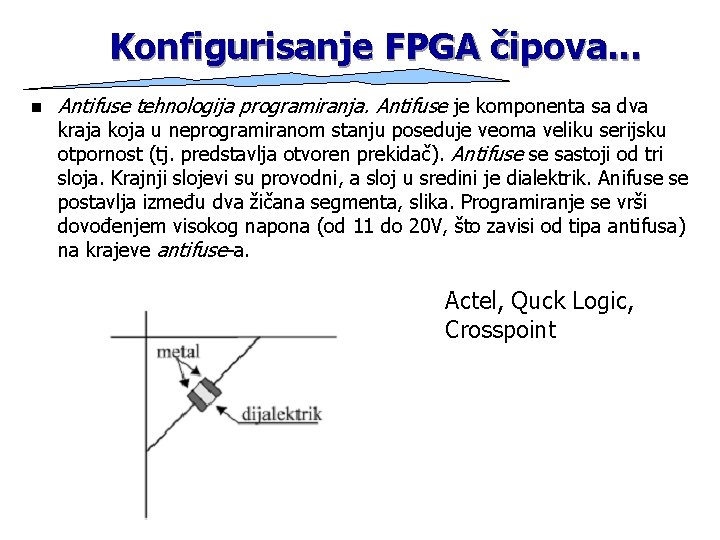

Konfigurisanje FPGA čipova • Konfigurabilnost PLD kola omogućena je postojanjem internih programabilnih tačka koje, u suštini, predstavljaju prekidačke elemente koji se mogu programirati tako da se ponašaju kao kratko-spojeni ili otvoreni prekidači. U fazi programiranja kola, signali koji se dovode na ulaz kola otvaraju i zatvaraju programabilne tačke (elektronske prekidače) i na taj način ostvaruju željene oblike povezivanja internih komponenta. • Kod prvih PLD kola za realizaciju programabilnih prekidača korišćeni su poluprovodnički osigurači. Inicijalno svi osigurači su "nesagoreni". Pobuđivanje kola nešto višim naponima od radnih uslovljava da kroz PLD protiču velike struje. Kao posledica, veze koje formiraju osigurači se raskidaju. Treba pri ovome naglasiti da ne postoji metod za rekonstrukciju (obnavljanje) stanja prekidača, tj. njegovo sagorevanje je trajno ili bespovratno. Tipičan predstavnik ovakvih kola je programabilni ROM ili PROM.

Konfigurisanje FPGA čipova. . . n n Danas, kod SPLD i CPLD kola, za realizaciju programabilnih prekidača, preovladavaju tehnologije zasnovane na tranzistorima sa izolovanim gejtom (floating-gate) EPROM ili EEPROM tipa, dok se kod FPGA uglavnom koriste SRAM (Static RAM) i antifuse tehnologije. SRAM tehnologija programiranja. Kod ove tehnologije, konfigurisanje kola se ostvaruje pomoću pass tanzistora i multipleksera koji se upravljaju SRAM ćelijama. Par “SRAM ćelija - pass tranzistor” se koristi kao programabilna veza između dva žičana segmenta, slika. Xilinix, Altera, Plessey, Algotronix, Concurent Logic i Toshiba.

Konfigurisanje FPGA čipova. . . n Floating_Gate tehnologija. Radi se o istoj tehnologiji koja se sreće kod EPROM i EEPROM memorija. Programabilni prekidač je tranzistor sa izolovanim gejtom (EPROM tranzistor), koji se, programiranjem, može permanentno zakočiti, slika. Ovo se postiže injektovanjem naelektrisanja na izolovani gejt tranzistora (gejt 2). Do injektovanja nelektrisanja dolazi kada se između upravljačkog gejta (gejt 1) i drejna tranzistora dovede visok napon. Injektovano naelektrisanje povećava napon praga tranzistora, tako da on, u normalnom režimu rada, ostaje stalno zakočen (tj. neprovodan). Altera, Plus Logic

Konfigurisanje FPGA čipova. . . n Antifuse tehnologija programiranja. Antifuse je komponenta sa dva kraja koja u neprogramiranom stanju poseduje veoma veliku serijsku otpornost (tj. predstavlja otvoren prekidač). Antifuse se sastoji od tri sloja. Krajnji slojevi su provodni, a sloj u sredini je dialektrik. Anifuse se postavlja između dva žičana segmenta, slika. Programiranje se vrši dovođenjem visokog napona (od 11 do 20 V, što zavisi od tipa antifusa) na krajeve antifuse-a. Actel, Quck Logic, Crosspoint

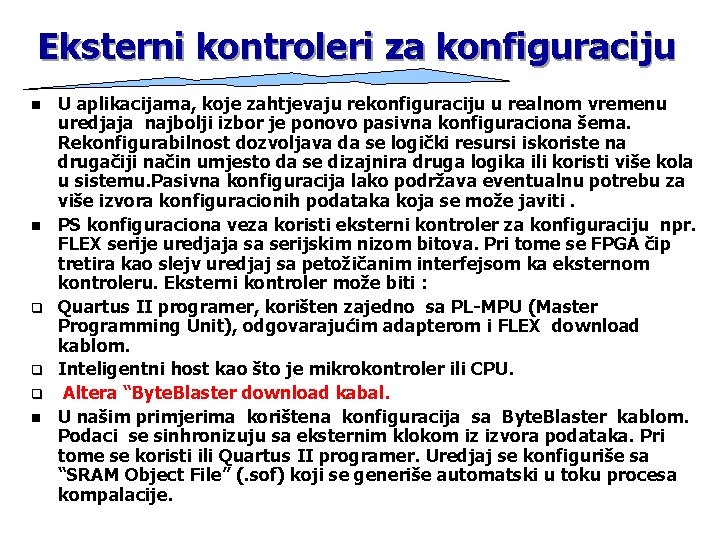

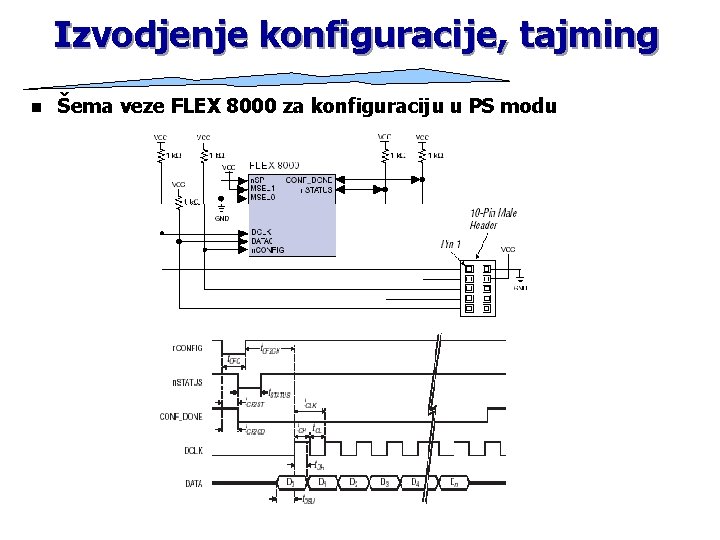

REALNI FPGA CIP Više vrsta pinova -Za napajanje (VCC, GND) -Za konfigurisanje (n. SP, MSEL 1, MSEL 0, DCLK, DATA 0, n. CONFIG CONF_DONE, n. STATUS) -Za klok (CLK) -. . . Npr: EPF 8452 ALC 84 -2 ima 84 pina od kojih 8 ide na masu (GND), 5 na VCC, 8 na konf.

Načini konfigurisanja FPGA n Moguće konfiguracione šeme Konfiguraciona šema Aktivna serijska Akronim AS Izvor podataka Konfiguracioni EPROM Aktivna paralelna gornja APU Paralelni EPROM Aktivna paralelna donja APD Paralelni EPROM Pasivna serijska PS Serijski kanal podataka Pasivna paralelna sinhrona PPS Inteligentni host Pasivna paralelna asinhrona PPA Inteligentni host

Eksterni kontroleri za konfiguraciju n n q q q n U aplikacijama, koje zahtjevaju rekonfiguraciju u realnom vremenu uredjaja najbolji izbor je ponovo pasivna konfiguraciona šema. Rekonfigurabilnost dozvoljava da se logički resursi iskoriste na drugačiji način umjesto da se dizajnira druga logika ili koristi više kola u sistemu. Pasivna konfiguracija lako podržava eventualnu potrebu za više izvora konfiguracionih podataka koja se može javiti. PS konfiguraciona veza koristi eksterni kontroler za konfiguraciju npr. FLEX serije uredjaja sa serijskim nizom bitova. Pri tome se FPGA čip tretira kao slejv uredjaj sa petožičanim interfejsom ka eksternom kontroleru. Eksterni kontroler može biti : Quartus II programer, korišten zajedno sa PL-MPU (Master Programming Unit), odgovarajućim adapterom i FLEX download kablom. Inteligentni host kao što je mikrokontroler ili CPU. Altera “Byte. Blaster download kabal. U našim primjerima korištena konfiguracija sa Byte. Blaster kablom. Podaci se sinhronizuju sa eksternim klokom iz izvora podataka. Pri tome se koristi ili Quartus II programer. Uredjaj se konfiguriše sa “SRAM Object File” (. sof) koji se generiše automatski u toku procesa kompalacije.

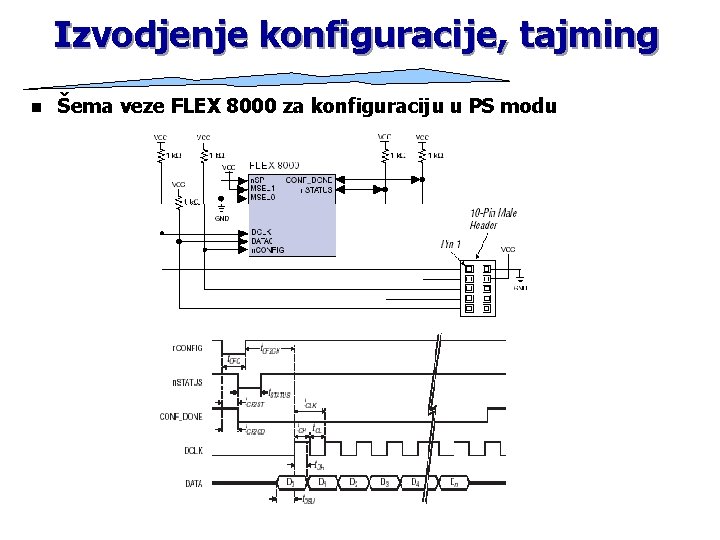

Izvodjenje konfiguracije, tajming n Šema veze FLEX 8000 za konfiguraciju u PS modu

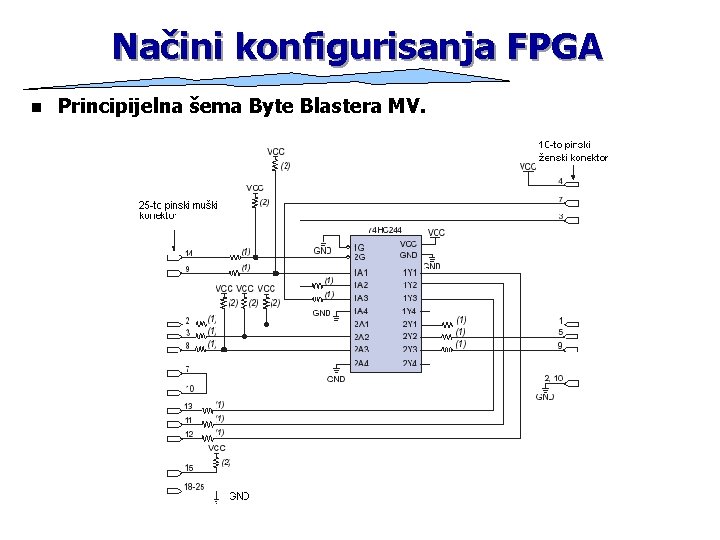

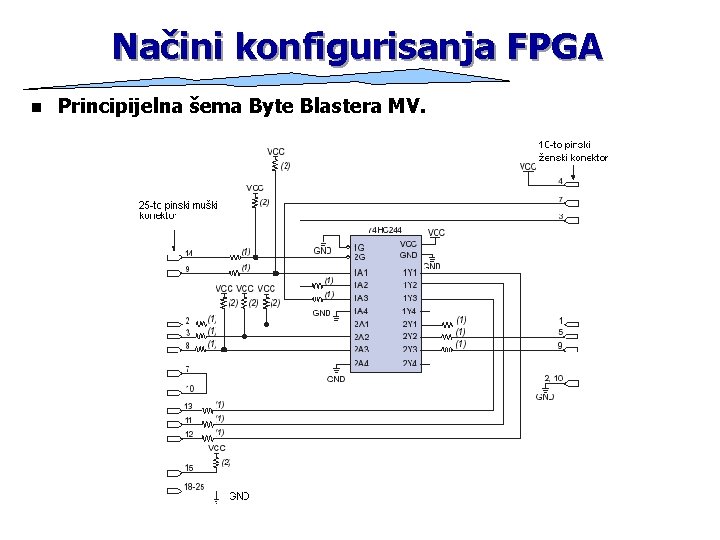

Načini konfigurisanja FPGA n Principijelna šema Byte Blastera MV.

Napredne tehnike projektovanja FPGA kola

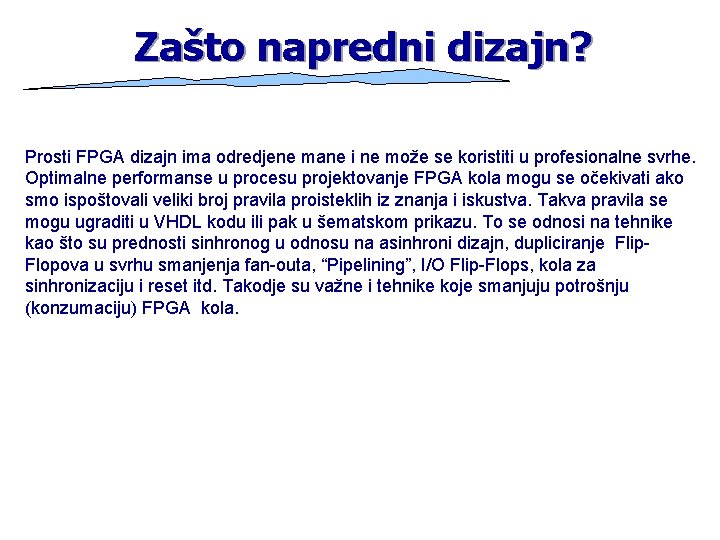

Zašto napredni dizajn? Prosti FPGA dizajn ima odredjene mane i ne može se koristiti u profesionalne svrhe. Optimalne performanse u procesu projektovanje FPGA kola mogu se očekivati ako smo ispoštovali veliki broj pravila proisteklih iz znanja i iskustva. Takva pravila se mogu ugraditi u VHDL kodu ili pak u šematskom prikazu. To se odnosi na tehnike kao što su prednosti sinhronog u odnosu na asinhroni dizajn, dupliciranje Flip. Flopova u svrhu smanjenja fan-outa, “Pipelining”, I/O Flip-Flops, kola za sinhronizaciju i reset itd. Takodje su važne i tehnike koje smanjuju potrošnju (konzumaciju) FPGA kola.

Sinhrona vs. asinhrona kola Sinhrona kola su mnogo pouzdanija. § Glavni princip ovih kola je da su sva zbivanja sinhronizovana sa klokom. § Izlaz iz jednog logičkog stanja treba da ima jedan puni period kloka da dodje do drugog. §“Skew faktor” – faktor skošenja, mora biti unutar istog klok intervala. Generalno, gdje god je to moguće treba koristiti sinhroni pristup. Asinhrona kola su manje pouzdana. §Uticaj kašnjenja je izražen (npr. 12 ns). §Višestruka kašnjenja mogu da dovedu do različitih posledica(e. g. DATA dolazi 5 ns prije SELECT) Treba ih izbjegavati prilikom projektovanja

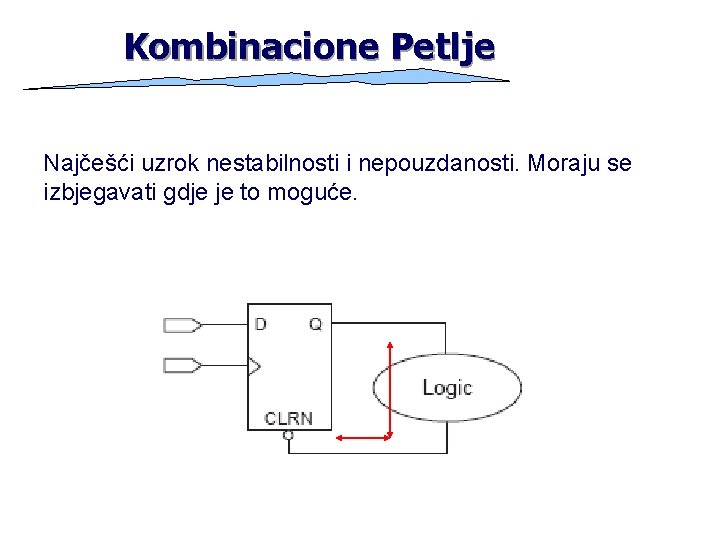

Kombinacione Petlje Najčešći uzrok nestabilnosti i nepouzdanosti. Moraju se izbjegavati gdje je to moguće.

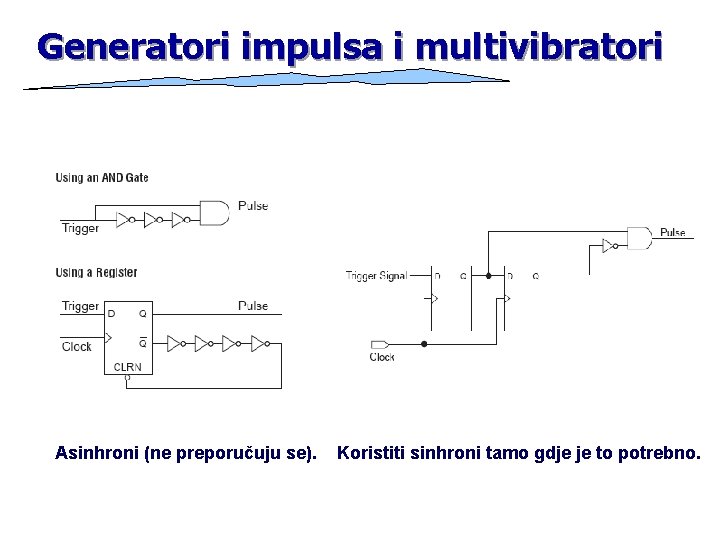

Generatori impulsa i multivibratori Asinhroni (ne preporučuju se). Koristiti sinhroni tamo gdje je to potrebno.

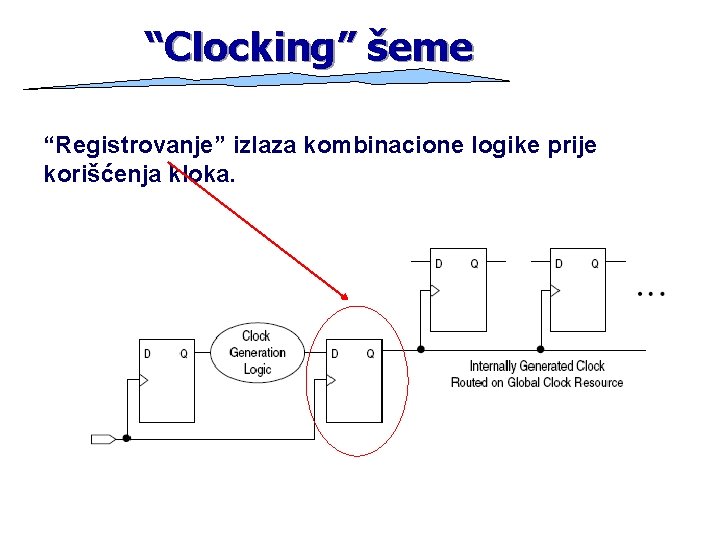

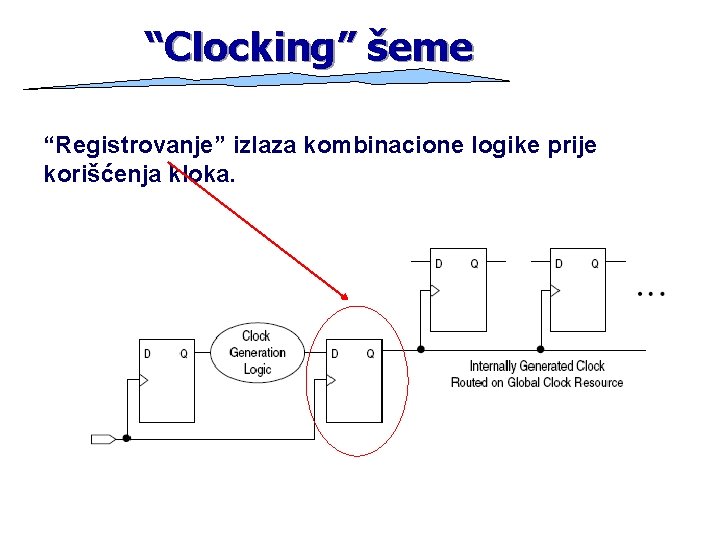

“Clocking” šeme “Registrovanje” izlaza kombinacione logike prije korišćenja kloka.

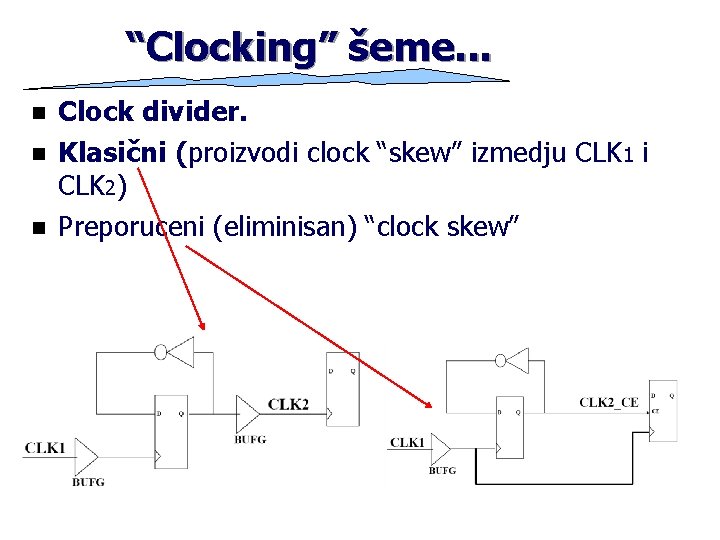

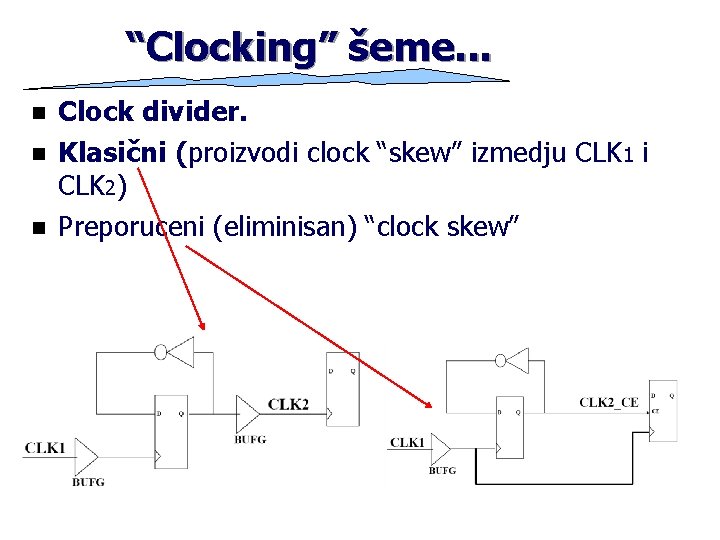

“Clocking” šeme. . . n n n Clock divider. Klasični (proizvodi clock “skew” izmedju CLK 1 i CLK 2) Preporuceni (eliminisan) “clock skew”

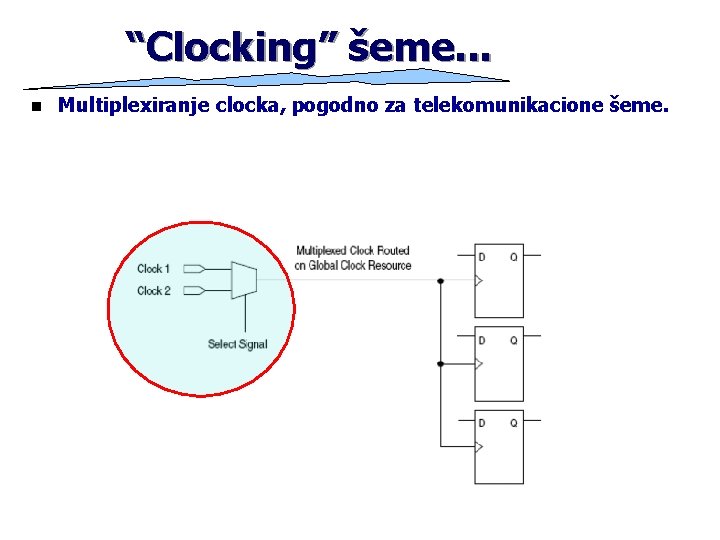

“Clocking” šeme. . . n Multiplexiranje clocka, pogodno za telekomunikacione šeme.

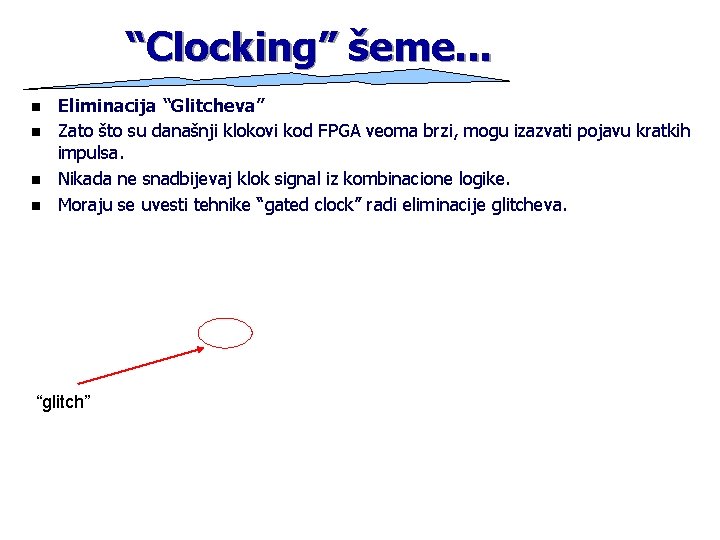

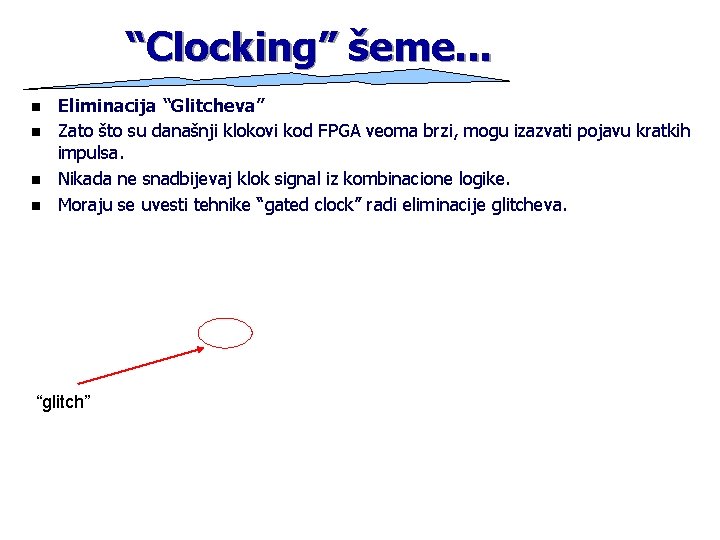

“Clocking” šeme. . . n n Eliminacija “Glitcheva” Zato što su današnji klokovi kod FPGA veoma brzi, mogu izazvati pojavu kratkih impulsa. Nikada ne snadbijevaj klok signal iz kombinacione logike. Moraju se uvesti tehnike “gated clock” radi eliminacije glitcheva. “glitch”

“Clocking” šeme. . . n Eliminacija “Glitcheva”, gornja funkcija, ali bez glitcheva.

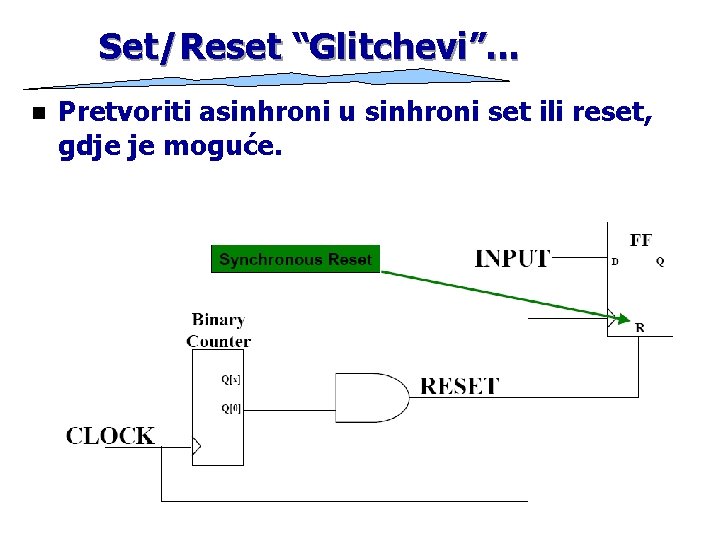

“Clocking” šeme. . . n “Gated clock”

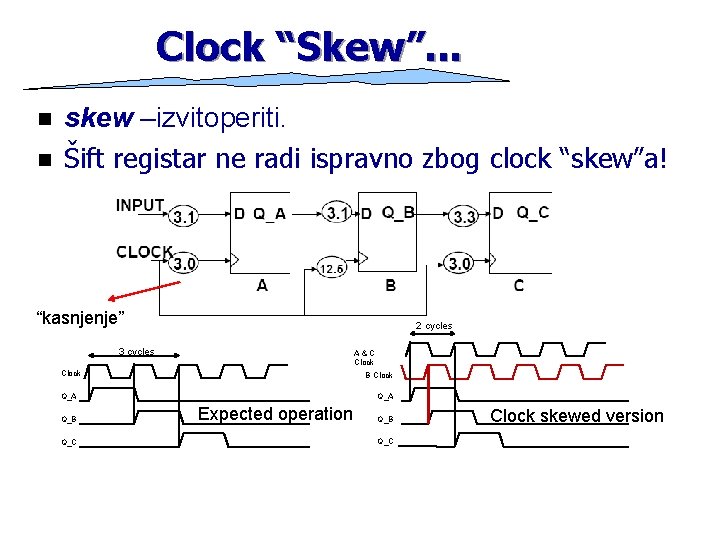

“Clocking” šeme. . . n Preporučena “Clock-Gating” tehnika.

Set/Reset “Glitchevi”. . . n n Glitch-glič, greška, neželjen impuls. Glitchevi na asinhronom clearu mogu izazvati probleme u kolu. glitch

Set/Reset “Glitchevi”. . . n Pretvoriti asinhroni u sinhroni set ili reset, gdje je moguće.

Clock “Skew”. . . n n skew –izvitoperiti. Šift registar ne radi ispravno zbog clock “skew”a! “kasnjenje” 2 cycles 3 cycles A&C Clock B Clock Q_A Q_B Q_C Q_A Expected operation Q_B Q_C Clock skewed version

Dupliciranje Flip-Flopova. . . § n Visoki-”fanout”, prekoračenje, može izazvati probleme (usporiti rad kola). (Fan - out) mogućnost opterećenja izlaza, najveci broj standardnih kola koje je moguće vezati na izlaz datog kola (kao opterećenje). Dupliciranje flip-flopa može pomoći.

“Pipelining” Koncept. . . pipe-line, cjevovod

Kašnjenja u “pipeline” arhitekturama n n Svaka “pipelin” faza dodaje kašnjenje od jednog kloka. Tehnika “filling the pipeline” može pomoći.

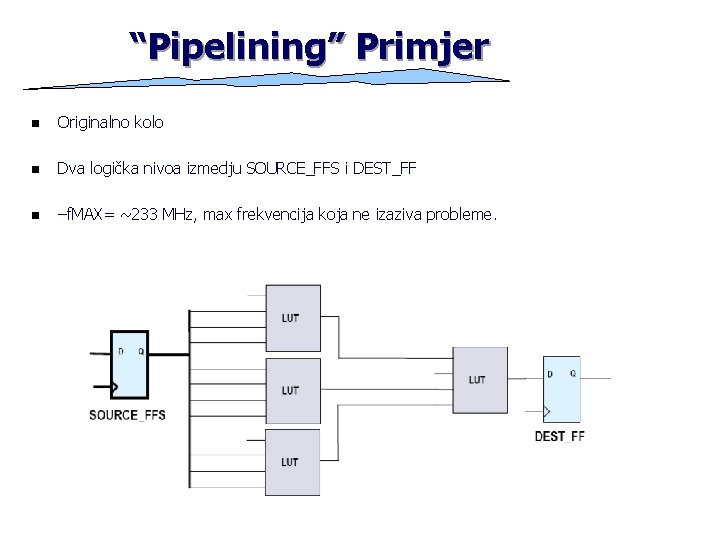

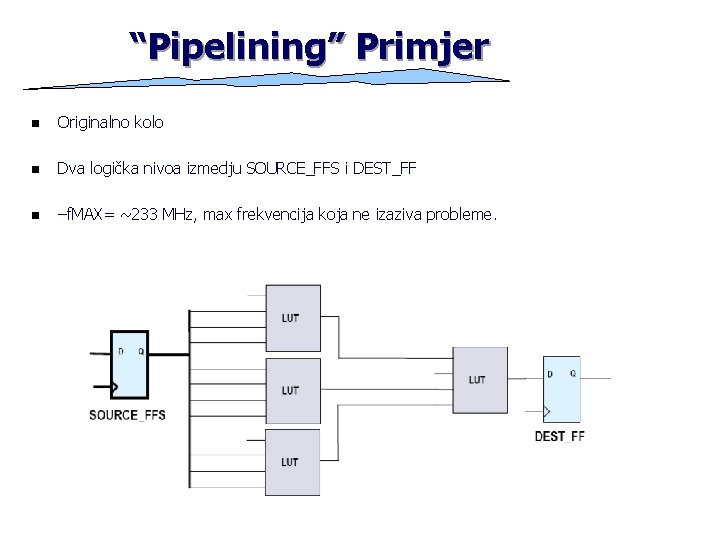

“Pipelining” Primjer n Originalno kolo n Dva logička nivoa izmedju SOURCE_FFS i DEST_FF n –f. MAX= ~233 MHz, max frekvencija koja ne izaziva probleme.

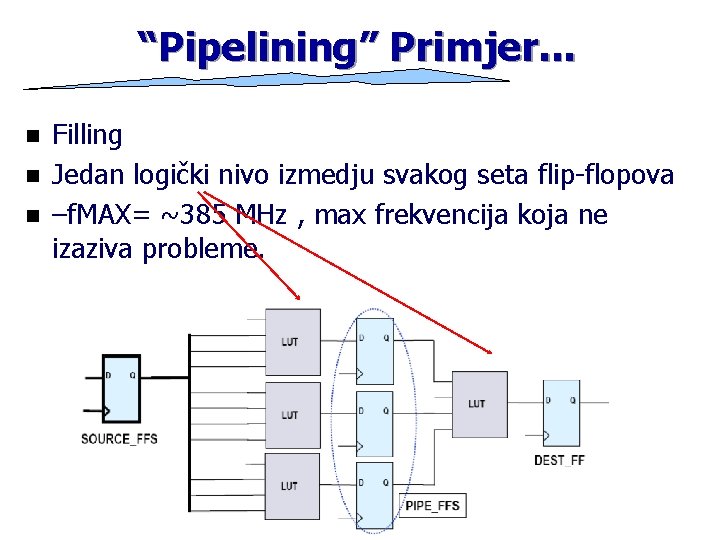

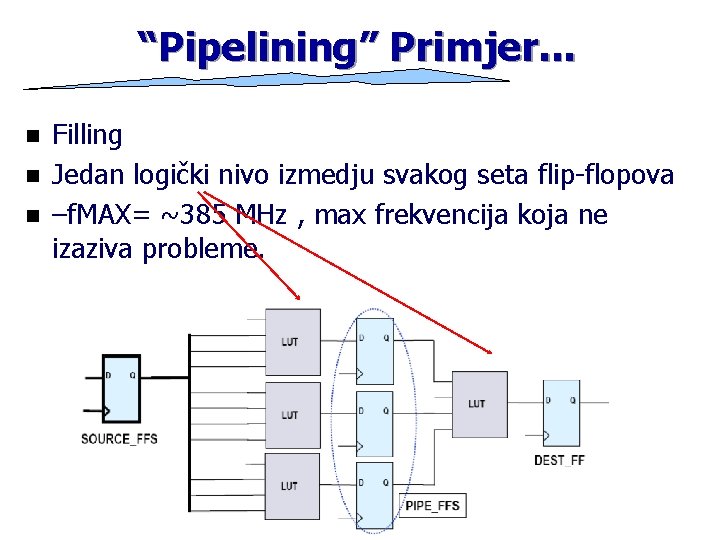

“Pipelining” Primjer. . . n n n Filling Jedan logički nivo izmedju svakog seta flip-flopova –f. MAX= ~385 MHz , max frekvencija koja ne izaziva probleme.

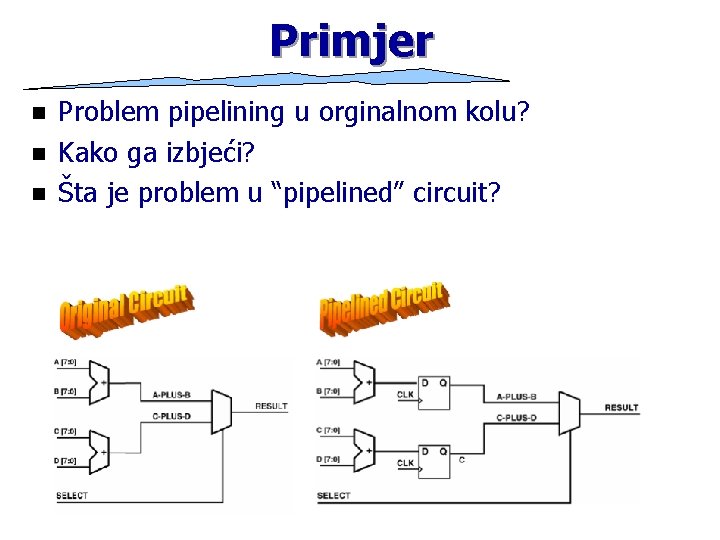

Primjer n n n Problem pipelining u orginalnom kolu? Kako ga izbjeći? Šta je problem u “pipelined” circuit?

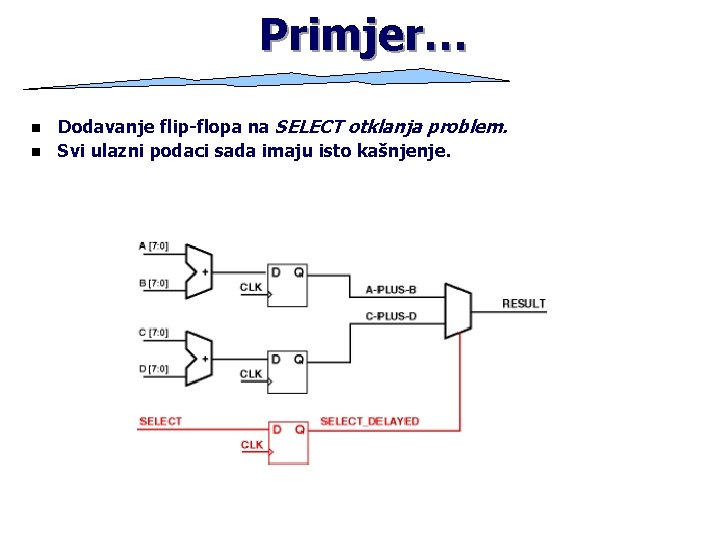

Primjer… n n Dodavanje flip-flopa na SELECT otklanja problem. Svi ulazni podaci sada imaju isto kašnjenje.

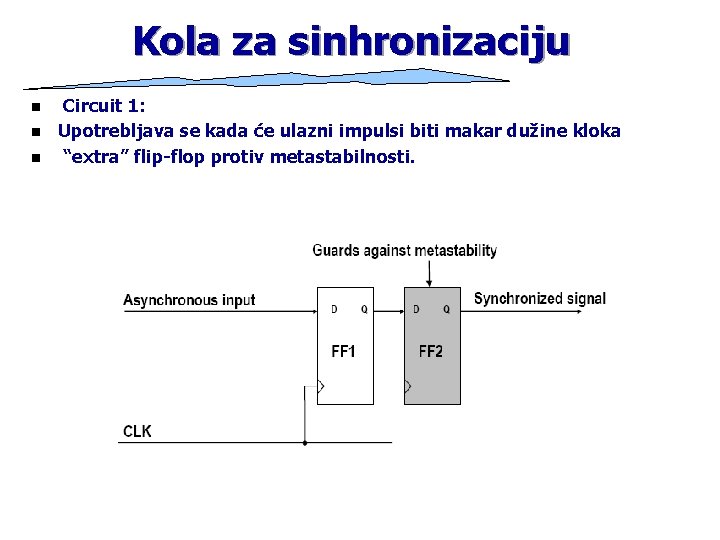

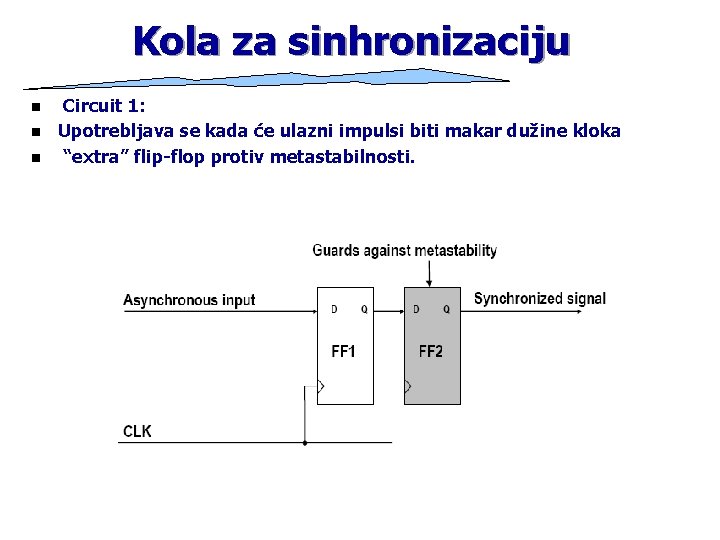

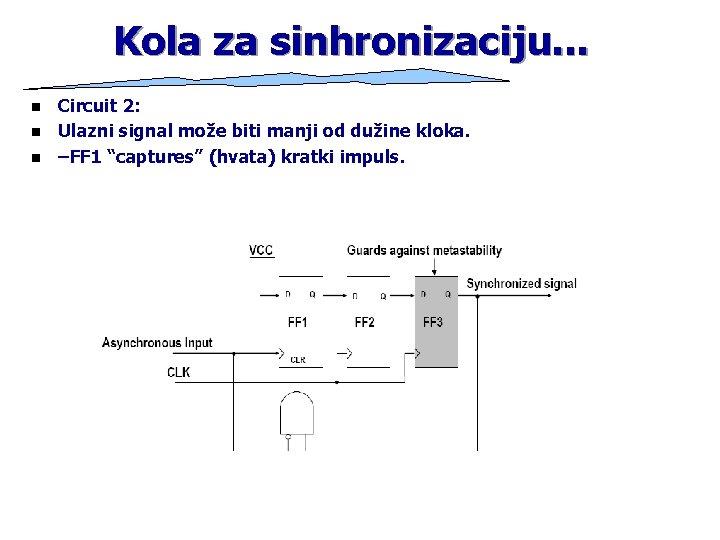

Kola za sinhronizaciju n n n Circuit 1: Upotrebljava se kada će ulazni impulsi biti makar dužine kloka “extra” flip-flop protiv metastabilnosti.

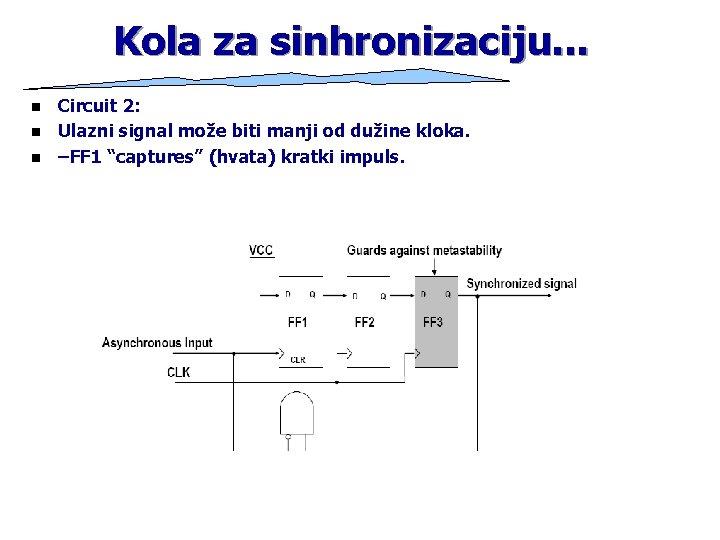

Kola za sinhronizaciju. . . n n n Circuit 2: Ulazni signal može biti manji od dužine kloka. –FF 1 “captures” (hvata) kratki impuls.

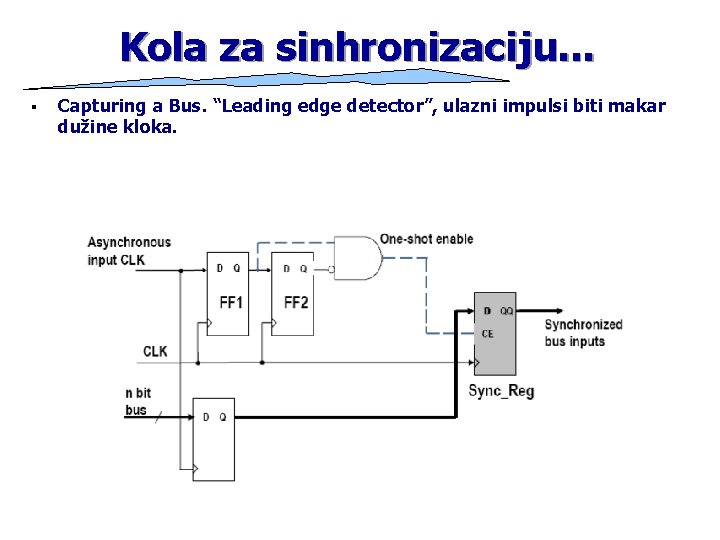

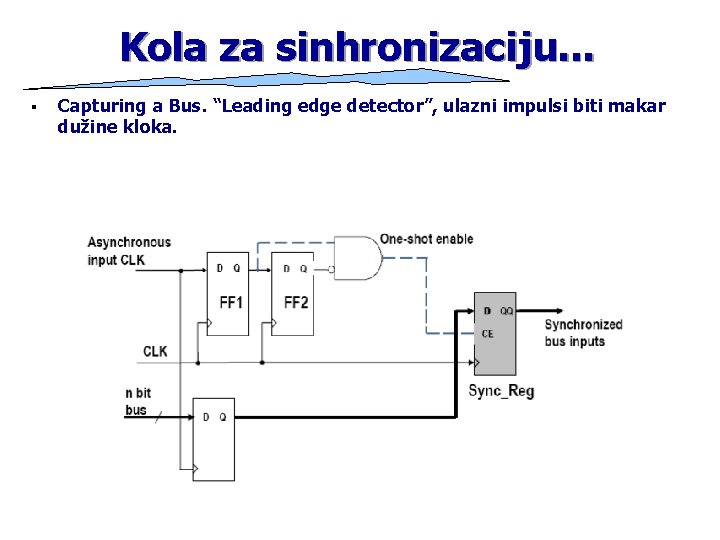

Kola za sinhronizaciju. . . § Capturing a Bus. “Leading edge detector”, ulazni impulsi biti makar dužine kloka.

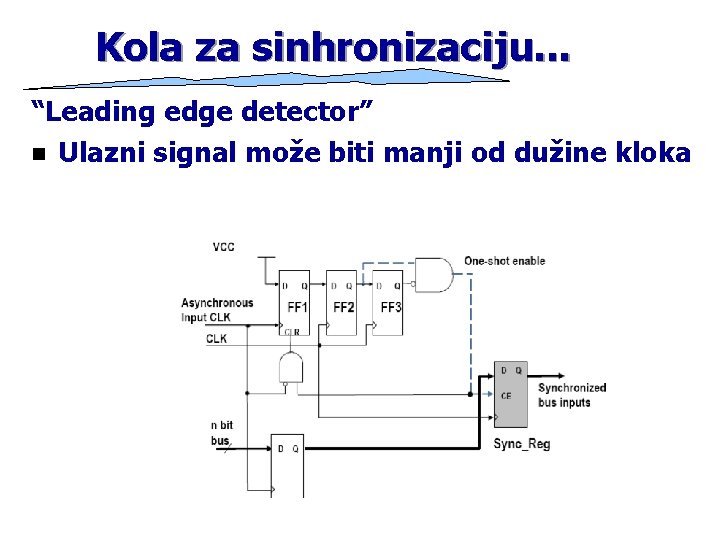

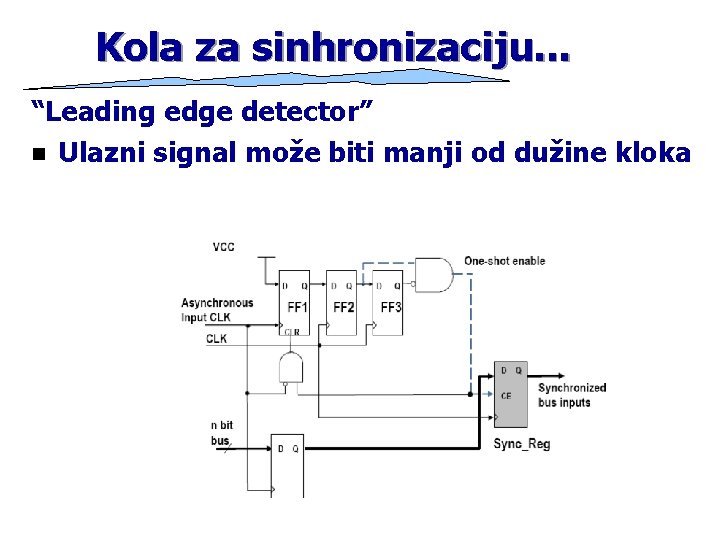

Kola za sinhronizaciju. . . “Leading edge detector” n Ulazni signal može biti manji od dužine kloka

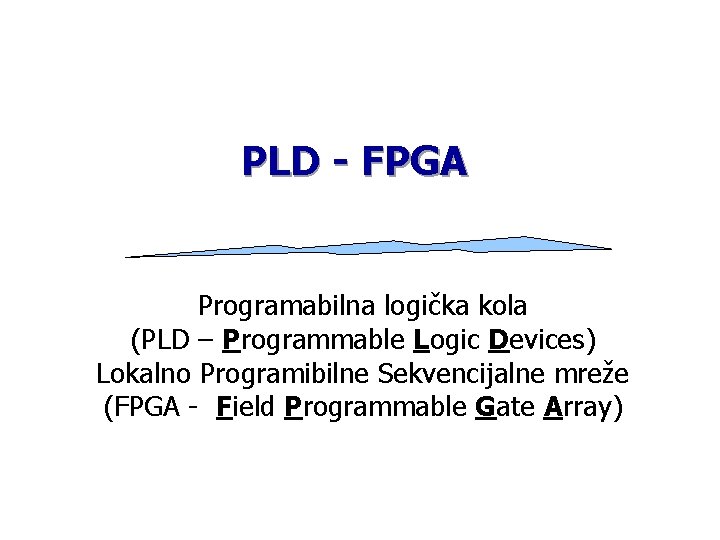

![Napredni dizajn Primjer realizacije FIR filtra gdje su yn izlaz xni je ulaz u Napredni dizajn Primjer realizacije FIR filtra: gdje su: y[n] izlaz x(n-i) je ulaz u](https://slidetodoc.com/presentation_image_h2/911241d46073b6051f3588afb6d9b140/image-193.jpg)

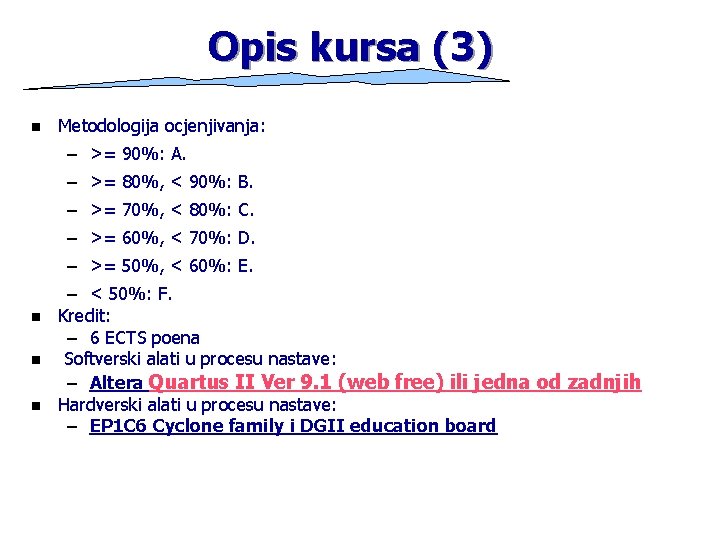

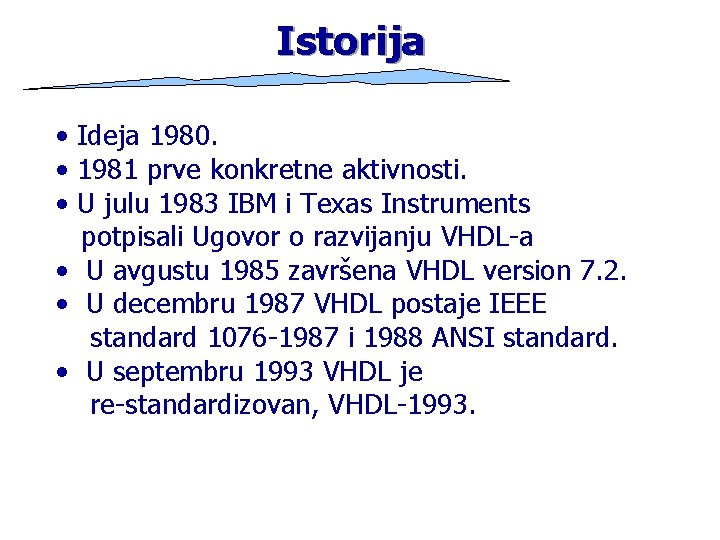

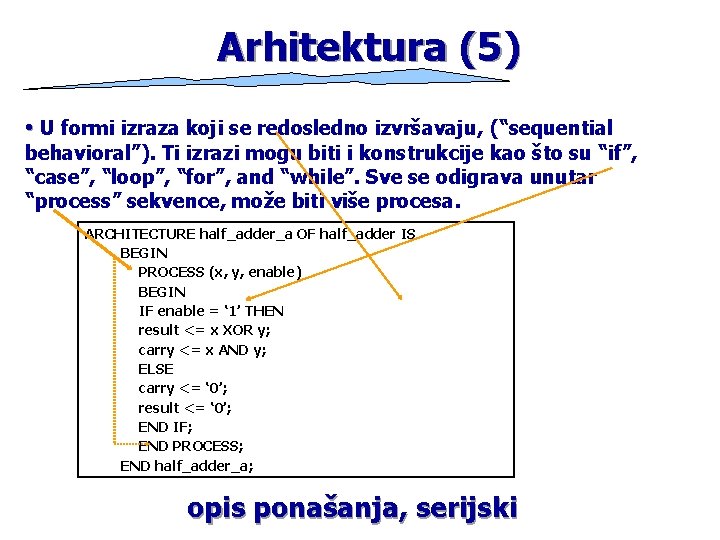

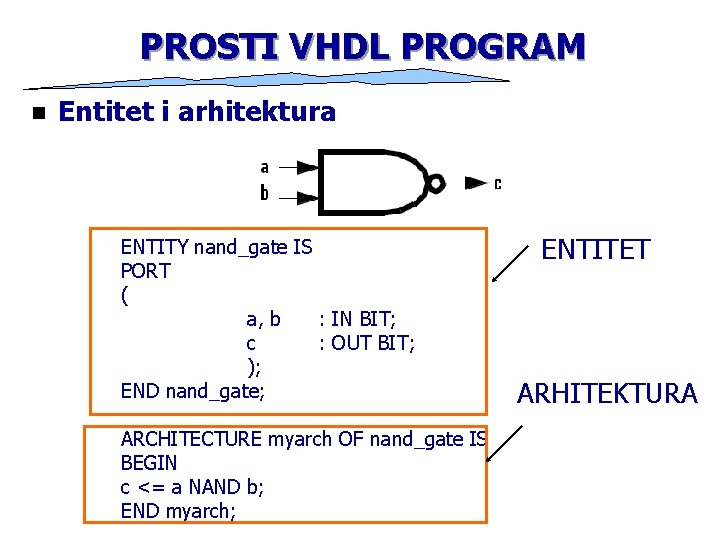

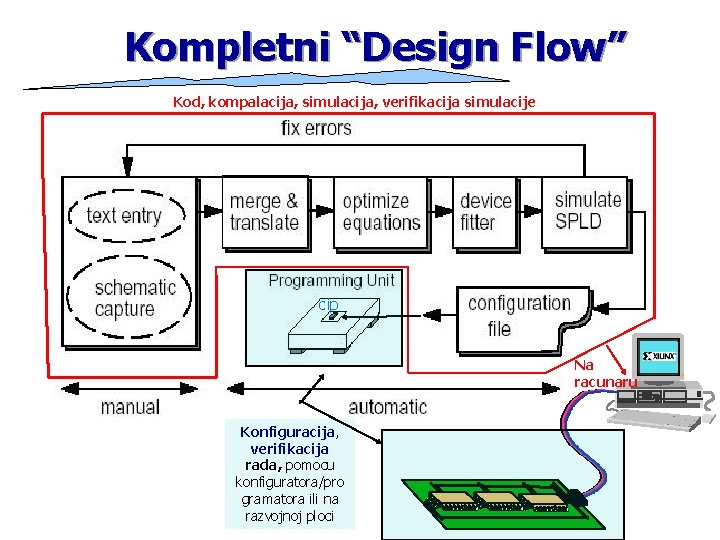

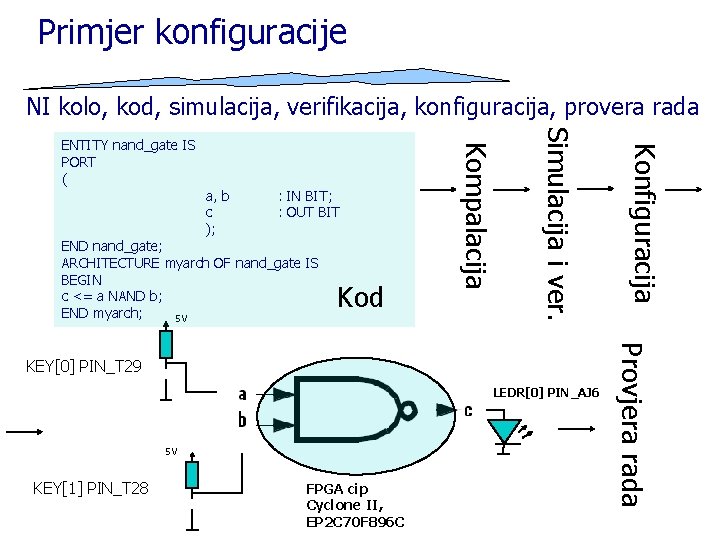

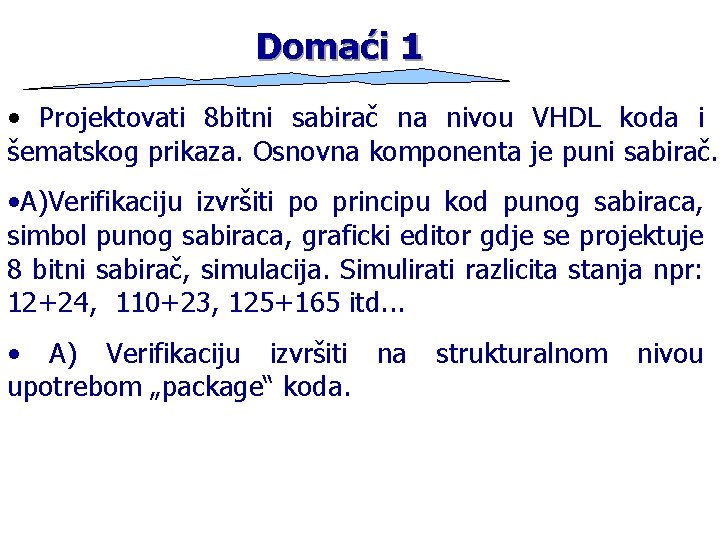

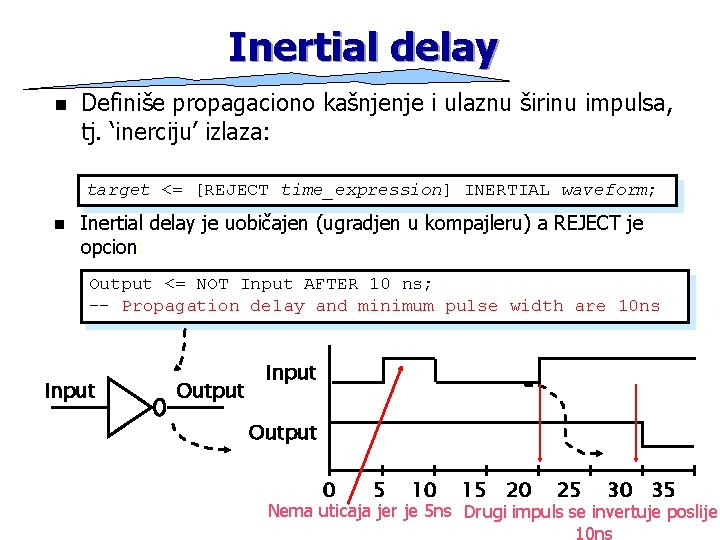

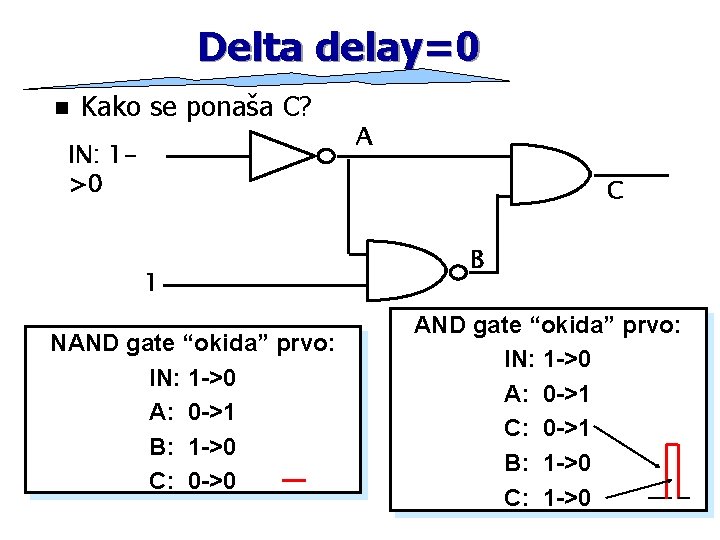

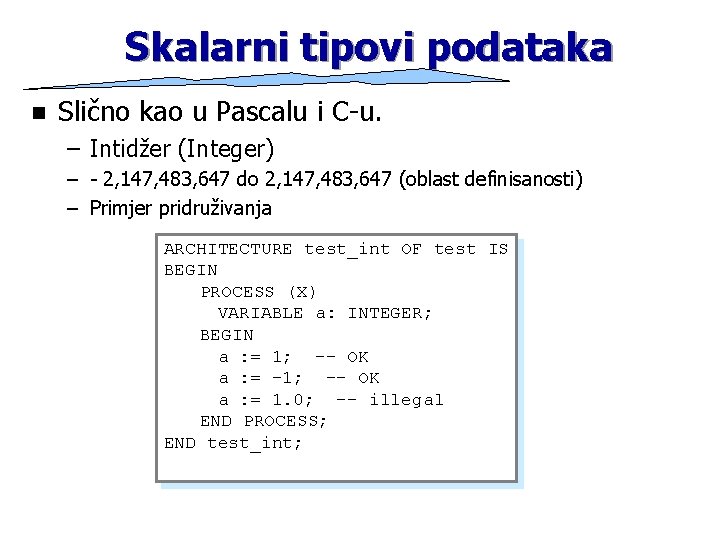

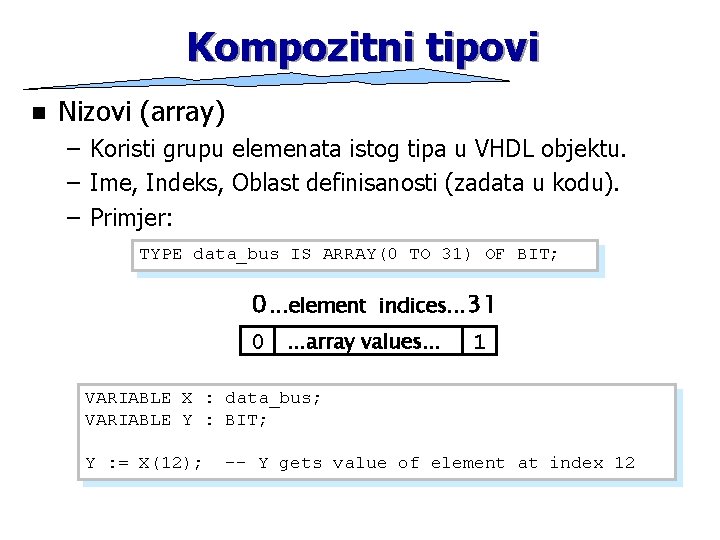

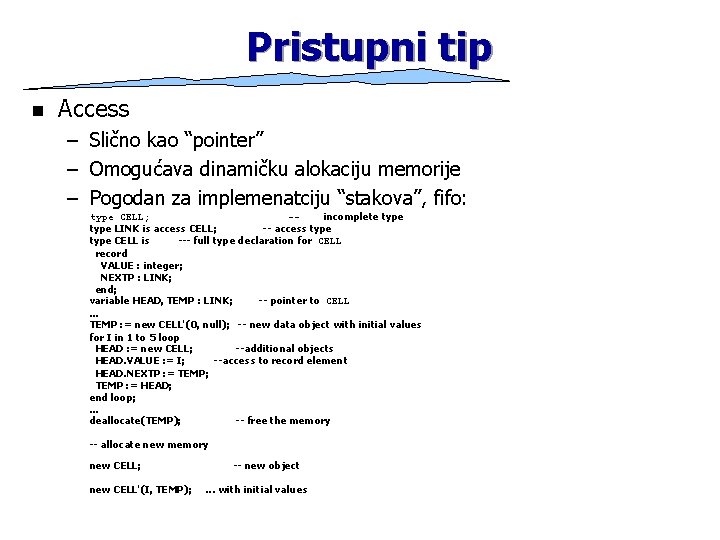

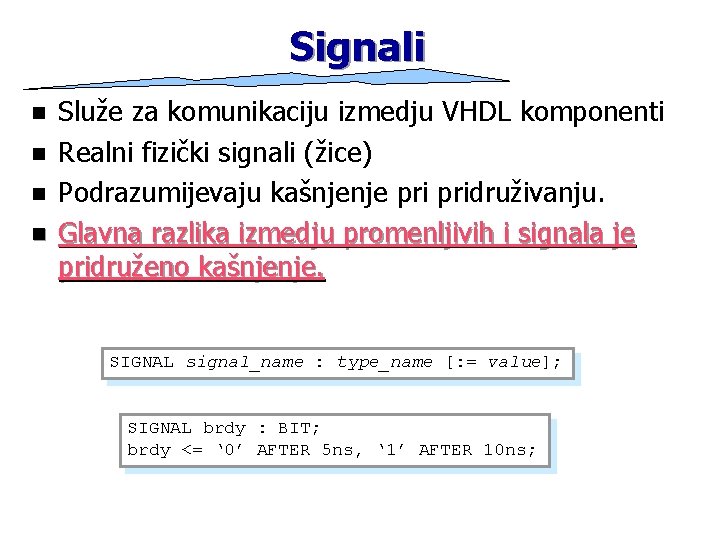

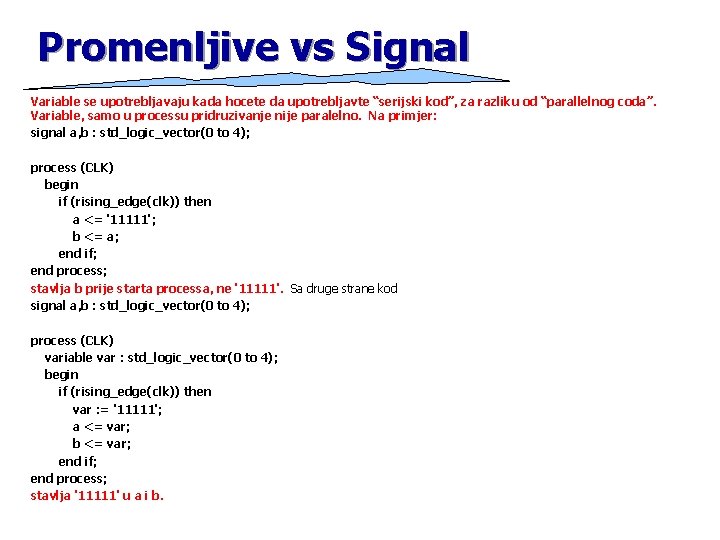

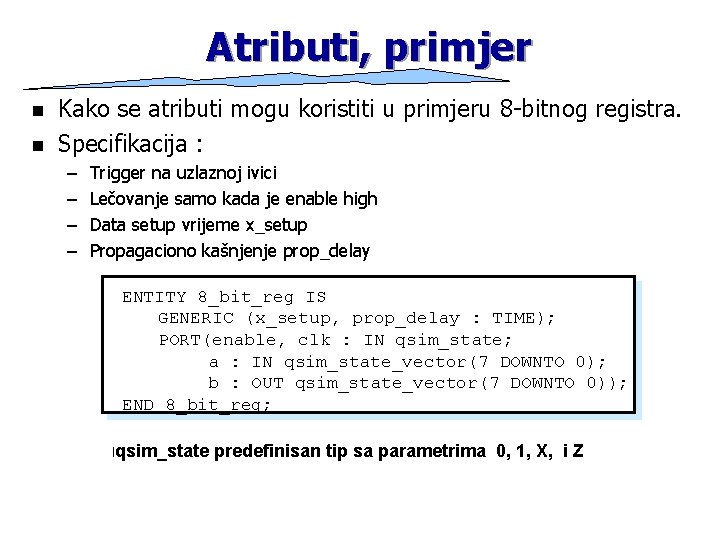

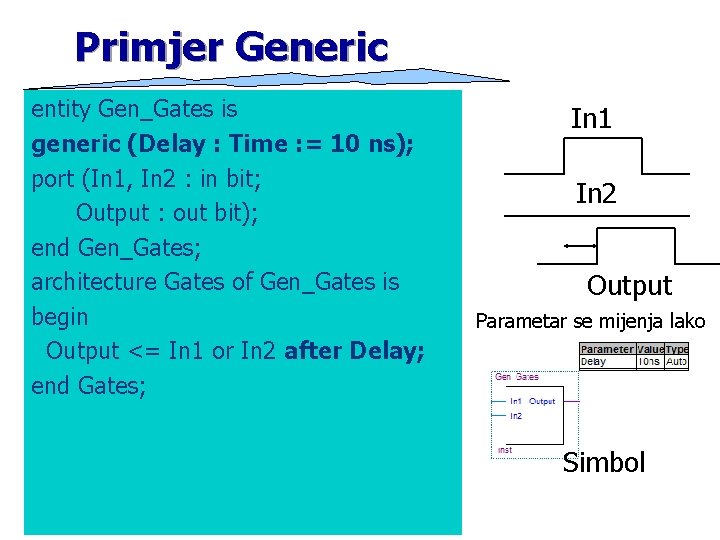

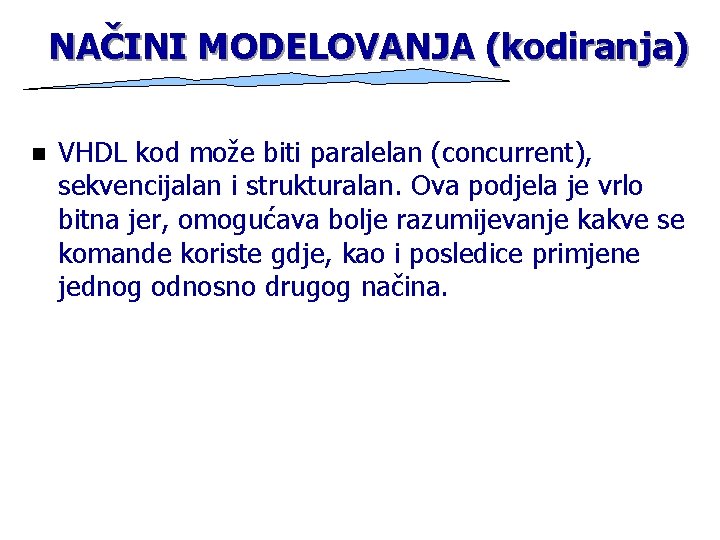

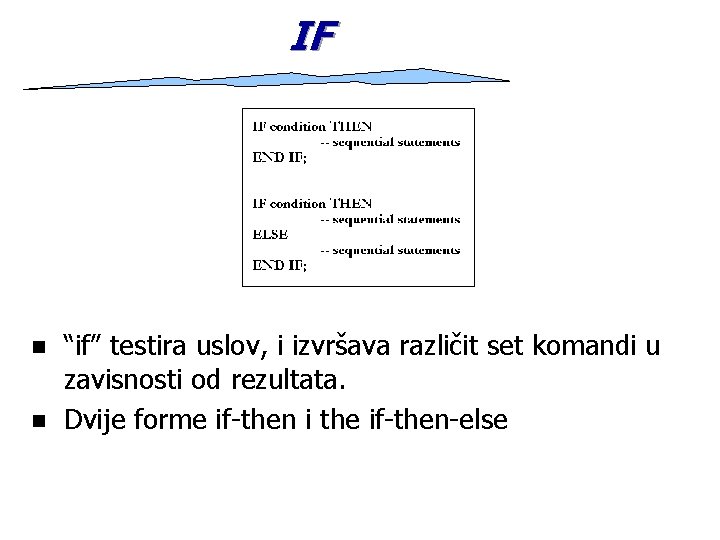

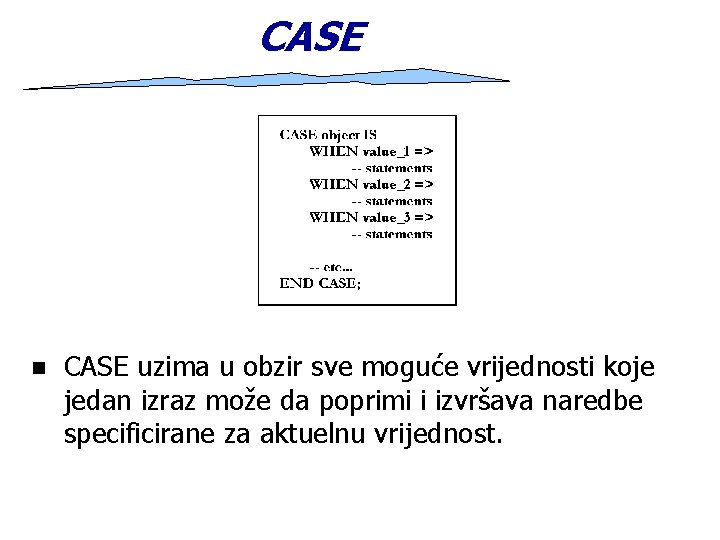

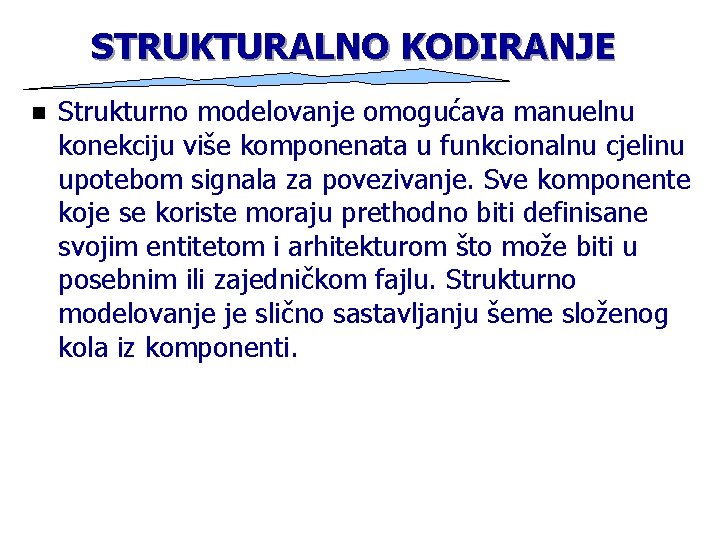

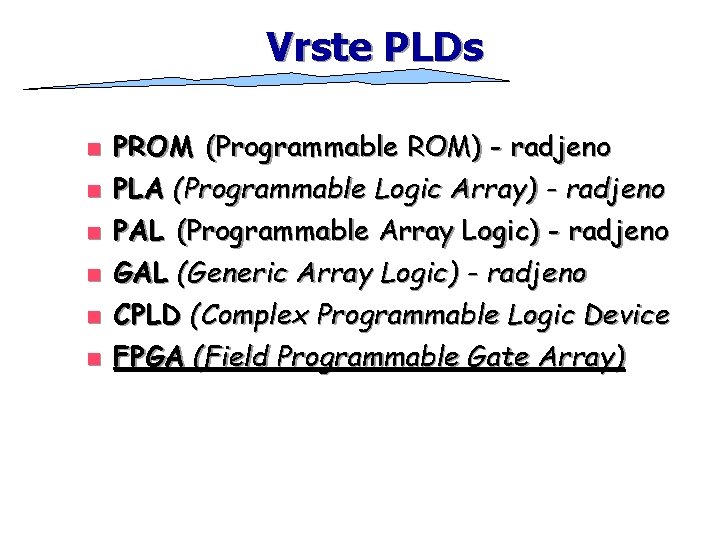

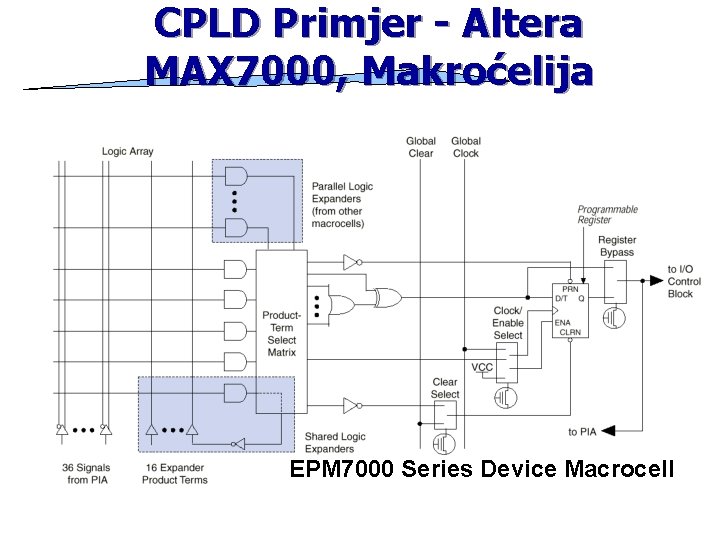

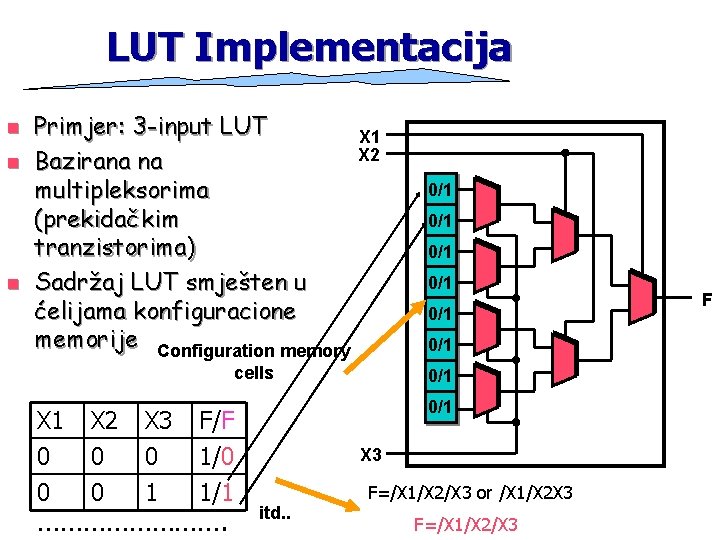

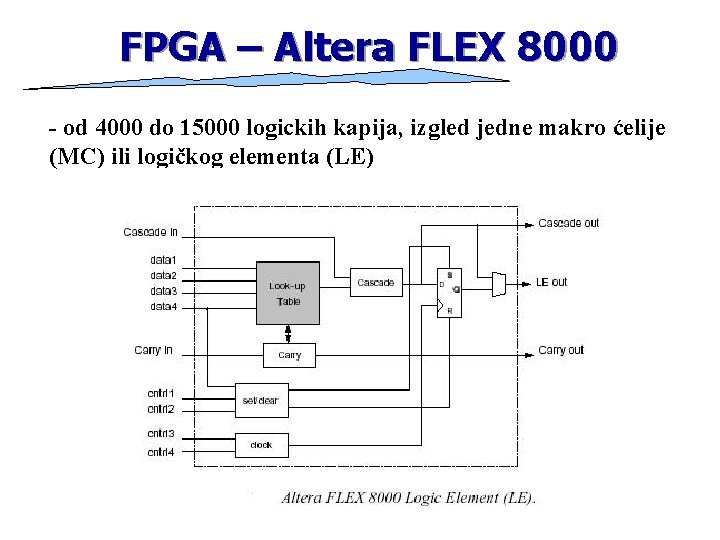

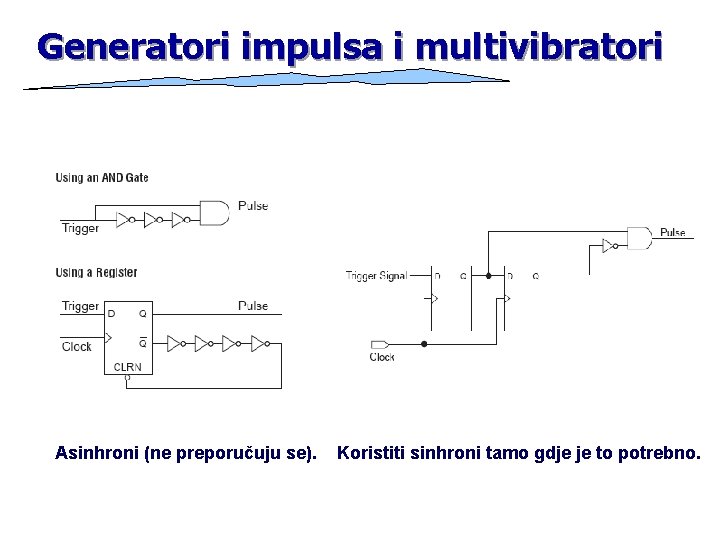

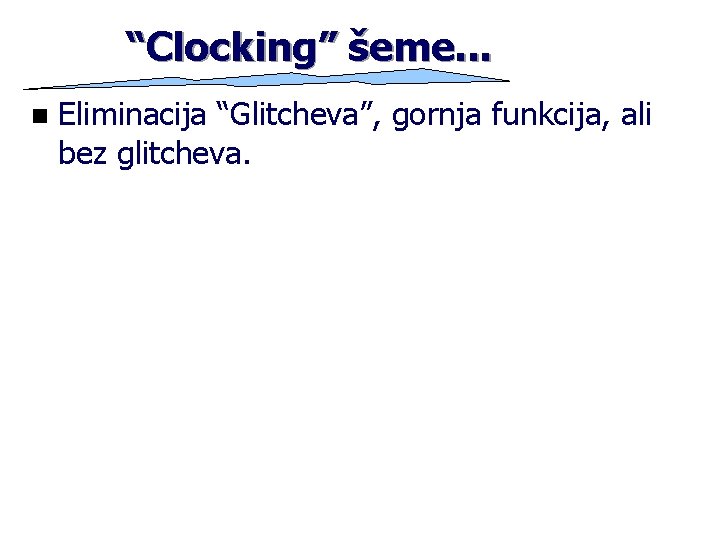

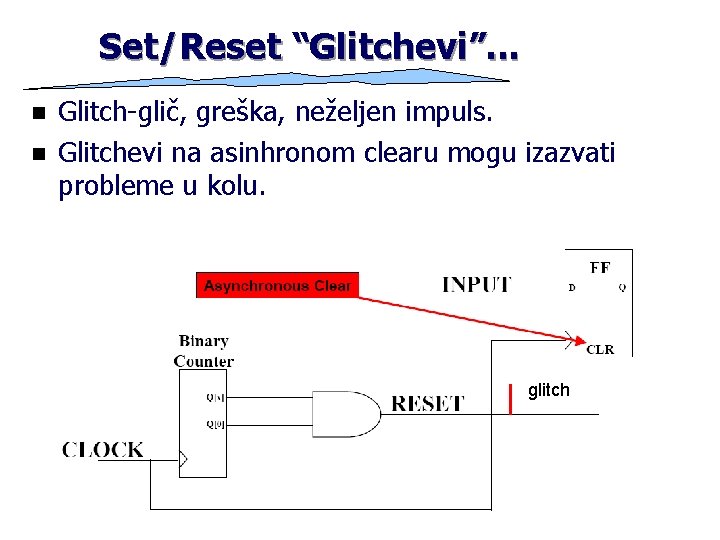

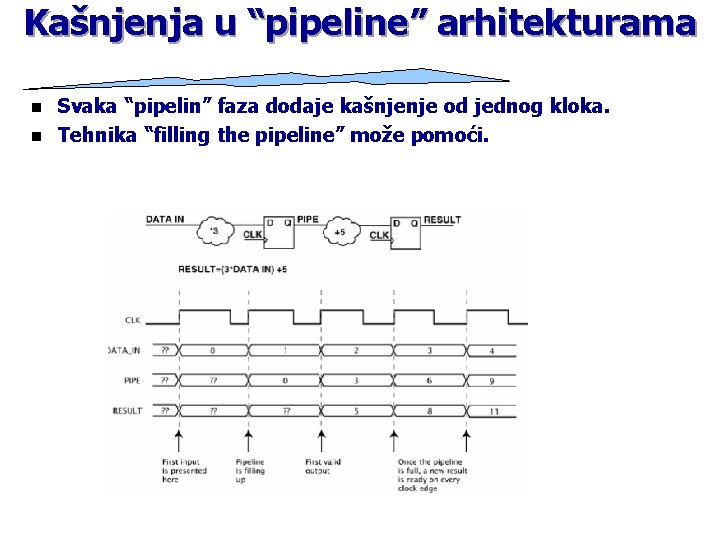

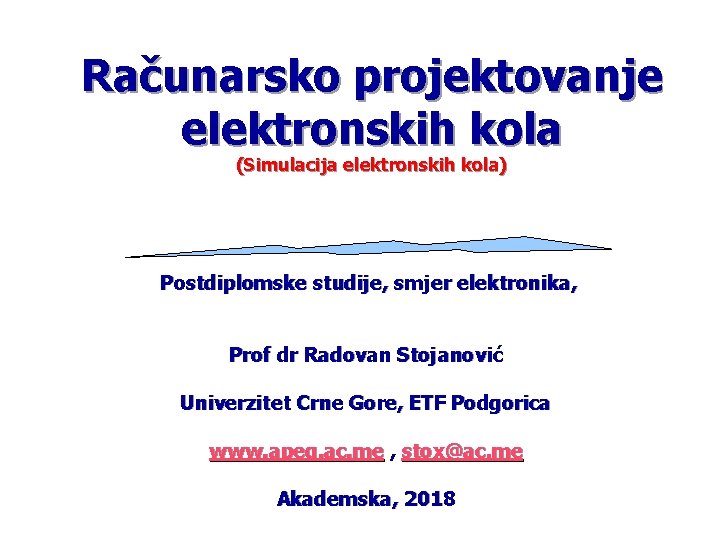

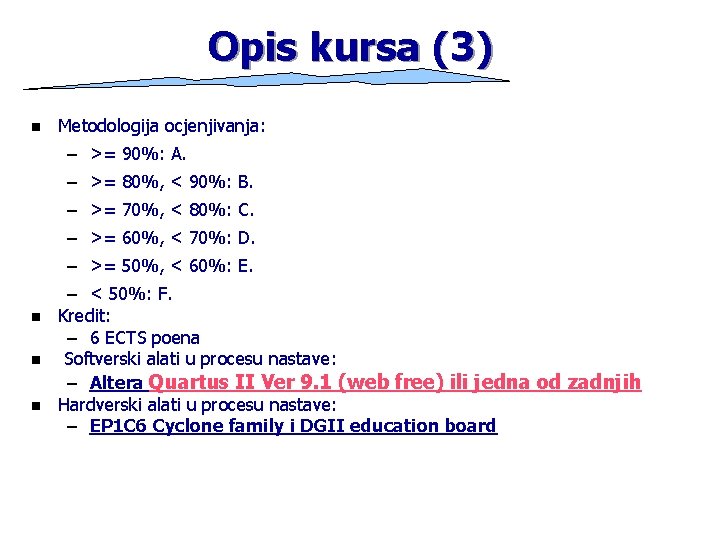

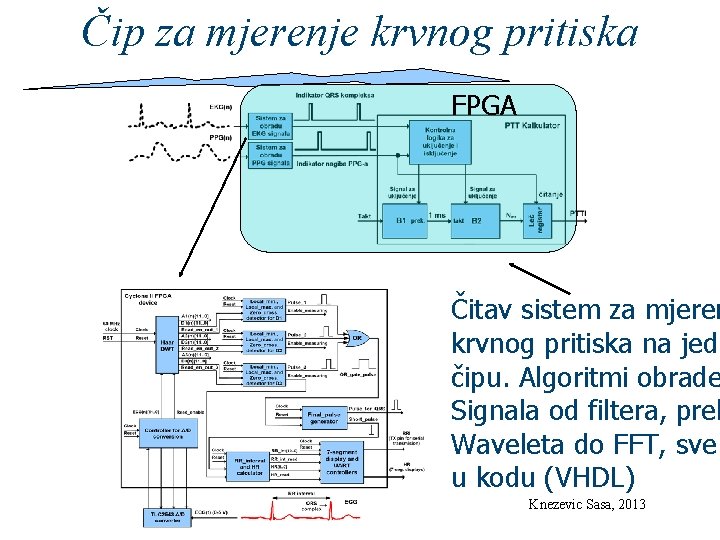

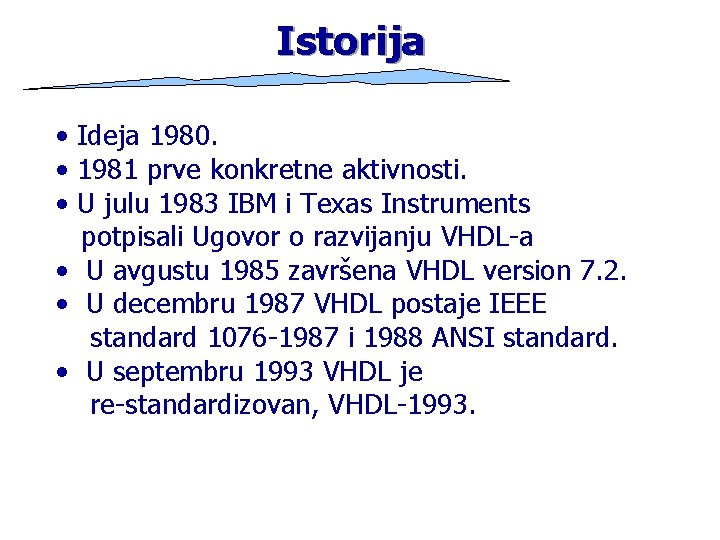

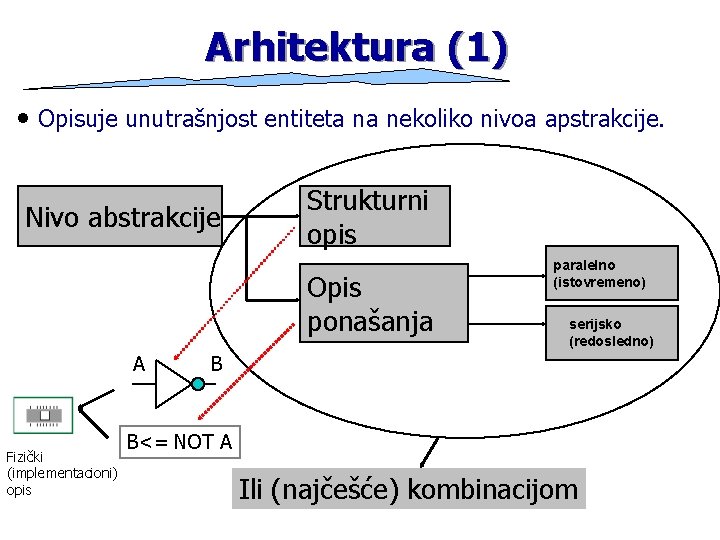

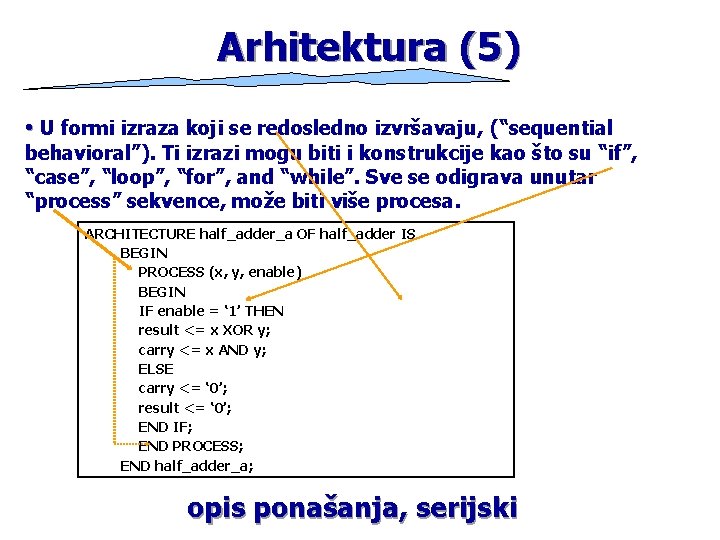

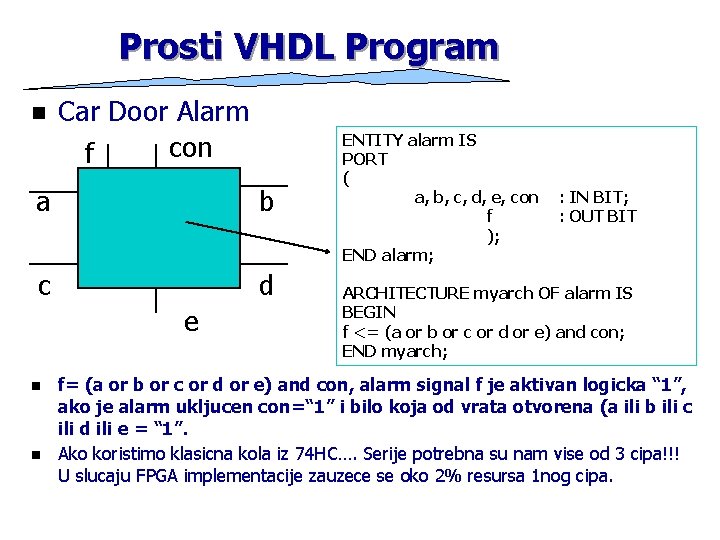

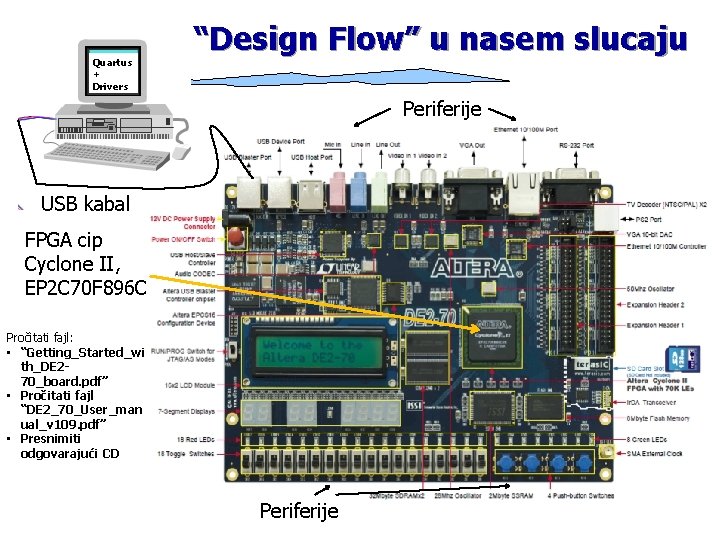

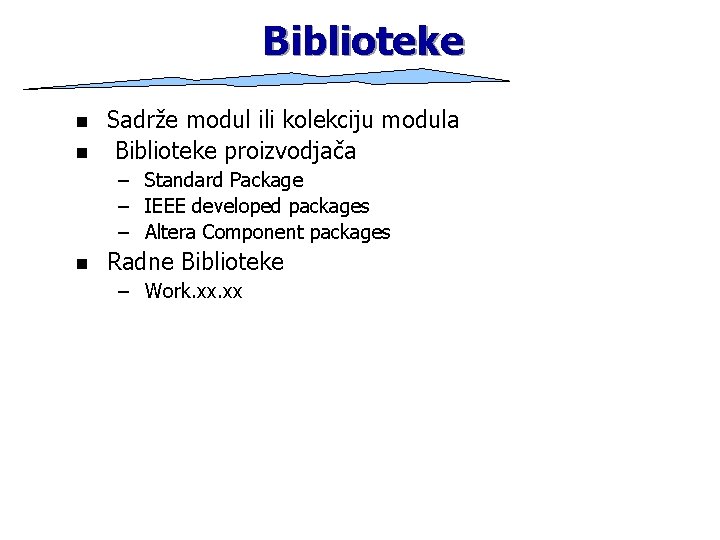

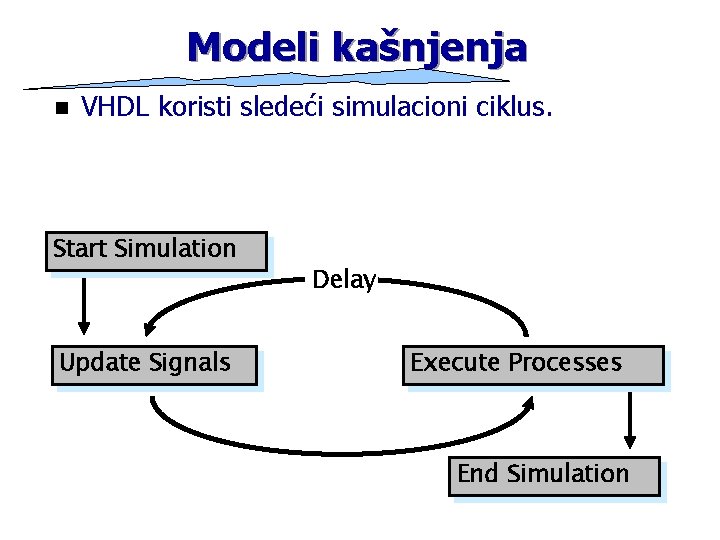

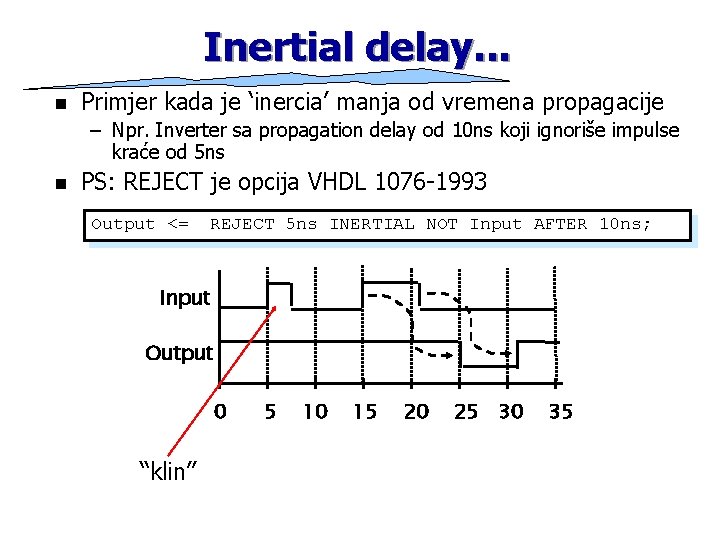

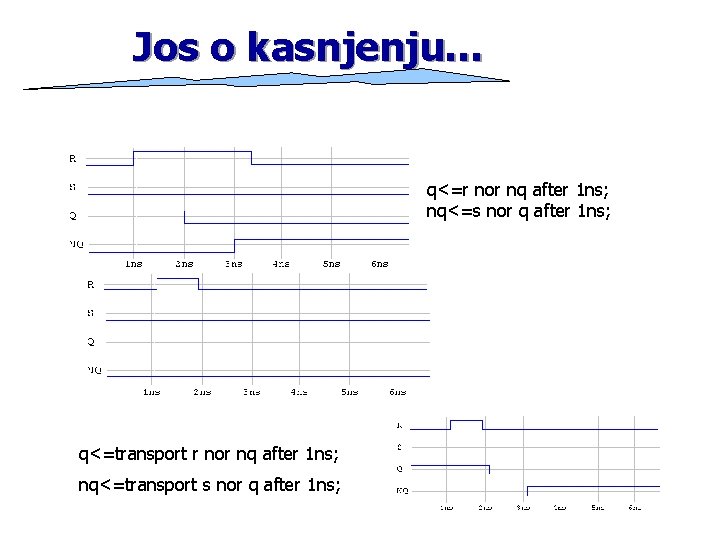

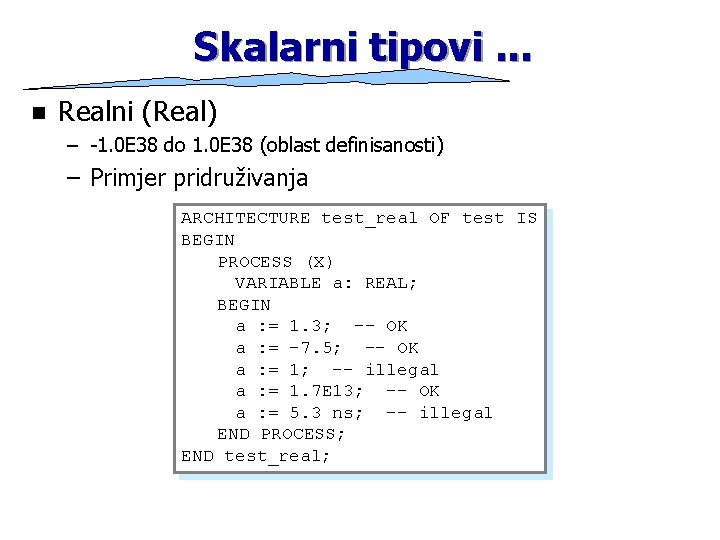

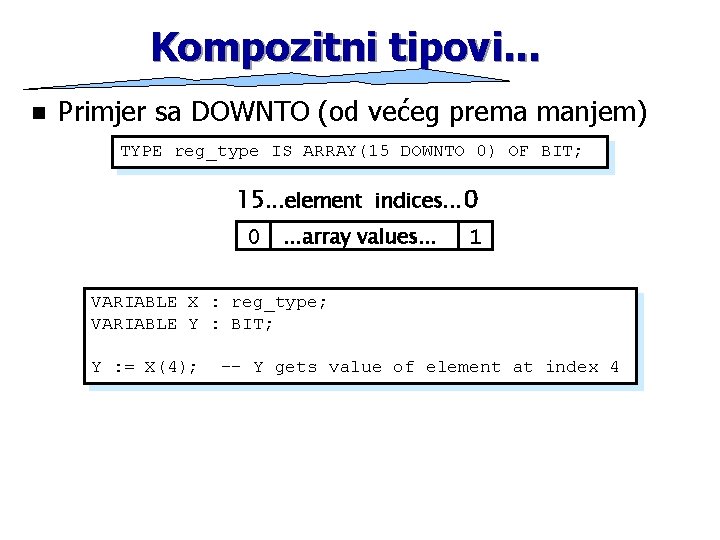

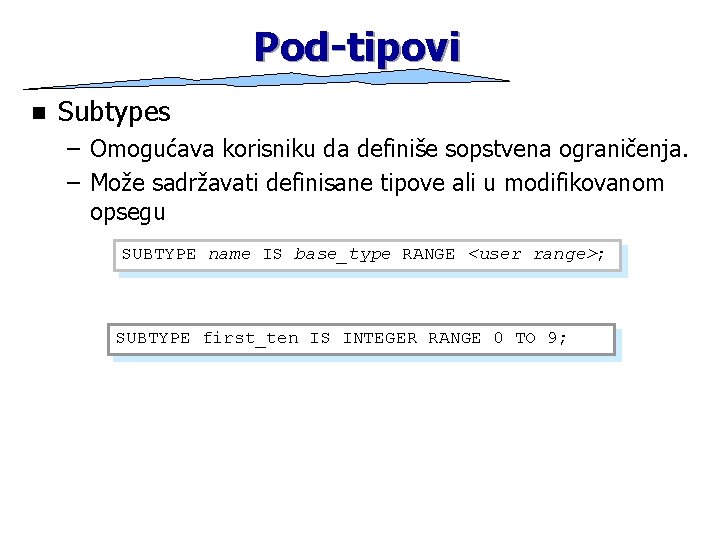

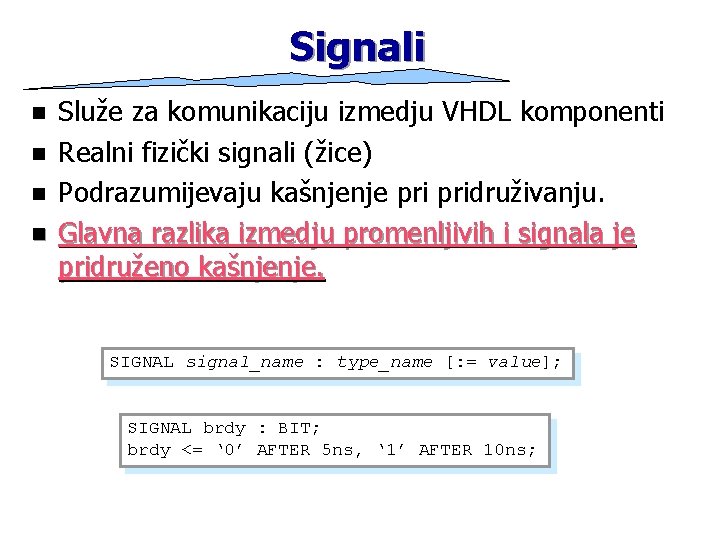

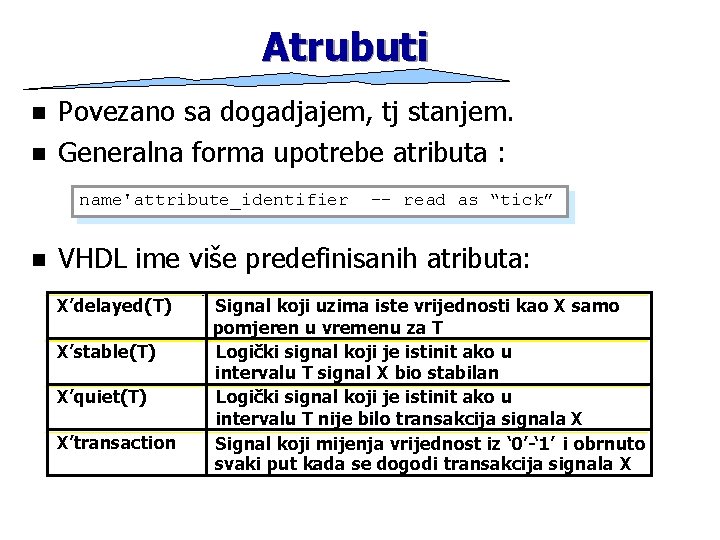

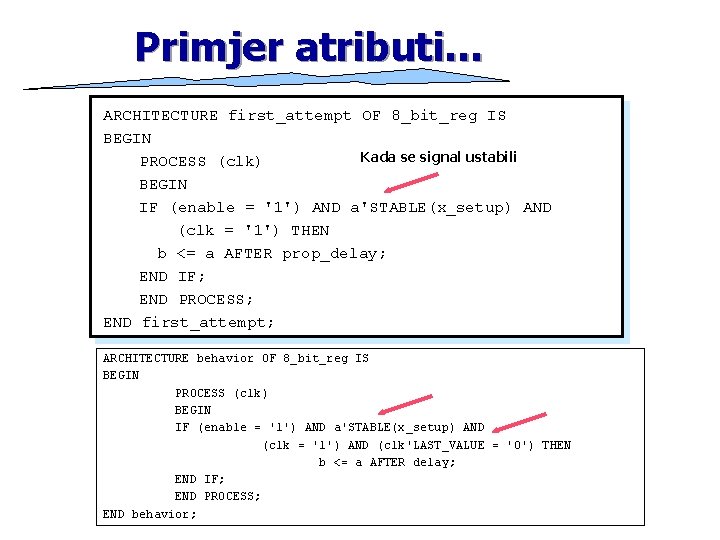

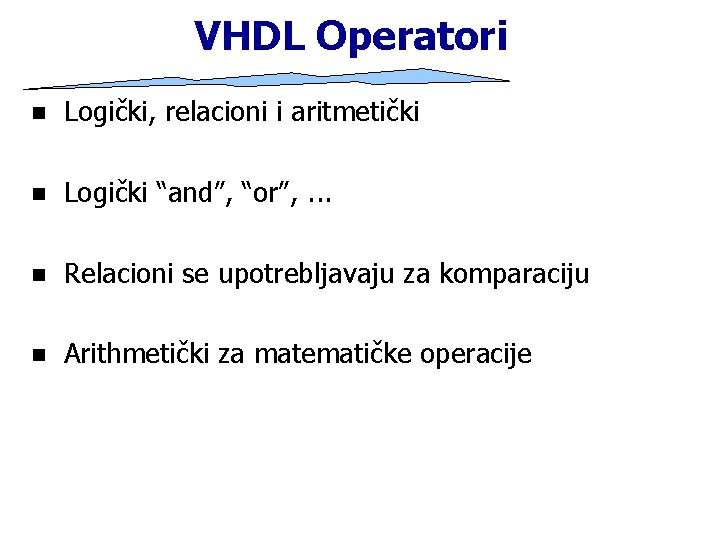

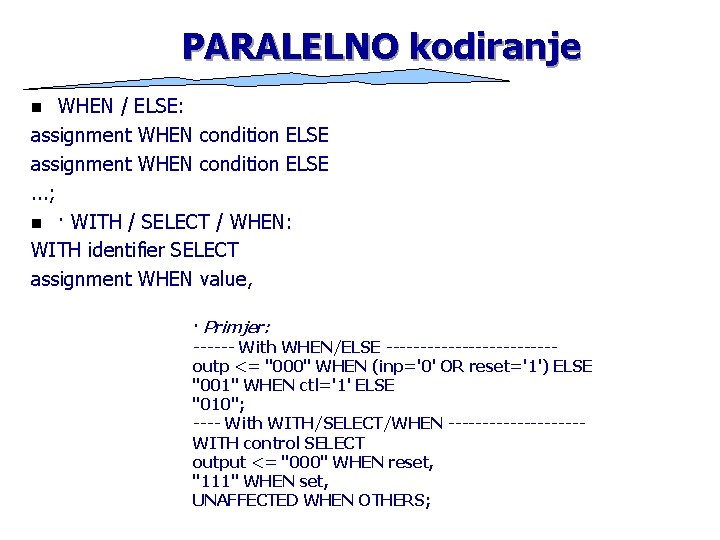

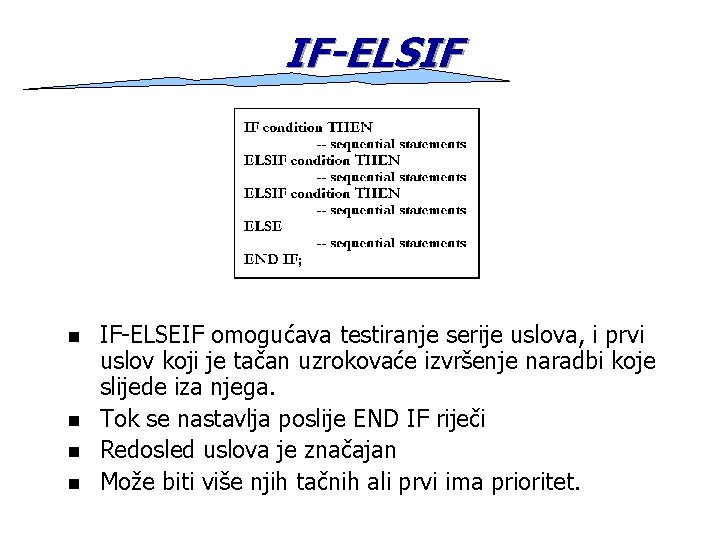

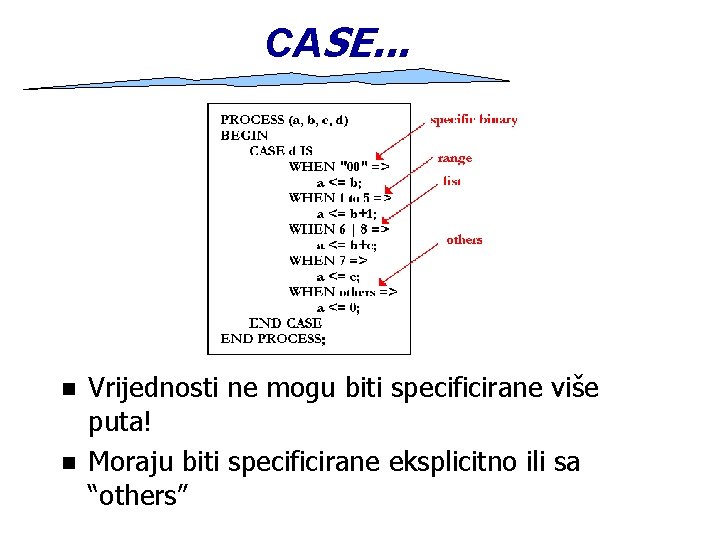

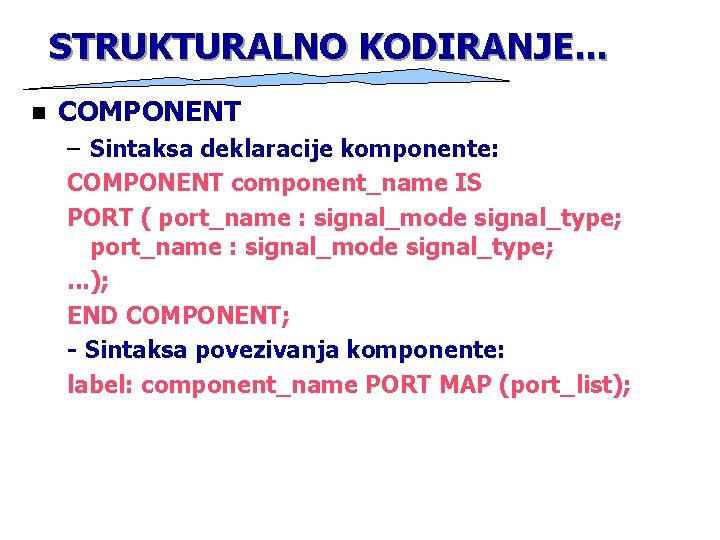

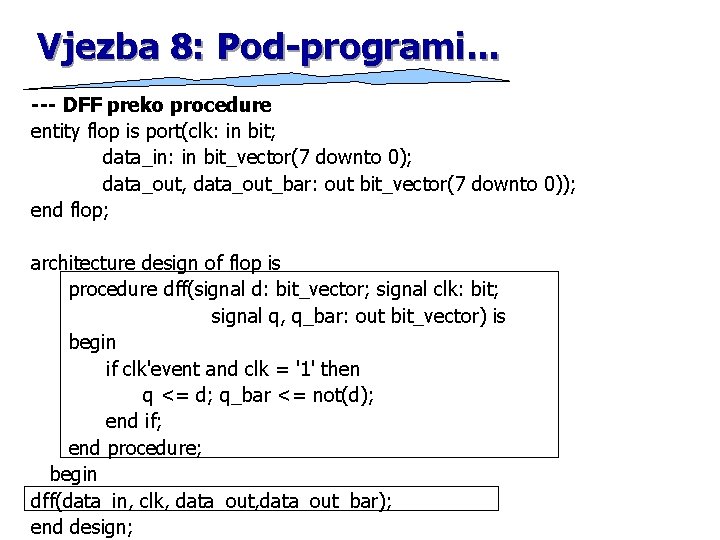

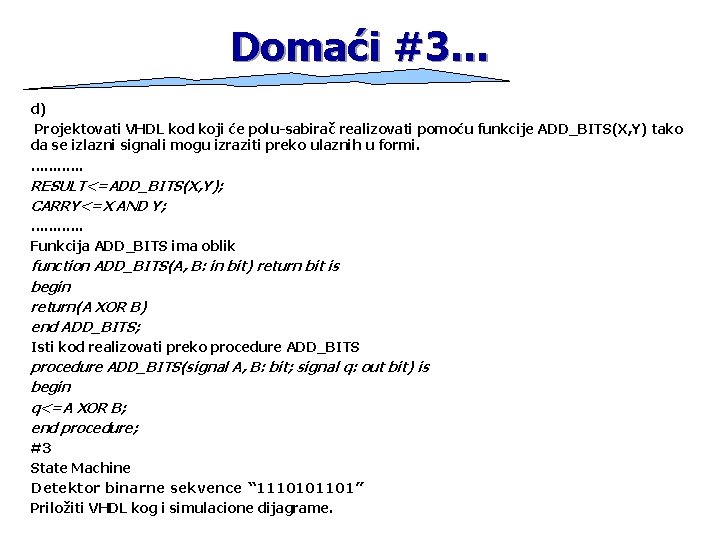

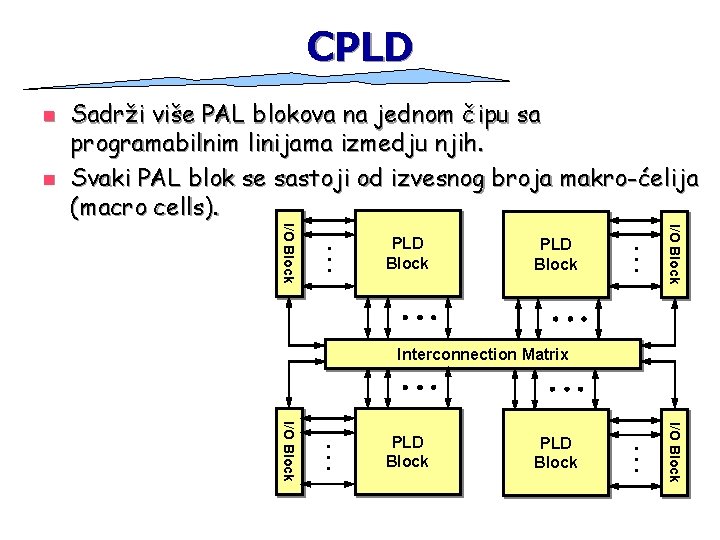

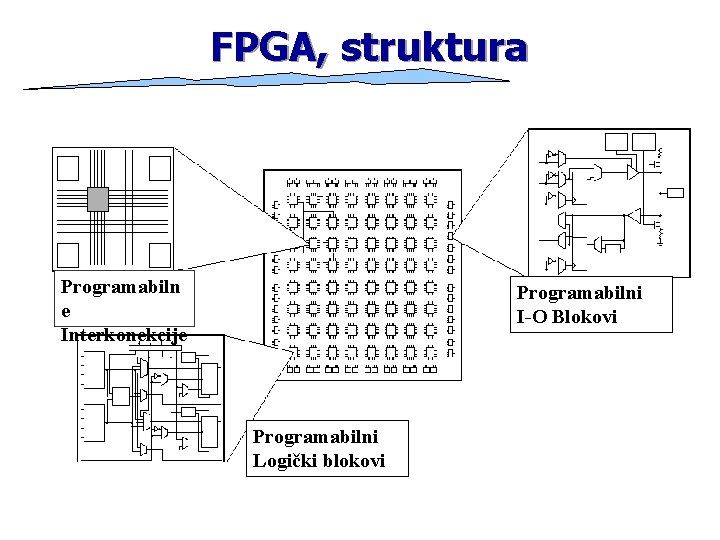

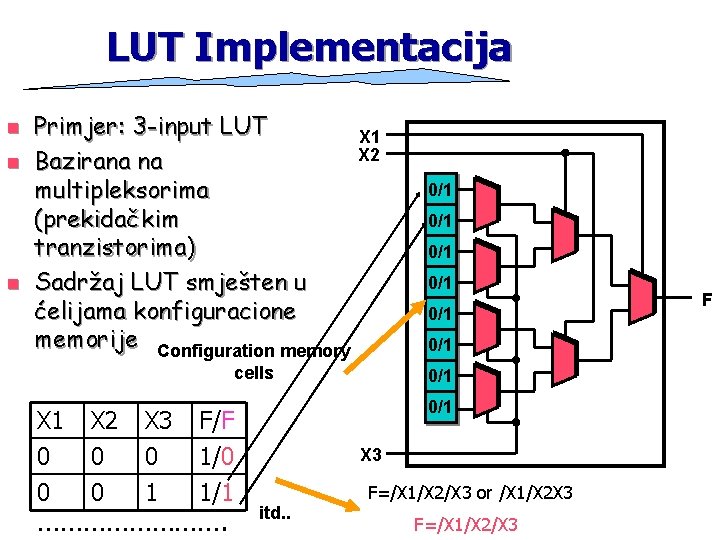

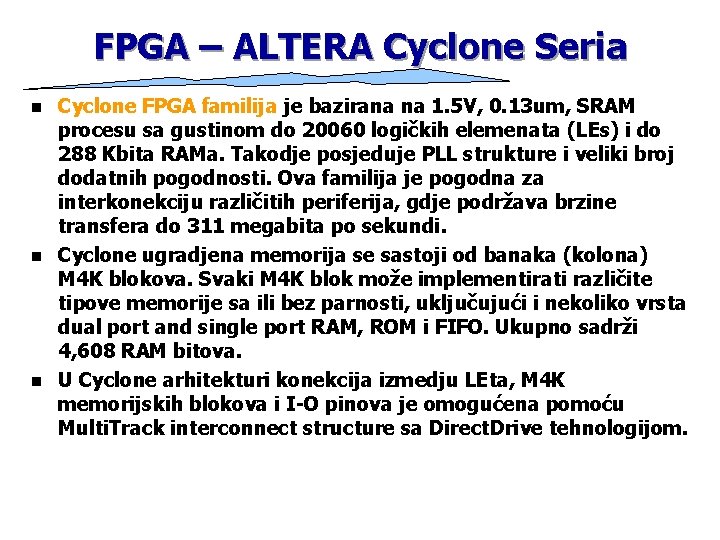

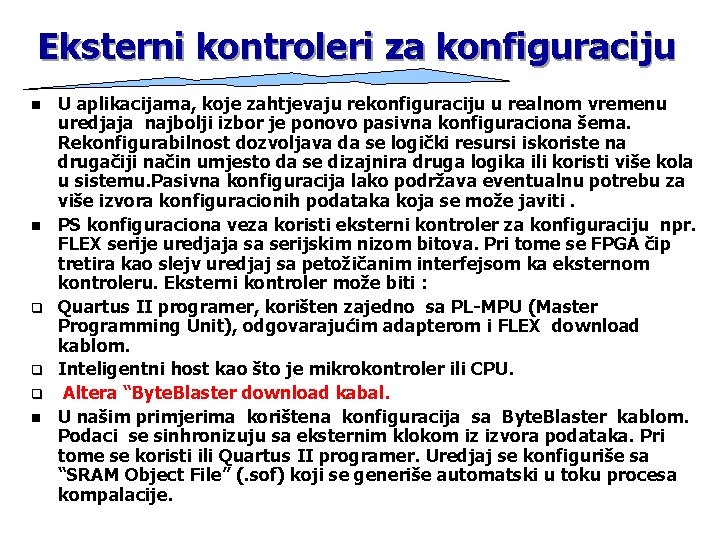

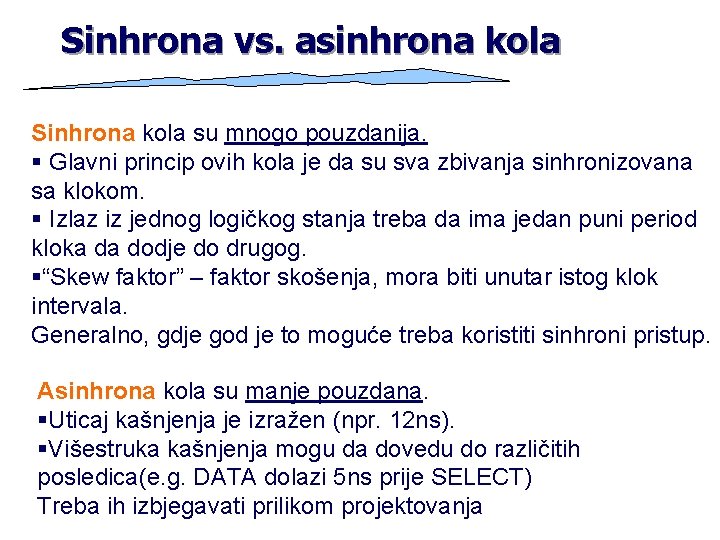

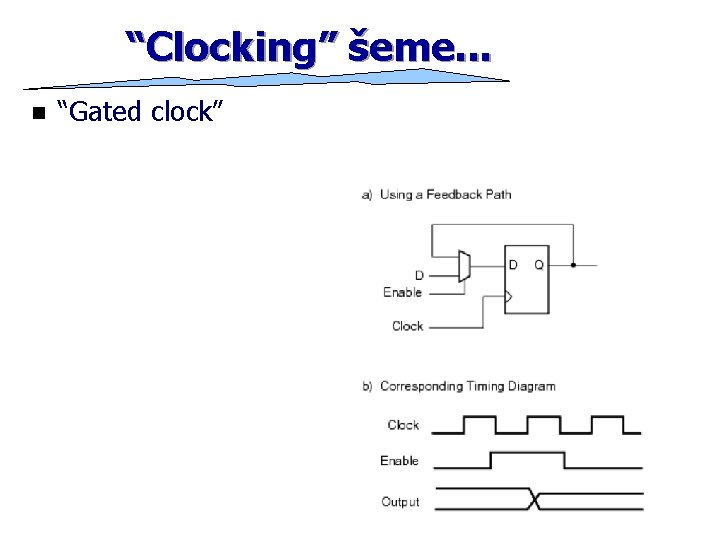

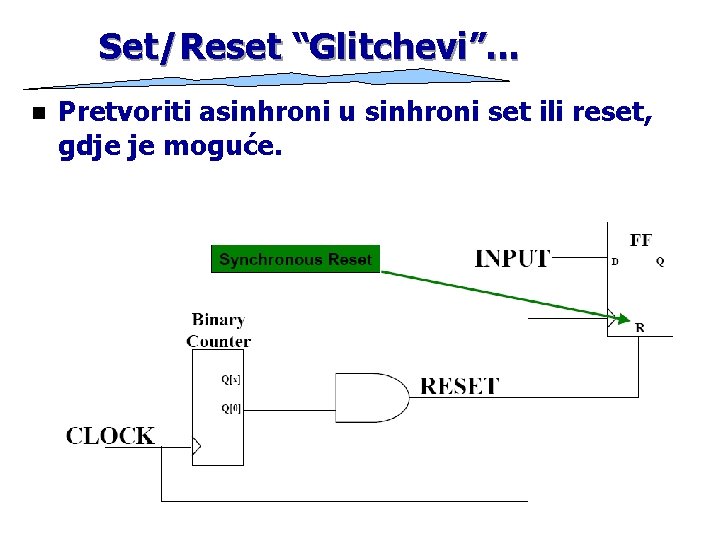

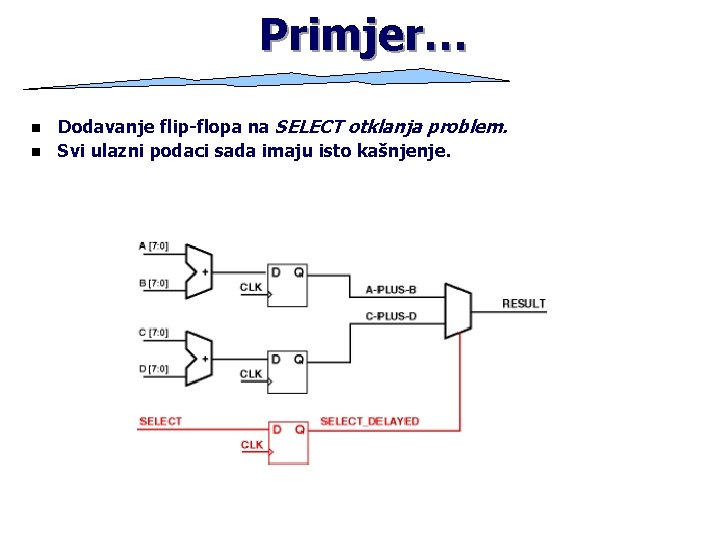

Napredni dizajn Primjer realizacije FIR filtra: gdje su: y[n] izlaz x(n-i) je ulaz u prethodnom i vremenu bi koeficijent filtra N je red filtra, N+1 “slavina” https: //www. digikey. com/eewiki/pages/viewpage. action? page. Id=78086825 https: //www. doulos. com/knowhow/vhdl_designers_guide/model s/finite_impulse_response_fir_filter/

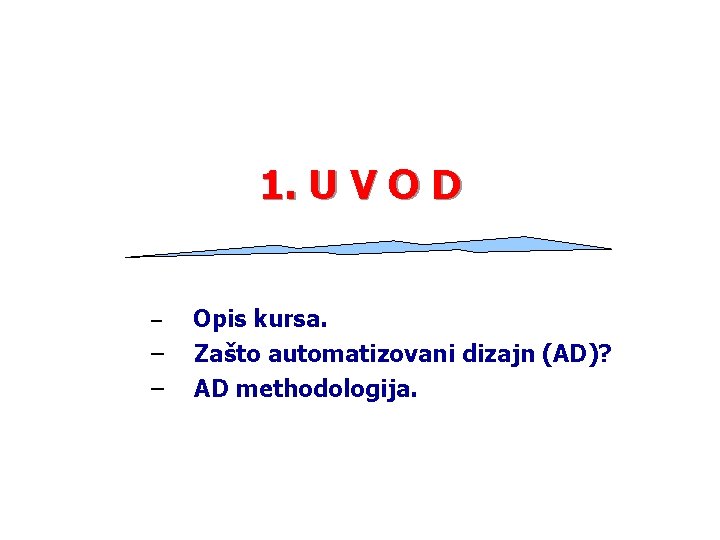

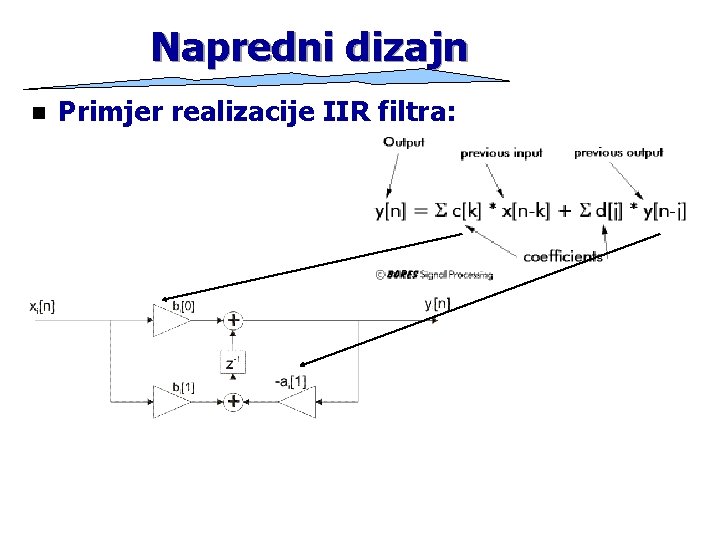

Napredni dizajn n Primjer realizacije IIR filtra:

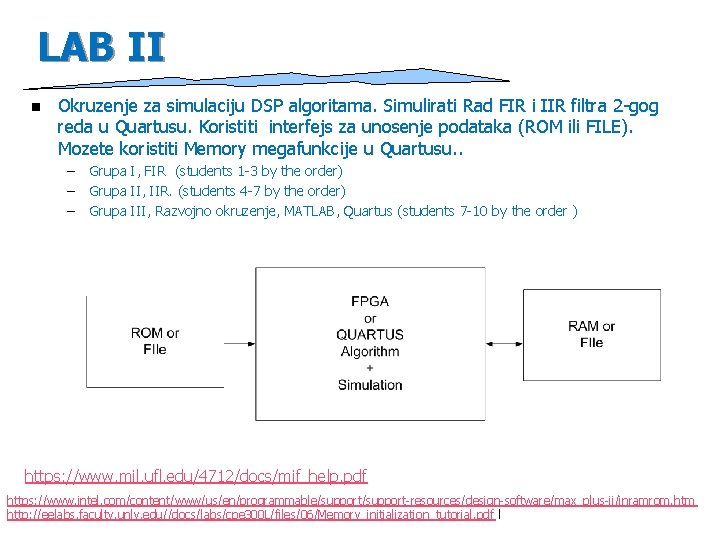

LAB II n Okruzenje za simulaciju DSP algoritama. Simulirati Rad FIR i IIR filtra 2 -gog reda u Quartusu. Koristiti interfejs za unosenje podataka (ROM ili FILE). Mozete koristiti Memory megafunkcije u Quartusu. . – – – Grupa I, FIR (students 1 -3 by the order) Grupa II, IIR. (students 4 -7 by the order) Grupa III, Razvojno okruzenje, MATLAB, Quartus (students 7 -10 by the order ) https: //www. mil. ufl. edu/4712/docs/mif_help. pdf https: //www. intel. com/content/www/us/en/programmable/support-resources/design-software/max_plus-ii/inramrom. htm http: //eelabs. faculty. unlv. edu//docs/labs/cpe 300 L/files/06/Memory_initialization_tutorial. pdf l

Projektovanje baza podataka

Projektovanje baza podataka Projektovanje stambenih zgrada

Projektovanje stambenih zgrada Ortogonalne projekcije

Ortogonalne projekcije Modeliranje i simulacija

Modeliranje i simulacija Simulakrumi i simulacija

Simulakrumi i simulacija Kolesarski izpit 5 razred vaje

Kolesarski izpit 5 razred vaje Velika kola pravopis

Velika kola pravopis Beyce kola

Beyce kola Erno teitti

Erno teitti Skloňování slova kola

Skloňování slova kola Pozadine kola

Pozadine kola Diferencijalni pojacavac

Diferencijalni pojacavac Rysowanie figur

Rysowanie figur Auto kola

Auto kola Cochineal böceği kola

Cochineal böceği kola Karla kola

Karla kola Itvan

Itvan Promiu

Promiu Magnetizam elektrotehnika

Magnetizam elektrotehnika Erno kola

Erno kola Forage de kola

Forage de kola Sloh popis obrazku

Sloh popis obrazku Oka kola

Oka kola Kola jilemnice

Kola jilemnice Lokacija teretnih kola

Lokacija teretnih kola Obvod obdlznika

Obvod obdlznika Mile živčić

Mile živčić Hipersorber

Hipersorber Mala sportska škola koprivnica

Mala sportska škola koprivnica Moja kola

Moja kola Karolina kola

Karolina kola Komutacija kanala

Komutacija kanala Popis kola sloh

Popis kola sloh M. deltoideus

M. deltoideus Redna i paralelna veza kondenzatora

Redna i paralelna veza kondenzatora Výpočet ozubených kolies

Výpočet ozubených kolies Foda de inca kola

Foda de inca kola Kolena skloňování

Kolena skloňování Kola land

Kola land Obvod trojholnika

Obvod trojholnika Obwod kola

Obwod kola Kola reg

Kola reg Sağ kürek kemiğinden kola vuran ağrı

Sağ kürek kemiğinden kola vuran ağrı Moja kola

Moja kola Rtl inverter

Rtl inverter Logicka kola zadaci

Logicka kola zadaci Ggl pada generator bangkit tergantung arus penguatan dan

Ggl pada generator bangkit tergantung arus penguatan dan Odklon kola

Odklon kola Erno kola

Erno kola Marijan biruš

Marijan biruš Panteli kola

Panteli kola Hidroliza

Hidroliza Omov zakon

Omov zakon Srednja medicinska škola slavonski brod

Srednja medicinska škola slavonski brod Obsah

Obsah Vrste srednjih škola

Vrste srednjih škola