Protected Mode Addressing Mechanism The 80386 DX has

- Slides: 30

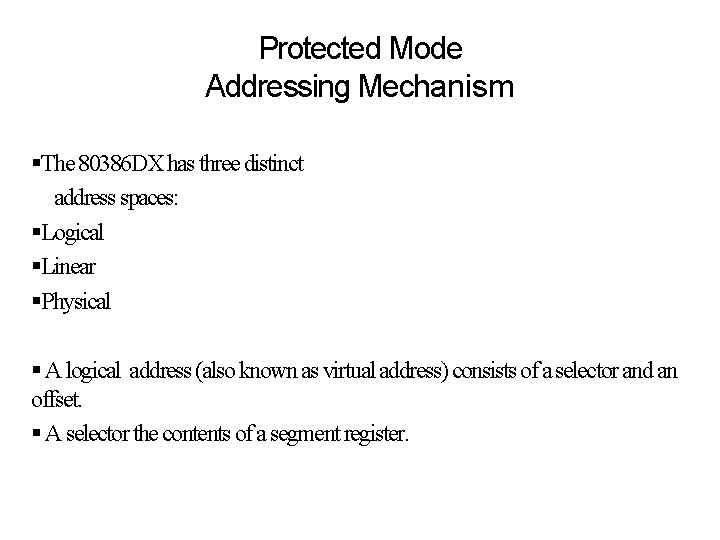

Protected Mode Addressing Mechanism §The 80386 DX has three distinct address spaces: §Logical §Linear §Physical § A logical address (also known as virtual address) consists of a selector and an offset. § A selector the contents of a segment register.

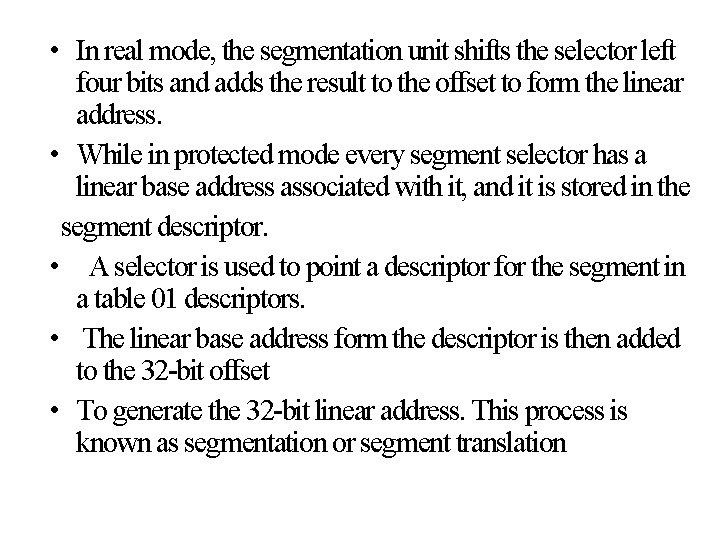

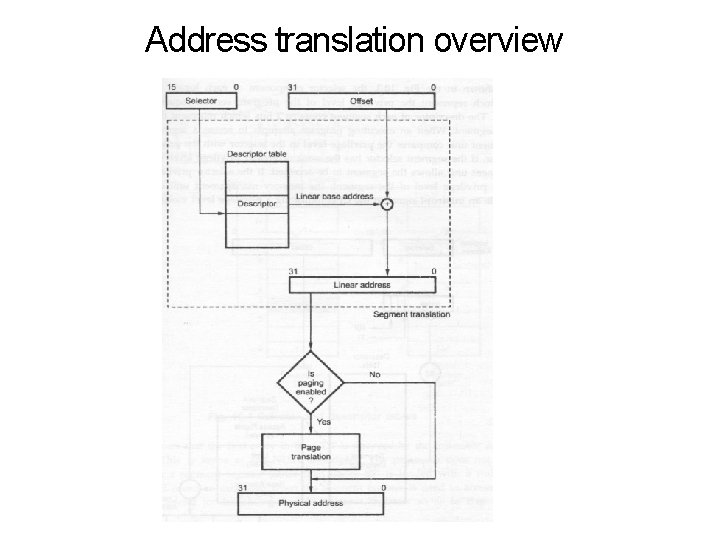

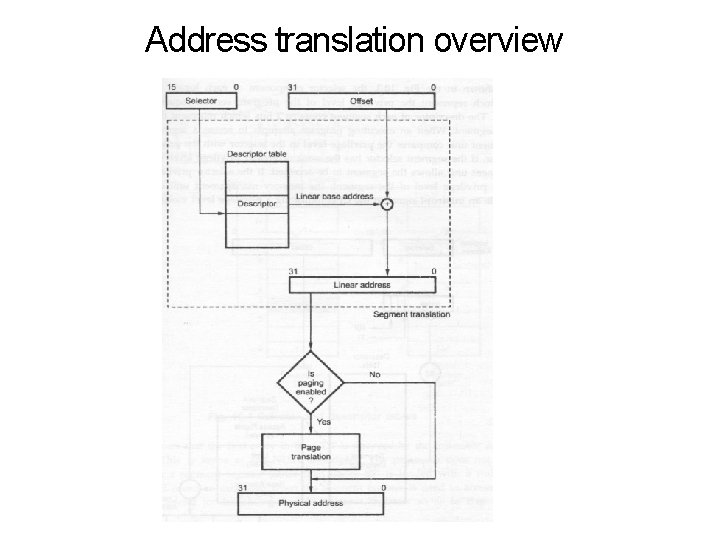

• In real mode, the segmentation unit shifts the selector left four bits and adds the result to the offset to form the linear address. • While in protected mode every segment selector has a linear base address associated with it, and it is stored in the segment descriptor. • A selector is used to point a descriptor for the segment in a table 01 descriptors. • The linear base address form the descriptor is then added to the 32 -bit offset • To generate the 32 -bit linear address. This process is known as segmentation or segment translation

• If paging unit is not enabled then the 32 -bit linear address corresponds to the physical address. • But if paging unit is enabled, paging mechanism translates the linear address space into the physical address space by paging translation.

Address translation overview

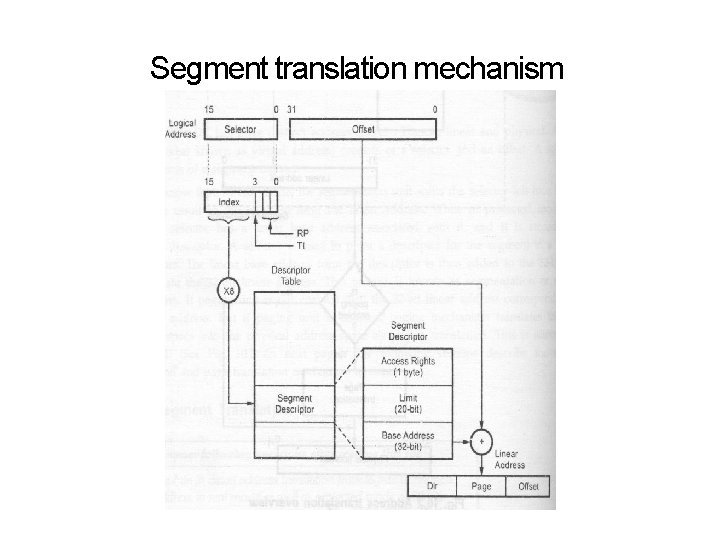

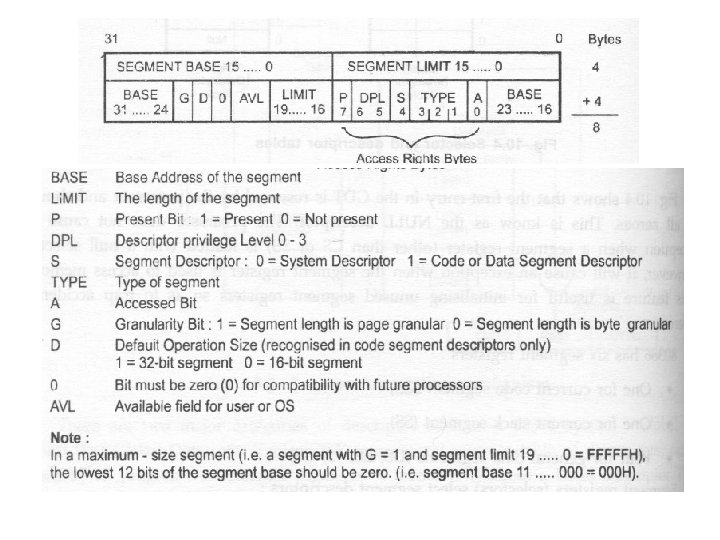

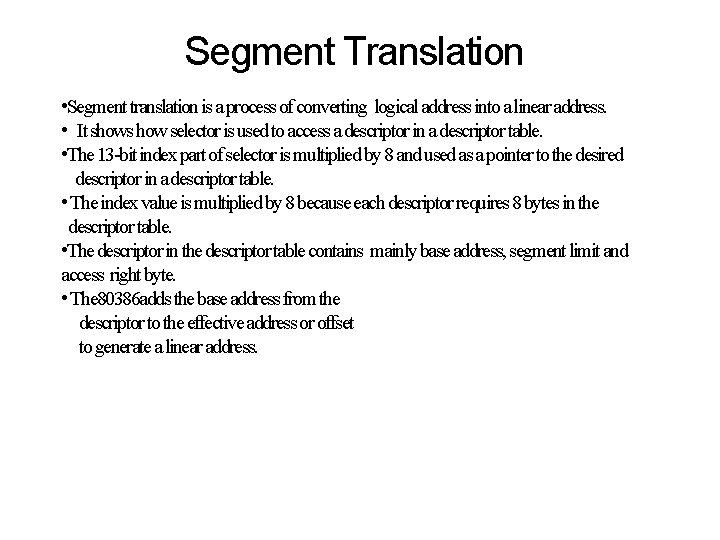

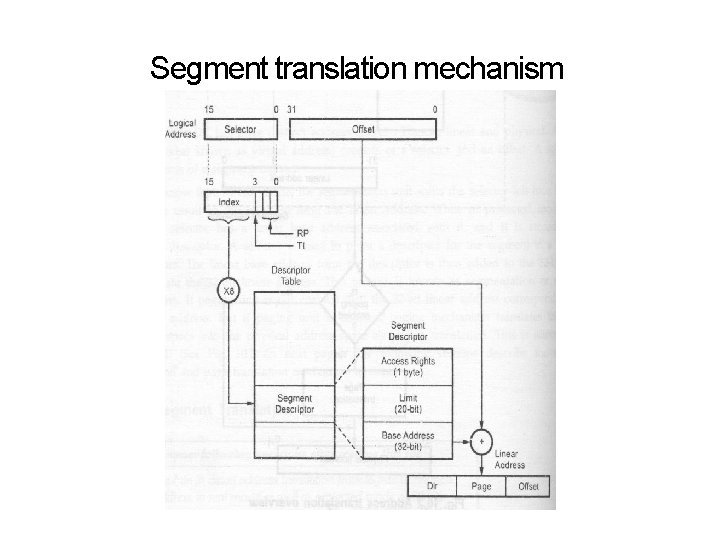

Segment Translation • Segment translation is a process of converting logical address into a linear address. • It shows how selector is used to access a descriptor in a descriptor table. • The 13 -bit index part of selector is multiplied by 8 and used as a pointer to the desired descriptor in a descriptor table. • The index value is multiplied by 8 because each descriptor requires 8 bytes in the descriptor table. • The descriptor in the descriptor table contains mainly base address, segment limit and access right byte. • The 80386 adds the base address from the descriptor to the effective address or offset to generate a linear address.

Segment translation mechanism

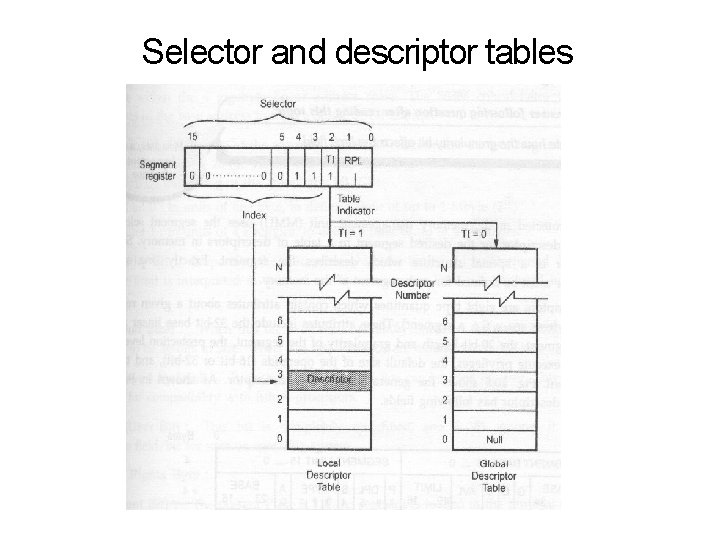

• As shown in the Fig, the selector component of each logical address contains 2 bits which represent the privilege level of the program section requesting access to a segment. • The descriptor of each segment contains 2 bits which represent the privilege level of that segment. • When an executing program attempts to access a segment, the memory management unit compares the privilege level in the selector with the privilege level in the descriptor.

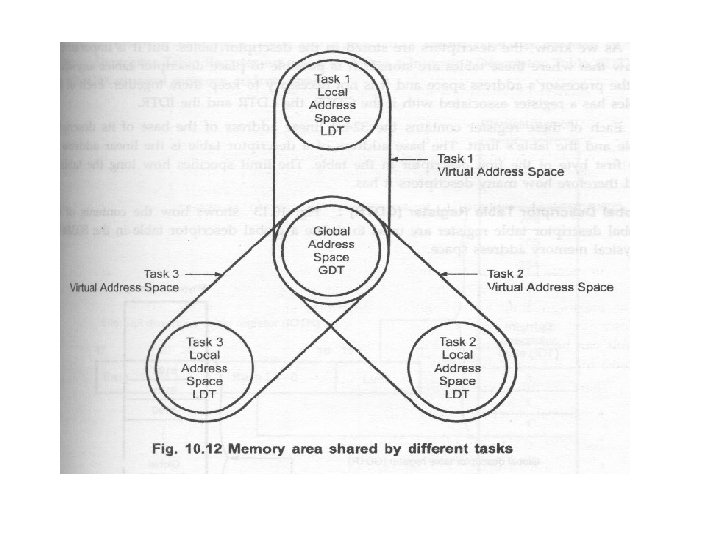

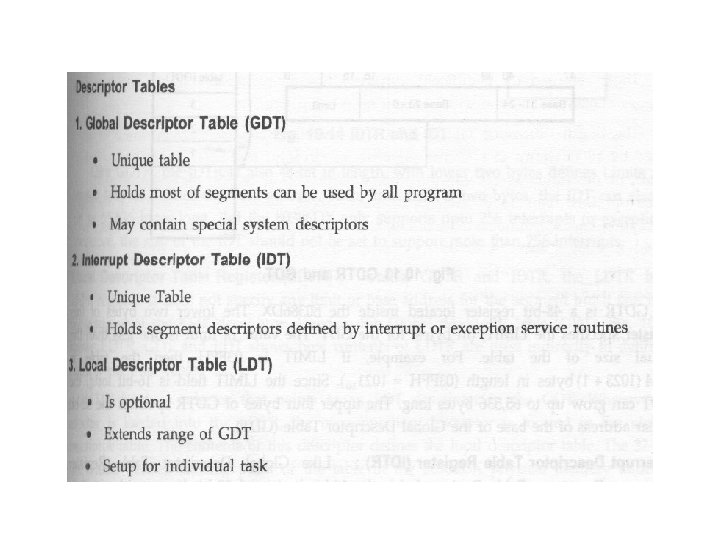

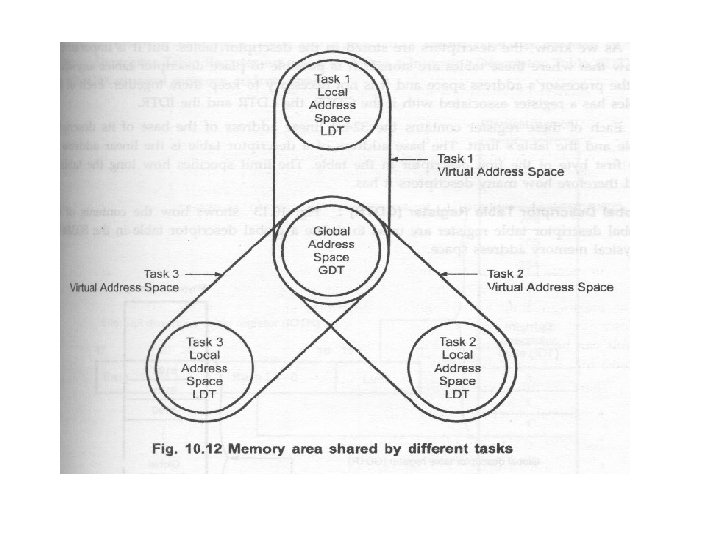

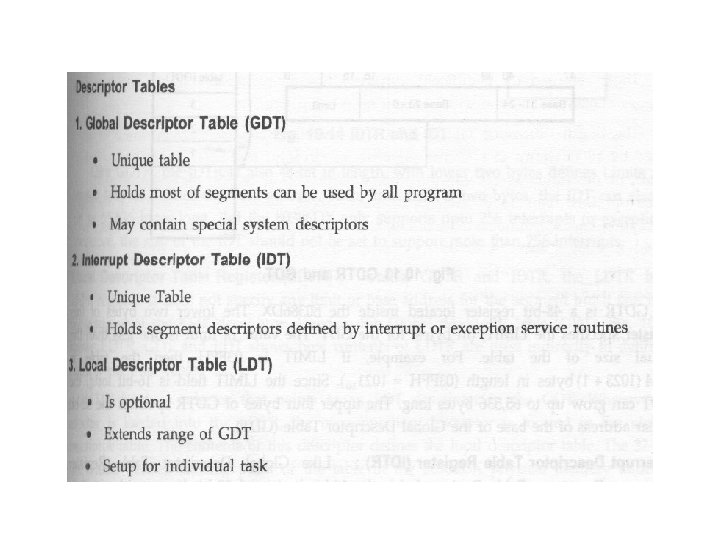

• If the segment selector has the same or greater privilege level, then the memory management unit allows the segment to be accessed. • If the selector privilege level is lower than the privilege level of the segment, the memory management unit denies the access and sends an interrupt signal to the CPU indicating a privilege level violation. • There are two major categories of descriptor table in a 80386 system: Global and Local.

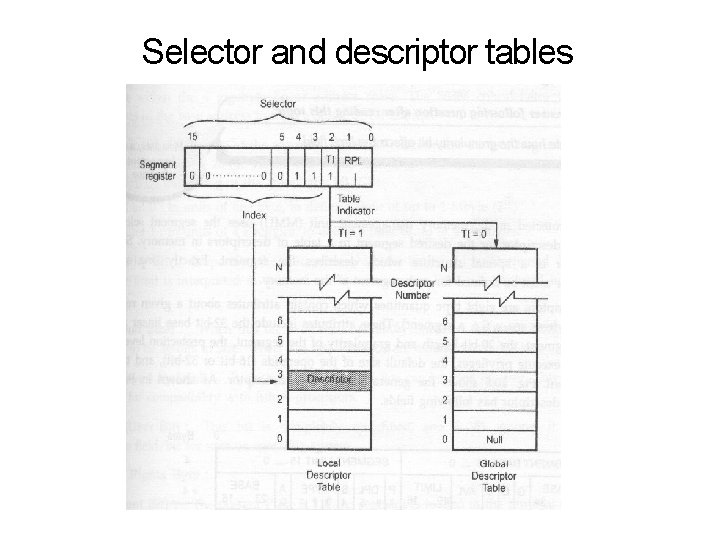

• The Global Descriptor Table (GDT) is a general purpose table of descriptors, can used by all programs to reference segments of memory. • Whereas a Local Descriptor Table (LDT) are set up in the system for individual task or closely related group of tasks 1. • Table Indicator (TI) bit in the selector decides which descriptor table should be referred the selector. • When T 1 bit is 0, the index portion of the selector refers to a descriptor in GDT. When 11 bit is 1, it refers to descriptor in the current LDT.

Selector and descriptor tables

• Fig shows that the first entry in the GDT is reserved by the processor and should be all zeroes. • This is know as the NULL descriptor. The processor does not cause an exception when a segment register (other than C 5 or 55) is loaded with a null selector. • However, it will cause an exception when the segment register is used to access memory. • This feature is useful for initializing unused segment registers so as to trap accidental References.

• 80386 has six segment registers: 1)One for current code segment (CS) 2)One for current stack segment (SS) 3)Four for general data segments (DS, ES, SS, GS) • Segment registers (selectors) select segment descriptors: 1) Thirteen bits select descriptor 2) One bit selects descriptor table 3)Two bits aid privilege checking

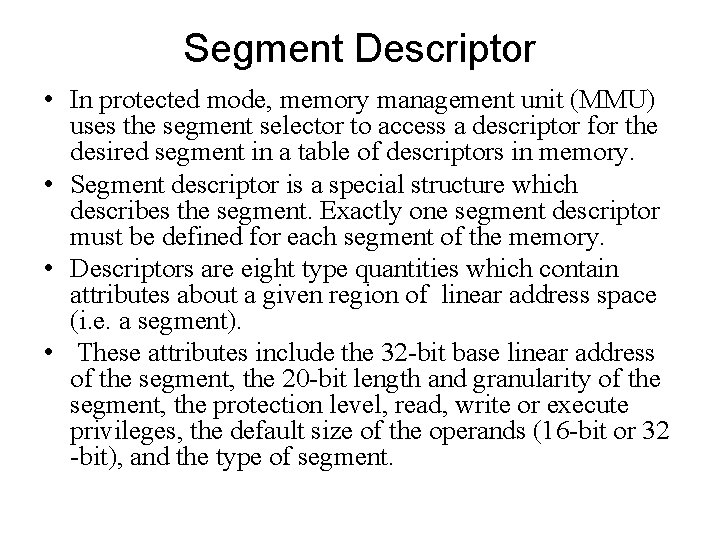

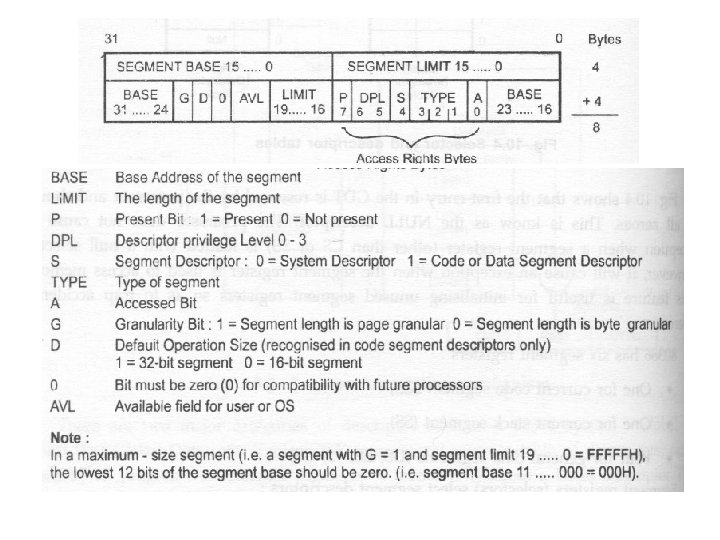

Segment Descriptor • In protected mode, memory management unit (MMU) uses the segment selector to access a descriptor for the desired segment in a table of descriptors in memory. • Segment descriptor is a special structure which describes the segment. Exactly one segment descriptor must be defined for each segment of the memory. • Descriptors are eight type quantities which contain attributes about a given region of linear address space (i. e. a segment). • These attributes include the 32 -bit base linear address of the segment, the 20 -bit length and granularity of the segment, the protection level, read, write or execute privileges, the default size of the operands (16 -bit or 32 -bit), and the type of segment.

Descriptor Tables • • There are three types of descriptor tables: Global Descriptor Table (GDT) Local Descriptor Table (LDT) Interrupt Descriptor Table (IDT)

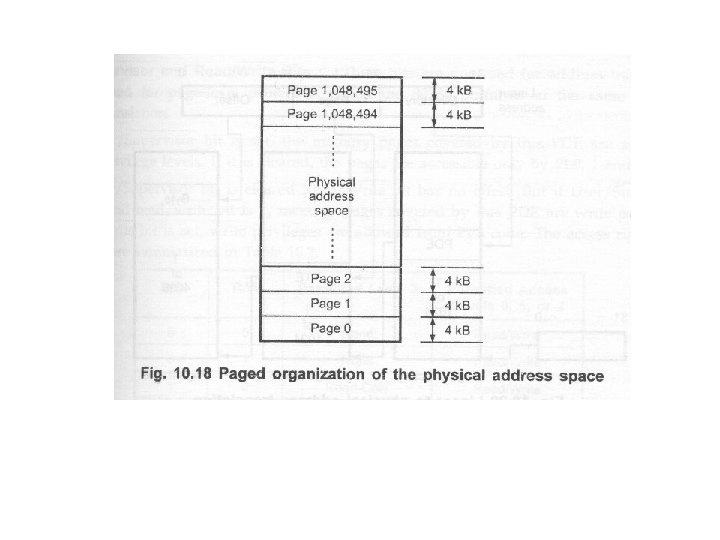

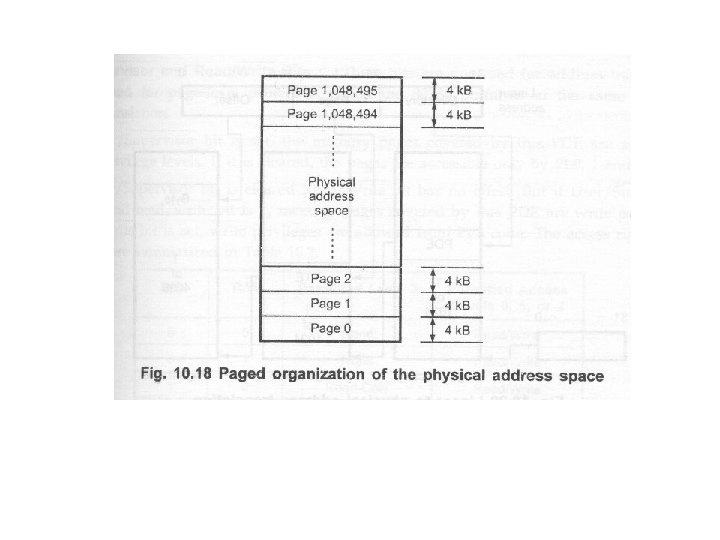

• Page translation is the second phase of address translation. In this phase 80386 transfoms a linear address generated by segment translation into a physical address. The page translation step is optional. • Page translation is in effect only when the PG bit of CR 0 is set. • Page translation is must if the operating system is to implement multiple virtual 8086 tasks, page-oriented protection, or page oriented virtual memory. • When paging is enabled, the paging unit arranges the physical address space into 1, 048, 496 pages that are each 4096 bytes long. Fig. shows organization of physical address space using paging.

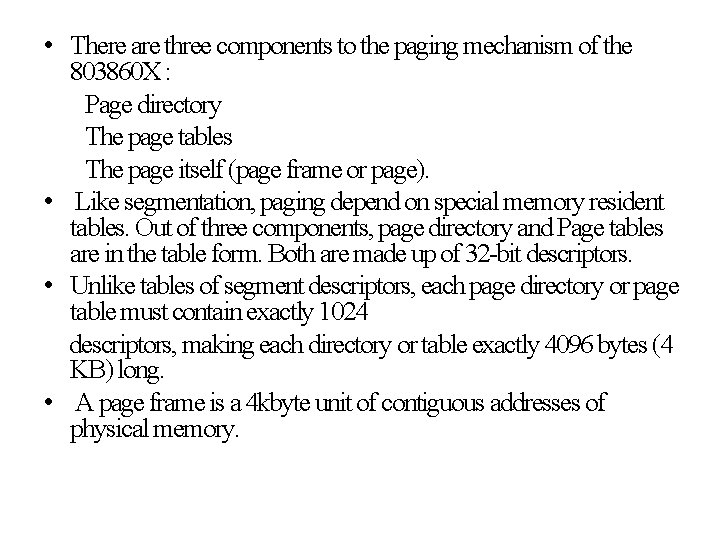

• There are three components to the paging mechanism of the 803860 X : Page directory The page tables The page itself (page frame or page). • Like segmentation, paging depend on special memory resident tables. Out of three components, page directory and Page tables are in the table form. Both are made up of 32 -bit descriptors. • Unlike tables of segment descriptors, each page directory or page table must contain exactly 1024 descriptors, making each directory or table exactly 4096 bytes (4 KB) long. • A page frame is a 4 kbyte unit of contiguous addresses of physical memory.

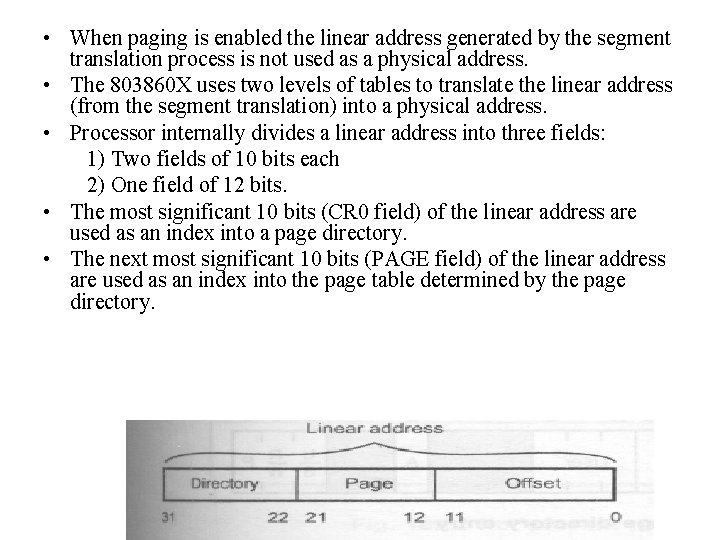

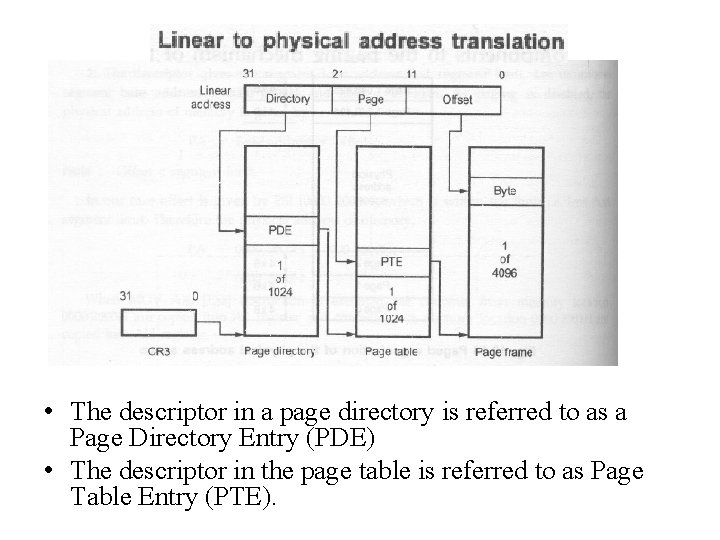

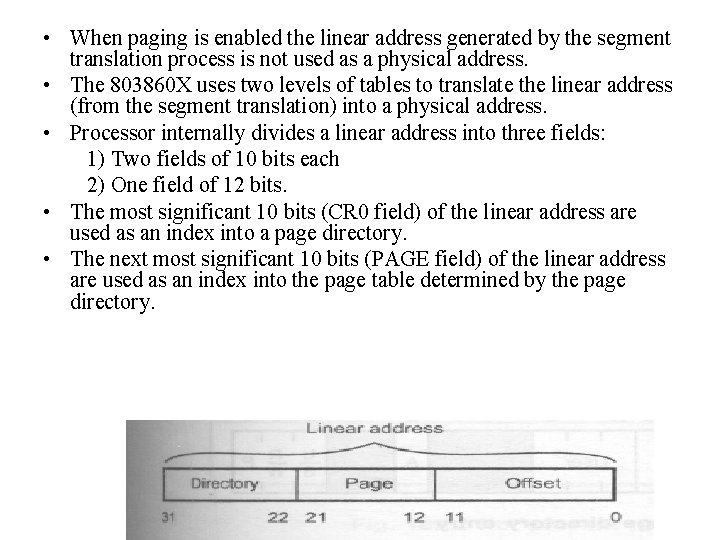

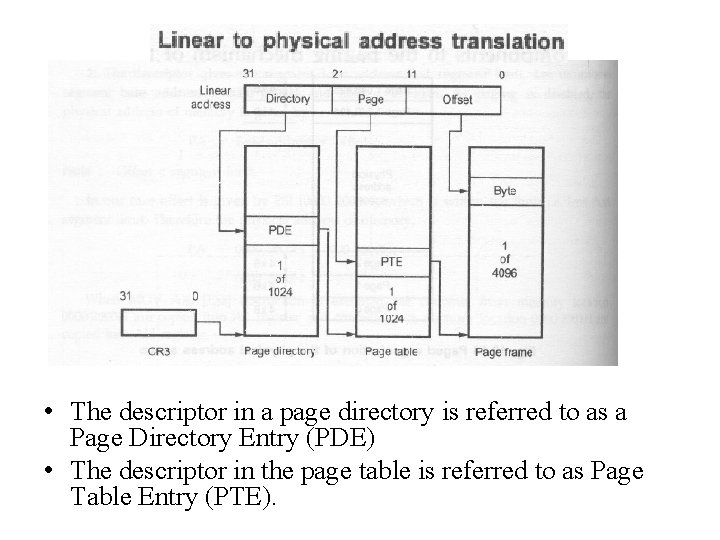

• When paging is enabled the linear address generated by the segment translation process is not used as a physical address. • The 803860 X uses two levels of tables to translate the linear address (from the segment translation) into a physical address. • Processor internally divides a linear address into three fields: 1) Two fields of 10 bits each 2) One field of 12 bits. • The most significant 10 bits (CR 0 field) of the linear address are used as an index into a page directory. • The next most significant 10 bits (PAGE field) of the linear address are used as an index into the page table determined by the page directory.

• The descriptor in a page directory is referred to as a Page Directory Entry (PDE) • The descriptor in the page table is referred to as Page Table Entry (PTE).

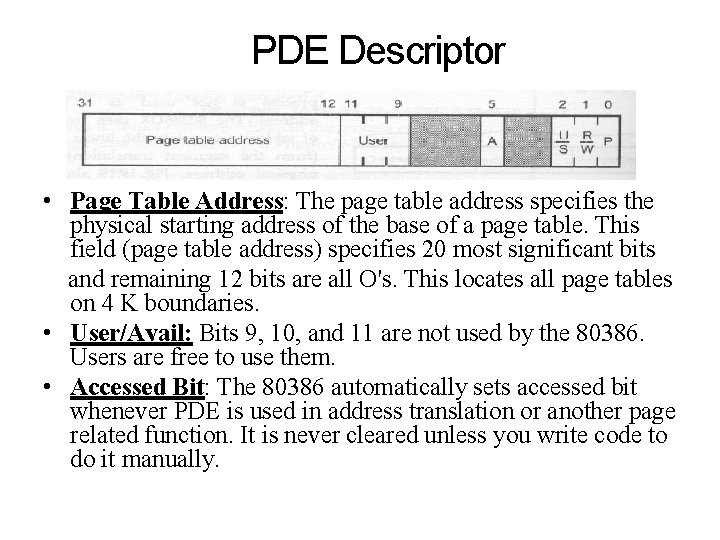

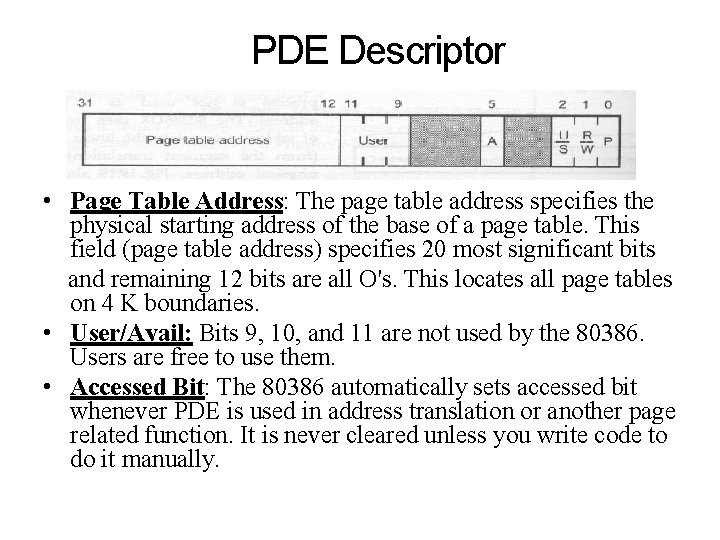

PDE Descriptor • Page Table Address: The page table address specifies the physical starting address of the base of a page table. This field (page table address) specifies 20 most significant bits and remaining 12 bits are all O's. This locates all page tables on 4 K boundaries. • User/Avail: Bits 9, 10, and 11 are not used by the 80386. Users are free to use them. • Accessed Bit: The 80386 automatically sets accessed bit whenever PDE is used in address translation or another page related function. It is never cleared unless you write code to do it manually.

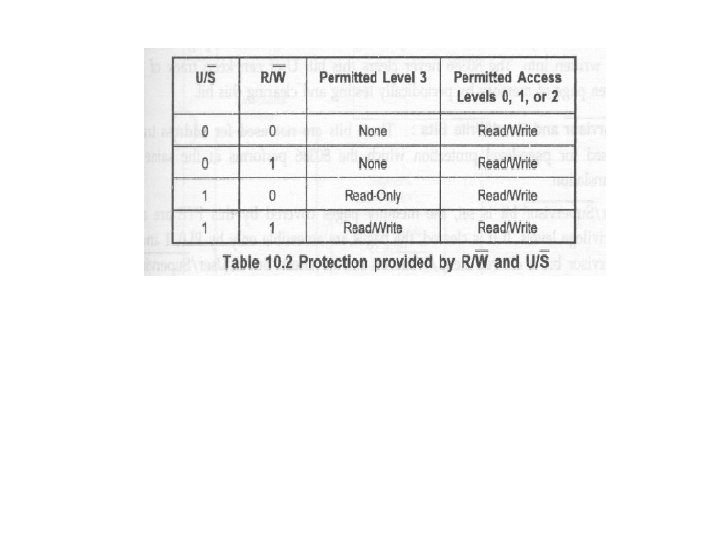

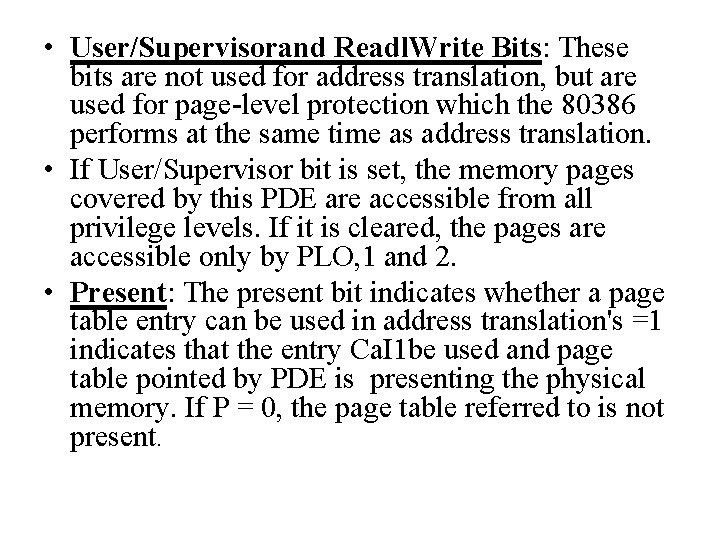

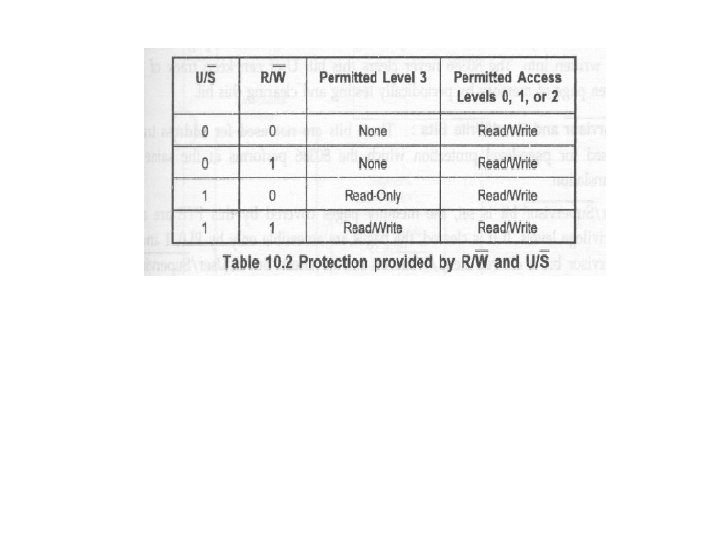

• User/Supervisorand Readl. Write Bits: These bits are not used for address translation, but are used for page-level protection which the 80386 performs at the same time as address translation. • If User/Supervisor bit is set, the memory pages covered by this PDE are accessible from all privilege levels. If it is cleared, the pages are accessible only by PLO, 1 and 2. • Present: The present bit indicates whether a page table entry can be used in address translation's =1 indicates that the entry Ca. I 1 be used and page table pointed by PDE is presenting the physical memory. If P = 0, the page table referred to is not present.

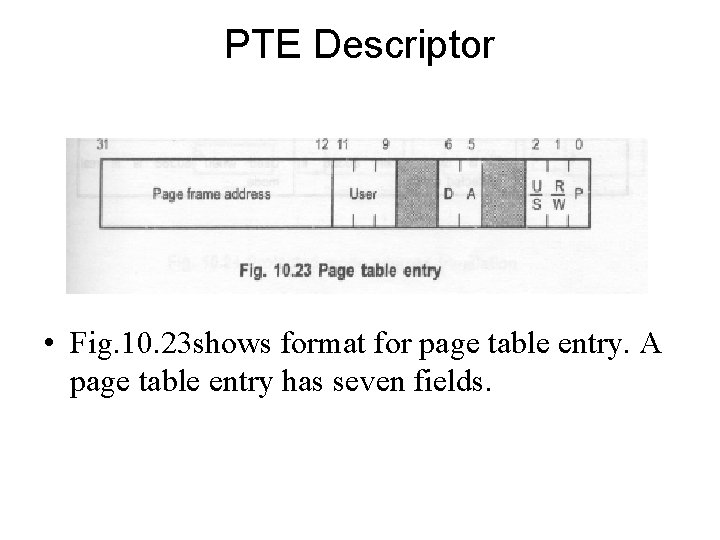

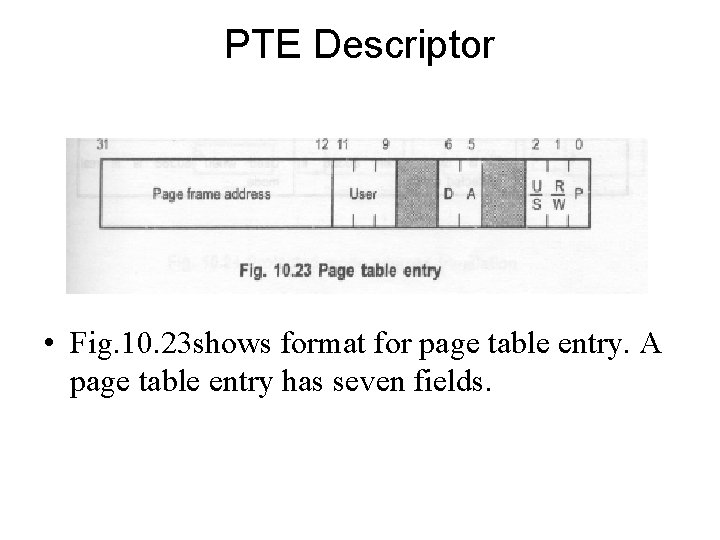

PTE Descriptor • Fig. 10. 23 shows format for page table entry. A page table entry has seven fields.

• • • • • Page Frame Address: The page frame address specifies the physical starting addressof a 4 k. B page frame or a page. This field (page frame address) specifies 20 most significant bits and remaining 12 bits are all O's. This locates all pages on 4 K boundaries. User/Avail Bits : Bits 9, 10, 11 are not used by the 80386. Users are free to use them. . 11 Logical Address [ Accessed Bit: Accessed bit is set by the 80386 whenever this PTE is used in a paging related function. The 80386 never clears this bit. User can keep track of the most often used pages of memory by periodically testing and clearing this bit in all PTEs. Dirty Bit: The dirty bit is automatically set by the 80386 whenever page frame covered by PTE is written into. The 80386 never clears this bit. User can keep track of the most often written page of memory by periodically testing and clearing this bit. 1~ [ User/Supervisor and Readl. Write Bits: These bits are not used for address translation, but are used for page-level protection which the 80386 performs at the same time as address translation.