Intel 80386 Intel 80386 32 bit Processor Can

Intel 80386

Intel 80386 � 32 bit Processor � Can � 32 work as 8086 in virtual 8086 mode bit address bus can address 4 GB � Memory � Paging � 132 divided into segments and pages first introduced in 80386 pin grid array packages � 20 Mhz and 30 Mhz

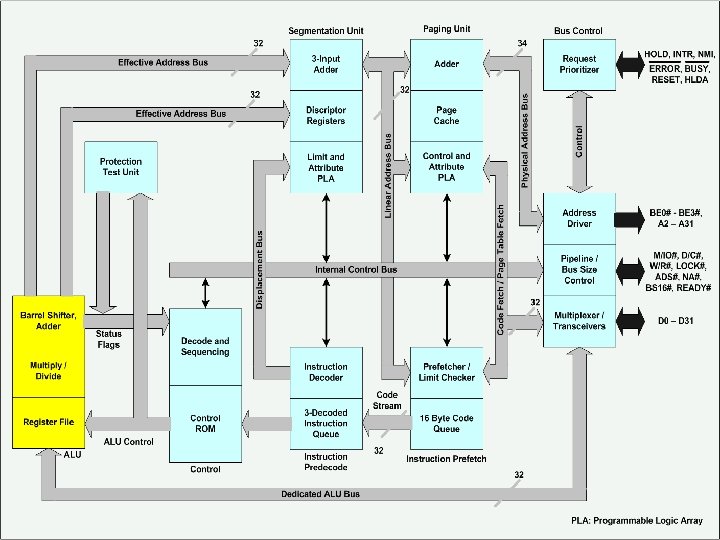

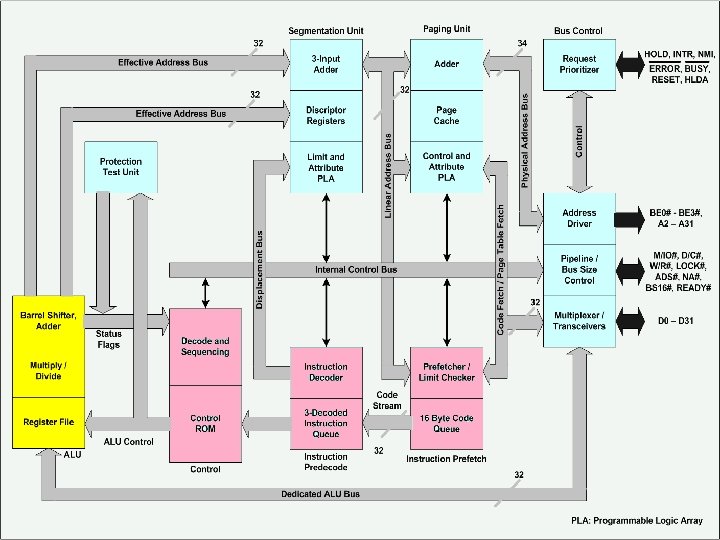

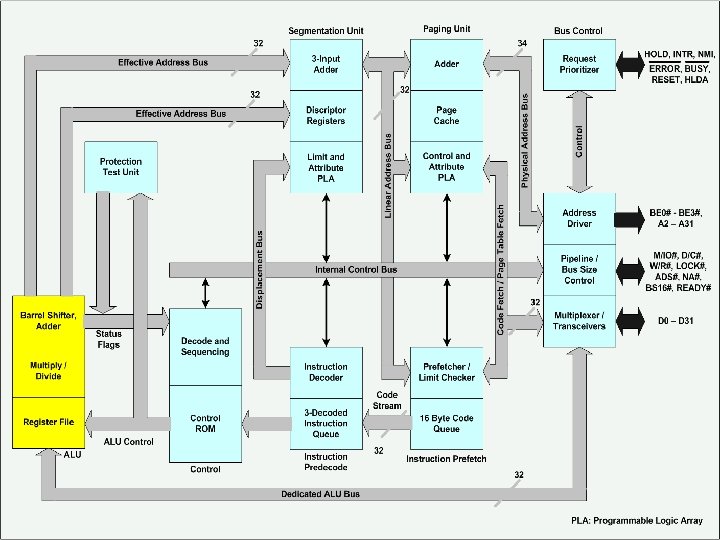

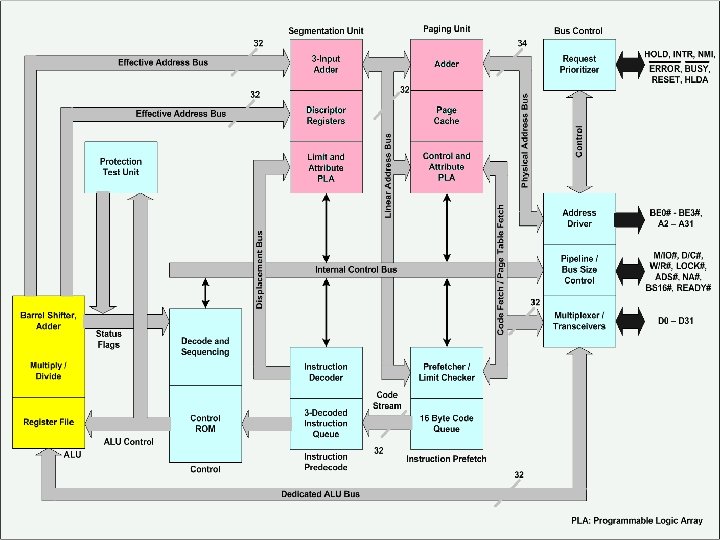

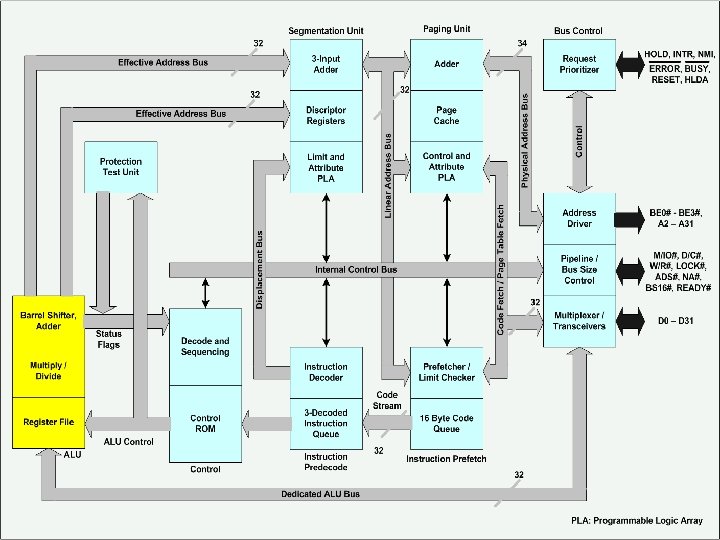

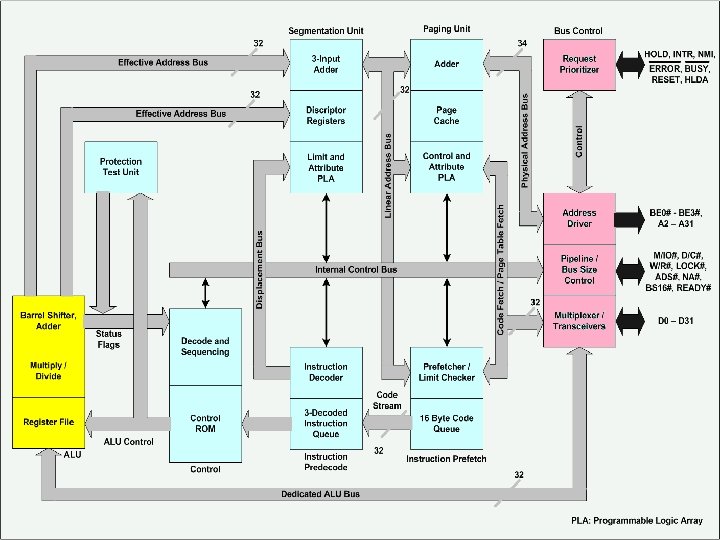

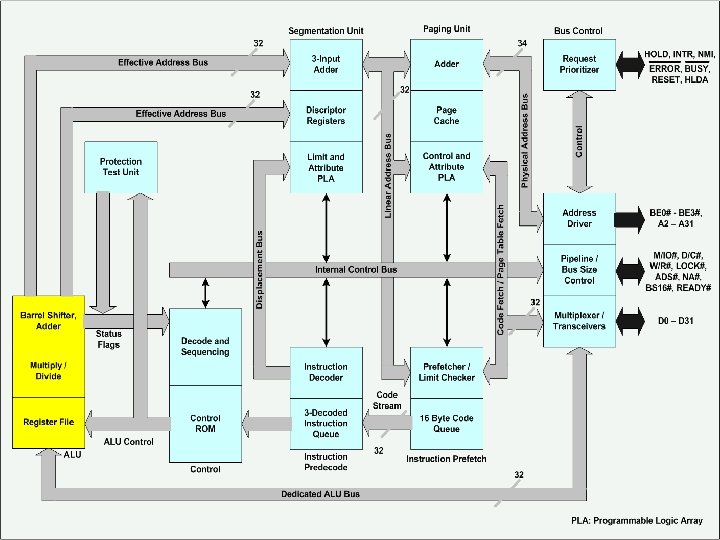

ARCHITECTURE OF 80386 It is divided into three sections v central processing unit vmemory management unit vbus interface unit. The central processing unit is divided Ø execution unit and instruction unit.

v The execution unit has eight general purpose and eight special purpose registers are used for handling data or calculating offset addresses.

v The instruction unit decodes the opcode bytes and arranges them in a 3 -instruction decoded-instruction queue

v The barrel shifter increases the speed of all shift and rotate operations. v The multiply/divide logic implements the bit-shift- rotate algorithms to complete the operations in minimum time

The memory management unit (MMU) is divided into Ø segmentation unit Ø paging unit.

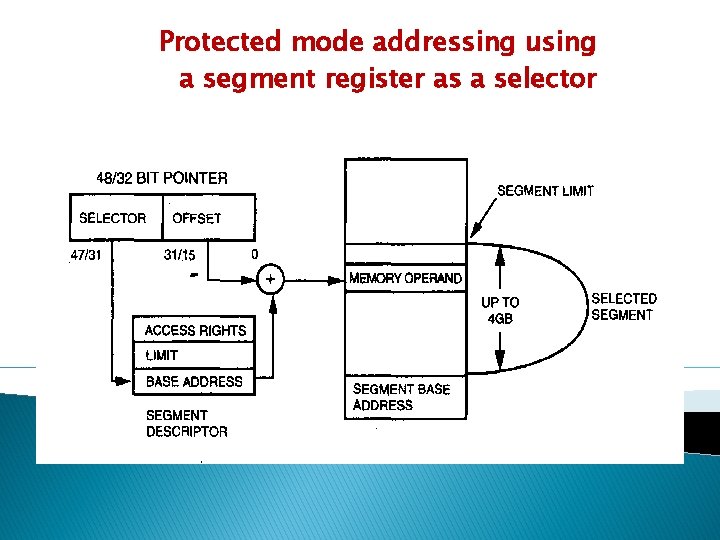

v The segmentation unit allows the use of two address components, viz. segment and offset for relocability and sharing of code and data v It allows segments of size 4 Gbytes at maximum.

v The paging unit converts linear addresses into physical addresses v. The control and attribute PLA checks the privileges at the page level. v The limit and attribute PLA checks segment limits and attributes at segment level to avoid invalid accesses to code and data in the memory segments

v The paging unit organizes the physical memory in terms of pages of 4 Kbytes size each. v The paging unit works under the control of the segmentation unit

v The bus control unit has a prioritizer to resolve the priority of the various bus requests. This controls the access of the bus. v The address driver drives the bus enable and address signals A 0 -A 31.

v The pipeline and dynamic bus sizing units handle the related control signals. v The data buffers interface the internal data bus with the system bus.

Protected mode addressing using a segment register as a selector

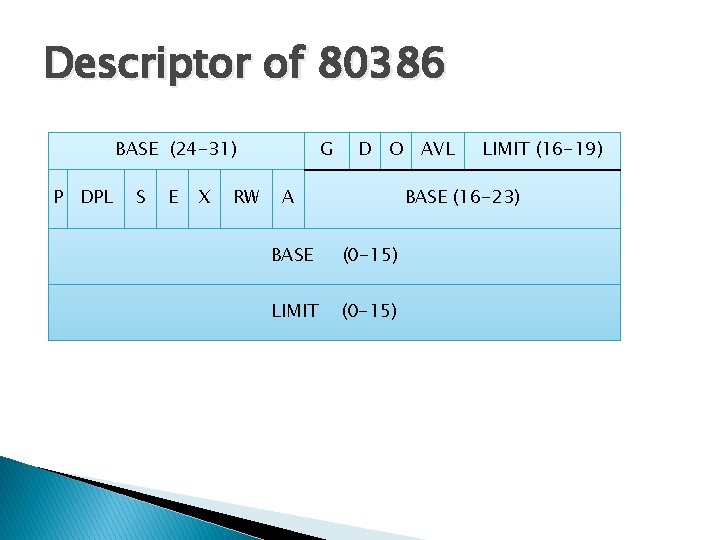

Descriptor of 80386 BASE (24 -31) P DPL S E X RW G D O AVL A LIMIT (16 -19) BASE (16 -23) BASE (0 -15) LIMIT (0 -15)

Thank you Visit: www. tijubaby. weebly. com For all these ppt’s and notes

- Slides: 23