80386 DX Features of 80386 DX It supports

- Slides: 42

80386 DX

Features of 80386 DX • It supports 8/16/32 bit data operands • It has 32 -bit internal registers • It supports 32 -bit data bus and 32 -bit non -multiplexed address bus • It supports – Physical Address of 4 GB – Virtual Address of 64 TB – Maximum Segment size of 4 GB

Features of 80386 DX • It operates in 3 different modes – Real – Protected – Virtual 8086 • MMU provides virtual memory, paging and 4 levels of protection • Clock Frequency : 20, 25 and 33 MHz • It has 132 pin package

Architecture of 80386 UQ: Draw the block diagram of the 80386 DX Processor and explain each block in brief 4

Architecture of 80386 Three Sections: Bus Interface units Central Processing Unit Memory Management Unit 5

Architecture of 80386 • The internal architecture of 80386 is divided into three sections: 1. Central Processing Unit 2. Memory Management Unit 3. Bus Interface unit 6

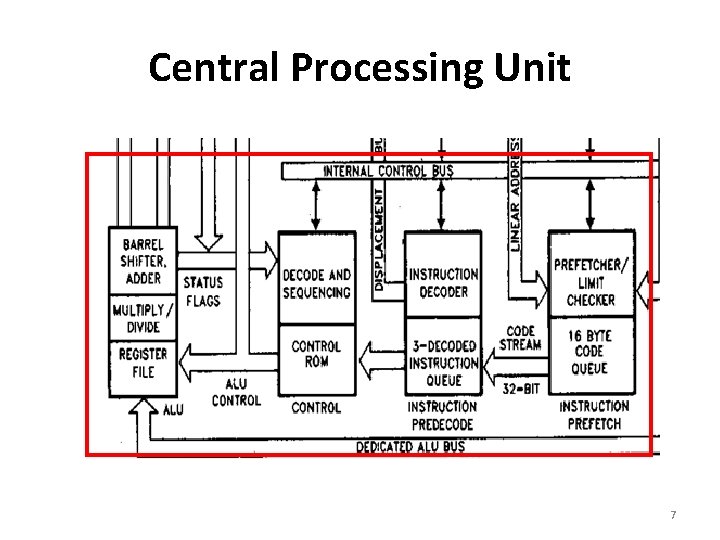

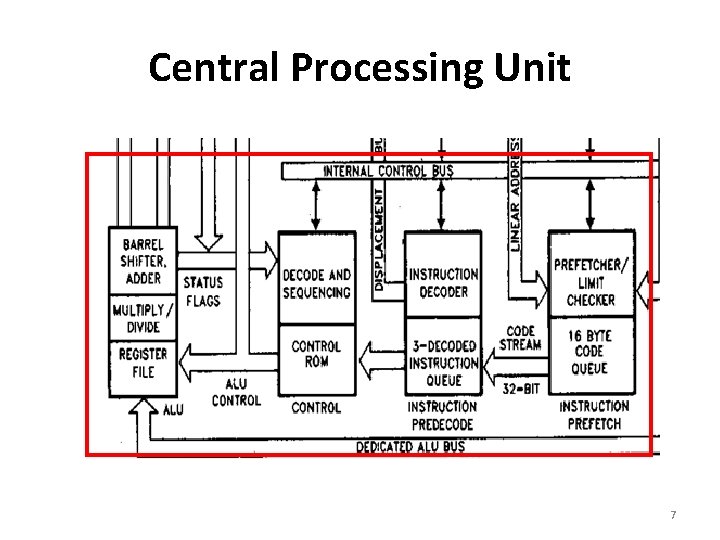

Central Processing Unit 7

Central Processing Unit • The CPU is further divided into: – Instruction Unit – Execution Unit • Instruction Unit: – It decodes the opcode bytes received from the 16 byte instruction queue and arranges them into a 3 -decoded instruction queue. – After decoding it is passed to control section for deriving necessary control signals 8

Central Processing Unit • Execution Unit: – It has 8 general purpose and 8 special purpose registers which either handles data or offset addresses. – The 64 -bit barrel shifter increases the speed of all shift, rotate, multiply and divide operations – The multiply/divide logic implements the bit-shiftrotate algorithms to complete the operations in minimum time(Even 32 bit multiplication is done in 1µs) 9

Central Processing Unit • Element of the EU – Arithmetic/logic unit (ALU) • Performs the operation identified by ADD, SUB, AND, etc. – Flags register • Holds status and control information – General-purpose registers • Holds address or data information – Control ROM • Contains microcode sequences that define operations performed by machine instructions – Special multiply, shift, and barrel shift hardware • Accelerate multiply, divide, and rotate operations 10

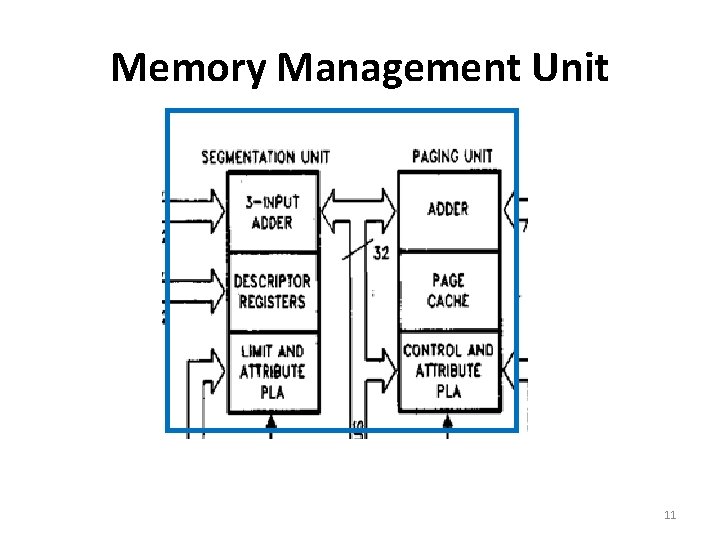

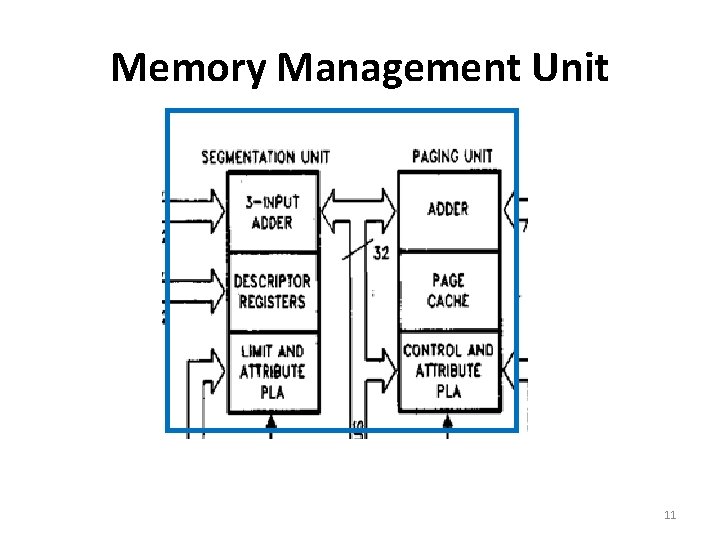

Memory Management Unit 11

Memory Management Unit • MMU consists of a segmentation unit and paging unit • Segmentation Unit: – It allows the use of two address components segment and offset – for relocability and sharing of code and data – It allows a maximum segment size of 4 GB – It provides a 4 -level protection mechanism for protecting and isolating system’s code and data from those of application program 12

Memory Management Unit – The limit and attribute PLA checks segment limits and attributes at segment level to avoid invalid accesses to code and data in memory segment. • Paging Unit – It organizes physical memory in terms of pages of 4 KB size – It works under the control of segmentation unit – It converts linear addresses into physical addresses – The control and attribute PLA checks privileges at page level. 13

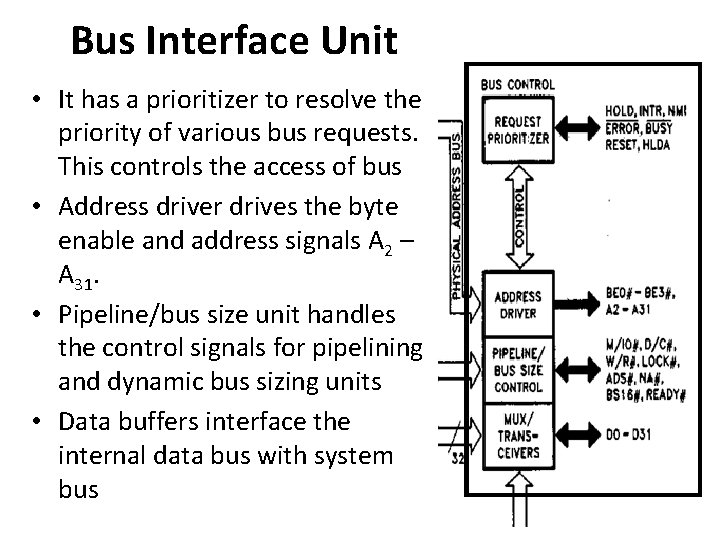

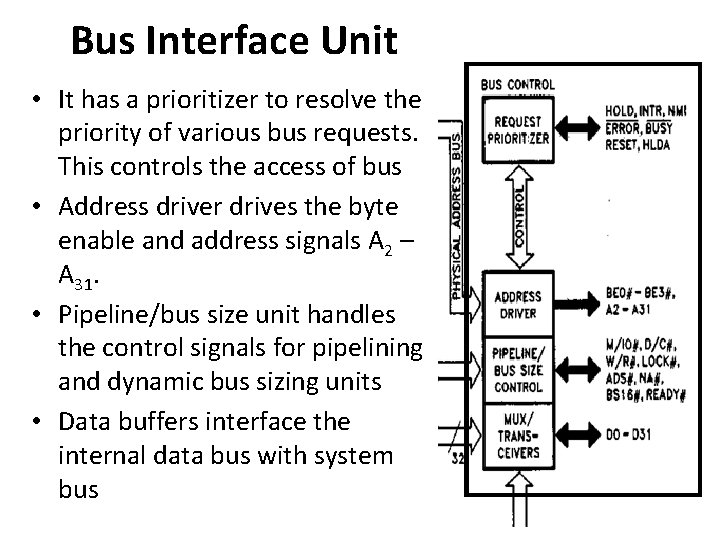

Bus Interface Unit • It has a prioritizer to resolve the priority of various bus requests. This controls the access of bus • Address driver drives the byte enable and address signals A 2 – A 31. • Pipeline/bus size unit handles the control signals for pipelining and dynamic bus sizing units • Data buffers interface the internal data bus with system bus 14

Signal Interface of 80386 DX 15

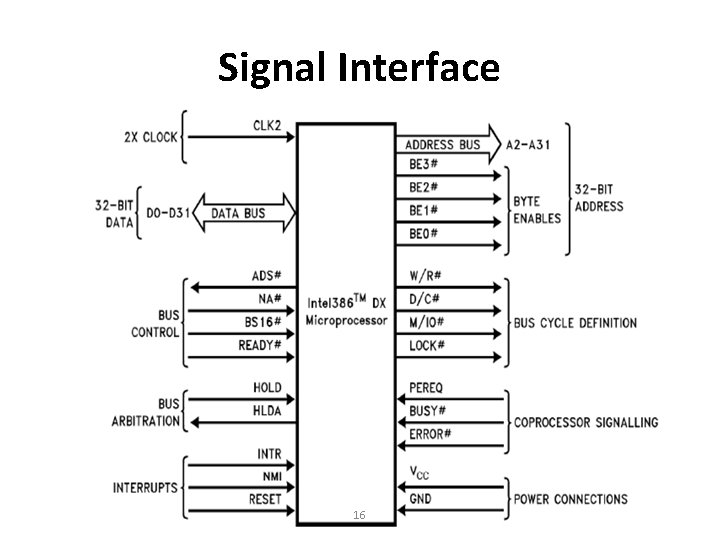

Signal Interface 16

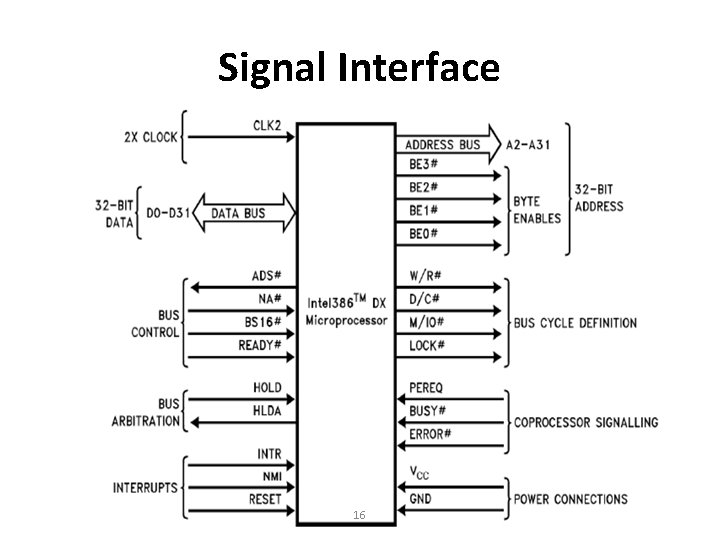

Signal Interface • • Signals are arranged by functional groups. The # symbol indicates active low signal. When no # is present, the signal is active high. Example: M/IO# - High voltage indicates memory selected - Low voltage indicates I/O selected 17

Signal Interface • Clock (CLK 2): – It is divided by two internally to generate the internal processor clock. – The clock can be synchronized to a known phase. • Data Bus (D 0 through D 31): – It has three-state bidirectional signals. – It can transfer data on 32 - and 16 -bit buses using a data bus sizing feature. 18

Signal Interface • Address Bus (A 2 through A 31) • Provides three-state outputs • It provides physical memory addresses or I/O port addresses. • It can access 4 GB of physical memory from 0000 H to FFFFH • Only higher 30 are released by MP(Microprocessor) • A 1 and A 0 are used internally by MP to produce the four byte enable signals(BE 3# -- BE 0#) 19

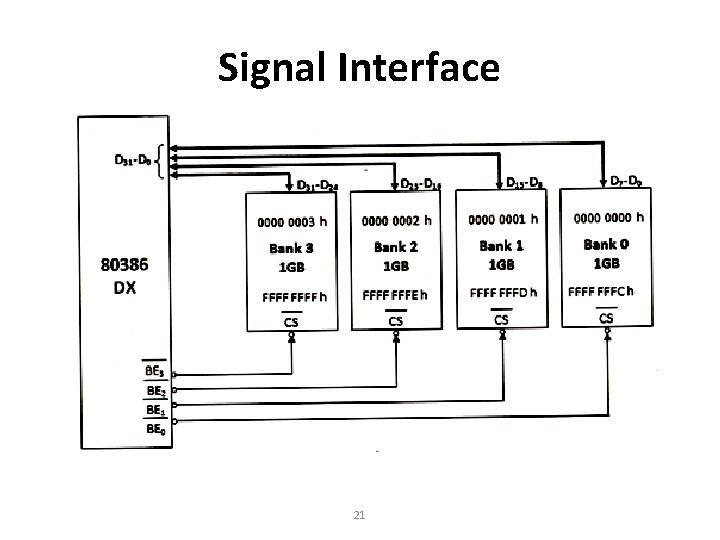

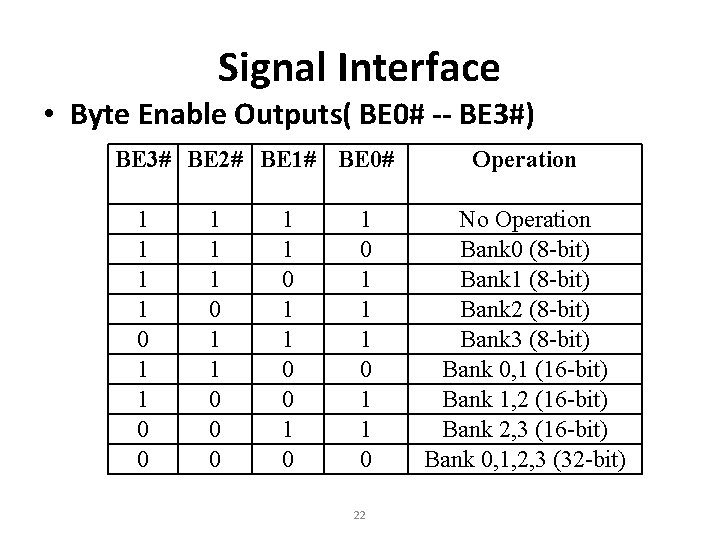

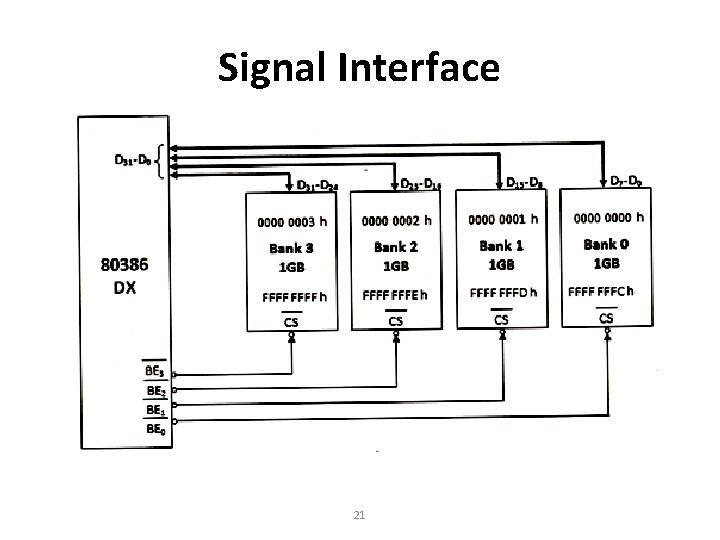

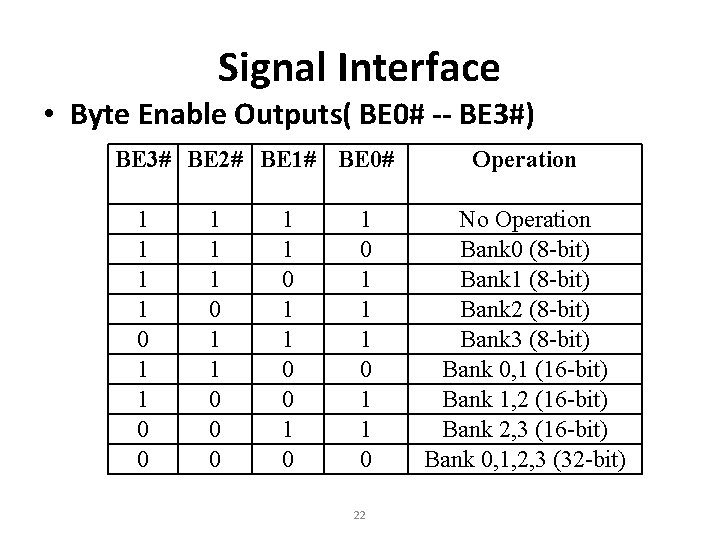

Signal Interface • Byte Enable Outputs( BE 0# -- BE 3#) – enable 4 memory banks – indicates which bytes of the 32 -bit data bus are involved with the current transfer. – BE 0# applies to D 0 -D 7 – BE 1# applies to D 8 -D 15 – BE 2# applies to D 16 -D 23 – BE 3# applies to D 24 -D 31 – No. of Byte Enables asserted indicates physical size of operand being transferred (1, 2, 3, or 4 bytes). 20

Signal Interface 21

Signal Interface • Byte Enable Outputs( BE 0# -- BE 3#) BE 3# BE 2# BE 1# BE 0# 1 1 0 0 1 1 1 0 0 0 1 1 0 0 1 0 1 1 1 0 22 Operation No Operation Bank 0 (8 -bit) Bank 1 (8 -bit) Bank 2 (8 -bit) Bank 3 (8 -bit) Bank 0, 1 (16 -bit) Bank 1, 2 (16 -bit) Bank 2, 3 (16 -bit) Bank 0, 1, 2, 3 (32 -bit)

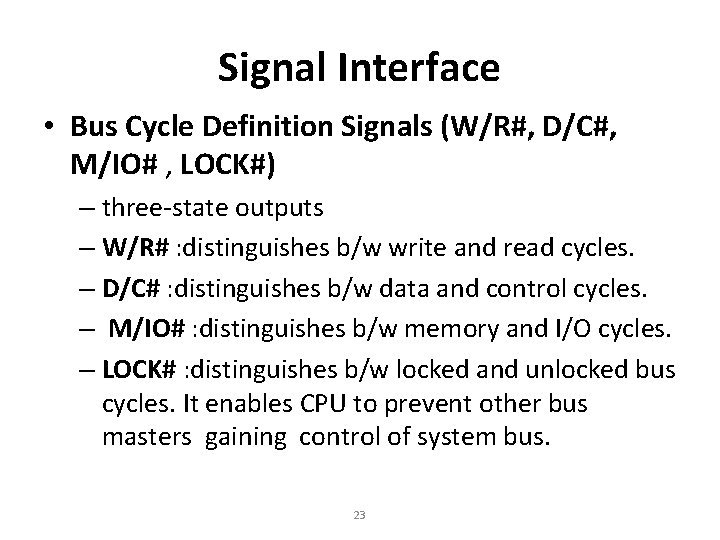

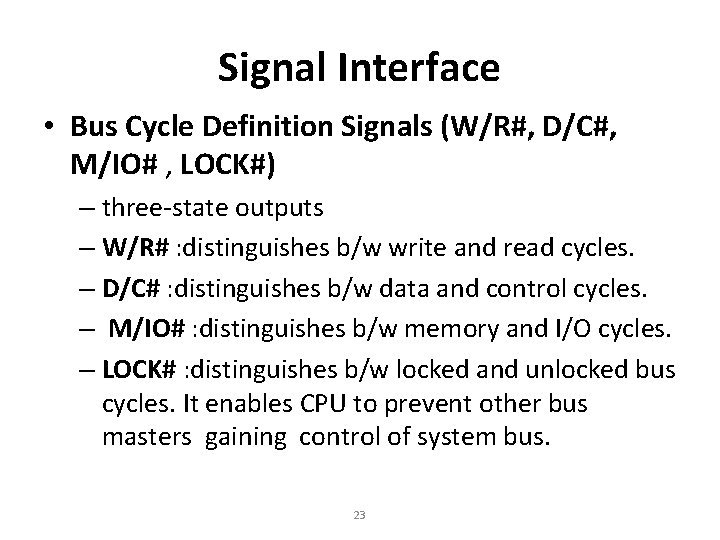

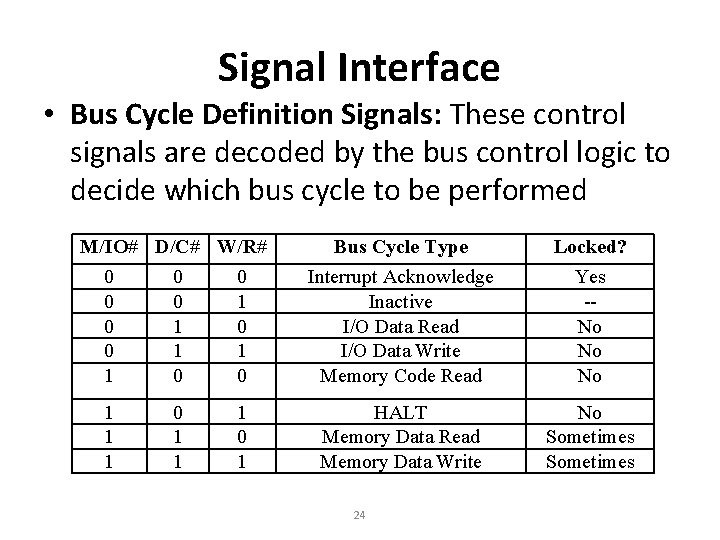

Signal Interface • Bus Cycle Definition Signals (W/R#, D/C#, M/IO# , LOCK#) – three-state outputs – W/R# : distinguishes b/w write and read cycles. – D/C# : distinguishes b/w data and control cycles. – M/IO# : distinguishes b/w memory and I/O cycles. – LOCK# : distinguishes b/w locked and unlocked bus cycles. It enables CPU to prevent other bus masters gaining control of system bus. 23

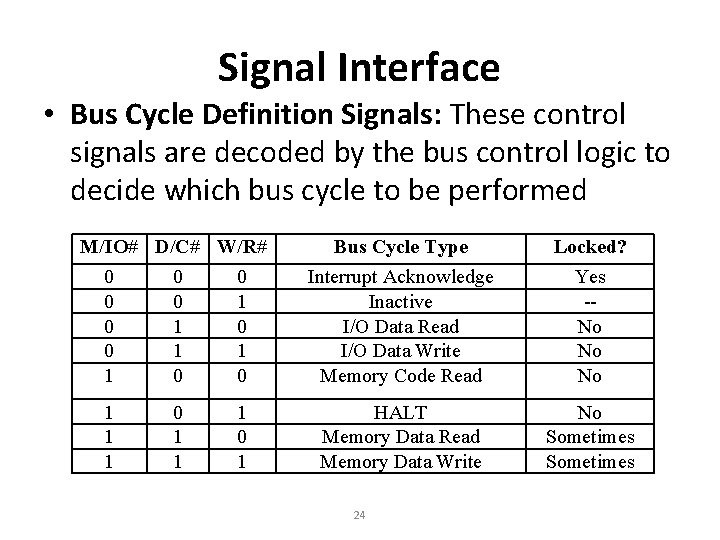

Signal Interface • Bus Cycle Definition Signals: These control signals are decoded by the bus control logic to decide which bus cycle to be performed M/IO# D/C# W/R# 0 0 0 1 1 1 0 1 Bus Cycle Type Interrupt Acknowledge Inactive I/O Data Read I/O Data Write Memory Code Read Locked? Yes -No No No HALT Memory Data Read Memory Data Write No Sometimes 24

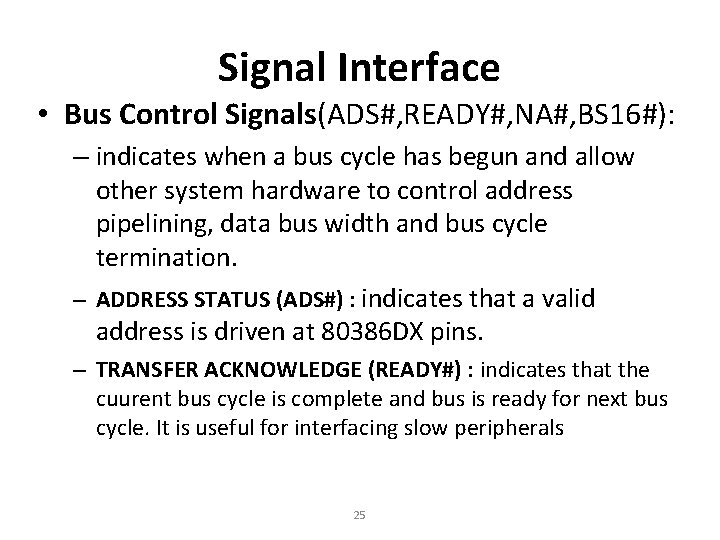

Signal Interface • Bus Control Signals(ADS#, READY#, NA#, BS 16#): – indicates when a bus cycle has begun and allow other system hardware to control address pipelining, data bus width and bus cycle termination. – ADDRESS STATUS (ADS#) : indicates that a valid address is driven at 80386 DX pins. – TRANSFER ACKNOWLEDGE (READY#) : indicates that the cuurent bus cycle is complete and bus is ready for next bus cycle. It is useful for interfacing slow peripherals 25

Signal Interface – NEXT ADDRESS REQUEST (NA#) : This is used to enable address pipelining. It indicates that the system is prepared to accept the next address even if the end of the current cycle is not being acknowledged on READY#. – BUS SIZE 16 (BS 16#) : This input constrains current bus cycle to use only D 0 -D 15 of data bus. 26

Bus Arbitration Signals (HOLD, HLDA) • BUS HOLD REQUEST (HOLD): – This input indicates some other device requires bus mastership. – HOLD must remain asserted as long as any other device is a local bus master. – HOLD is not recognized while RESET is asserted. (i. e. RESET has priority over HOLD) – HOLD is level-sensitive. 27

Bus Arbitration Signals (HOLD, HLDA) • BUS HOLD ACKNOWLEDGE (HLDA): – This output indicates 80386 has given control of its local bus in response to HOLD asserted and it is in Bus Hold Acknowledge state. – This state offers near-complete signal isolation – The other output signals (D 0 -D 31, BE 0#-BE 3#, A 2 A 31, W/R#, D/C#, M/IO#, LOCK# and ADS#) are in a high-impedance state so the requesting bus master may control them. 28

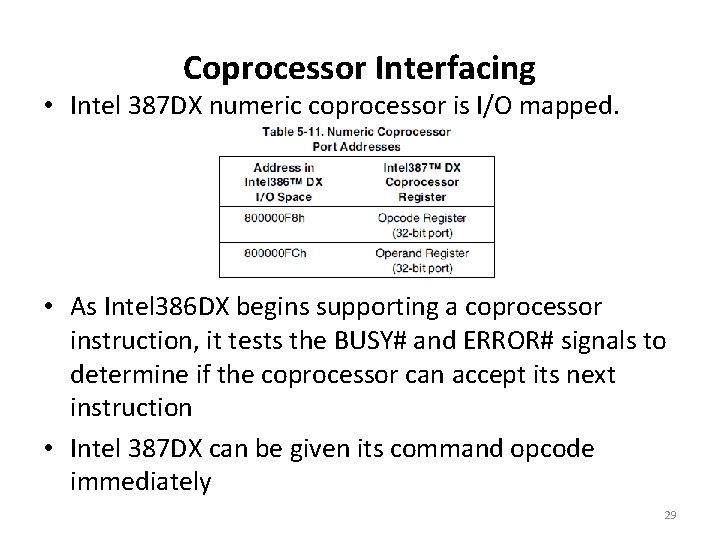

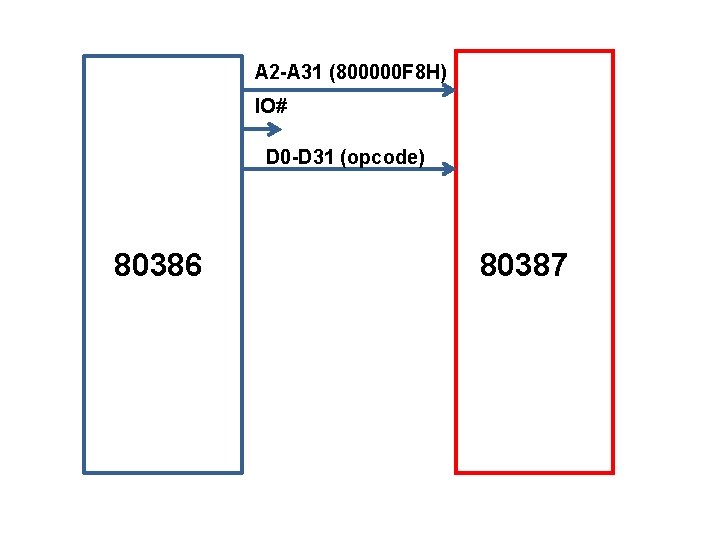

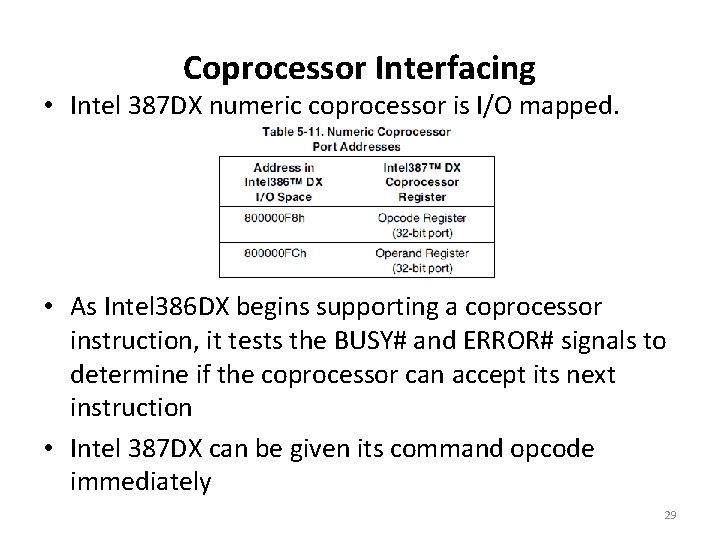

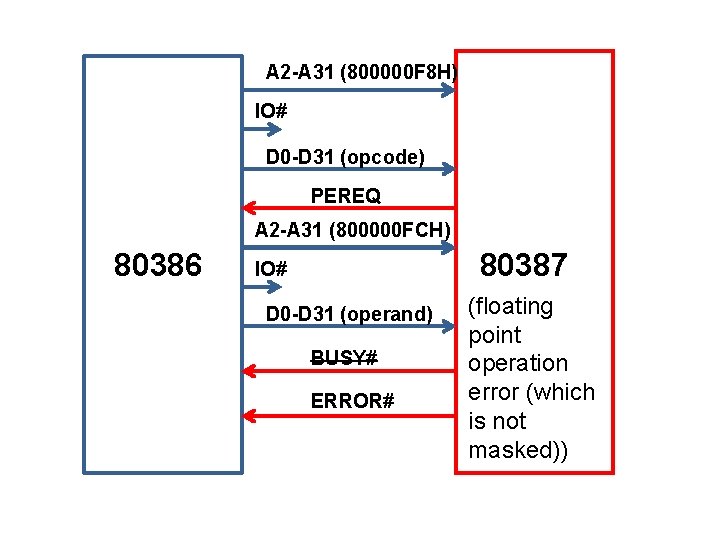

Coprocessor Interfacing • Intel 387 DX numeric coprocessor is I/O mapped. • As Intel 386 DX begins supporting a coprocessor instruction, it tests the BUSY# and ERROR# signals to determine if the coprocessor can accept its next instruction • Intel 387 DX can be given its command opcode immediately 29

Coprocessor Interface Signals (PEREQ, BUSY#, ERROR#) • COPROCESSOR REQUEST (PEREQ) : – PEREQ stands for Processor Extension Request. – This input signal indicates a coprocessor request for a data operand to be transferred to/from memory by the Intel 386 DX. – PEREQ is level-sensitive 30

Coprocessor Interface Signals (PEREQ, BUSY#, ERROR#) • COPROCESSOR BUSY (BUSY#) : – This input indicates that coprocessor is still executing an instruction and is not yet able to accept another. – BUSY# is level-sensitive 31

Coprocessor Interface Signals (PEREQ, BUSY#, ERROR#) • COPROCESSOR ERROR (ERROR#) : • This input signal indicates that the previous coprocessor instruction generated a coprocessor error of a type not masked by coprocessor's control register. • ERROR# is level-sensitive 32

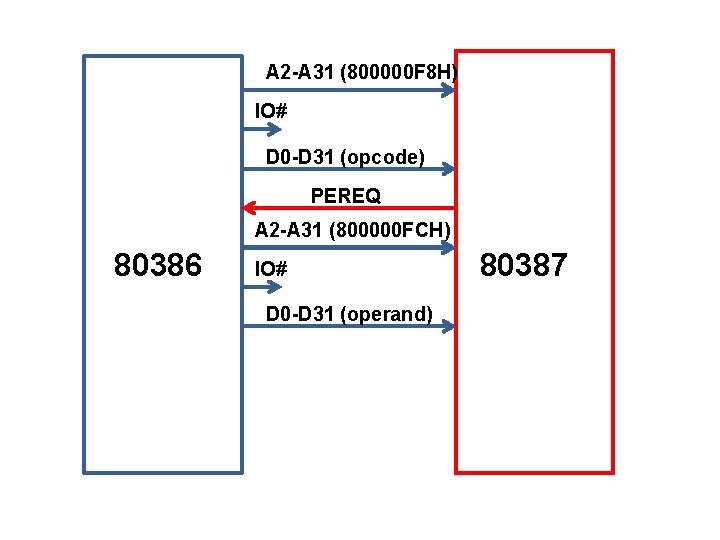

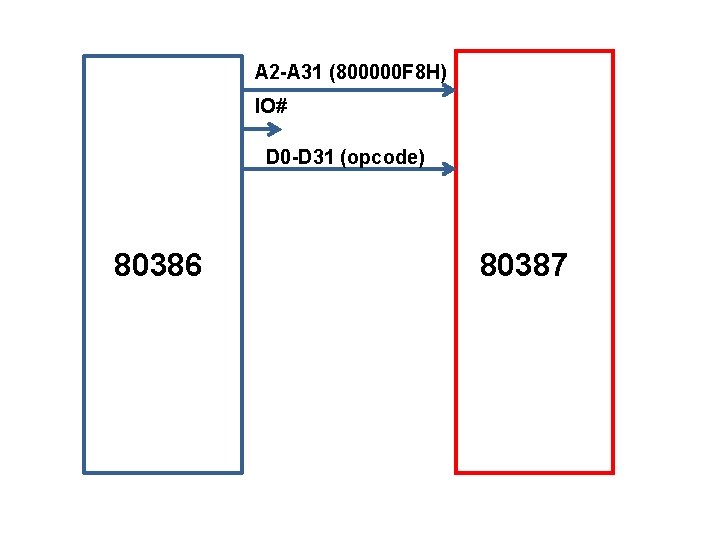

A 2 -A 31 (800000 F 8 H) IO# D 0 -D 31 (opcode) 80386 80387

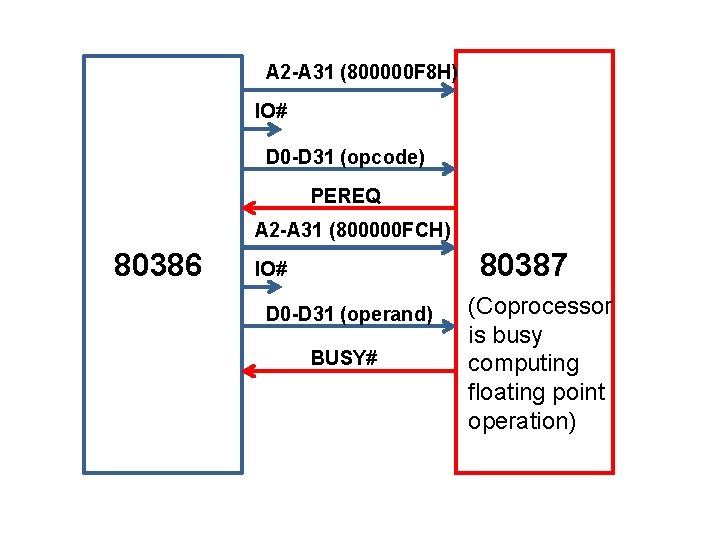

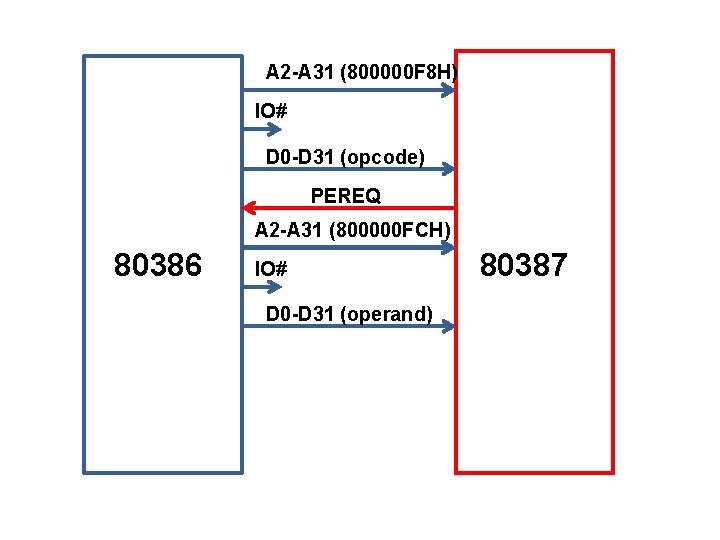

A 2 -A 31 (800000 F 8 H) IO# D 0 -D 31 (opcode) PEREQ A 2 -A 31 (800000 FCH) 80386 IO# D 0 -D 31 (operand) 80387

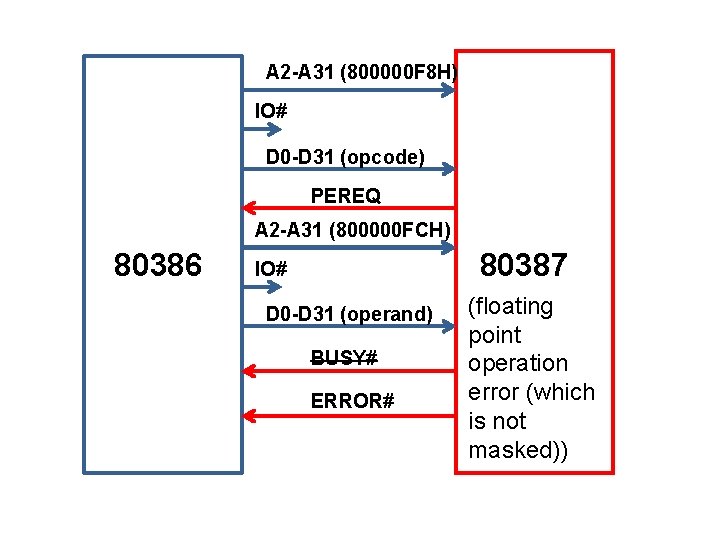

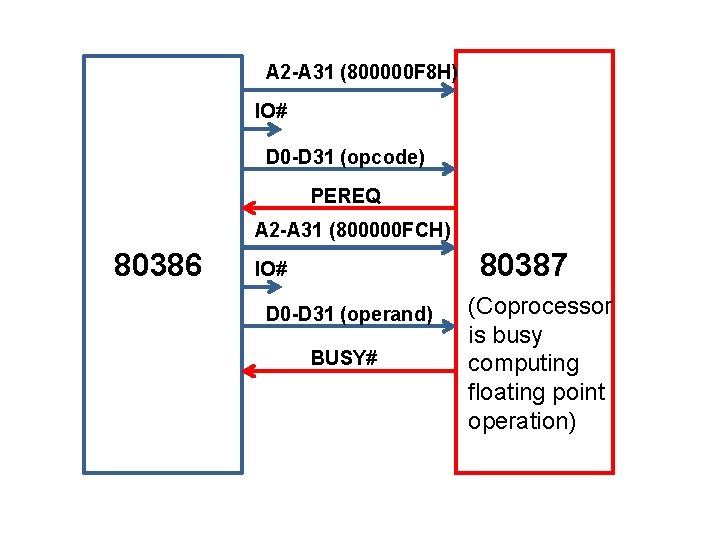

A 2 -A 31 (800000 F 8 H) IO# D 0 -D 31 (opcode) PEREQ A 2 -A 31 (800000 FCH) 80386 80387 IO# D 0 -D 31 (operand) BUSY# (Coprocessor is busy computing floating point operation)

A 2 -A 31 (800000 F 8 H) IO# D 0 -D 31 (opcode) PEREQ A 2 -A 31 (800000 FCH) 80386 80387 IO# D 0 -D 31 (operand) BUSY# ERROR# (floating point operation error (which is not masked))

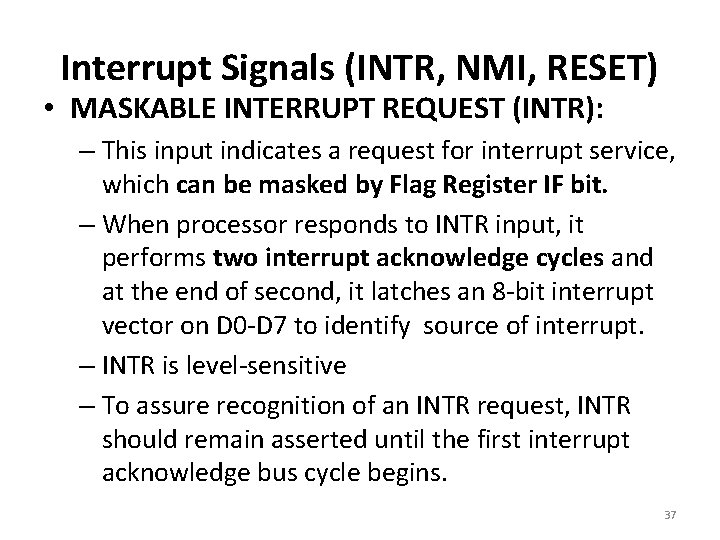

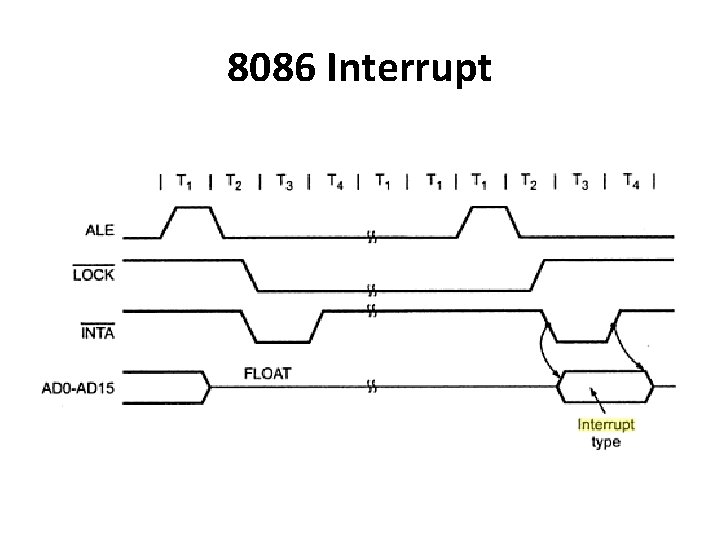

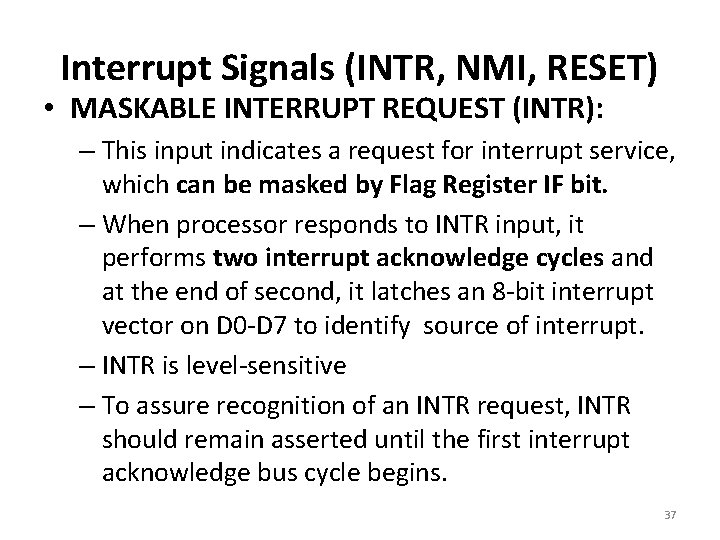

Interrupt Signals (INTR, NMI, RESET) • MASKABLE INTERRUPT REQUEST (INTR): – This input indicates a request for interrupt service, which can be masked by Flag Register IF bit. – When processor responds to INTR input, it performs two interrupt acknowledge cycles and at the end of second, it latches an 8 -bit interrupt vector on D 0 -D 7 to identify source of interrupt. – INTR is level-sensitive – To assure recognition of an INTR request, INTR should remain asserted until the first interrupt acknowledge bus cycle begins. 37

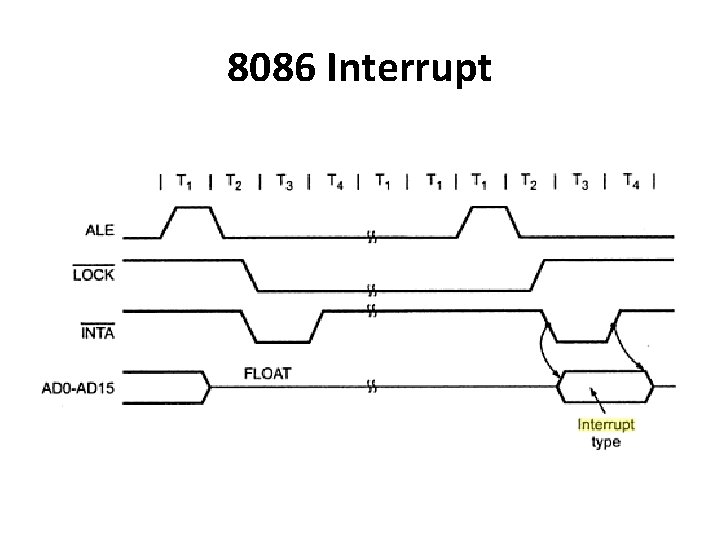

8086 Interrupt

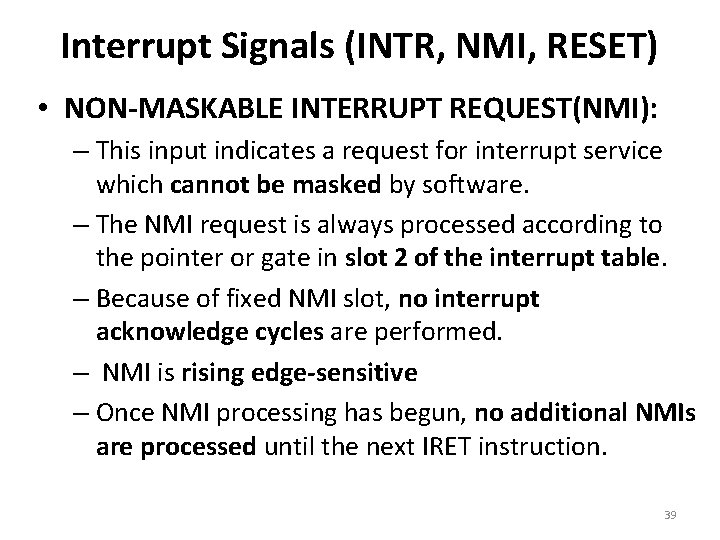

Interrupt Signals (INTR, NMI, RESET) • NON-MASKABLE INTERRUPT REQUEST(NMI): – This input indicates a request for interrupt service which cannot be masked by software. – The NMI request is always processed according to the pointer or gate in slot 2 of the interrupt table. – Because of fixed NMI slot, no interrupt acknowledge cycles are performed. – NMI is rising edge-sensitive – Once NMI processing has begun, no additional NMIs are processed until the next IRET instruction. 39

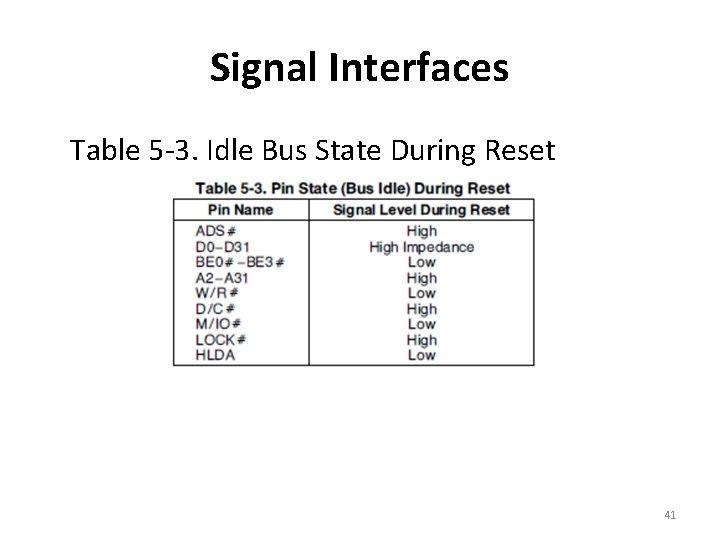

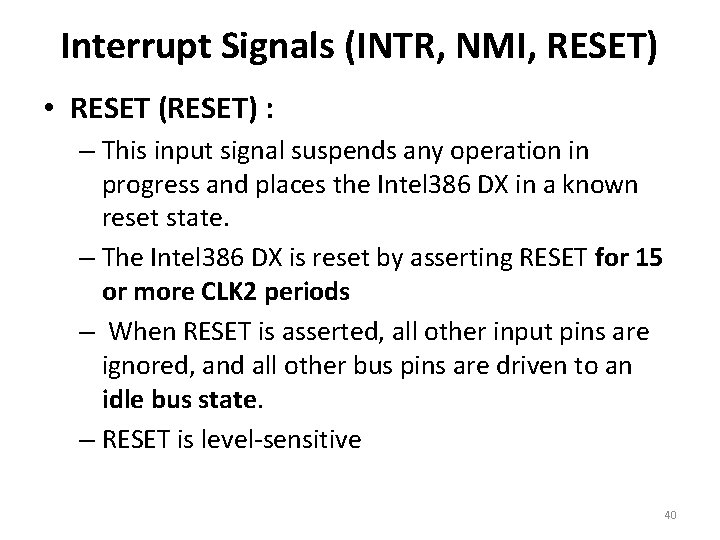

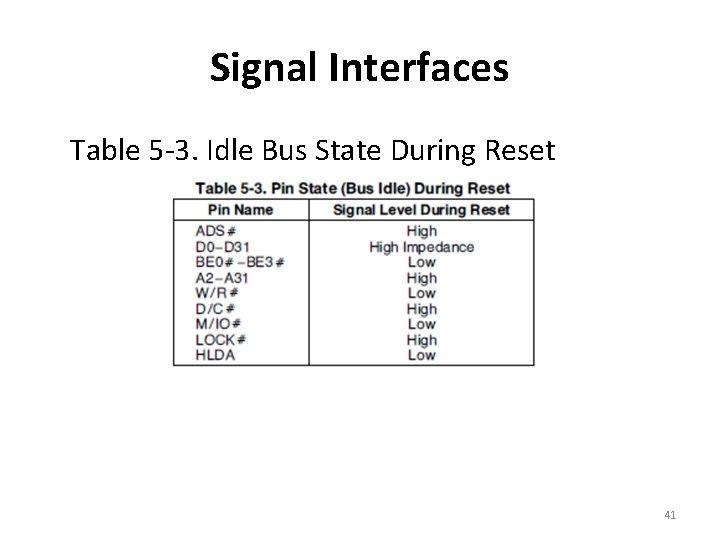

Interrupt Signals (INTR, NMI, RESET) • RESET (RESET) : – This input signal suspends any operation in progress and places the Intel 386 DX in a known reset state. – The Intel 386 DX is reset by asserting RESET for 15 or more CLK 2 periods – When RESET is asserted, all other input pins are ignored, and all other bus pins are driven to an idle bus state. – RESET is level-sensitive 40

Signal Interfaces Table 5 -3. Idle Bus State During Reset 41

Signal Interfaces • Vcc: These are system power supply lines • GND: These are return lines for the power supply 42