Addressing Modes n the addressing mode defines how

- Slides: 9

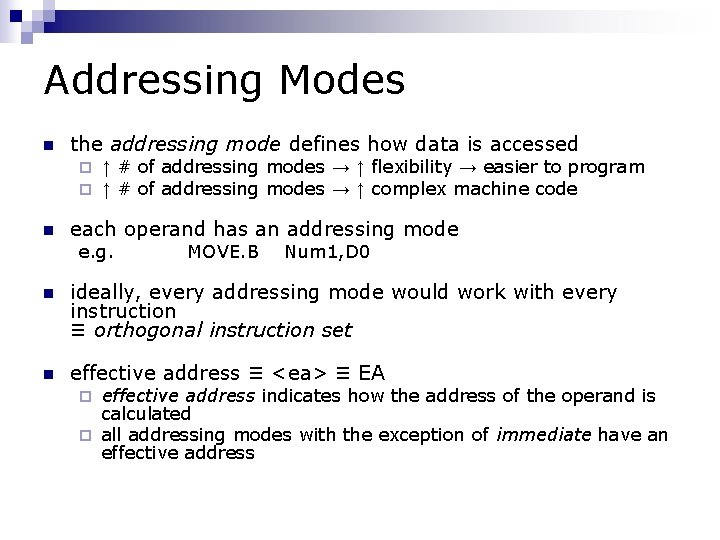

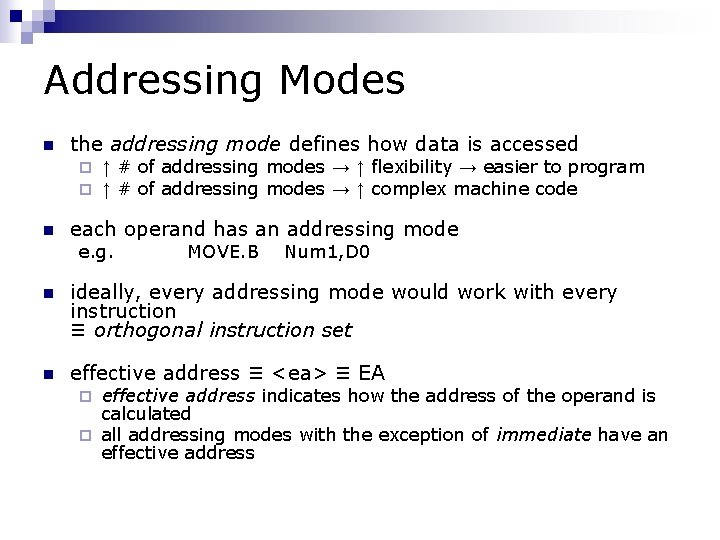

Addressing Modes n the addressing mode defines how data is accessed ¨ ¨ n ↑ # of addressing modes → ↑ flexibility → easier to program ↑ # of addressing modes → ↑ complex machine code each operand has an addressing mode e. g. MOVE. B Num 1, D 0 n ideally, every addressing mode would work with every instruction ≡ orthogonal instruction set n effective address ≡ <ea> ≡ EA effective address indicates how the address of the operand is calculated ¨ all addressing modes with the exception of immediate have an effective address ¨

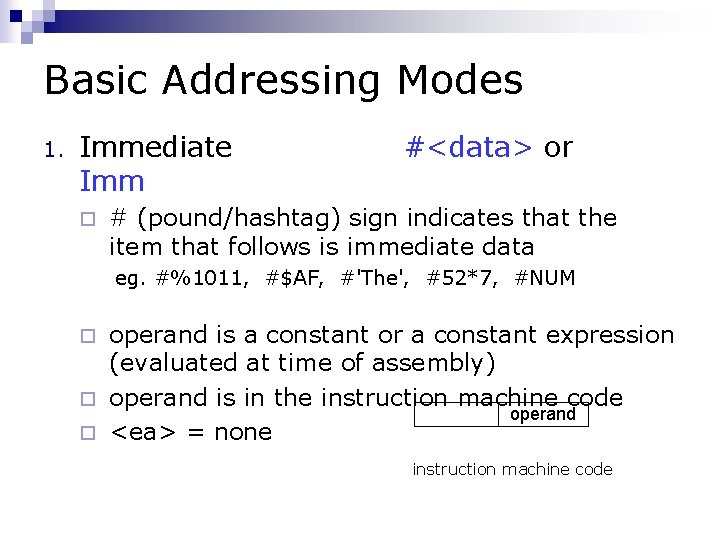

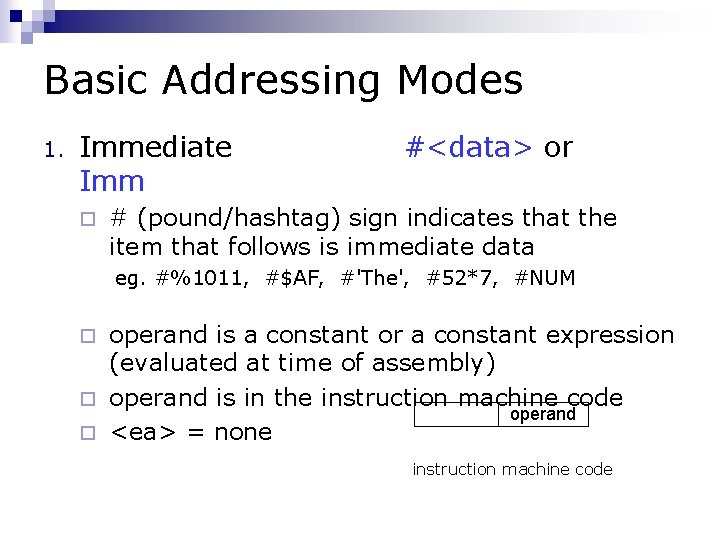

Basic Addressing Modes 1. Immediate Imm ¨ #<data> or # (pound/hashtag) sign indicates that the item that follows is immediate data eg. #%1011, #$AF, #'The', #52*7, #NUM operand is a constant or a constant expression (evaluated at time of assembly) ¨ operand is in the instruction machine code operand ¨ <ea> = none ¨ instruction machine code

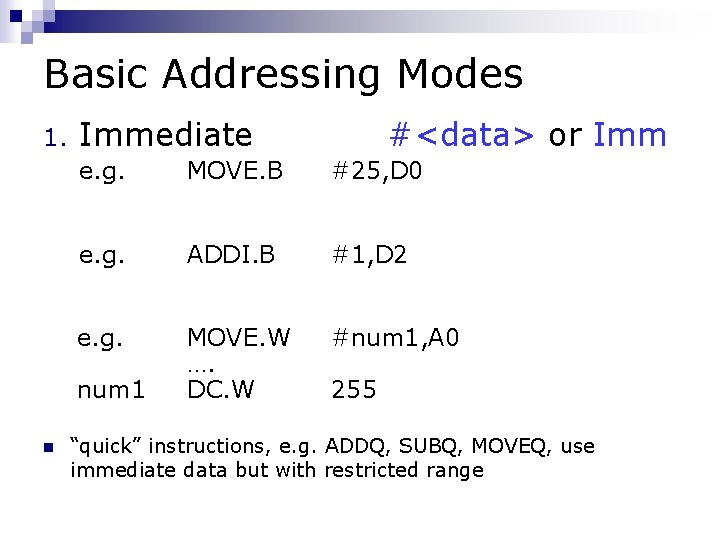

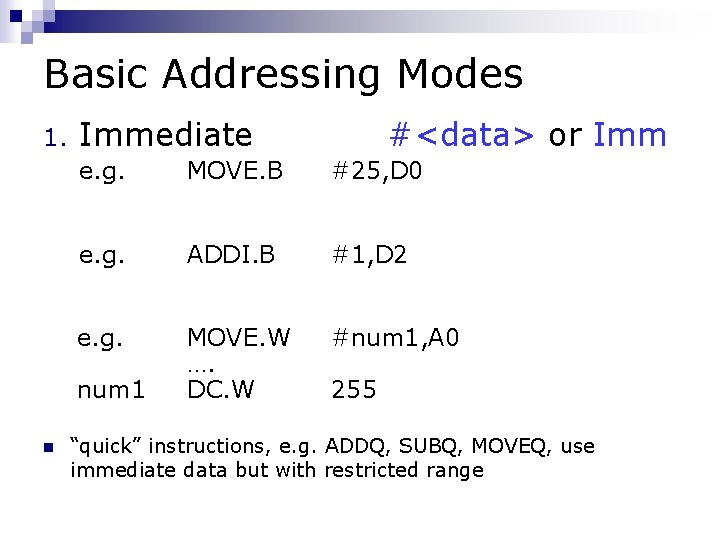

Basic Addressing Modes 1. Immediate e. g. MOVE. B #25, D 0 e. g. ADDI. B #1, D 2 e. g. MOVE. W …. DC. W #num 1, A 0 num 1 n #<data> or Imm 255 “quick” instructions, e. g. ADDQ, SUBQ, MOVEQ, use immediate data but with restricted range

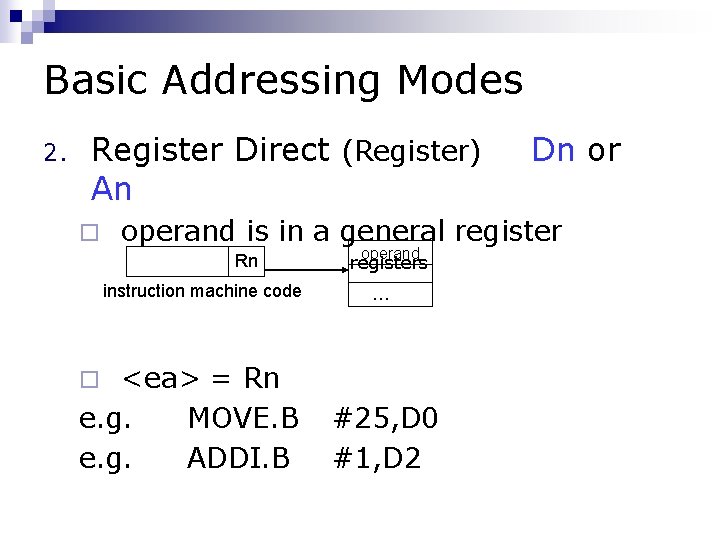

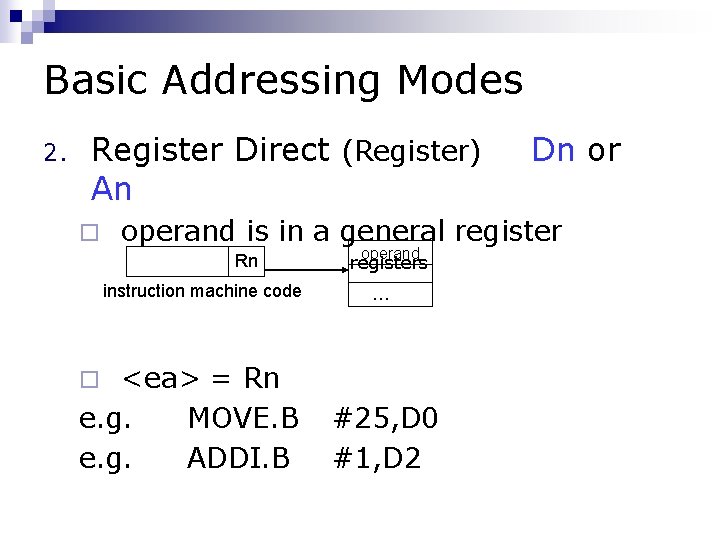

Basic Addressing Modes 2. Register Direct (Register) An ¨ Dn or operand is in a general register Rn instruction machine code <ea> = Rn e. g. MOVE. B e. g. ADDI. B operand registers … ¨ #25, D 0 #1, D 2

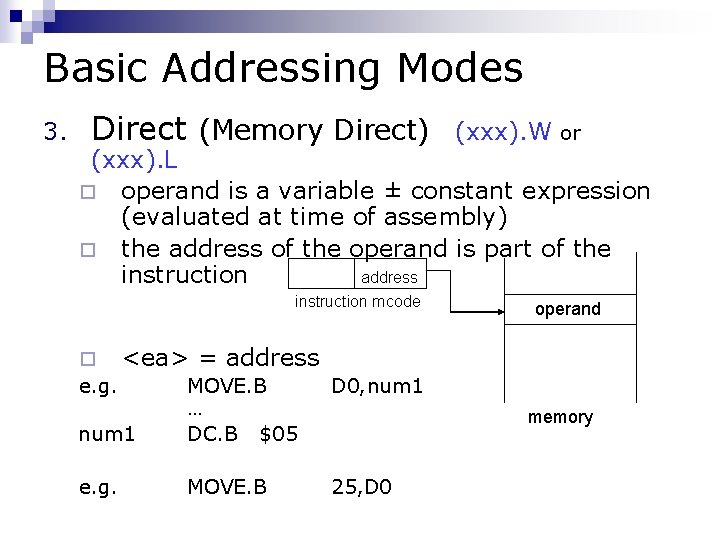

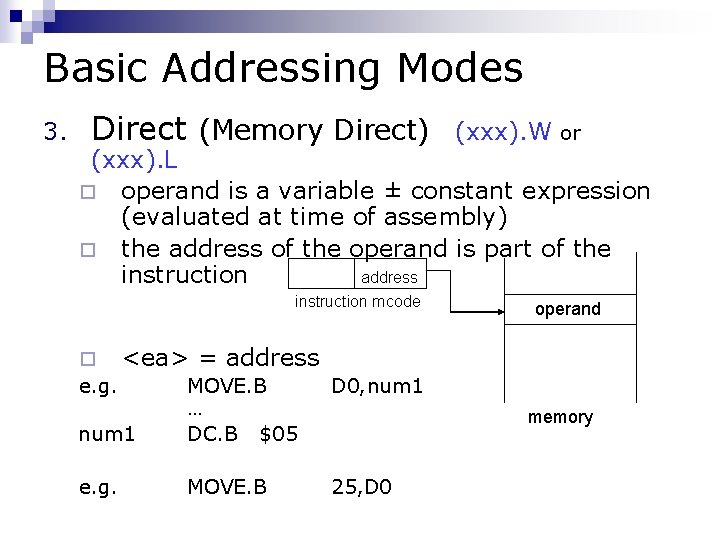

Basic Addressing Modes 3. Direct (Memory Direct) (xxx). W or (xxx). L ¨ operand is a variable ± constant expression (evaluated at time of assembly) ¨ the address of the operand is part of the instruction address instruction mcode ¨ <ea> = address e. g. MOVE. B D 0, num 1 … num 1 DC. B $05 e. g. MOVE. B 25, D 0 operand memory

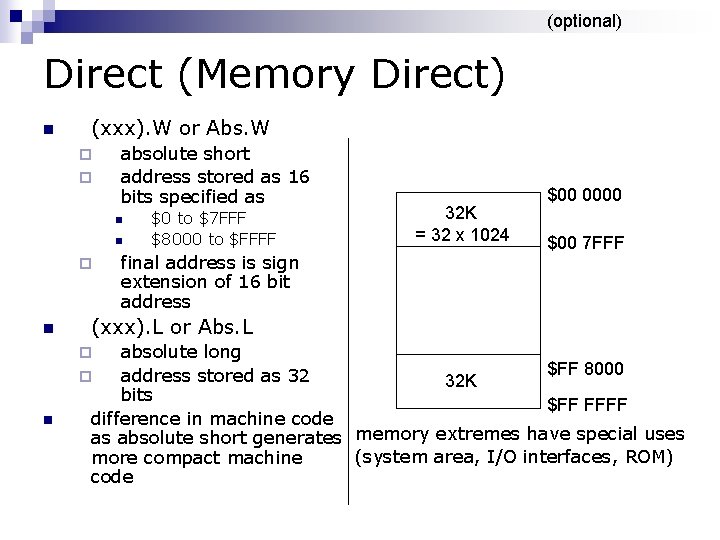

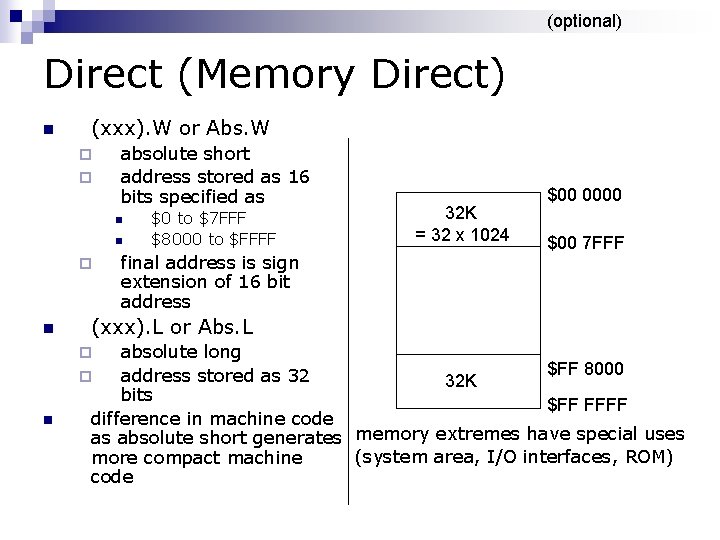

(optional) Direct (Memory Direct) n (xxx). W or Abs. W ¨ ¨ absolute short address stored as 16 bits specified as n n ¨ n final address is sign extension of 16 bit address 32 K = 32 x 1024 $00 7 FFF (xxx). L or Abs. L absolute long $FF 8000 ¨ address stored as 32 32 K bits $FF FFFF difference in machine code as absolute short generates memory extremes have special uses (system area, I/O interfaces, ROM) more compact machine code ¨ n $0 to $7 FFF $8000 to $FFFF $00 0000

e. g. shift a 16 bit variable left one bit; in place

eg. Divide an 8 -bit variable into two 4 -bit nibbles. Store the top nibble of the original into the low nibble of the top byte of the result and store the low nibble of the original into the low nibble of the low byte of the result. “unpack” the number For example, if byte =$5 F, the resulting word would be $050 F.

Reading/Expectations n n Reading: ¨ Endianness White Paper read pages 1 -8 [pdf, 22 p, Intel, ¨ Orthogonal instruction set [Wikipedia®] November 15, 2004] Expectations: you are able to write simple programs using the three addressing modes ¨ you can determine the addressing modes for any instruction (currently limited to the 3 addressing modes that you know) ¨ you can explain the concept of effective address and provide it for these and all future addressing modes ¨