Nov 2004 doc IEEE 802 15 04 0586

- Slides: 49

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b Project: IEEE P 802. 15 Working Group for Wireless Personal Area Networks (WPANs) Submission Title: [IEEE 802. 15. 4 b High Rate Alt-PHY proposals - Further Performance Comparison] Date Submitted: [10 Nov, 2004] Source: [Francois Chin] Company: [Institute for Infocomm Research, Singapore] Address: [21 Heng Mui Keng Terrace, Singapore 119613] Voice: [65 -6874 -5687] FAX: [65 -6774 -4990] E-Mail: [chinfrancois@i 2 r. a-star. edu. sg] Re: [Response to the call for proposal of IEEE 802. 15. 4 b, Doc Number: 15 -04 -0239 -00 -004 b] Abstract: [This presentation compares all proposals for the IEEE 802. 15. 4 b PHY standard. ] Purpose: [Proposal to IEEE 802. 15. 4 b Task Group] Notice: This document has been prepared to assist the IEEE P 802. 15. It is offered as a basis for discussion and is not binding on the contributing individual(s) or organization(s). The material in this document is subject to change in form and content after further study. The contributor(s) reserve(s) the right to add, amend or withdraw material contained herein. Release: The contributor acknowledges and accepts that this contribution becomes the property of IEEE and may be made publicly available by P 802. 15. Submission 1 Francois Chin, Institute for Infocomm Research (I 2 R)

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b Background – Main contribution of current doc is to provide further simulation results based on 1000 channel realisation, for the PHY proposals using coherent detection – Previous comparison used 100 channel realisation, as in IEEE Doc 15 -04 -0507 -04 -004 b – Performance comparison herein done with • {0, 1, 2} cyclic chip extension • {1, 2, 3} RAKE fingers Submission 2 Francois Chin, Institute for Infocomm Research (I 2 R)

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b Updates – Corrected 3 -RAKE multipath performance for all proposals (due to programme bug in previous version) – Included PSSS performance with Precoding – Determined RMS Delay Spread threshold below which cyclic chip extension is not necessary – Include 868 MHz multipath performance with raised cosine filter (roll-off factor = 0. 2) – Include PER performance curves – 915 MHz Transmit PSD for COBI-16 & 868 MHz Transmit PSD for COBI-8 & PSSS – Stated Recommendation based on realistic channel RMS delay spread, achievable Transmit PSD and PER performance Submission 3 Francois Chin, Institute for Infocomm Research (I 2 R)

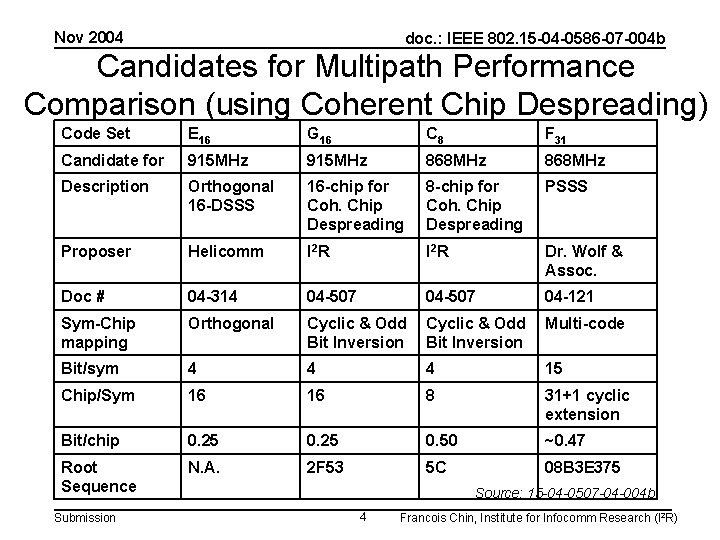

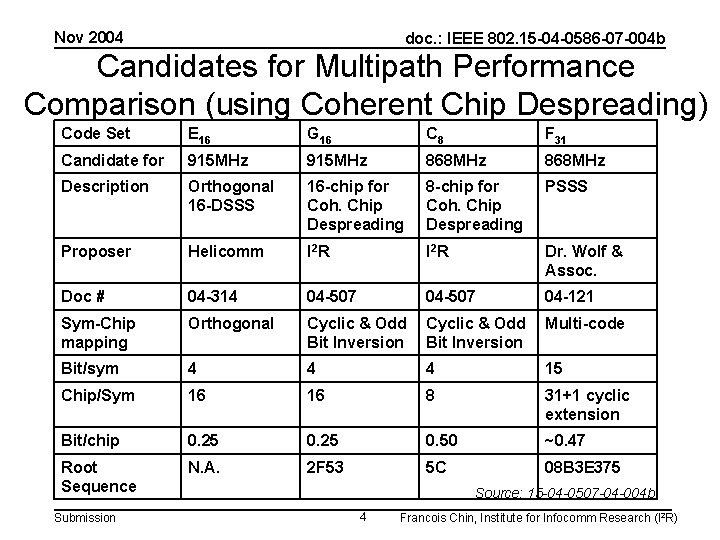

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b Candidates for Multipath Performance Comparison (using Coherent Chip Despreading) Code Set E 16 G 16 C 8 F 31 Candidate for 915 MHz 868 MHz Description Orthogonal 16 -DSSS 16 -chip for Coh. Chip Despreading 8 -chip for Coh. Chip Despreading PSSS Proposer Helicomm I 2 R Dr. Wolf & Assoc. Doc # 04 -314 04 -507 04 -121 Sym-Chip mapping Orthogonal Cyclic & Odd Bit Inversion Multi-code Bit/sym 4 4 4 15 Chip/Sym 16 16 8 31+1 cyclic extension Bit/chip 0. 25 0. 50 ~0. 47 Root Sequence N. A. 2 F 53 5 C 08 B 3 E 375 Submission Source: 15 -04 -0507 -04 -004 b 4 Francois Chin, Institute for Infocomm Research (I 2 R)

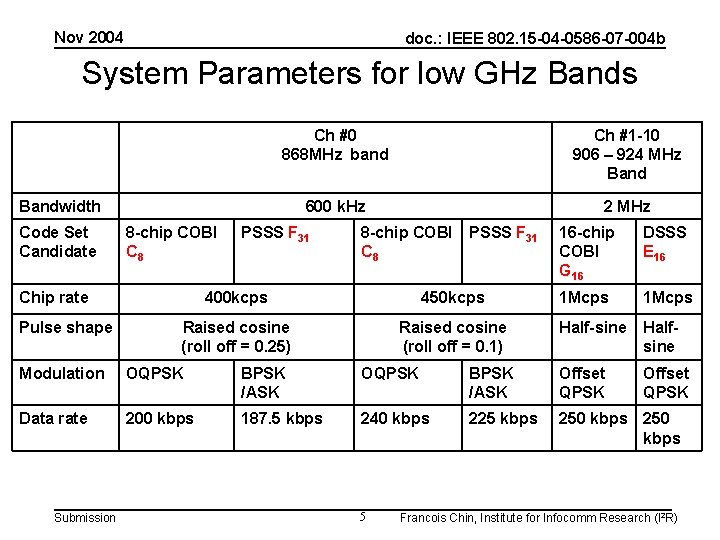

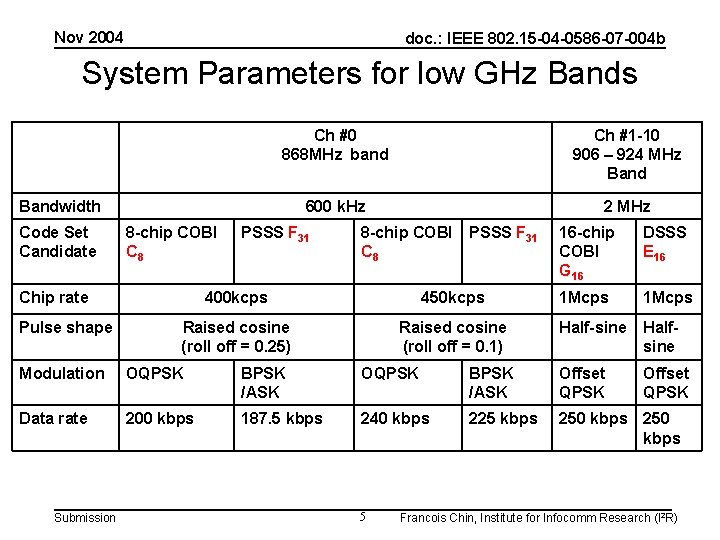

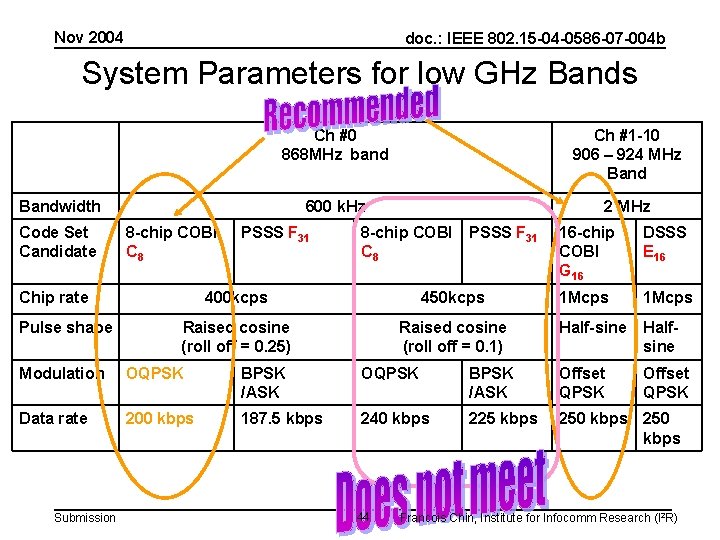

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b System Parameters for low GHz Bands Ch #0 868 MHz band Ch #1 -10 906 – 924 MHz Band 600 k. Hz 2 MHz Bandwidth Code Set Candidate 8 -chip COBI C 8 Chip rate Pulse shape PSSS F 31 8 -chip COBI C 8 PSSS F 31 400 kcps 450 kcps Raised cosine (roll off = 0. 25) Raised cosine (roll off = 0. 1) 16 -chip COBI G 16 DSSS E 16 1 Mcps Half-sine Halfsine Offset QPSK Modulation OQPSK BPSK /ASK Offset QPSK Data rate 200 kbps 187. 5 kbps 240 kbps 225 kbps 250 kbps Submission 5 Francois Chin, Institute for Infocomm Research (I 2 R)

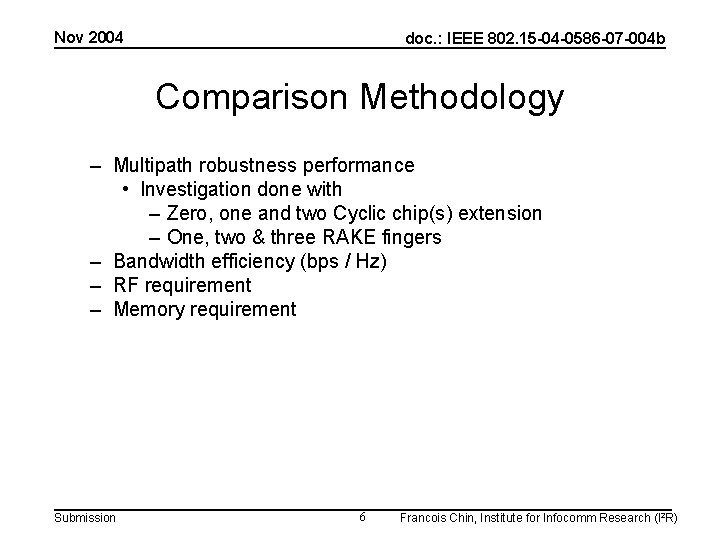

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b Comparison Methodology – Multipath robustness performance • Investigation done with – Zero, one and two Cyclic chip(s) extension – One, two & three RAKE fingers – Bandwidth efficiency (bps / Hz) – RF requirement – Memory requirement Submission 6 Francois Chin, Institute for Infocomm Research (I 2 R)

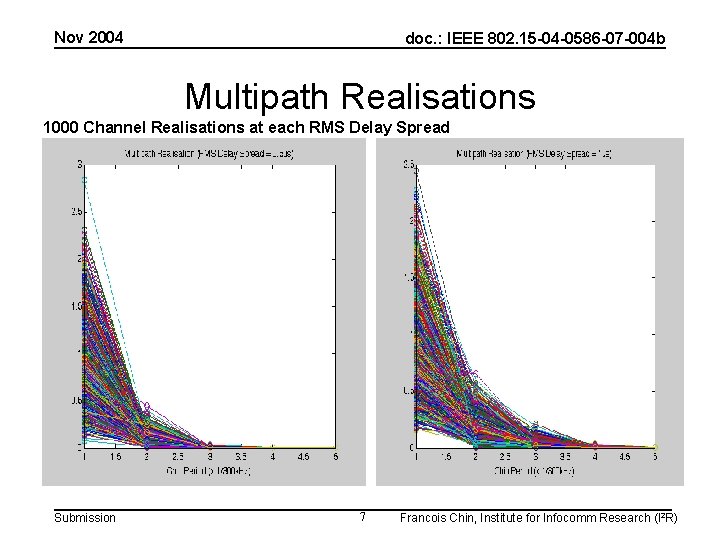

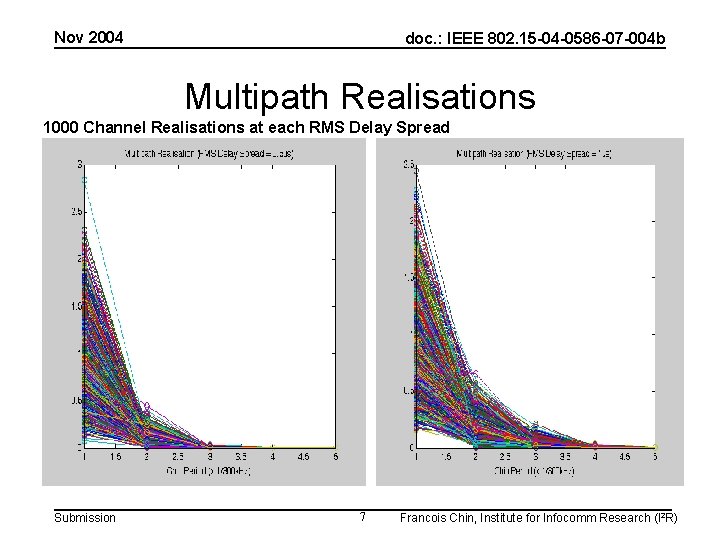

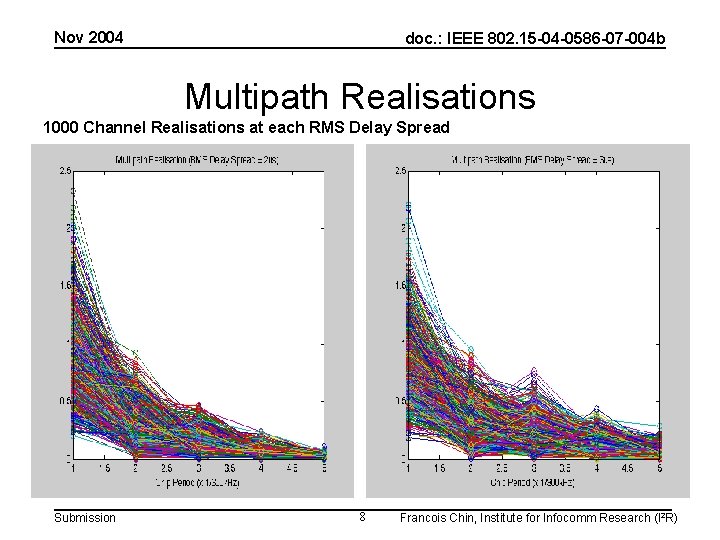

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b Multipath Realisations 1000 Channel Realisations at each RMS Delay Spread Submission 7 Francois Chin, Institute for Infocomm Research (I 2 R)

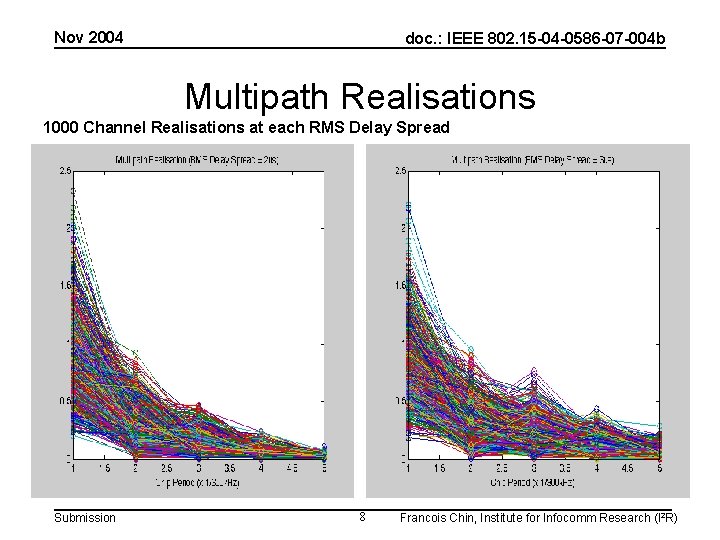

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b Multipath Realisations 1000 Channel Realisations at each RMS Delay Spread Submission 8 Francois Chin, Institute for Infocomm Research (I 2 R)

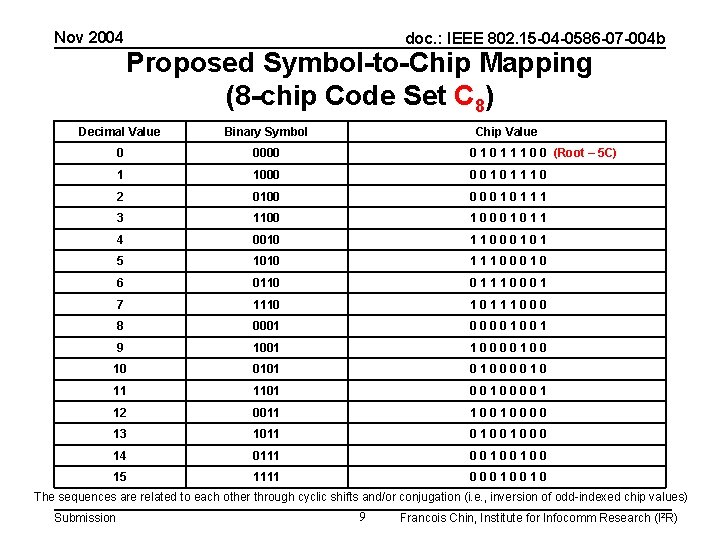

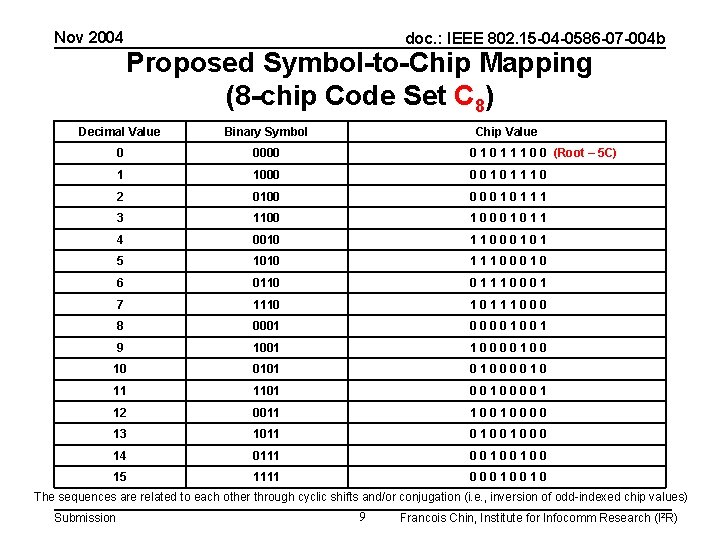

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b Proposed Symbol-to-Chip Mapping (8 -chip Code Set C 8) Decimal Value Binary Symbol Chip Value 0 0000 0 1 1 1 0 0 (Root – 5 C) 1 1000 00101110 2 0100 00010111 3 1100 10001011 4 0010 11000101 5 1010 11100010 6 0110 01110001 7 1110 10111000 8 0001 00001001 9 1001 10000100 10 0101 01000010 11 1101 00100001 12 0011 10010000 13 1011 01001000 14 0111 00100100 15 1111 00010010 The sequences are related to each other through cyclic shifts and/or conjugation (i. e. , inversion of odd-indexed chip values) Submission 9 Francois Chin, Institute for Infocomm Research (I 2 R)

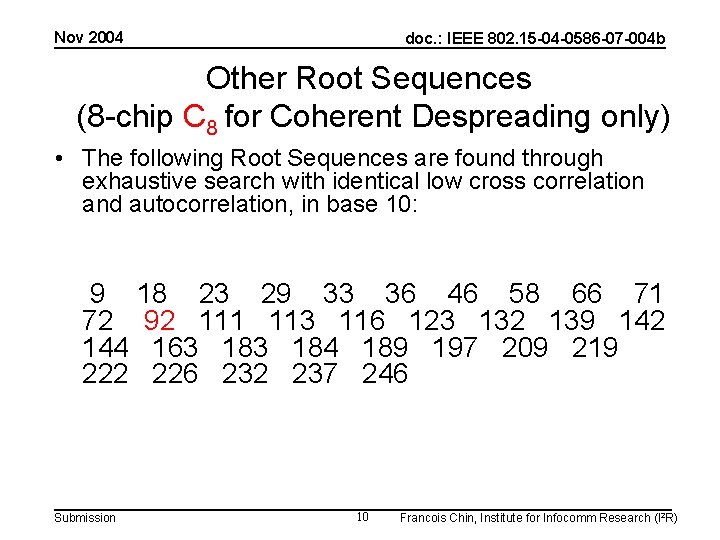

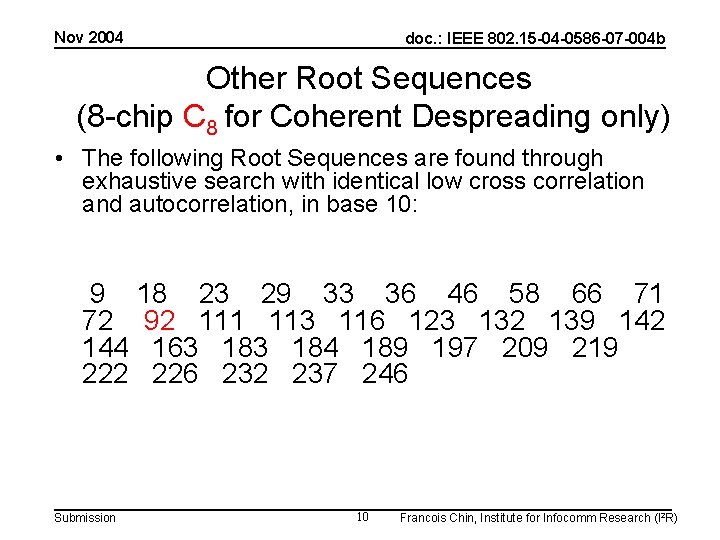

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b Other Root Sequences (8 -chip C 8 for Coherent Despreading only) • The following Root Sequences are found through exhaustive search with identical low cross correlation and autocorrelation, in base 10: 9 18 23 29 33 36 46 58 66 71 72 92 111 113 116 123 132 139 142 144 163 184 189 197 209 219 222 226 232 237 246 Submission 10 Francois Chin, Institute for Infocomm Research (I 2 R)

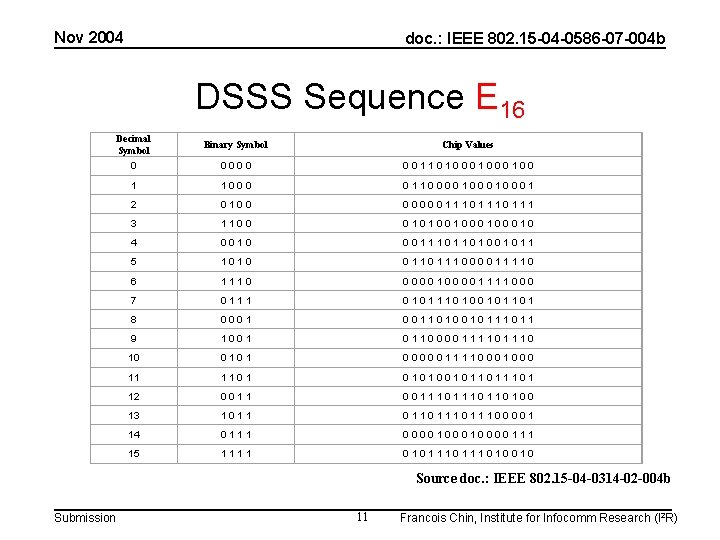

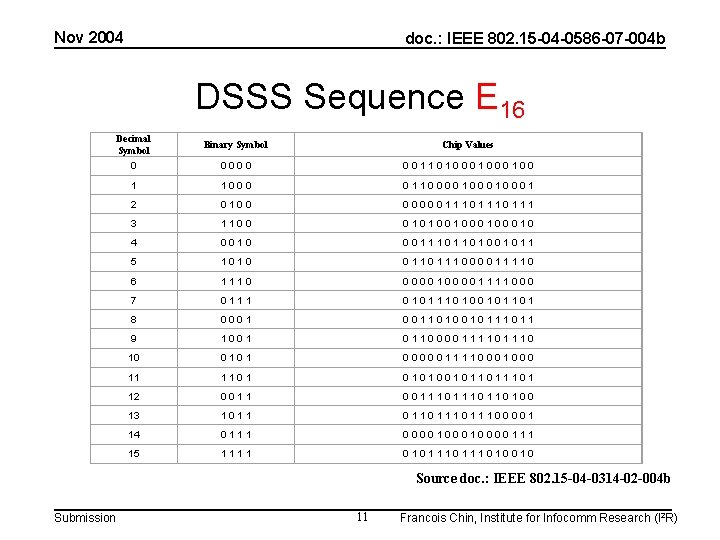

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b DSSS Sequence E 16 Decimal Symbol Binary Symbol Chip Values 0 0000 001101000100 1 1000 011000010001 2 0100 000001110111 3 1100 010100100010 4 0010 0011101101001011 5 1010 0110111000011110 6 1110 00001111000 7 0111 0101110100101101 8 0001 001101001011 9 1001 011000011110 10 0101 000001111000 11 1101 010100101101 12 001110110100 13 1011 011011100001 14 0111 000010000111 15 1111 010111010010 Source doc. : IEEE 802. 15 -04 -0314 -02 -004 b Submission 11 Francois Chin, Institute for Infocomm Research (I 2 R)

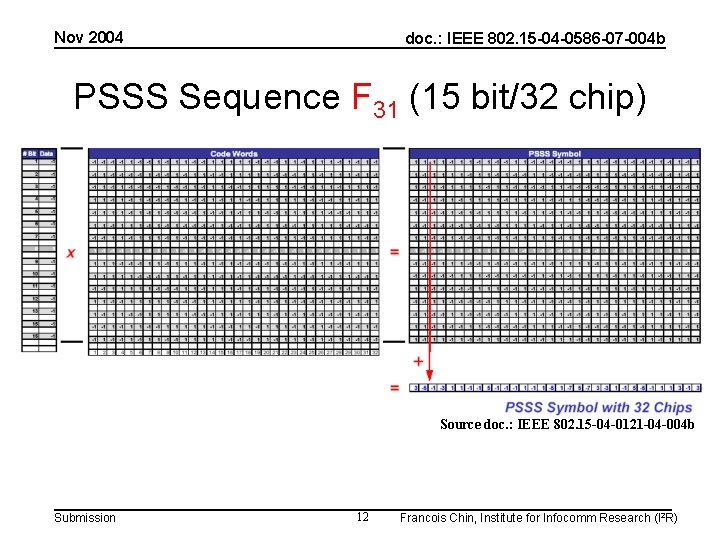

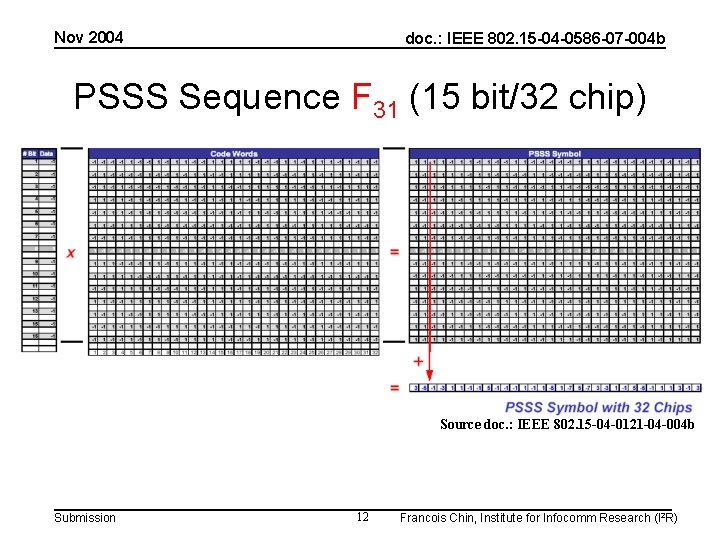

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b PSSS Sequence F 31 (15 bit/32 chip) Source doc. : IEEE 802. 15 -04 -0121 -04 -004 b Submission 12 Francois Chin, Institute for Infocomm Research (I 2 R)

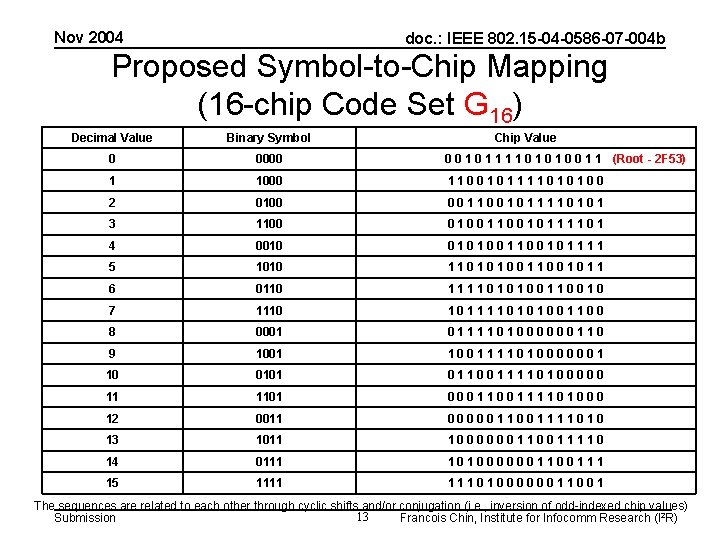

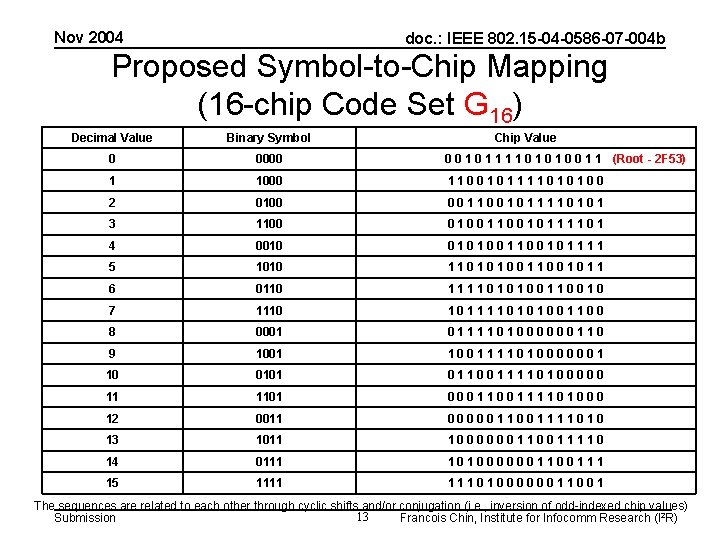

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b Proposed Symbol-to-Chip Mapping (16 -chip Code Set G 16) Decimal Value Binary Symbol Chip Value 0 0000 0 0 1 1 1 1 0 1 0 0 1 1 (Root - 2 F 53) 1 1000 1100101111010100 2 0100 0011001011110101 3 1100 010010111101 4 0010 010100101111 5 1010 110101001011 6 0110 111101010010 7 1110 1011110101001100 8 0001 0111101000000110 9 1001111010000001 10 0101 0110011110100000 11 1101 000111101000 12 0011 000001111010 13 1011 100000011110 14 0111 101000000111 15 1111 1110100000011001 The sequences are related to each other through cyclic shifts and/or conjugation (i. e. , inversion of odd-indexed chip values) 13 Submission Francois Chin, Institute for Infocomm Research (I 2 R)

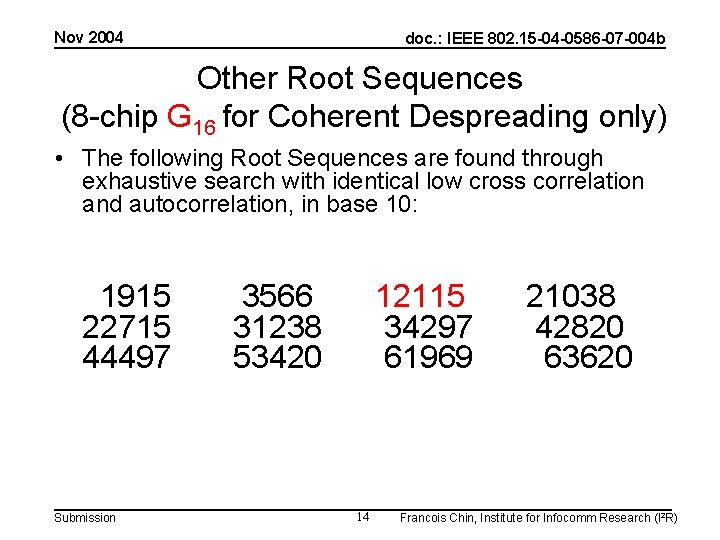

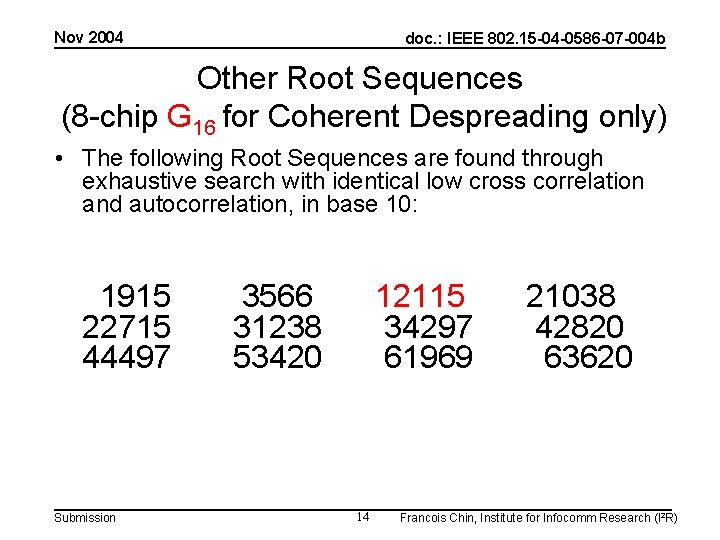

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b Other Root Sequences (8 -chip G 16 for Coherent Despreading only) • The following Root Sequences are found through exhaustive search with identical low cross correlation and autocorrelation, in base 10: 1915 22715 44497 Submission 3566 31238 53420 12115 34297 61969 14 21038 42820 63620 Francois Chin, Institute for Infocomm Research (I 2 R)

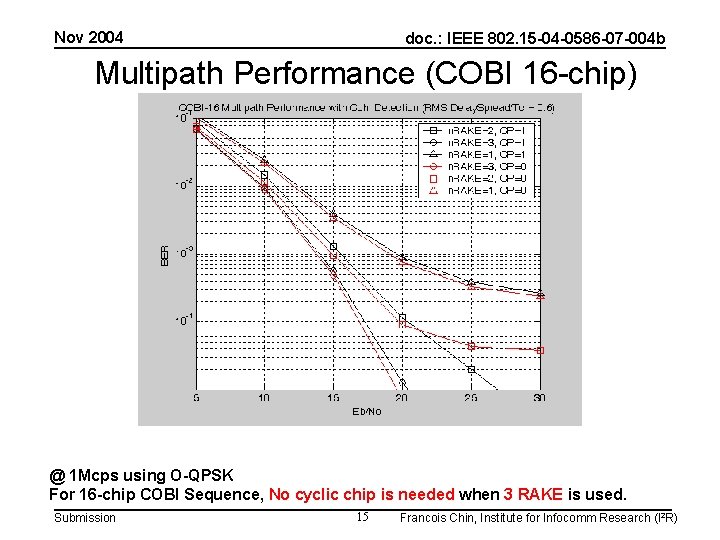

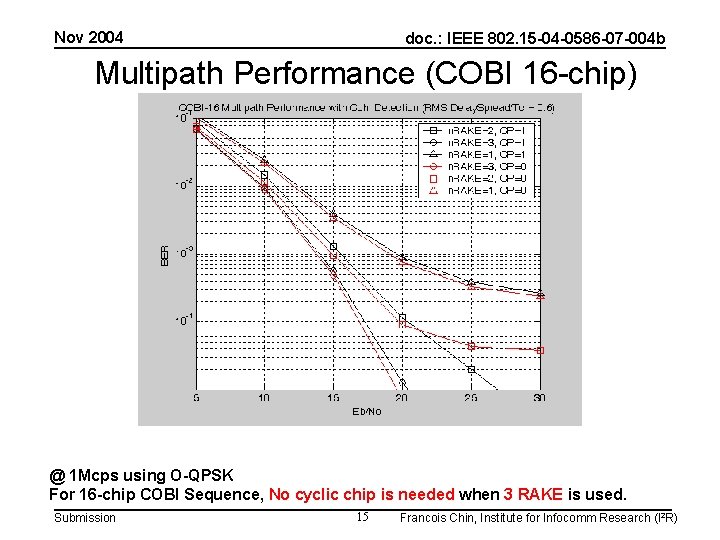

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b Multipath Performance (COBI 16 -chip) @ 1 Mcps using O-QPSK For 16 -chip COBI Sequence, No cyclic chip is needed when 3 RAKE is used. Submission 15 Francois Chin, Institute for Infocomm Research (I 2 R)

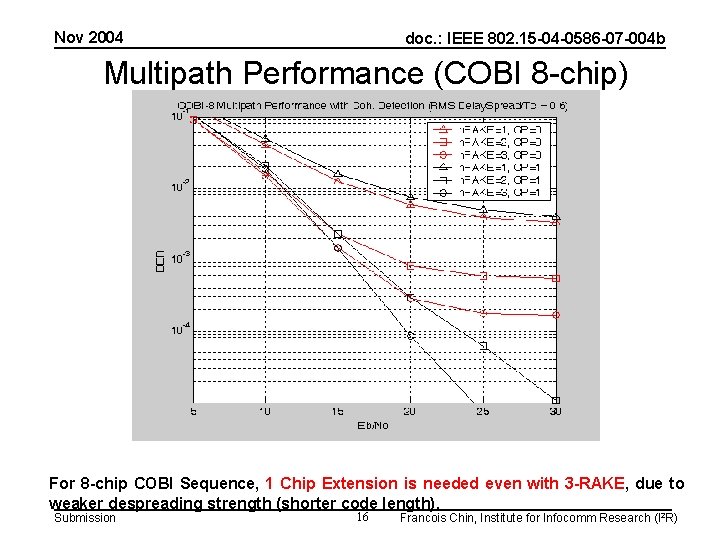

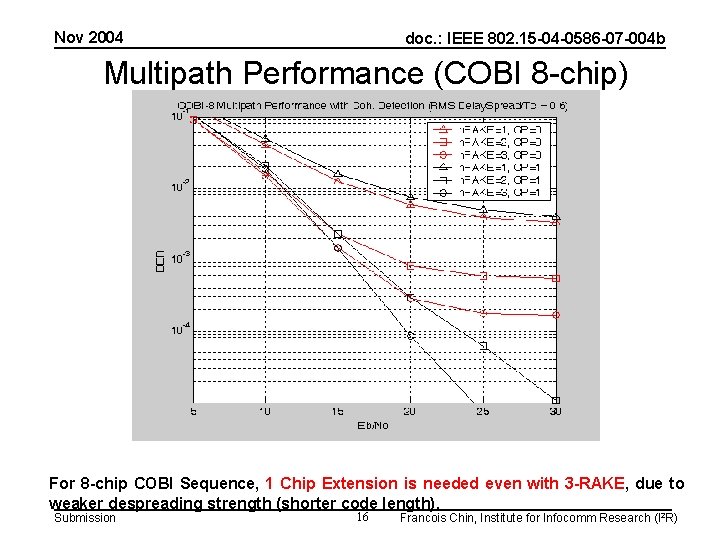

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b Multipath Performance (COBI 8 -chip) For 8 -chip COBI Sequence, 1 Chip Extension is needed even with 3 -RAKE, due to weaker despreading strength (shorter code length). Submission 16 Francois Chin, Institute for Infocomm Research (I 2 R)

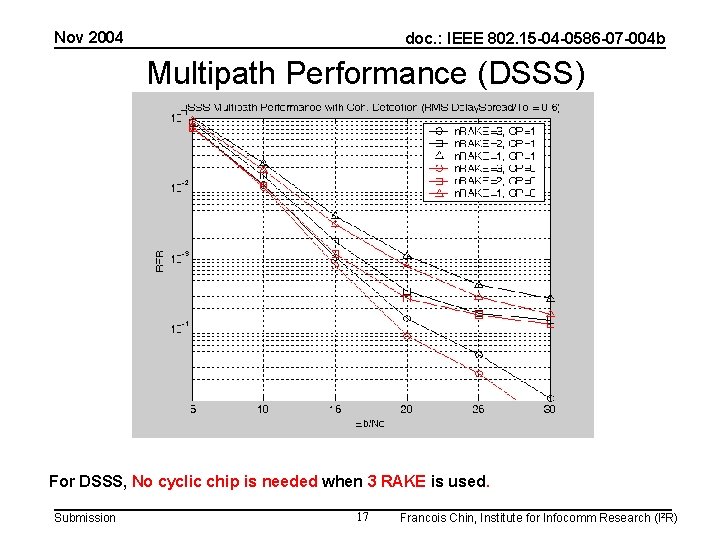

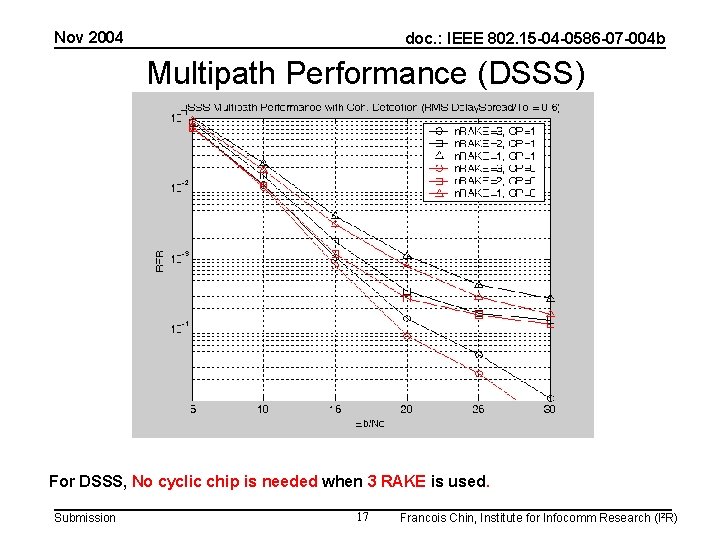

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b Multipath Performance (DSSS) For DSSS, No cyclic chip is needed when 3 RAKE is used. Submission 17 Francois Chin, Institute for Infocomm Research (I 2 R)

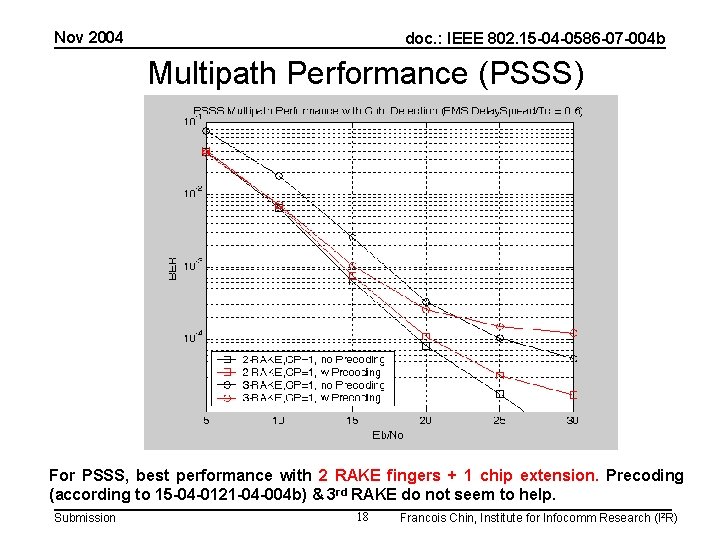

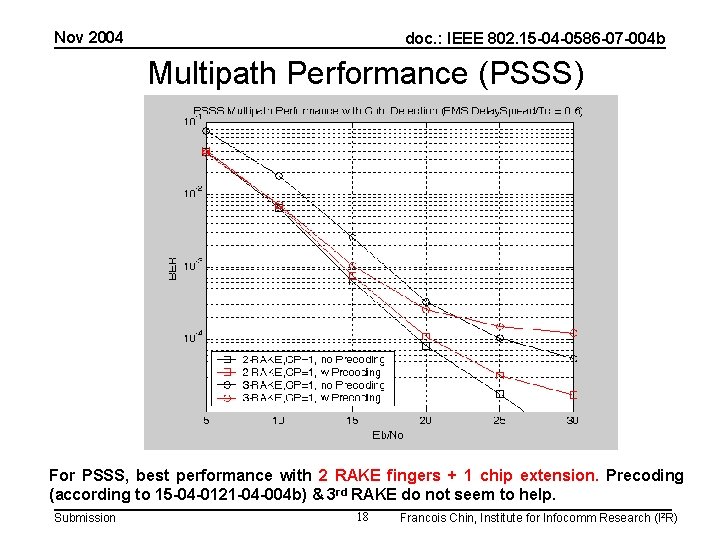

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b Multipath Performance (PSSS) For PSSS, best performance with 2 RAKE fingers + 1 chip extension. Precoding (according to 15 -04 -0121 -04 -004 b) & 3 rd RAKE do not seem to help. Submission 18 Francois Chin, Institute for Infocomm Research (I 2 R)

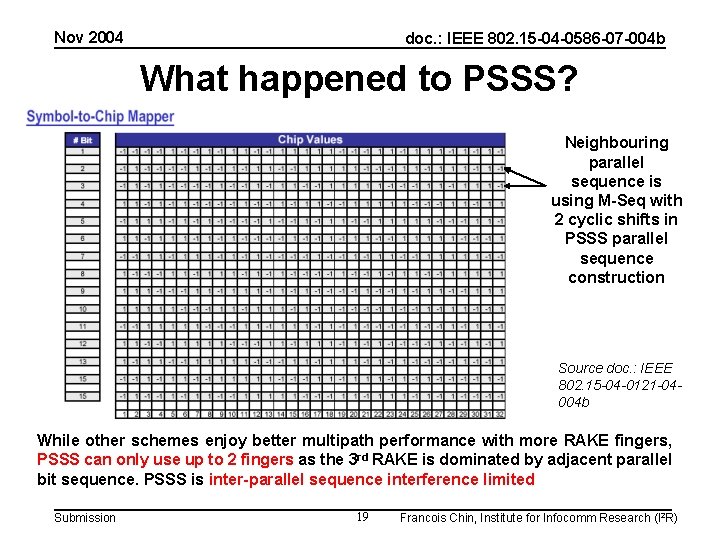

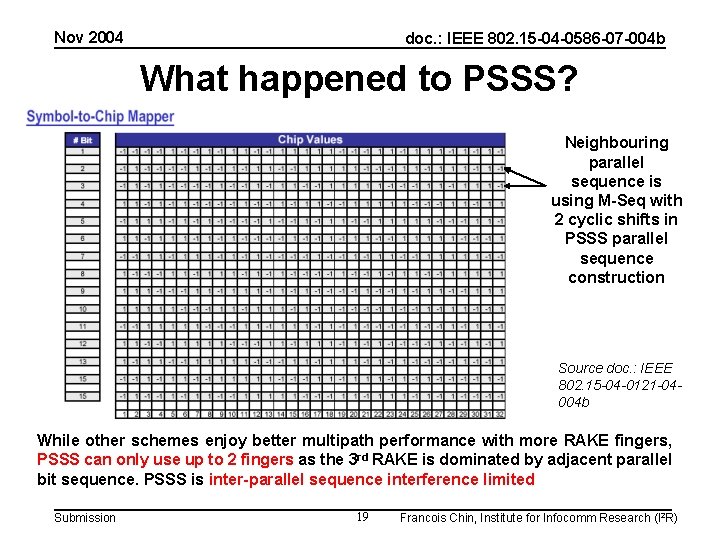

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b What happened to PSSS? Neighbouring parallel sequence is using M-Seq with 2 cyclic shifts in PSSS parallel sequence construction Source doc. : IEEE 802. 15 -04 -0121 -04004 b While other schemes enjoy better multipath performance with more RAKE fingers, PSSS can only use up to 2 fingers as the 3 rd RAKE is dominated by adjacent parallel bit sequence. PSSS is inter-parallel sequence interference limited Submission 19 Francois Chin, Institute for Infocomm Research (I 2 R)

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b 915 MHz Bands COBI-16 vs DSSS Submission 20 Francois Chin, Institute for Infocomm Research (I 2 R)

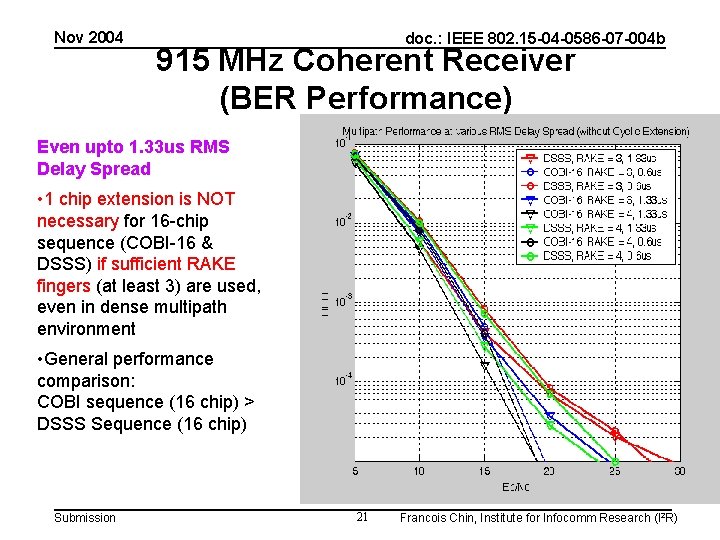

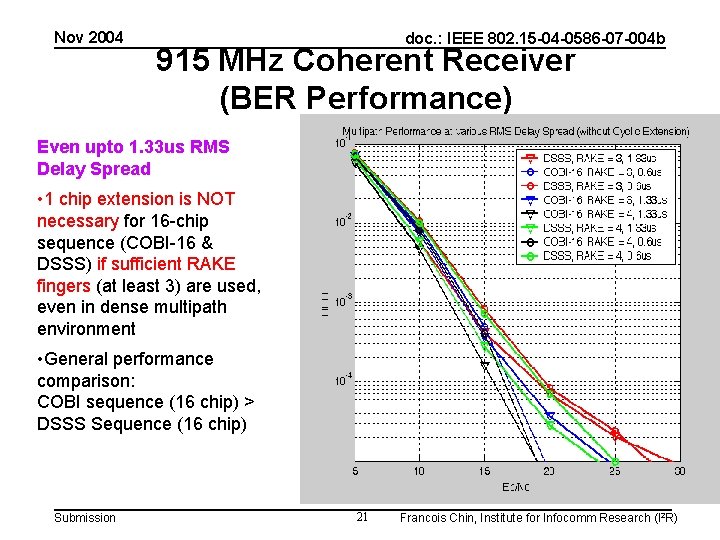

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b 915 MHz Coherent Receiver (BER Performance) Even upto 1. 33 us RMS Delay Spread • 1 chip extension is NOT necessary for 16 -chip sequence (COBI-16 & DSSS) if sufficient RAKE fingers (at least 3) are used, even in dense multipath environment • General performance comparison: COBI sequence (16 chip) > DSSS Sequence (16 chip) Submission 21 Francois Chin, Institute for Infocomm Research (I 2 R)

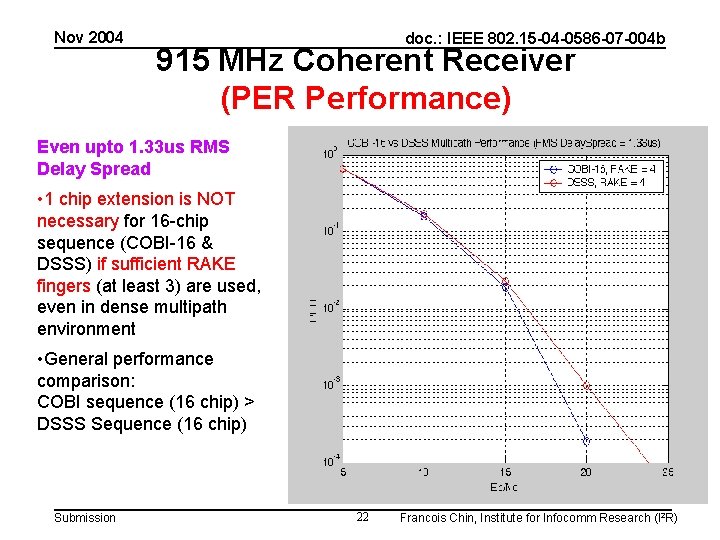

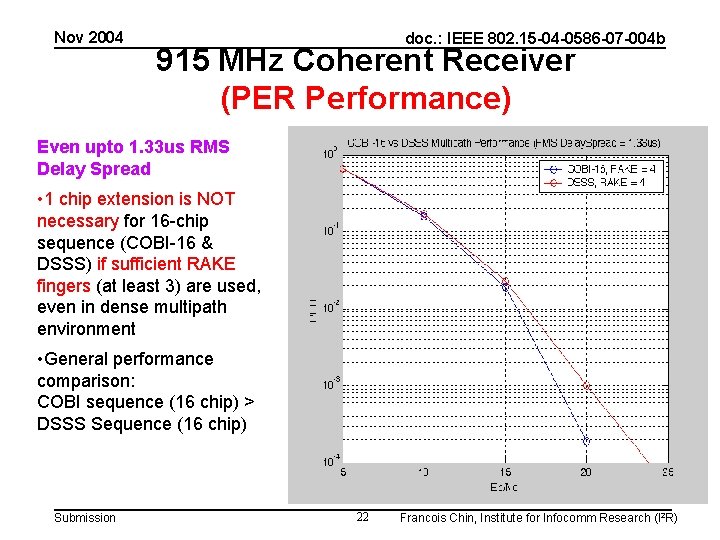

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b 915 MHz Coherent Receiver (PER Performance) Even upto 1. 33 us RMS Delay Spread • 1 chip extension is NOT necessary for 16 -chip sequence (COBI-16 & DSSS) if sufficient RAKE fingers (at least 3) are used, even in dense multipath environment • General performance comparison: COBI sequence (16 chip) > DSSS Sequence (16 chip) Submission 22 Francois Chin, Institute for Infocomm Research (I 2 R)

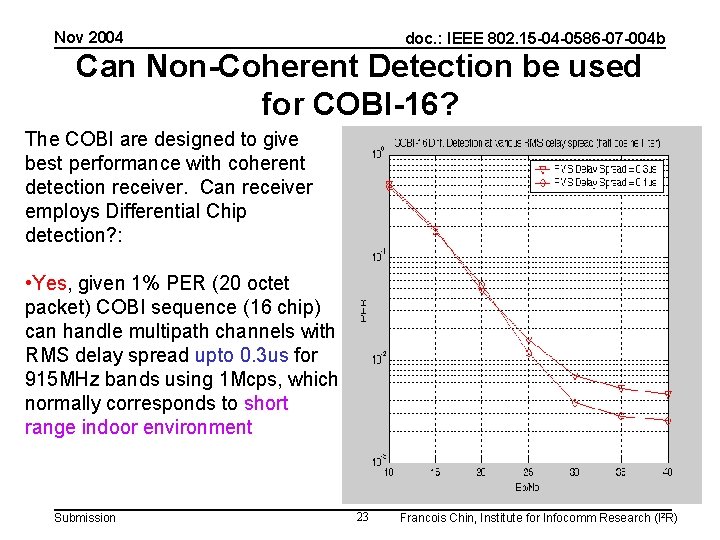

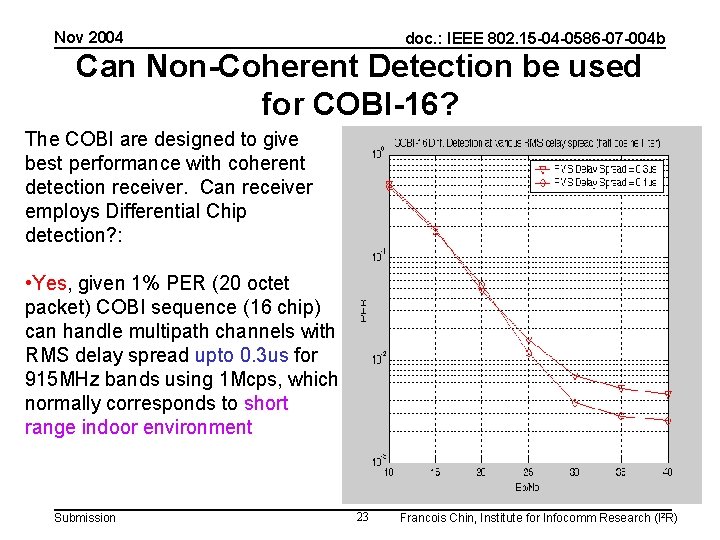

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b Can Non-Coherent Detection be used for COBI-16? The COBI are designed to give best performance with coherent detection receiver. Can receiver employs Differential Chip detection? : • Yes, given 1% PER (20 octet packet) COBI sequence (16 chip) can handle multipath channels with RMS delay spread upto 0. 3 us for 915 MHz bands using 1 Mcps, which normally corresponds to short range indoor environment Submission 23 Francois Chin, Institute for Infocomm Research (I 2 R)

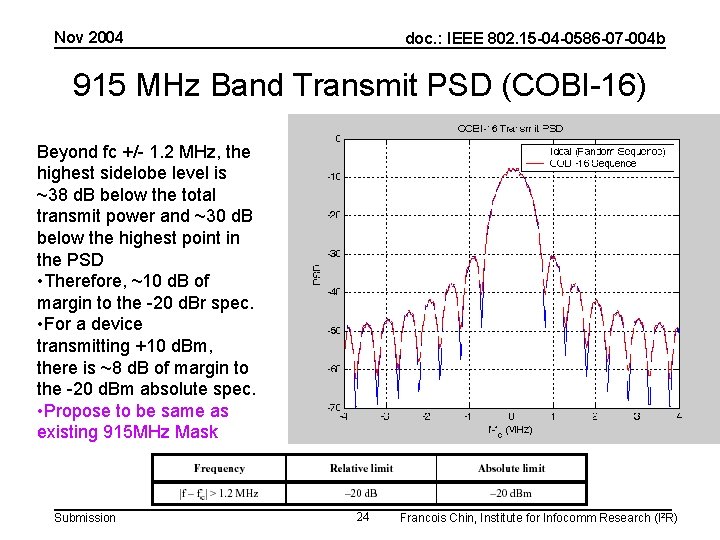

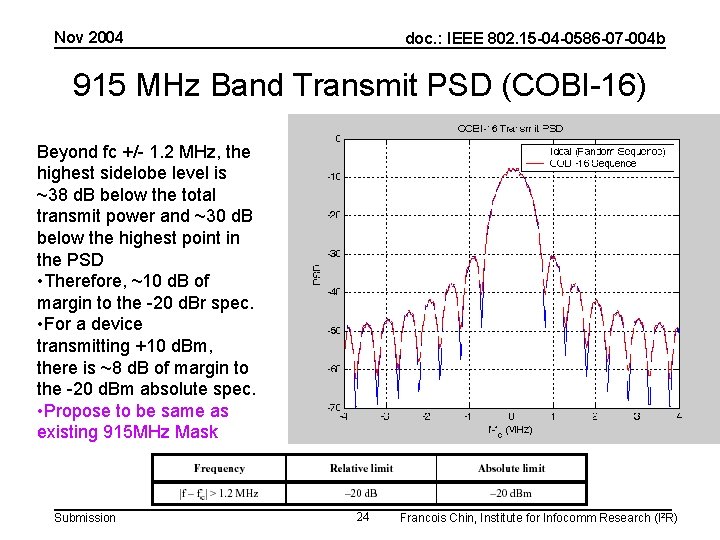

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b 915 MHz Band Transmit PSD (COBI-16) Beyond fc +/- 1. 2 MHz, the highest sidelobe level is ~38 d. B below the total transmit power and ~30 d. B below the highest point in the PSD • Therefore, ~10 d. B of margin to the -20 d. Br spec. • For a device transmitting +10 d. Bm, there is ~8 d. B of margin to the -20 d. Bm absolute spec. • Propose to be same as existing 915 MHz Mask Submission 24 Francois Chin, Institute for Infocomm Research (I 2 R)

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b 868 MHz Band COBI-8 vs PSSS Submission 25 Francois Chin, Institute for Infocomm Research (I 2 R)

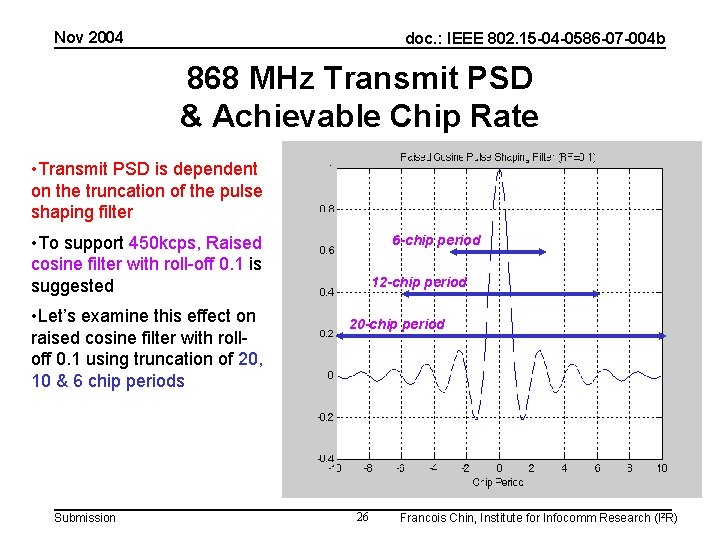

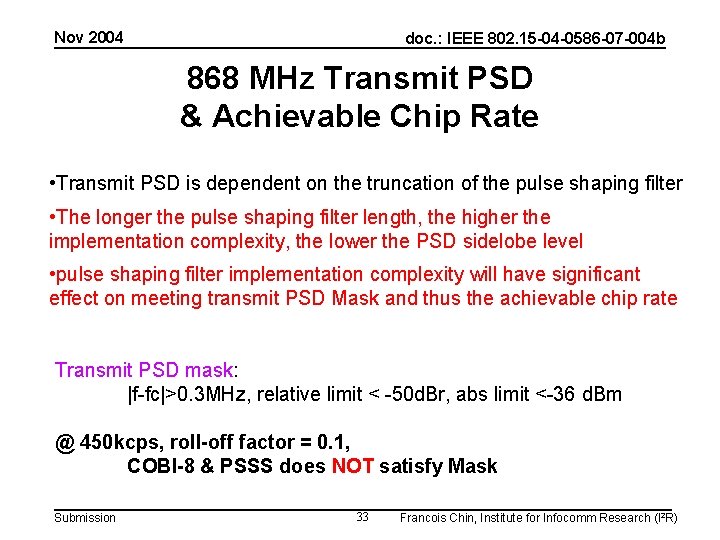

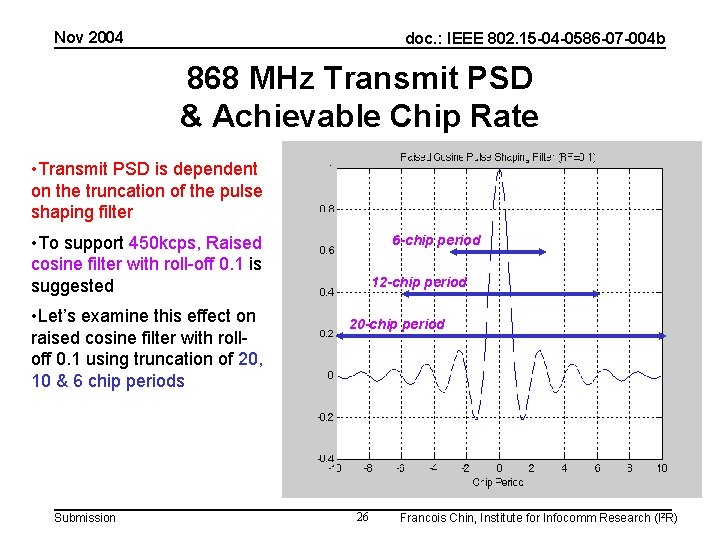

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b 868 MHz Transmit PSD & Achievable Chip Rate • Transmit PSD is dependent on the truncation of the pulse shaping filter • To support 450 kcps, Raised cosine filter with roll-off 0. 1 is suggested • Let’s examine this effect on raised cosine filter with rolloff 0. 1 using truncation of 20, 10 & 6 chip periods Submission 6 -chip period 12 -chip period 20 -chip period 26 Francois Chin, Institute for Infocomm Research (I 2 R)

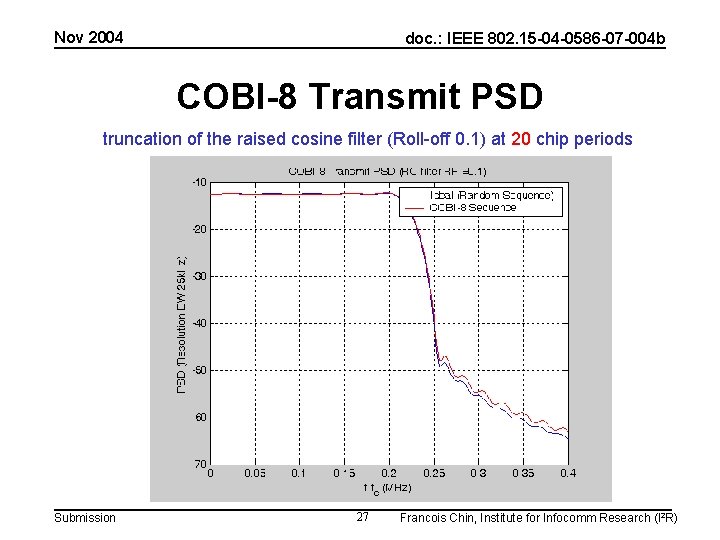

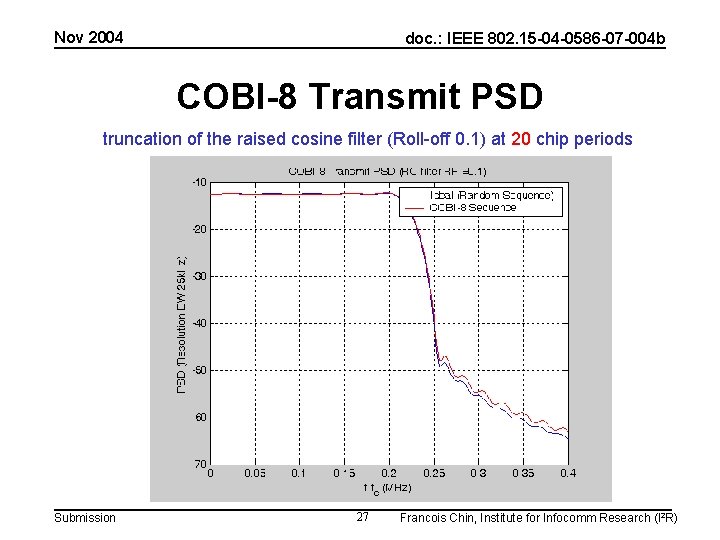

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b COBI-8 Transmit PSD truncation of the raised cosine filter (Roll-off 0. 1) at 20 chip periods Submission 27 Francois Chin, Institute for Infocomm Research (I 2 R)

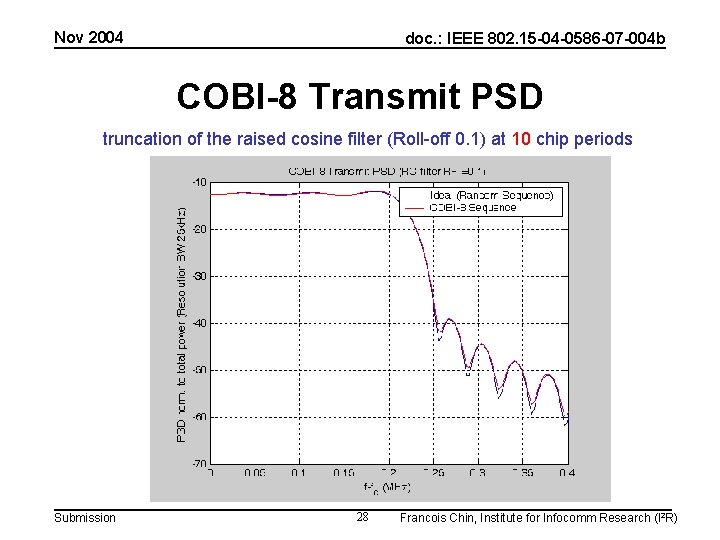

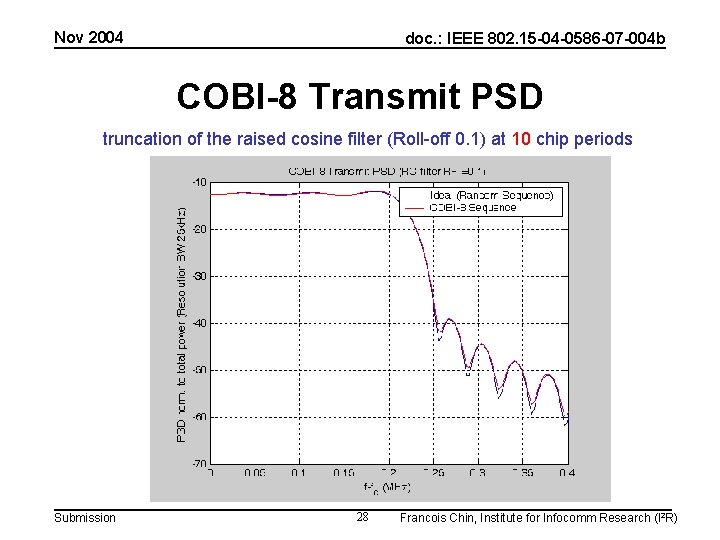

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b COBI-8 Transmit PSD truncation of the raised cosine filter (Roll-off 0. 1) at 10 chip periods Submission 28 Francois Chin, Institute for Infocomm Research (I 2 R)

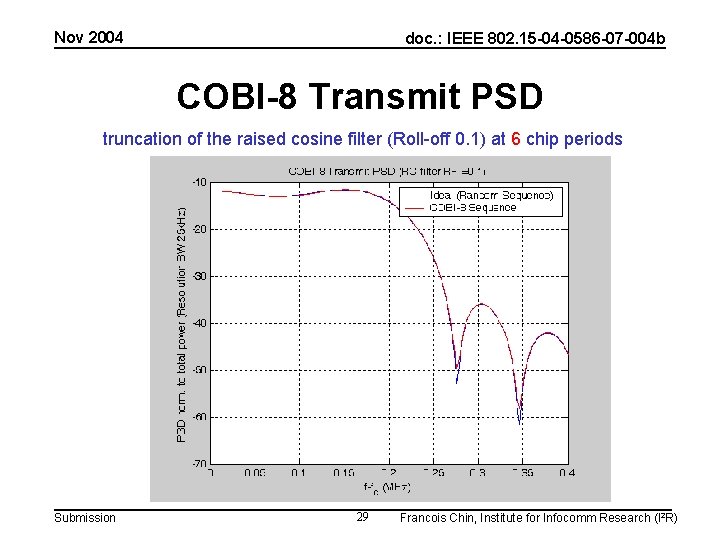

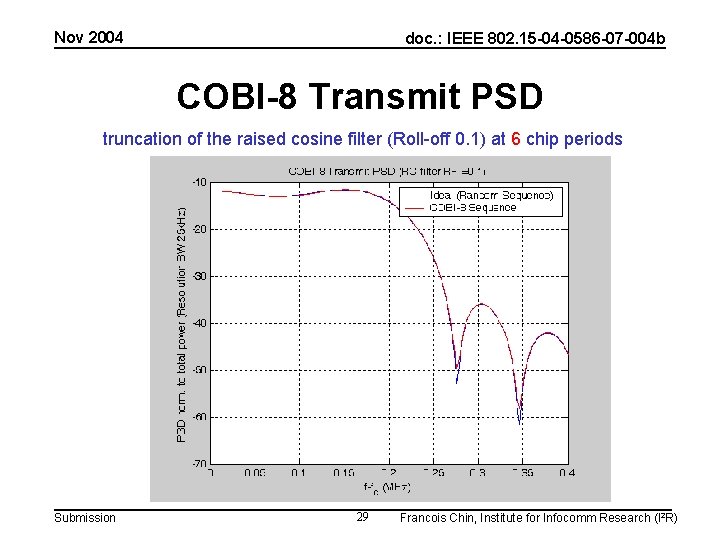

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b COBI-8 Transmit PSD truncation of the raised cosine filter (Roll-off 0. 1) at 6 chip periods Submission 29 Francois Chin, Institute for Infocomm Research (I 2 R)

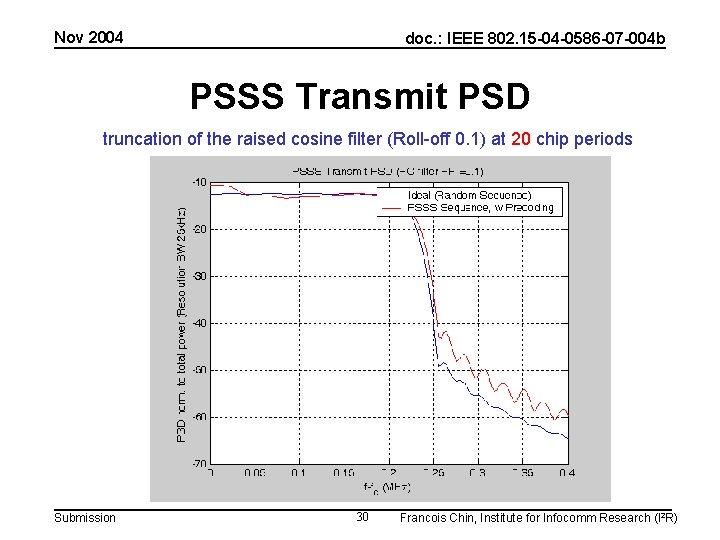

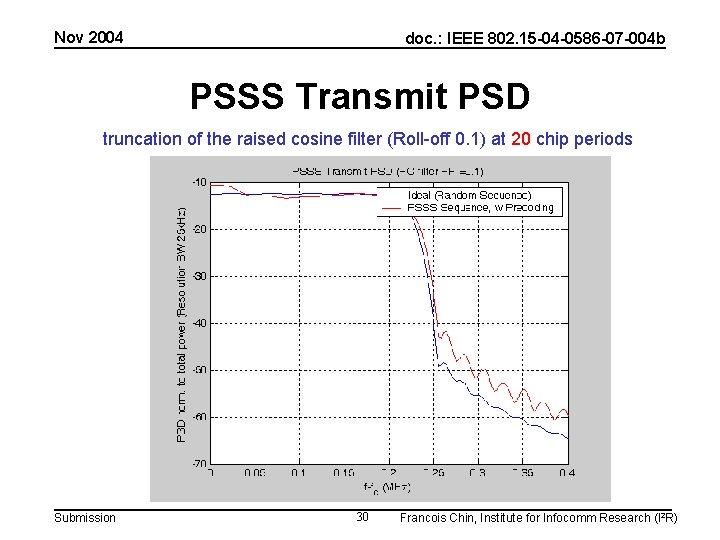

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b PSSS Transmit PSD truncation of the raised cosine filter (Roll-off 0. 1) at 20 chip periods Submission 30 Francois Chin, Institute for Infocomm Research (I 2 R)

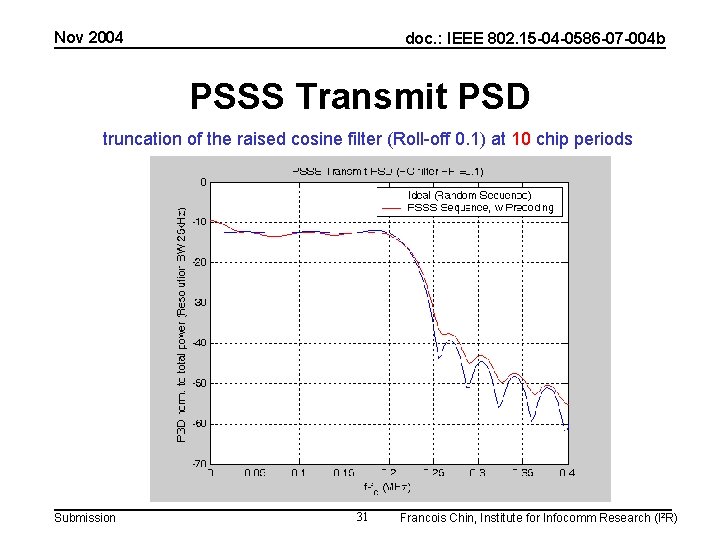

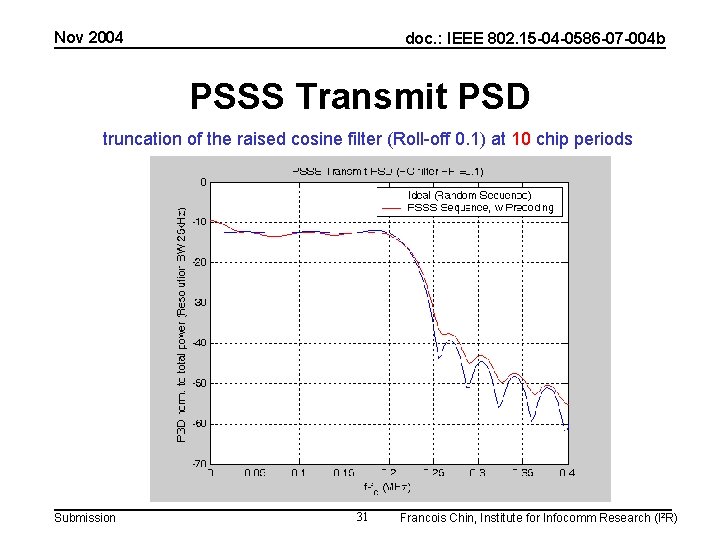

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b PSSS Transmit PSD truncation of the raised cosine filter (Roll-off 0. 1) at 10 chip periods Submission 31 Francois Chin, Institute for Infocomm Research (I 2 R)

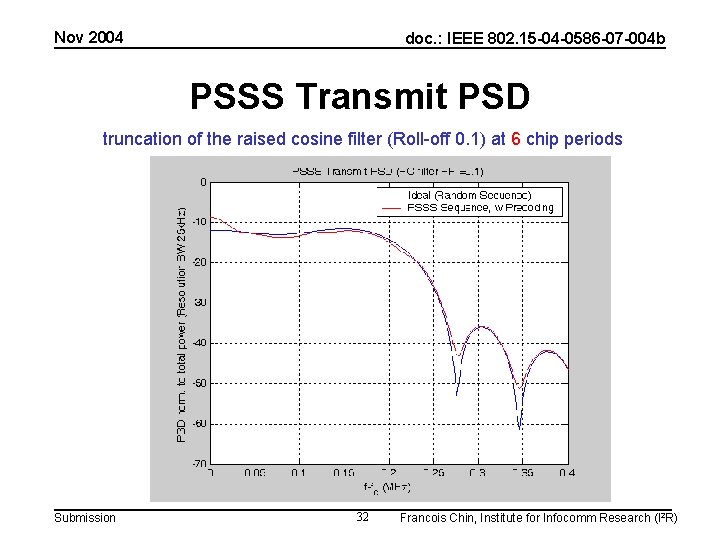

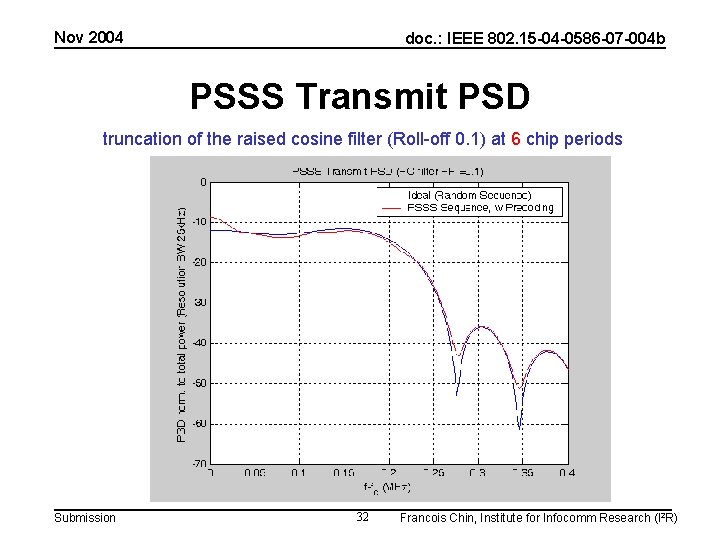

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b PSSS Transmit PSD truncation of the raised cosine filter (Roll-off 0. 1) at 6 chip periods Submission 32 Francois Chin, Institute for Infocomm Research (I 2 R)

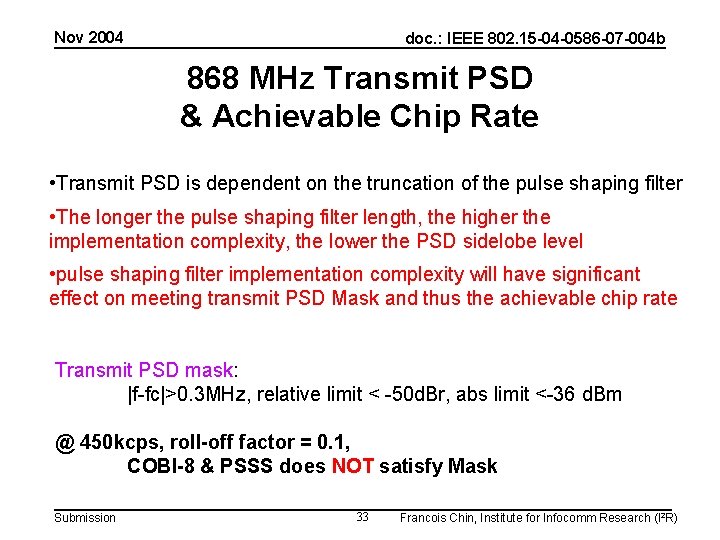

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b 868 MHz Transmit PSD & Achievable Chip Rate • Transmit PSD is dependent on the truncation of the pulse shaping filter • The longer the pulse shaping filter length, the higher the implementation complexity, the lower the PSD sidelobe level • pulse shaping filter implementation complexity will have significant effect on meeting transmit PSD Mask and thus the achievable chip rate Transmit PSD mask: |f-fc|>0. 3 MHz, relative limit < -50 d. Br, abs limit <-36 d. Bm @ 450 kcps, roll-off factor = 0. 1, COBI-8 & PSSS does NOT satisfy Mask Submission 33 Francois Chin, Institute for Infocomm Research (I 2 R)

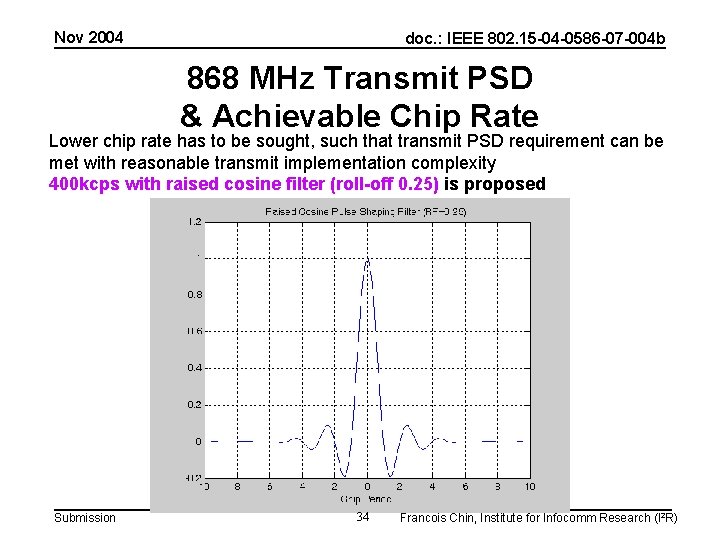

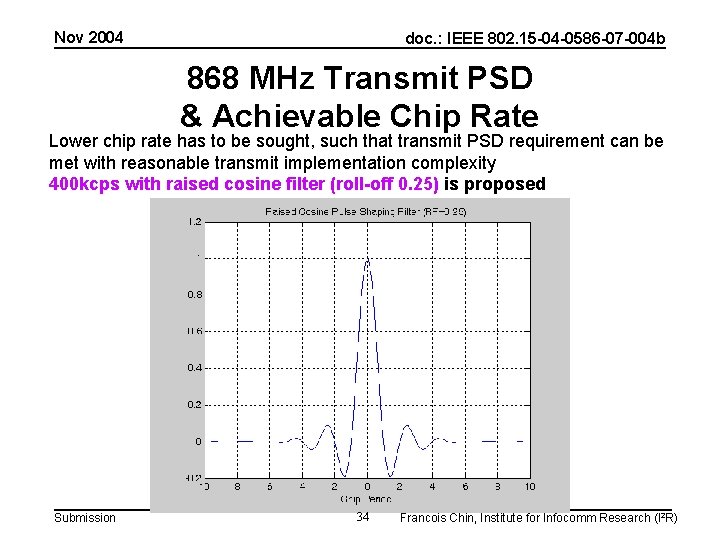

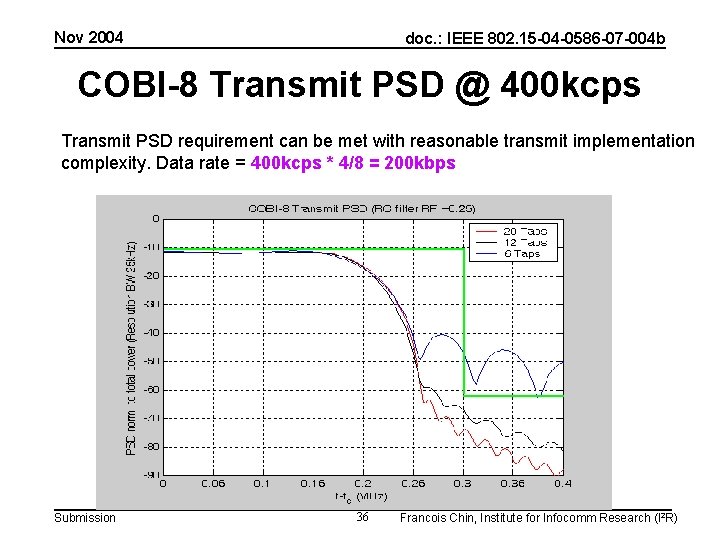

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b 868 MHz Transmit PSD & Achievable Chip Rate Lower chip rate has to be sought, such that transmit PSD requirement can be met with reasonable transmit implementation complexity 400 kcps with raised cosine filter (roll-off 0. 25) is proposed Submission 34 Francois Chin, Institute for Infocomm Research (I 2 R)

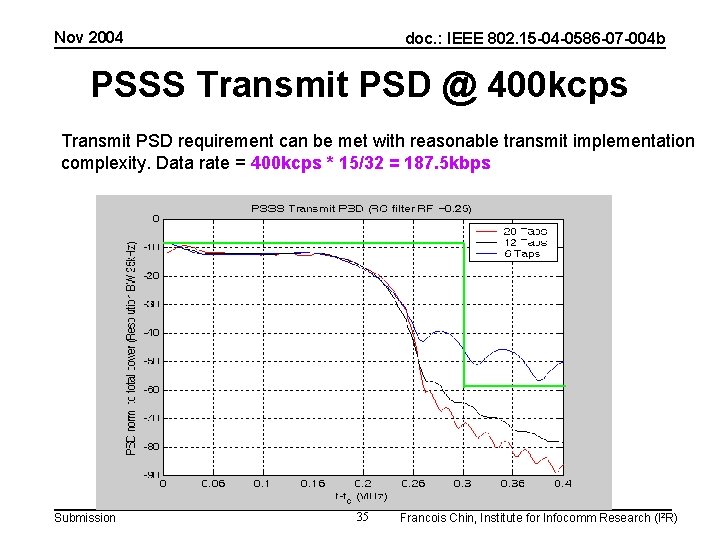

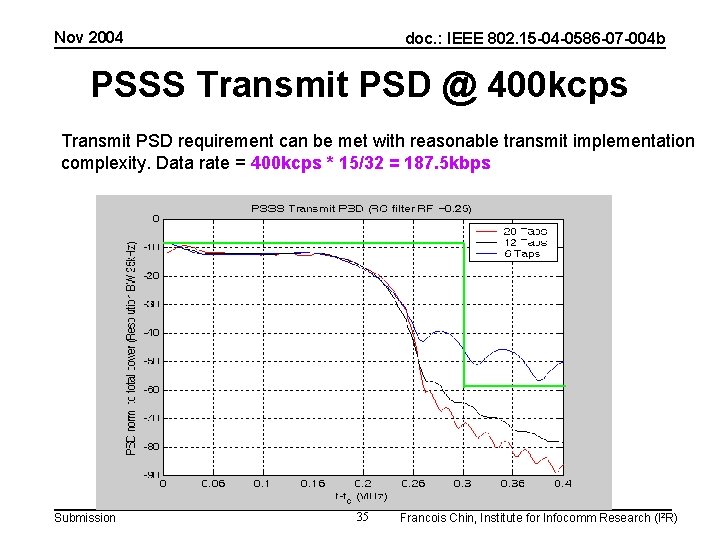

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b PSSS Transmit PSD @ 400 kcps Transmit PSD requirement can be met with reasonable transmit implementation complexity. Data rate = 400 kcps * 15/32 = 187. 5 kbps Submission 35 Francois Chin, Institute for Infocomm Research (I 2 R)

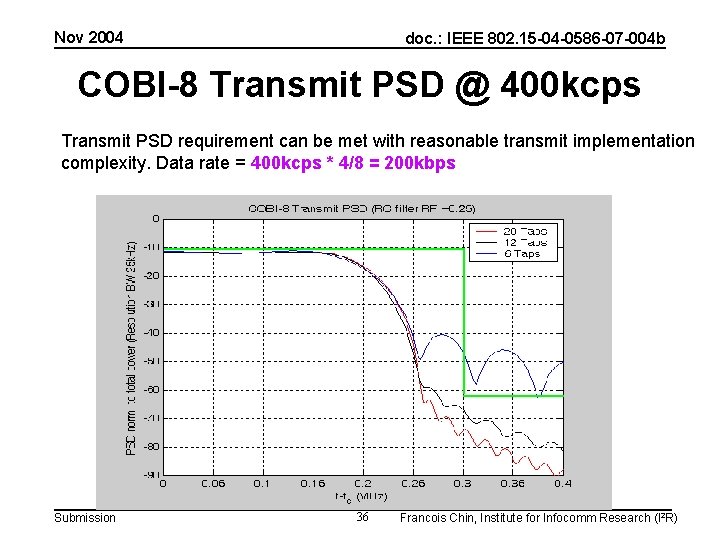

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b COBI-8 Transmit PSD @ 400 kcps Transmit PSD requirement can be met with reasonable transmit implementation complexity. Data rate = 400 kcps * 4/8 = 200 kbps Submission 36 Francois Chin, Institute for Infocomm Research (I 2 R)

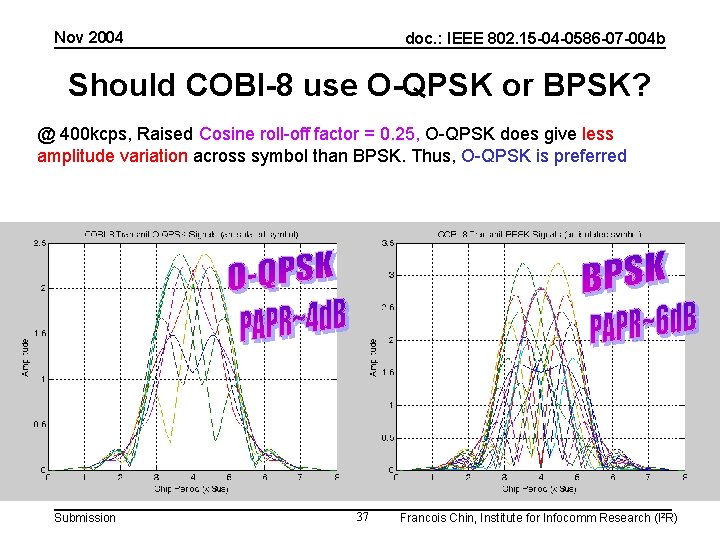

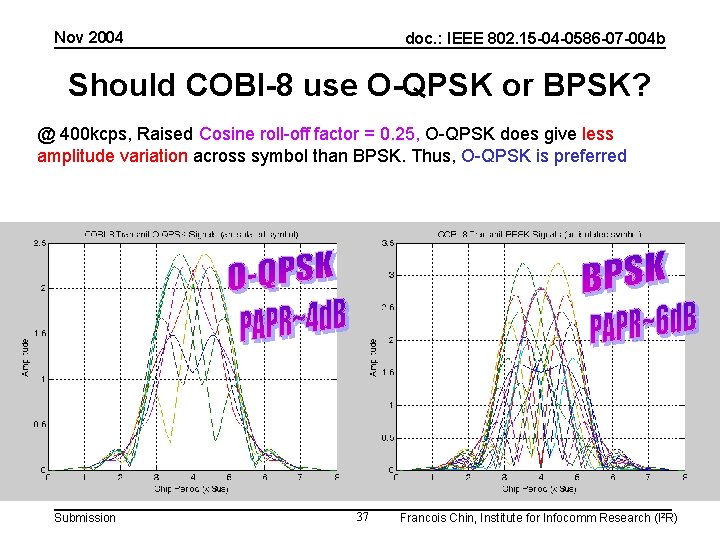

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b Should COBI-8 use O-QPSK or BPSK? @ 400 kcps, Raised Cosine roll-off factor = 0. 25, O-QPSK does give less amplitude variation across symbol than BPSK. Thus, O-QPSK is preferred Submission 37 Francois Chin, Institute for Infocomm Research (I 2 R)

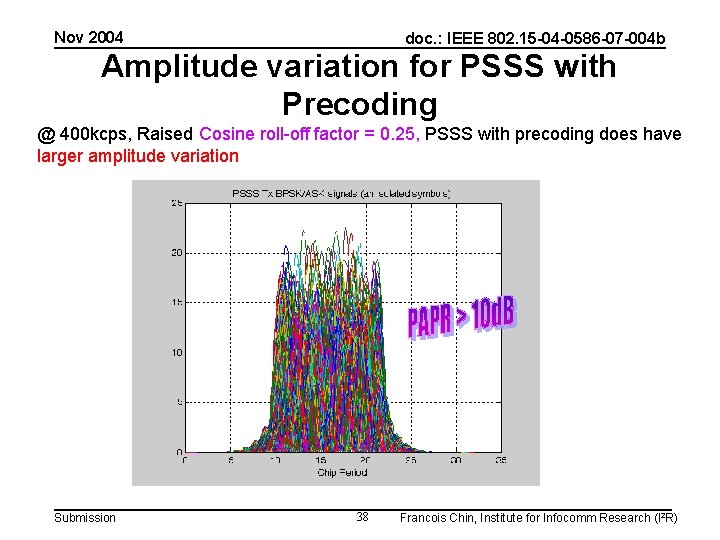

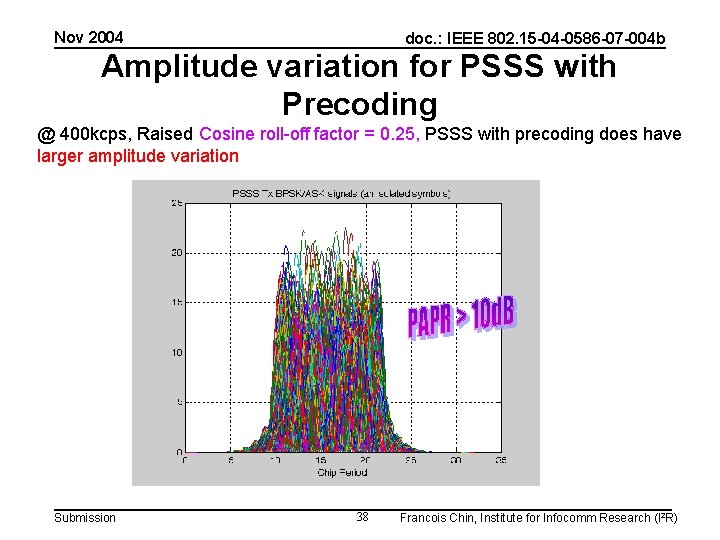

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b Amplitude variation for PSSS with Precoding @ 400 kcps, Raised Cosine roll-off factor = 0. 25, PSSS with precoding does have larger amplitude variation Submission 38 Francois Chin, Institute for Infocomm Research (I 2 R)

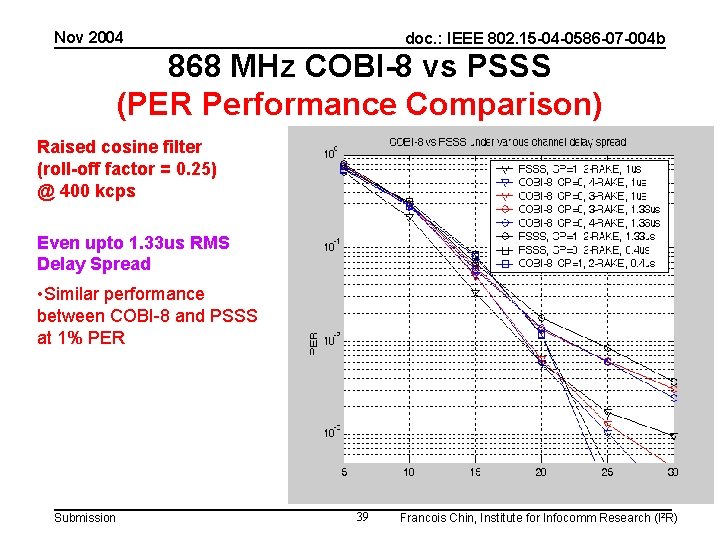

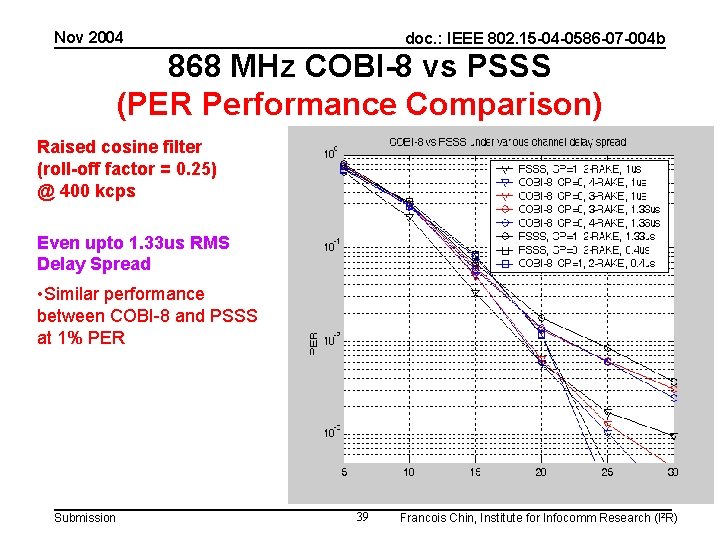

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b 868 MHz COBI-8 vs PSSS (PER Performance Comparison) Raised cosine filter (roll-off factor = 0. 25) @ 400 kcps Even upto 1. 33 us RMS Delay Spread • Similar performance between COBI-8 and PSSS at 1% PER Submission 39 Francois Chin, Institute for Infocomm Research (I 2 R)

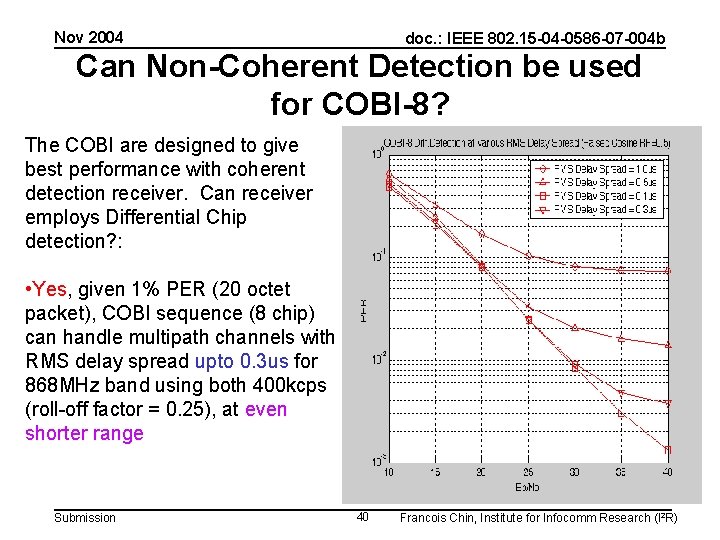

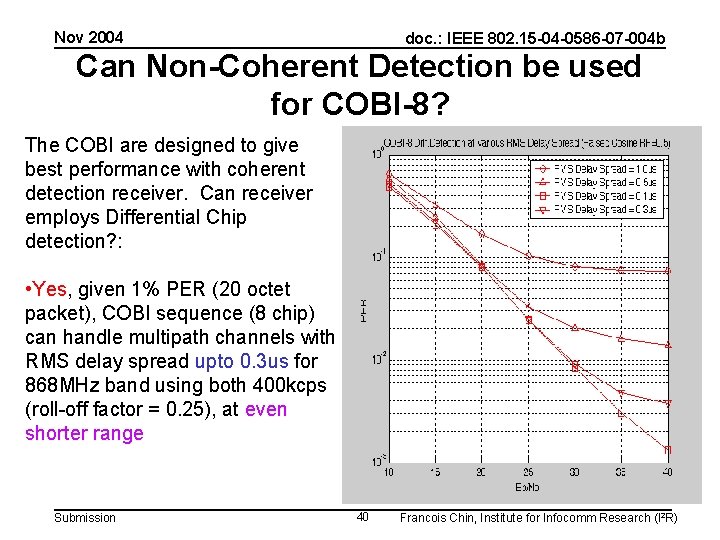

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b Can Non-Coherent Detection be used for COBI-8? The COBI are designed to give best performance with coherent detection receiver. Can receiver employs Differential Chip detection? : • Yes, given 1% PER (20 octet packet), COBI sequence (8 chip) can handle multipath channels with RMS delay spread upto 0. 3 us for 868 MHz band using both 400 kcps (roll-off factor = 0. 25), at even shorter range Submission 40 Francois Chin, Institute for Infocomm Research (I 2 R)

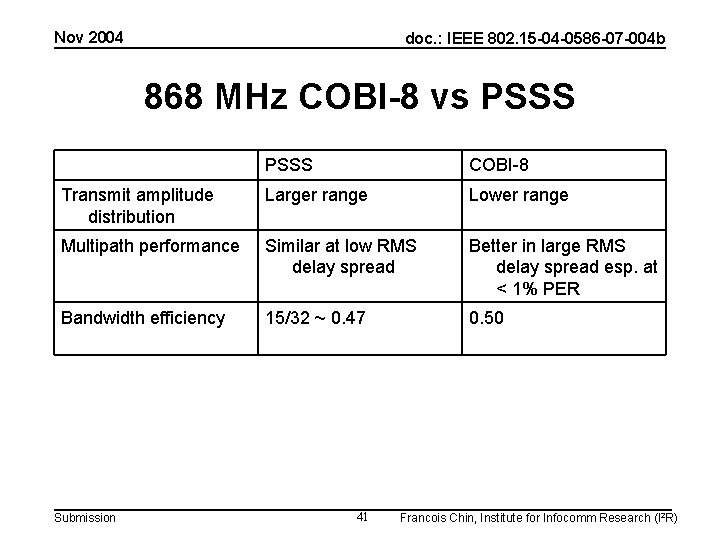

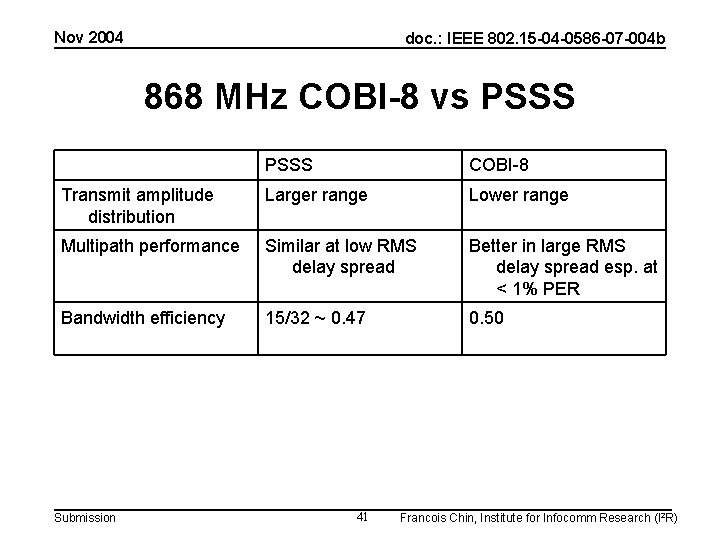

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b 868 MHz COBI-8 vs PSSS COBI-8 Transmit amplitude distribution Larger range Lower range Multipath performance Similar at low RMS delay spread Better in large RMS delay spread esp. at < 1% PER Bandwidth efficiency 15/32 ~ 0. 47 0. 50 Submission 41 Francois Chin, Institute for Infocomm Research (I 2 R)

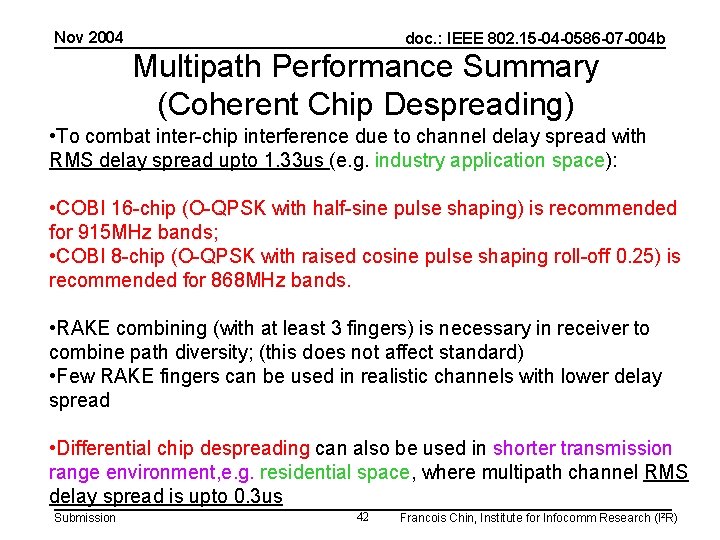

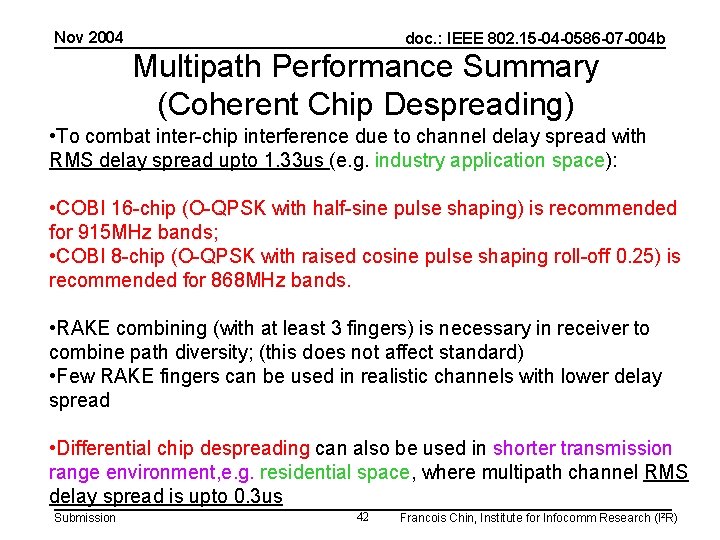

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b Multipath Performance Summary (Coherent Chip Despreading) • To combat inter-chip interference due to channel delay spread with RMS delay spread upto 1. 33 us (e. g. industry application space): • COBI 16 -chip (O-QPSK with half-sine pulse shaping) is recommended for 915 MHz bands; • COBI 8 -chip (O-QPSK with raised cosine pulse shaping roll-off 0. 25) is recommended for 868 MHz bands. • RAKE combining (with at least 3 fingers) is necessary in receiver to combine path diversity; (this does not affect standard) • Few RAKE fingers can be used in realistic channels with lower delay spread • Differential chip despreading can also be used in shorter transmission range environment, e. g. residential space, where multipath channel RMS delay spread is upto 0. 3 us Submission 42 Francois Chin, Institute for Infocomm Research (I 2 R)

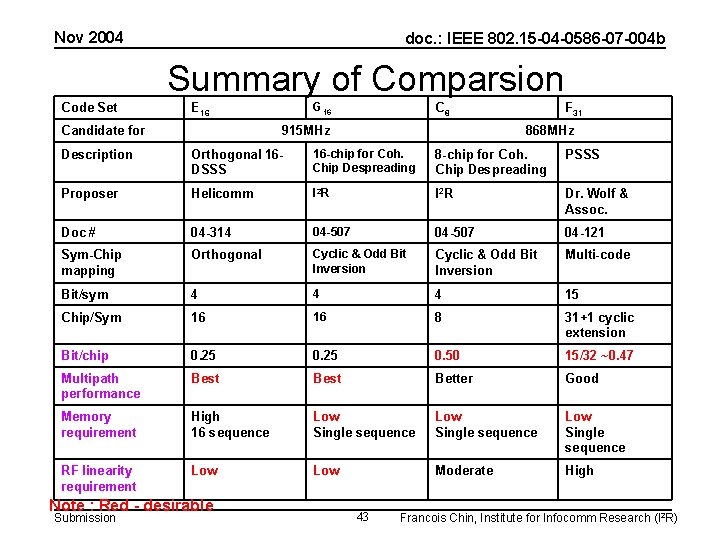

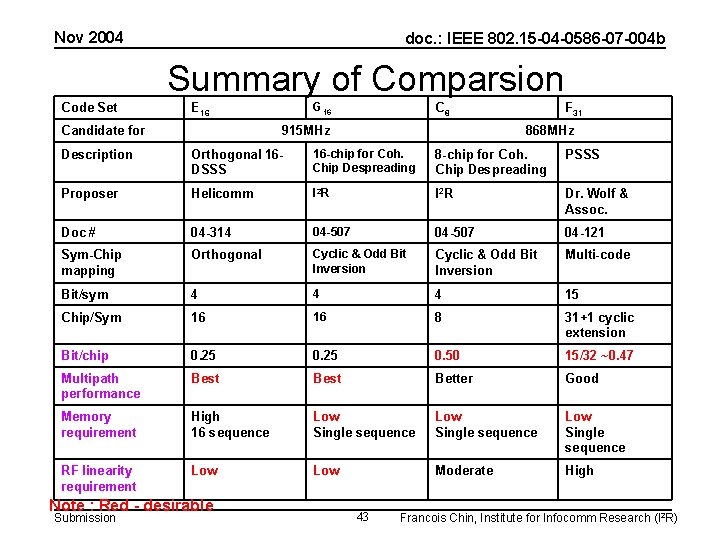

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b Summary of Comparsion Code Set G 16 E 16 Candidate for C 8 915 MHz F 31 868 MHz Description Orthogonal 16 DSSS 16 -chip for Coh. Chip Despreading 8 -chip for Coh. Chip Despreading PSSS Proposer Helicomm I 2 R Dr. Wolf & Assoc. Doc # 04 -314 04 -507 04 -121 Sym-Chip mapping Orthogonal Cyclic & Odd Bit Inversion Multi-code Bit/sym 4 4 4 15 Chip/Sym 16 16 8 31+1 cyclic extension Bit/chip 0. 25 0. 50 15/32 ~0. 47 Multipath performance Best Better Good Memory requirement High 16 sequence Low Single sequence RF linearity requirement Low Moderate High Note : Red - desirable Submission 43 Francois Chin, Institute for Infocomm Research (I 2 R)

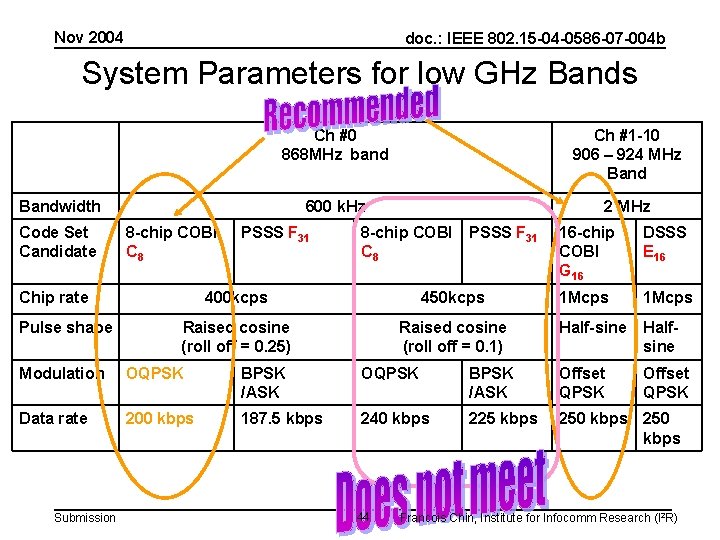

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b System Parameters for low GHz Bands Ch #0 868 MHz band Ch #1 -10 906 – 924 MHz Band 600 k. Hz 2 MHz Bandwidth Code Set Candidate 8 -chip COBI C 8 Chip rate Pulse shape PSSS F 31 8 -chip COBI C 8 PSSS F 31 400 kcps 450 kcps Raised cosine (roll off = 0. 25) Raised cosine (roll off = 0. 1) 16 -chip COBI G 16 DSSS E 16 1 Mcps Half-sine Halfsine Offset QPSK Modulation OQPSK BPSK /ASK Offset QPSK Data rate 200 kbps 187. 5 kbps 240 kbps 225 kbps 250 kbps Submission 44 Francois Chin, Institute for Infocomm Research (I 2 R)

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b Supporting Materials Submission 45 Francois Chin, Institute for Infocomm Research (I 2 R)

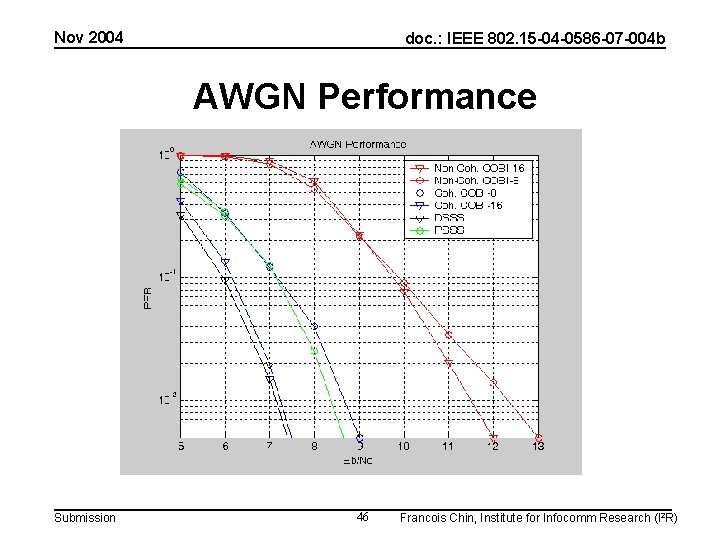

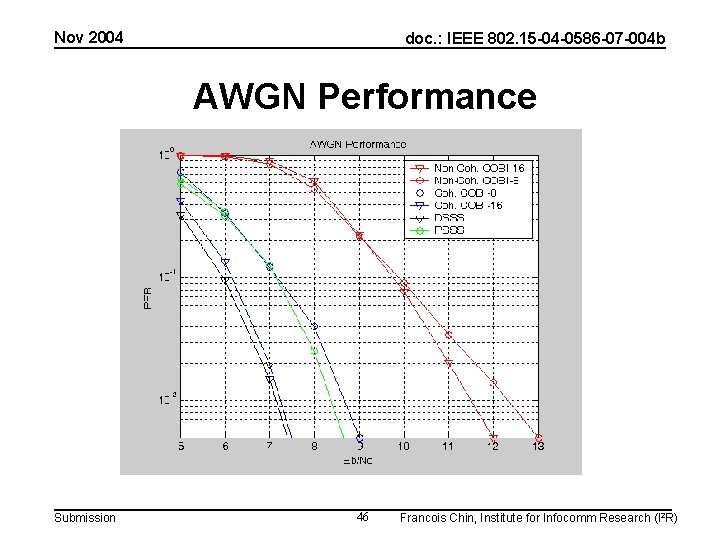

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b AWGN Performance Submission 46 Francois Chin, Institute for Infocomm Research (I 2 R)

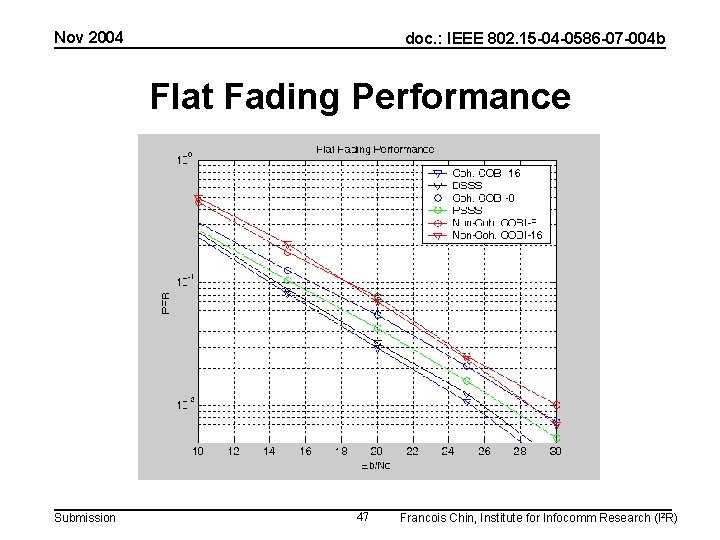

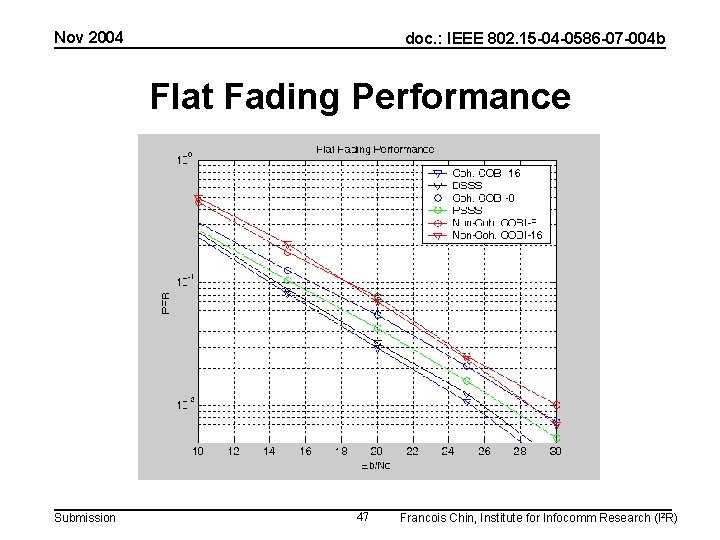

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b Flat Fading Performance Submission 47 Francois Chin, Institute for Infocomm Research (I 2 R)

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b Coherent Receiver Multipath Performance What leads to Multipath robustness? Frequency selectivity leads to Inter-chip interference, and that is the killer…. To overcome, code must have good autocorrelation properties, i. e. low sidelodes Submission 48 Francois Chin, Institute for Infocomm Research (I 2 R)

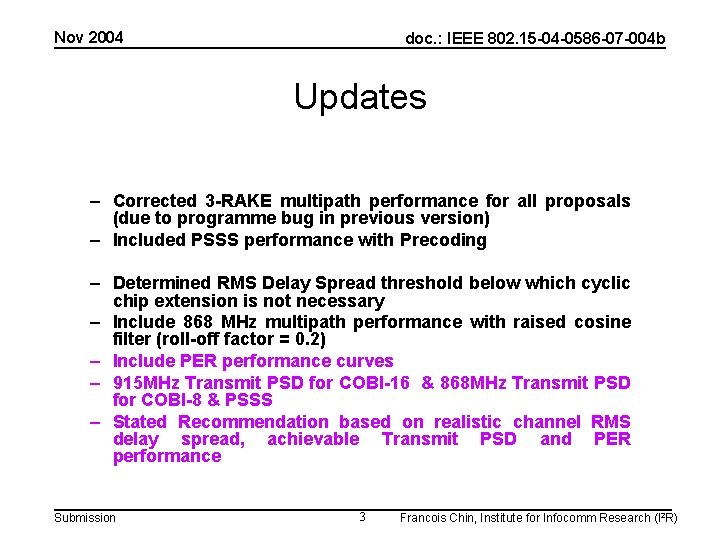

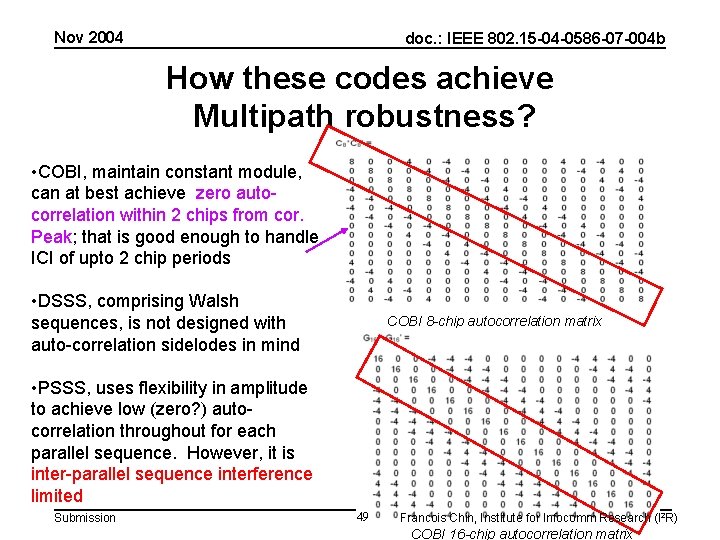

Nov 2004 doc. : IEEE 802. 15 -04 -0586 -07 -004 b How these codes achieve Multipath robustness? • COBI, maintain constant module, can at best achieve zero autocorrelation within 2 chips from cor. Peak; that is good enough to handle ICI of upto 2 chip periods • DSSS, comprising Walsh sequences, is not designed with auto-correlation sidelodes in mind COBI 8 -chip autocorrelation matrix • PSSS, uses flexibility in amplitude to achieve low (zero? ) autocorrelation throughout for each parallel sequence. However, it is inter-parallel sequence interference limited Submission 49 Francois Chin, Institute for Infocomm Research (I 2 R) COBI 16 -chip autocorrelation matrix