Improving Memristor Memory with Sneak Current Sharing Manjunath

- Slides: 26

Improving Memristor Memory with Sneak Current Sharing Manjunath Shevgoor, Rajeev Balasubramonian, Naveen Muralimanohar, Yoocharn Jeon University of Utah, HP Labs Improving Memristor Memory with Sneak Current Sharing 33 rd IEEE International Conference on Computer Design ICCD 2015 1

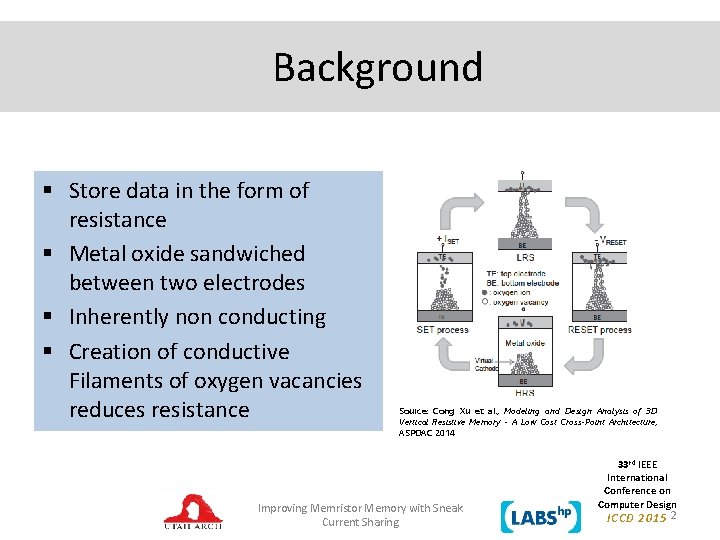

Background § Store data in the form of resistance § Metal oxide sandwiched between two electrodes § Inherently non conducting § Creation of conductive Filaments of oxygen vacancies reduces resistance Source: Cong Xu et al. , Modeling and Design Analysis of 3 D Vertical Resistive Memory - A Low Cost Cross-Point Architecture, ASPDAC 2014 Improving Memristor Memory with Sneak Current Sharing 33 rd IEEE International Conference on Computer Design ICCD 2015 2

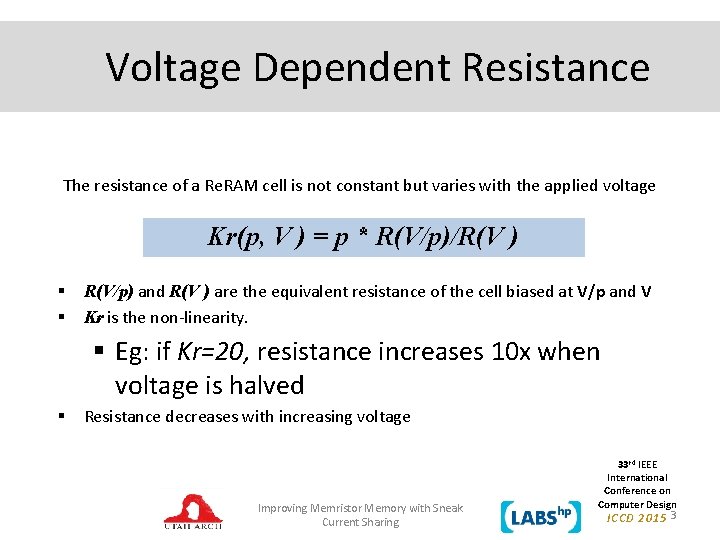

Voltage Dependent Resistance The resistance of a Re. RAM cell is not constant but varies with the applied voltage Kr(p, V ) = p * R(V/p)/R(V ) § § R(V/p) and R(V ) are the equivalent resistance of the cell biased at V/p and V Kr is the non-linearity. § Eg: if Kr=20, resistance increases 10 x when voltage is halved § Resistance decreases with increasing voltage Improving Memristor Memory with Sneak Current Sharing 33 rd IEEE International Conference on Computer Design ICCD 2015 3

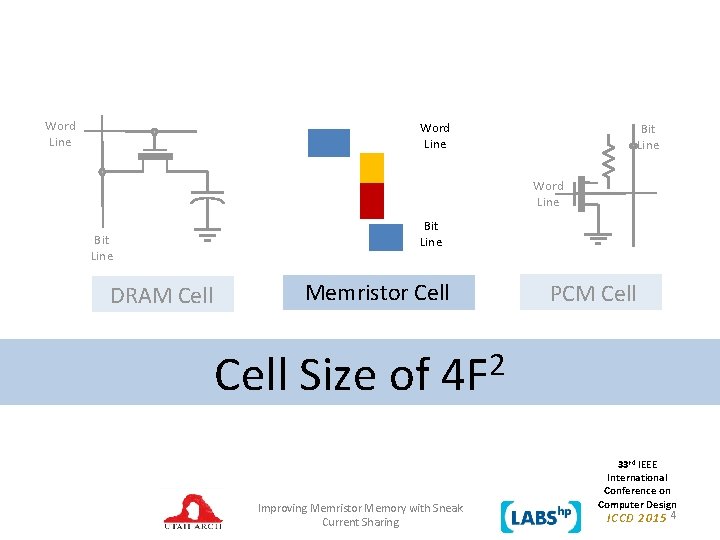

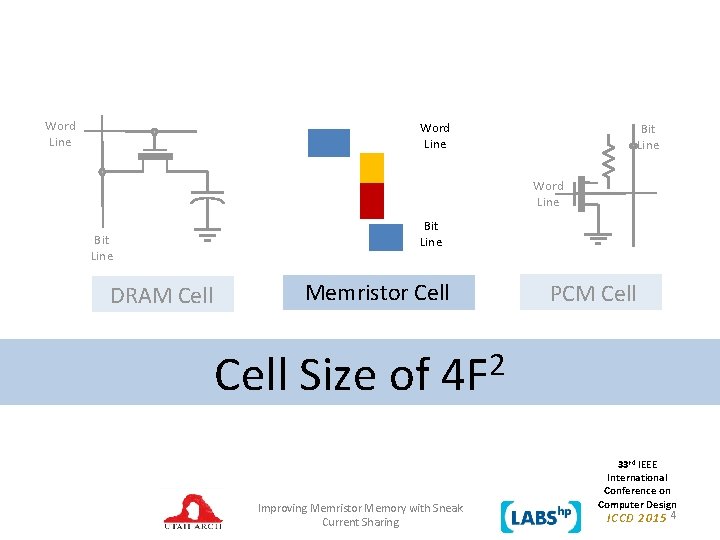

Word Line Bit Line DRAM Cell Bit Line Memristor Cell Size of PCM Cell 2 4 F Improving Memristor Memory with Sneak Current Sharing 33 rd IEEE International Conference on Computer Design ICCD 2015 4

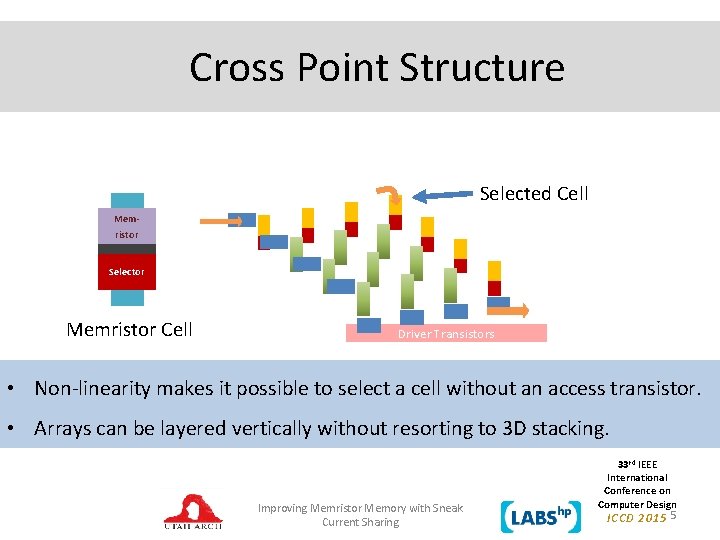

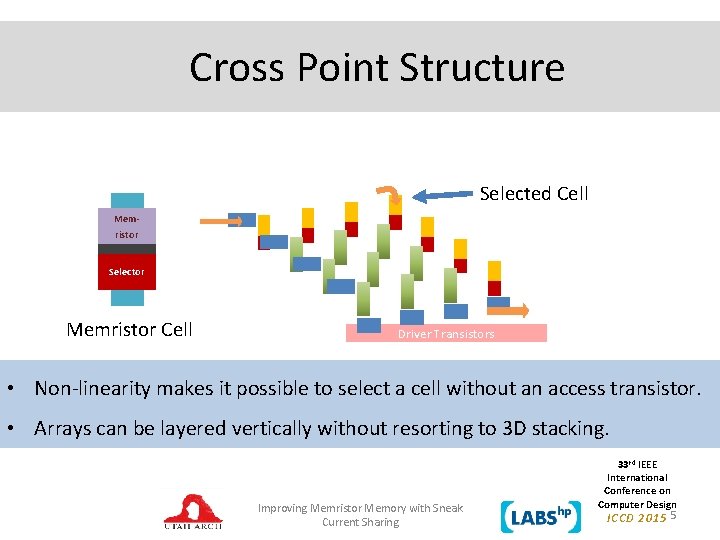

Cross Point Structure Selected Cell Memristor Selector Memristor Cell Driver Transistors • Non-linearity makes it possible to select a cell without an access transistor. • Arrays can be layered vertically without resorting to 3 D stacking. Improving Memristor Memory with Sneak Current Sharing 33 rd IEEE International Conference on Computer Design ICCD 2015 5

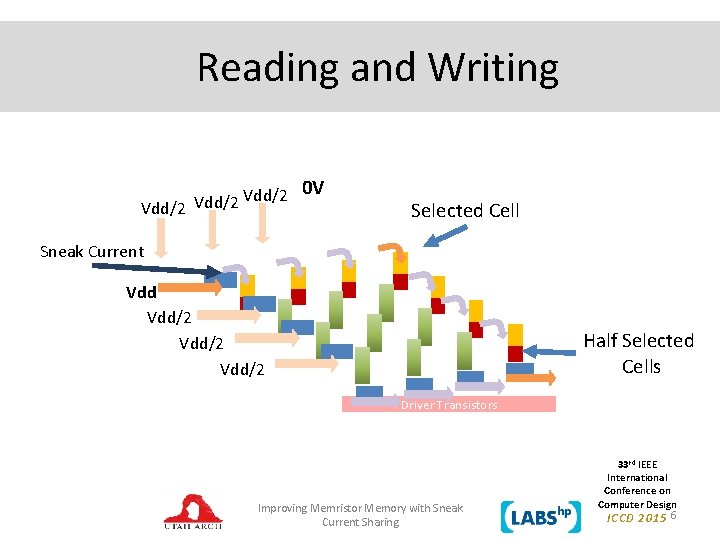

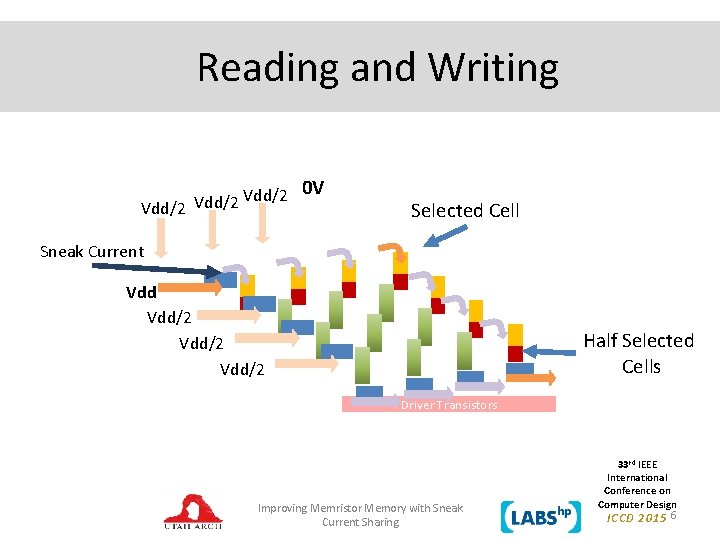

Reading and Writing Vdd/2 0 V Vdd/2 Selected Cell Sneak Current Vdd/2 Half Selected Cells Driver Transistors Improving Memristor Memory with Sneak Current Sharing 33 rd IEEE International Conference on Computer Design ICCD 2015 6

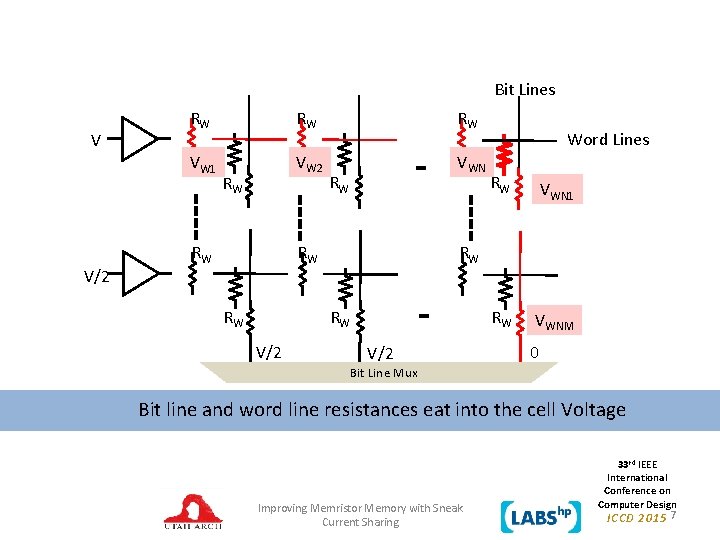

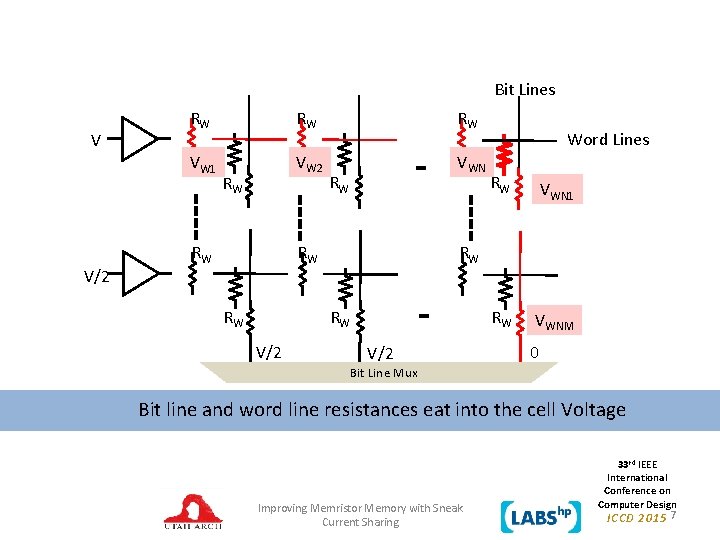

Bit Lines V V/2 RW RW RW VW 1 VW 2 VWN RW RW V/2 RW VWN 1 RW VWNM RW RW RW Word Lines V/2 0 Bit Line Mux Bit line and word line resistances eat into the cell Voltage Improving Memristor Memory with Sneak Current Sharing 33 rd IEEE International Conference on Computer Design ICCD 2015 7

EFFECTS OF ILEAK Improving Memristor Memory with Sneak Current Sharing 33 rd IEEE International Conference on Computer Design ICCD 2015 8

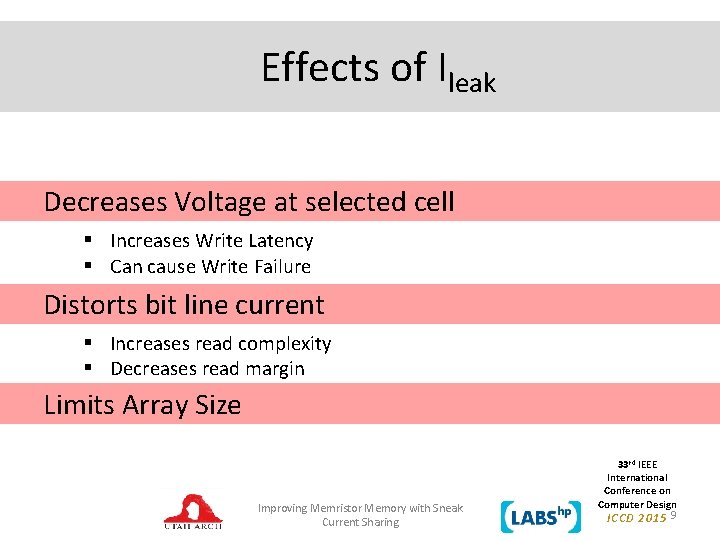

Effects of Ileak Decreases Voltage at selected cell § Increases Write Latency § Can cause Write Failure Distorts bit line current § Increases read complexity § Decreases read margin Limits Array Size Improving Memristor Memory with Sneak Current Sharing 33 rd IEEE International Conference on Computer Design ICCD 2015 9

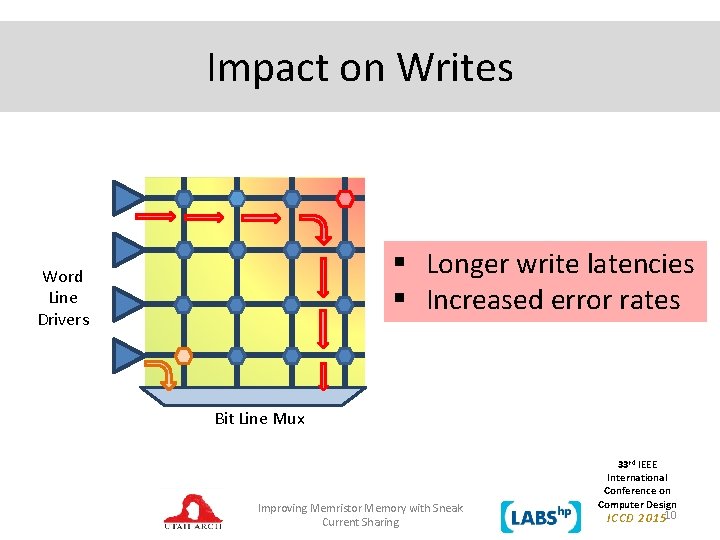

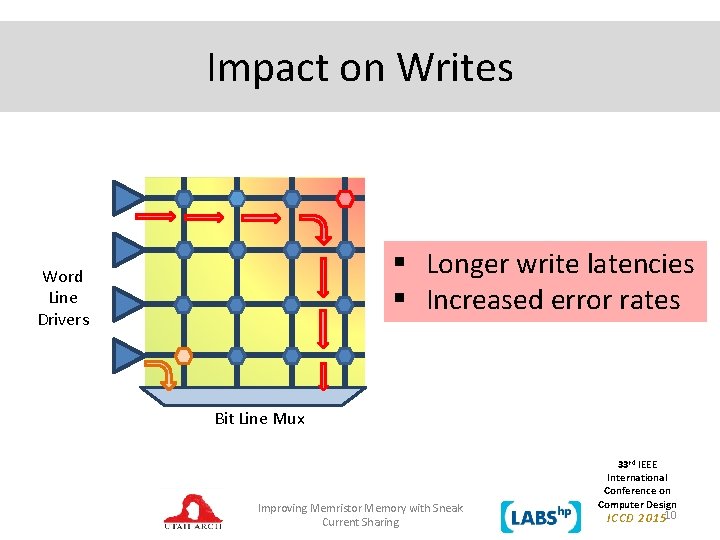

Impact on Writes § Longer write latencies § Increased error rates Word Line Drivers Bit Line Mux Improving Memristor Memory with Sneak Current Sharing 33 rd IEEE International Conference on Computer Design ICCD 201510

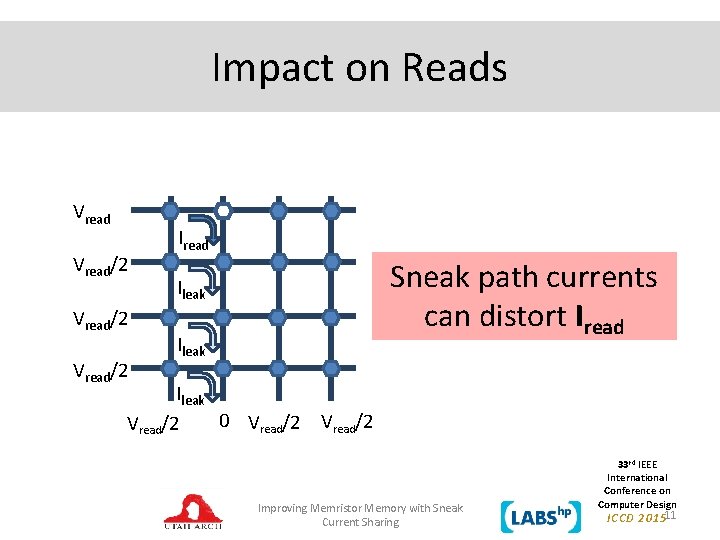

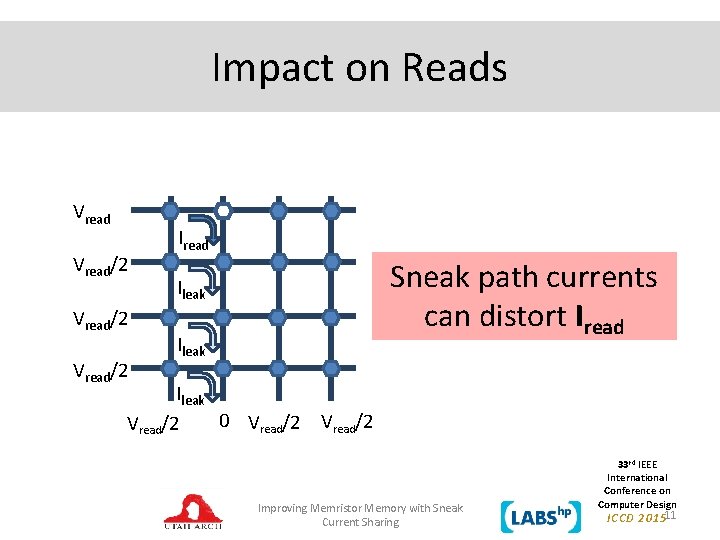

Impact on Reads Vread/2 Iread Sneak path currents can distort Iread Ileak 0 Vread/2 Improving Memristor Memory with Sneak Current Sharing 33 rd IEEE International Conference on Computer Design ICCD 201511

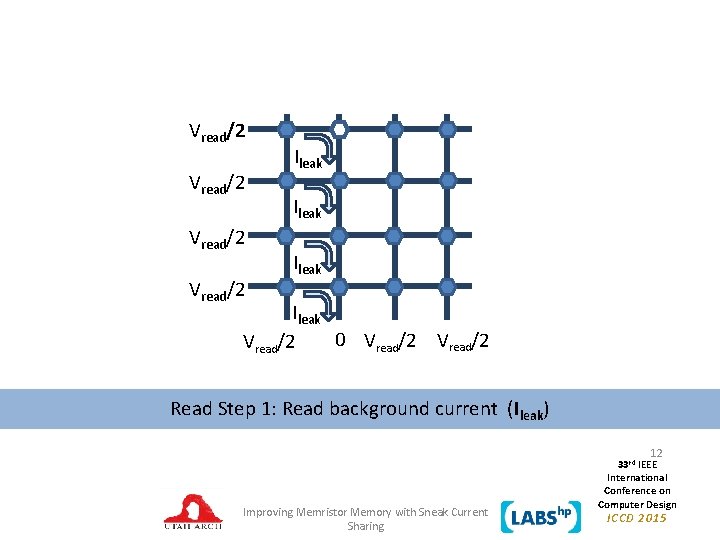

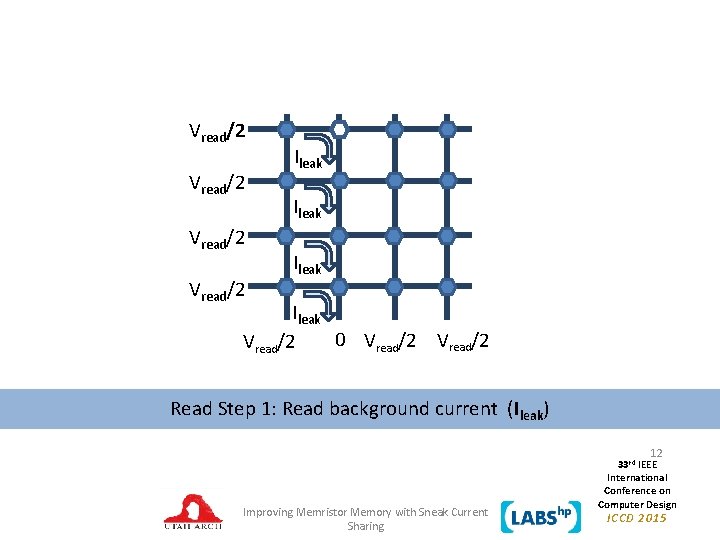

Vread/2 Ileak 0 Vread/2 Read Step 1: Read background current (Ileak) 12 Improving Memristor Memory with Sneak Current Sharing 33 rd IEEE International Conference on Computer Design ICCD 2015

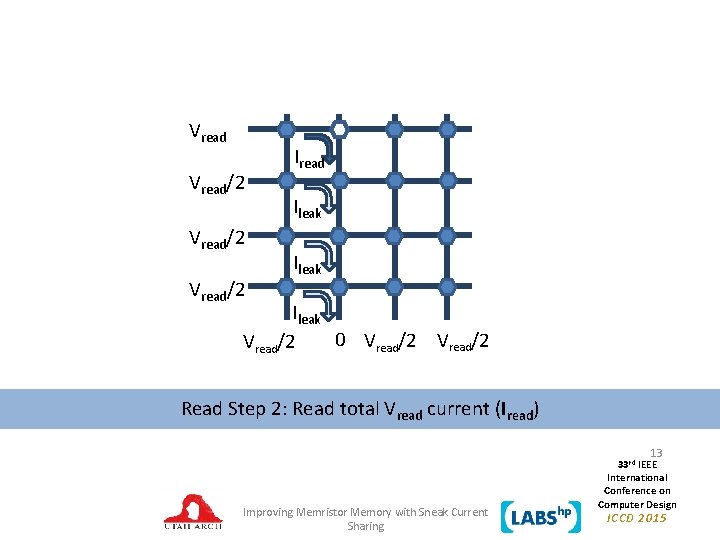

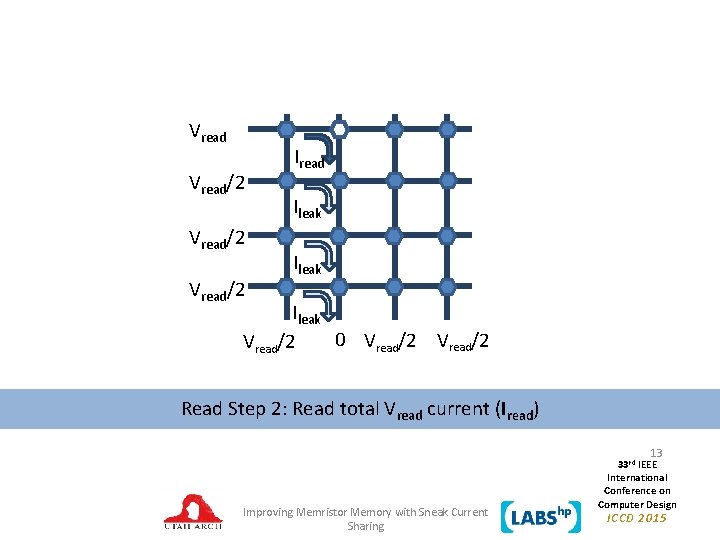

Vread/2 Vread/2 Iread Ileak 0 Vread/2 Read Step 2: Read total Vread current (Iread) 13 Improving Memristor Memory with Sneak Current Sharing 33 rd IEEE International Conference on Computer Design ICCD 2015

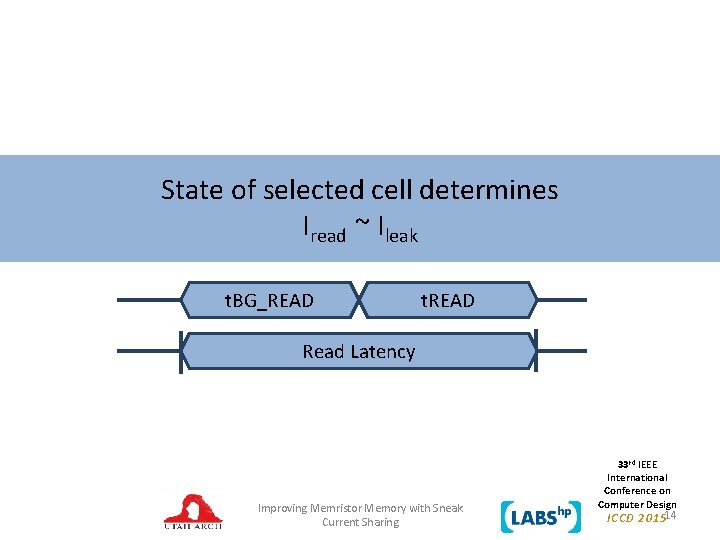

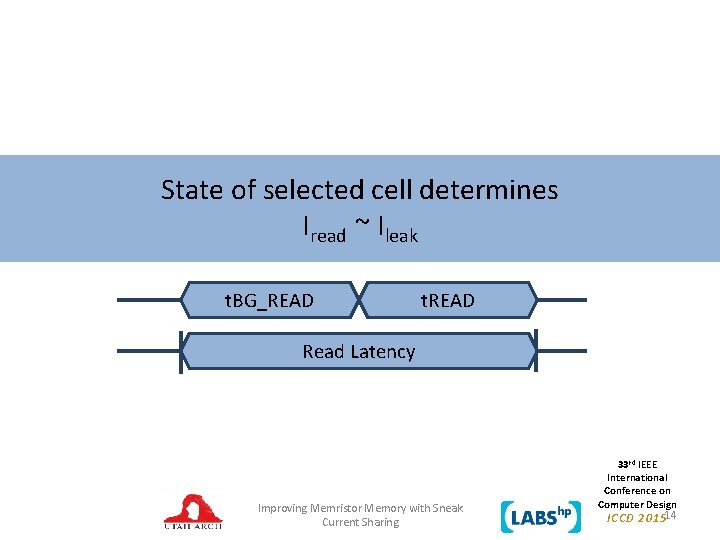

State of selected cell determines Iread ~ Ileak t. BG_READ t. READ Read Latency Improving Memristor Memory with Sneak Current Sharing 33 rd IEEE International Conference on Computer Design ICCD 201514

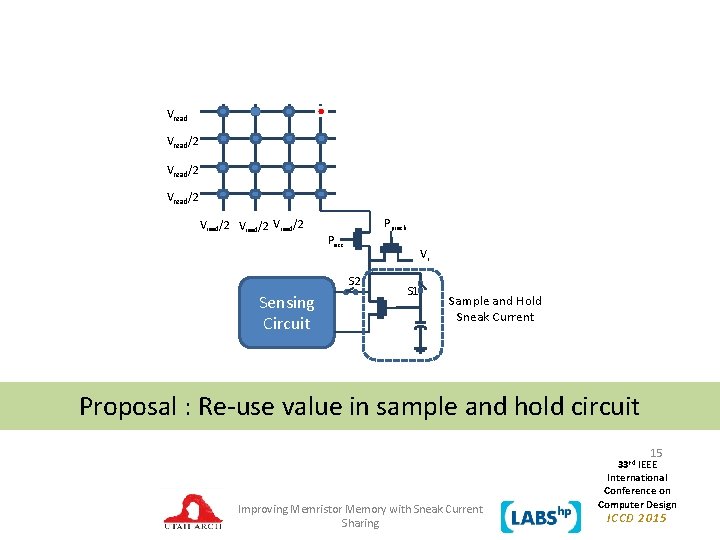

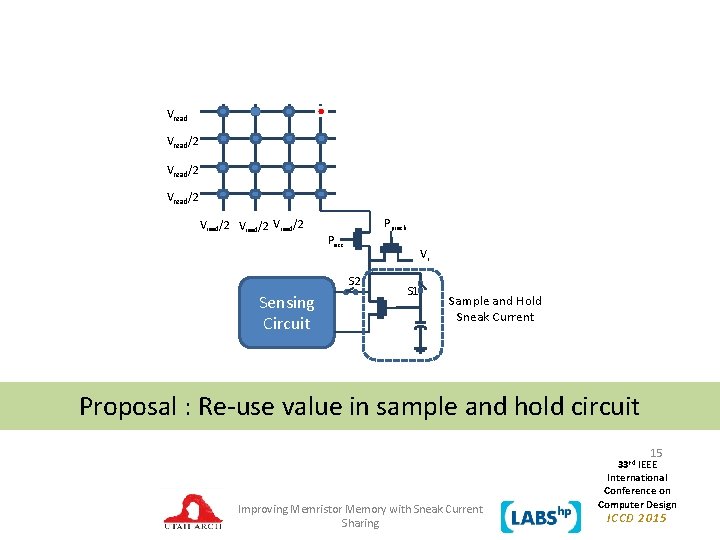

Vread/2 Vread/2 Pprech Pacc Vr S 2 Sensing Circuit S 1 Sample and Hold Sneak Current Proposal : Re-use value in sample and hold circuit 15 Improving Memristor Memory with Sneak Current Sharing 33 rd IEEE International Conference on Computer Design ICCD 2015

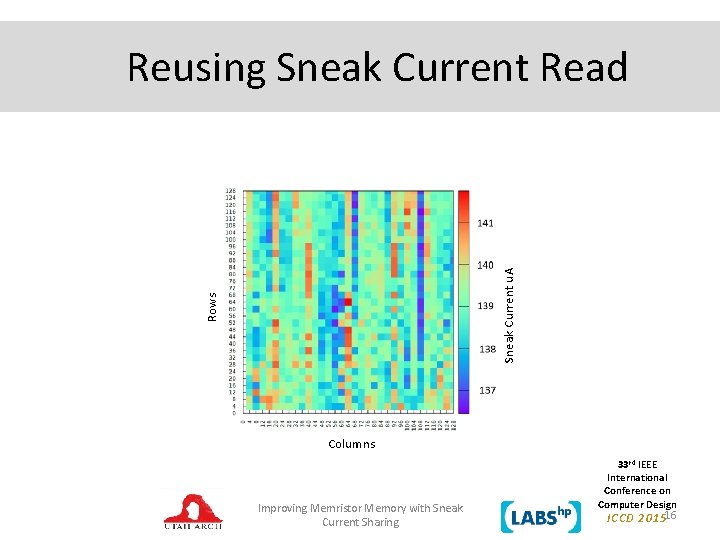

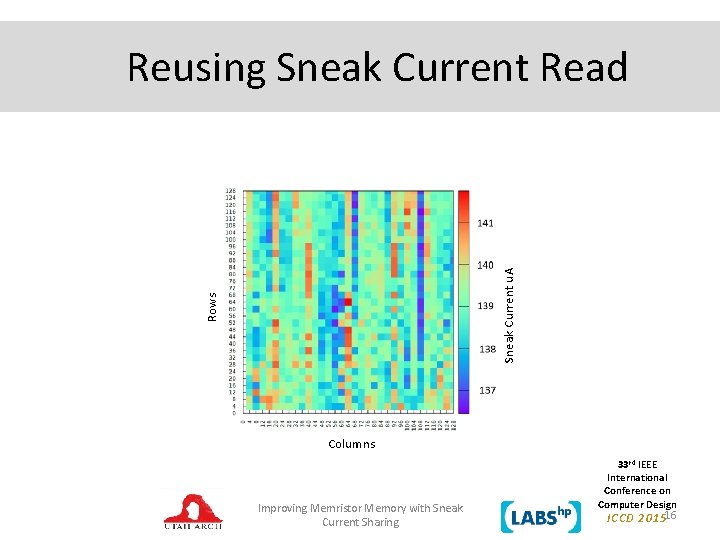

Rows Sneak Current u. A Reusing Sneak Current Read Columns Improving Memristor Memory with Sneak Current Sharing 33 rd IEEE International Conference on Computer Design ICCD 201516

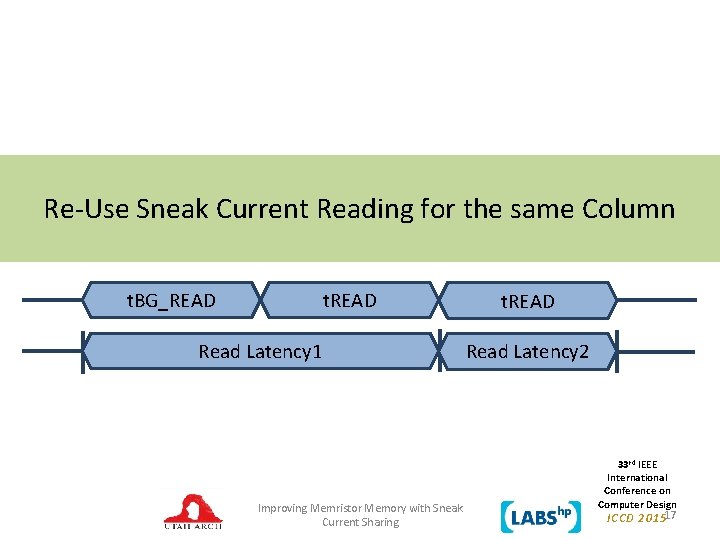

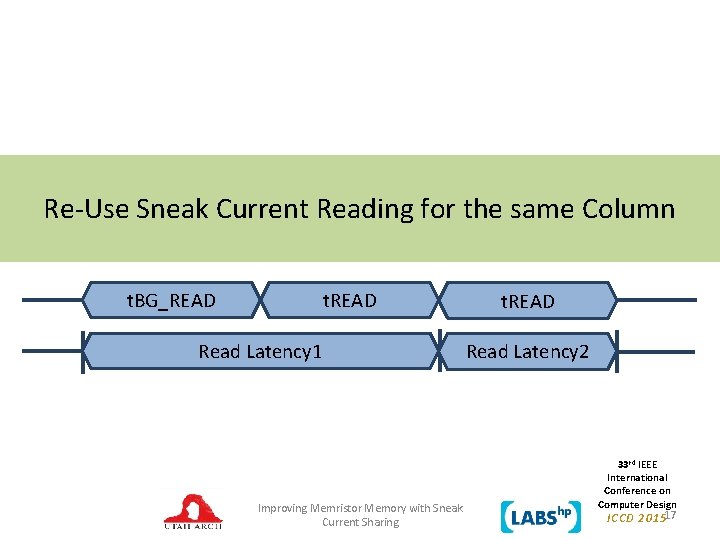

Re-Use Sneak Current Reading for the same Column t. BG_READ t. READ Read Latency 1 Improving Memristor Memory with Sneak Current Sharing t. READ Read Latency 2 33 rd IEEE International Conference on Computer Design ICCD 201517

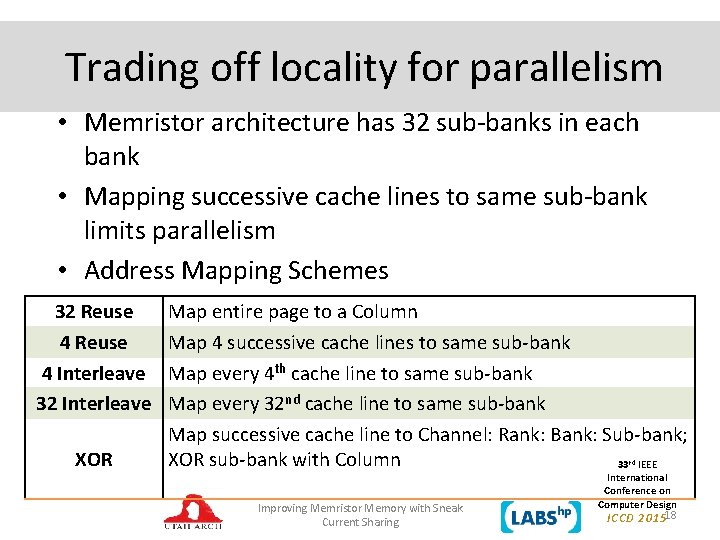

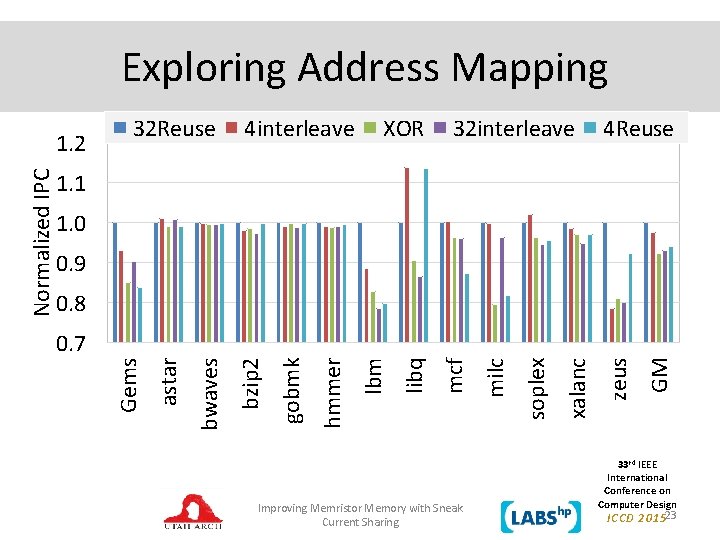

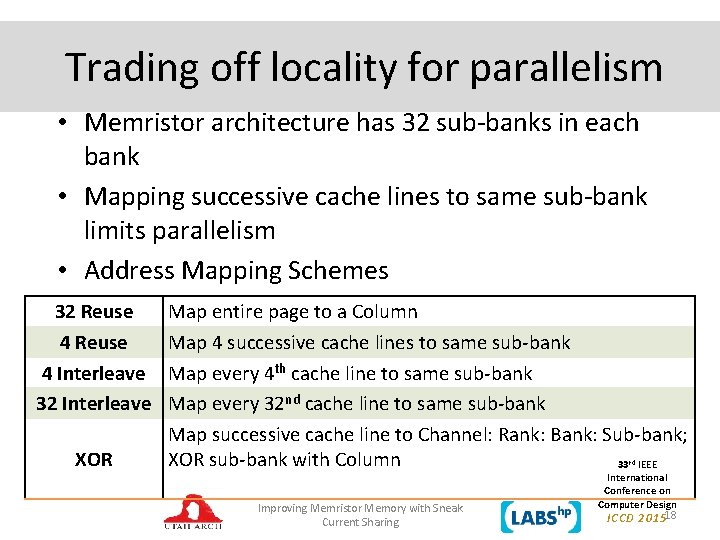

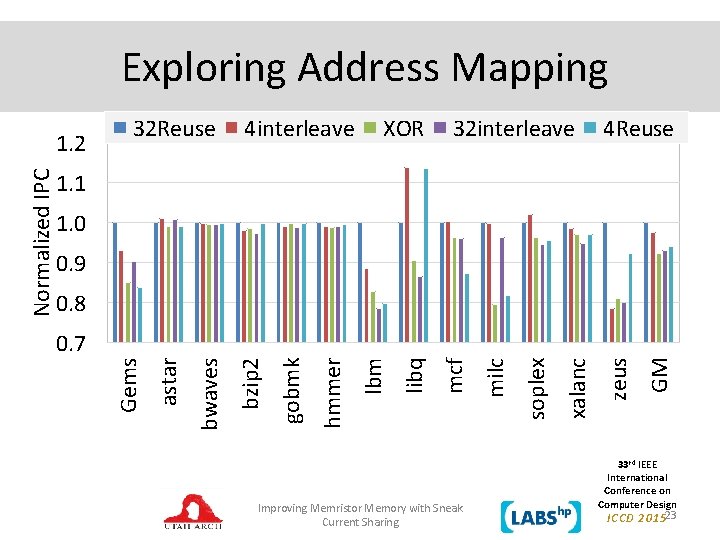

Trading off locality for parallelism • Memristor architecture has 32 sub-banks in each bank • Mapping successive cache lines to same sub-bank limits parallelism • Address Mapping Schemes 32 Reuse 4 Interleave 32 Interleave XOR Map entire page to a Column Map 4 successive cache lines to same sub-bank Map every 4 th cache line to same sub-bank Map every 32 nd cache line to same sub-bank Map successive cache line to Channel: Rank: Bank: Sub-bank; XOR sub-bank with Column 33 IEEE rd Improving Memristor Memory with Sneak Current Sharing International Conference on Computer Design ICCD 201518

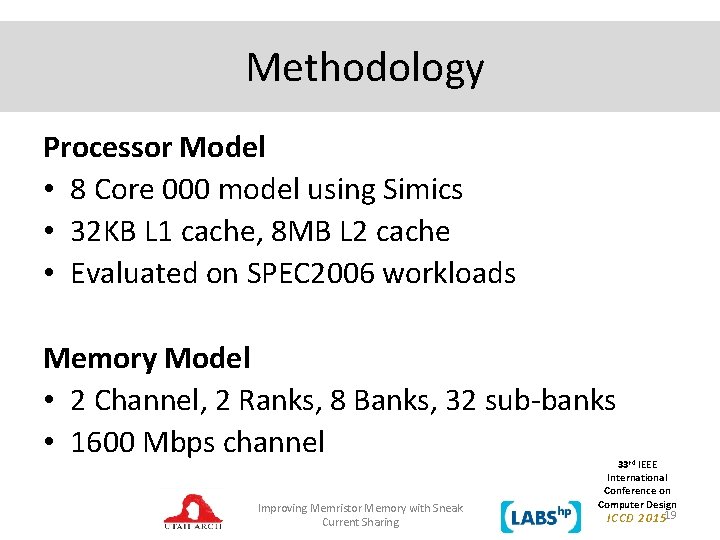

Methodology Processor Model • 8 Core 000 model using Simics • 32 KB L 1 cache, 8 MB L 2 cache • Evaluated on SPEC 2006 workloads Memory Model • 2 Channel, 2 Ranks, 8 Banks, 32 sub-banks • 1600 Mbps channel Improving Memristor Memory with Sneak Current Sharing 33 rd IEEE International Conference on Computer Design ICCD 201519

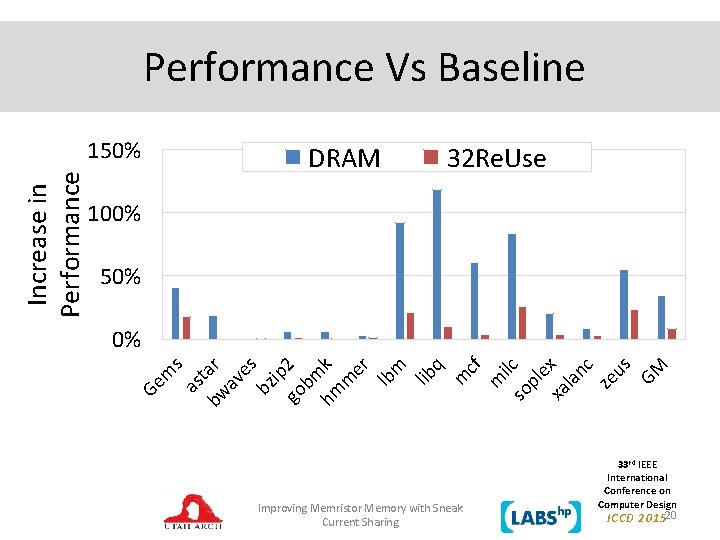

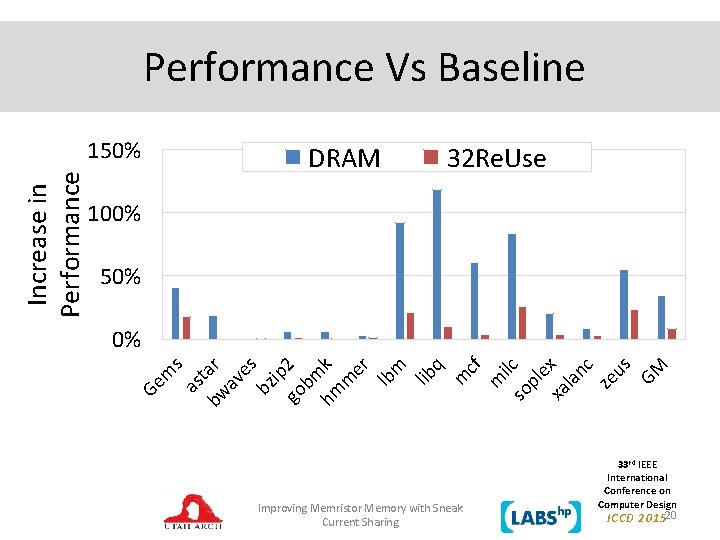

Performance Vs Baseline DRAM 32 Re. Use 100% 50% t bw ar av es bz ip go 2 bm hm k m er lb m lib q m cf m ilc so pl ex xa la nc ze us GM as m s 0% Ge Increase in Performance 150% Improving Memristor Memory with Sneak Current Sharing 33 rd IEEE International Conference on Computer Design ICCD 201520

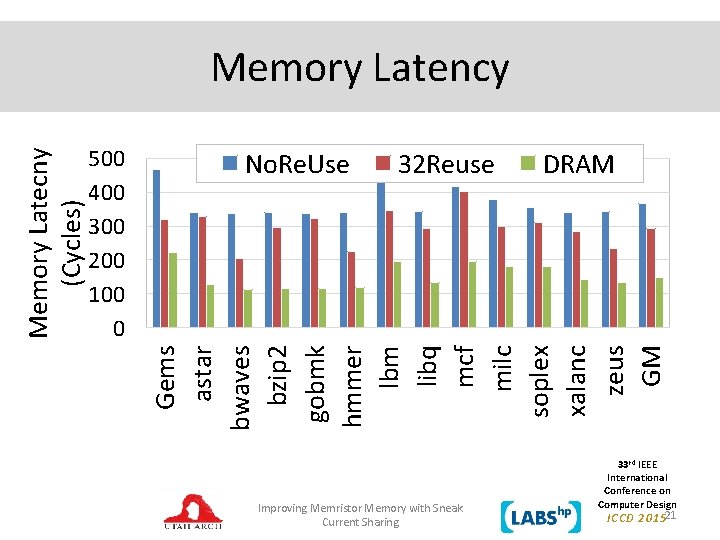

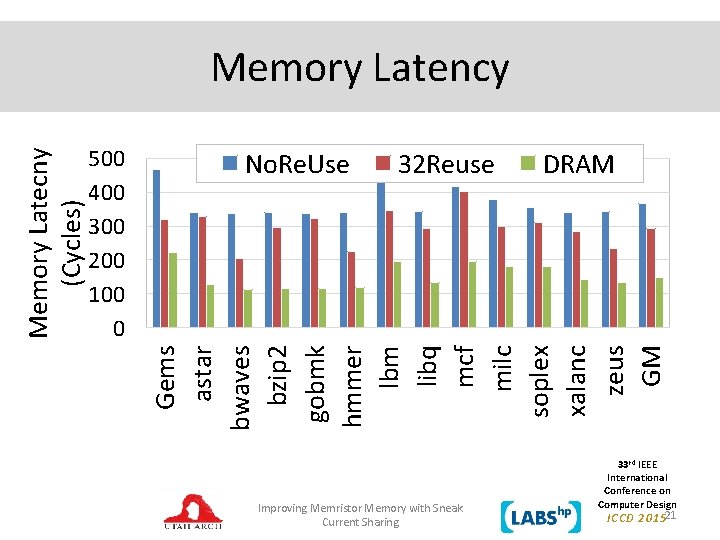

500 400 300 200 100 0 No. Re. Use 32 Reuse DRAM Gems astar bwaves bzip 2 gobmk hmmer lbm libq mcf milc soplex xalanc zeus GM Memory Latecny (Cycles) Memory Latency Improving Memristor Memory with Sneak Current Sharing 33 rd IEEE International Conference on Computer Design ICCD 201521

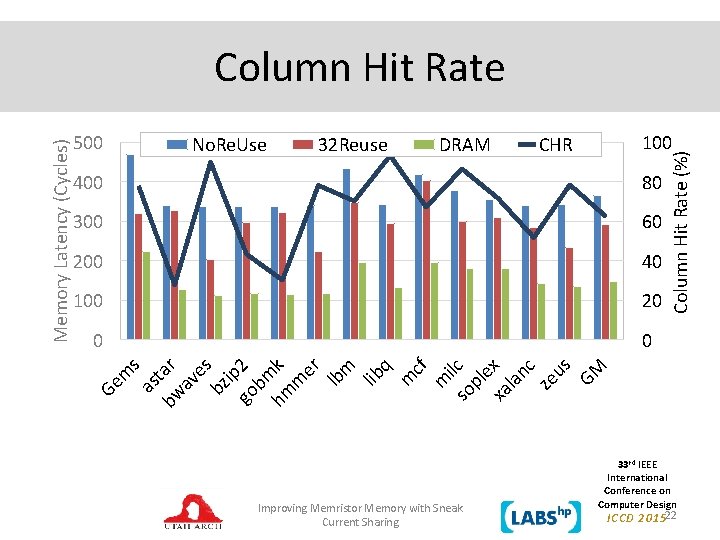

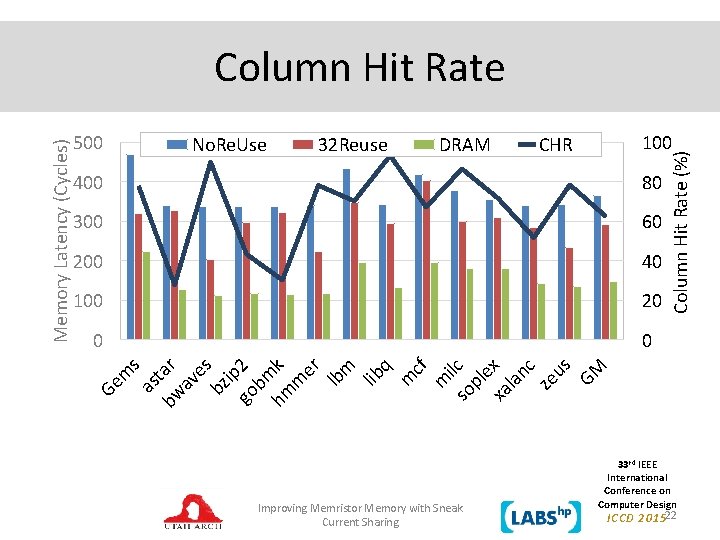

No. Re. Use 32 Reuse DRAM 100 CHR 400 80 300 60 200 40 100 20 0 s as bw tar av es bz ip go 2 bm hm k m er lb m lib q m cf m i so lc pl e xa x la nc ze us GM 0 Column Hit Rate (%) 500 Ge m Memory Latency (Cycles) Column Hit Rate Improving Memristor Memory with Sneak Current Sharing 33 rd IEEE International Conference on Computer Design ICCD 201522

Exploring Address Mapping 4 interleave XOR 32 interleave 4 Reuse 1. 1 1. 0 0. 9 0. 8 Improving Memristor Memory with Sneak Current Sharing GM zeus xalanc soplex milc mcf libq lbm hmmer gobmk bzip 2 bwaves astar 0. 7 Gems Normalized IPC 1. 2 32 Reuse 33 rd IEEE International Conference on Computer Design ICCD 201523

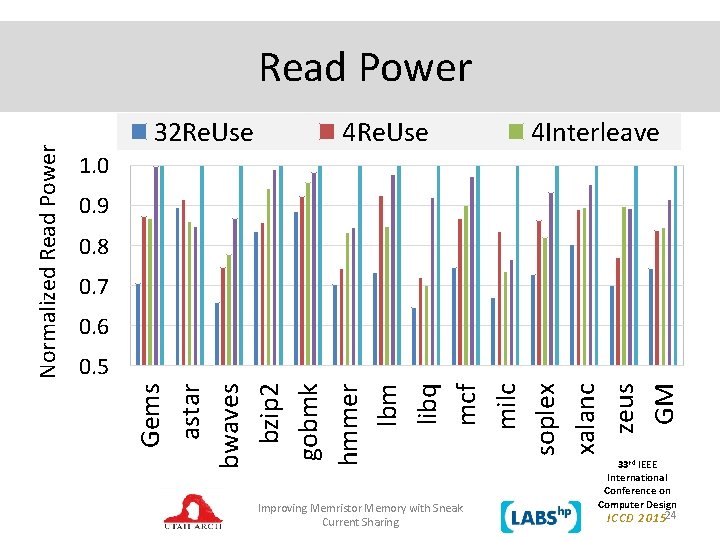

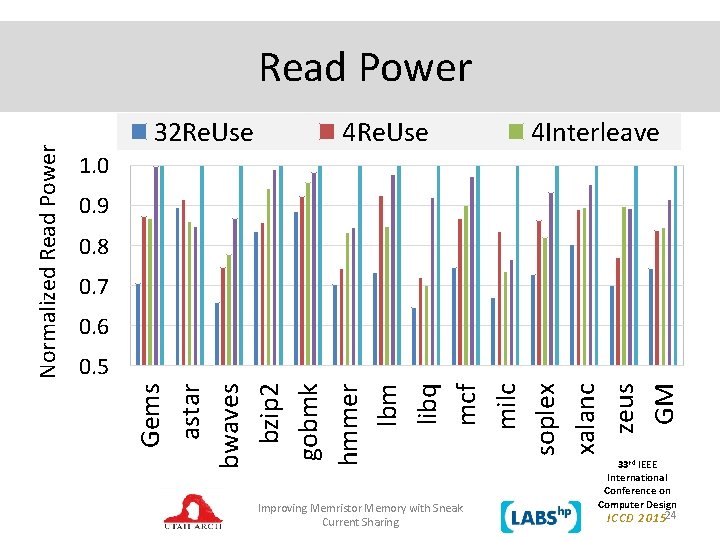

32 Re. Use 4 Interleave 1. 0 0. 9 0. 8 0. 7 0. 6 0. 5 Gems astar bwaves bzip 2 gobmk hmmer lbm libq mcf milc soplex xalanc zeus GM Normalized Read Power Improving Memristor Memory with Sneak Current Sharing 33 rd IEEE International Conference on Computer Design ICCD 201524

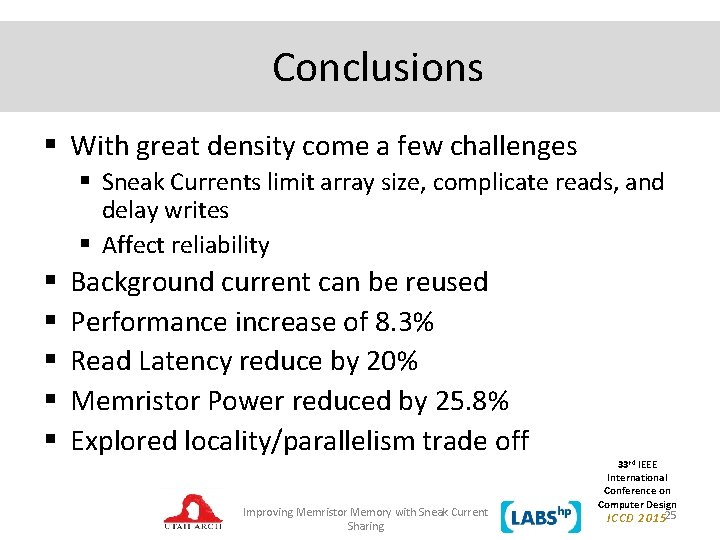

Conclusions § With great density come a few challenges § Sneak Currents limit array size, complicate reads, and delay writes § Affect reliability § § § Background current can be reused Performance increase of 8. 3% Read Latency reduce by 20% Memristor Power reduced by 25. 8% Explored locality/parallelism trade off Improving Memristor Memory with Sneak Current Sharing 33 rd IEEE International Conference on Computer Design ICCD 201525

THANK YOU Improving Memristor Memory with Sneak Current Sharing 33 rd IEEE International Conference on Computer Design ICCD 201526