Implementation of Logical and Memory Functions with Memristor

![The Architecture of a Classical Cellular Nonlinear Network (CNN) • CNN [Chu 88]: spatially-discrete The Architecture of a Classical Cellular Nonlinear Network (CNN) • CNN [Chu 88]: spatially-discrete](https://slidetodoc.com/presentation_image_h/0515d0cbe36a7c8983d9b477d8d164f3/image-3.jpg)

- Slides: 18

Implementation of Logical and Memory Functions with Memristor Cellular Nonlinear Networks Alon Ascoli 1, Ioannis Messaris 1, Ahmet Samil Demirkol 1, Ronald Tetzlaff 1, Leon Chua 2, Dalibor Biolek 3, Viera Biolková 4, and Zdenek Kolka 4 1 Chair of Fundamentals of Electrical Engineering, Institute of Circuits and Systems, Faculty of Electrical and Computer Engineering, Technische Universität Dresden, Germany 2 Department of Electrical Engineering and Computer Sciences, University of California Berkeley, California, USA 3 4 Department of Microelectronics, Brno University of Technology, Brno, Czech Republic Department of Radio Electronics, Brno University of Technology, Brno, Czech Republic 07 -10 September 2020, Sofia, Bulgaria

Presentation outline • Cellular Nonlinear Networks (CNNs) • Classical DRM Investigation and Design Tool for CNNs • The Memristor CNN (M-CNN) Image Memprocessing Paradigm • MCNNs with Bistable-like or Analogue Dynamic Memristors • Classical or Extended DRM Tool for M-CNN Gene Synthesis and Analysis • Application to Logical Mem-Computations with Binary Image Operands

![The Architecture of a Classical Cellular Nonlinear Network CNN CNN Chu 88 spatiallydiscrete The Architecture of a Classical Cellular Nonlinear Network (CNN) • CNN [Chu 88]: spatially-discrete](https://slidetodoc.com/presentation_image_h/0515d0cbe36a7c8983d9b477d8d164f3/image-3.jpg)

The Architecture of a Classical Cellular Nonlinear Network (CNN) • CNN [Chu 88]: spatially-discrete collection of continuous-time nonlinear dynamic cells • Each CNN cell has a state, an input, and an output 1, 1 The time evolution of the cell states toward prescribed equilibria lies at the basis of a huge library of CNN-based computations 1, 6 3, 4 inputs and outputs from neighbours self input and self output 6, 1 [Chu 88] L. O. Chua and L. Yang, “Cellular Neural Networks: Theory”, IEEE Trans. on CAS–I, vol. 35, no. 10, pp. 1257– 1272, 1988 6, 6

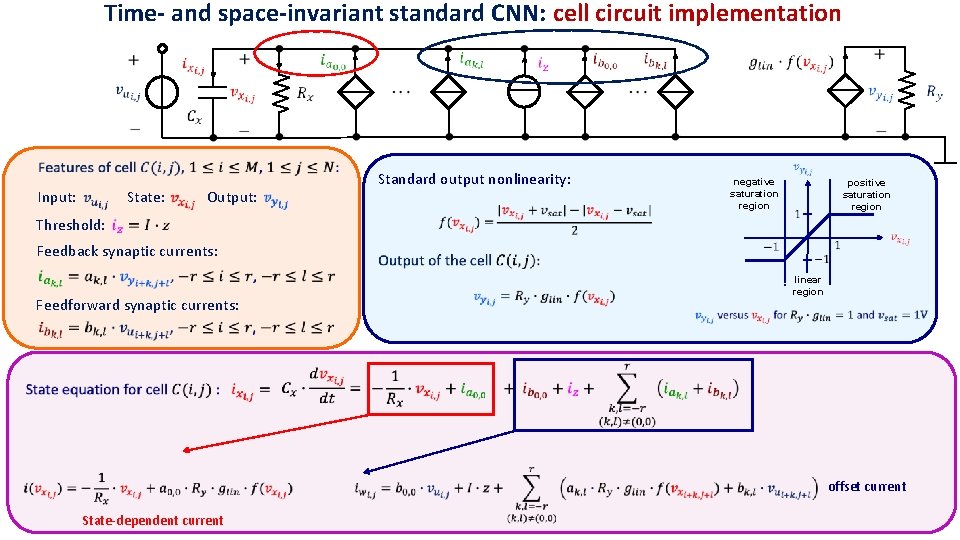

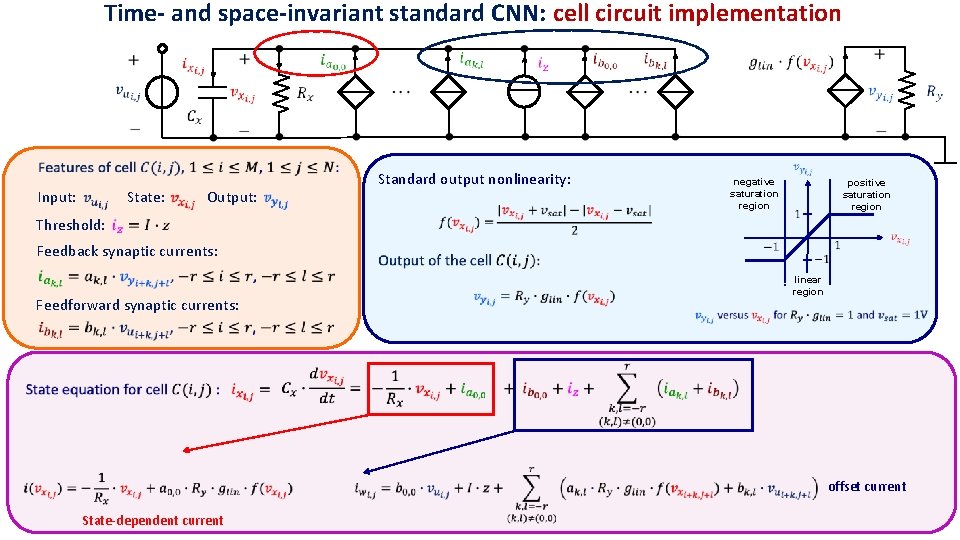

Time- and space-invariant standard CNN: cell circuit implementation Input: State: Standard output nonlinearity: Output: Threshold: Feedback synaptic currents: State-dependent current positive saturation region linear region Feedforward synaptic currents: negative saturation region offset current

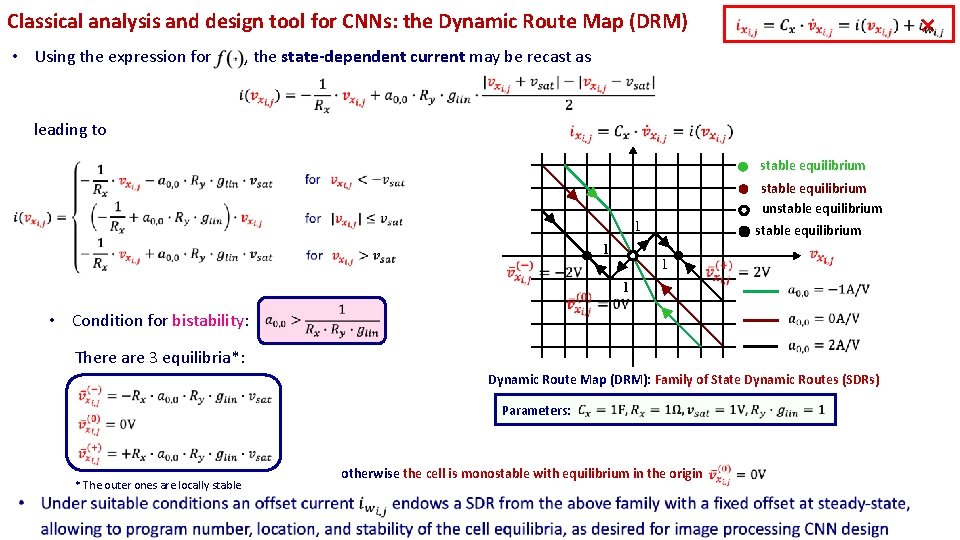

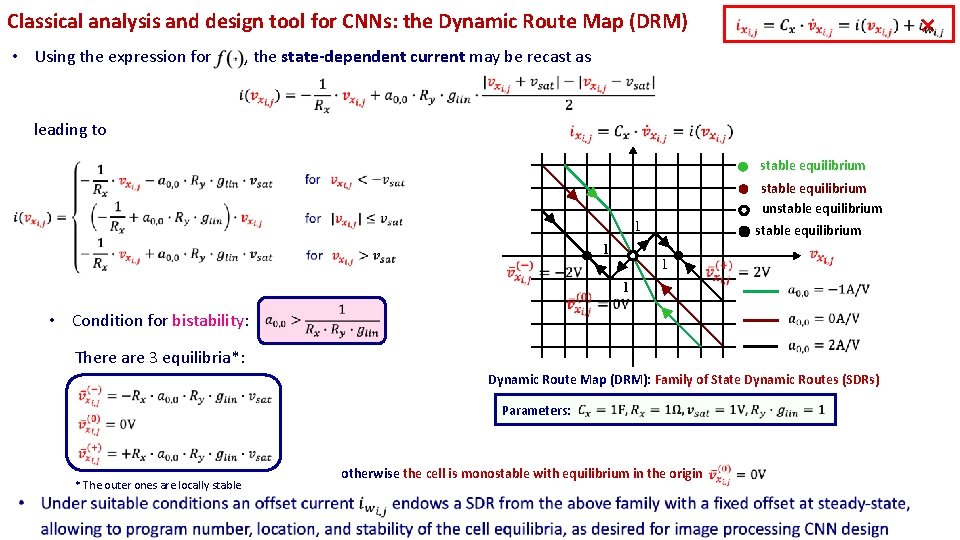

Classical analysis and design tool for CNNs: the Dynamic Route Map (DRM) × • Using the expression for , the state-dependent current may be recast as leading to stable equilibrium unstable equilibrium • Condition for bistability: stable equilibrium There are 3 equilibria*: * The outer ones are locally stable Dynamic Route Map (DRM): Family of State Dynamic Routes (SDRs) Parameters: otherwise the cell is monostable with equilibrium in the origin

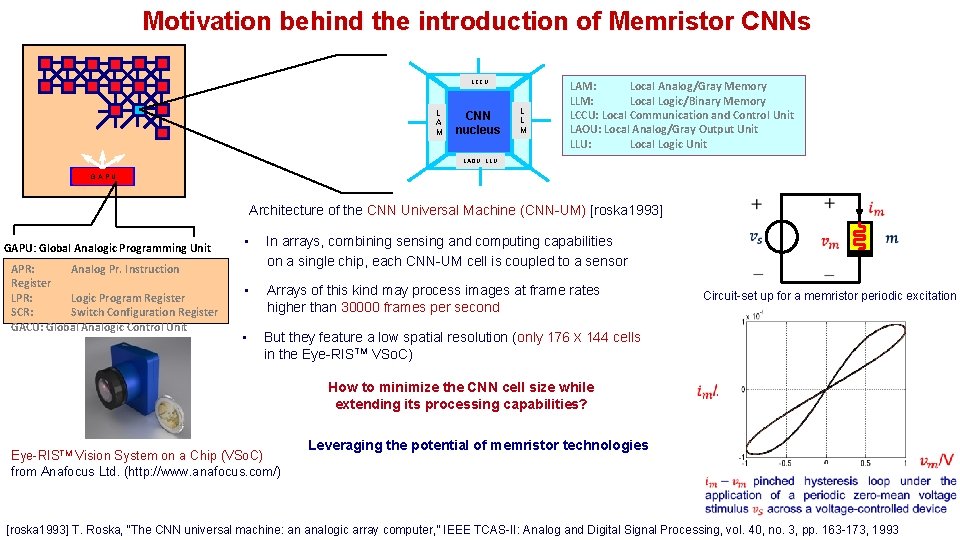

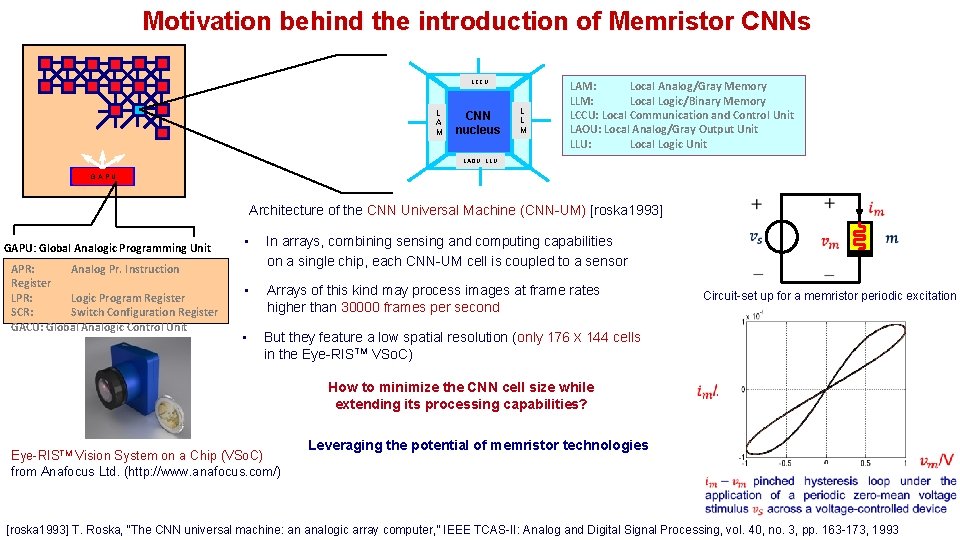

Motivation behind the introduction of Memristor CNNs LCCU L A M CNN nucleus L L M LAM: Local Analog/Gray Memory LLM: Local Logic/Binary Memory LCCU: Local Communication and Control Unit LAOU: Local Analog/Gray Output Unit LLU: Local Logic Unit LAOU LLU GAPU Architecture of the CNN Universal Machine (CNN-UM) [roska 1993] GAPU: Global Analogic Programming Unit APR: Analog Pr. Instruction Register LPR: Logic Program Register SCR: Switch Configuration Register GACU: Global Analogic Control Unit • In arrays, combining sensing and computing capabilities on a single chip, each CNN-UM cell is coupled to a sensor • Arrays of this kind may process images at frame rates higher than 30000 frames per second • But they feature a low spatial resolution (only 176 X 144 cells in the Eye-RISTM VSo. C) How to minimize the CNN cell size while extending its processing capabilities? Eye-RISTM Vision System on a Chip (VSo. C) from Anafocus Ltd. (http: //www. anafocus. com/) Circuit-set up for a memristor periodic excitation Leveraging the potential of memristor technologies [roska 1993] T. Roska, “The CNN universal machine: an analogic array computer, ” IEEE TCAS-II: Analog and Digital Signal Processing, vol. 40, no. 3, pp. 163 -173, 1993

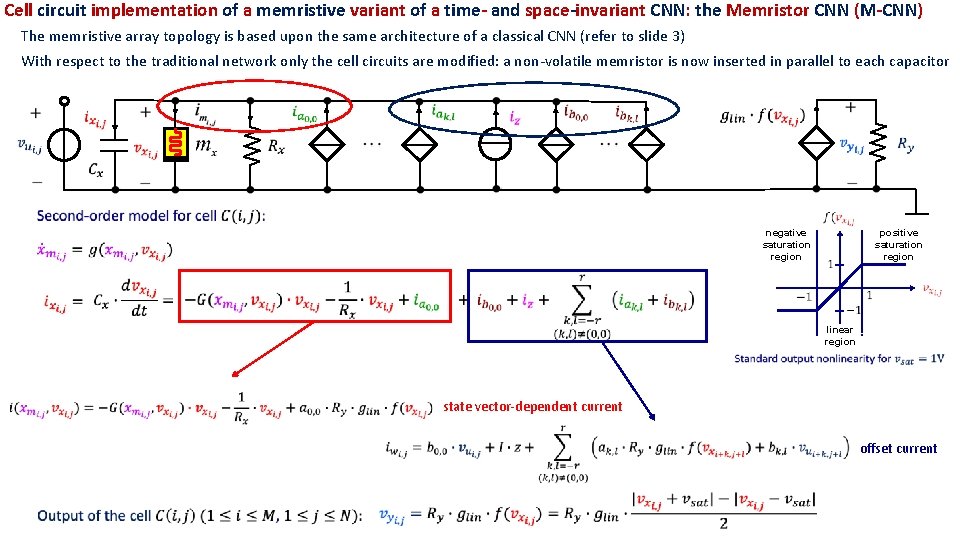

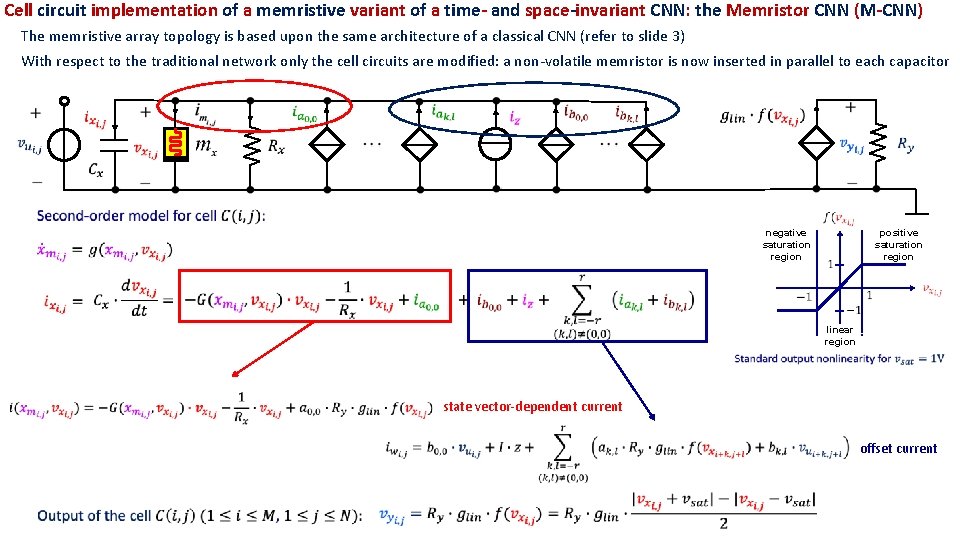

Cell circuit implementation of a memristive variant of a time- and space-invariant CNN: the Memristor CNN (M-CNN) The memristive array topology is based upon the same architecture of a classical CNN (refer to slide 3) With respect to the traditional network only the cell circuits are modified: a non-volatile memristor is now inserted in parallel to each capacitor negative saturation region positive saturation region linear region state vector-dependent current offset current

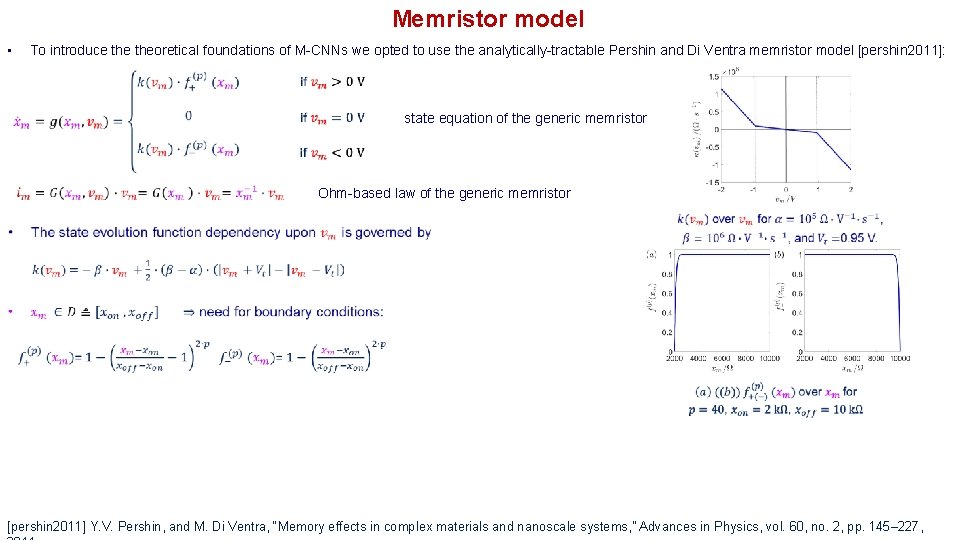

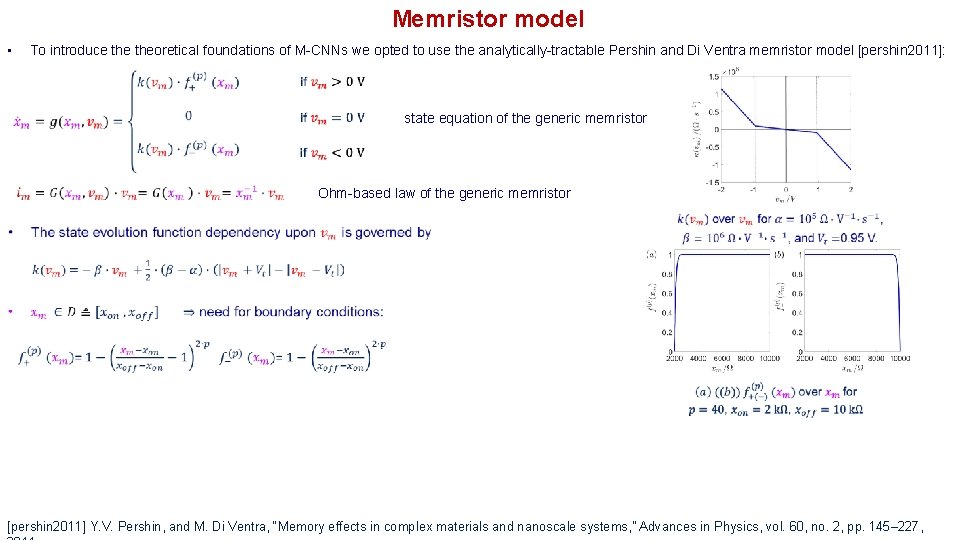

Memristor model • To introduce theoretical foundations of M-CNNs we opted to use the analytically-tractable Pershin and Di Ventra memristor model [pershin 2011]: state equation of the generic memristor Ohm-based law of the generic memristor [pershin 2011] Y. V. Pershin, and M. Di Ventra, “Memory effects in complex materials and nanoscale systems, ” Advances in Physics, vol. 60, no. 2, pp. 145– 227,

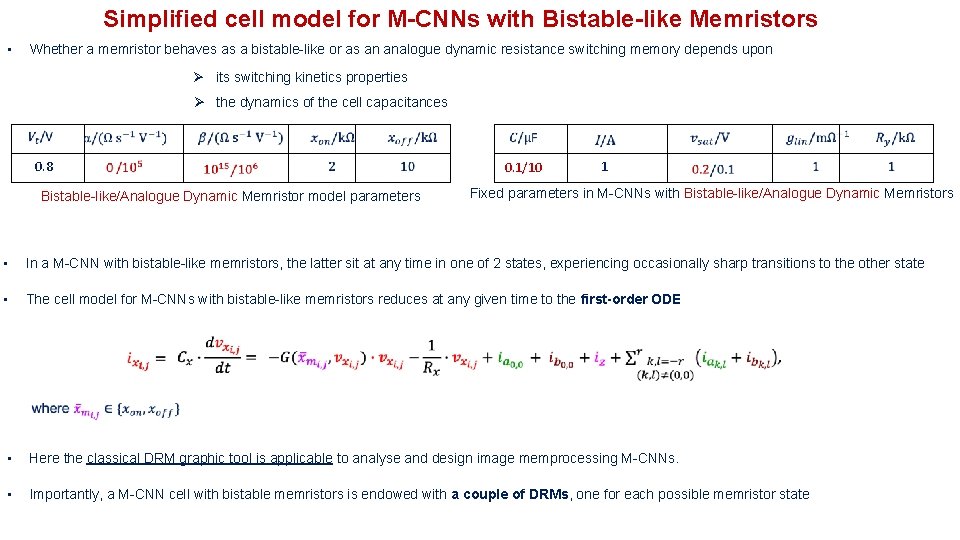

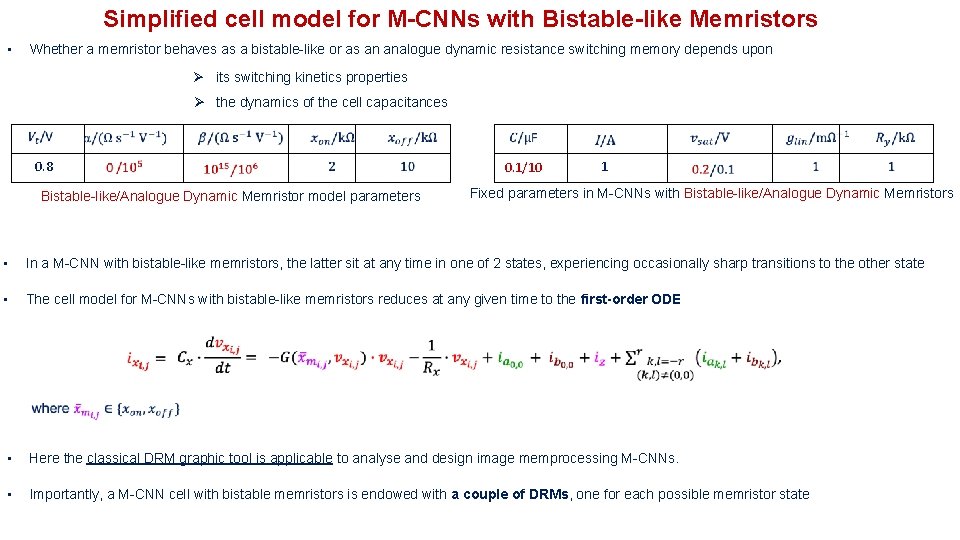

Simplified cell model for M-CNNs with Bistable-like Memristors • Whether a memristor behaves as a bistable-like or as an analogue dynamic resistance switching memory depends upon Ø its switching kinetics properties Ø the dynamics of the cell capacitances 0. 8 0. 1/10 Bistable-like/Analogue Dynamic Memristor model parameters 1 Fixed parameters in M-CNNs with Bistable-like/Analogue Dynamic Memristors • In a M-CNN with bistable-like memristors, the latter sit at any time in one of 2 states, experiencing occasionally sharp transitions to the other state • The cell model for M-CNNs with bistable-like memristors reduces at any given time to the first-order ODE • Here the classical DRM graphic tool is applicable to analyse and design image memprocessing M-CNNs. • Importantly, a M-CNN cell with bistable memristors is endowed with a couple of DRMs, one for each possible memristor state

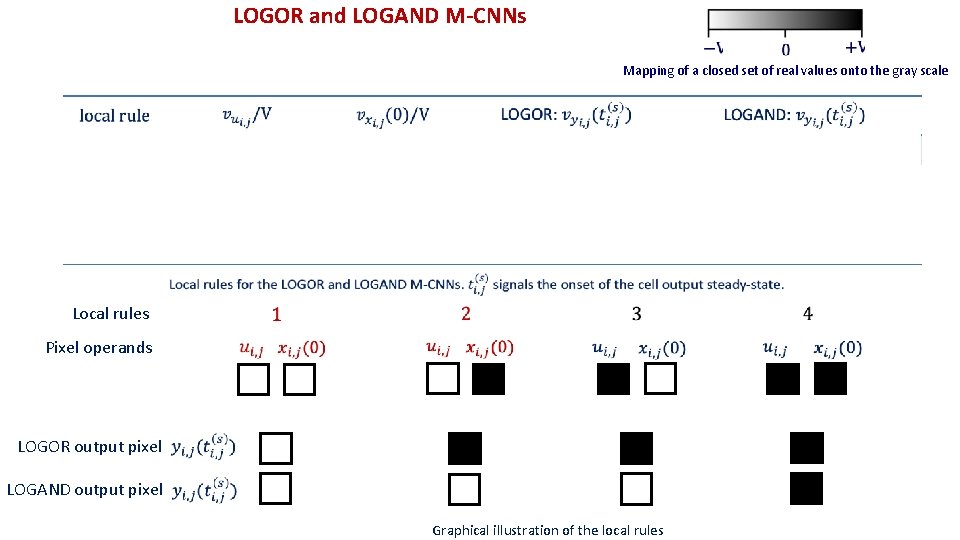

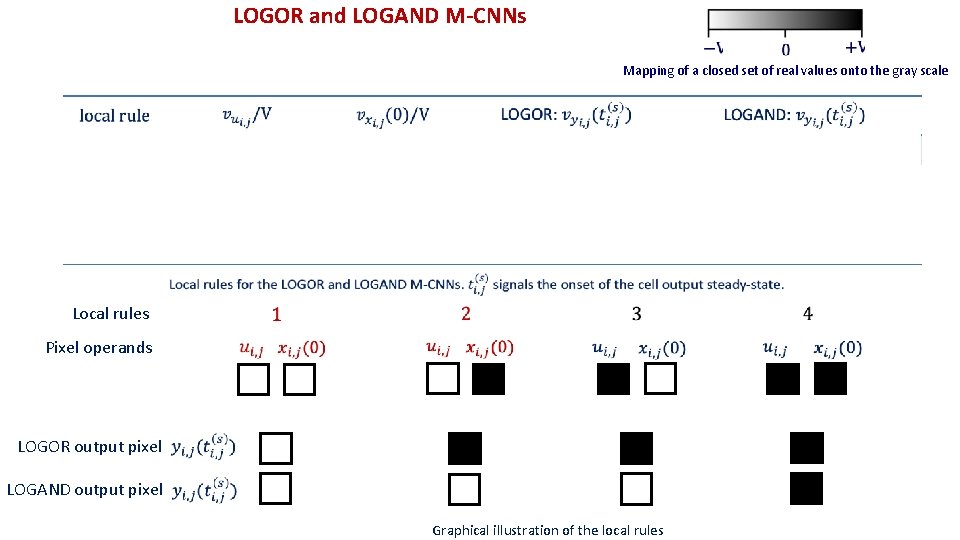

LOGOR and LOGAND M-CNNs Mapping of a closed set of real values onto the gray scale Pixel operands Local rules LOGOR output pixel LOGAND output pixel Graphical illustration of the local rules

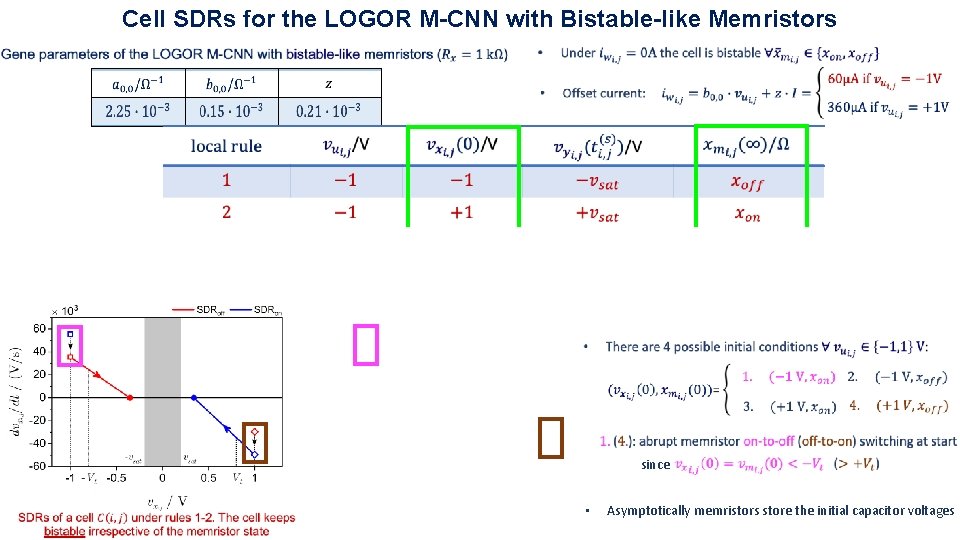

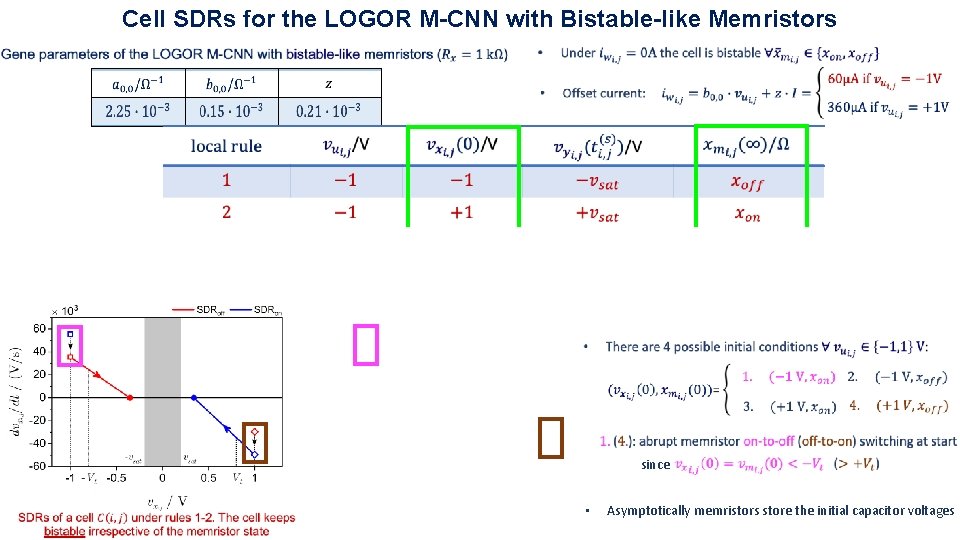

Cell SDRs for the LOGOR M-CNN with Bistable-like Memristors since • Asymptotically memristors store the initial capacitor voltages

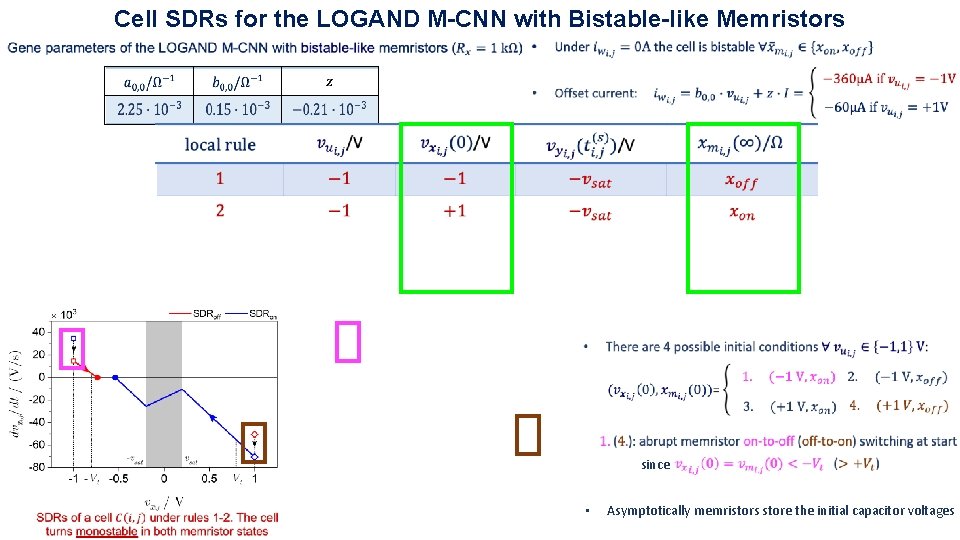

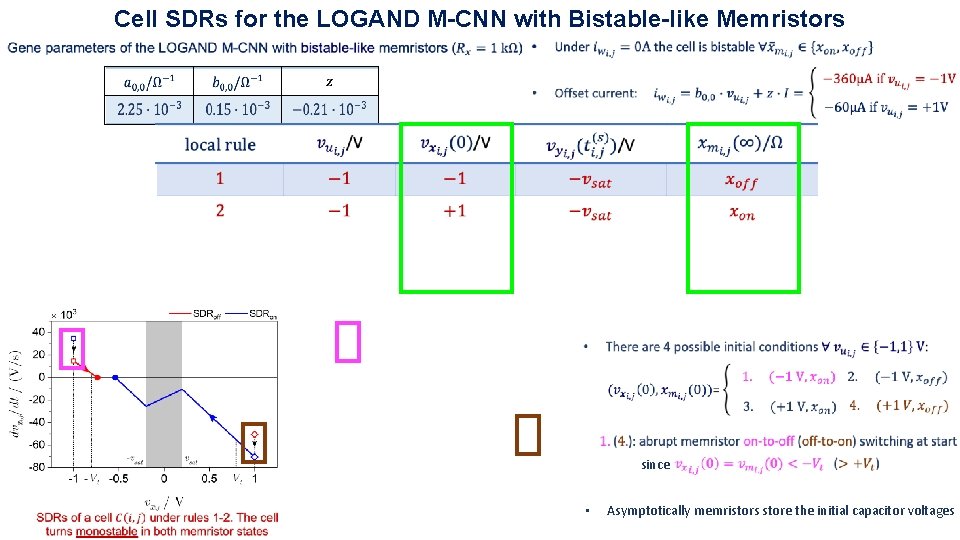

Cell SDRs for the LOGAND M-CNN with Bistable-like Memristors since • Asymptotically memristors store the initial capacitor voltages

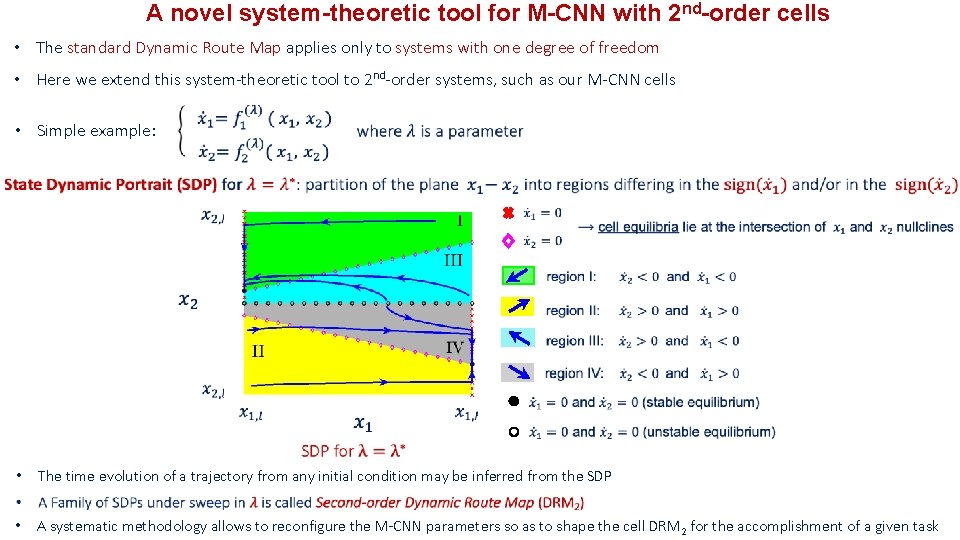

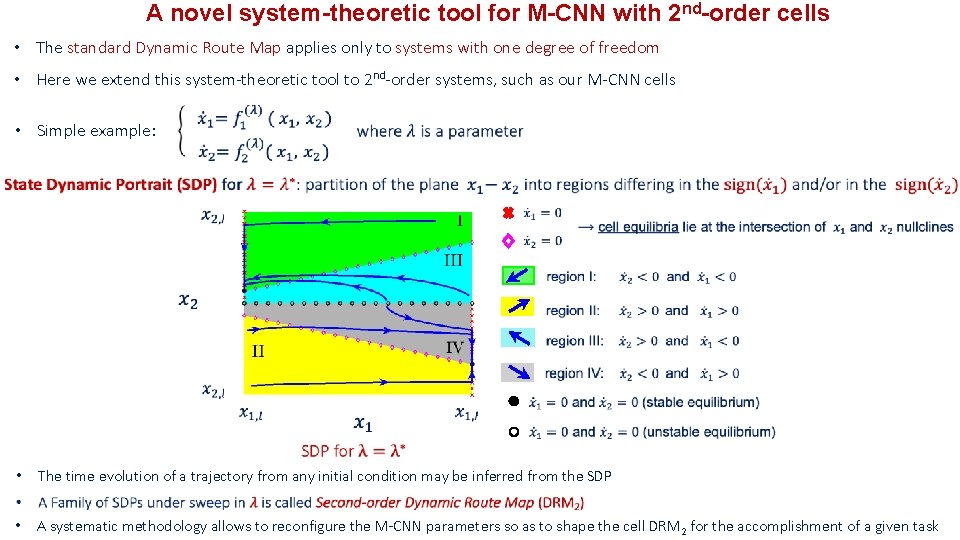

A novel system-theoretic tool for M-CNN with 2 nd-order cells • The standard Dynamic Route Map applies only to systems with one degree of freedom • Here we extend this system-theoretic tool to 2 nd-order systems, such as our M-CNN cells • Simple example: • The time evolution of a trajectory from any initial condition may be inferred from the SDP • A systematic methodology allows to reconfigure the M-CNN parameters so as to shape the cell DRM 2 for the accomplishment of a given task

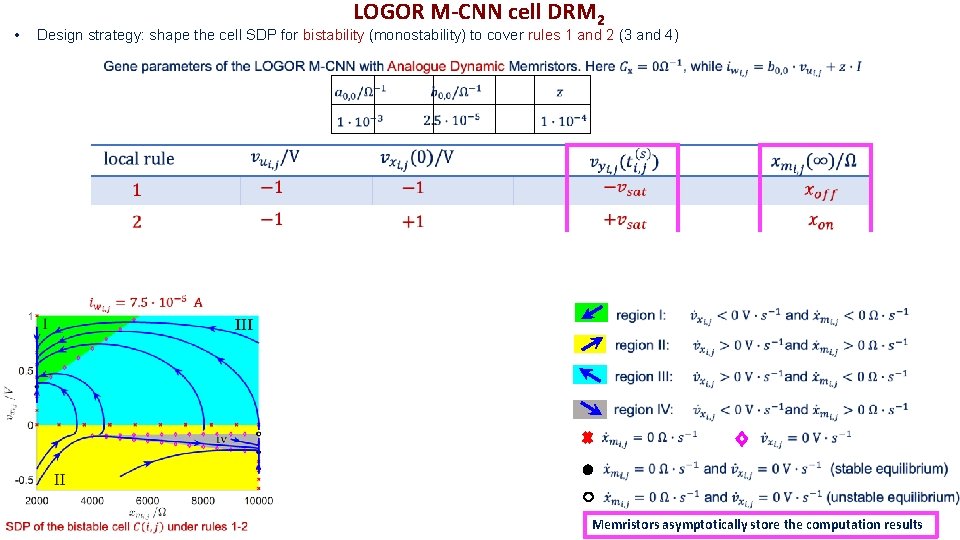

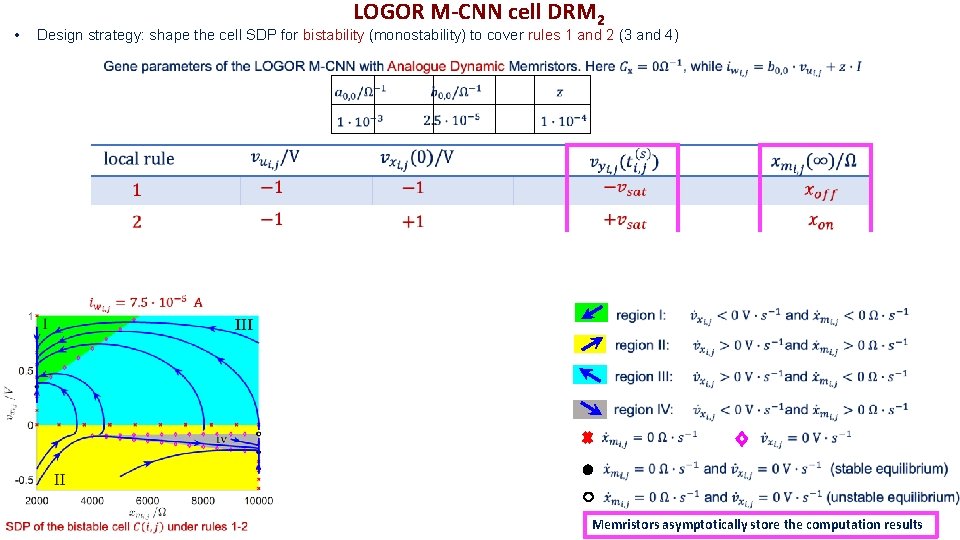

• LOGOR M-CNN cell DRM 2 Design strategy: shape the cell SDP for bistability (monostability) to cover rules 1 and 2 (3 and 4) Memristors asymptotically store the computation results

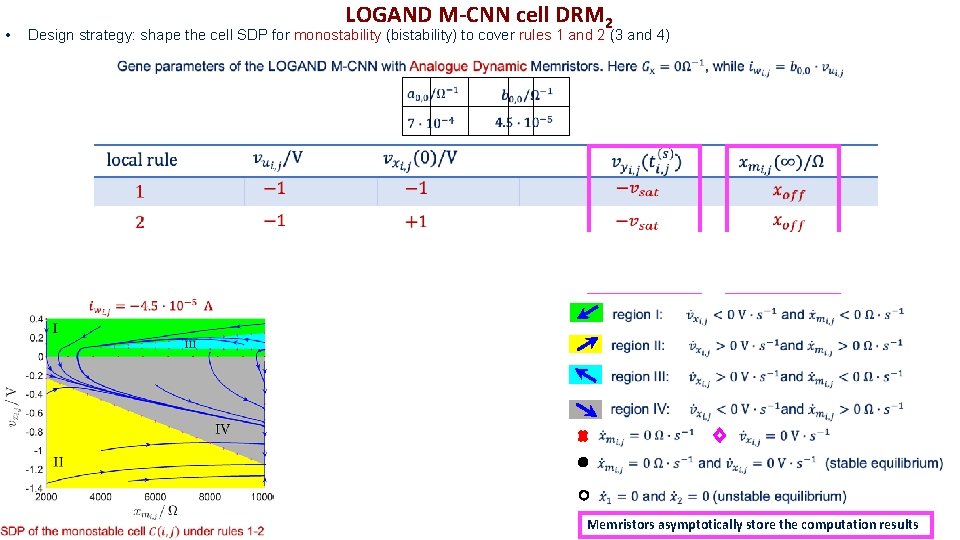

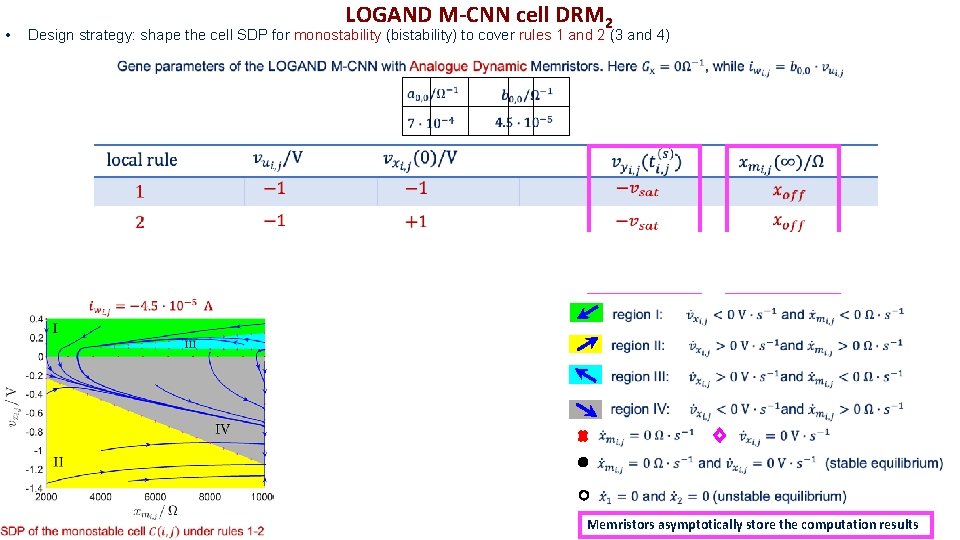

• LOGAND M-CNN cell DRM 2 Design strategy: shape the cell SDP for monostability (bistability) to cover rules 1 and 2 (3 and 4) Memristors asymptotically store the computation results

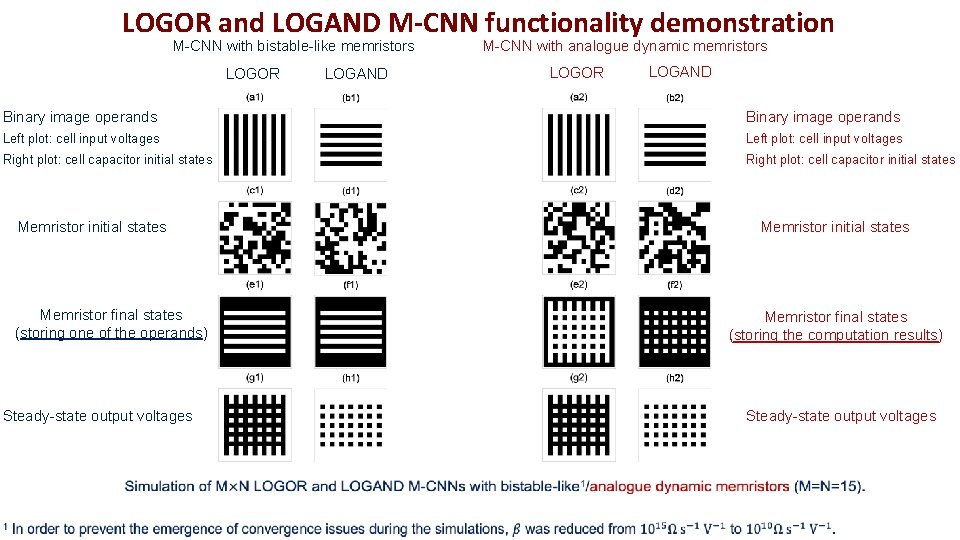

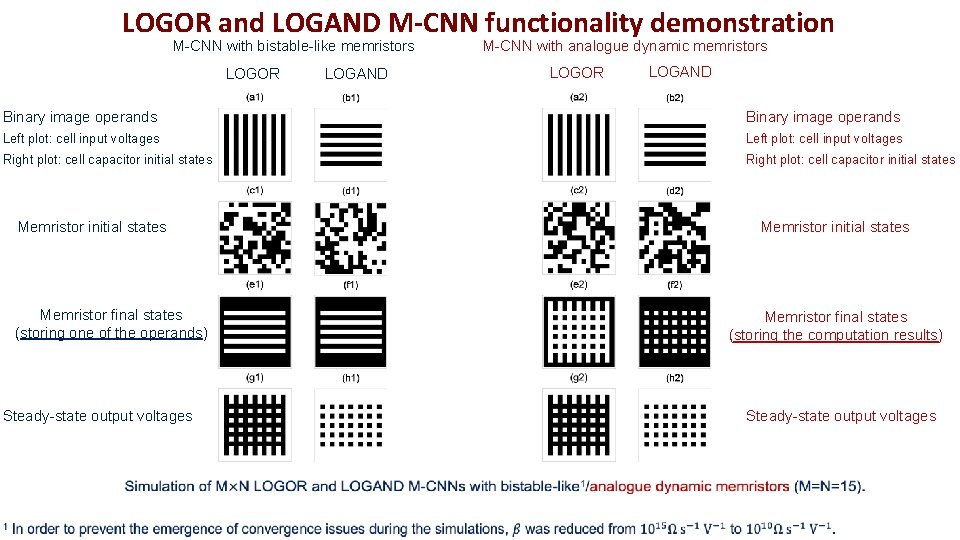

LOGOR and LOGAND M-CNN functionality demonstration M-CNN with bistable-like memristors LOGOR LOGAND M-CNN with analogue dynamic memristors LOGOR LOGAND Binary image operands Left plot: cell input voltages Right plot: cell capacitor initial states Memristor final states (storing one of the operands) Steady-state output voltages Memristor initial states Memristor final states (storing the computation results) Steady-state output voltages

Conclusions • Linear system-theoretic methods are not suitable for the analysis and design of memristor-based circuits • For a full exploration of the potential of memristors in electronics, recurring to concepts from nonlinear system theory is necessary • Converting traditional nonlinear circuits to memristive equivalents may require the extension of classical nonlinear system-theoretic techniques • Adopting the classical/extended DRM graphical tools, systematic methodologies to program M-CNNs with bistable-like/analogue dynamic memristors for executing logic mem-computations between binary image operands may be established. Thank you

More details may be found in A. Ascoli, R. Tetzlaff, Sung-Mo “Steve” Kang, and L. O. Chua, “Theoretical Foundations of Memristor Cellular Nonlinear Networks: a DRM 2 -based Method to design Memcomputers with Dynamic Memristors”, IEEE Trans. on Circuits and Systems–I: Regular Papers, 2020, DOI: 10. 1109/TCSI. 2020. 2978460 A. Ascoli, I. Messaris, R. Tetzlaff, and L. O. Chua, “Theoretical Foundations of Memristor Cellular Nonlinear Networks: Stability Analysis with Dynamic Memristors”, IEEE Trans. on Circuits and Systems–I: Regular Papers, vol. 67, no. 4, pp. 1389 -1401, April 2020, DOI: 10. 1109/TCSI. 2019. 2957813 R. Tetzlaff, A. Ascoli, I. Messaris, and L. O. Chua, “Theoretical Foundations of Memristor Cellular Nonlinear Networks: Memcomputing with Bistable-like Memristors”, IEEE Trans. on Circuits and Systems–I: Regular Papers, vol. 67, no. 2, pp. 502 -515, Feb. 2020, DOI: 10. 1109/TCSI. 2019. 2940909