IEE 5011 FALL 2013 Memory Systems LPDDR 3

- Slides: 38

IEE 5011 – FALL 2013 Memory Systems LPDDR 3 DRAM for Mobile Applications Balakumar Department of Electronics Engineering National Chiao Tung University balakumar. meirtt@gmail. com Balakumar January 16, 2014

Outline n Motivation n PC Like Performance n Mobile DRAM Evolutionary Path n LPDDRx (Across generations) n LPDDR 3 n ISM (Inner Stack Memory Module) n Comparison with Wide I/O n Samsung LPDDR 3 n Conclusion Balakumar January 16, 2014 NCTU IEE 5011 Memory Systems 2013 2

Motivation n Energy efficiency is the major optimization criteria for systems-on-chip (So. Cs) for mobile devices (smartphones and tablets). n Performance and power consumption of DRAMs (LPDDRs) depends on the configuration of system level parameters, such as operating frequency, interference bandwidth, request size, and memory map. Balakumar January 16, 2014 NCTU IEE 5011 Memory Systems 2013 3

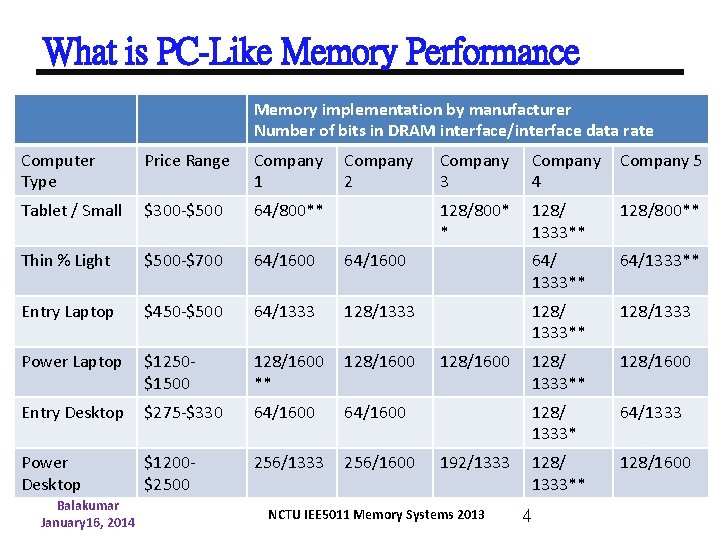

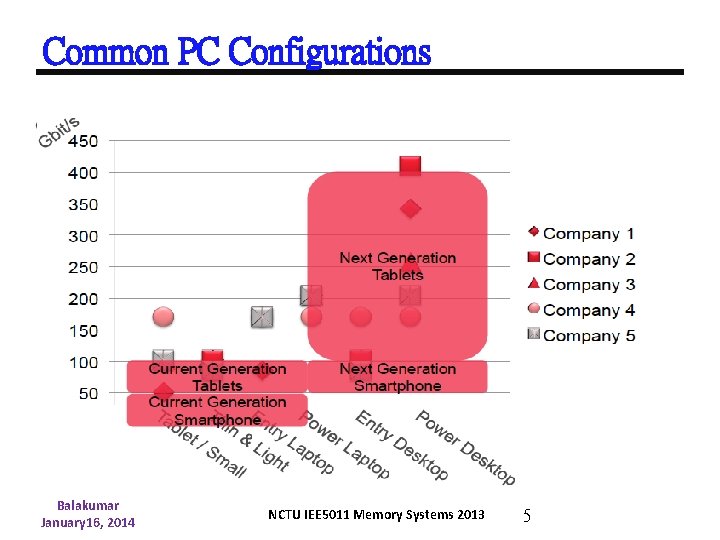

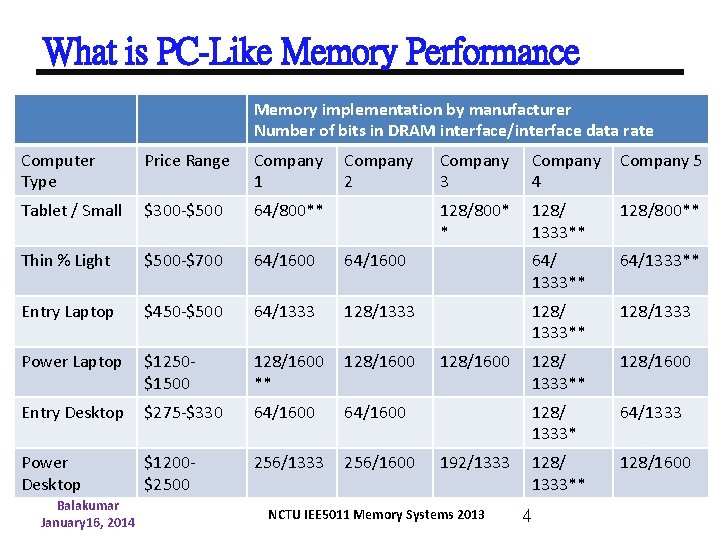

What is PC-Like Memory Performance Memory implementation by manufacturer Number of bits in DRAM interface/interface data rate Computer Type Price Range Company 1 Tablet / Small $300 -$500 64/800** Thin % Light $500 -$700 64/1600 Entry Laptop $450 -$500 Power Laptop Company 3 Company 4 Company 5 128/800* * 128/ 1333** 128/800** 64/1600 64/ 1333** 64/1333 128/ 1333** 128/1333 $1250$1500 128/1600 ** 128/1600 128/ 1333** 128/1600 Entry Desktop $275 -$330 64/1600 128/ 1333* 64/1333 Power Desktop $1200$2500 256/1333 256/1600 128/ 1333** 128/1600 Balakumar January 16, 2014 Company 2 128/1600 192/1333 NCTU IEE 5011 Memory Systems 2013 4

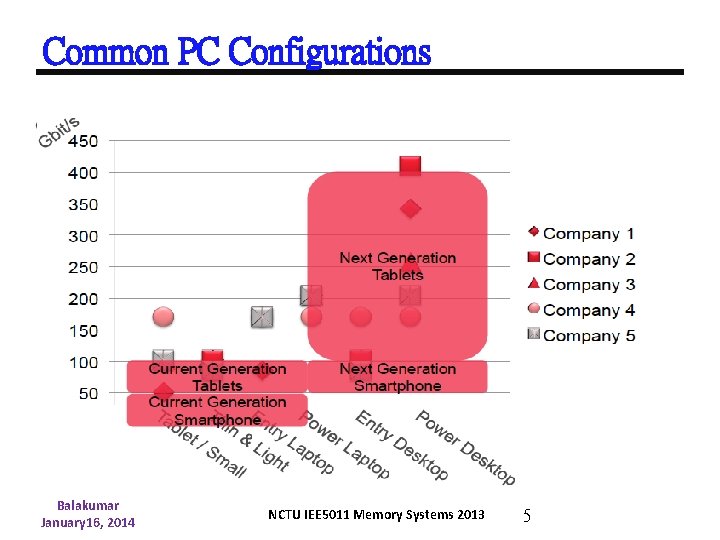

Common PC Configurations Balakumar January 16, 2014 NCTU IEE 5011 Memory Systems 2013 5

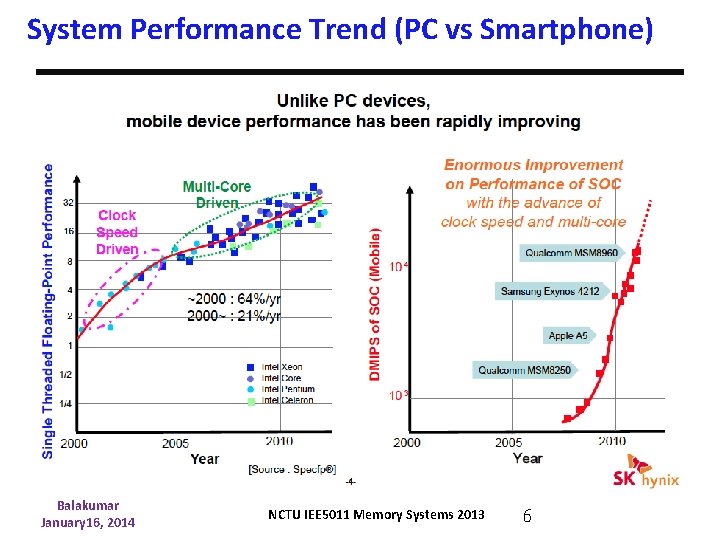

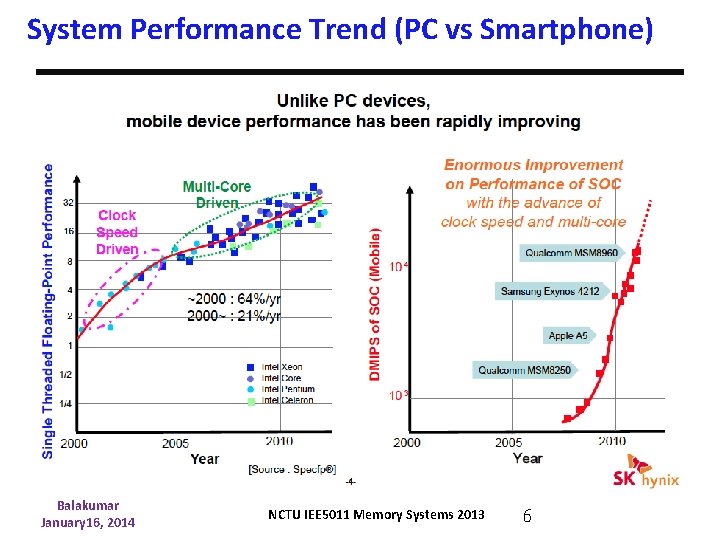

System Performance Trend (PC vs Smartphone) Balakumar January 16, 2014 NCTU IEE 5011 Memory Systems 2013 6

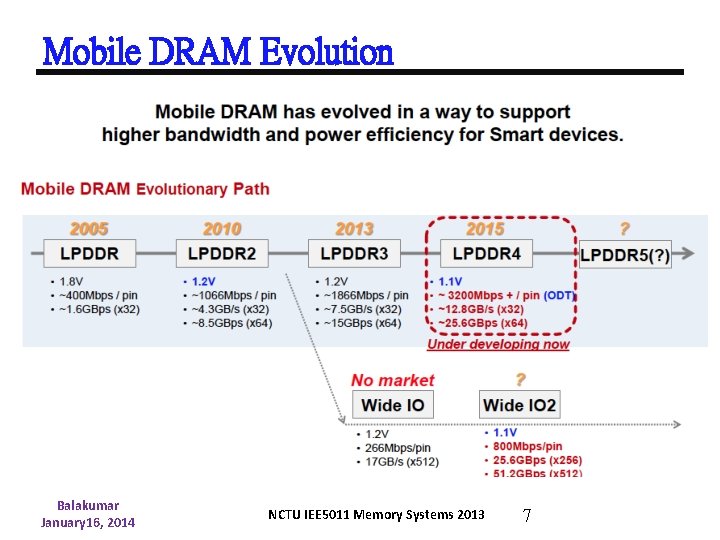

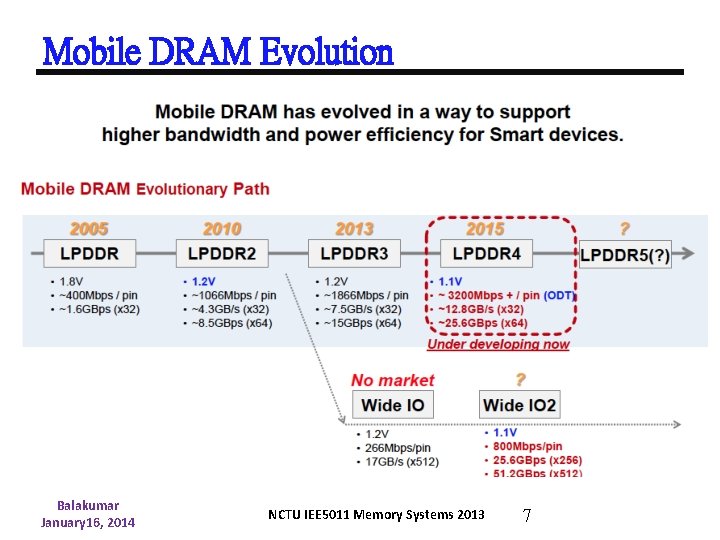

Mobile DRAM Evolution Balakumar January 16, 2014 NCTU IEE 5011 Memory Systems 2013 7

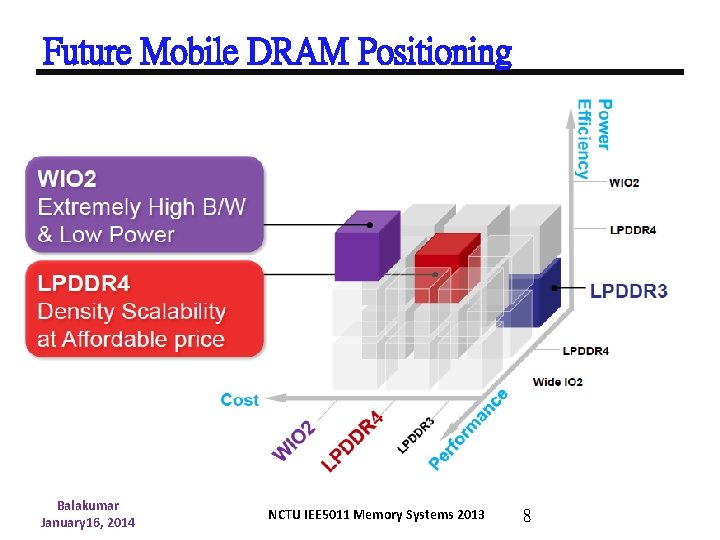

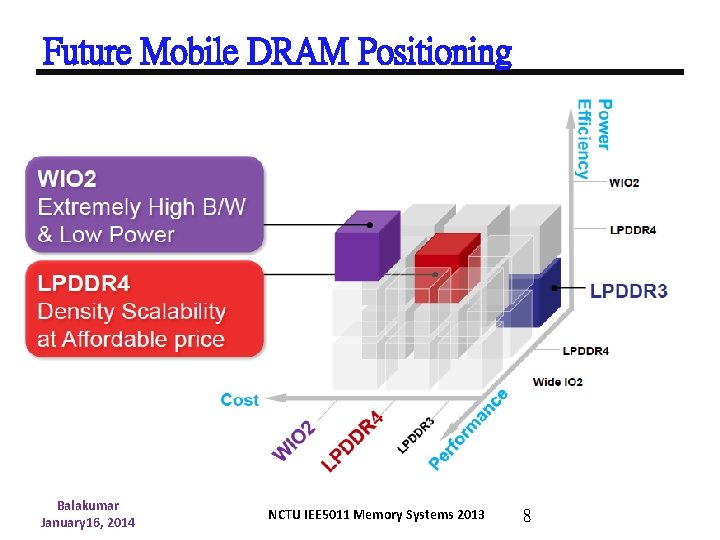

Future Mobile DRAM Positioning Balakumar January 16, 2014 NCTU IEE 5011 Memory Systems 2013 8

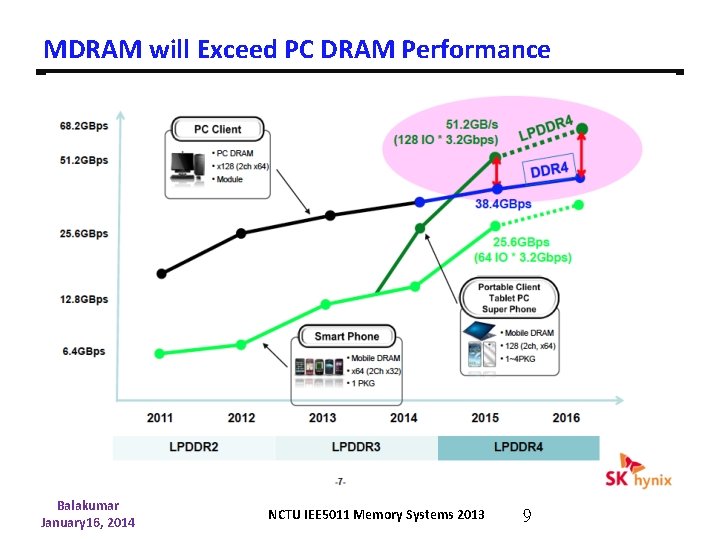

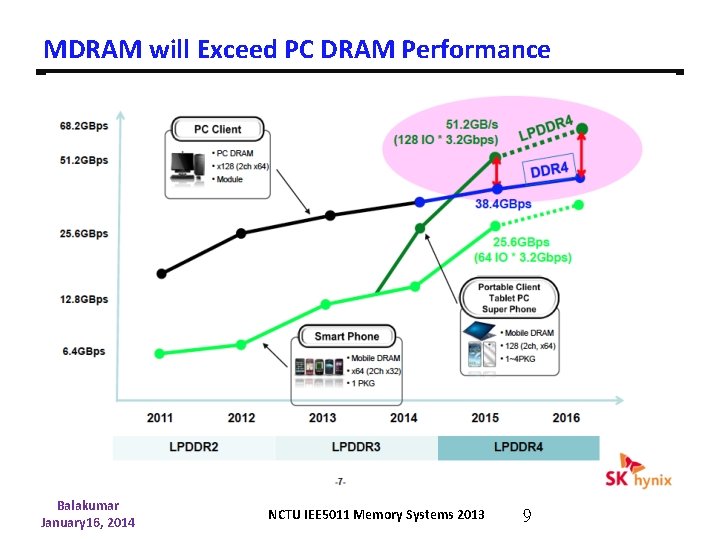

MDRAM will Exceed PC DRAM Performance Balakumar January 16, 2014 NCTU IEE 5011 Memory Systems 2013 9

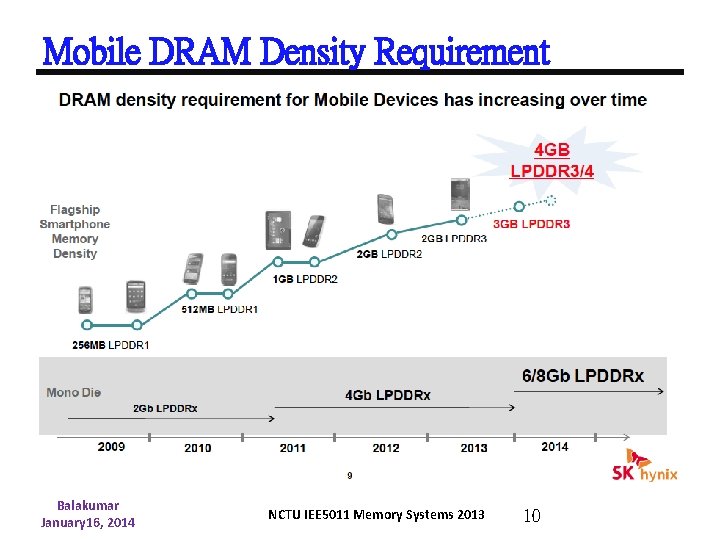

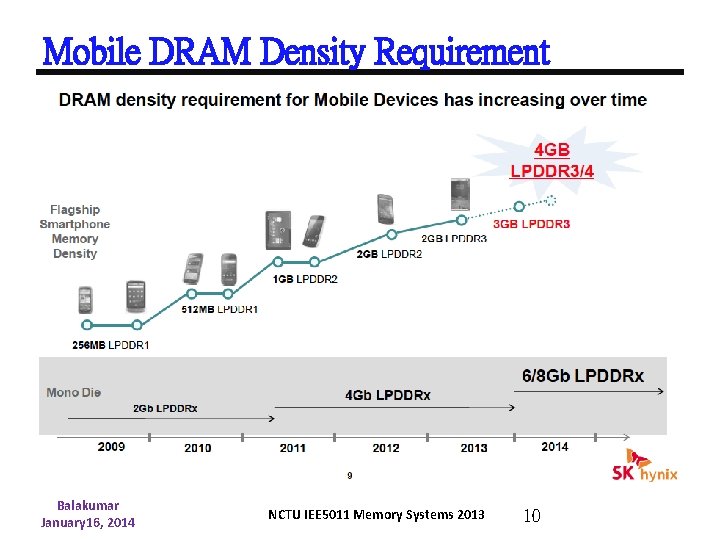

Mobile DRAM Density Requirement Balakumar January 16, 2014 NCTU IEE 5011 Memory Systems 2013 10

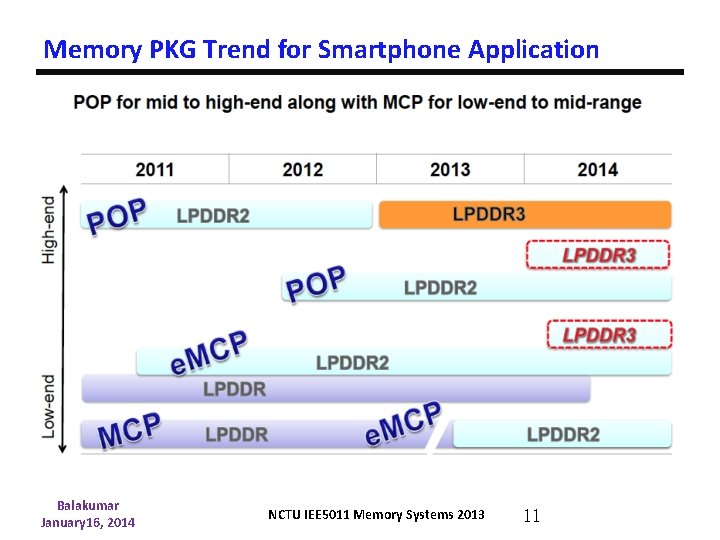

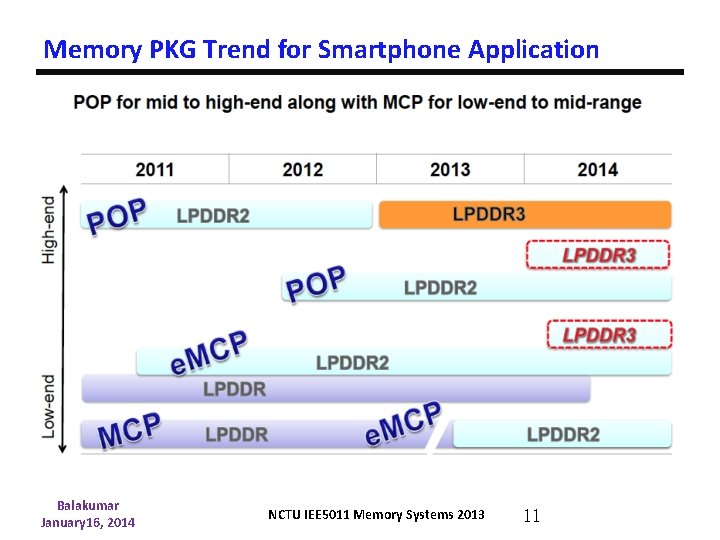

Memory PKG Trend for Smartphone Application Balakumar January 16, 2014 NCTU IEE 5011 Memory Systems 2013 11

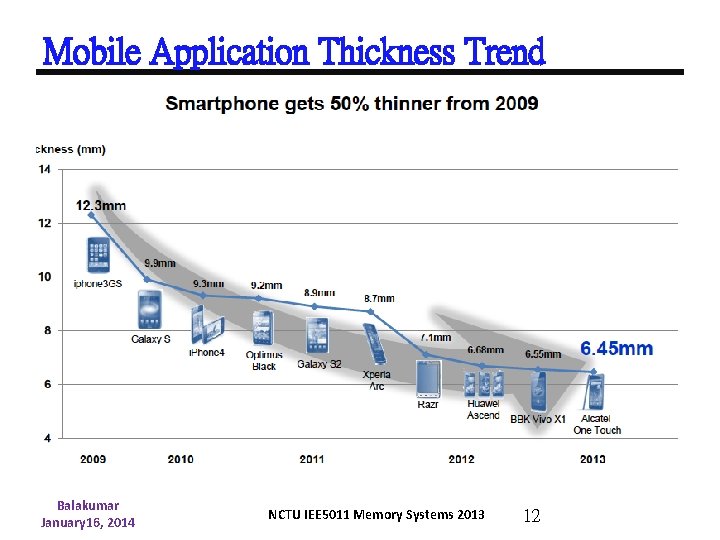

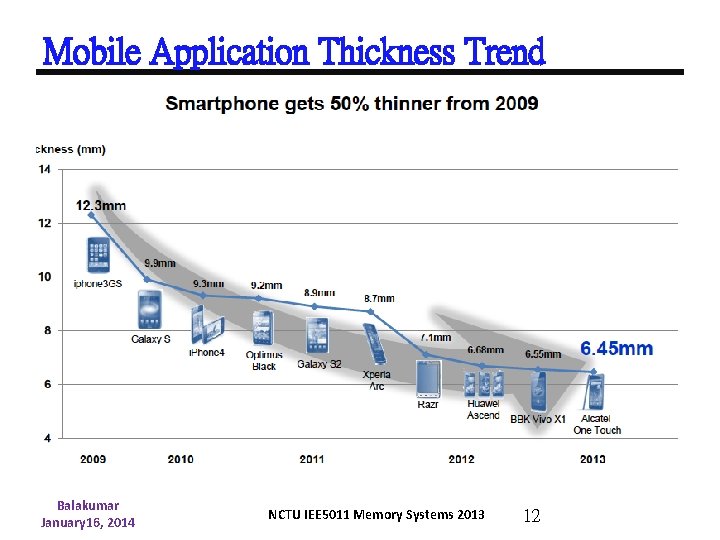

Mobile Application Thickness Trend Balakumar January 16, 2014 NCTU IEE 5011 Memory Systems 2013 12

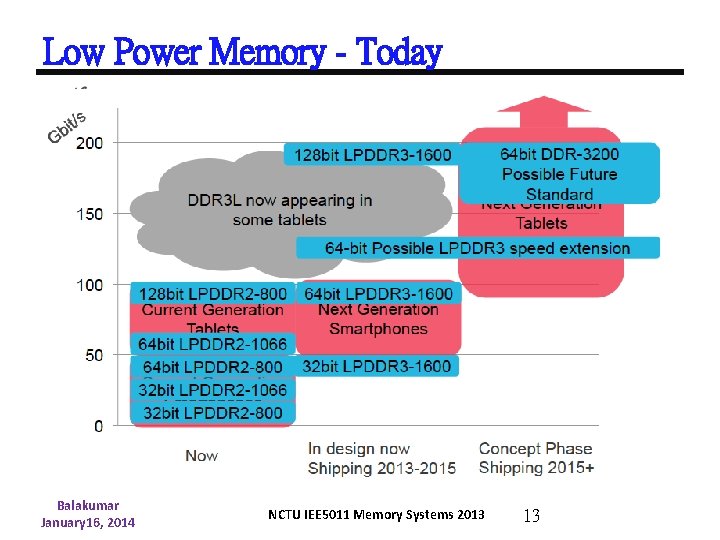

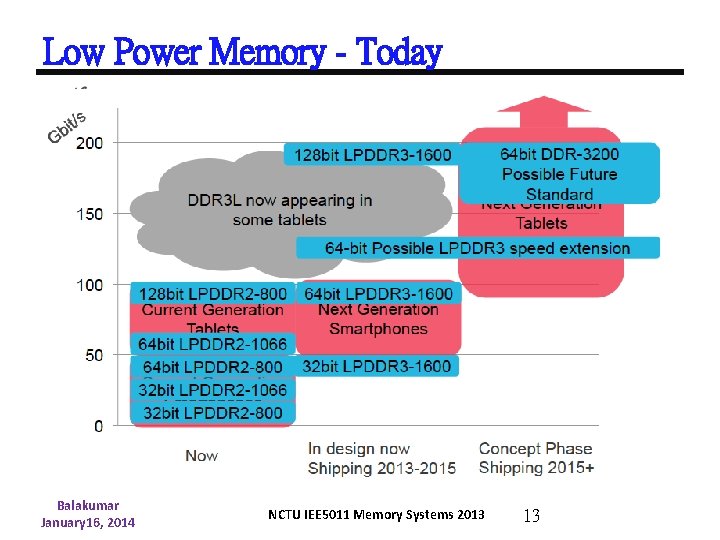

Low Power Memory - Today Balakumar January 16, 2014 NCTU IEE 5011 Memory Systems 2013 13

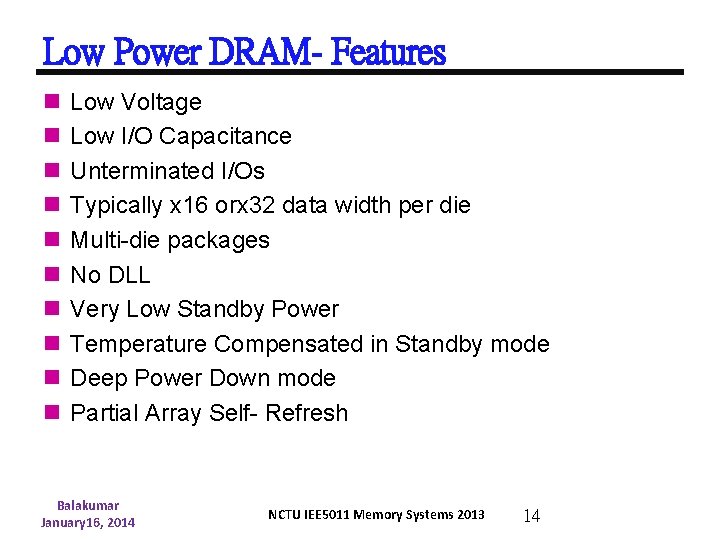

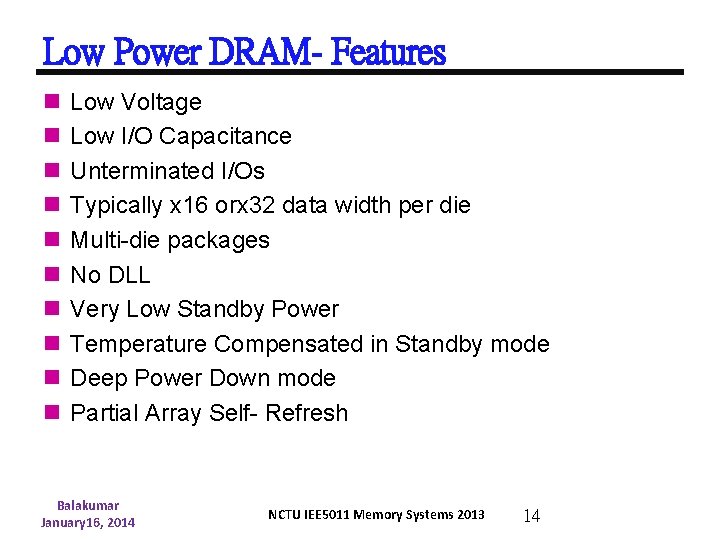

Low Power DRAM- Features n n n n n Low Voltage Low I/O Capacitance Unterminated I/Os Typically x 16 orx 32 data width per die Multi-die packages No DLL Very Low Standby Power Temperature Compensated in Standby mode Deep Power Down mode Partial Array Self- Refresh Balakumar January 16, 2014 NCTU IEE 5011 Memory Systems 2013 14

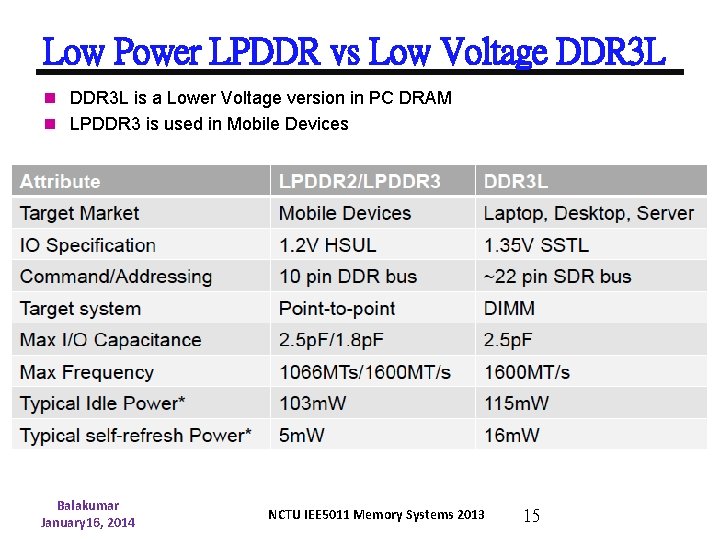

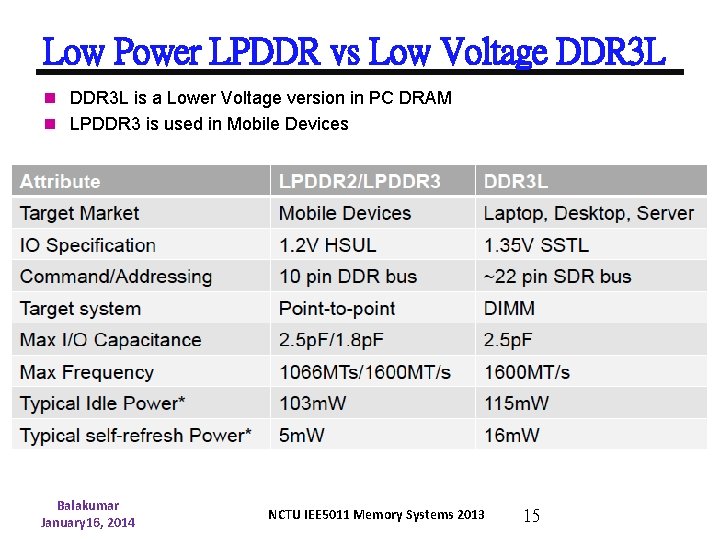

Low Power LPDDR vs Low Voltage DDR 3 L n DDR 3 L is a Lower Voltage version in PC DRAM n LPDDR 3 is used in Mobile Devices Balakumar January 16, 2014 NCTU IEE 5011 Memory Systems 2013 15

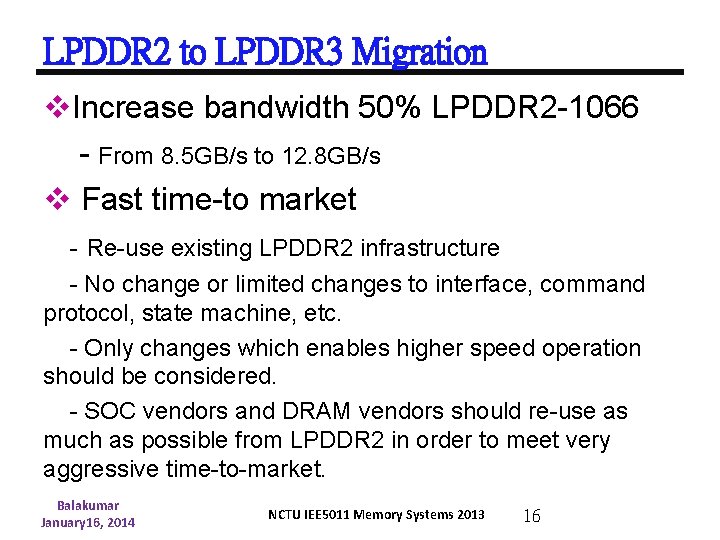

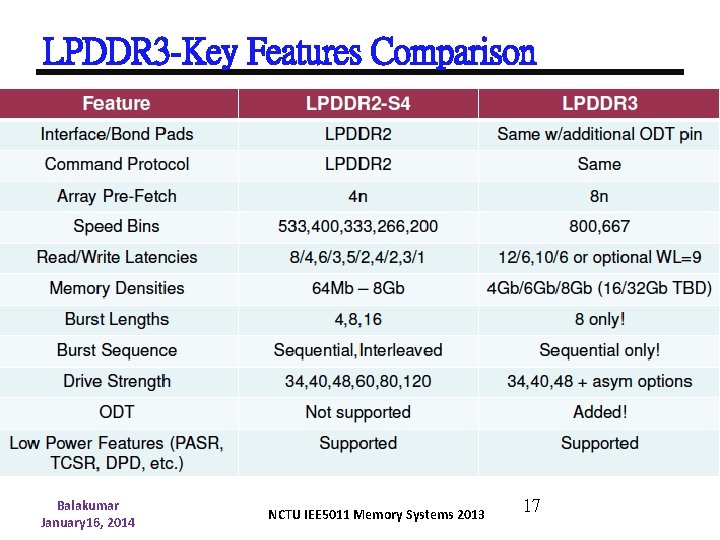

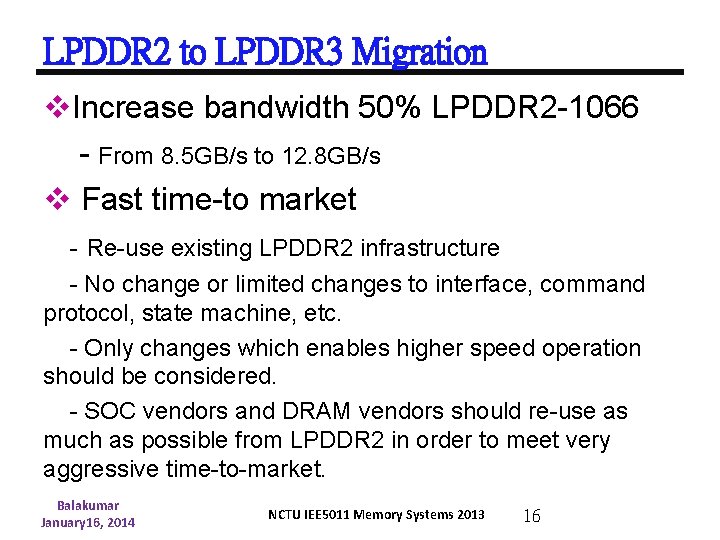

LPDDR 2 to LPDDR 3 Migration v. Increase bandwidth 50% LPDDR 2 -1066 - From 8. 5 GB/s to 12. 8 GB/s v Fast time-to market - Re-use existing LPDDR 2 infrastructure - No change or limited changes to interface, command protocol, state machine, etc. - Only changes which enables higher speed operation should be considered. - SOC vendors and DRAM vendors should re-use as much as possible from LPDDR 2 in order to meet very aggressive time-to-market. Balakumar January 16, 2014 NCTU IEE 5011 Memory Systems 2013 16

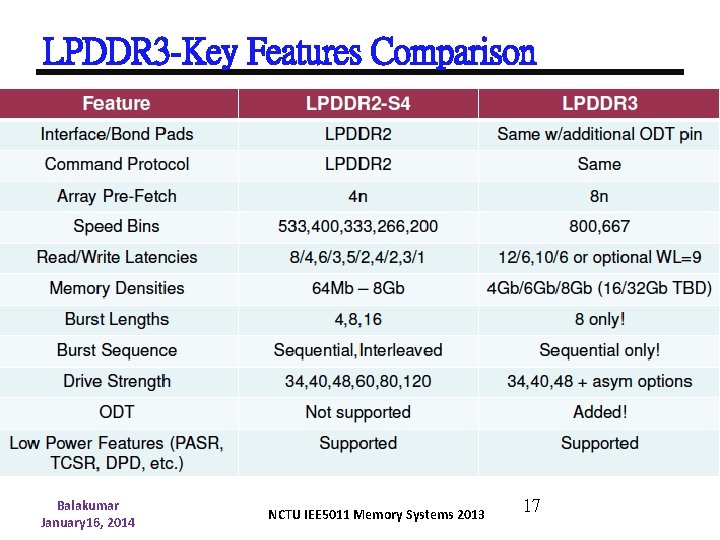

LPDDR 3 -Key Features Comparison Balakumar January 16, 2014 NCTU IEE 5011 Memory Systems 2013 17

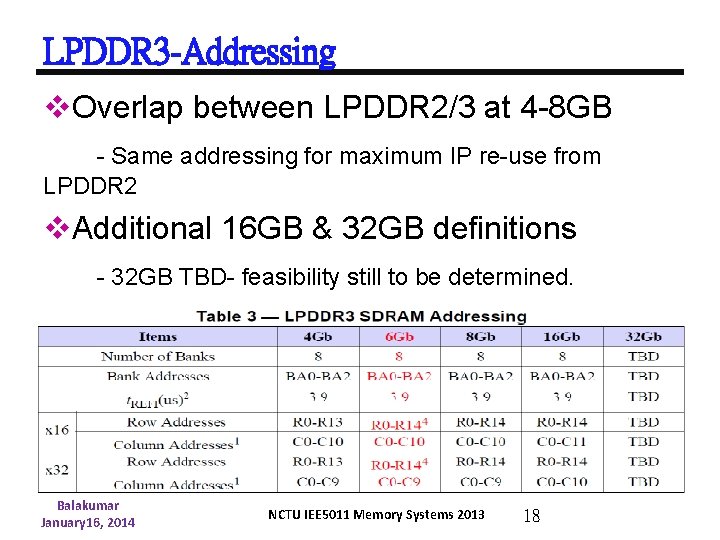

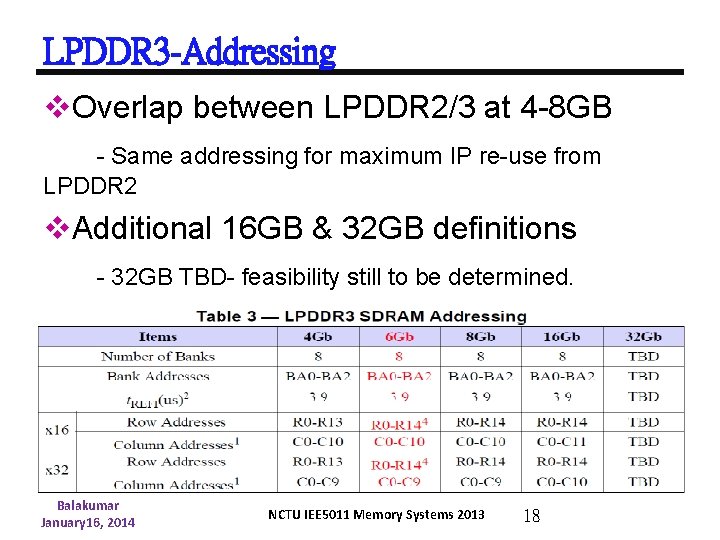

LPDDR 3 -Addressing v. Overlap between LPDDR 2/3 at 4 -8 GB - Same addressing for maximum IP re-use from LPDDR 2 v. Additional 16 GB & 32 GB definitions - 32 GB TBD- feasibility still to be determined. - 16 GB addressing defined, but refresh requirements still TBD. Balakumar January 16, 2014 NCTU IEE 5011 Memory Systems 2013 18

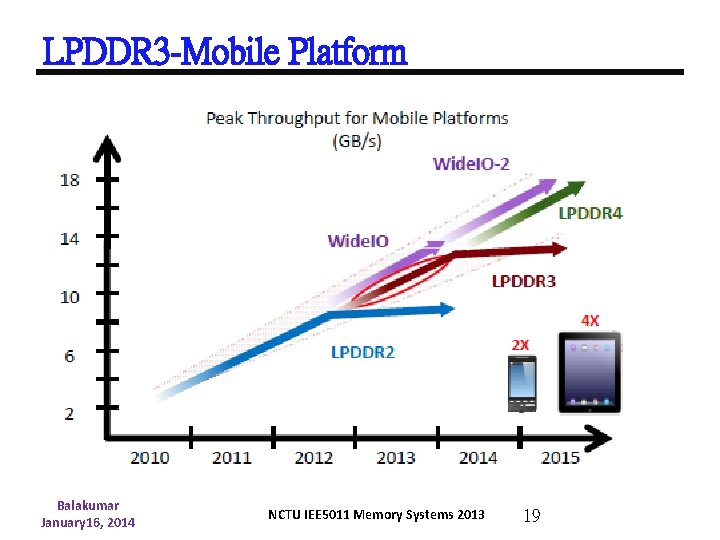

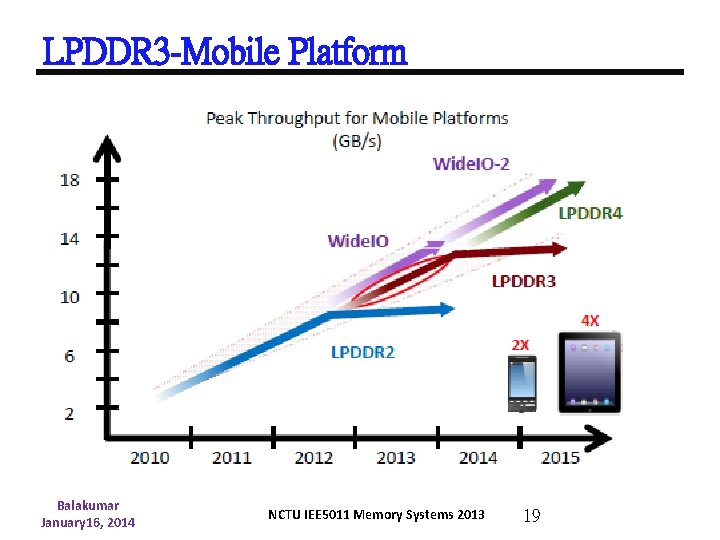

LPDDR 3 -Mobile Platform Balakumar January 16, 2014 NCTU IEE 5011 Memory Systems 2013 19

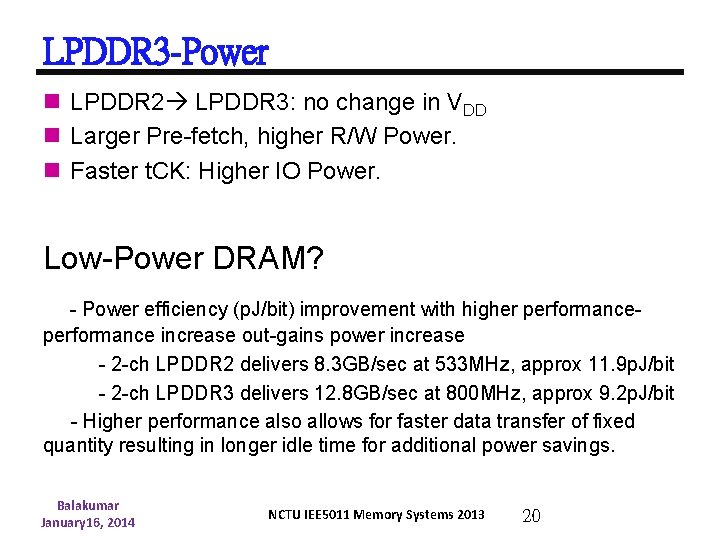

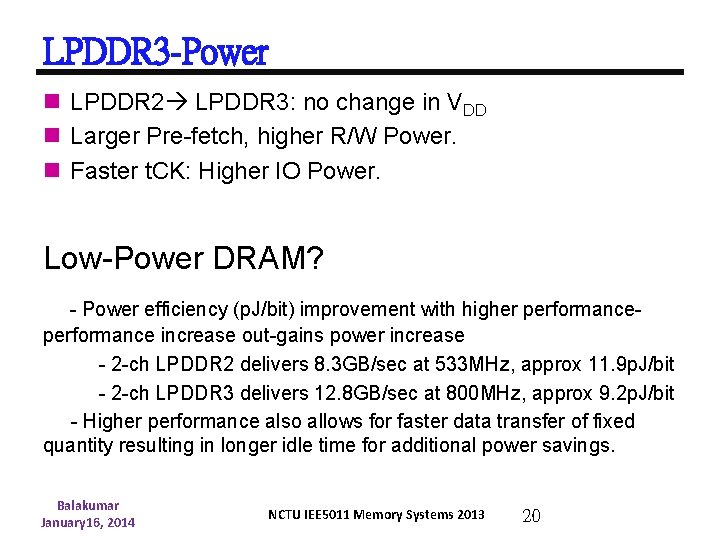

LPDDR 3 -Power n LPDDR 2 LPDDR 3: no change in VDD n Larger Pre-fetch, higher R/W Power. n Faster t. CK: Higher IO Power. Low-Power DRAM? - Power efficiency (p. J/bit) improvement with higher performance increase out-gains power increase - 2 -ch LPDDR 2 delivers 8. 3 GB/sec at 533 MHz, approx 11. 9 p. J/bit - 2 -ch LPDDR 3 delivers 12. 8 GB/sec at 800 MHz, approx 9. 2 p. J/bit - Higher performance also allows for faster data transfer of fixed quantity resulting in longer idle time for additional power savings. Balakumar January 16, 2014 NCTU IEE 5011 Memory Systems 2013 20

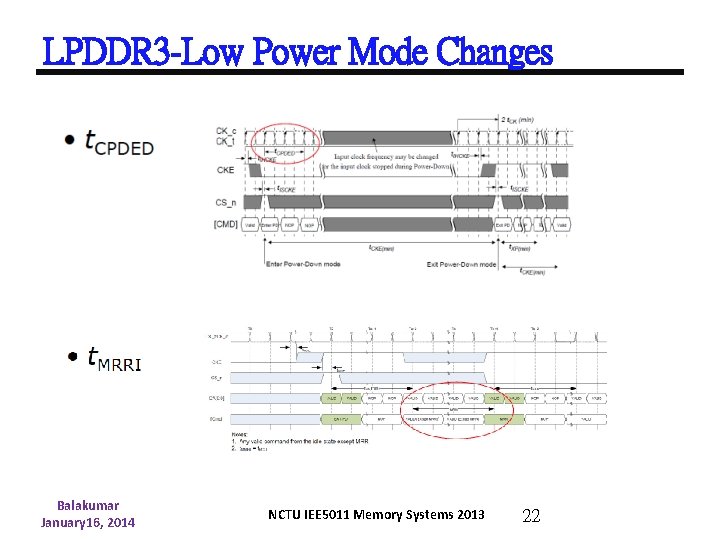

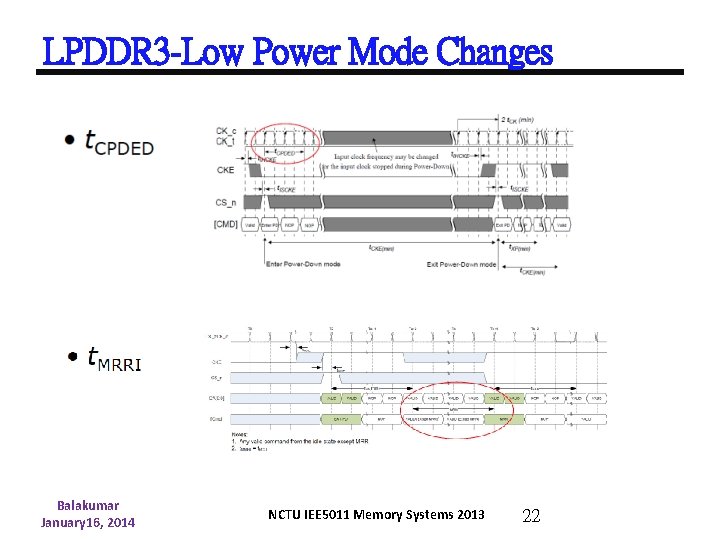

LPDDR 3 -Low Power Features Ø TCSR- same feature as LPDDR 2 Ø PASR- same as LPDDR 2 (identical bank & segment masking as S 4) Ø DPD- supported Ø Power-down mode Ø Self-refresh mode Ø New Requirements - t. CPDED required for PD/SREF/DPD entry - t. MRRI required upon PD exit Balakumar January 16, 2014 NCTU IEE 5011 Memory Systems 2013 21

LPDDR 3 -Low Power Mode Changes Balakumar January 16, 2014 NCTU IEE 5011 Memory Systems 2013 22

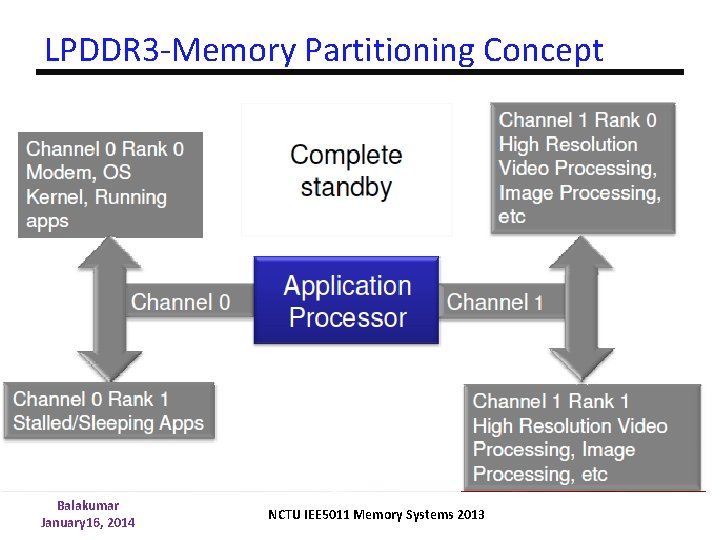

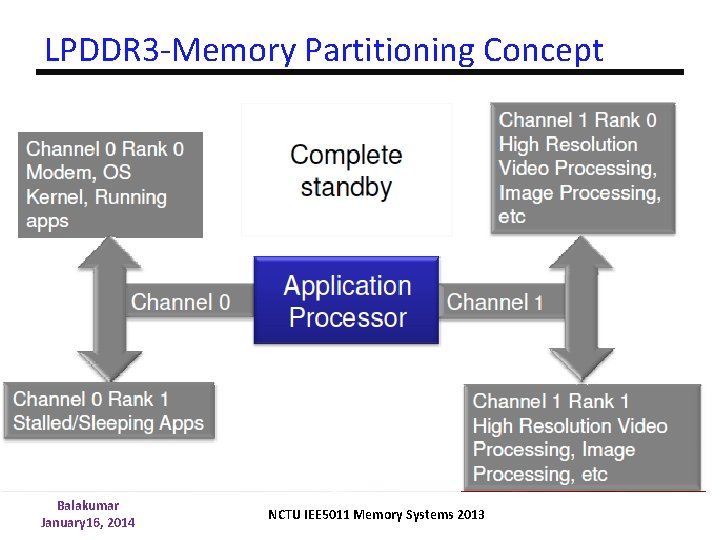

LPDDR 3 -Memory Partitioning Concept 23 Balakumar January 16, 2014 NCTU IEE 5011 Memory Systems 2013

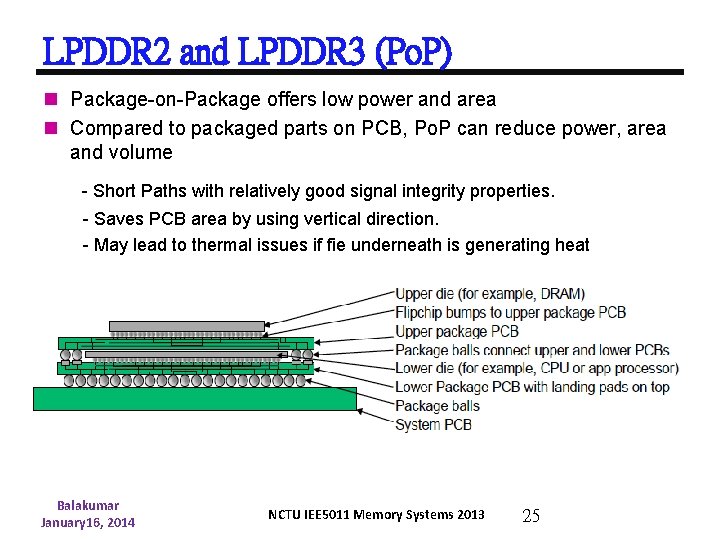

LPDDR 3 -System Design Considerations Ø Signal Integrity is significantly affected by these parameters. - CIO (capacitance) - Driver slew rate - Package design - Power delivery (key in Po. P implementation) Ø Great care must be taken to design a system that has good signal integrity at 1600 MT/s with this PHY Ø It is highly recommended to work with memory vendors to model your system using extracted driver and package parameters. Ø Additional features can be employed to improve signal margin. Balakumar - DQ on January 16, 2014 Die Termination NCTU(ODT) IEE 5011 Memory Systems 2013 24

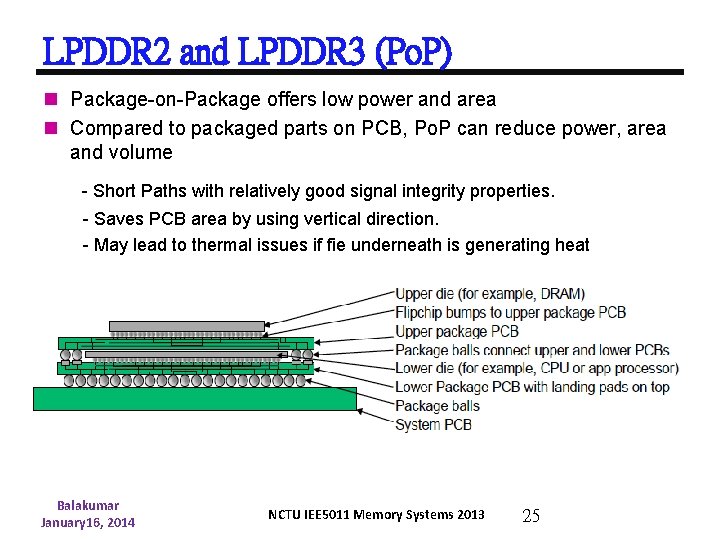

LPDDR 2 and LPDDR 3 (Po. P) n Package-on-Package offers low power and area n Compared to packaged parts on PCB, Po. P can reduce power, area and volume - Short Paths with relatively good signal integrity properties. - Saves PCB area by using vertical direction. - May lead to thermal issues if fie underneath is generating heat Balakumar January 16, 2014 NCTU IEE 5011 Memory Systems 2013 25

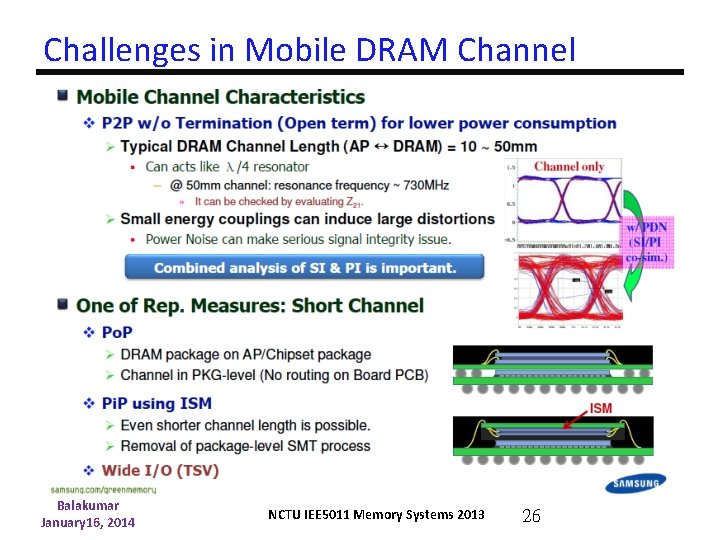

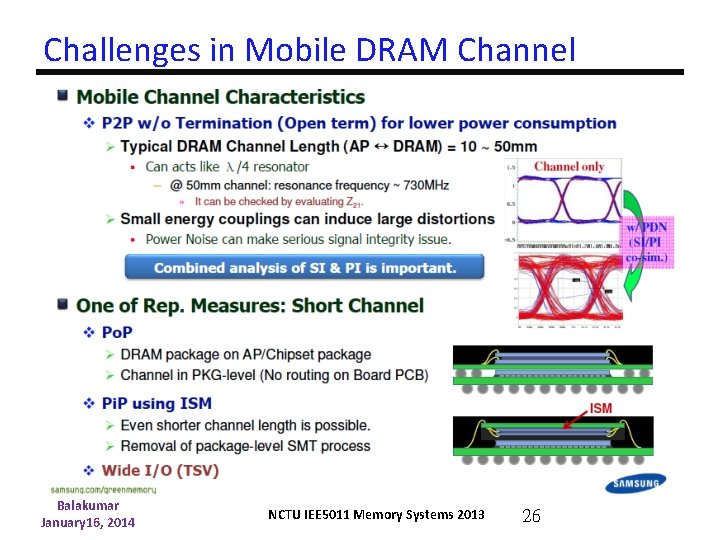

Challenges in Mobile DRAM Channel Balakumar January 16, 2014 NCTU IEE 5011 Memory Systems 2013 26

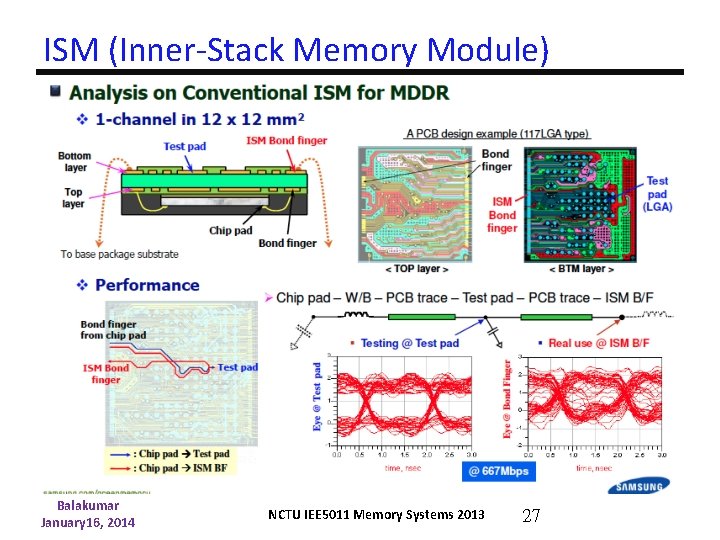

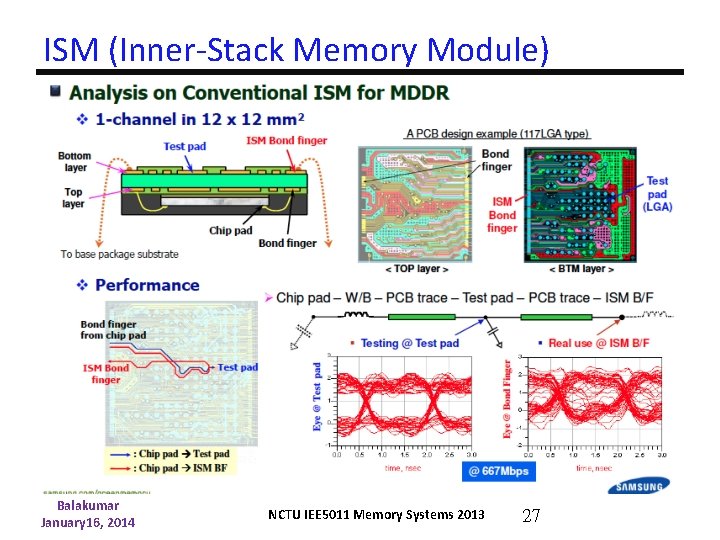

ISM (Inner-Stack Memory Module) Balakumar January 16, 2014 NCTU IEE 5011 Memory Systems 2013 27

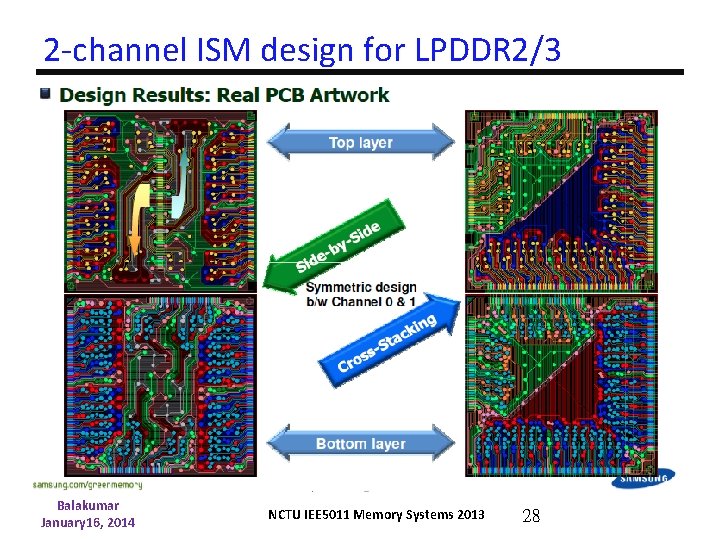

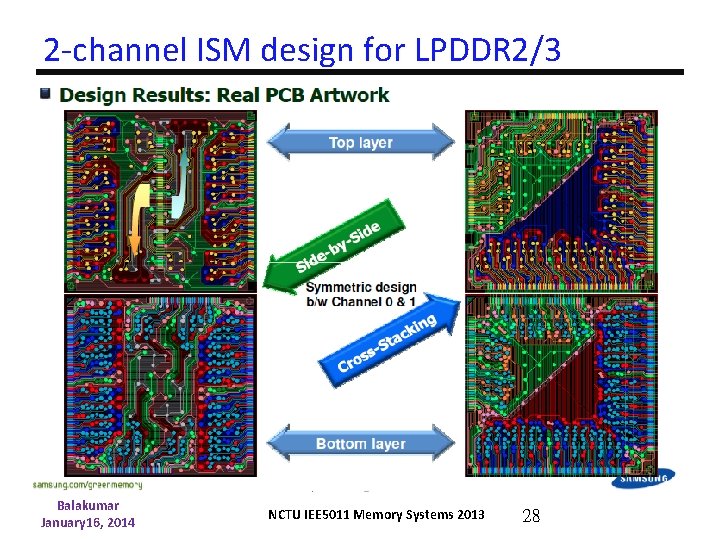

2 -channel ISM design for LPDDR 2/3 Balakumar January 16, 2014 NCTU IEE 5011 Memory Systems 2013 28

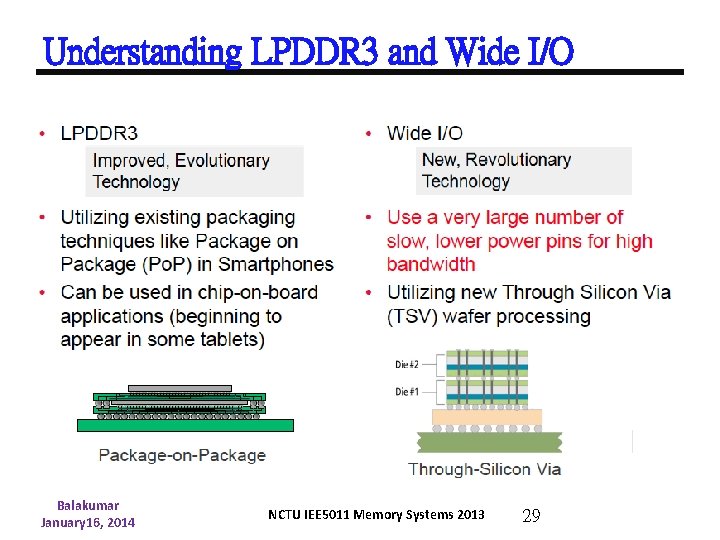

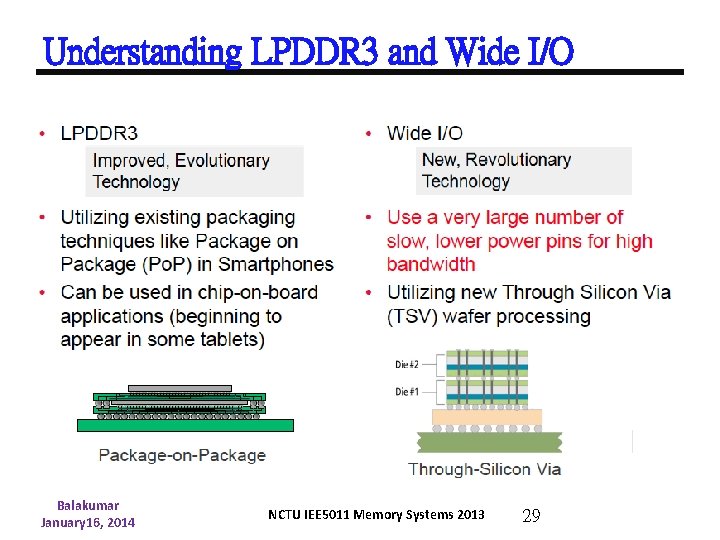

Understanding LPDDR 3 and Wide I/O Balakumar January 16, 2014 NCTU IEE 5011 Memory Systems 2013 29

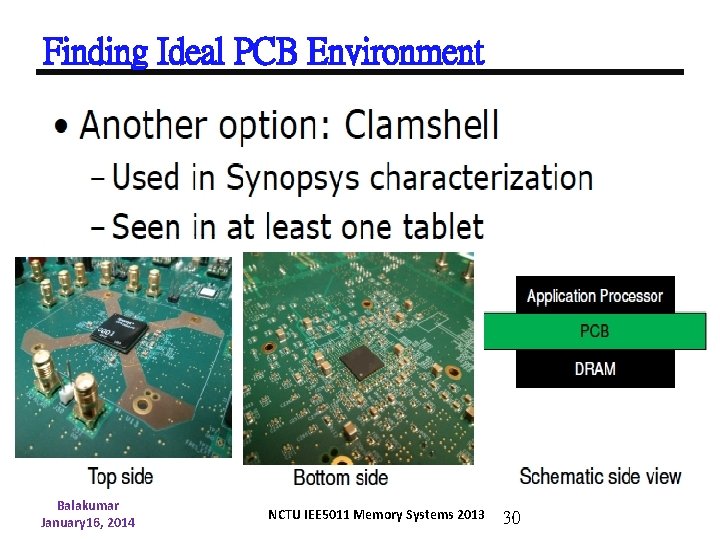

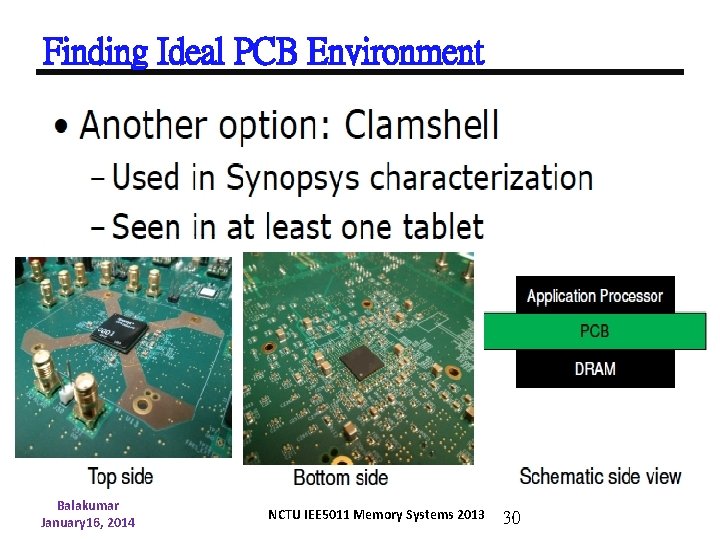

Finding Ideal PCB Environment n Pop provides very short Electrical Connection for high speed and low power - Power dissipation is limited Balakumar January 16, 2014 NCTU IEE 5011 Memory Systems 2013 30

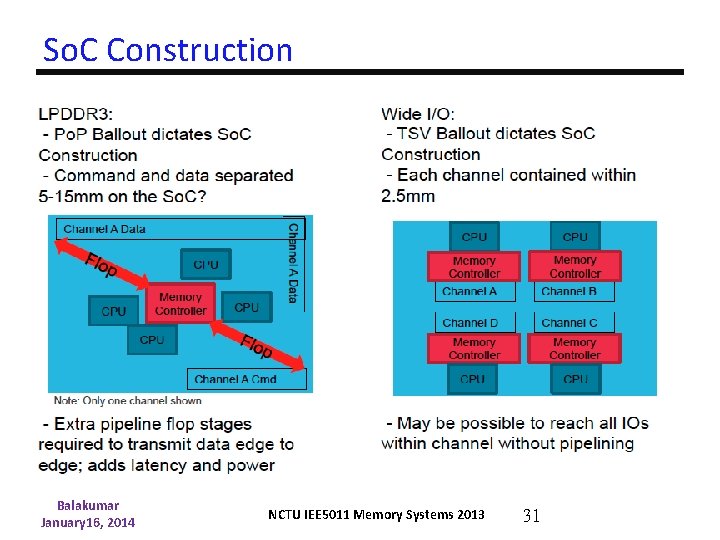

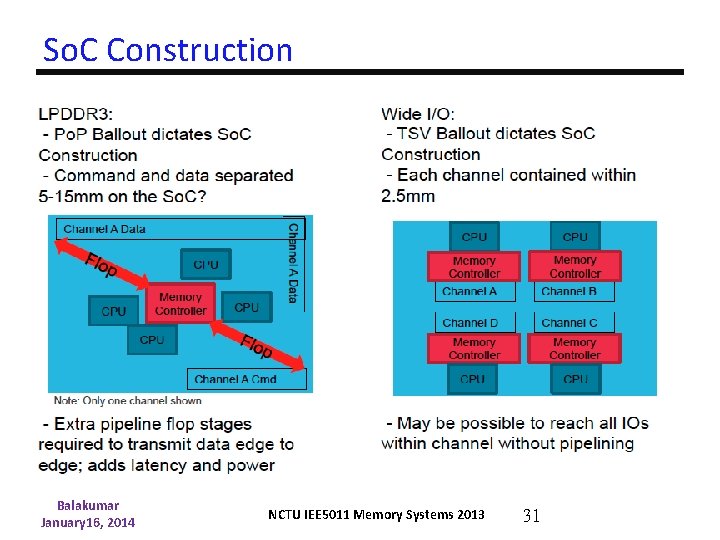

So. C Construction Balakumar January 16, 2014 NCTU IEE 5011 Memory Systems 2013 31

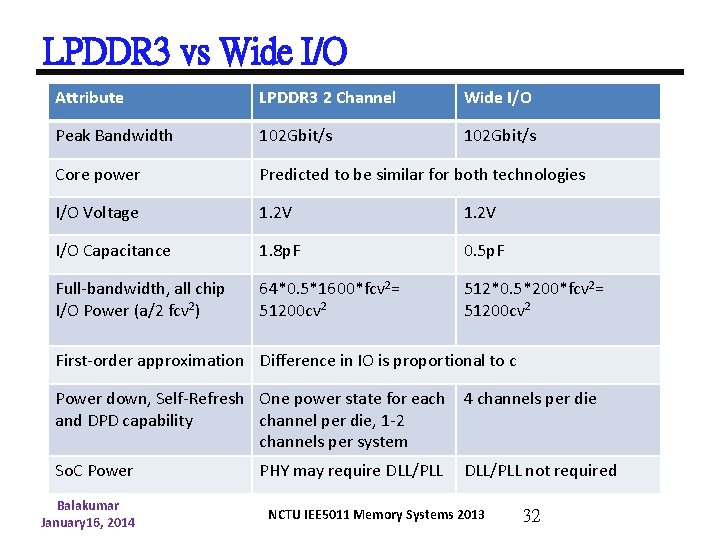

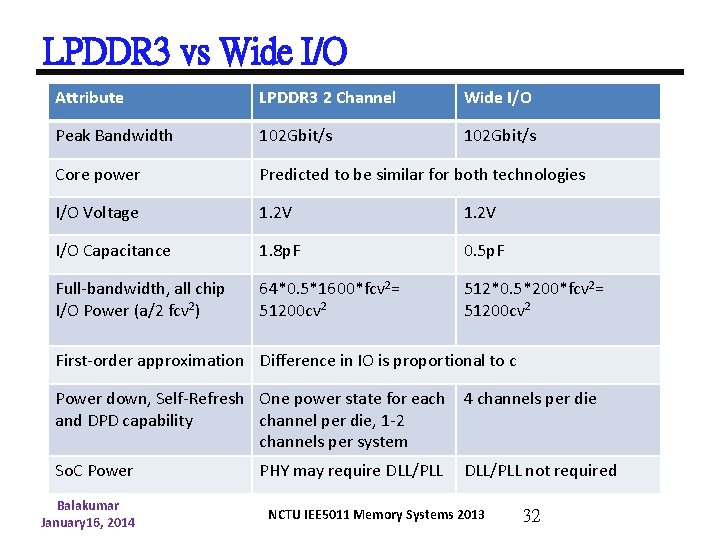

LPDDR 3 vs Wide I/O Attribute LPDDR 3 2 Channel Wide I/O Peak Bandwidth 102 Gbit/s Core power Predicted to be similar for both technologies I/O Voltage 1. 2 V I/O Capacitance 1. 8 p. F 0. 5 p. F Full-bandwidth, all chip I/O Power (a/2 fcv 2) 64*0. 5*1600*fcv 2= 51200 cv 2 512*0. 5*200*fcv 2= 51200 cv 2 First-order approximation Difference in IO is proportional to c Power down, Self-Refresh One power state for each and DPD capability channel per die, 1 -2 channels per system 4 channels per die So. C Power DLL/PLL not required Balakumar January 16, 2014 PHY may require DLL/PLL NCTU IEE 5011 Memory Systems 2013 32

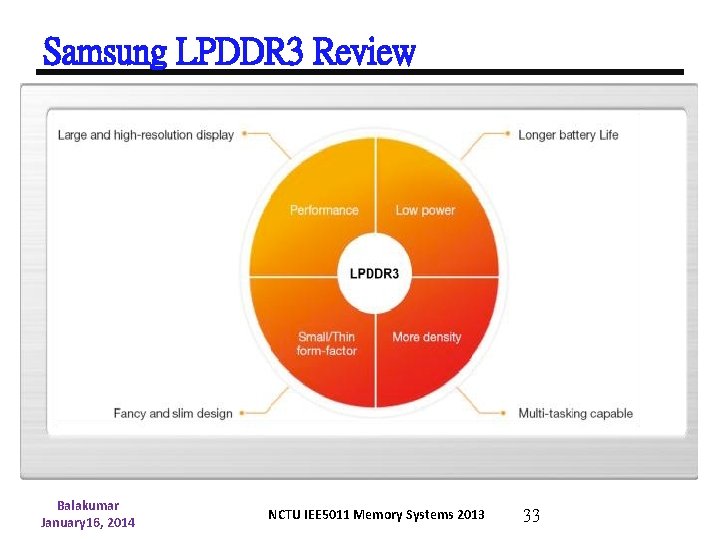

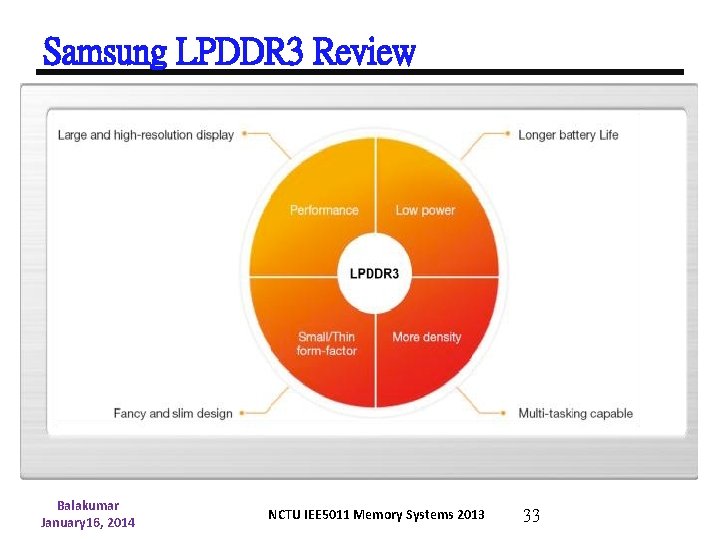

Samsung LPDDR 3 Review Balakumar January 16, 2014 NCTU IEE 5011 Memory Systems 2013 33

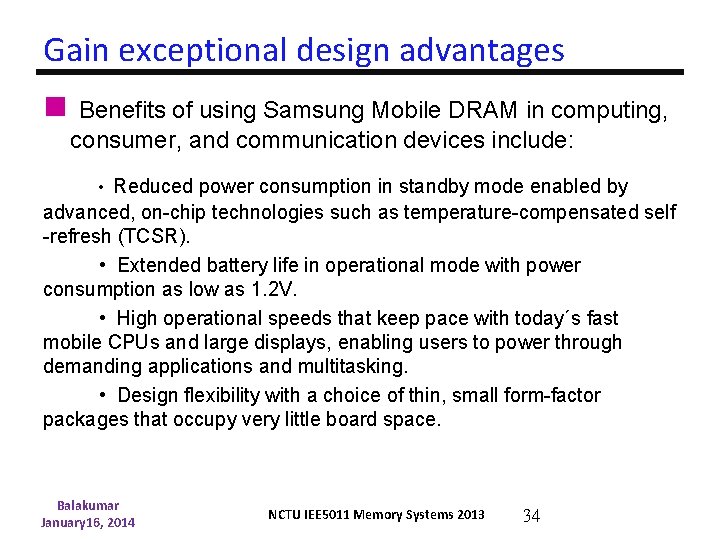

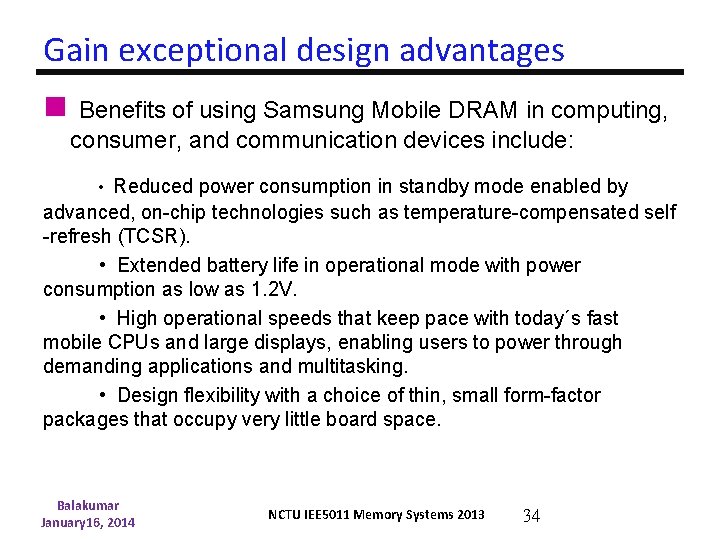

Gain exceptional design advantages n Benefits of using Samsung Mobile DRAM in computing, consumer, and communication devices include: • Reduced power consumption in standby mode enabled by advanced, on-chip technologies such as temperature-compensated self -refresh (TCSR). • Extended battery life in operational mode with power consumption as low as 1. 2 V. • High operational speeds that keep pace with today´s fast mobile CPUs and large displays, enabling users to power through demanding applications and multitasking. • Design flexibility with a choice of thin, small form-factor packages that occupy very little board space. Balakumar January 16, 2014 NCTU IEE 5011 Memory Systems 2013 34

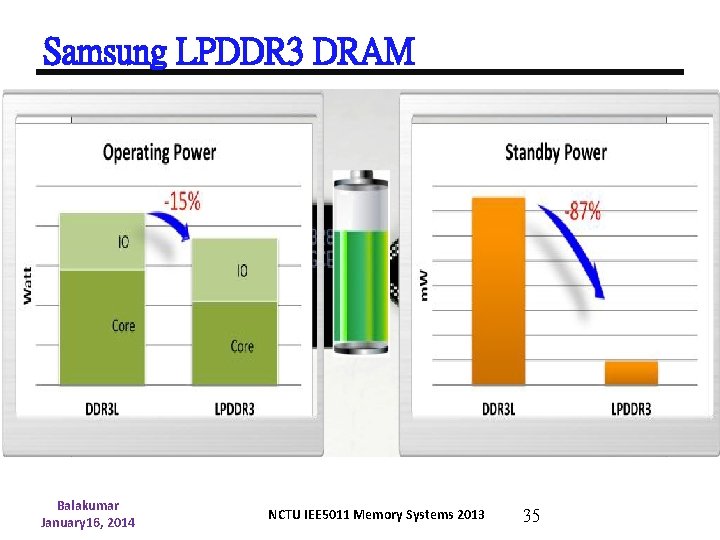

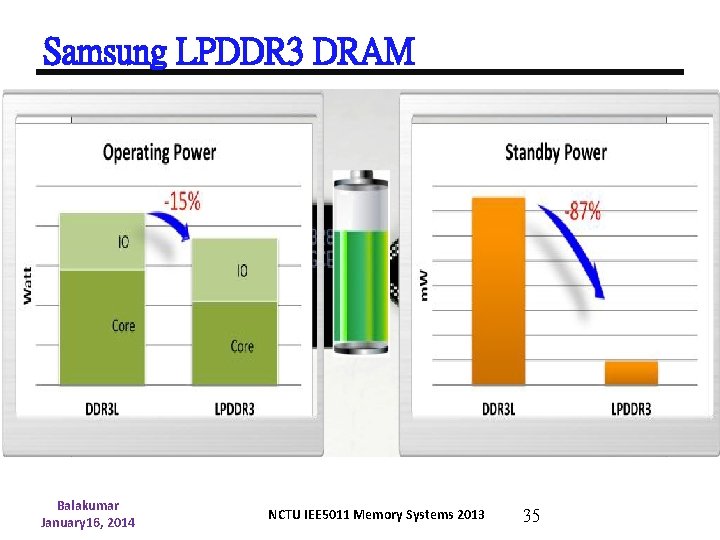

Samsung LPDDR 3 DRAM Balakumar January 16, 2014 NCTU IEE 5011 Memory Systems 2013 35

Conclusion n Future DRAM bandwidth will continue to increase n Power is reduced in LPDDR 3, but still proportional to bandwidth. n Use multiple techniques to meet performance and power goals of high bandwidth low power DRAM. Balakumar January 16, 2014 NCTU IEE 5011 Memory Systems 2013 36

Refrence 1. Young-Chul Cho; Yong-Cheol Bae; Byoung-Mo Moon; Yoon-Joo Eom; Min-Su Ahn; Won Young Lee; Cheong-Ryong Cho; Min-Ho Park; Young-Jin Jeon; Jin-Oh Ahn; Baek-Kyu Choi; Dan-Kyu Kang; Sang-Hyuk Yoon; Yun-Seok Yang; Kwang-Il Park; Jung-Hwan Choi; Jung-Bae Lee; Joo. Sun Choi, "A Sub-1. 0 V 20 nm 5 Gb/s/pin post-LPDDR 3 I/O interface with Low. Voltage-Swing Terminated Logic and adaptive calibration scheme for mobile application, " VLSICircuits (VLSIC), 2013 Symposium on , vol. , no. , pp. C 240, C 241, 12 -14 June 2013. 2. A. B. Kahng and V. Srinivas, “Mobile System Considerations for SDRAM Interface Trends, ” in Proc. SLIP, 2011. 3. Nomura, T. ; Mori, R. ; Ito, M. ; Takayanagi, K. ; Ochiai, T. ; Fukuoka, K. ; Otsuga, K. ; Nii, K. ; Morita, S. ; Hashimoto, T. ; Kida, T. ; Yamada, J. ; Tanaka, H. , "Testability improvement for 12. 8 GB/s Wide IO DRAM controller by small area pre-bonding TSV tests and a 1 GHz sampled fully digital noise monitor, " Custom Integrated Circuits Conference (CICC), 2013 IEEE , vol. , no. , pp. 1, 4, 22 -25 Sept. 2013. 4. Leibowitz, B, et al. “A 4. 3 GB/s Mobile Memory Interface With Power-Efficient BW Scaling” IEEE JSSC, pp, 889 -898, Feb. 2010. 5. Weis, C. ; Loi, I. ; Benini, L. ; Wehn, N. , "Exploration and Optimization of 3 -D Integrated DRAM Subsystems, " Computer-Aided Design of Integrated Circuits and Systems, IEEE Transactions on , vol. 32, no. 4, pp. 597, 610, April 2013. 6. Gomony, M. D. ; Weis, C. ; Akesson, B. ; When, N. ; Goossens, K. , "DRAM selection and configuration for real-time mobile systems, " Design, Automation & Test in Europe Conference & Exhibition (DATE), 2012 , vol. , no. , pp. 51, 56, 12 -16 March 2012 doi: 10. 1109/DATE. 2012. 6176432. 7. “JEDEC Low Power Double Data Rate (LPDDR 3) SDRAM Standard, ” Sep 2011. 8. Balakumar “JEDEC Low Power Double Data Rate (LPDDR 2) SDRAM Standard, ” Dec 2010. NCTU IEE 5011 Memory Systems 2013 37 January 16, 2014 9. “JEDEC Low Power Double Data Rate (LPDDR) SDRAM Standard, ” Feb 2009.

Reference 10. B. Akesson et al. , “Memory Controllers for High-Performance and Real-Time MPSo. Cs, ” in Proc. CODES+ISSS, 2011. JEDEC Standard Wide IO SDR specification. Dec. 2011. 12. Y. C. Bae, et al. “A 1. 2 V 1. 6 Gb/s/pin 4 Gb Low Power DDR 3 SDRAM with Input Skew Calibration and Enhanced Refresh Control Schemes” IEEE ISSCC, pp. 44 -45, Feb. 2012. 13. Park, S. -S. et ai, "Integrated circuit package-inpackage system with side-by-side and offset packaging, US patent. No. US 7, 812, 435 B 2. 14. http: //www. samsung. com/global/business/semiconductor/product/mobile-dram/overview. 15. http: //www. samsung. com/global/business/semiconductor/newsevents/pressreleases/detail? news. Id=12979. 16. https: //memorylink. samsung. com/ecomobile/mem/ecomobile/product. Overview. do? top. Me nu=P&sub. Menu=mobile. Dram&part. Set. No=LPDDR 3&part. Set. Label=LPDDR 3. Balakumar January 16, 2014 NCTU IEE 5011 Memory Systems 2013 38