IEE 5011 Fall 2013 Memory Systems Wide IO

- Slides: 25

IEE 5011 –Fall 2013 Memory Systems Wide I/O High Bandwidth DRAM Yi-Lin, Tu Department of Electronics Engineering National Chiao Tung University b 22531423@hotmail. com Yi-Lin, Tu 2013

Outline n Introduction n Proximity Communication n A Wide I/O DRAM Architecture n Conclusion n Reference Yi-Lin, Tu NCTU IEE 5011 Memory Systems 2013 2

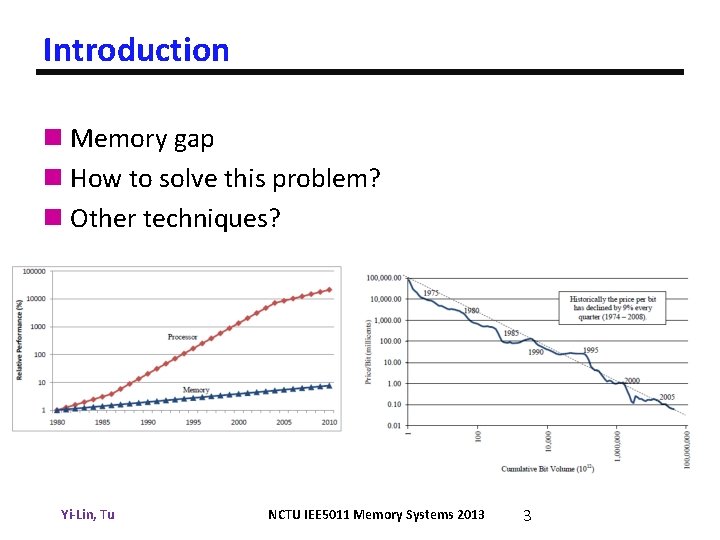

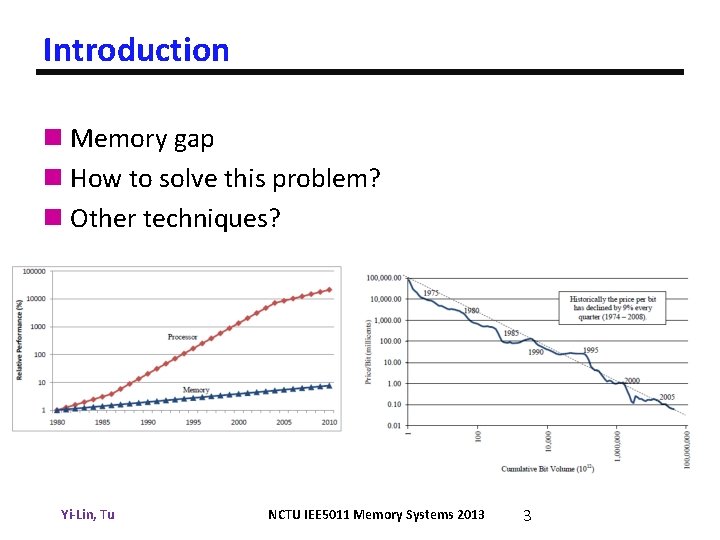

Introduction n Memory gap n How to solve this problem? n Other techniques? Yi-Lin, Tu NCTU IEE 5011 Memory Systems 2013 3

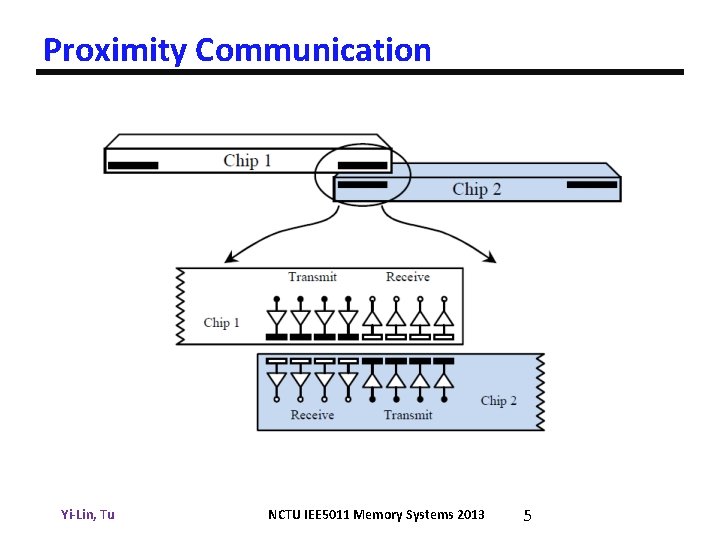

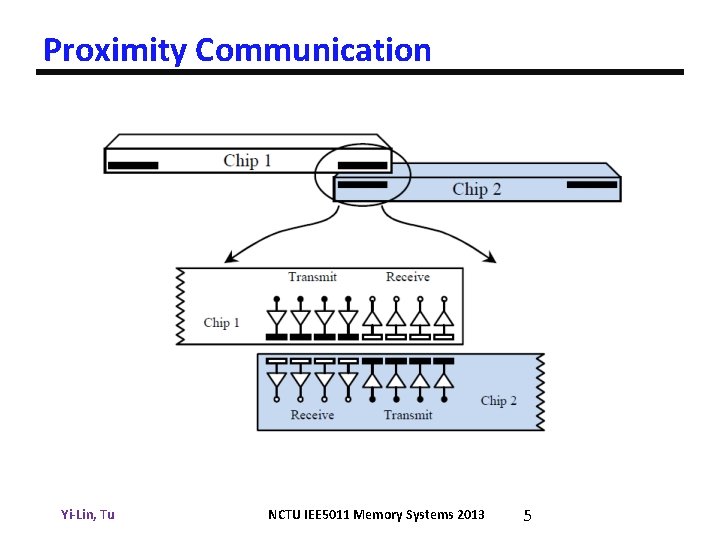

Proximity Communication n A wireless chip-to-chip communication technology. n Two chips are placed face to face and their bonding pads are allowed to come within close proximity of each other without touching. Yi-Lin, Tu NCTU IEE 5011 Memory Systems 2013 4

Proximity Communication Yi-Lin, Tu NCTU IEE 5011 Memory Systems 2013 5

Proximity Communication n Advantages l Increase I/O density l Remove the on/off chip wires l Remove the on-die termination l Ease of testability l Remove the ESD structures Yi-Lin, Tu NCTU IEE 5011 Memory Systems 2013 6

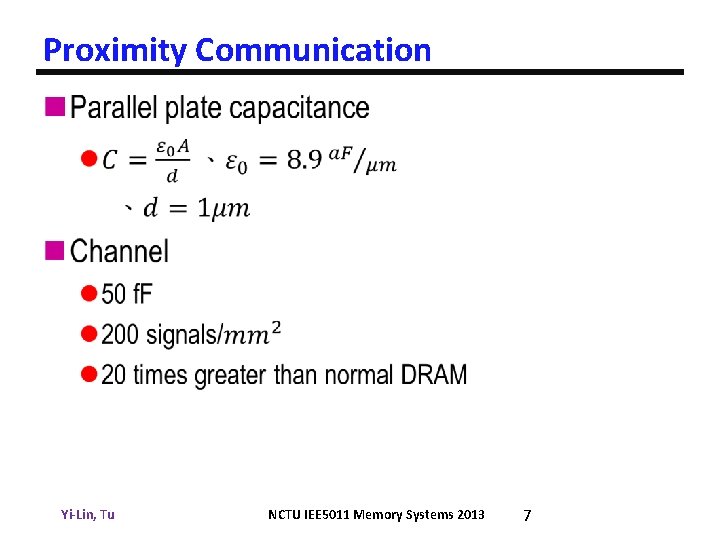

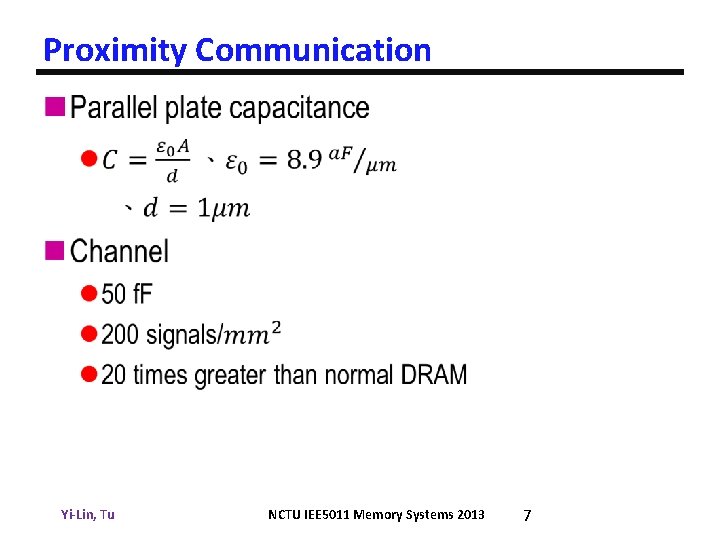

Proximity Communication n Yi-Lin, Tu NCTU IEE 5011 Memory Systems 2013 7

Proximity Communication n Challenges l Mechanical misalignment l Supplying power to chips l Thermal removal Yi-Lin, Tu NCTU IEE 5011 Memory Systems 2013 8

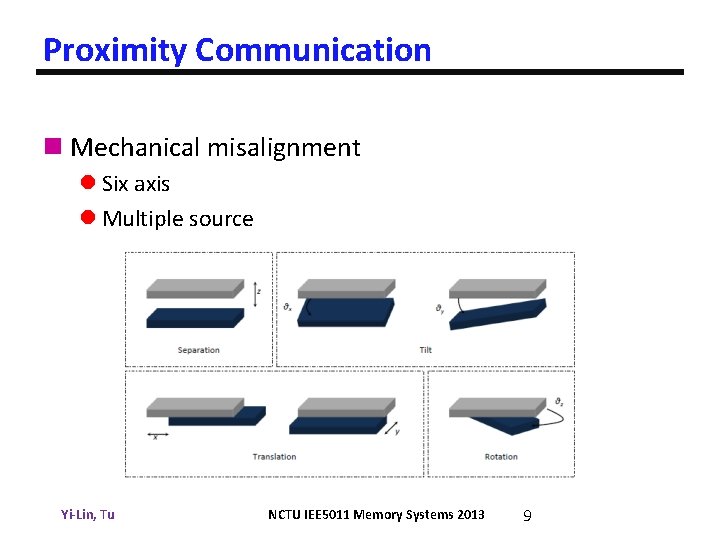

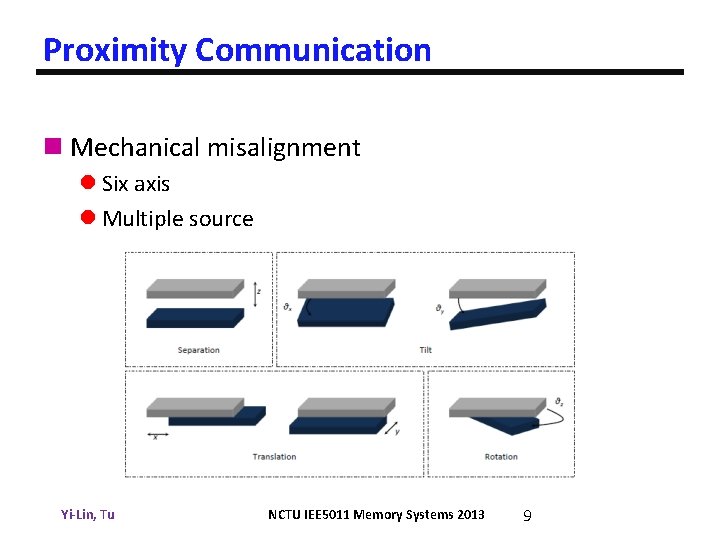

Proximity Communication n Mechanical misalignment l Six axis l Multiple source Yi-Lin, Tu NCTU IEE 5011 Memory Systems 2013 9

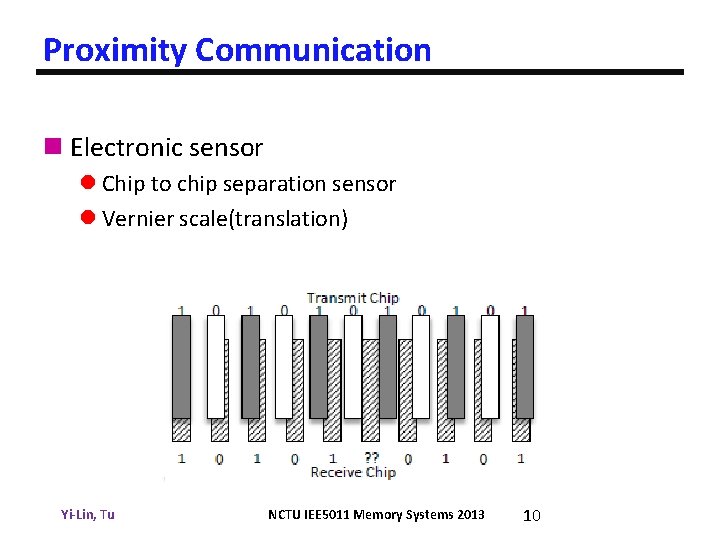

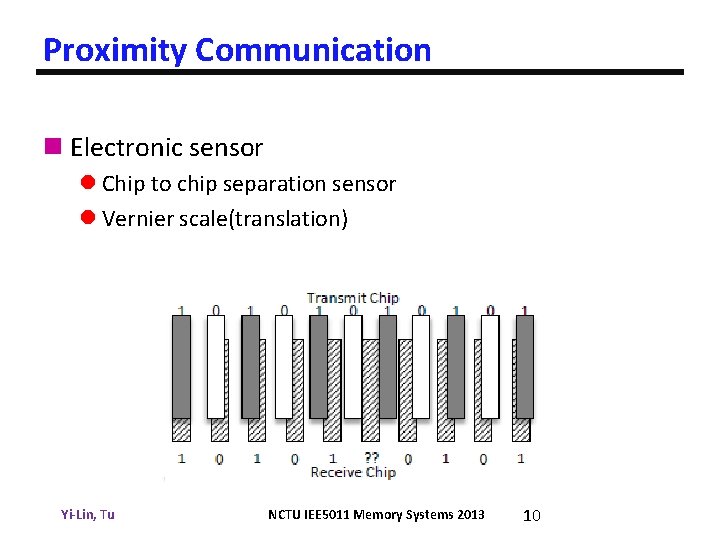

Proximity Communication n Electronic sensor l Chip to chip separation sensor l Vernier scale(translation) Yi-Lin, Tu NCTU IEE 5011 Memory Systems 2013 10

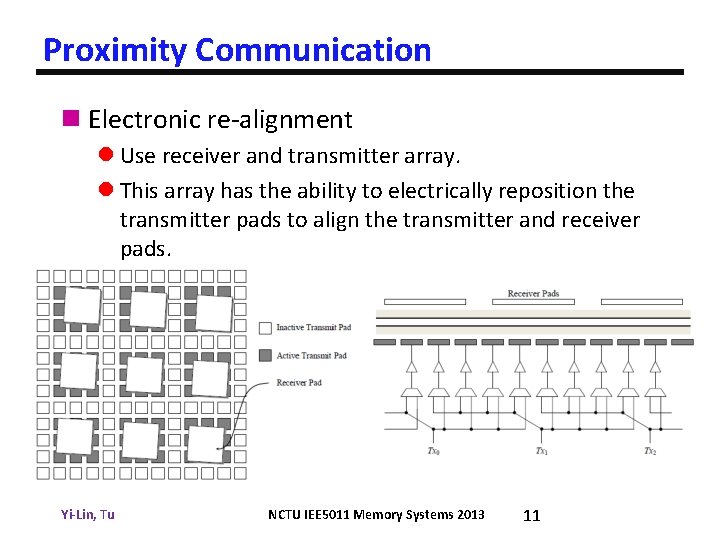

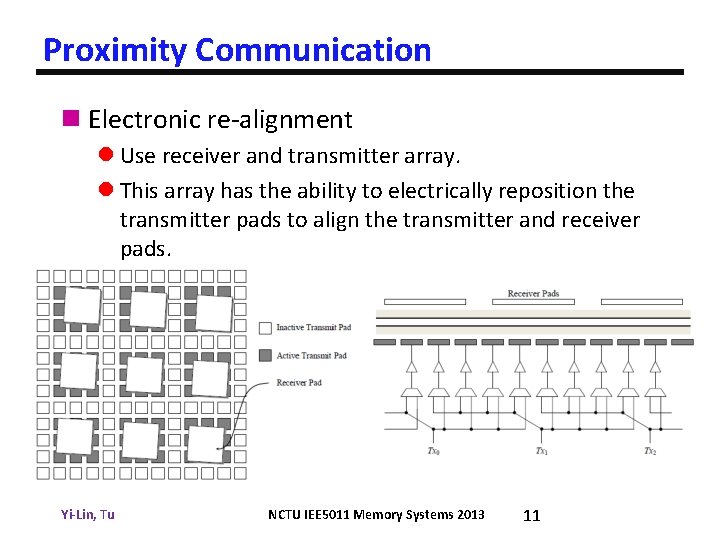

Proximity Communication n Electronic re-alignment l Use receiver and transmitter array. l This array has the ability to electrically reposition the transmitter pads to align the transmitter and receiver pads. Yi-Lin, Tu NCTU IEE 5011 Memory Systems 2013 11

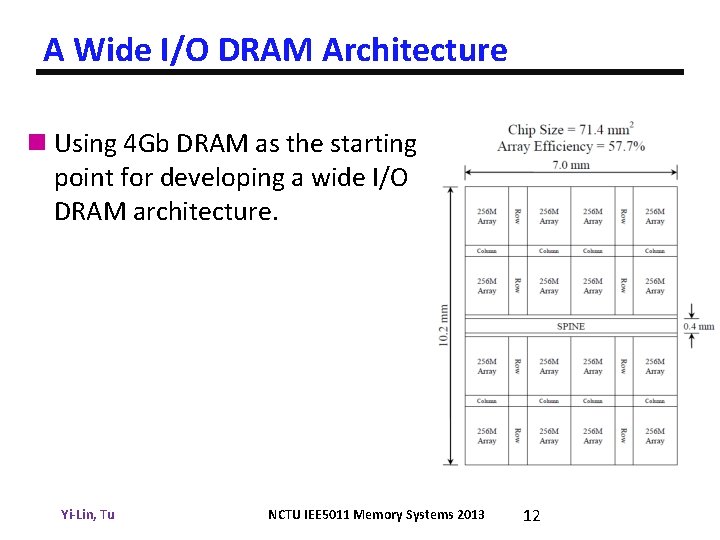

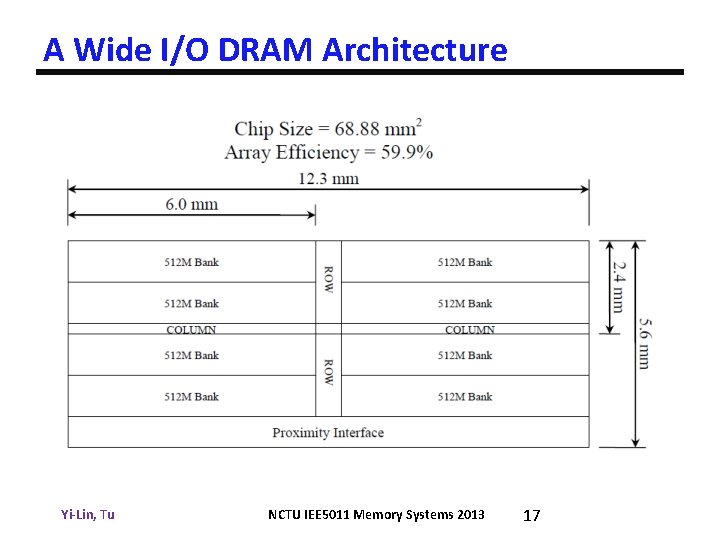

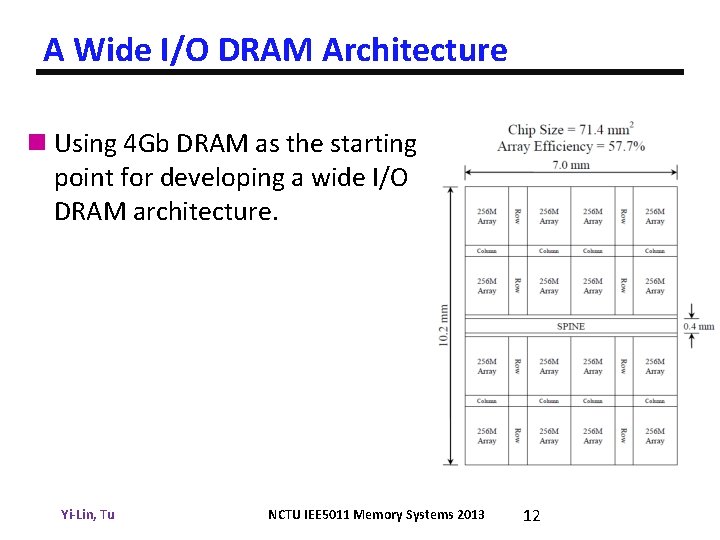

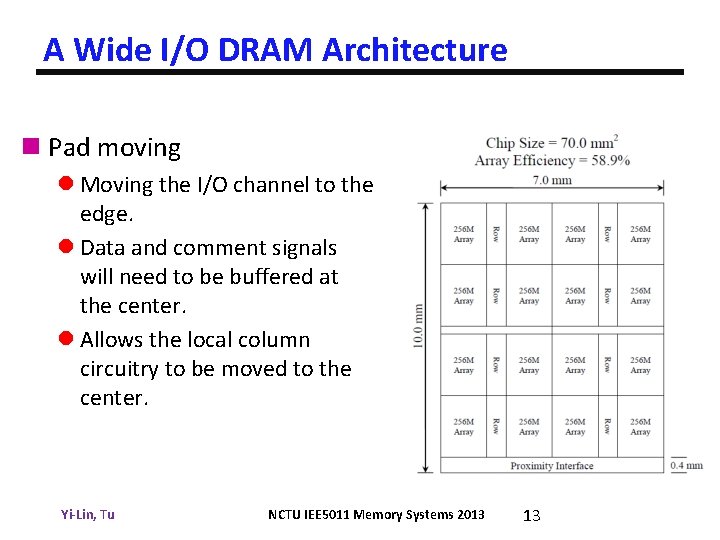

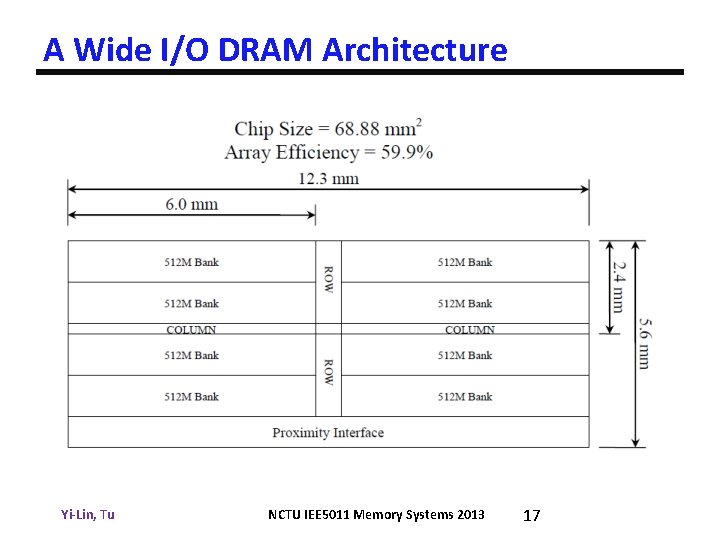

A Wide I/O DRAM Architecture n Using 4 Gb DRAM as the starting point for developing a wide I/O DRAM architecture. Yi-Lin, Tu NCTU IEE 5011 Memory Systems 2013 12

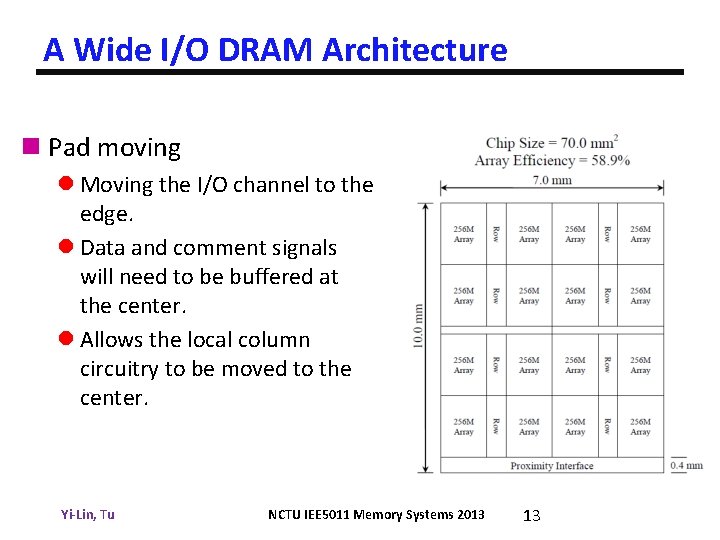

A Wide I/O DRAM Architecture n Pad moving l Moving the I/O channel to the edge. l Data and comment signals will need to be buffered at the center. l Allows the local column circuitry to be moved to the center. Yi-Lin, Tu NCTU IEE 5011 Memory Systems 2013 13

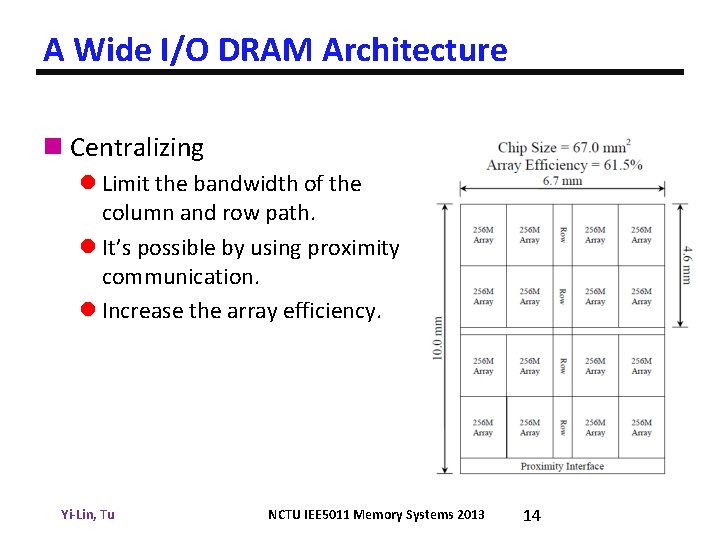

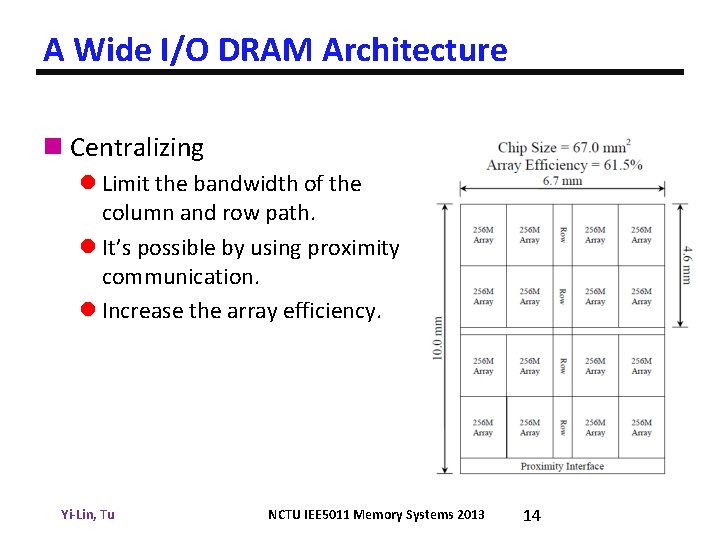

A Wide I/O DRAM Architecture n Centralizing l Limit the bandwidth of the column and row path. l It’s possible by using proximity communication. l Increase the array efficiency. Yi-Lin, Tu NCTU IEE 5011 Memory Systems 2013 14

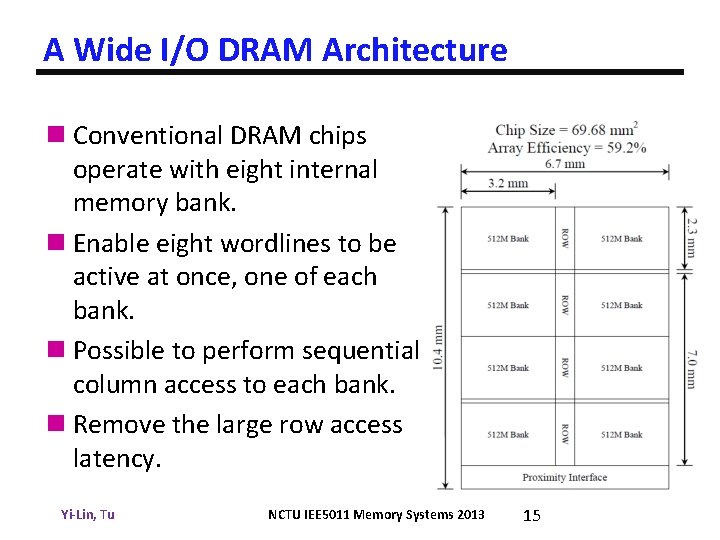

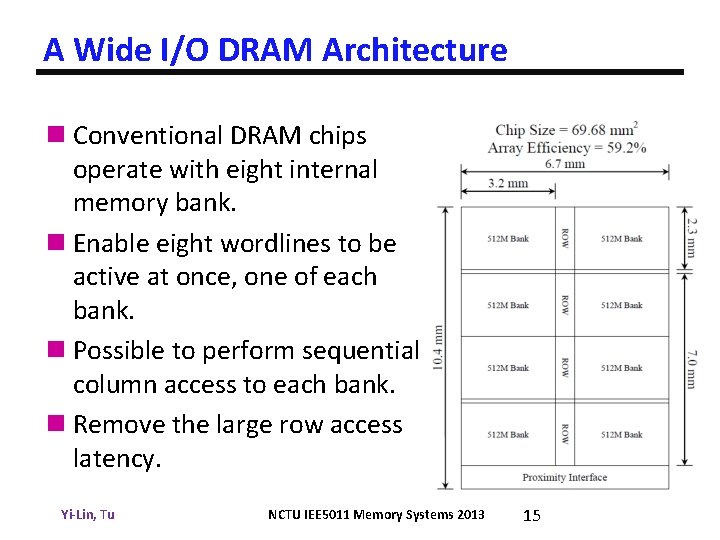

A Wide I/O DRAM Architecture n Conventional DRAM chips operate with eight internal memory bank. n Enable eight wordlines to be active at once, one of each bank. n Possible to perform sequential column access to each bank. n Remove the large row access latency. Yi-Lin, Tu NCTU IEE 5011 Memory Systems 2013 15

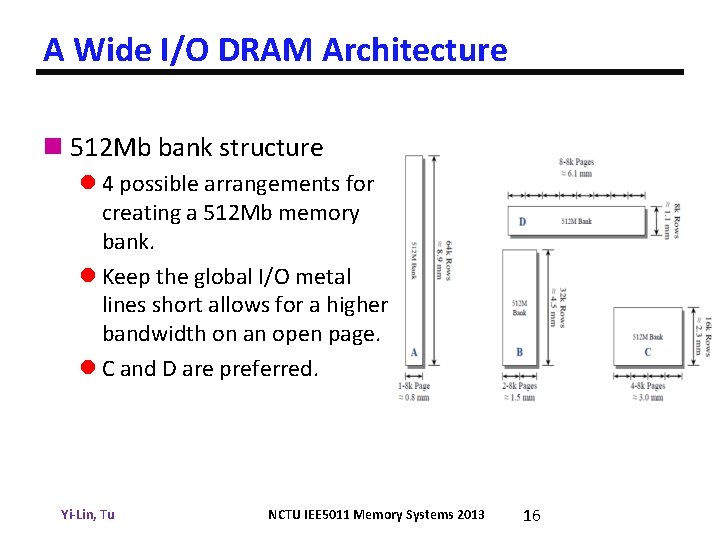

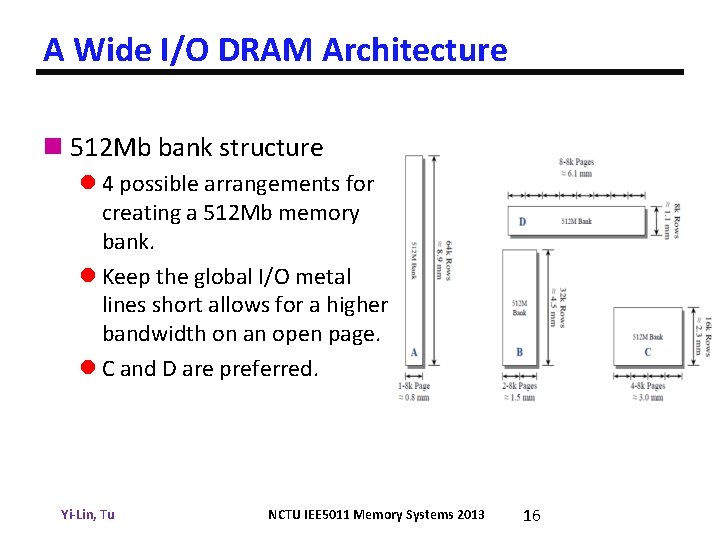

A Wide I/O DRAM Architecture n 512 Mb bank structure l 4 possible arrangements for creating a 512 Mb memory bank. l Keep the global I/O metal lines short allows for a higher bandwidth on an open page. l C and D are preferred. Yi-Lin, Tu NCTU IEE 5011 Memory Systems 2013 16

A Wide I/O DRAM Architecture Yi-Lin, Tu NCTU IEE 5011 Memory Systems 2013 17

A Wide I/O DRAM Architecture n Challenges l Number of metal layers l Global I/O routing l Local I/O routing Yi-Lin, Tu NCTU IEE 5011 Memory Systems 2013 18

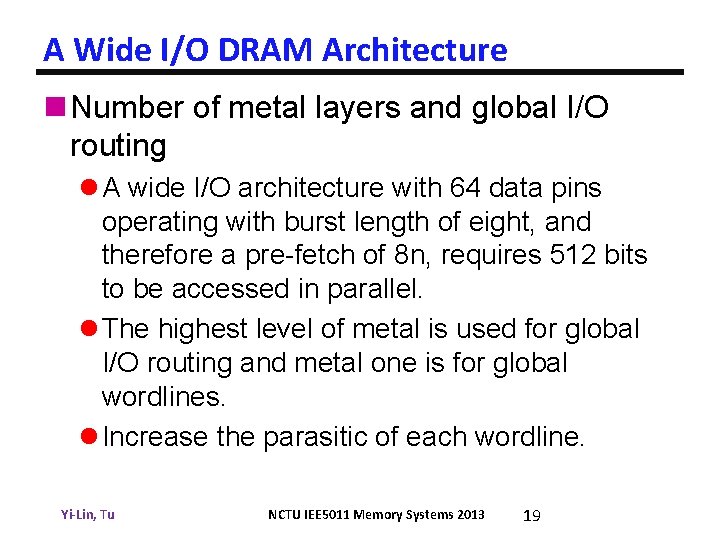

A Wide I/O DRAM Architecture n Number of metal layers and global I/O routing l A wide I/O architecture with 64 data pins operating with burst length of eight, and therefore a pre-fetch of 8 n, requires 512 bits to be accessed in parallel. l The highest level of metal is used for global I/O routing and metal one is for global wordlines. l Increase the parasitic of each wordline. Yi-Lin, Tu NCTU IEE 5011 Memory Systems 2013 19

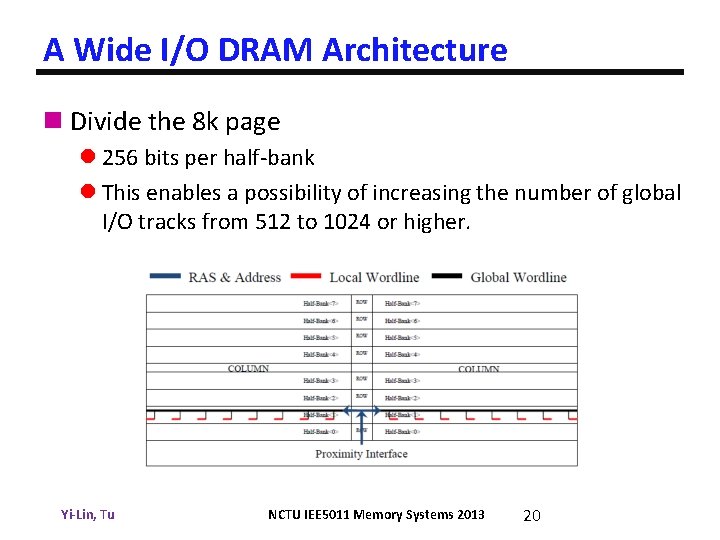

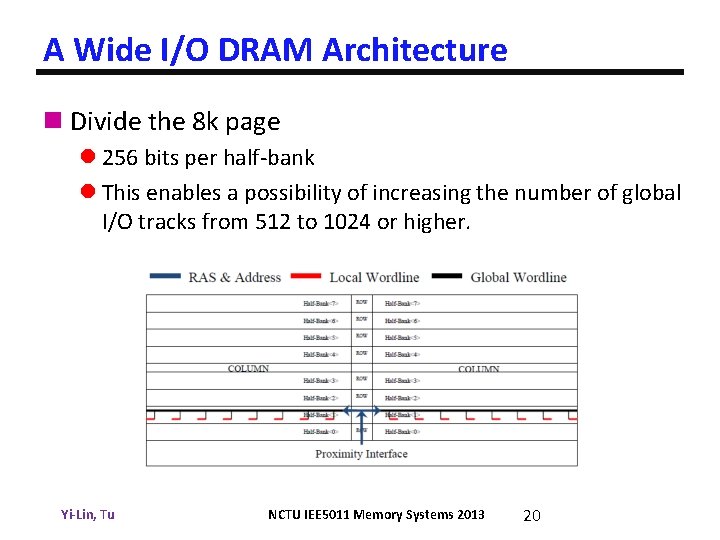

A Wide I/O DRAM Architecture n Divide the 8 k page l 256 bits per half-bank l This enables a possibility of increasing the number of global I/O tracks from 512 to 1024 or higher. Yi-Lin, Tu NCTU IEE 5011 Memory Systems 2013 20

A Wide I/O DRAM Architecture n Local I/O routing l The large number of global I/O tracks requires 32 data signals from each 256 kb memory array. l Moving 32 data signals from the bitline sense amplifiers to the global I/O track is a major challenge due to the limited routing space above the bitline sense amplifiers. l Signals can be routed to the top and bottom of each 256 kb memory segment. Yi-Lin, Tu NCTU IEE 5011 Memory Systems 2013 21

A Wide I/O DRAM Architecture n Summary l Developing a wide I/O DRAM architecture that is suitable for Proximity Communication requires the communication channel to be moved to the side of the DRAM chip. l A distributed page and bank structure was developed to enable the possibility of using Proximity Communication with 32 data pins. l Reaching the use of 64 data pins required architectural changes that would not increase the manufacturing cost compared to current DRAM architectures. Yi-Lin, Tu NCTU IEE 5011 Memory Systems 2013 22

Conclusion n A DRAM architecture that uses proximity communication to increase the off-chip bandwidth while scaling the number of data pins. n Proximity communication allows for an increase of I/O density, ease of testability, removal of ESD structures and resistive termination. n Electrical sensors and electrical re-alignment techniques has enabled proximity communication to become a viable I/O technology. n The challenges of creating a wide I/O Yi-Lin, Tu NCTU IEE 5011 Memory Systems 2013 23 architecture were found to be in the global and

Reference n Q. Harvard, “Wide I/O DRAM architecture utilizing proximity communication, ” Master’s thesis, Boise State University, December 2009. n Q. Harvard, R. J. Baker, and R. Drost, “Main memory with proximity communication: A wide I/O DRAM architecture, ” in Proc. IEEE Workshop Microelectron. Electron Devices, Apr. 2010, pp. 1– 4. n Harvard, Q. , Baker, R. J. , “A scalable I/O architecture for wide I/O DRAM, ” 54 th International Midwest Symposium on Circuits and Systems (MWSCAS), 7 -10 Aug. 2011, Seoul, 2011 Yi-Lin, Tu NCTU IEE 5011 Memory Systems 2013 24

Thank you Yi-Lin, Tu 2013 25