FAMUFSU College of Engineering EEL 3705 3705 L

- Slides: 80

FAMU-FSU College of Engineering EEL 3705 / 3705 L Digital Logic Design Spring 2007 Instructor: Dr. Michael Frank Module #99 (Extra Slides): Design Examples 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 1

FAMU-FSU College of Engineering MAX 7000 Programming Example Demonstration of the Design and Programming of an Extremely Simple Example Circuit for the MAX 7000 PLD in Quartus 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 2

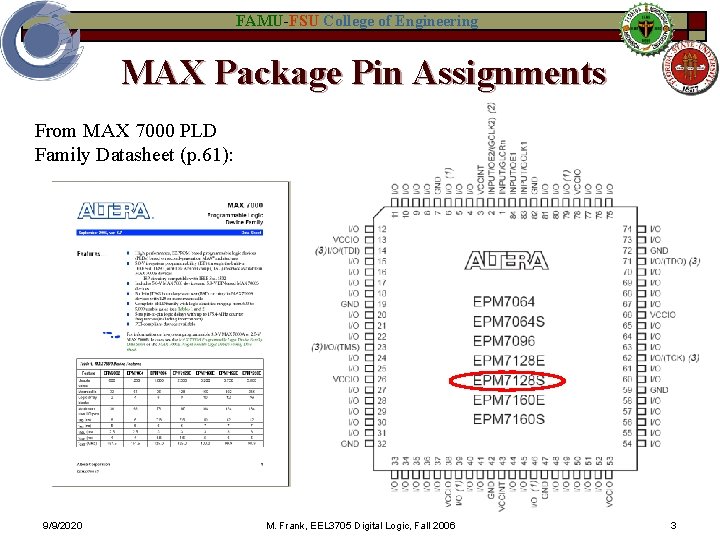

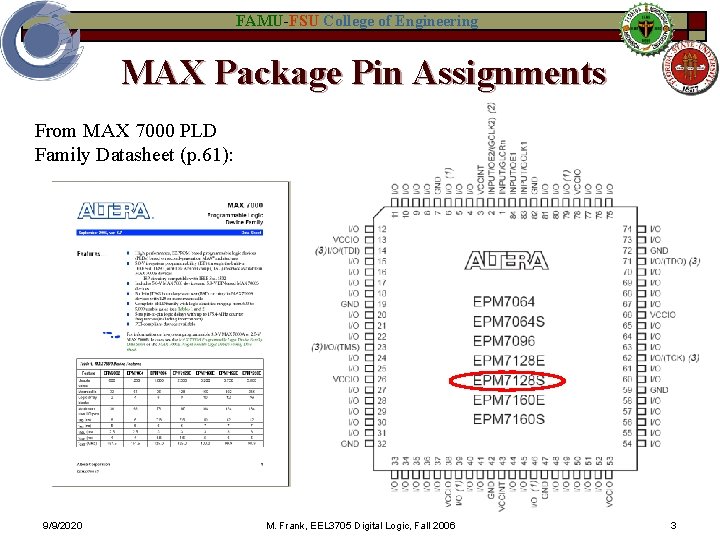

FAMU-FSU College of Engineering MAX Package Pin Assignments From MAX 7000 PLD Family Datasheet (p. 61): 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 3

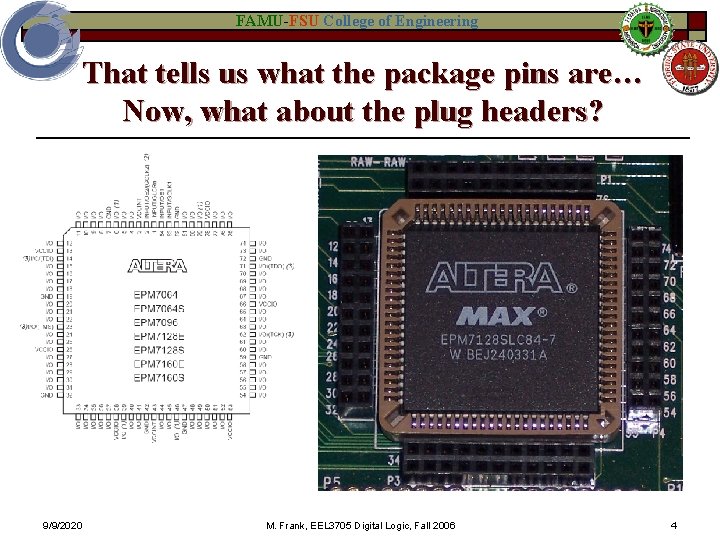

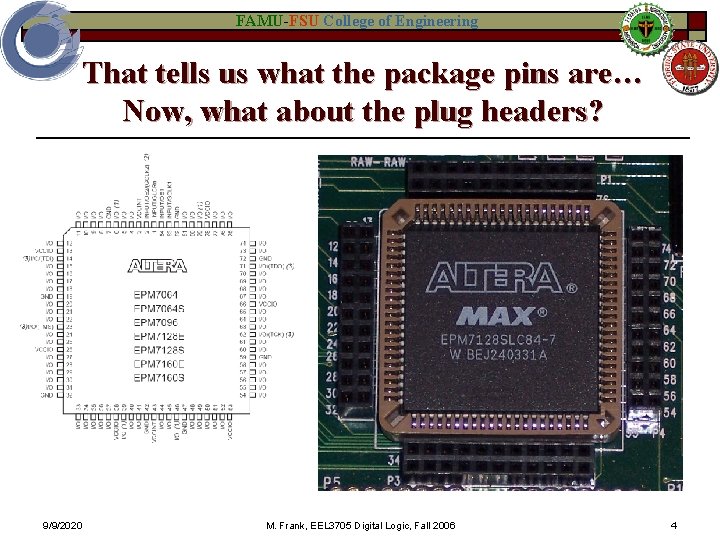

FAMU-FSU College of Engineering That tells us what the package pins are… Now, what about the plug headers? 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 4

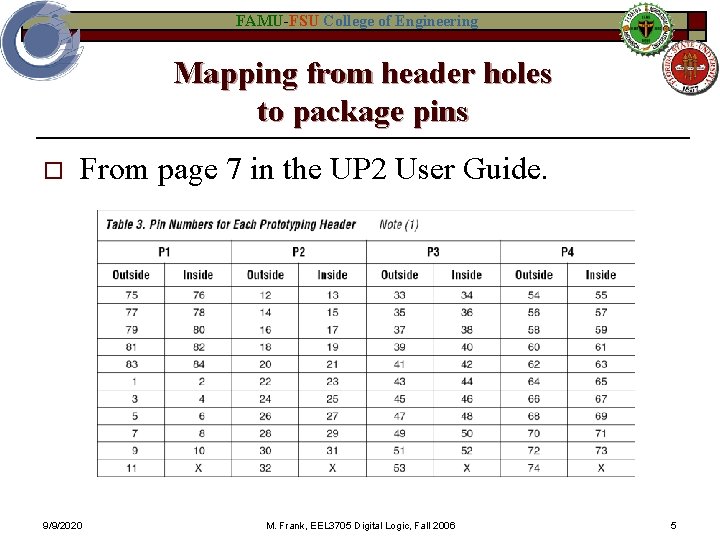

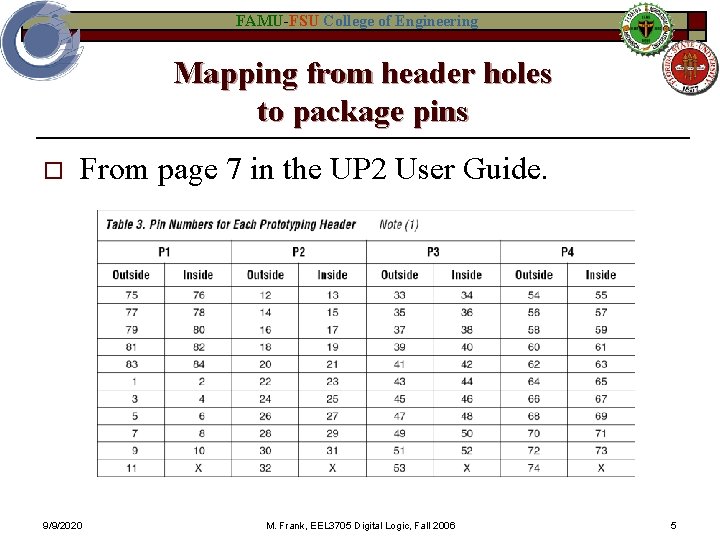

FAMU-FSU College of Engineering Mapping from header holes to package pins o From page 7 in the UP 2 User Guide. 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 5

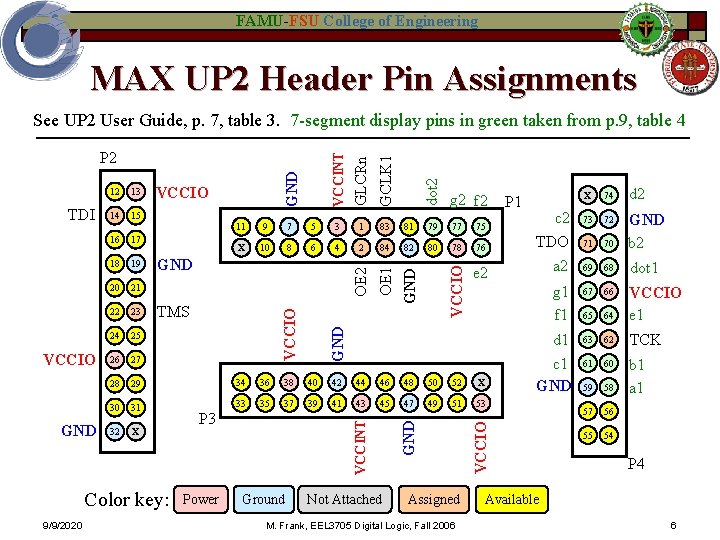

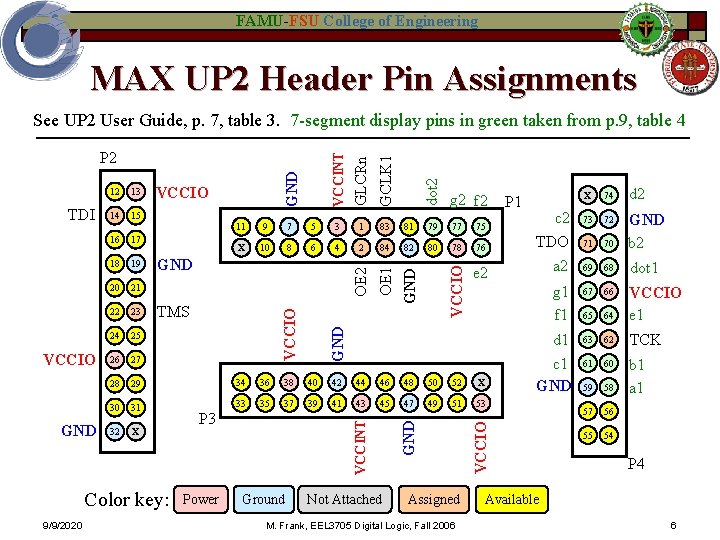

FAMU-FSU College of Engineering MAX UP 2 Header Pin Assignments See UP 2 User Guide, p. 7, table 3. 7 -segment display pins in green taken from p. 9, table 4 GCLK 1 7 5 3 1 83 81 79 77 75 X 10 8 6 4 2 84 82 80 78 76 VCCIO e 2 dot 2 GLCRn 9 g 2 f 2 17 18 19 20 21 22 23 24 25 26 27 28 29 34 36 38 40 42 44 46 48 50 52 X 30 31 33 35 37 39 41 43 45 47 49 51 53 32 X OE 2 GND Power Ground Not Attached Assigned M. Frank, EEL 3705 Digital Logic, Fall 2006 P 1 X 74 d 2 c 2 TDO 73 72 71 70 GND b 2 a 2 69 68 dot 1 g 1 f 1 67 66 65 64 VCCIO e 1 d 1 c 1 GND 63 62 TCK 61 60 59 58 b 1 a 1 57 56 55 54 VCCIO P 3 GND TMS OE 1 GND 16 Color key: 9/9/2020 11 GND 15 VCCINT GND 14 VCCIO GND VCCIO 13 VCCIO TDI 12 VCCINT P 2 P 4 Available 6

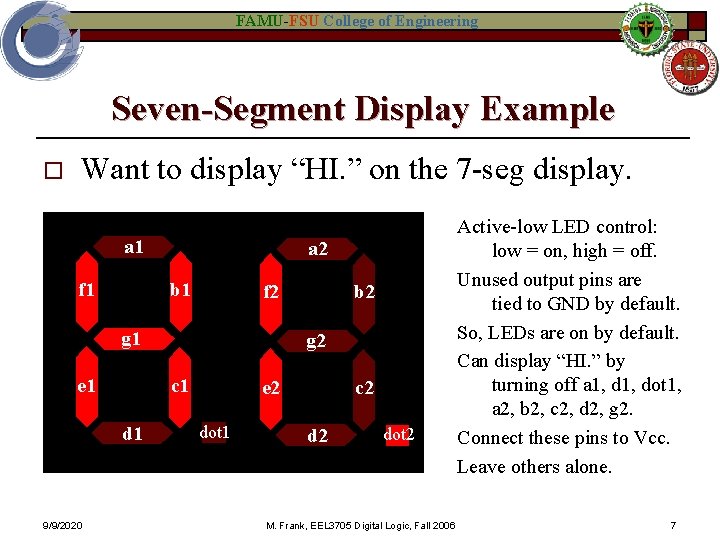

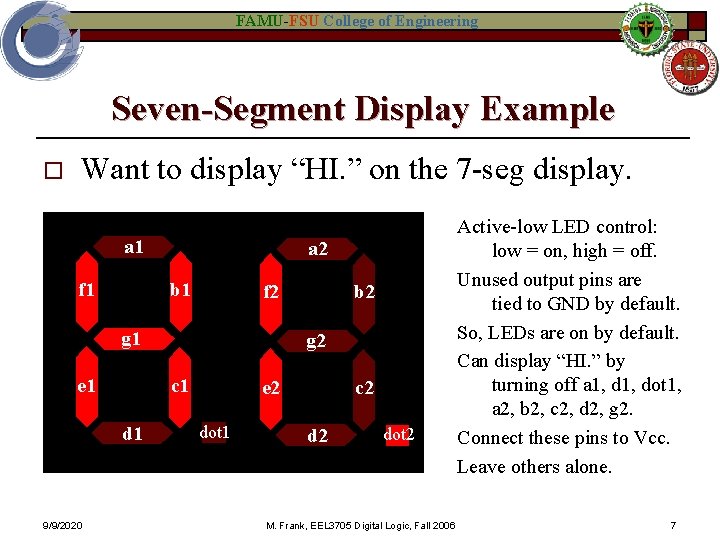

FAMU-FSU College of Engineering Seven-Segment Display Example o Want to display “HI. ” on the 7 -seg display. a 1 f 1 a 2 b 1 f 2 g 1 e 1 9/9/2020 g 2 c 1 d 1 b 2 e 2 dot 1 c 2 dot 2 M. Frank, EEL 3705 Digital Logic, Fall 2006 Active-low LED control: low = on, high = off. Unused output pins are tied to GND by default. So, LEDs are on by default. Can display “HI. ” by turning off a 1, dot 1, a 2, b 2, c 2, d 2, g 2. Connect these pins to Vcc. Leave others alone. 7

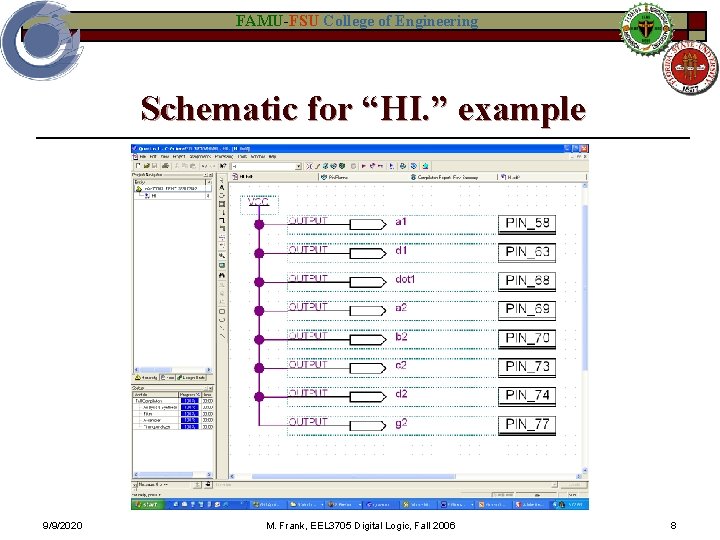

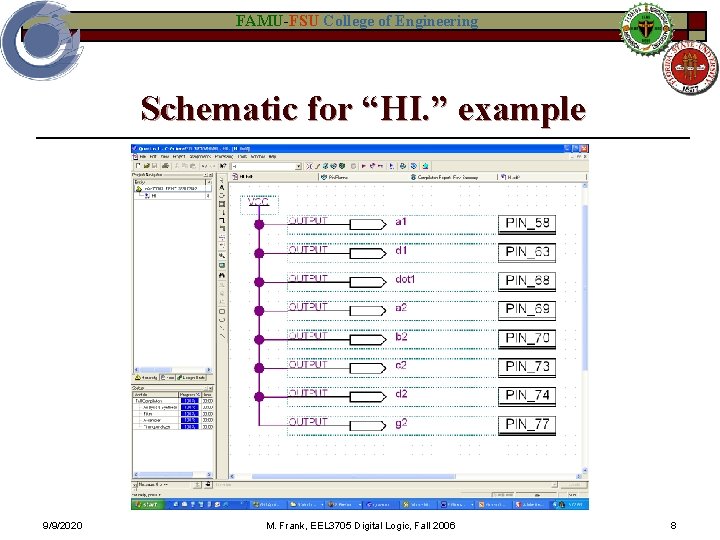

FAMU-FSU College of Engineering Schematic for “HI. ” example 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 8

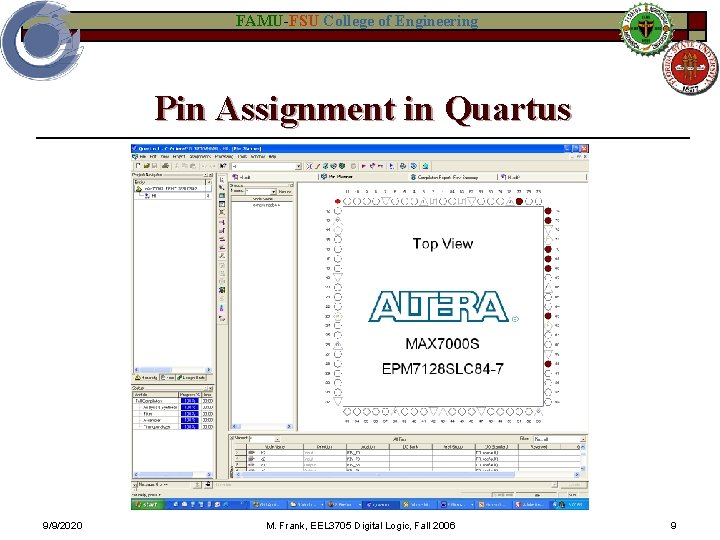

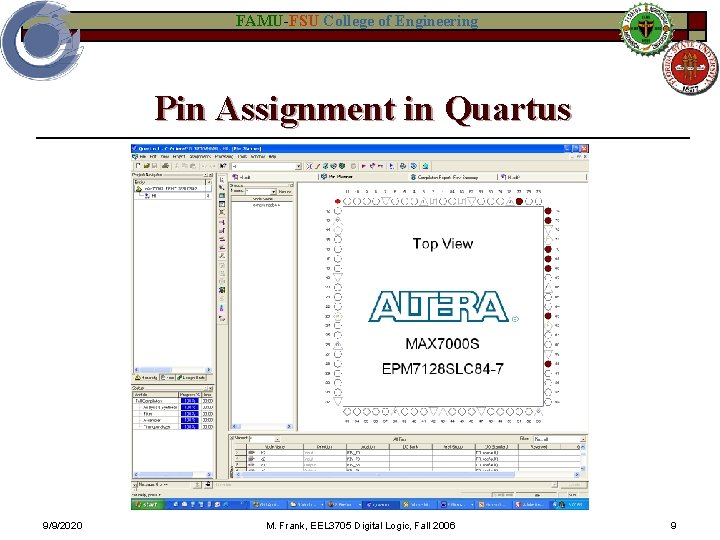

FAMU-FSU College of Engineering Pin Assignment in Quartus 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 9

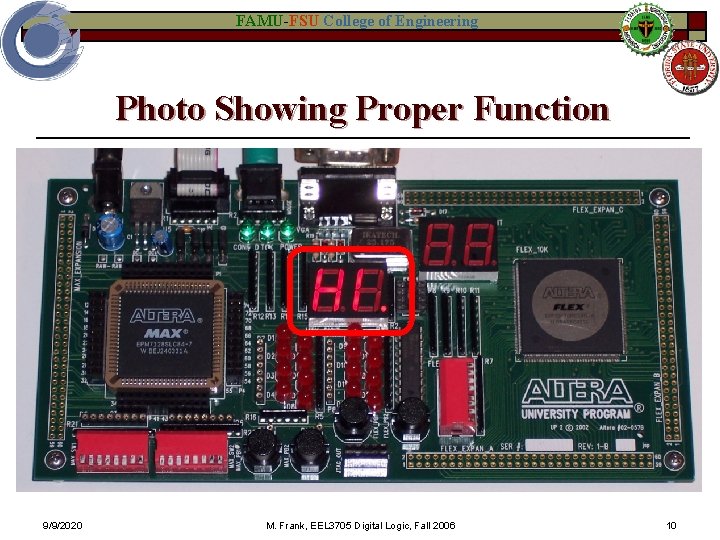

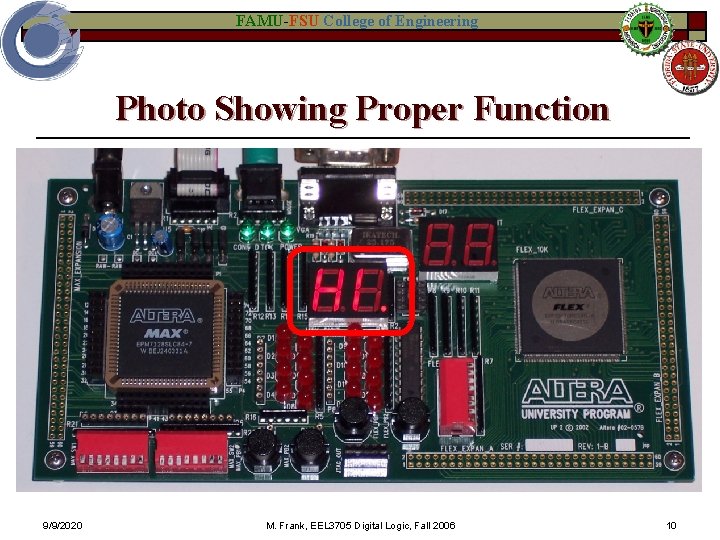

FAMU-FSU College of Engineering Photo Showing Proper Function 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 10

FAMU-FSU College of Engineering FLEX 10 K: VGA Graphics Programming Examples A Simple VGA Driver, Test Pattern Generator, and Character Generator for the FLEX 10 K 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 11

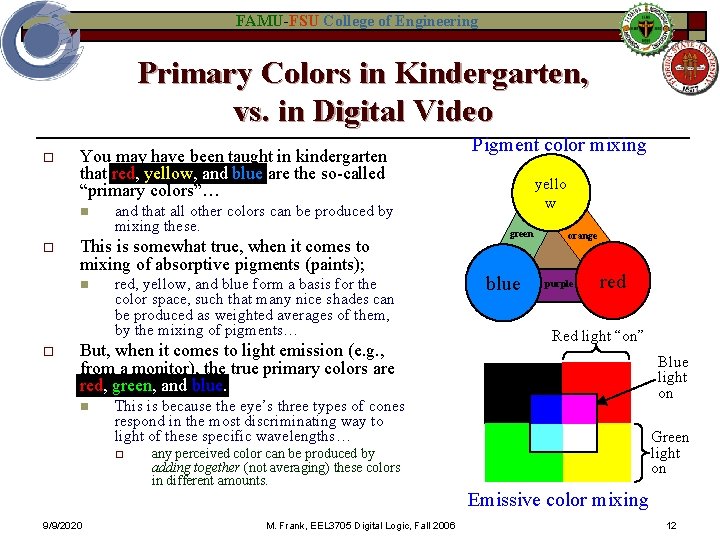

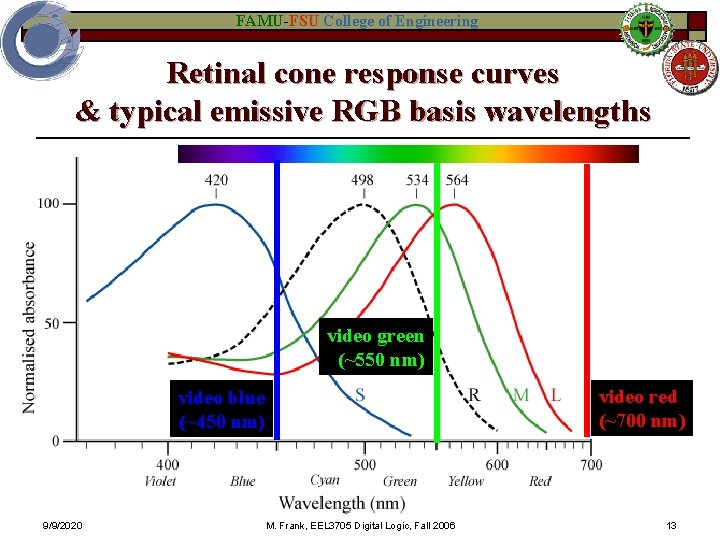

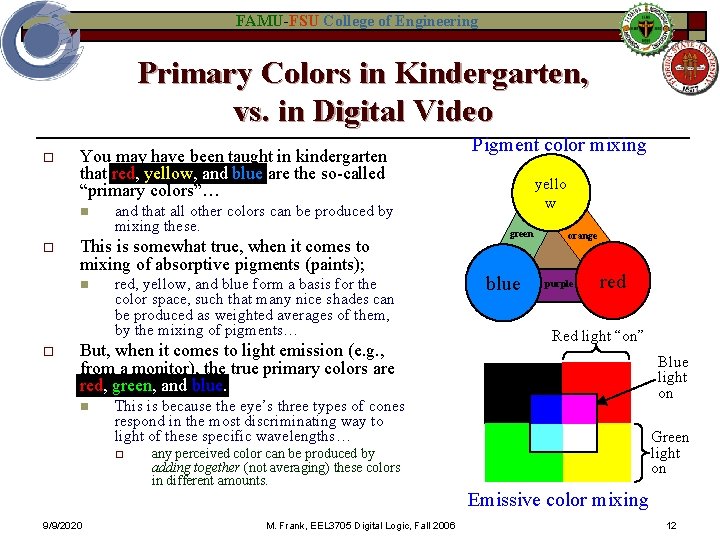

FAMU-FSU College of Engineering Primary Colors in Kindergarten, vs. in Digital Video o You may have been taught in kindergarten that red, yellow, and blue are the so-called “primary colors”… n o This is somewhat true, when it comes to mixing of absorptive pigments (paints); n o and that all other colors can be produced by mixing these. red, yellow, and blue form a basis for the color space, such that many nice shades can be produced as weighted averages of them, by the mixing of pigments… But, when it comes to light emission (e. g. , from a monitor), the true primary colors are red, green, and blue. n yello w green blue orange purple red Red light “on” Blue light on This is because the eye’s three types of cones respond in the most discriminating way to light of these specific wavelengths… o 9/9/2020 Pigment color mixing any perceived color can be produced by adding together (not averaging) these colors in different amounts. M. Frank, EEL 3705 Digital Logic, Fall 2006 Green light on Emissive color mixing 12

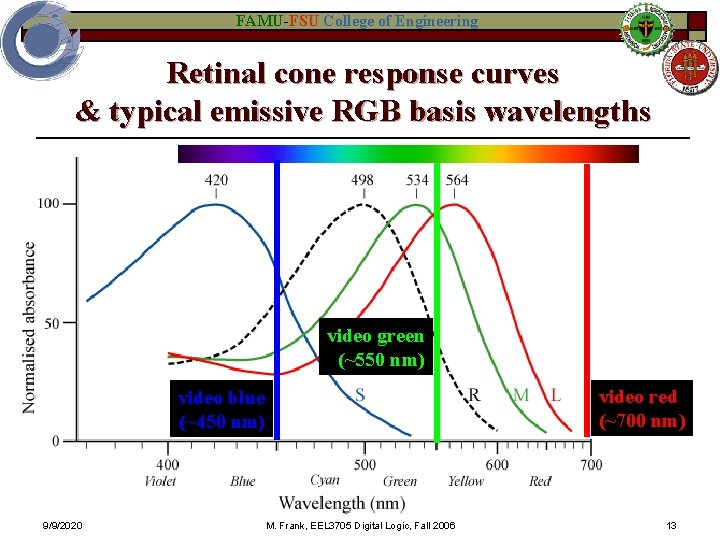

FAMU-FSU College of Engineering Retinal cone response curves & typical emissive RGB basis wavelengths video green (~550 nm) video red (~700 nm) video blue (~450 nm) 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 13

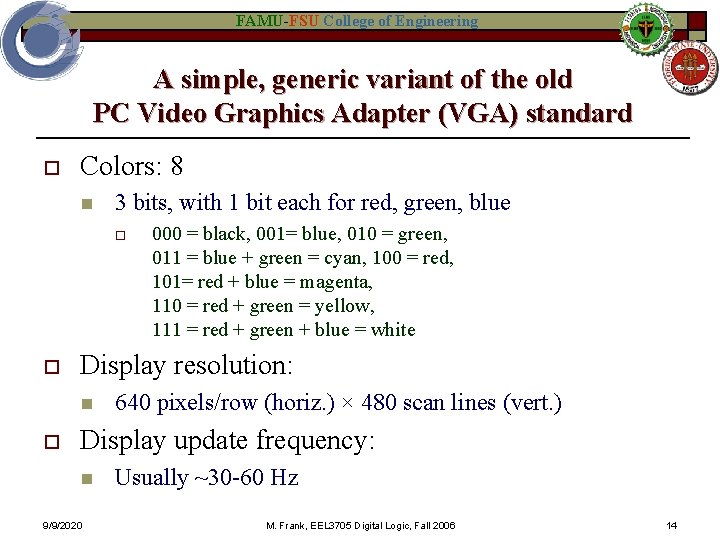

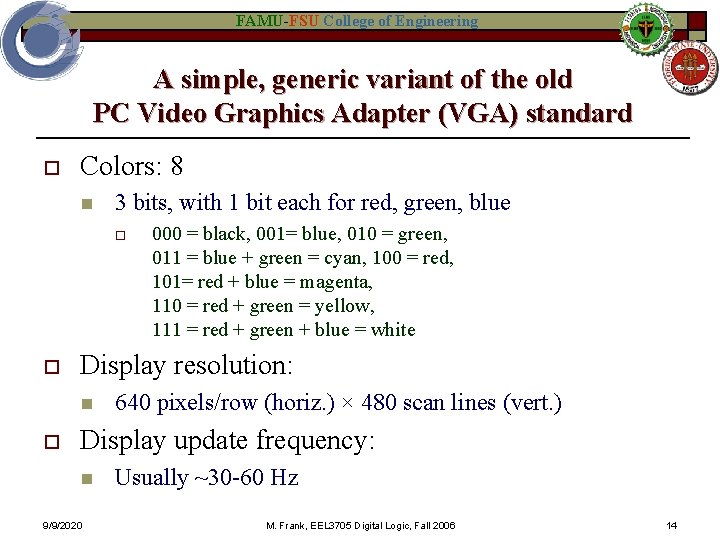

FAMU-FSU College of Engineering A simple, generic variant of the old PC Video Graphics Adapter (VGA) standard o Colors: 8 n 3 bits, with 1 bit each for red, green, blue o o Display resolution: n o 000 = black, 001= blue, 010 = green, 011 = blue + green = cyan, 100 = red, 101= red + blue = magenta, 110 = red + green = yellow, 111 = red + green + blue = white 640 pixels/row (horiz. ) × 480 scan lines (vert. ) Display update frequency: n 9/9/2020 Usually ~30 -60 Hz M. Frank, EEL 3705 Digital Logic, Fall 2006 14

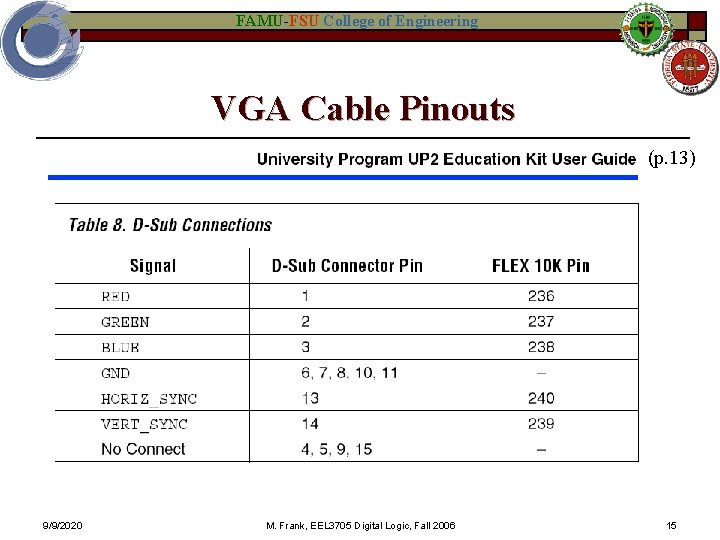

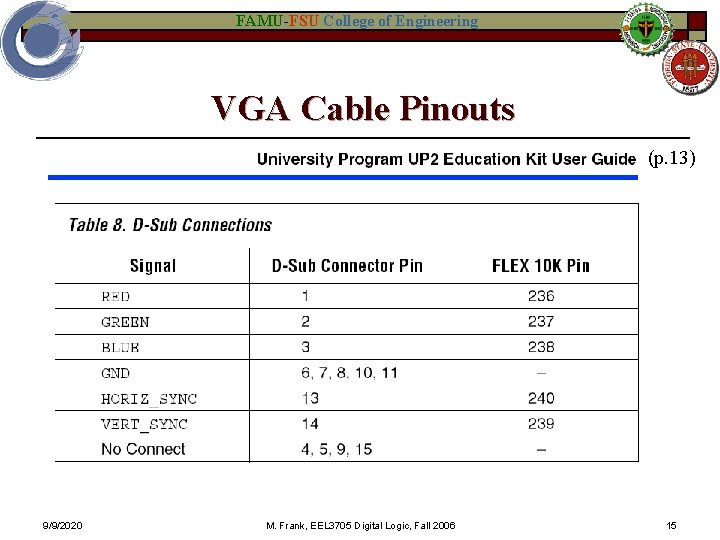

FAMU-FSU College of Engineering VGA Cable Pinouts (p. 13) 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 15

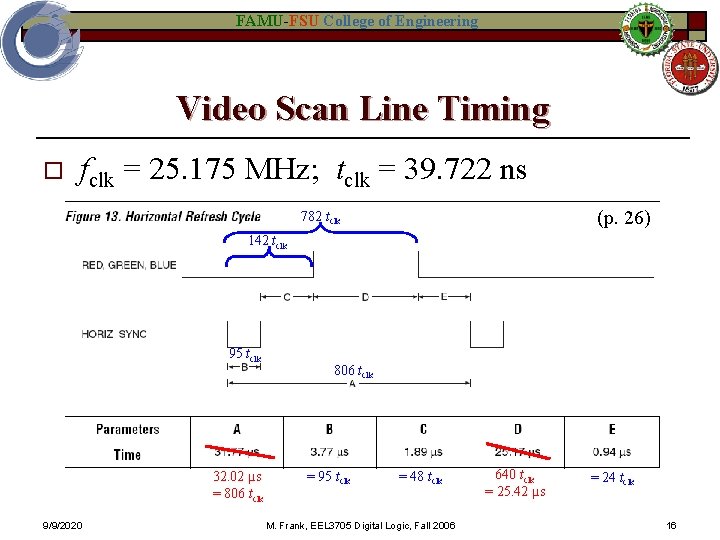

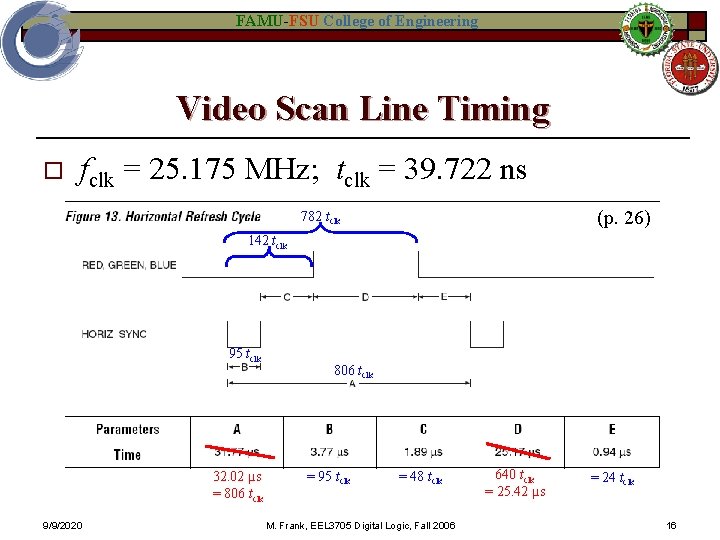

FAMU-FSU College of Engineering Video Scan Line Timing o fclk = 25. 175 MHz; tclk = 39. 722 ns (p. 26) 782 tclk 142 tclk 95 tclk 32. 02 µs = 806 tclk 9/9/2020 806 tclk = 95 tclk = 48 tclk M. Frank, EEL 3705 Digital Logic, Fall 2006 640 tclk = 25. 42 µs = 24 tclk 16

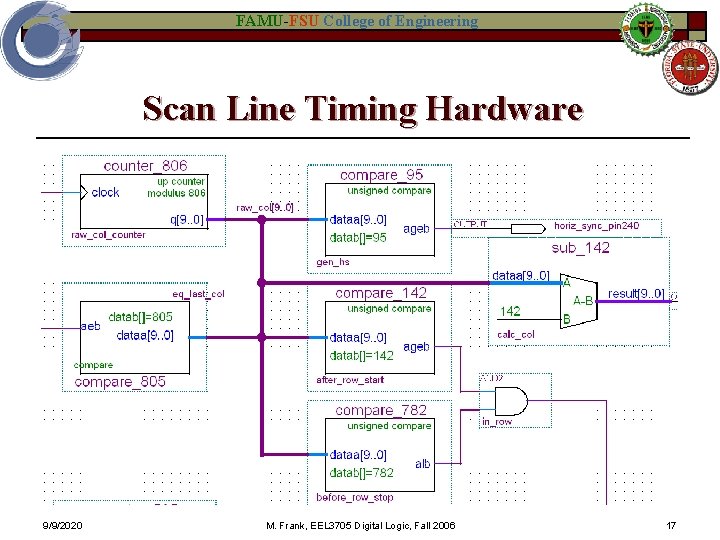

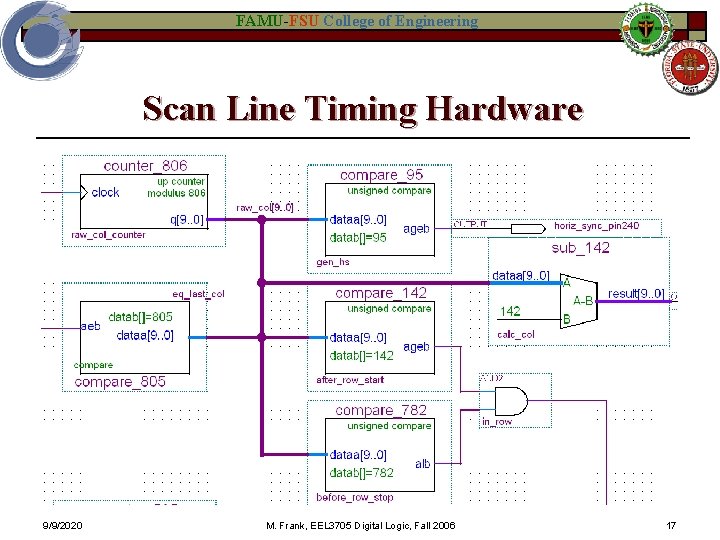

FAMU-FSU College of Engineering Scan Line Timing Hardware 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 17

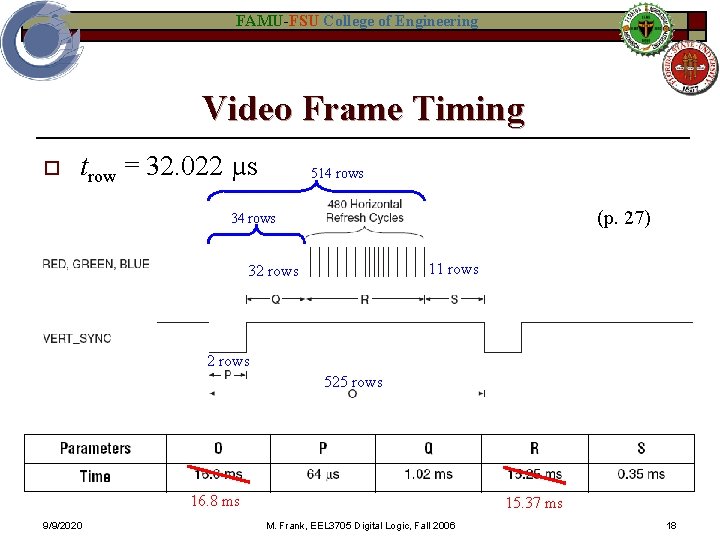

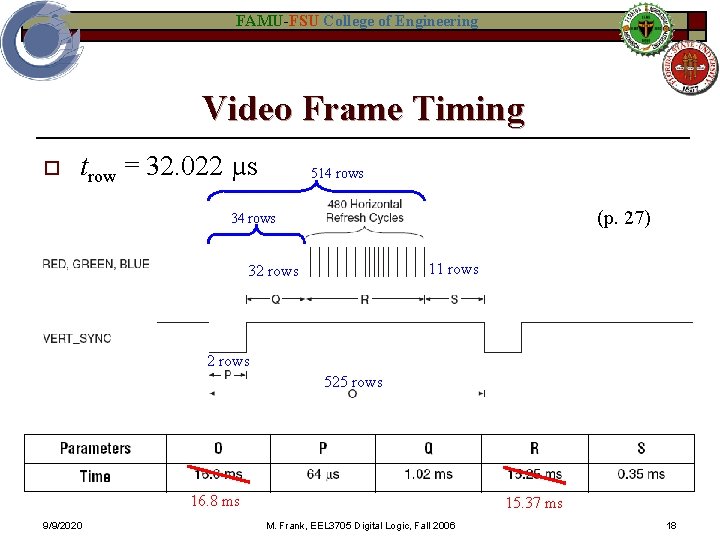

FAMU-FSU College of Engineering Video Frame Timing o trow = 32. 022 µs 514 rows (p. 27) 34 rows 11 rows 32 rows 525 rows 16. 8 ms 9/9/2020 15. 37 ms M. Frank, EEL 3705 Digital Logic, Fall 2006 18

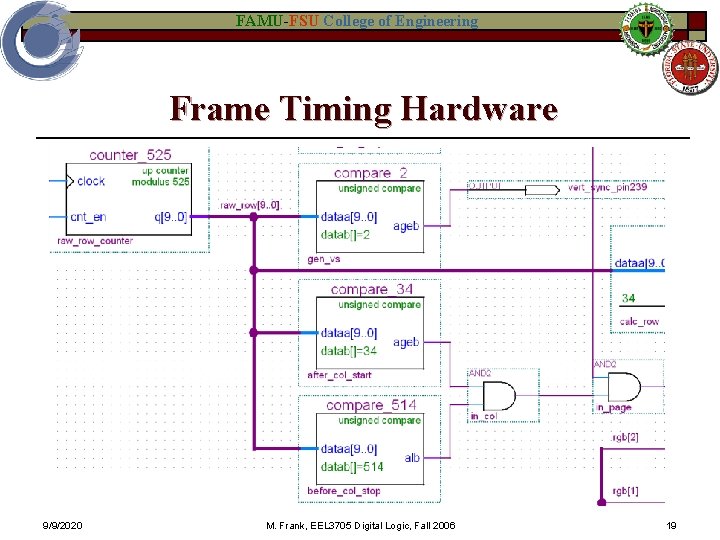

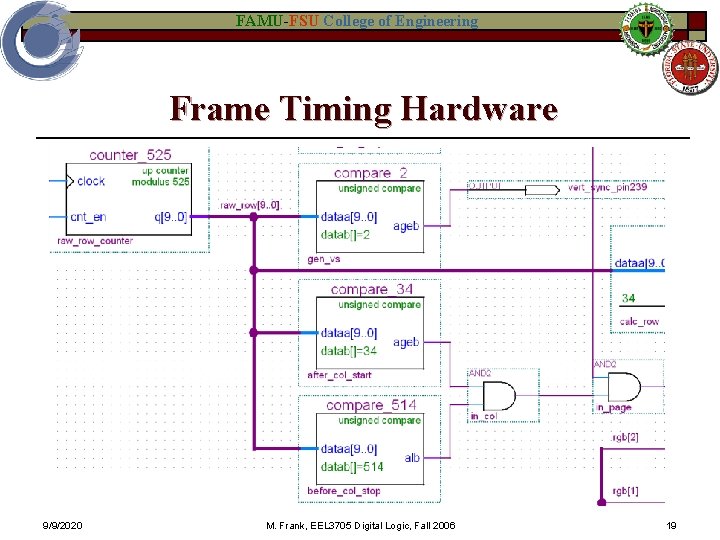

FAMU-FSU College of Engineering Frame Timing Hardware 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 19

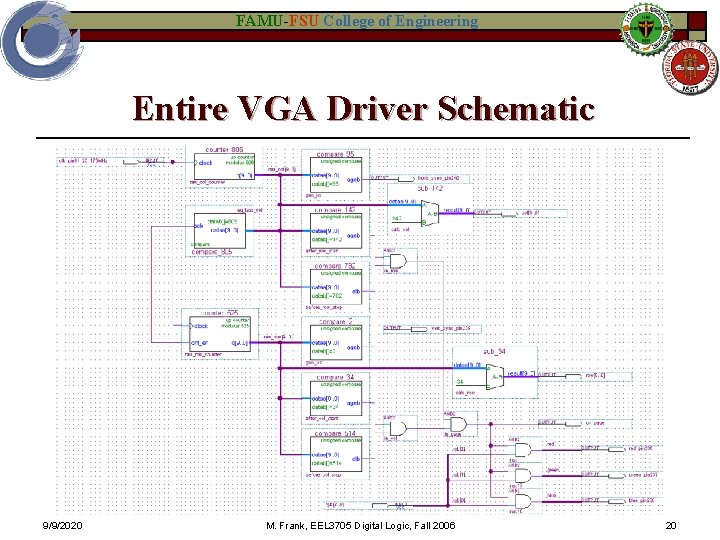

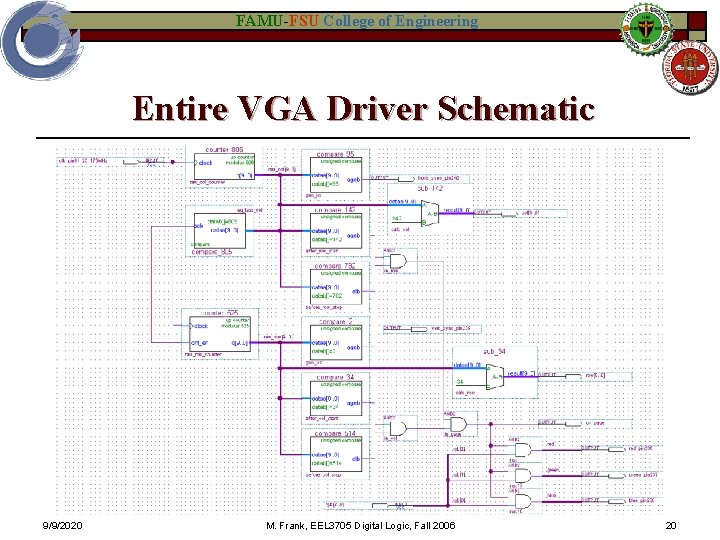

FAMU-FSU College of Engineering Entire VGA Driver Schematic 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 20

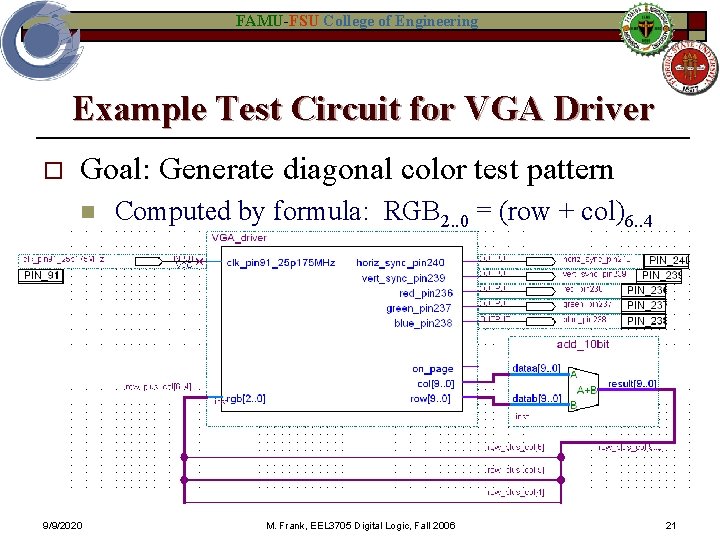

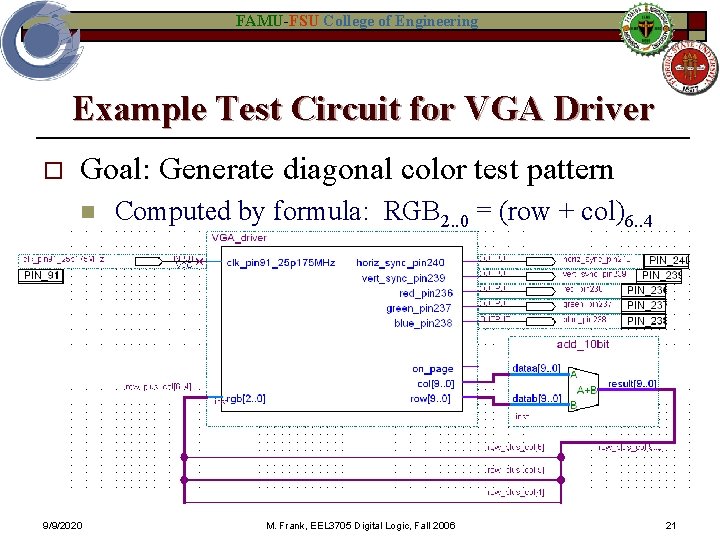

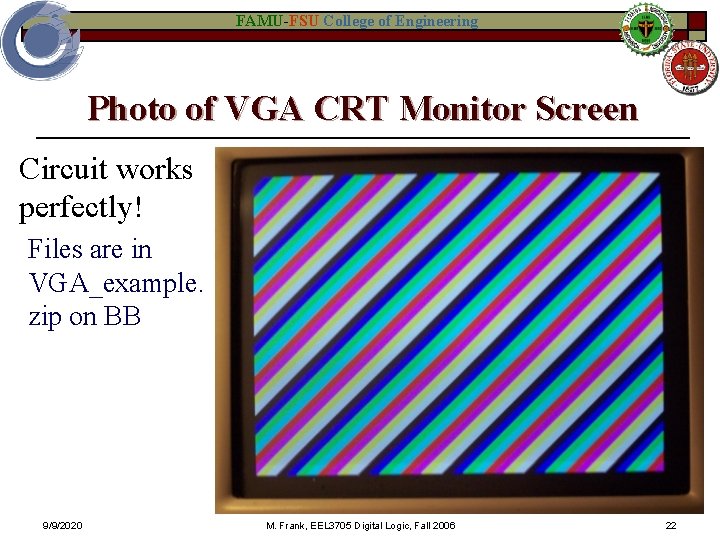

FAMU-FSU College of Engineering Example Test Circuit for VGA Driver o Goal: Generate diagonal color test pattern n 9/9/2020 Computed by formula: RGB 2. . 0 = (row + col)6. . 4 M. Frank, EEL 3705 Digital Logic, Fall 2006 21

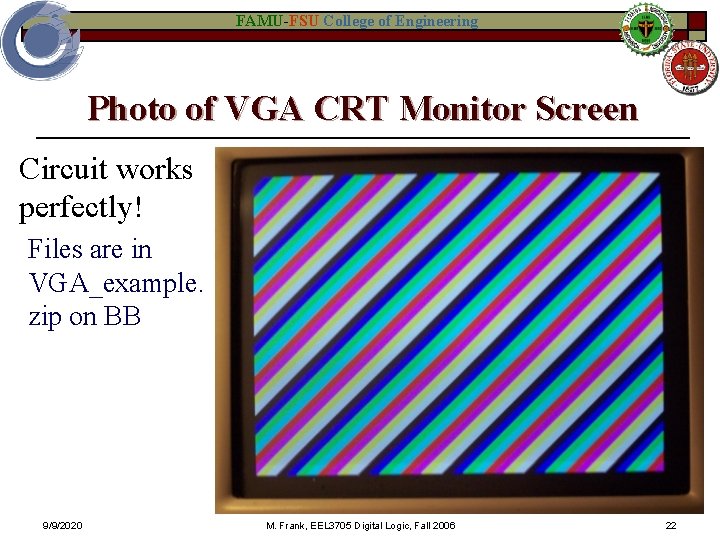

FAMU-FSU College of Engineering Photo of VGA CRT Monitor Screen Circuit works perfectly! Files are in VGA_example. zip on BB 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 22

FAMU-FSU College of Engineering VGA Text Display Programming Examples Character Generator and Text Page Display for the FLEX 10 K 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 23

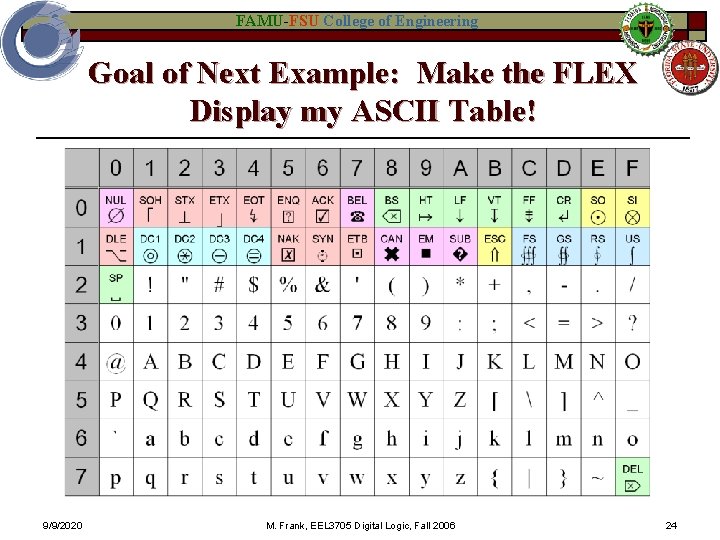

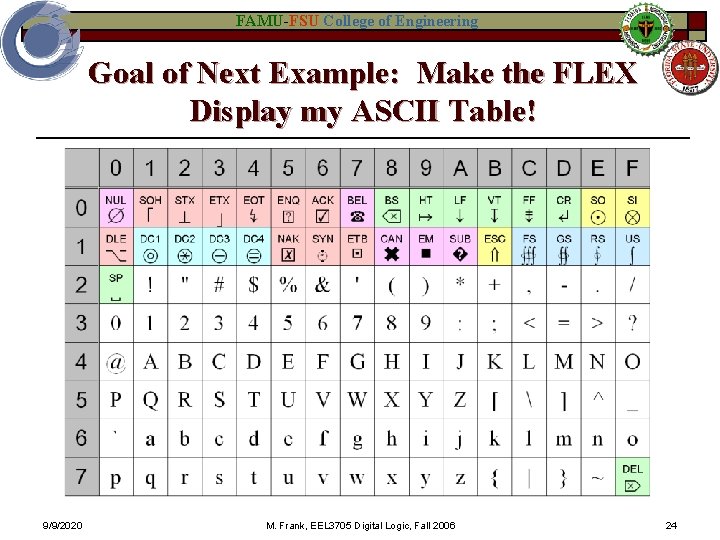

FAMU-FSU College of Engineering Goal of Next Example: Make the FLEX Display my ASCII Table! 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 24

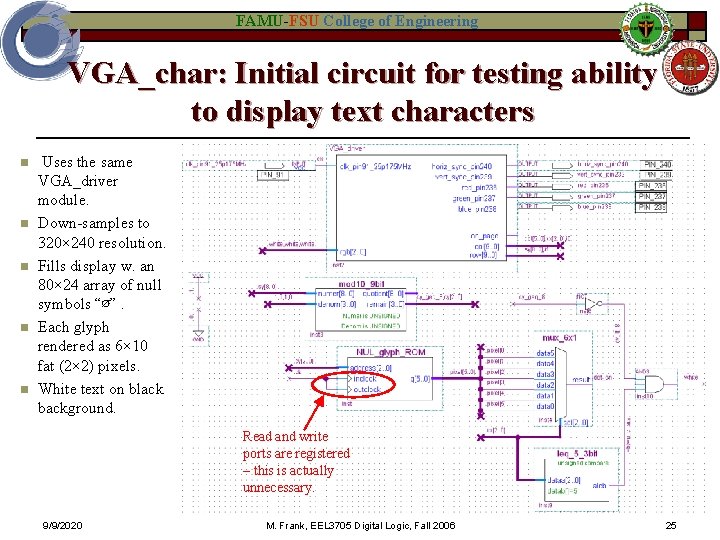

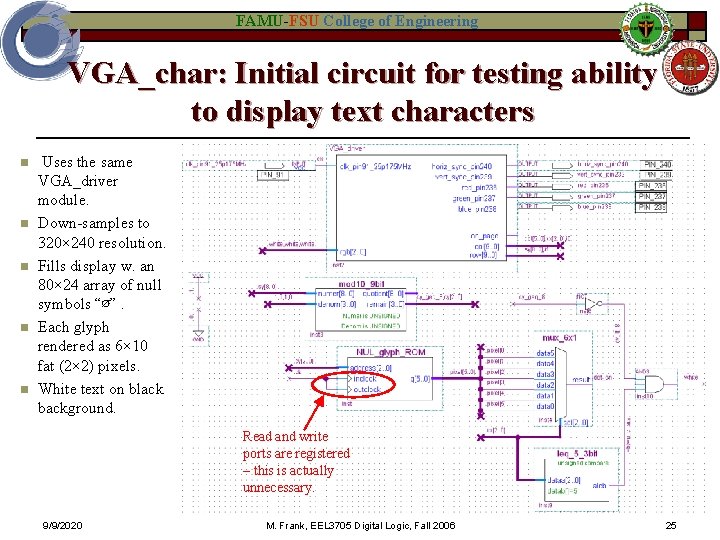

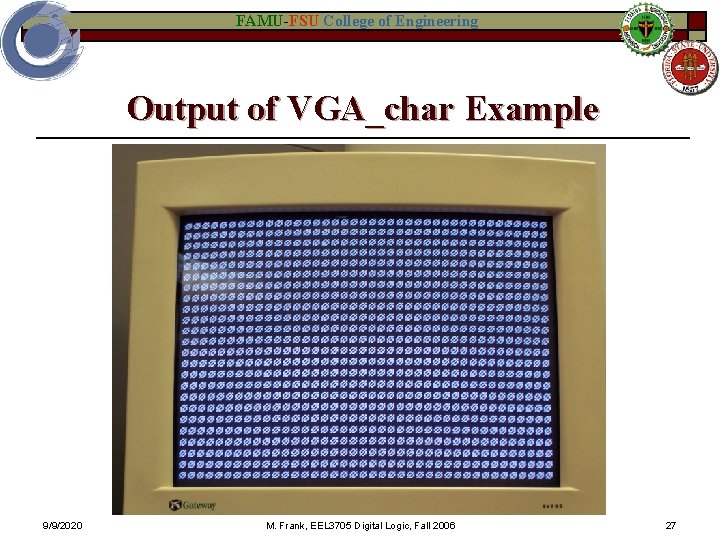

FAMU-FSU College of Engineering VGA_char: Initial circuit for testing ability to display text characters n n n Uses the same VGA_driver module. Down-samples to 320× 240 resolution. Fills display w. an 80× 24 array of null symbols “∅”. Each glyph rendered as 6× 10 fat (2× 2) pixels. White text on black background. Read and write ports are registered – this is actually unnecessary. 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 25

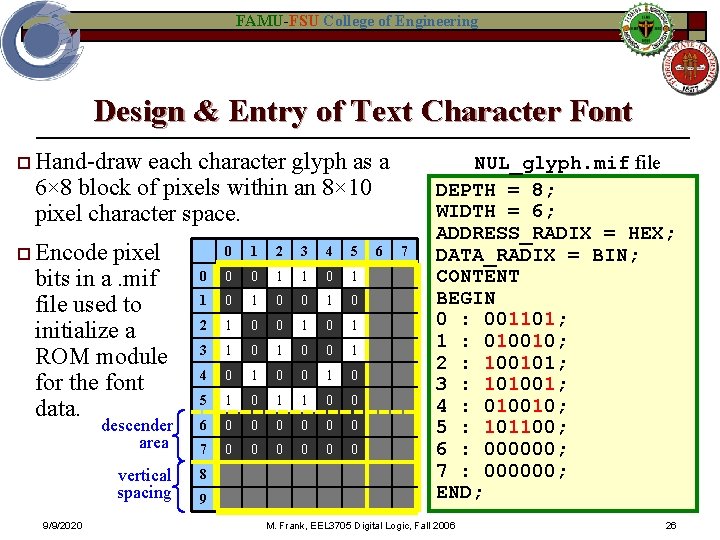

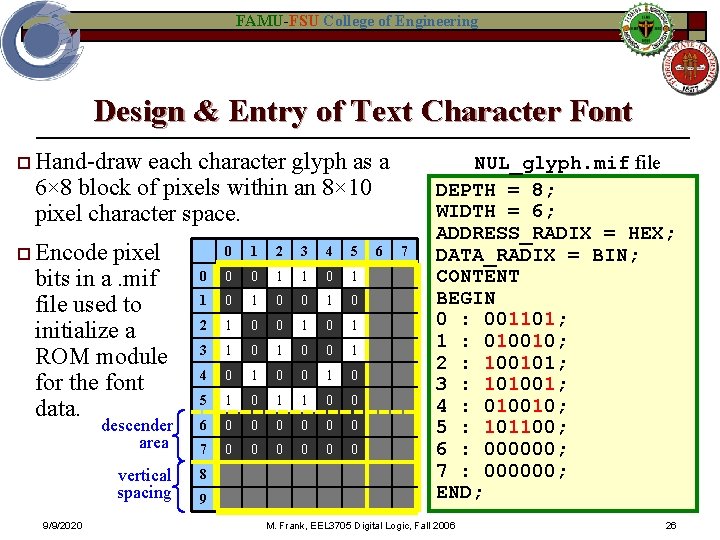

FAMU-FSU College of Engineering Design & Entry of Text Character Font o Hand-draw each character glyph as a 6× 8 block of pixels within an 8× 10 pixel character space. o Encode pixel bits in a. mif file used to initialize a ROM module for the font data. 9/9/2020 0 1 2 3 4 5 0 0 0 1 1 0 1 0 2 1 0 0 1 3 1 0 0 1 4 0 1 0 5 1 0 1 1 0 0 descender area 6 0 0 0 7 0 0 0 vertical spacing 8 9 6 7 NUL_glyph. mif file DEPTH = 8; WIDTH = 6; ADDRESS_RADIX = HEX; DATA_RADIX = BIN; CONTENT BEGIN 0 : 001101; 1 : 010010; 2 : 100101; 3 : 101001; 4 : 010010; 5 : 101100; 6 : 000000; 7 : 000000; END; M. Frank, EEL 3705 Digital Logic, Fall 2006 26

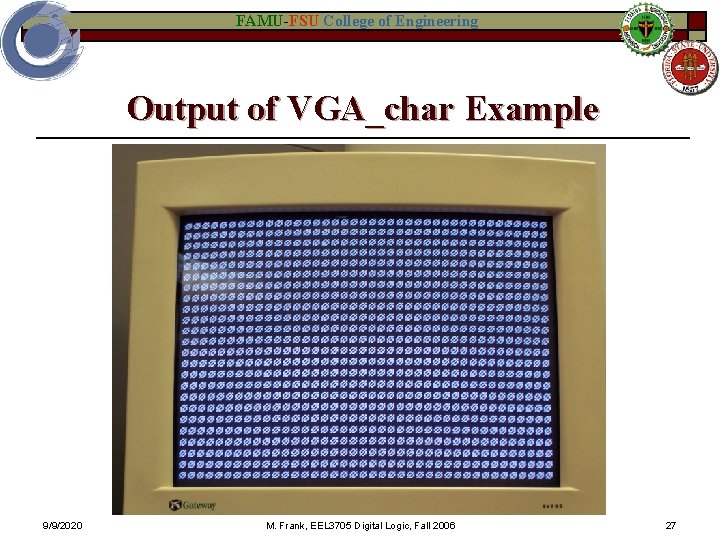

FAMU-FSU College of Engineering Output of VGA_char Example 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 27

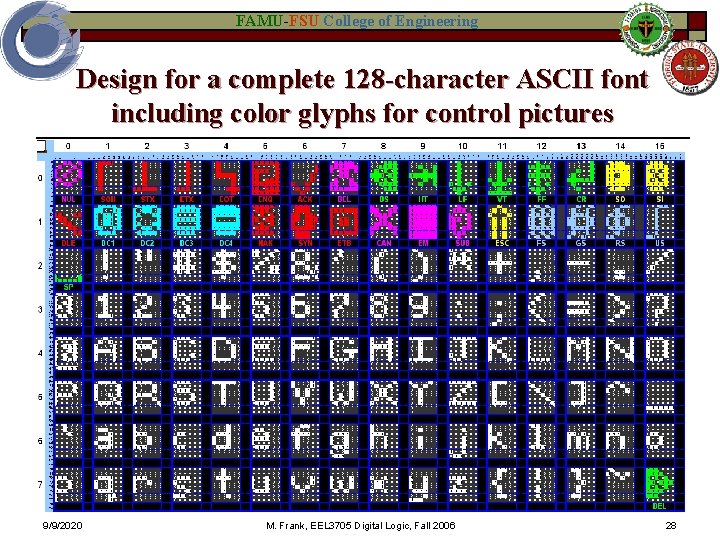

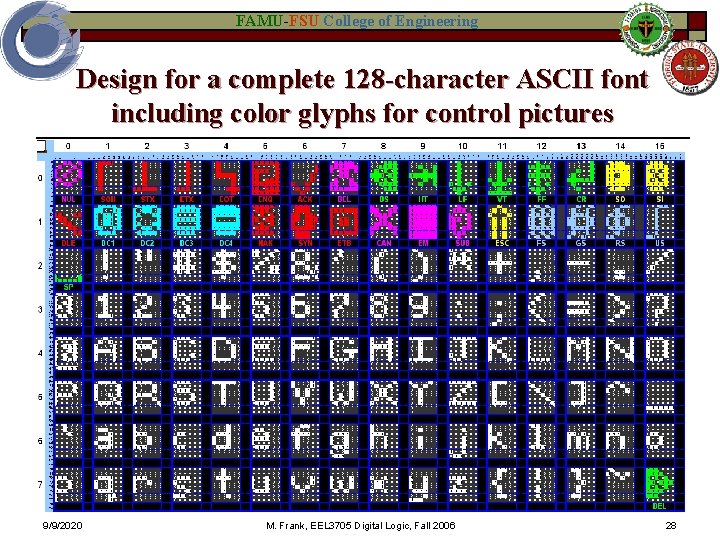

FAMU-FSU College of Engineering Design for a complete 128 -character ASCII font including color glyphs for control pictures 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 28

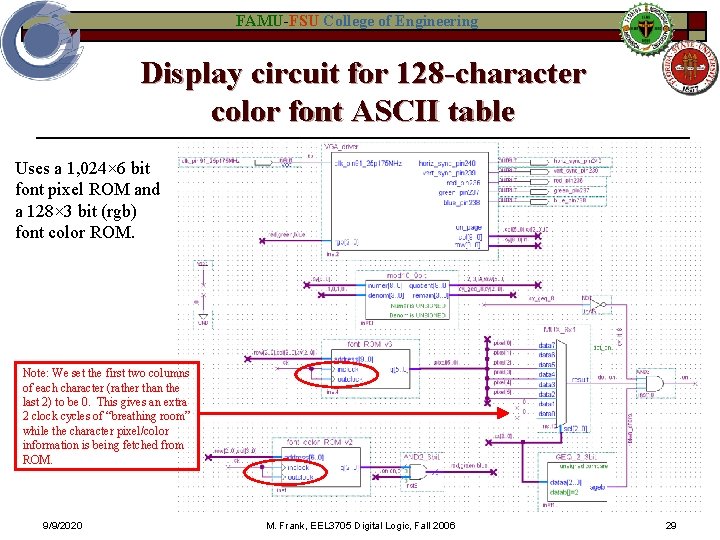

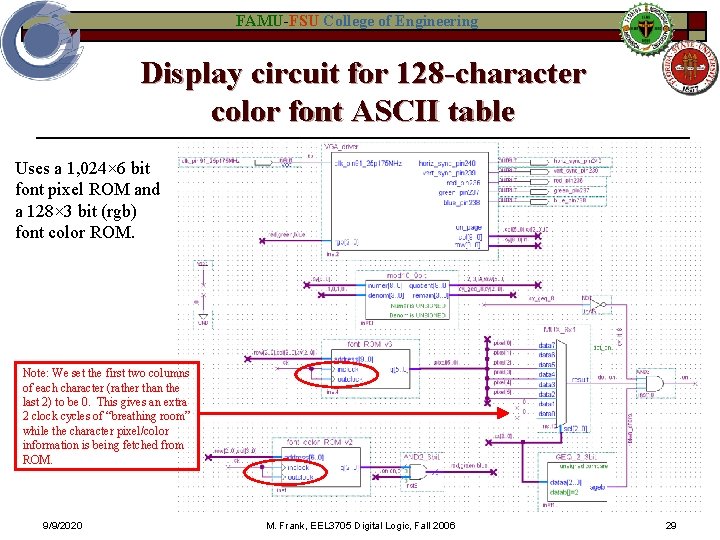

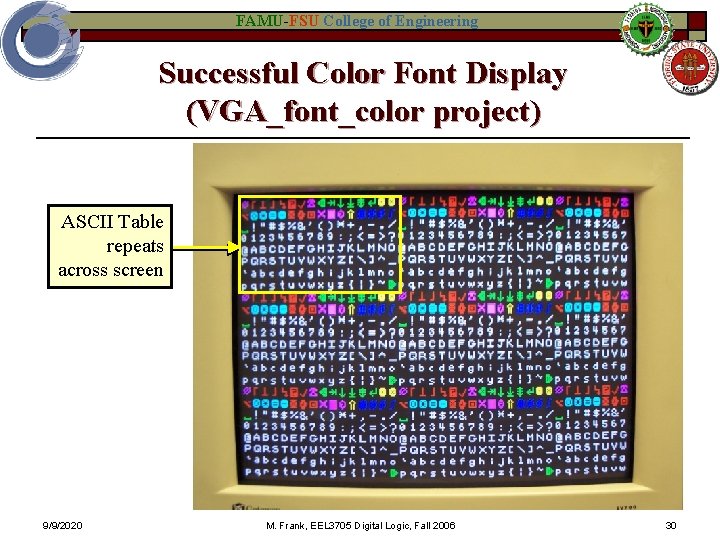

FAMU-FSU College of Engineering Display circuit for 128 -character color font ASCII table Uses a 1, 024× 6 bit font pixel ROM and a 128× 3 bit (rgb) font color ROM. Note: We set the first two columns of each character (rather than the last 2) to be 0. This gives an extra 2 clock cycles of “breathing room” while the character pixel/color information is being fetched from ROM. 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 29

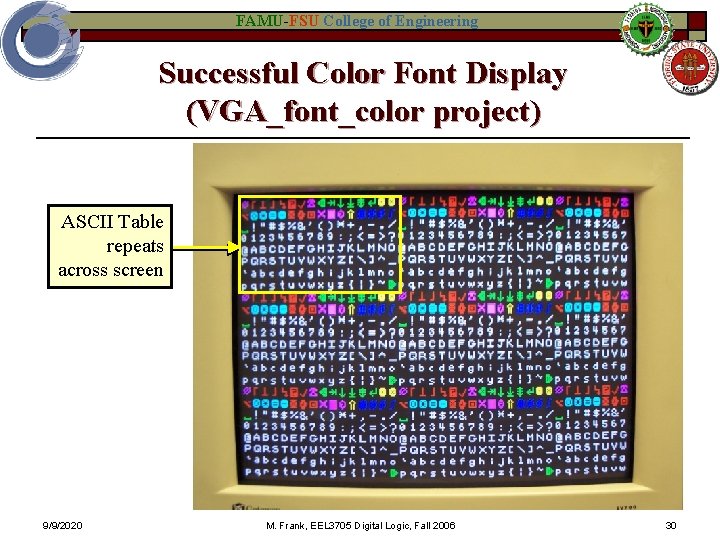

FAMU-FSU College of Engineering Successful Color Font Display (VGA_font_color project) ASCII Table repeats across screen 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 30

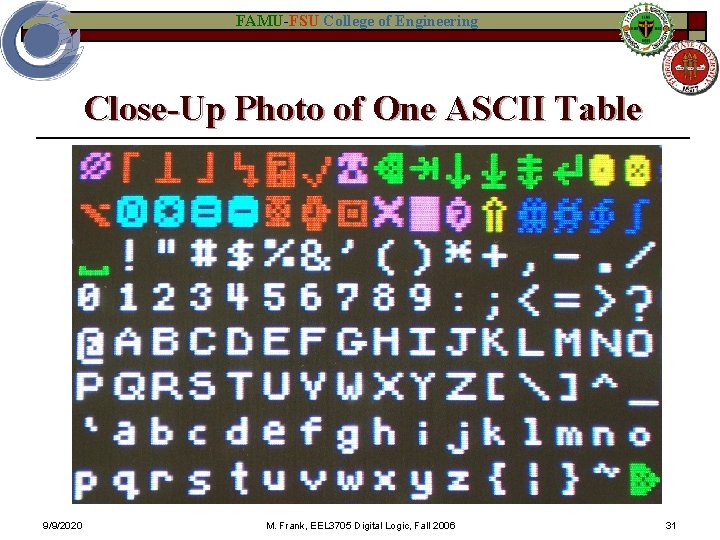

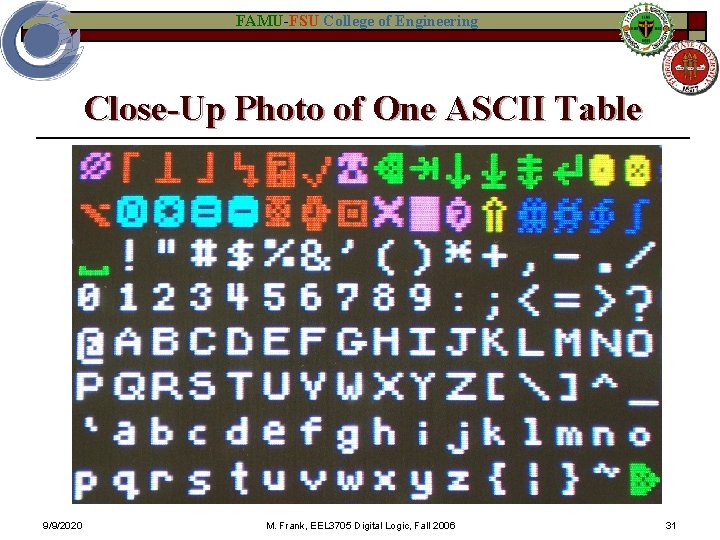

FAMU-FSU College of Engineering Close-Up Photo of One ASCII Table 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 31

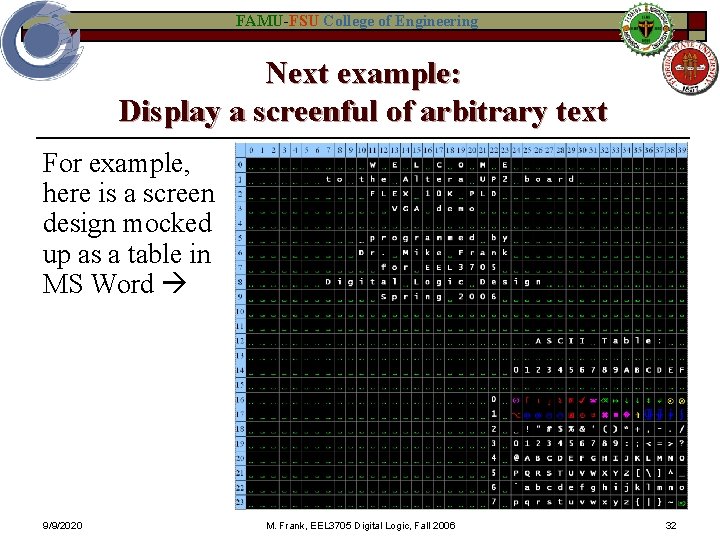

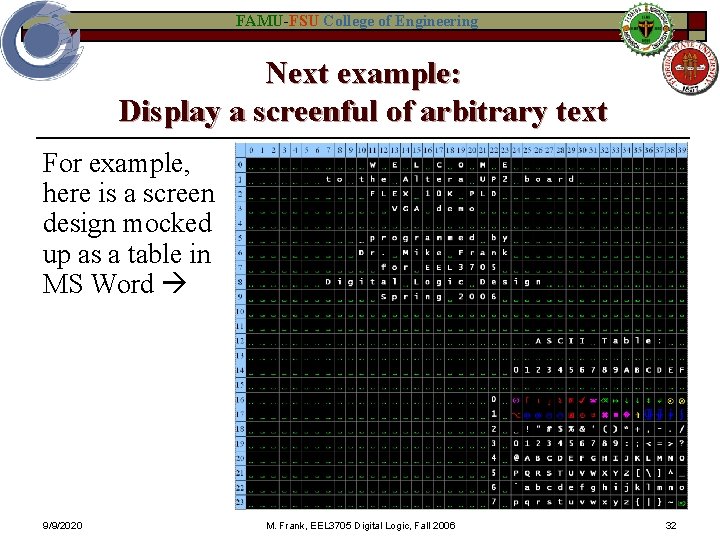

FAMU-FSU College of Engineering Next example: Display a screenful of arbitrary text For example, here is a screen design mocked up as a table in MS Word 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 32

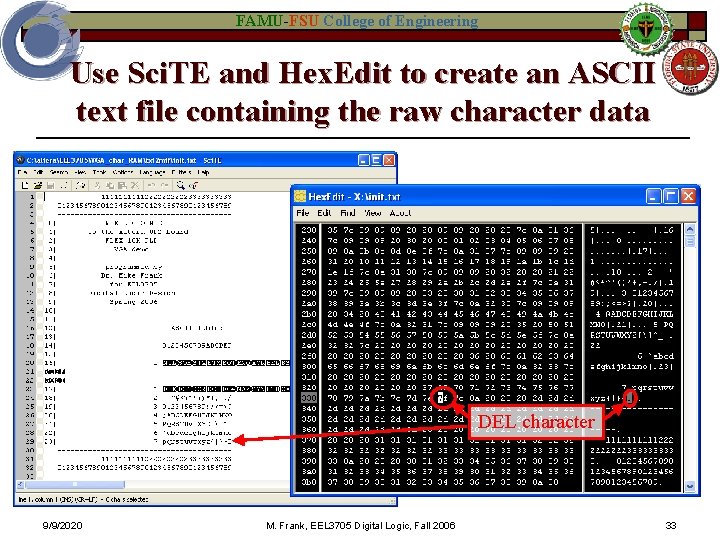

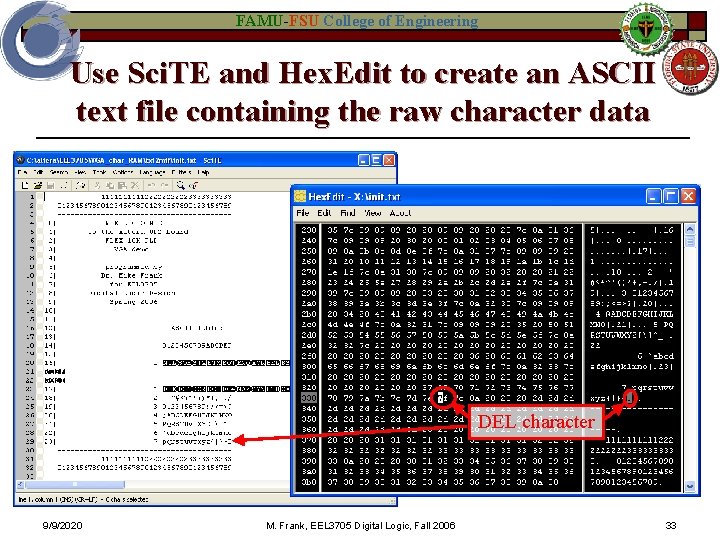

FAMU-FSU College of Engineering Use Sci. TE and Hex. Edit to create an ASCII text file containing the raw character data DEL character 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 33

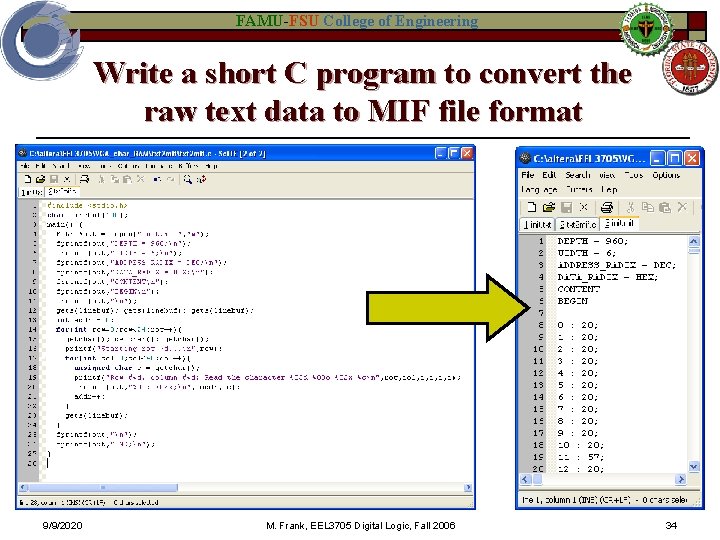

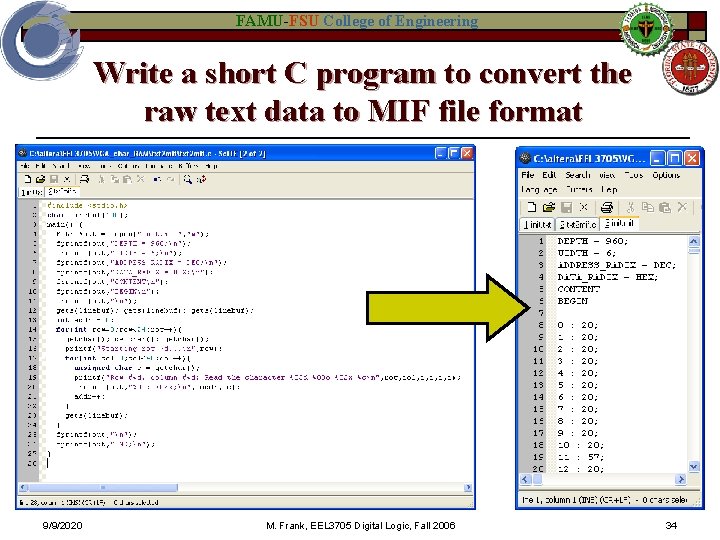

FAMU-FSU College of Engineering Write a short C program to convert the raw text data to MIF file format 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 34

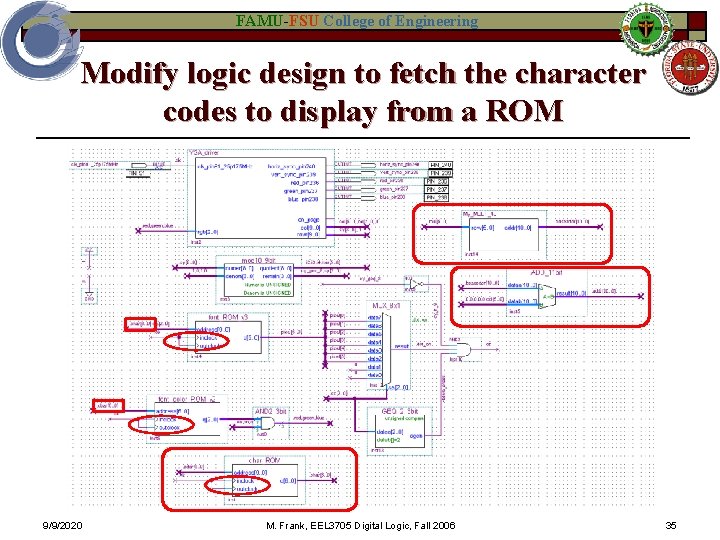

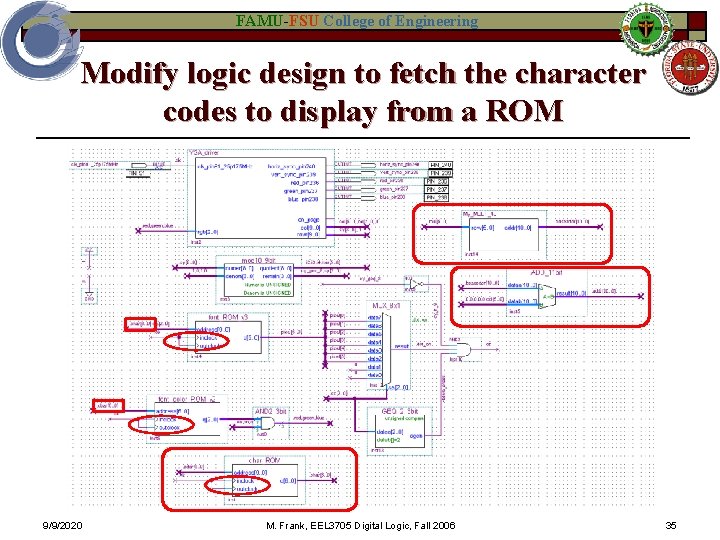

FAMU-FSU College of Engineering Modify logic design to fetch the character codes to display from a ROM 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 35

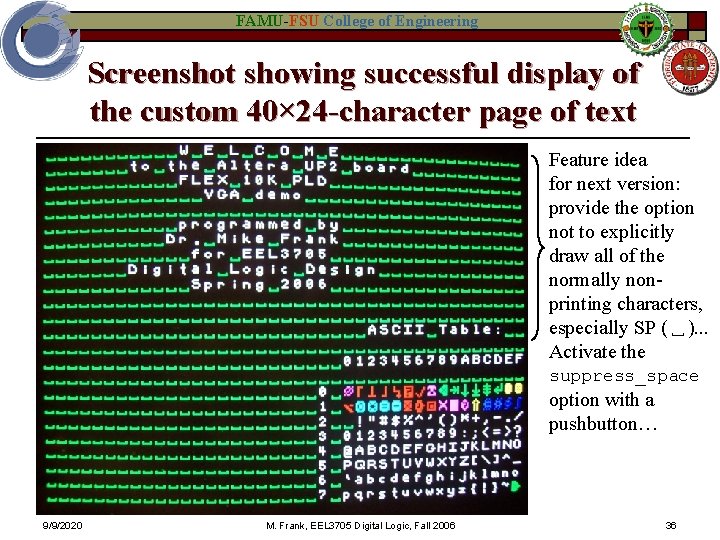

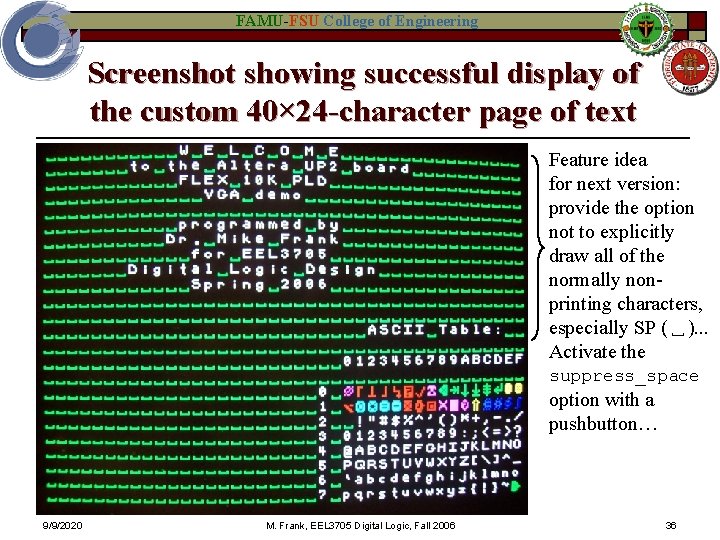

FAMU-FSU College of Engineering Screenshot showing successful display of the custom 40× 24 -character page of text Feature idea for next version: provide the option not to explicitly draw all of the normally nonprinting characters, especially SP (␣). . . Activate the suppress_space option with a pushbutton… 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 36

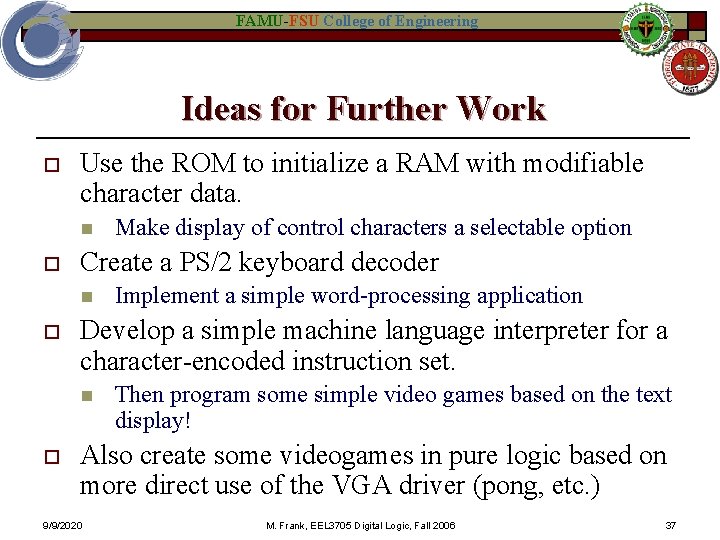

FAMU-FSU College of Engineering Ideas for Further Work o Use the ROM to initialize a RAM with modifiable character data. n o Create a PS/2 keyboard decoder n o Implement a simple word-processing application Develop a simple machine language interpreter for a character-encoded instruction set. n o Make display of control characters a selectable option Then program some simple video games based on the text display! Also create some videogames in pure logic based on more direct use of the VGA driver (pong, etc. ) 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 37

FAMU-FSU College of Engineering Ping-Pong Videogame Example Dynamic Display Generation, Layered Graphics, Controlled Paddle Motion 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 38

FAMU-FSU College of Engineering Real-World Ping-Pong Table Image credit: Wikipedia 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 39

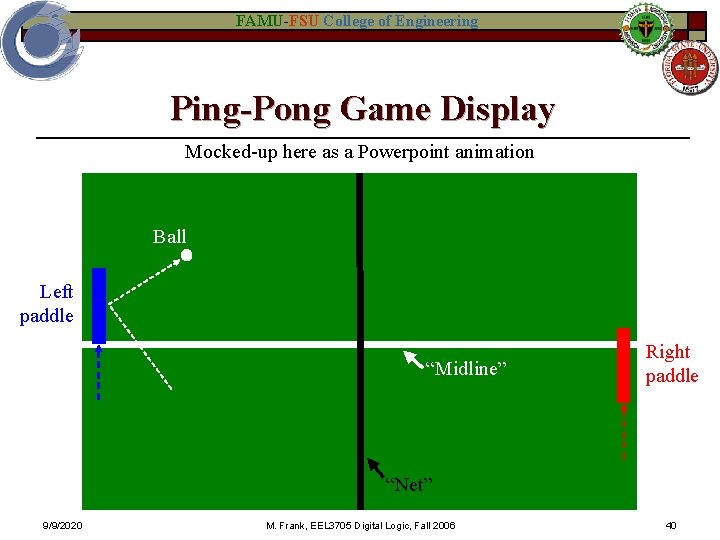

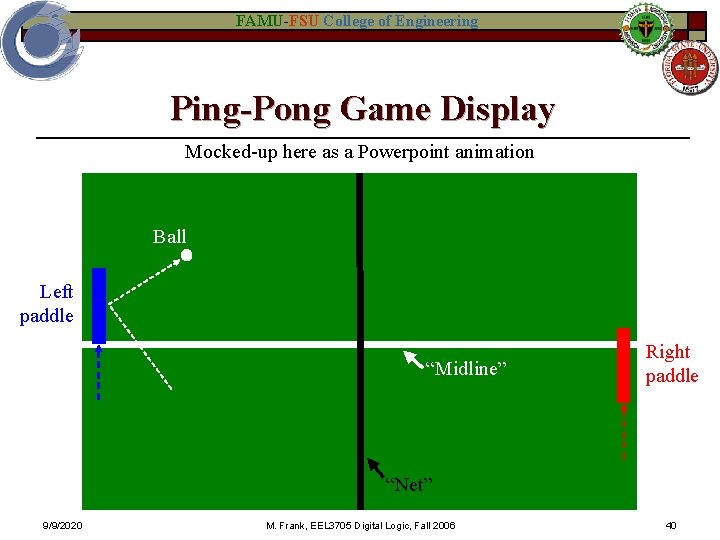

FAMU-FSU College of Engineering Ping-Pong Game Display Mocked-up here as a Powerpoint animation Ball Left paddle “Midline” Right paddle “Net” 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 40

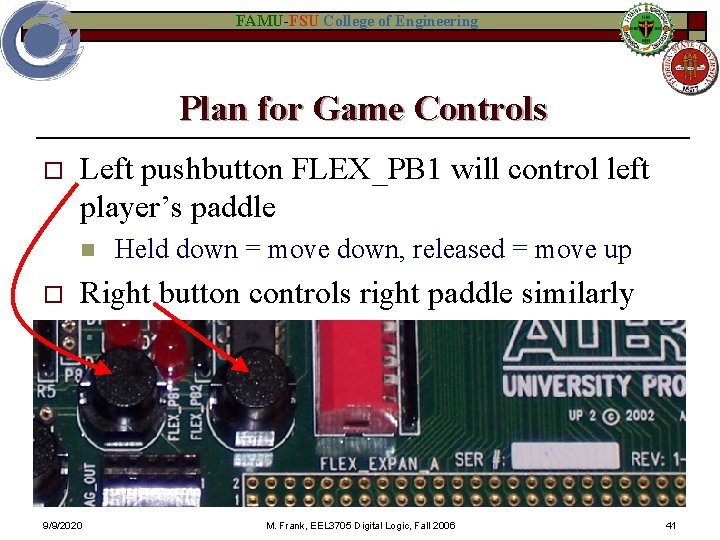

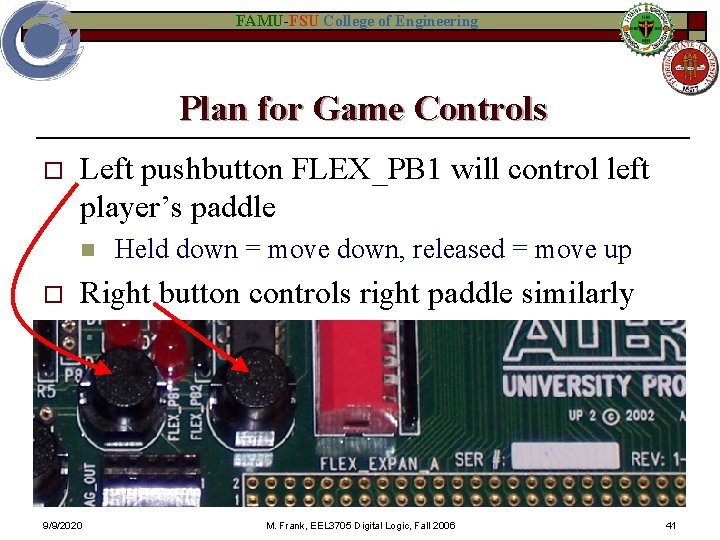

FAMU-FSU College of Engineering Plan for Game Controls o Left pushbutton FLEX_PB 1 will control left player’s paddle n o Held down = move down, released = move up Right button controls right paddle similarly 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 41

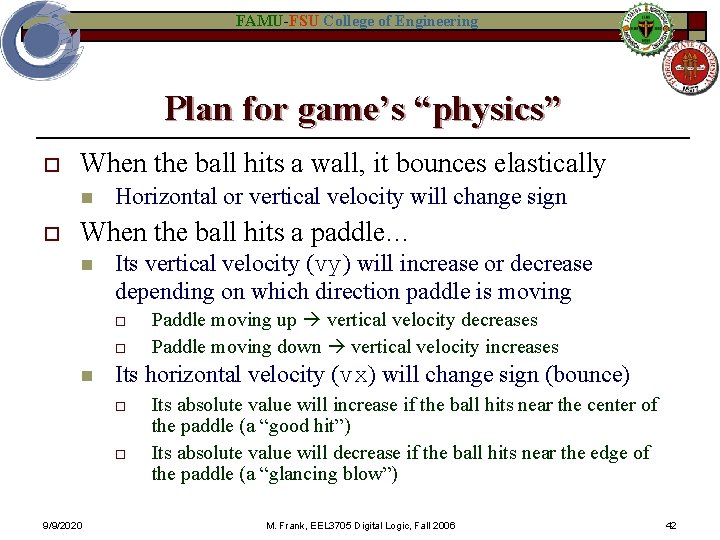

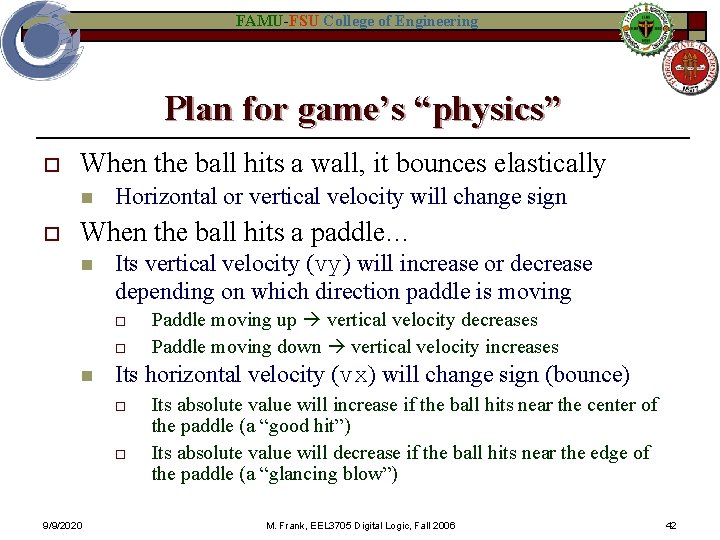

FAMU-FSU College of Engineering Plan for game’s “physics” o When the ball hits a wall, it bounces elastically n o Horizontal or vertical velocity will change sign When the ball hits a paddle… n Its vertical velocity (vy) will increase or decrease depending on which direction paddle is moving o o n Its horizontal velocity (vx) will change sign (bounce) o o 9/9/2020 Paddle moving up vertical velocity decreases Paddle moving down vertical velocity increases Its absolute value will increase if the ball hits near the center of the paddle (a “good hit”) Its absolute value will decrease if the ball hits near the edge of the paddle (a “glancing blow”) M. Frank, EEL 3705 Digital Logic, Fall 2006 42

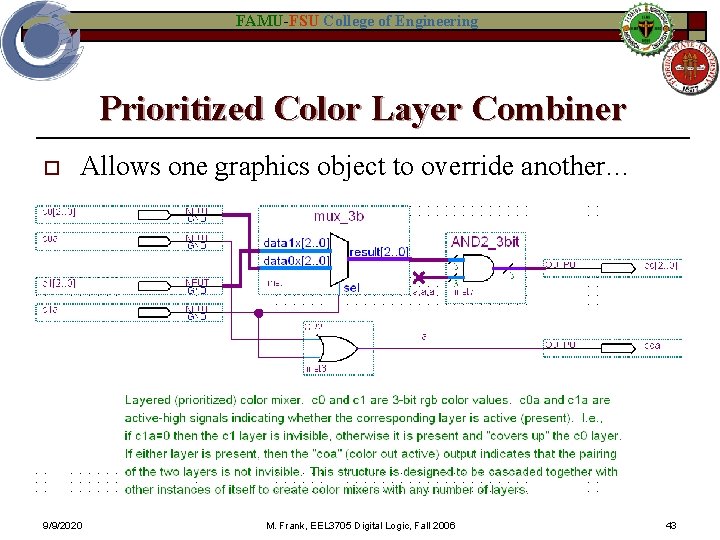

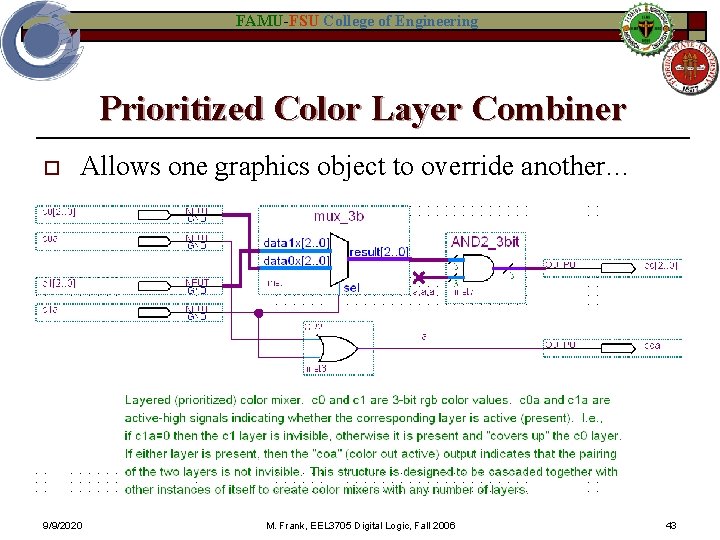

FAMU-FSU College of Engineering Prioritized Color Layer Combiner o Allows one graphics object to override another… 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 43

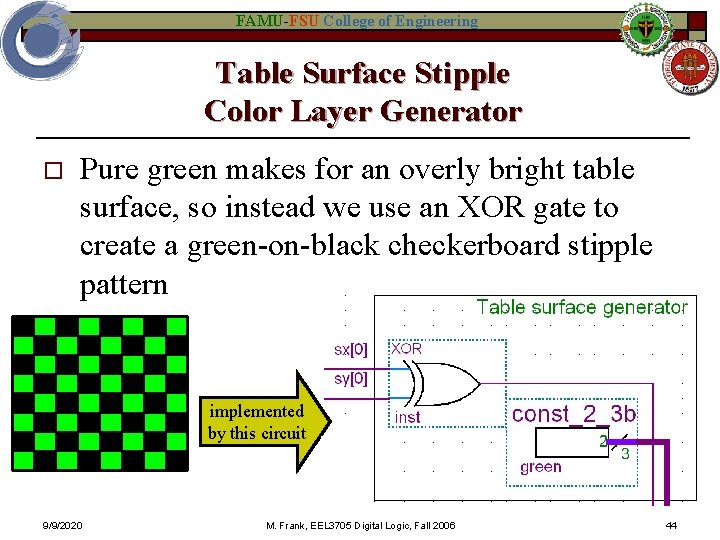

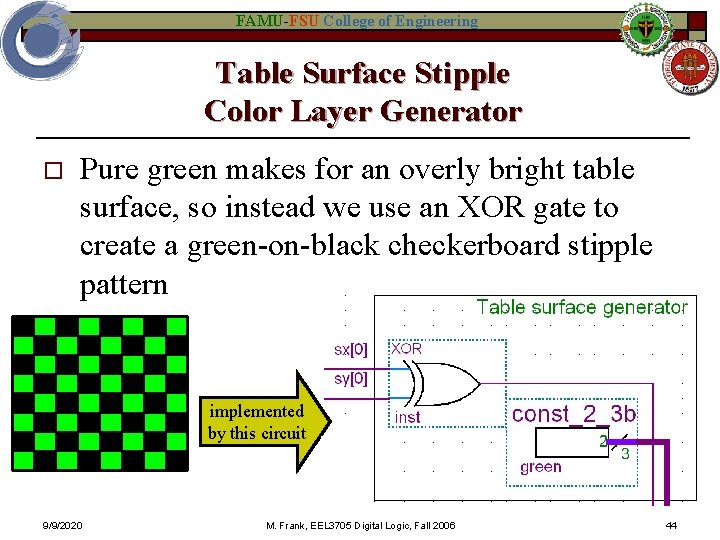

FAMU-FSU College of Engineering Table Surface Stipple Color Layer Generator o Pure green makes for an overly bright table surface, so instead we use an XOR gate to create a green-on-black checkerboard stipple pattern implemented by this circuit 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 44

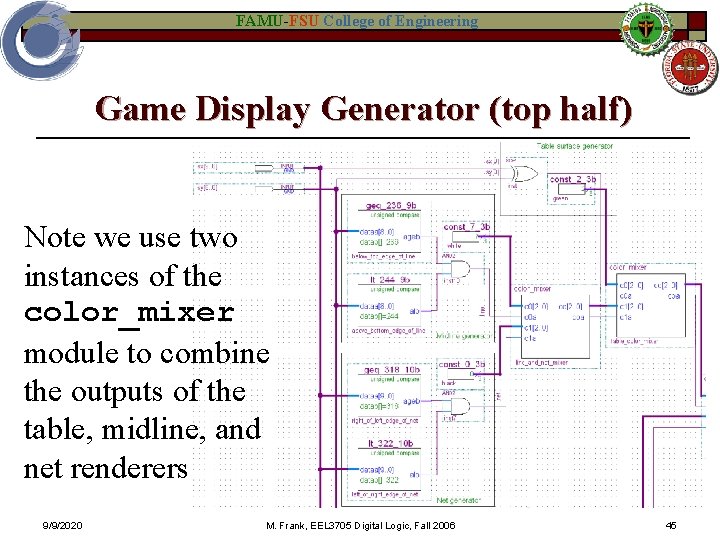

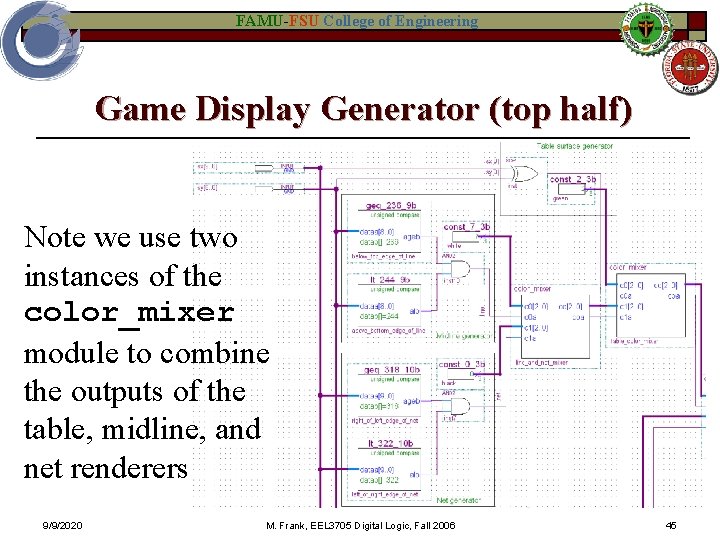

FAMU-FSU College of Engineering Game Display Generator (top half) Note we use two instances of the color_mixer module to combine the outputs of the table, midline, and net renderers 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 45

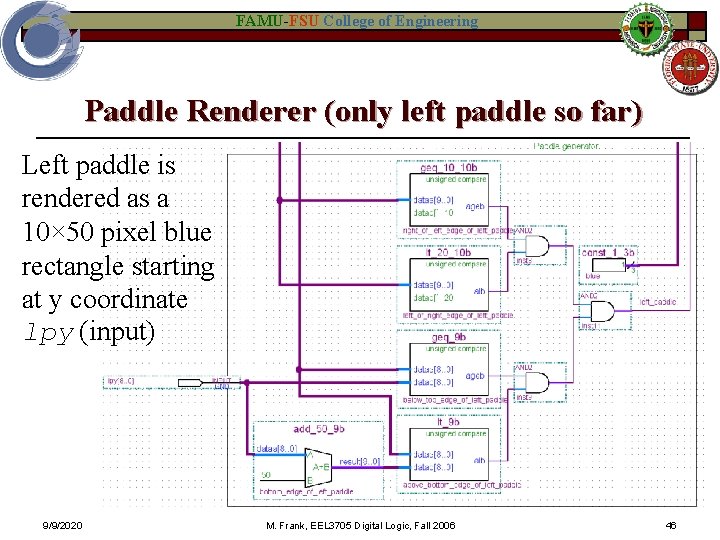

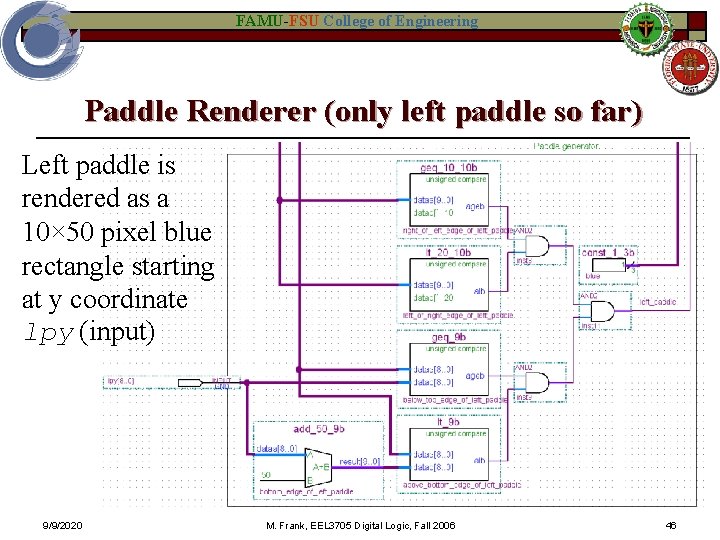

FAMU-FSU College of Engineering Paddle Renderer (only left paddle so far) Left paddle is rendered as a 10× 50 pixel blue rectangle starting at y coordinate lpy (input) 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 46

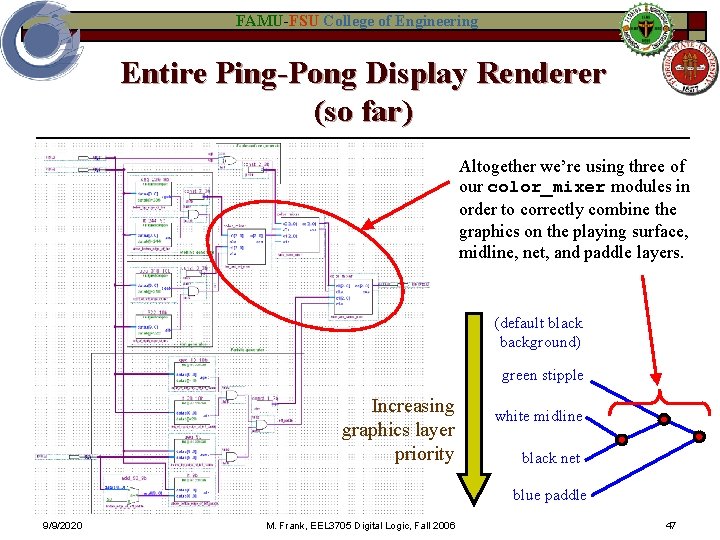

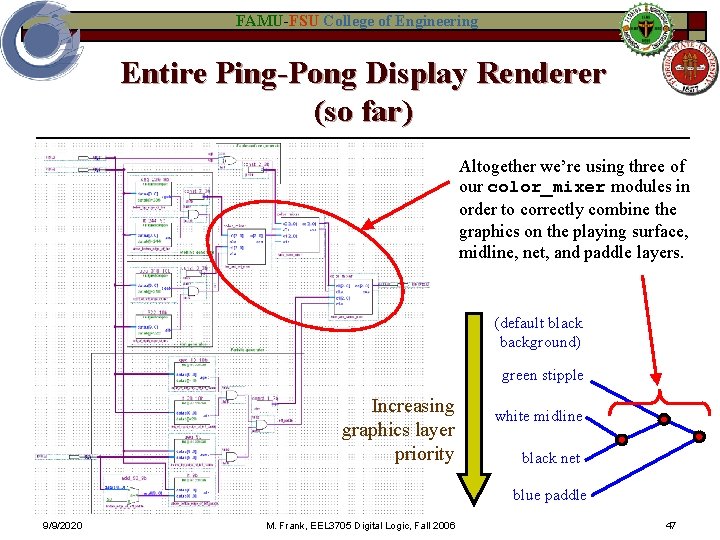

FAMU-FSU College of Engineering Entire Ping-Pong Display Renderer (so far) Altogether we’re using three of our color_mixer modules in order to correctly combine the graphics on the playing surface, midline, net, and paddle layers. (default black background) green stipple Increasing graphics layer priority white midline black net blue paddle 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 47

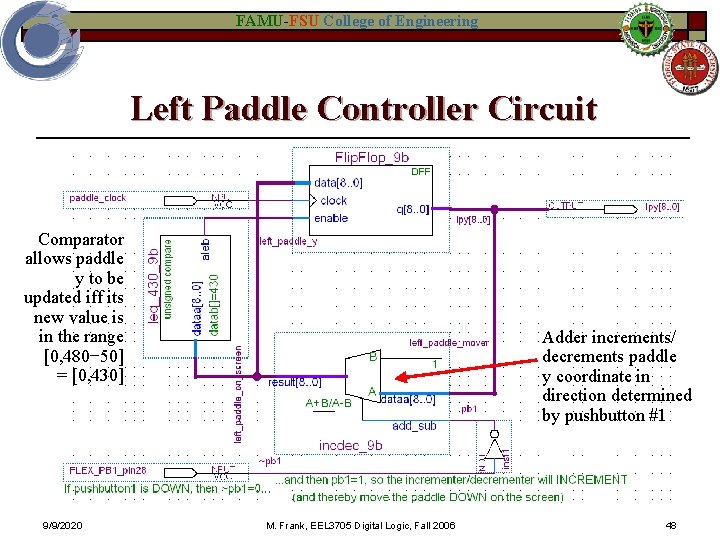

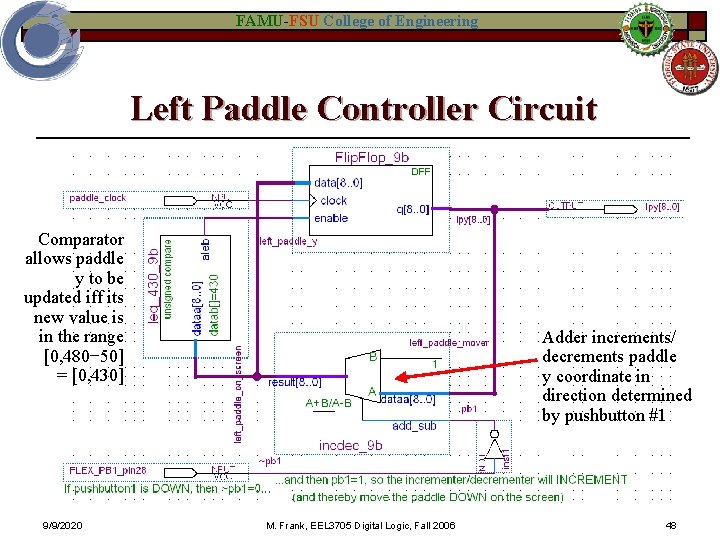

FAMU-FSU College of Engineering Left Paddle Controller Circuit Comparator allows paddle y to be updated iff its new value is in the range [0, 480− 50] = [0, 430] 9/9/2020 Adder increments/ decrements paddle y coordinate in direction determined by pushbutton #1 M. Frank, EEL 3705 Digital Logic, Fall 2006 48

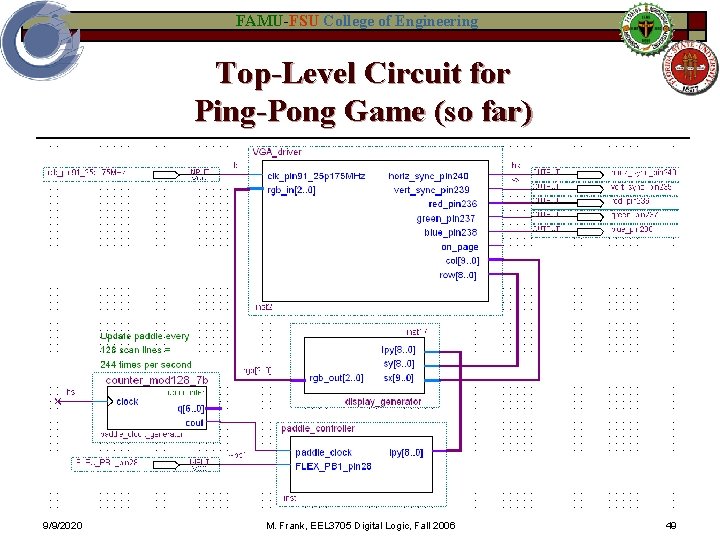

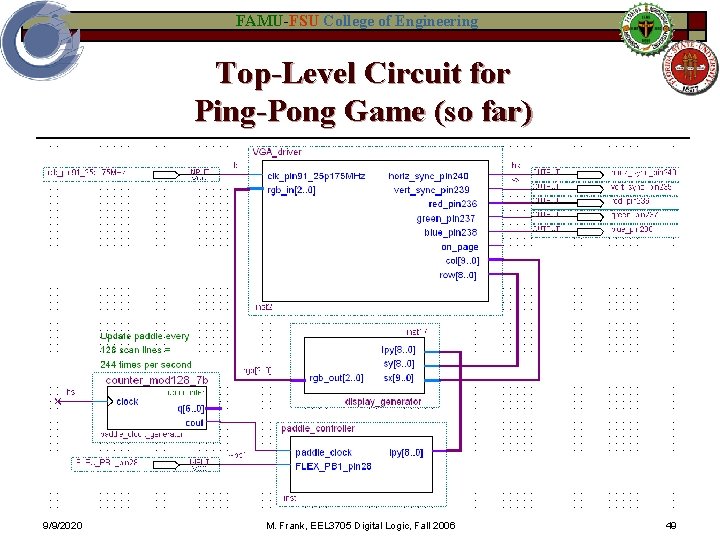

FAMU-FSU College of Engineering Top-Level Circuit for Ping-Pong Game (so far) 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 49

FAMU-FSU College of Engineering Demonstration of Game Display (so far) o We can hook up the board directly to the lecture hall video projector in order to demonstrate the left paddle’s live functionality to the class… 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 50

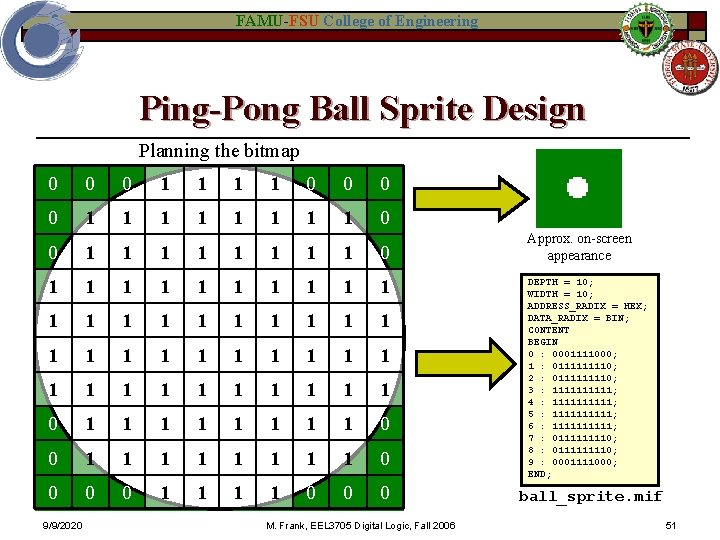

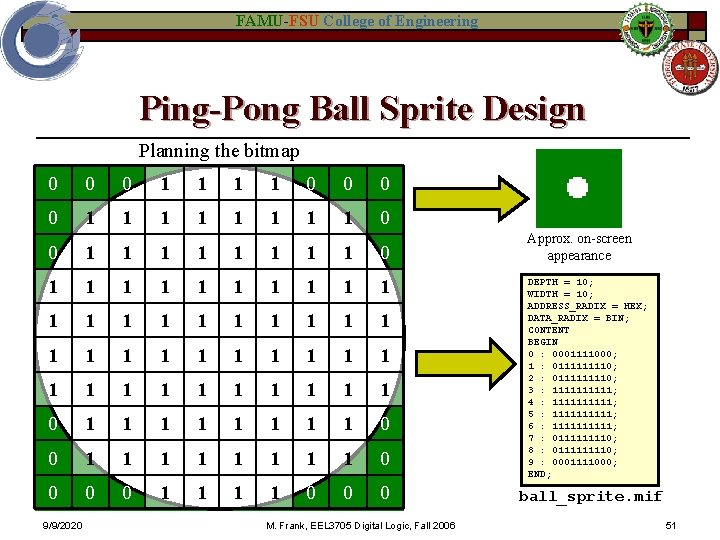

FAMU-FSU College of Engineering Ping-Pong Ball Sprite Design Planning the bitmap 0 0 0 1 1 1 1 0 0 1 1 1 1 1 1 1 1 1 1 1 1 0 1 1 1 1 0 0 0 0 1 1 0 0 0 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 Approx. on-screen appearance DEPTH = 10; WIDTH = 10; ADDRESS_RADIX = HEX; DATA_RADIX = BIN; CONTENT BEGIN 0 : 0001111000; 1 : 011110; 2 : 011110; 3 : 11111; 4 : 11111; 5 : 11111; 6 : 11111; 7 : 011110; 8 : 011110; 9 : 0001111000; END; ball_sprite. mif 51

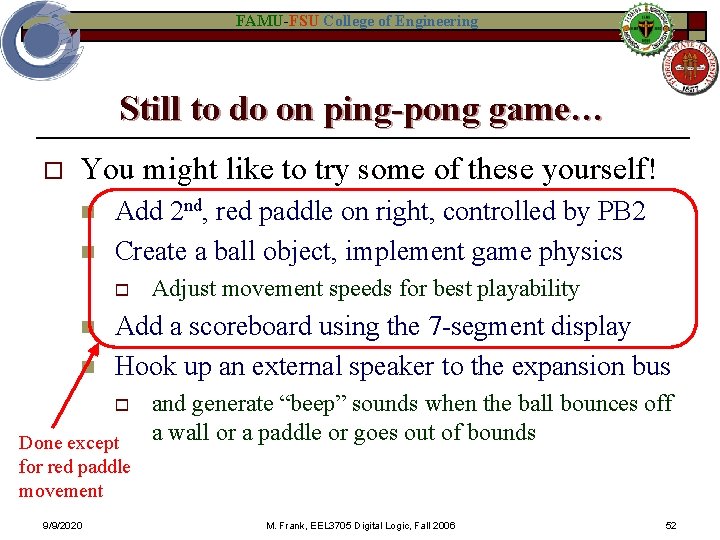

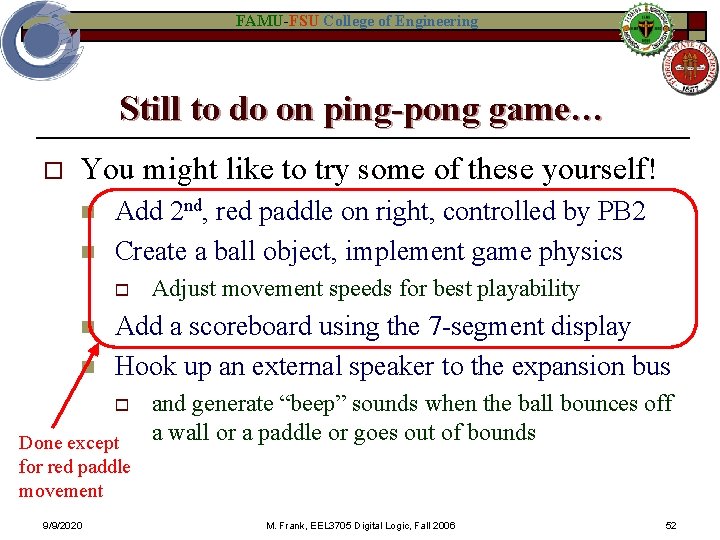

FAMU-FSU College of Engineering Still to do on ping-pong game… o You might like to try some of these yourself! n n Add 2 nd, red paddle on right, controlled by PB 2 Create a ball object, implement game physics o n n Add a scoreboard using the 7 -segment display Hook up an external speaker to the expansion bus o Done except for red paddle movement 9/9/2020 Adjust movement speeds for best playability and generate “beep” sounds when the ball bounces off a wall or a paddle or goes out of bounds M. Frank, EEL 3705 Digital Logic, Fall 2006 52

FAMU-FSU College of Engineering Keyboard and Mouse Input Using the PS/2 Port 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 53

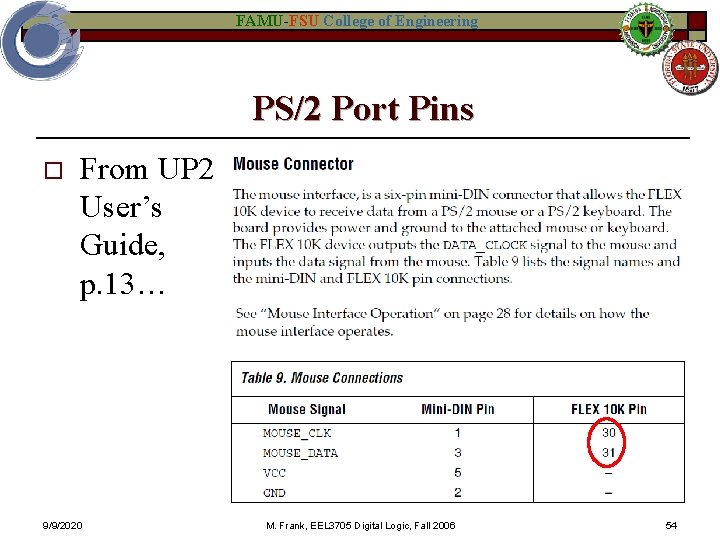

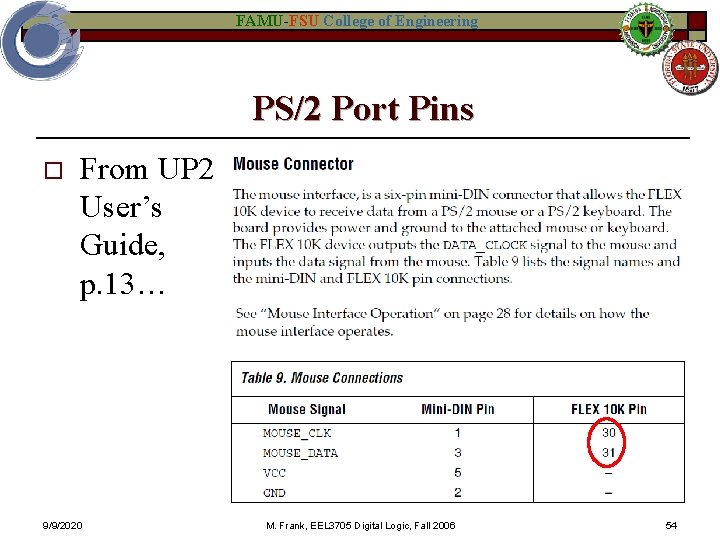

FAMU-FSU College of Engineering PS/2 Port Pins o From UP 2 User’s Guide, p. 13… 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 54

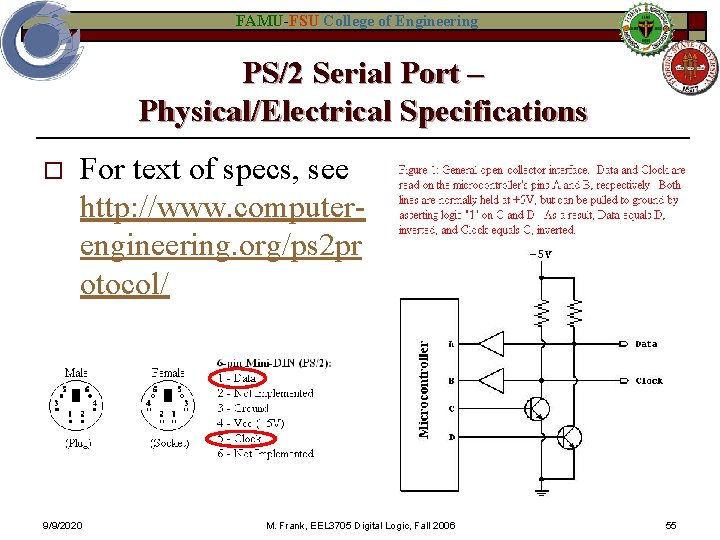

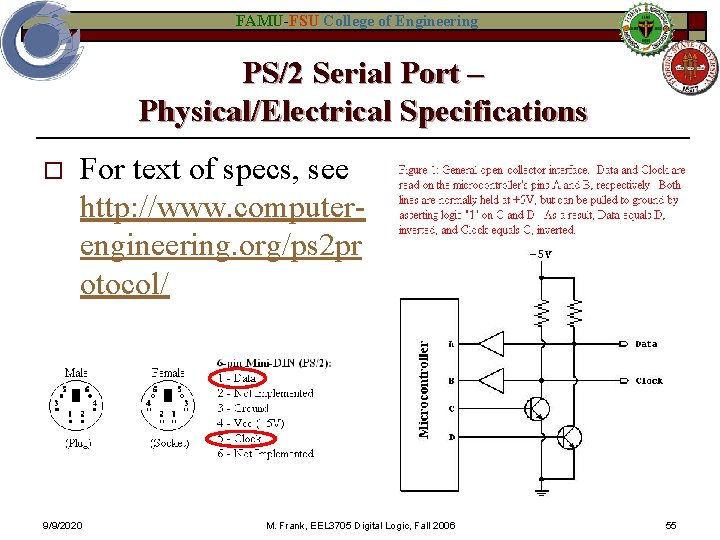

FAMU-FSU College of Engineering PS/2 Serial Port – Physical/Electrical Specifications o For text of specs, see http: //www. computerengineering. org/ps 2 pr otocol/ 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 55

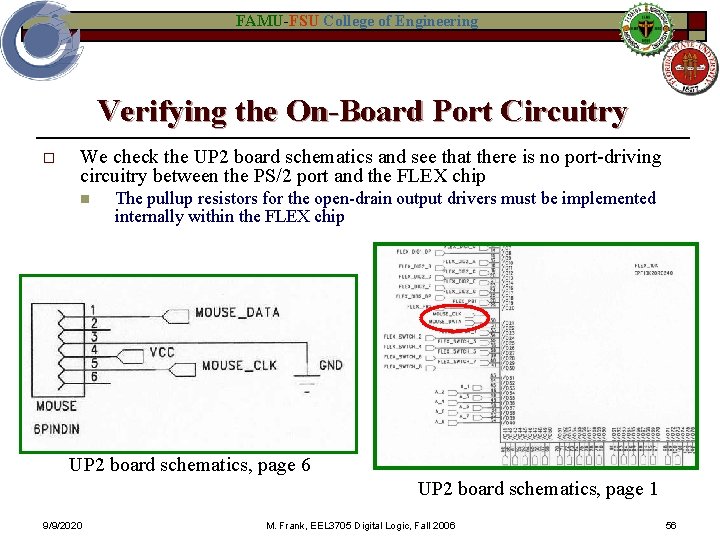

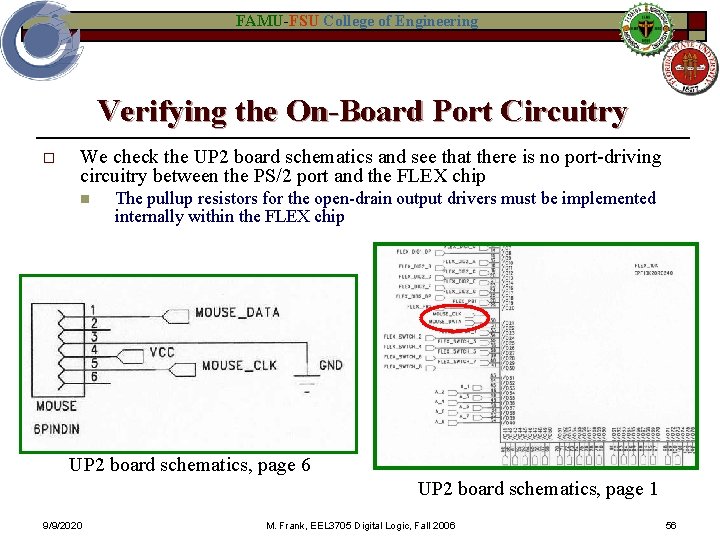

FAMU-FSU College of Engineering Verifying the On-Board Port Circuitry o We check the UP 2 board schematics and see that there is no port-driving circuitry between the PS/2 port and the FLEX chip n The pullup resistors for the open-drain output drivers must be implemented internally within the FLEX chip UP 2 board schematics, page 6 UP 2 board schematics, page 1 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 56

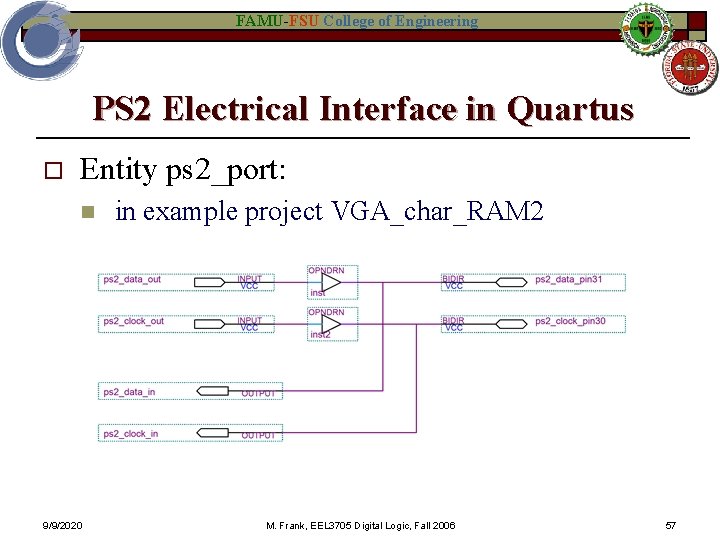

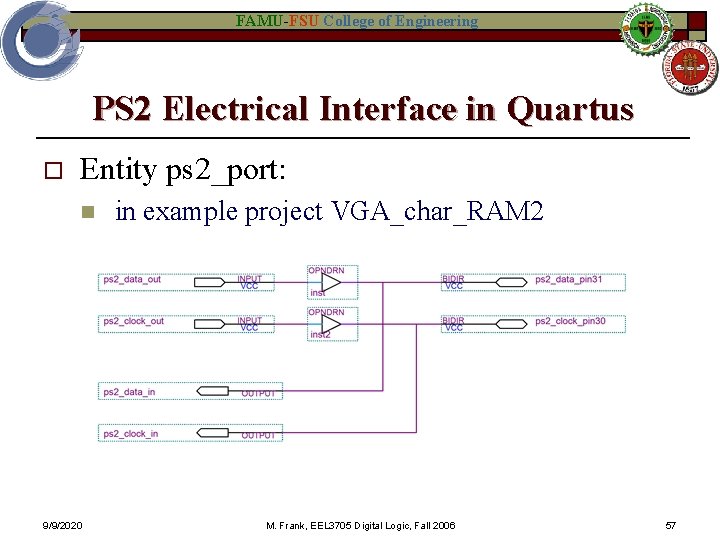

FAMU-FSU College of Engineering PS 2 Electrical Interface in Quartus o Entity ps 2_port: n 9/9/2020 in example project VGA_char_RAM 2 M. Frank, EEL 3705 Digital Logic, Fall 2006 57

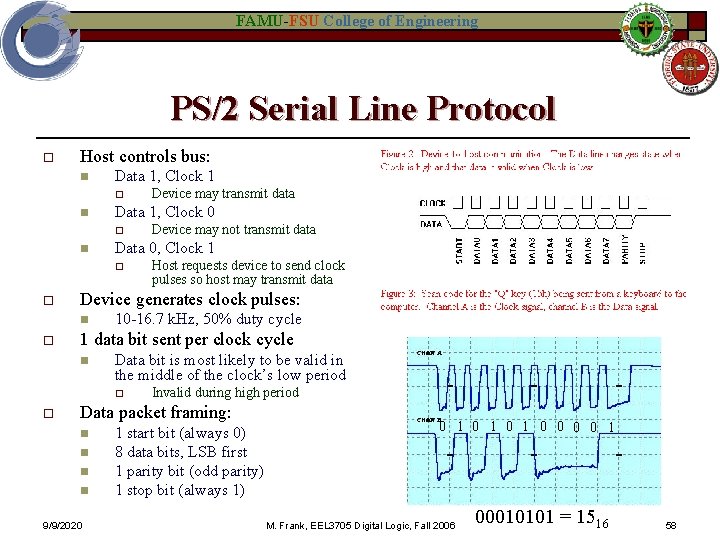

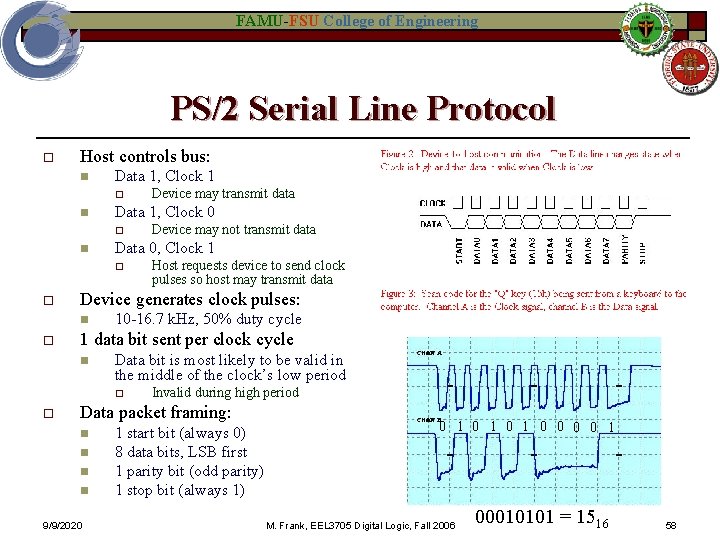

FAMU-FSU College of Engineering PS/2 Serial Line Protocol o Host controls bus: n Data 1, Clock 1 o n Data 1, Clock 0 o n 10 -16. 7 k. Hz, 50% duty cycle 1 data bit sent per clock cycle n Data bit is most likely to be valid in the middle of the clock’s low period o o Host requests device to send clock pulses so host may transmit data Device generates clock pulses: n o Device may not transmit data Data 0, Clock 1 o o Device may transmit data Invalid during high period Data packet framing: n n 9/9/2020 1 start bit (always 0) 8 data bits, LSB first 1 parity bit (odd parity) 1 stop bit (always 1) 0 1 0 1 0 0 1 M. Frank, EEL 3705 Digital Logic, Fall 2006 00010101 = 1516 58

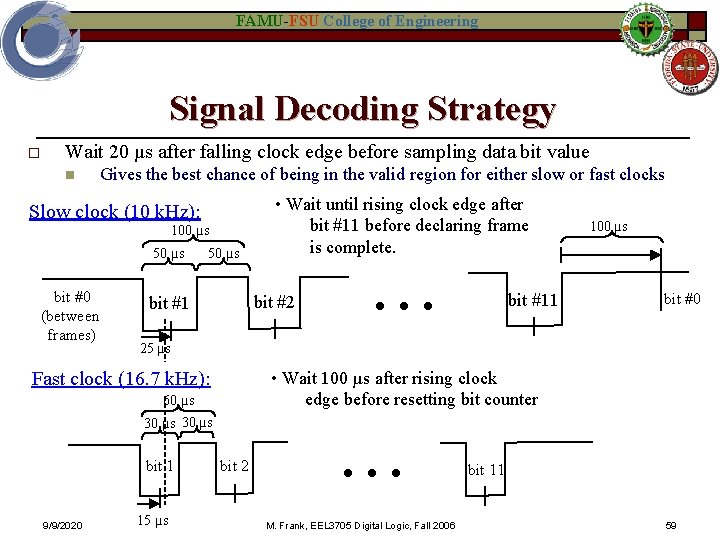

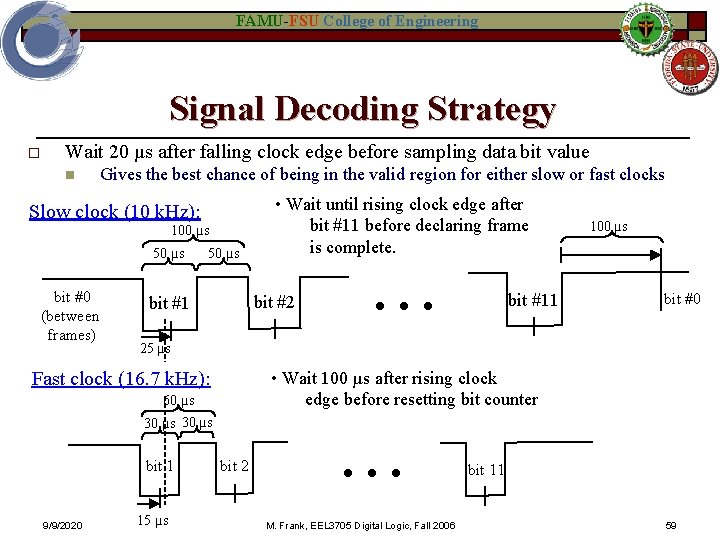

FAMU-FSU College of Engineering Signal Decoding Strategy o Wait 20 µs after falling clock edge before sampling data bit value n Gives the best chance of being in the valid region for either slow or fast clocks Slow clock (10 k. Hz): 100 µs 50 µs bit #0 (between frames) 50 µs bit #2 bit #1 … bit #11 100 µs bit #0 25 µs Fast clock (16. 7 k. Hz): • Wait 100 µs after rising clock edge before resetting bit counter 60 µs 30 µs bit 1 9/9/2020 • Wait until rising clock edge after bit #11 before declaring frame is complete. 15 µs bit 2 … M. Frank, EEL 3705 Digital Logic, Fall 2006 bit 11 59

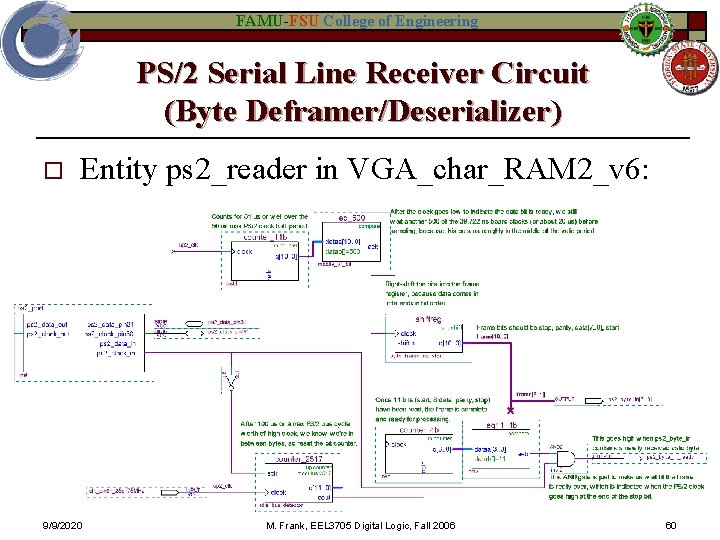

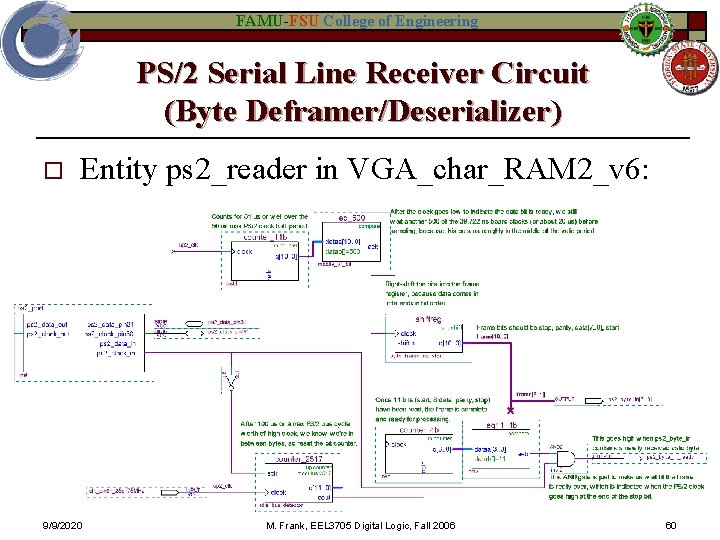

FAMU-FSU College of Engineering PS/2 Serial Line Receiver Circuit (Byte Deframer/Deserializer) o Entity ps 2_reader in VGA_char_RAM 2_v 6: 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 60

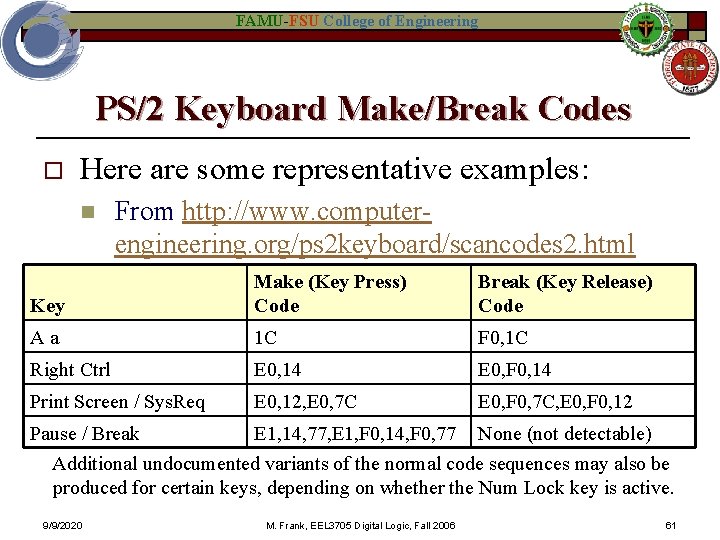

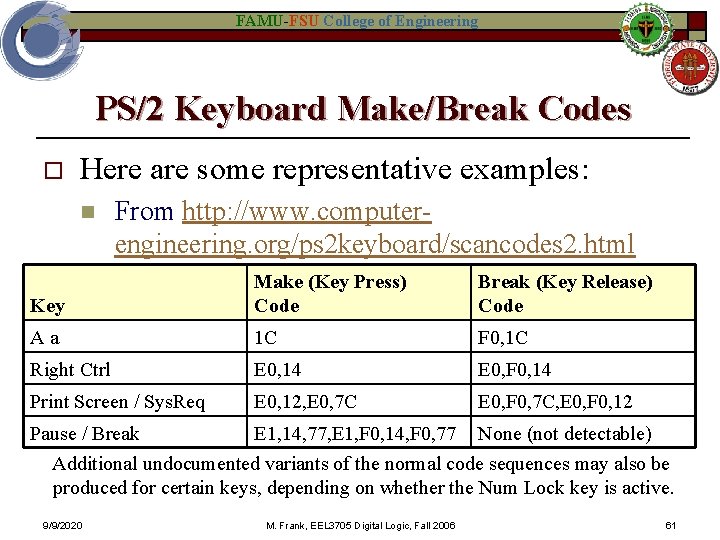

FAMU-FSU College of Engineering PS/2 Keyboard Make/Break Codes o Here are some representative examples: n From http: //www. computerengineering. org/ps 2 keyboard/scancodes 2. html Key Make (Key Press) Code Break (Key Release) Code Aa 1 C F 0, 1 C Right Ctrl E 0, 14 E 0, F 0, 14 Print Screen / Sys. Req E 0, 12, E 0, 7 C E 0, F 0, 7 C, E 0, F 0, 12 Pause / Break E 1, 14, 77, E 1, F 0, 14, F 0, 77 None (not detectable) Additional undocumented variants of the normal code sequences may also be produced for certain keys, depending on whether the Num Lock key is active. 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 61

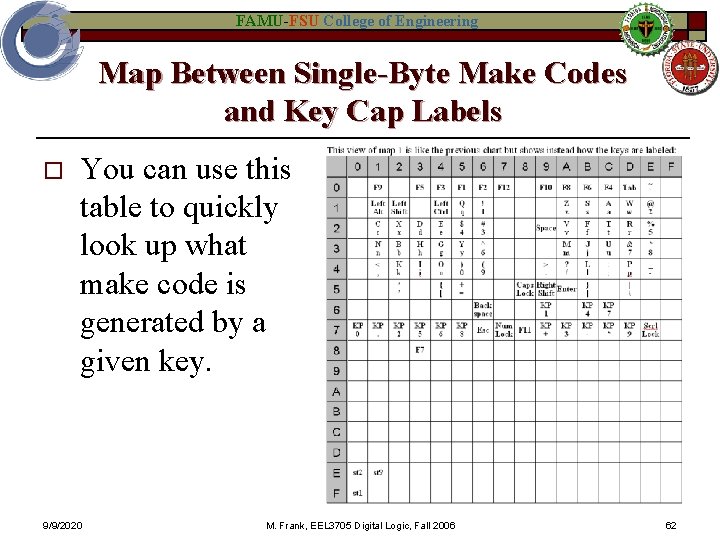

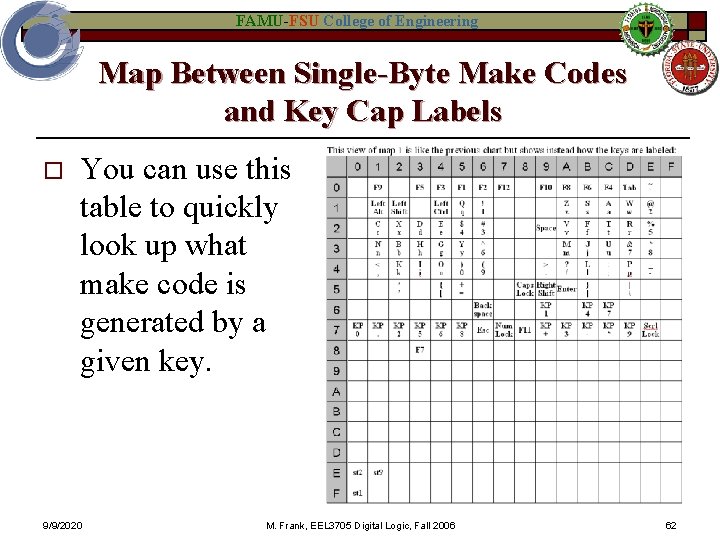

FAMU-FSU College of Engineering Map Between Single-Byte Make Codes and Key Cap Labels o You can use this table to quickly look up what make code is generated by a given key. 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 62

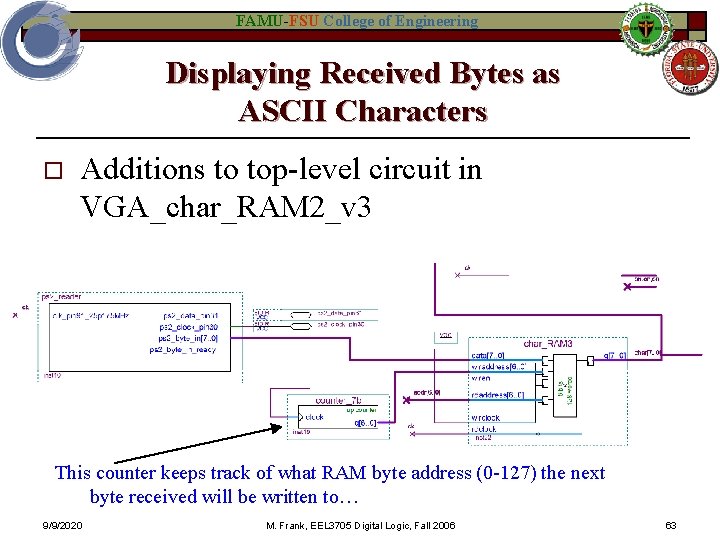

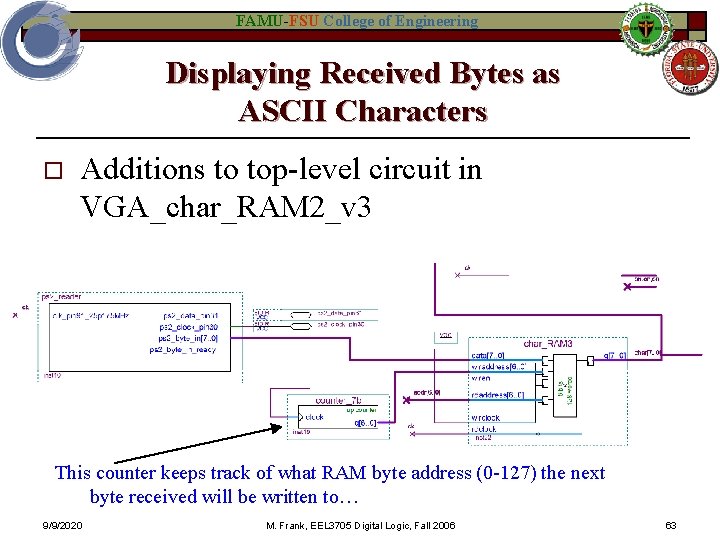

FAMU-FSU College of Engineering Displaying Received Bytes as ASCII Characters o Additions to top-level circuit in VGA_char_RAM 2_v 3 This counter keeps track of what RAM byte address (0 -127) the next byte received will be written to… 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 63

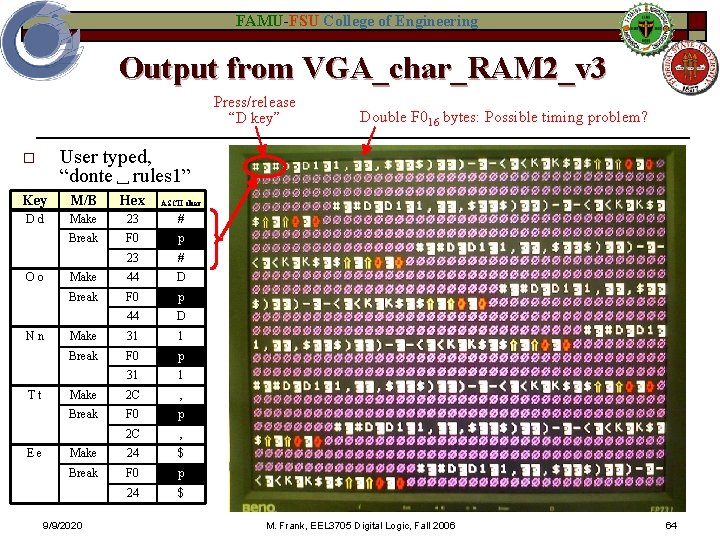

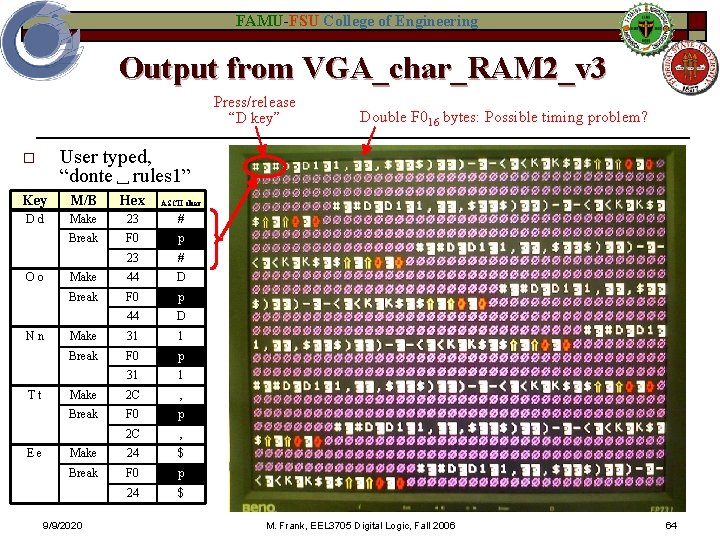

FAMU-FSU College of Engineering Output from VGA_char_RAM 2_v 3 Press/release “D key” User typed, “donte␣rules 1” o Key M/B Hex ASCII char Dd Make 23 # Break F 0 p 23 # Make 44 D Break F 0 p 44 D Make 31 1 Break F 0 p 31 1 Make 2 C , Break F 0 p 2 C , Make 24 $ Break F 0 p 24 $ Oo Nn Tt Ee Double F 016 bytes: Possible timing problem? 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 64

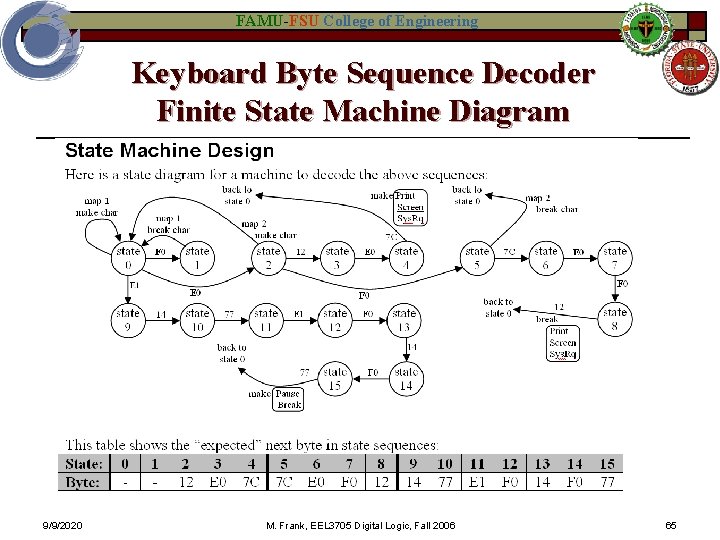

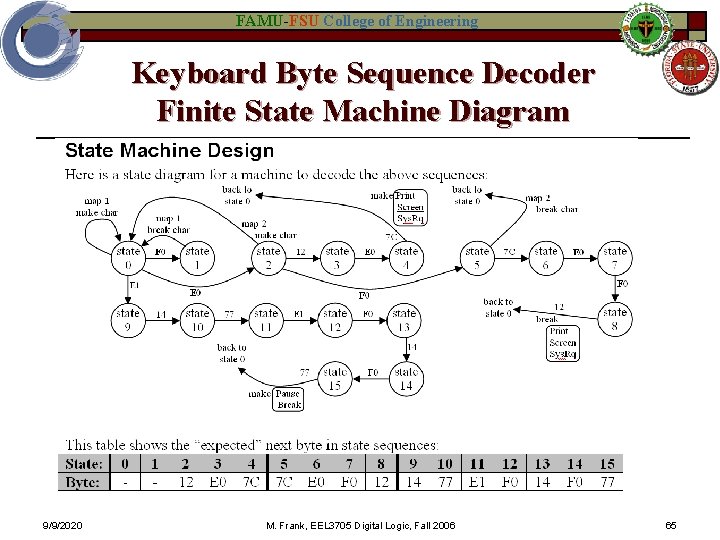

FAMU-FSU College of Engineering Keyboard Byte Sequence Decoder Finite State Machine Diagram 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 65

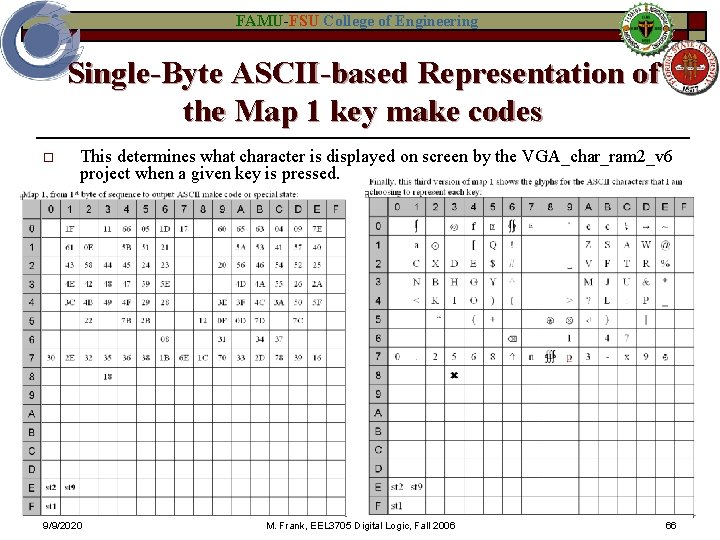

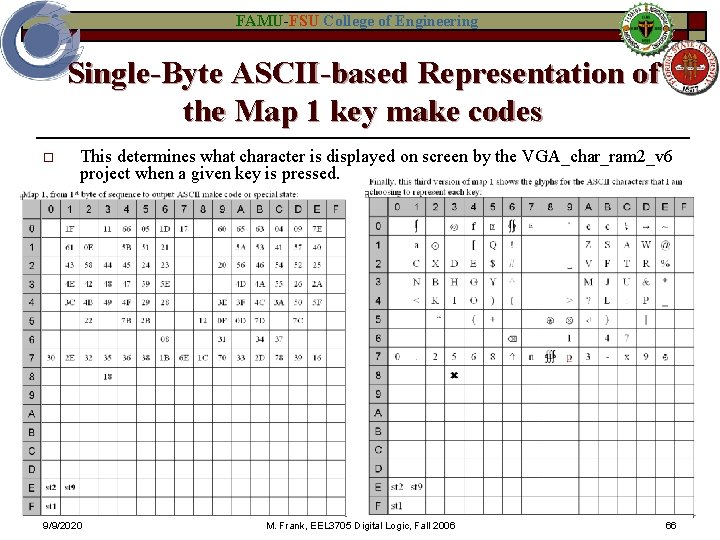

FAMU-FSU College of Engineering Single-Byte ASCII-based Representation of the Map 1 key make codes o This determines what character is displayed on screen by the VGA_char_ram 2_v 6 project when a given key is pressed. 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 66

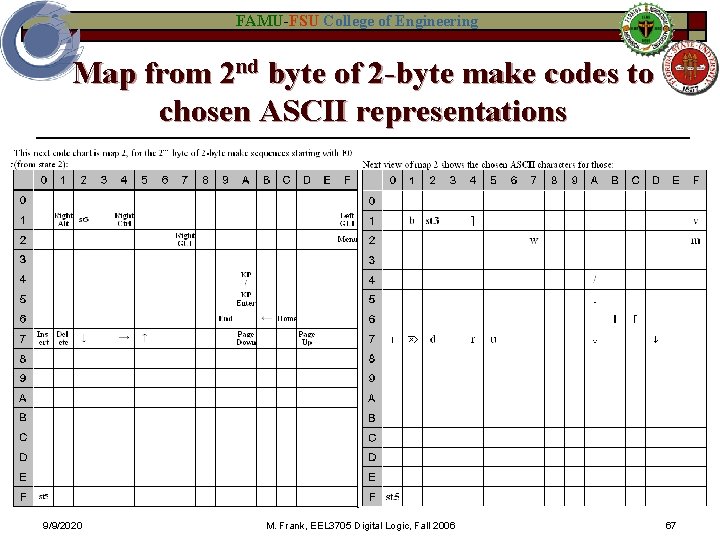

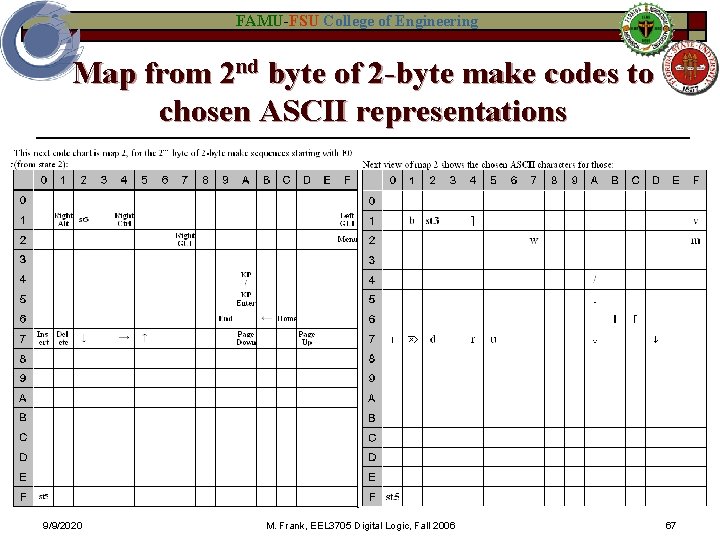

FAMU-FSU College of Engineering Map from 2 nd byte of 2 -byte make codes to chosen ASCII representations 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 67

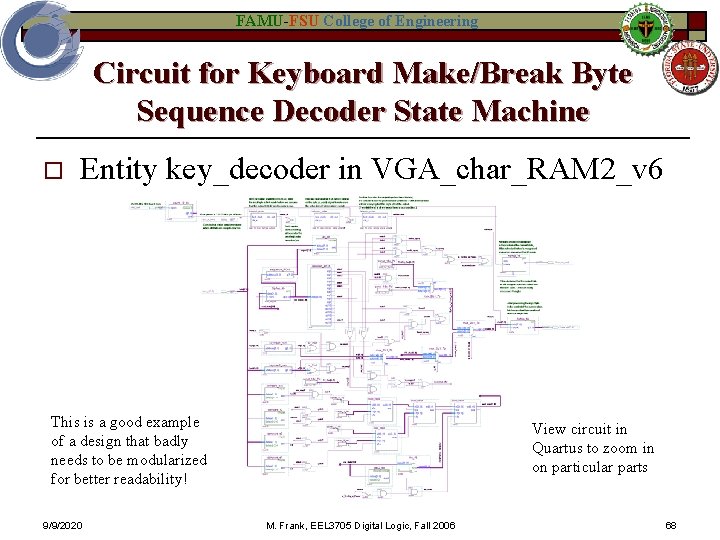

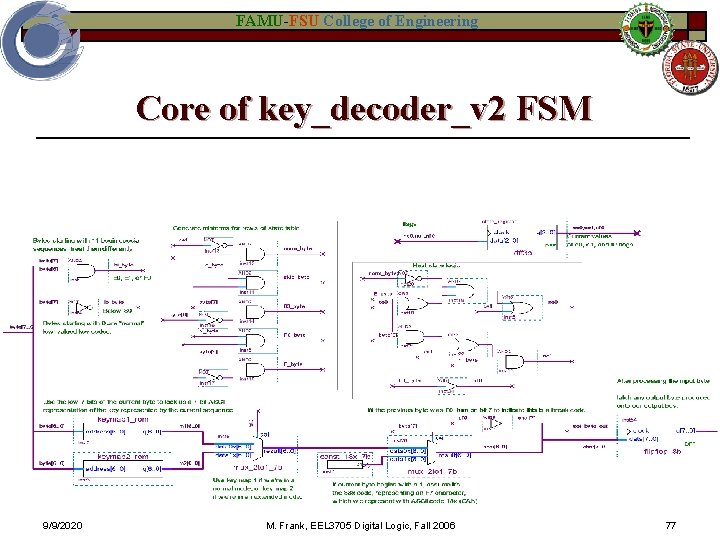

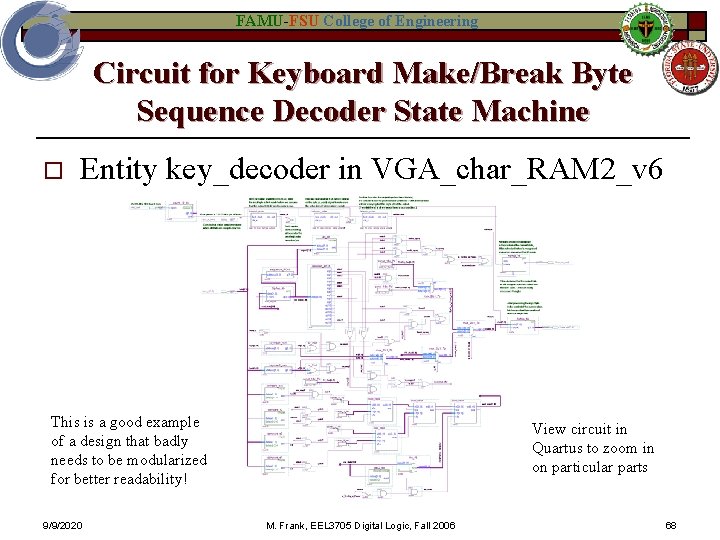

FAMU-FSU College of Engineering Circuit for Keyboard Make/Break Byte Sequence Decoder State Machine o Entity key_decoder in VGA_char_RAM 2_v 6 This is a good example of a design that badly needs to be modularized for better readability! 9/9/2020 View circuit in Quartus to zoom in on particular parts M. Frank, EEL 3705 Digital Logic, Fall 2006 68

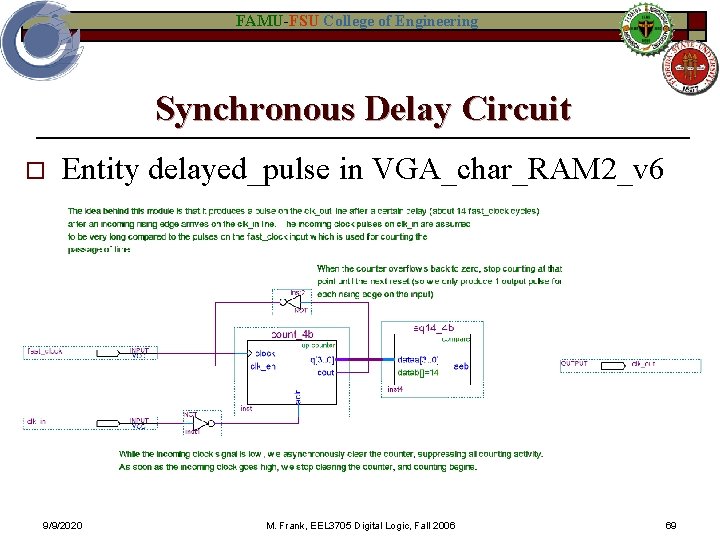

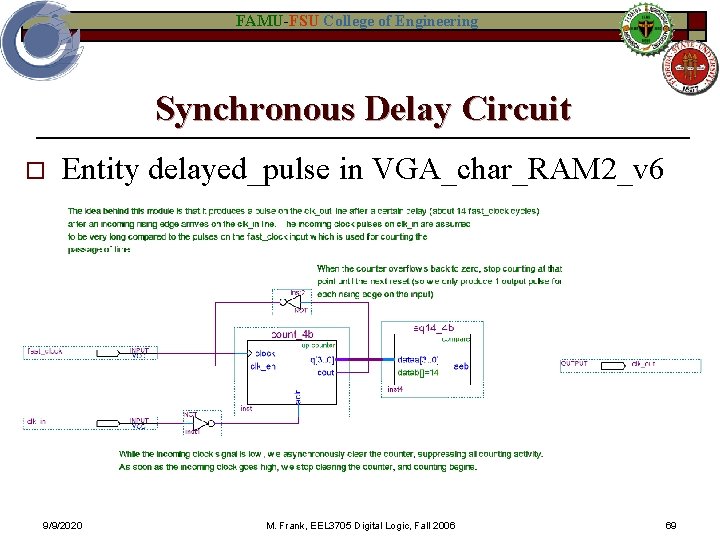

FAMU-FSU College of Engineering Synchronous Delay Circuit o Entity delayed_pulse in VGA_char_RAM 2_v 6 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 69

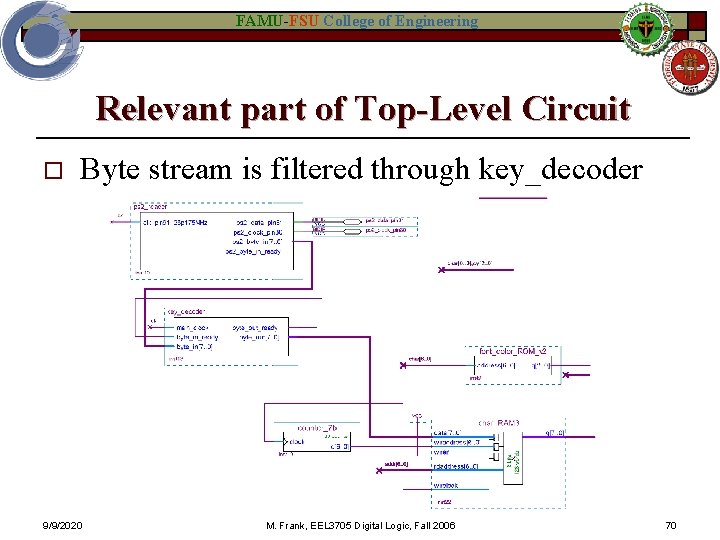

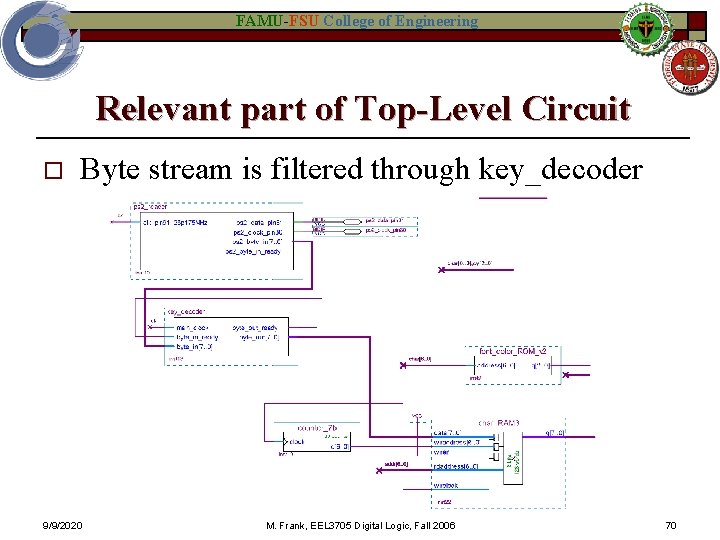

FAMU-FSU College of Engineering Relevant part of Top-Level Circuit o Byte stream is filtered through key_decoder 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 70

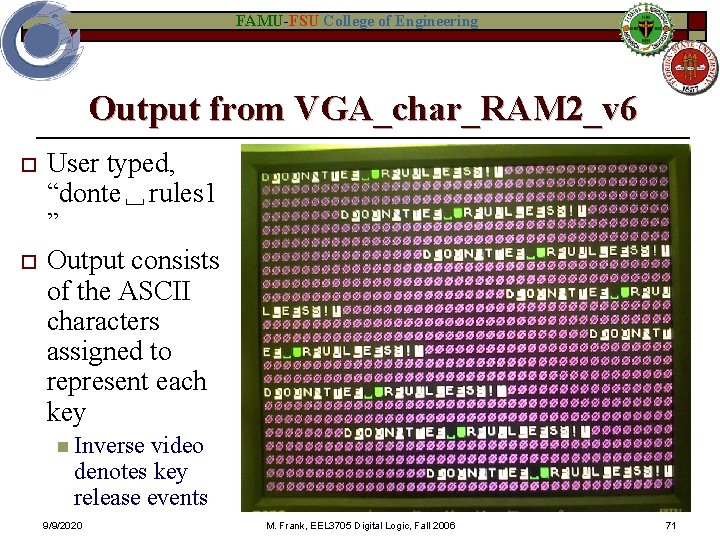

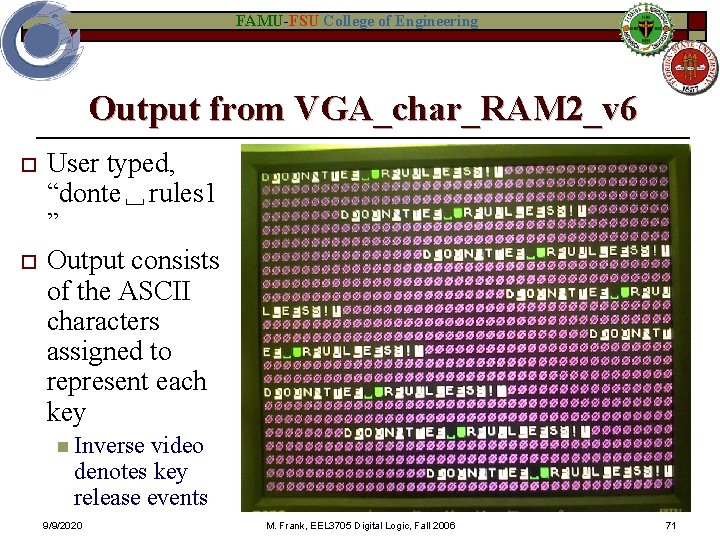

FAMU-FSU College of Engineering Output from VGA_char_RAM 2_v 6 o o User typed, “donte␣rules 1 ” Output consists of the ASCII characters assigned to represent each key n Inverse video denotes key release events 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 71

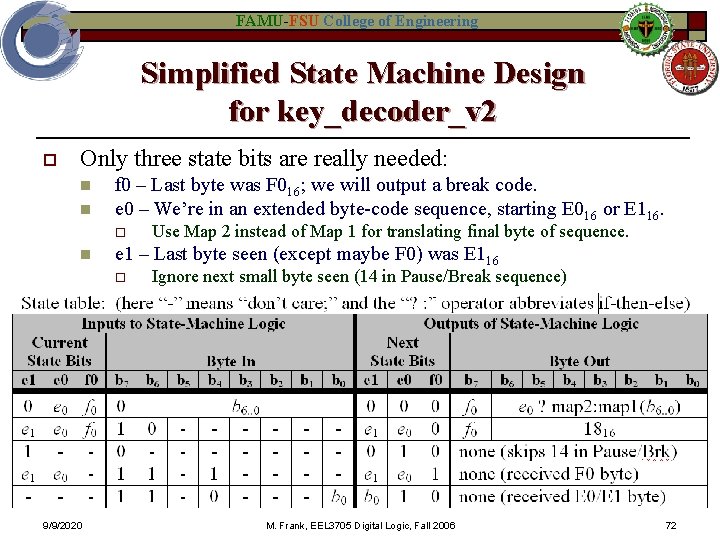

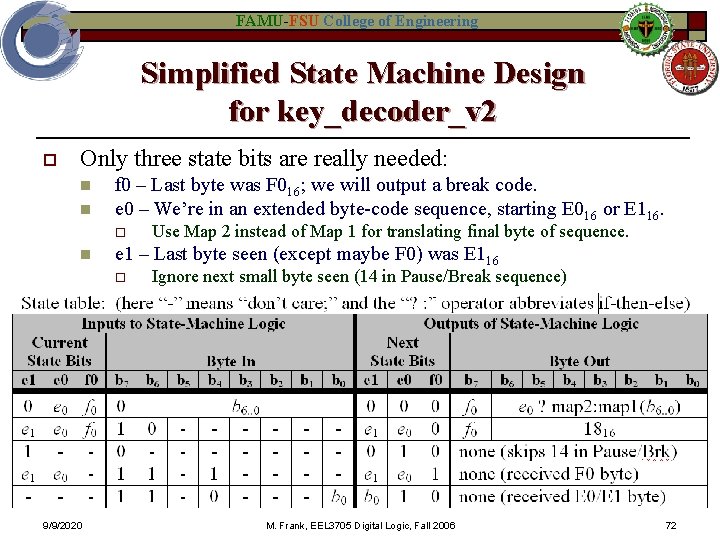

FAMU-FSU College of Engineering Simplified State Machine Design for key_decoder_v 2 o Only three state bits are really needed: n n f 0 – Last byte was F 016; we will output a break code. e 0 – We’re in an extended byte-code sequence, starting E 016 or E 116. o n e 1 – Last byte seen (except maybe F 0) was E 116 o 9/9/2020 Use Map 2 instead of Map 1 for translating final byte of sequence. Ignore next small byte seen (14 in Pause/Break sequence) M. Frank, EEL 3705 Digital Logic, Fall 2006 72

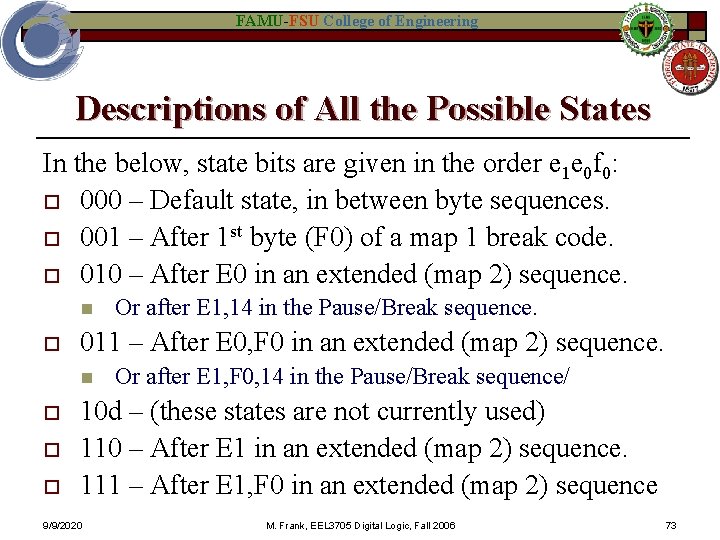

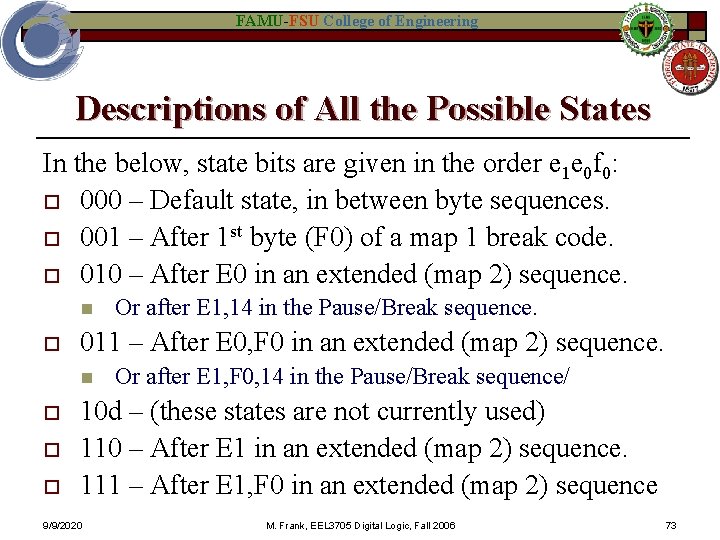

FAMU-FSU College of Engineering Descriptions of All the Possible States In the below, state bits are given in the order e 1 e 0 f 0: o 000 – Default state, in between byte sequences. o 001 – After 1 st byte (F 0) of a map 1 break code. o 010 – After E 0 in an extended (map 2) sequence. n o 011 – After E 0, F 0 in an extended (map 2) sequence. n o o o Or after E 1, 14 in the Pause/Break sequence. Or after E 1, F 0, 14 in the Pause/Break sequence/ 10 d – (these states are not currently used) 110 – After E 1 in an extended (map 2) sequence. 111 – After E 1, F 0 in an extended (map 2) sequence 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 73

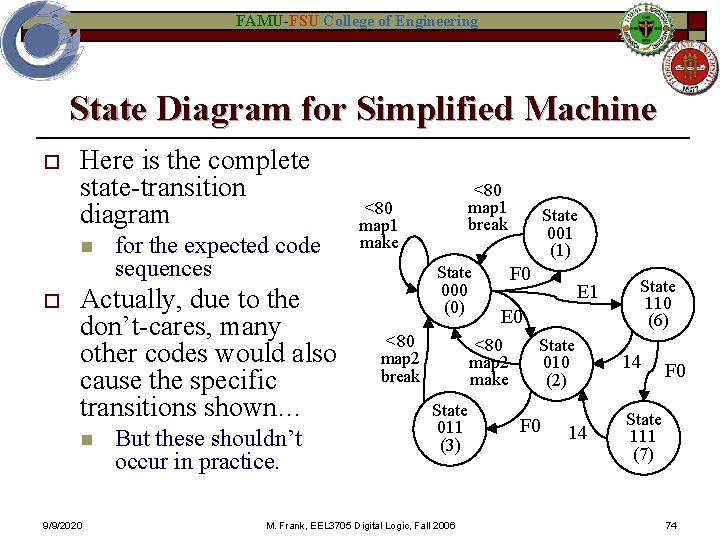

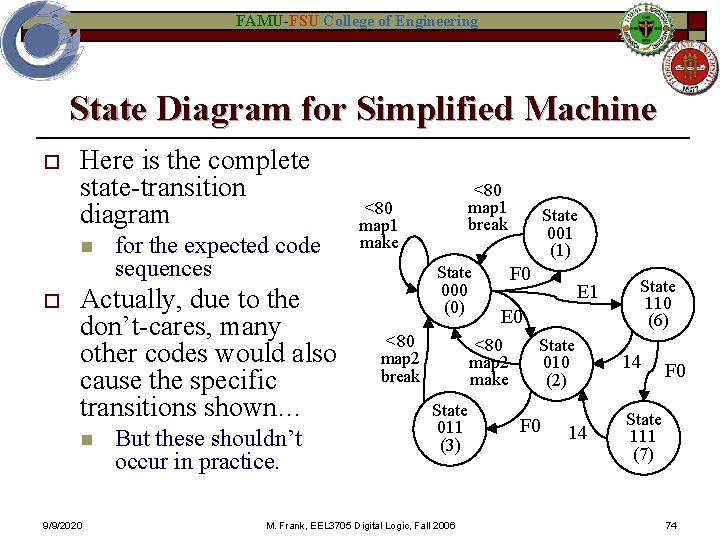

FAMU-FSU College of Engineering State Diagram for Simplified Machine o Here is the complete state-transition diagram n o for the expected code sequences Actually, due to the don’t-cares, many other codes would also cause the specific transitions shown… n 9/9/2020 But these shouldn’t occur in practice. <80 map 1 break <80 map 1 make State 000 (0) <80 map 2 break F 0 M. Frank, EEL 3705 Digital Logic, Fall 2006 E 1 E 0 <80 map 2 make State 011 (3) State 001 (1) State 010 (2) F 0 14 State 110 (6) 14 F 0 State 111 (7) 74

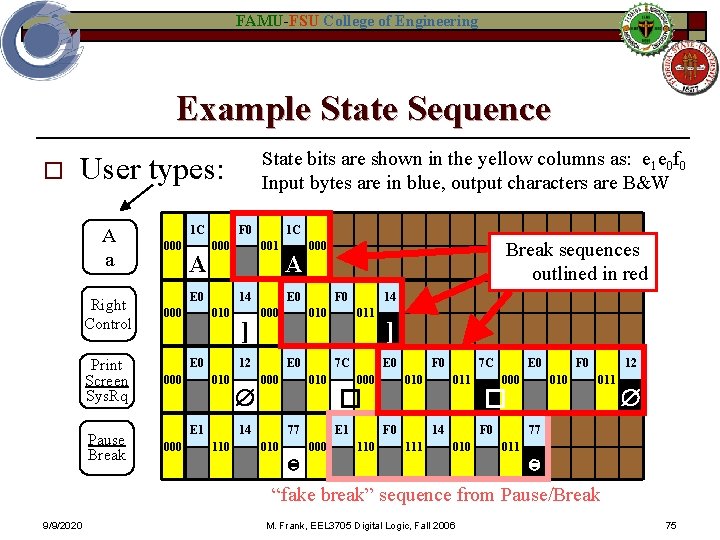

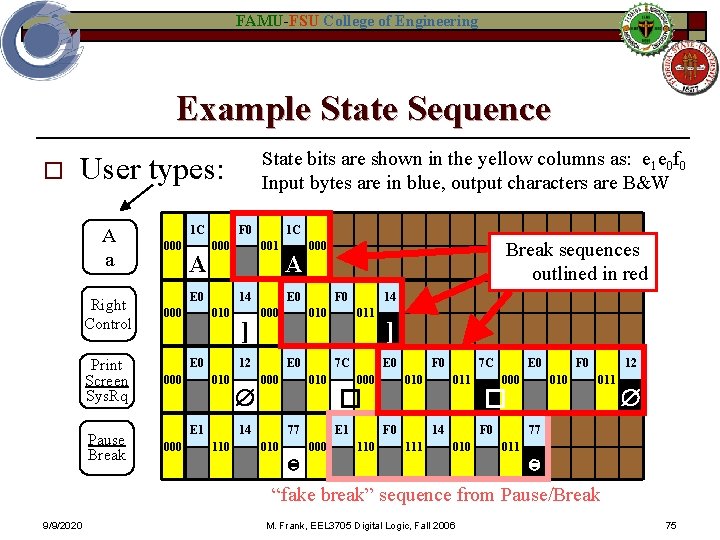

FAMU-FSU College of Engineering Example State Sequence o State bits are shown in the yellow columns as: e 1 e 0 f 0 Input bytes are in blue, output characters are B&W User types: A a Right Control Print Screen Sys. Rq Pause Break 1 C 000 A F 0 000 E 0 ] 010 000 010 ⊜ 14 011 7 C 77 010 Break sequences outlined in red F 0 E 0 14 110 A 000 E 0 12 E 1 000 001 14 010 000 1 C E 0 000 F 0 010 � E 1 000 ] F 0 110 7 C 011 14 111 E 0 000 010 � F 0 12 011 77 011 ⊜ “fake break” sequence from Pause/Break 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 75

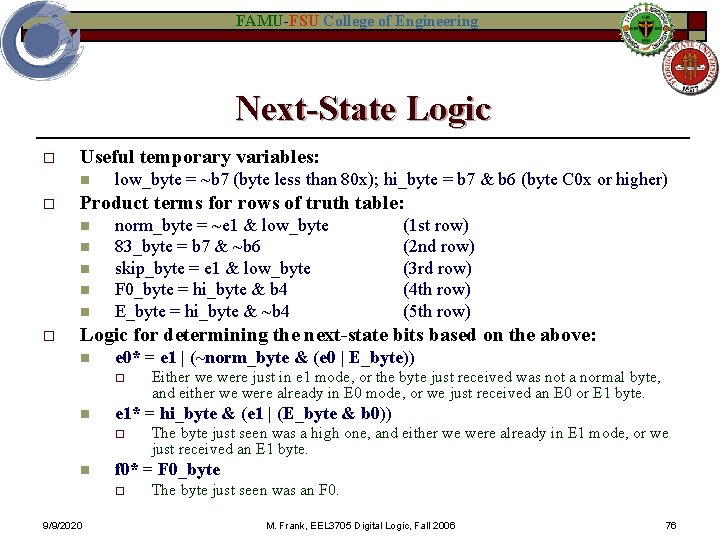

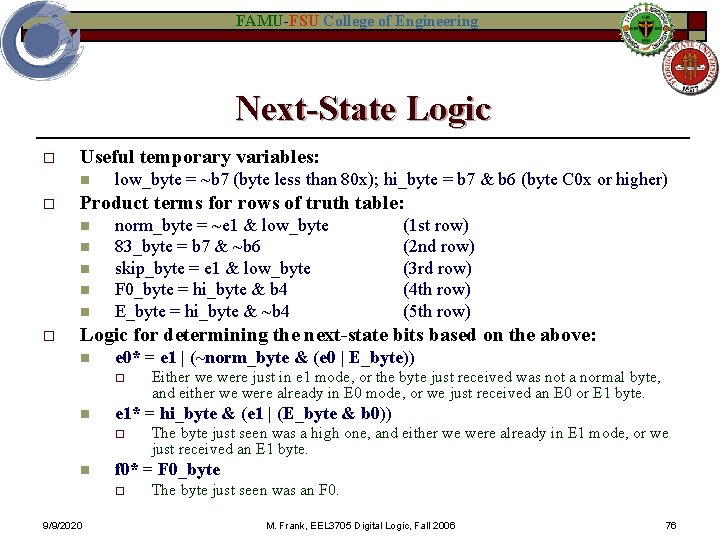

FAMU-FSU College of Engineering Next-State Logic o Useful temporary variables: n o Product terms for rows of truth table: n n n o low_byte = ~b 7 (byte less than 80 x); hi_byte = b 7 & b 6 (byte C 0 x or higher) norm_byte = ~e 1 & low_byte 83_byte = b 7 & ~b 6 skip_byte = e 1 & low_byte F 0_byte = hi_byte & b 4 E_byte = hi_byte & ~b 4 (1 st row) (2 nd row) (3 rd row) (4 th row) (5 th row) Logic for determining the next-state bits based on the above: n e 0* = e 1 | (~norm_byte & (e 0 | E_byte)) o n e 1* = hi_byte & (e 1 | (E_byte & b 0)) o n The byte just seen was a high one, and either we were already in E 1 mode, or we just received an E 1 byte. f 0* = F 0_byte o 9/9/2020 Either we were just in e 1 mode, or the byte just received was not a normal byte, and either we were already in E 0 mode, or we just received an E 0 or E 1 byte. The byte just seen was an F 0. M. Frank, EEL 3705 Digital Logic, Fall 2006 76

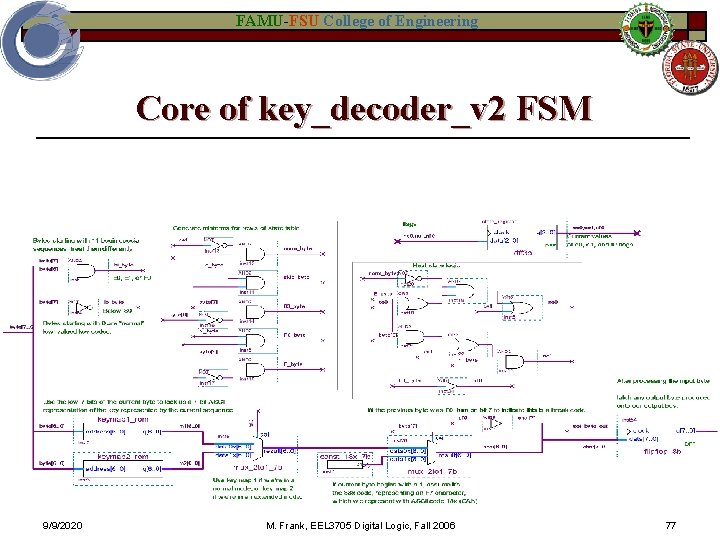

FAMU-FSU College of Engineering Core of key_decoder_v 2 FSM 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 77

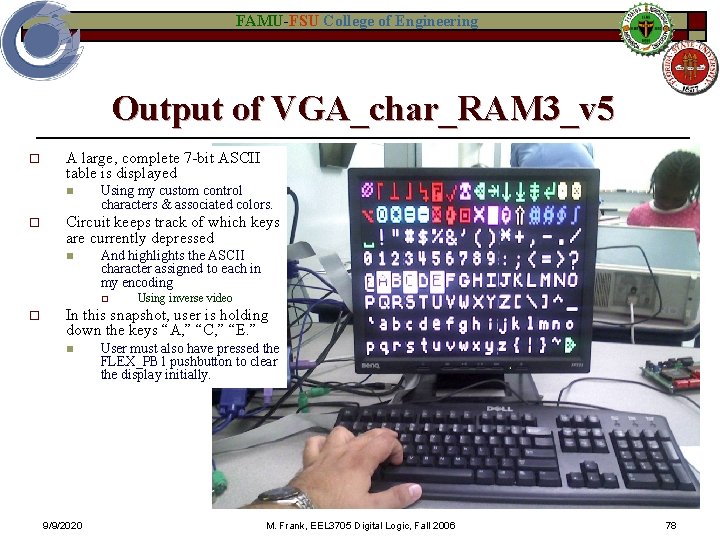

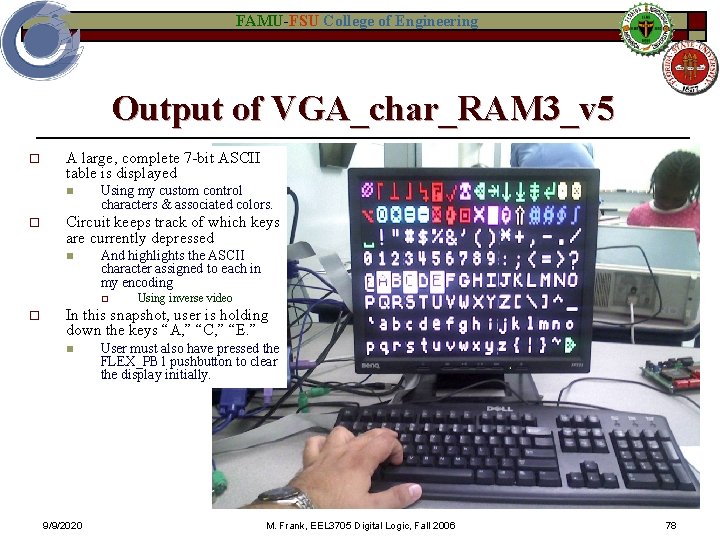

FAMU-FSU College of Engineering Output of VGA_char_RAM 3_v 5 o A large, complete 7 -bit ASCII table is displayed n o Using my custom control characters & associated colors. Circuit keeps track of which keys are currently depressed n And highlights the ASCII character assigned to each in my encoding o o Using inverse video In this snapshot, user is holding down the keys “A, ” “C, ” “E. ” n 9/9/2020 User must also have pressed the FLEX_PB 1 pushbutton to clear the display initially. M. Frank, EEL 3705 Digital Logic, Fall 2006 78

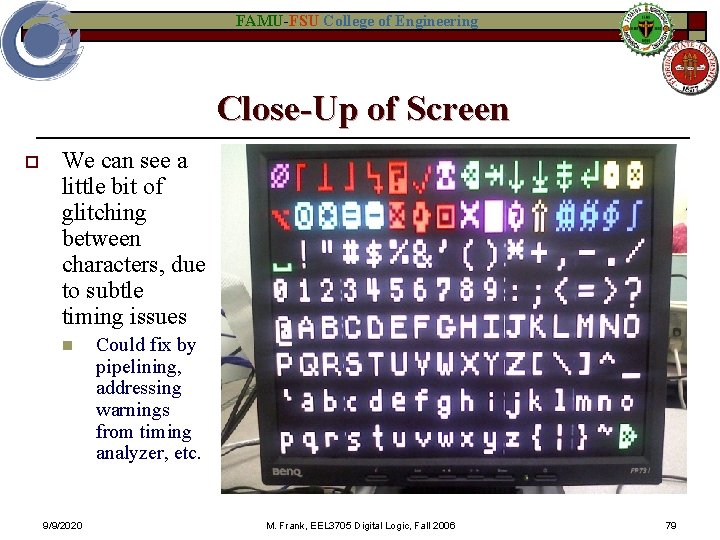

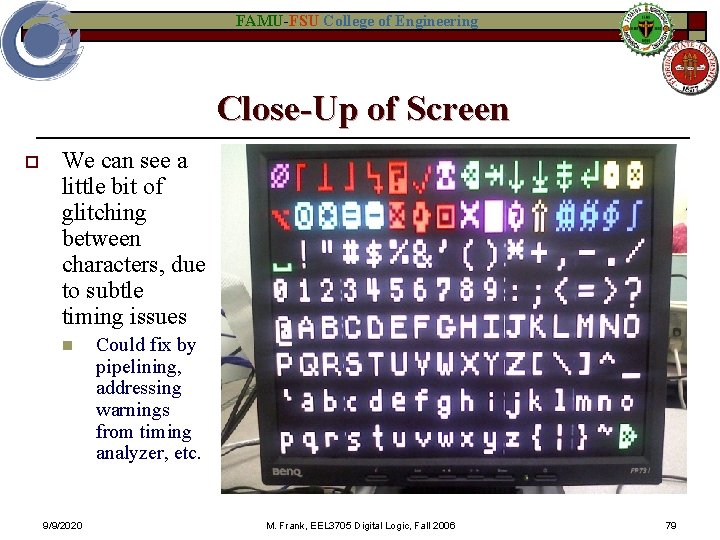

FAMU-FSU College of Engineering Close-Up of Screen o We can see a little bit of glitching between characters, due to subtle timing issues n 9/9/2020 Could fix by pipelining, addressing warnings from timing analyzer, etc. M. Frank, EEL 3705 Digital Logic, Fall 2006 79

FAMU-FSU College of Engineering Further Ideas for Building on Key Decoder o Write a secondary decoder that translates makebreak sequences into standard ASCII characters… n E. g. , take as input the following event sequence… o n o and produce as output the single character “&” Write a simple text-entry application n o make (left shift), make (& 7), break (left shift) Accept formatting characters �↦ ↓ ↧ ↡ ↵ and translate them into appropriate cursor movements Video games, music synthesizer (piano keyboard), etc… 9/9/2020 M. Frank, EEL 3705 Digital Logic, Fall 2006 80