EE 2174 Digital Logic and Lab Professor Shiyan

EE 2174: Digital Logic and Lab Professor Shiyan Hu Department of Electrical and Computer Engineering Michigan Technological University Encoder and Decoder

Overview of Encoder and Decoder n n n MUX Gate Rudimentary functions Binary Decoders n n 25 -Nov-20 Expansion Circuit implementation Binary Encoders Priority Encoders PJF - 2

Multiplexer n n “Selects” binary information from one of many input lines and directs it to a single output line. Also know as the “selector” circuit, Selection is controlled by a particular set of inputs lines whose # depends on the # of the data input lines. For a 2 n-to-1 multiplexer, there are 2 n data input lines and n selection lines whose bit combination determines which input is selected. 25 -Nov-20 PJF - 3 Combinational Logic

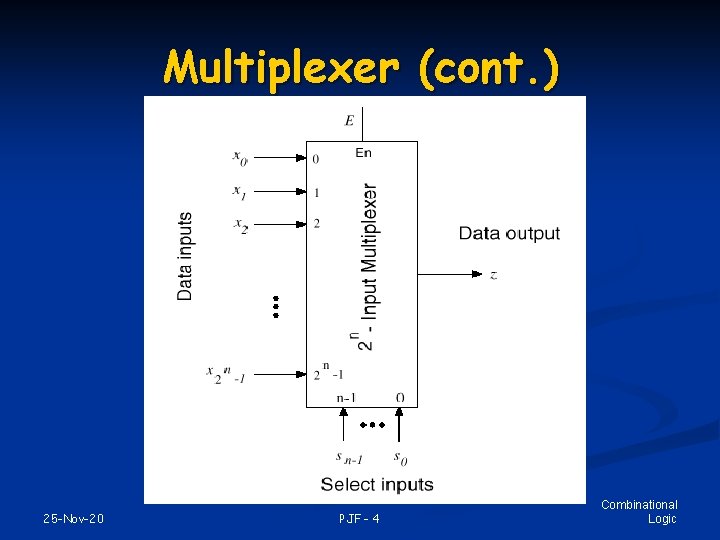

Multiplexer (cont. ) 25 -Nov-20 PJF - 4 Combinational Logic

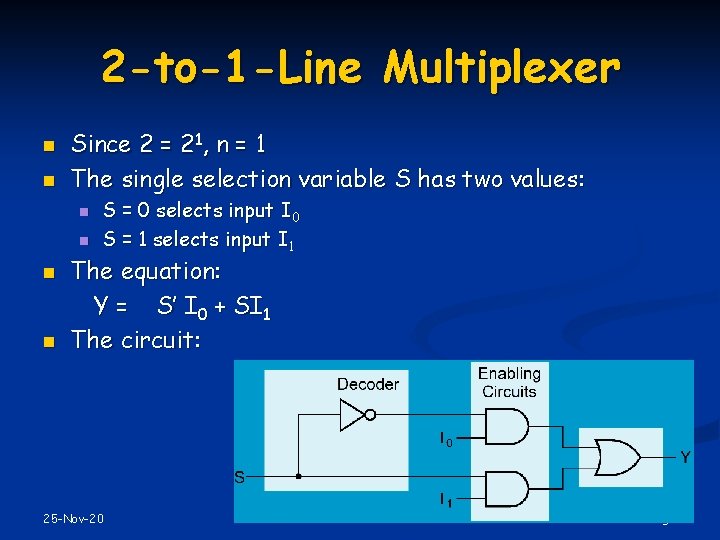

2 -to-1 -Line Multiplexer n n Since 2 = 21, n = 1 The single selection variable S has two values: n n S = 0 selects input I 0 S = 1 selects input I 1 The equation: Y = S’ I 0 + SI 1 The circuit: 25 -Nov-20 PJF - 5 Combinational Logic

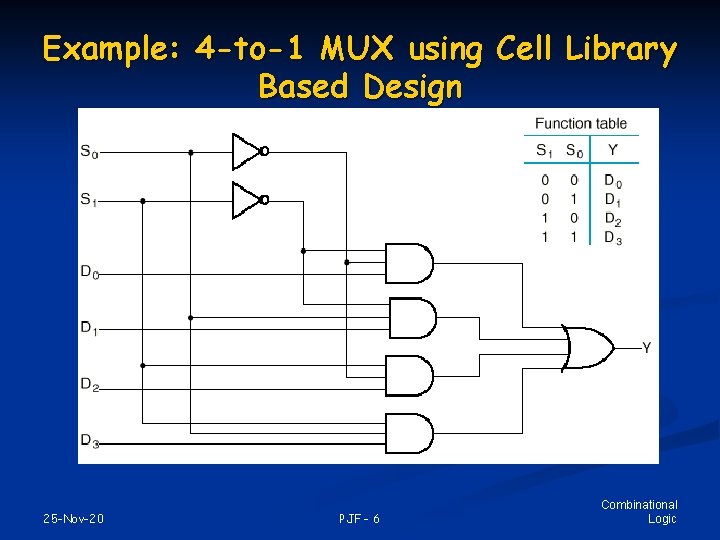

Example: 4 -to-1 MUX using Cell Library Based Design 25 -Nov-20 PJF - 6 Combinational Logic

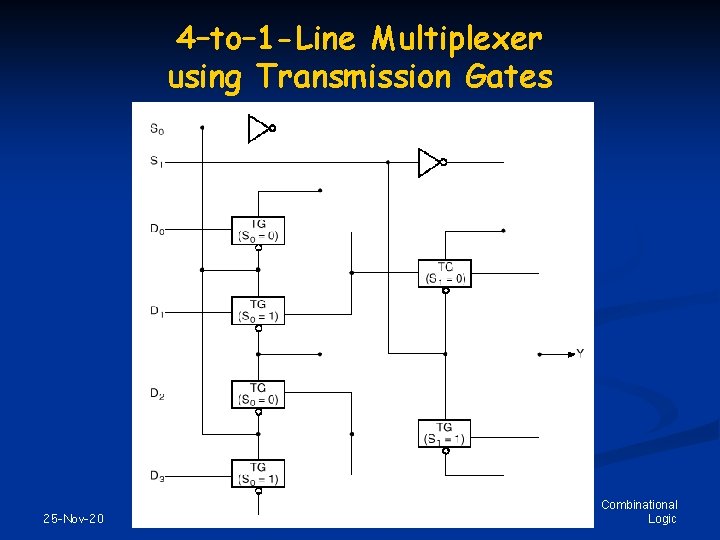

4–to– 1 -Line Multiplexer using Transmission Gates 25 -Nov-20 PJF - 7 Combinational Logic

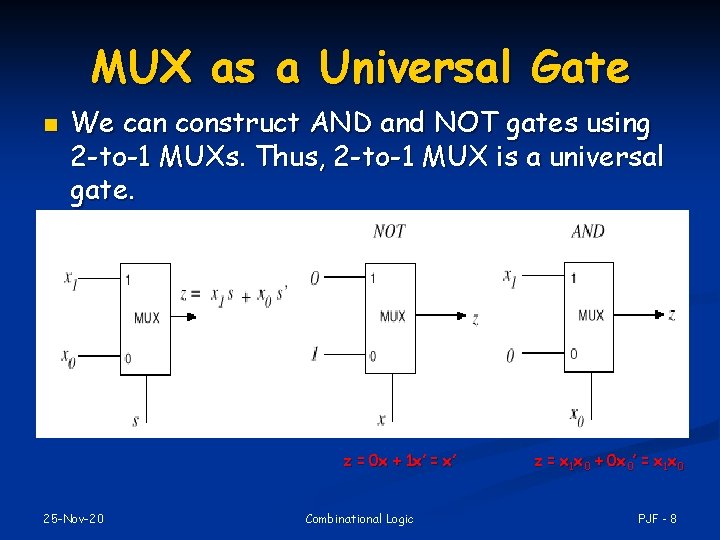

MUX as a Universal Gate n We can construct AND and NOT gates using 2 -to-1 MUXs. Thus, 2 -to-1 MUX is a universal gate. z = 0 x + 1 x’ = x’ 25 -Nov-20 Combinational Logic z = x 1 x 0 + 0 x 0’ = x 1 x 0 PJF - 8

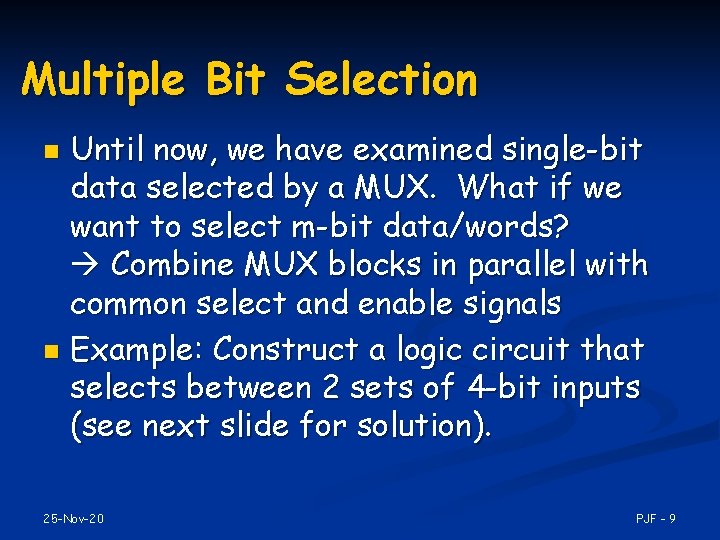

Multiple Bit Selection Until now, we have examined single-bit data selected by a MUX. What if we want to select m-bit data/words? Combine MUX blocks in parallel with common select and enable signals n Example: Construct a logic circuit that selects between 2 sets of 4 -bit inputs (see next slide for solution). n 25 -Nov-20 PJF - 9

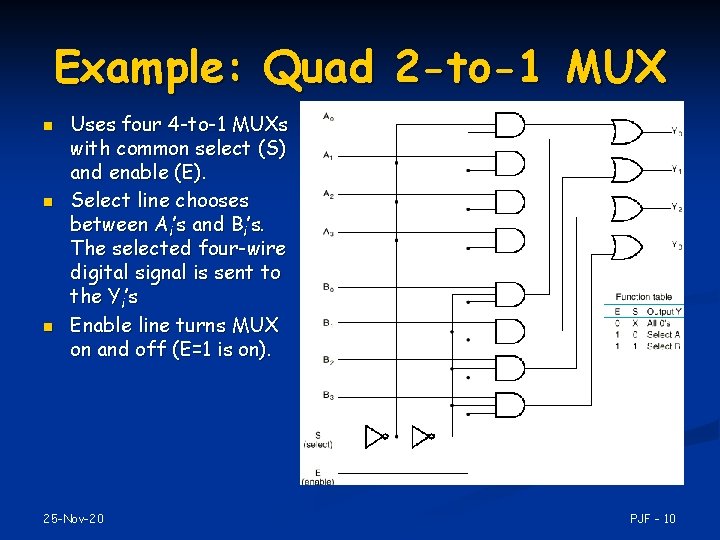

Example: Quad 2 -to-1 MUX n n n Uses four 4 -to-1 MUXs with common select (S) and enable (E). Select line chooses between Ai’s and Bi’s. The selected four-wire digital signal is sent to the Yi’s Enable line turns MUX on and off (E=1 is on). 25 -Nov-20 PJF - 10

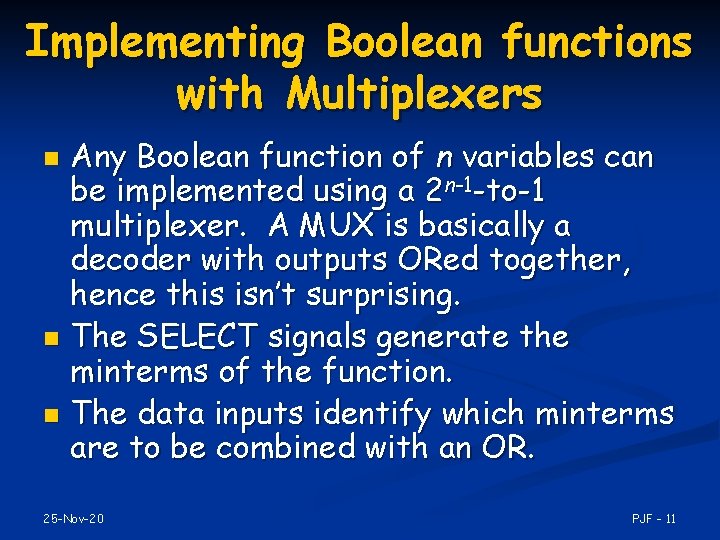

Implementing Boolean functions with Multiplexers Any Boolean function of n variables can be implemented using a 2 n-1 -to-1 multiplexer. A MUX is basically a decoder with outputs ORed together, hence this isn’t surprising. n The SELECT signals generate the minterms of the function. n The data inputs identify which minterms are to be combined with an OR. n 25 -Nov-20 PJF - 11

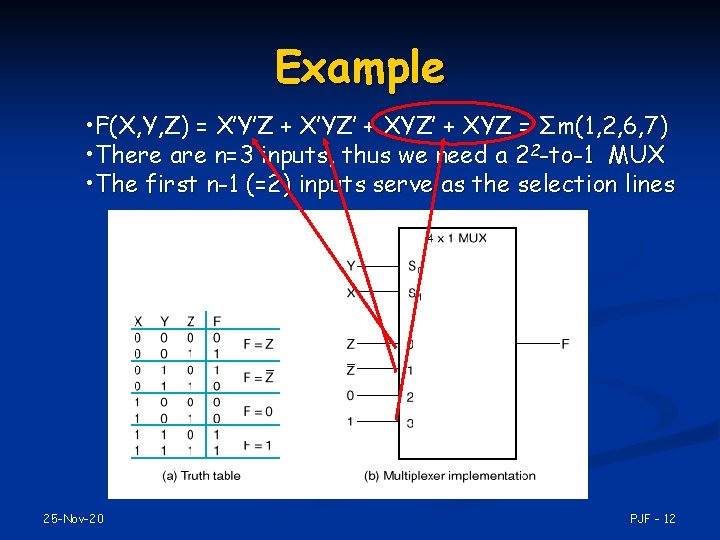

Example • F(X, Y, Z) = X’Y’Z + X’YZ’ + XYZ = Σm(1, 2, 6, 7) • There are n=3 inputs, thus we need a 22 -to-1 MUX • The first n-1 (=2) inputs serve as the selection lines 25 -Nov-20 PJF - 12

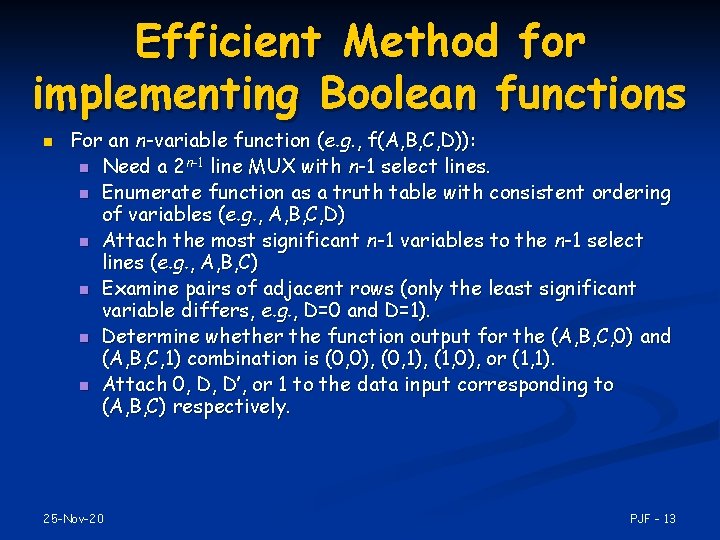

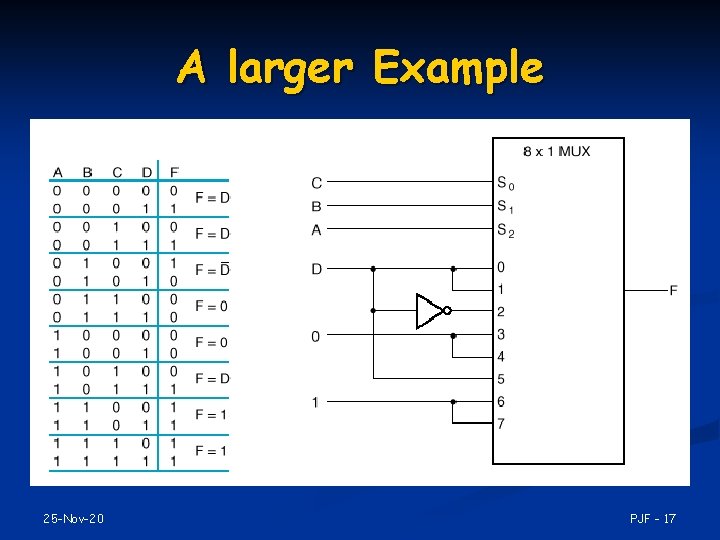

Efficient Method for implementing Boolean functions n For an n-variable function (e. g. , f(A, B, C, D)): n Need a 2 n-1 line MUX with n-1 select lines. n Enumerate function as a truth table with consistent ordering of variables (e. g. , A, B, C, D) n Attach the most significant n-1 variables to the n-1 select lines (e. g. , A, B, C) n Examine pairs of adjacent rows (only the least significant variable differs, e. g. , D=0 and D=1). n Determine whether the function output for the (A, B, C, 0) and (A, B, C, 1) combination is (0, 0), (0, 1), (1, 0), or (1, 1). n Attach 0, D, D’, or 1 to the data input corresponding to (A, B, C) respectively. 25 -Nov-20 PJF - 13

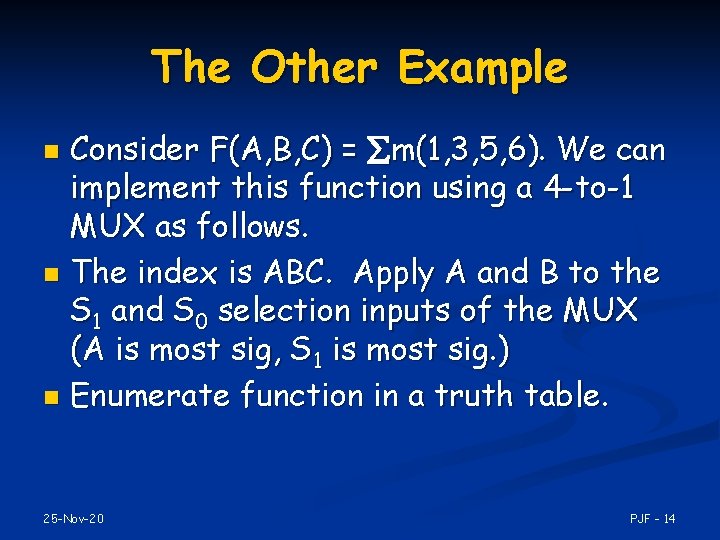

The Other Example Consider F(A, B, C) = m(1, 3, 5, 6). We can implement this function using a 4 -to-1 MUX as follows. n The index is ABC. Apply A and B to the S 1 and S 0 selection inputs of the MUX (A is most sig, S 1 is most sig. ) n Enumerate function in a truth table. n 25 -Nov-20 PJF - 14

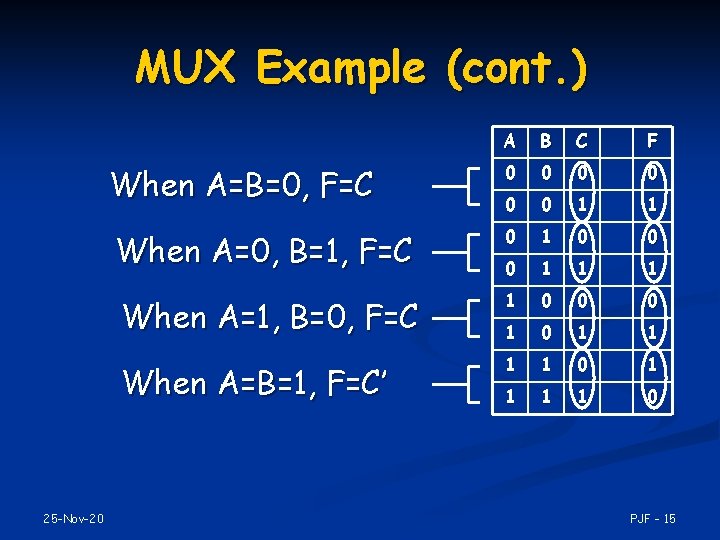

MUX Example (cont. ) A B C F 0 0 0 1 1 1 When A=1, B=0, F=C 1 0 0 0 1 1 When A=B=1, F=C’ 1 1 0 When A=B=0, F=C When A=0, B=1, F=C 25 -Nov-20 PJF - 15

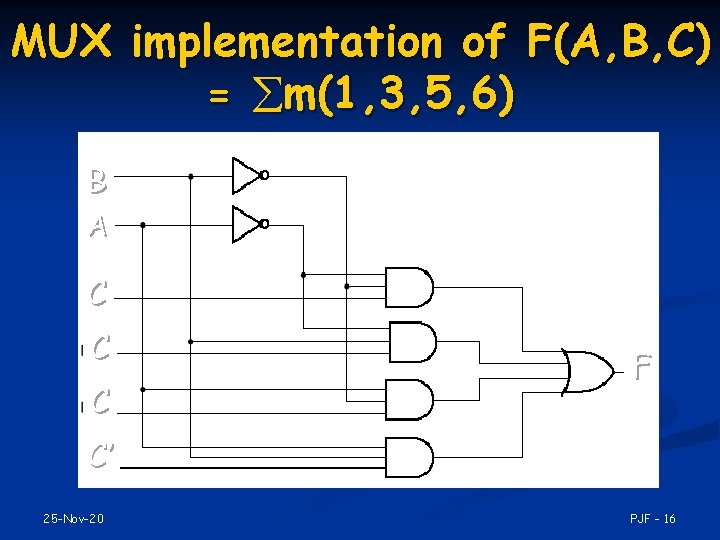

MUX implementation of F(A, B, C) = m(1, 3, 5, 6) B A C C C F C’ 25 -Nov-20 PJF - 16

A larger Example 25 -Nov-20 PJF - 17

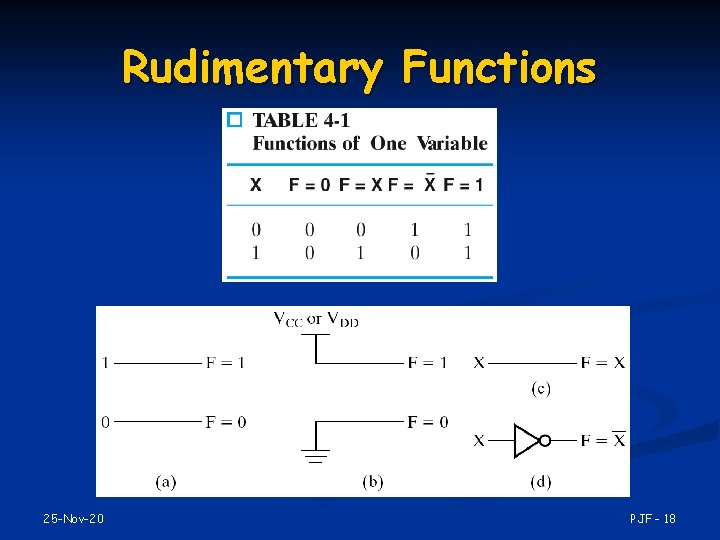

Rudimentary Functions 25 -Nov-20 PJF - 18

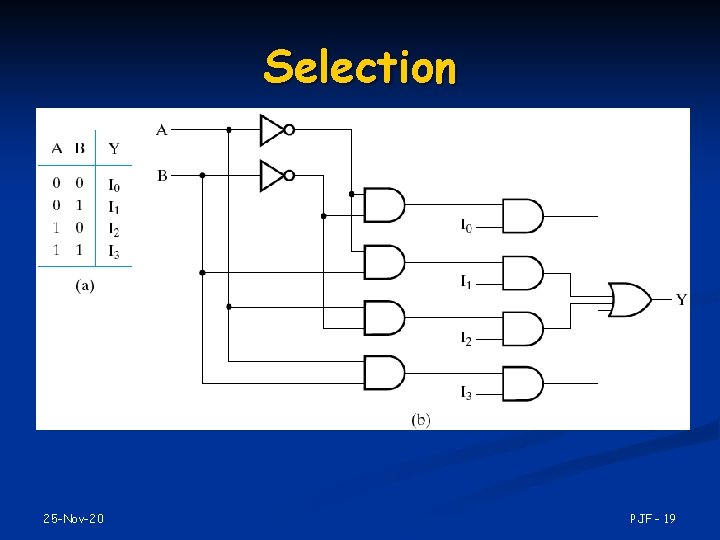

Selection 25 -Nov-20 PJF - 19

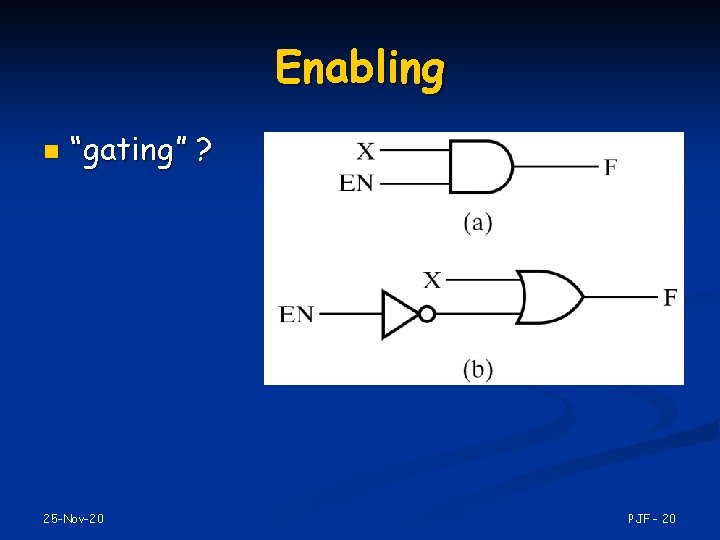

Enabling n “gating” ? 25 -Nov-20 PJF - 20

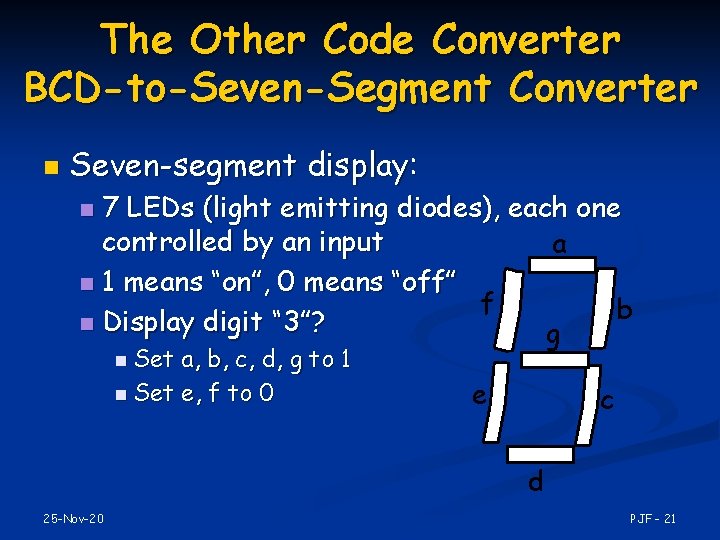

The Other Code Converter BCD-to-Seven-Segment Converter n Seven-segment display: 7 LEDs (light emitting diodes), each one controlled by an input a n 1 means “on”, 0 means “off” f b n Display digit “ 3”? g n n Set a, b, c, d, g to 1 n Set e, f to 0 e c d 25 -Nov-20 PJF - 21

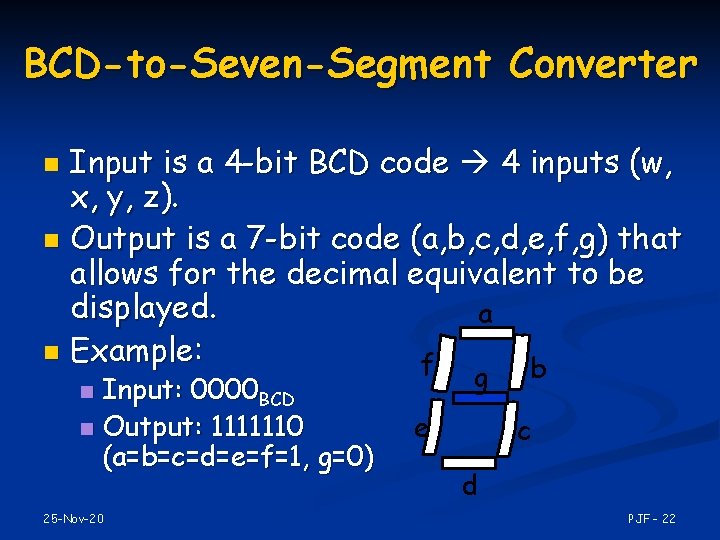

BCD-to-Seven-Segment Converter Input is a 4 -bit BCD code 4 inputs (w, x, y, z). n Output is a 7 -bit code (a, b, c, d, e, f, g) that allows for the decimal equivalent to be displayed. a n Example: f b n Input: 0000 BCD n Output: 1111110 (a=b=c=d=e=f=1, g=0) g n 25 -Nov-20 e c d PJF - 22

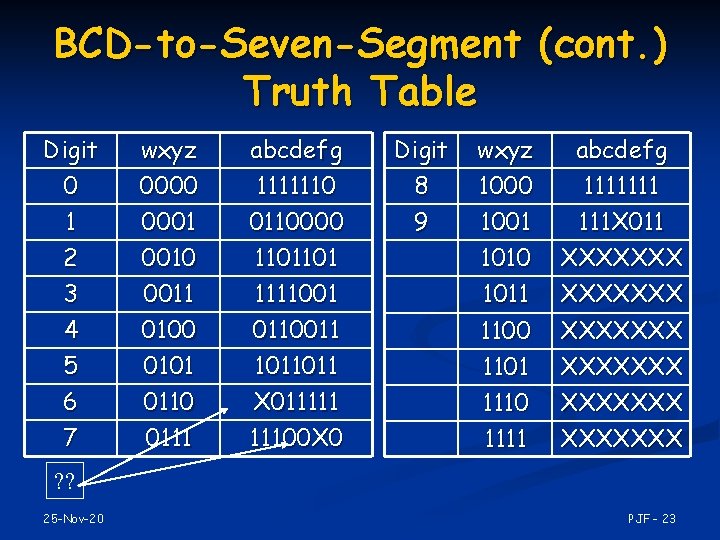

BCD-to-Seven-Segment (cont. ) Truth Table Digit 0 1 2 wxyz 0000 0001 0010 abcdefg 1111110 0110000 1101101 3 4 5 6 7 0011 0100 0101 0110 0111 1111001 0110011 1011011 X 011111 11100 X 0 Digit 8 9 wxyz 1000 1001 1010 abcdefg 1111111 111 X 011 XXXXXXX 1011 1100 1101 1110 1111 XXXXXXX XXXXXXX ? ? 25 -Nov-20 PJF - 23

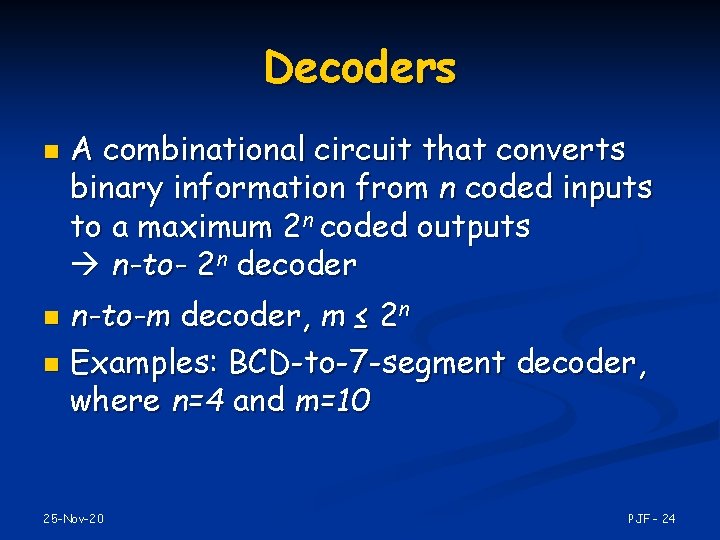

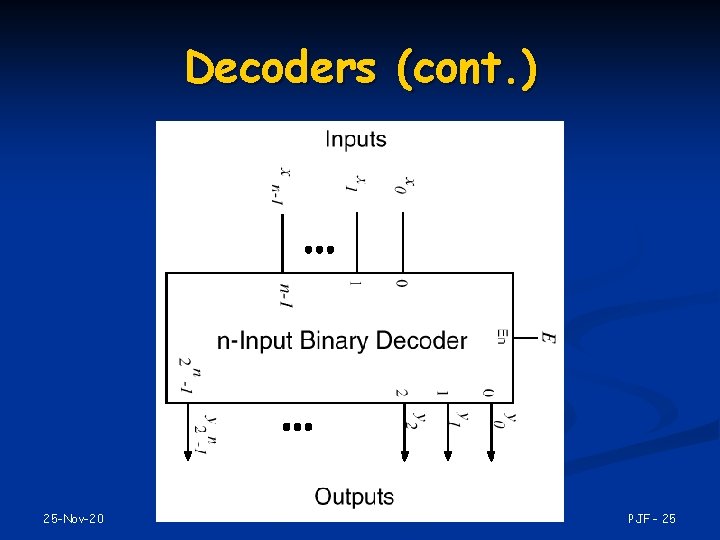

Decoders n A combinational circuit that converts binary information from n coded inputs to a maximum 2 n coded outputs n-to- 2 n decoder n-to-m decoder, m ≤ 2 n n Examples: BCD-to-7 -segment decoder, where n=4 and m=10 n 25 -Nov-20 PJF - 24

Decoders (cont. ) 25 -Nov-20 PJF - 25

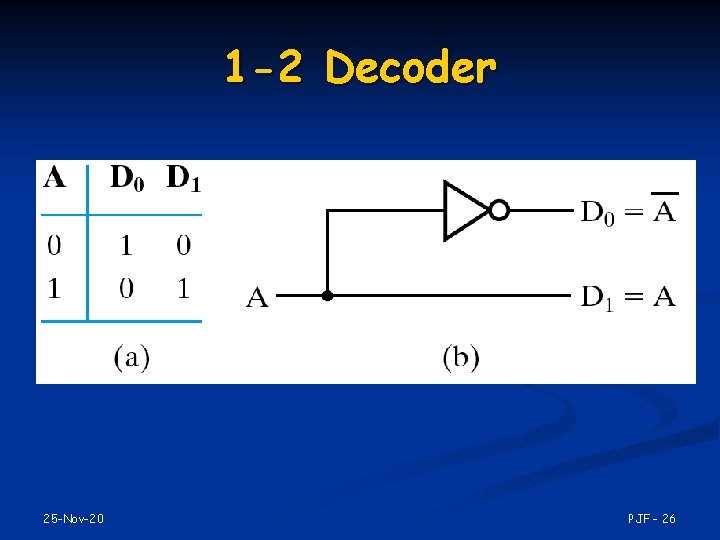

1 -2 Decoder 25 -Nov-20 PJF - 26

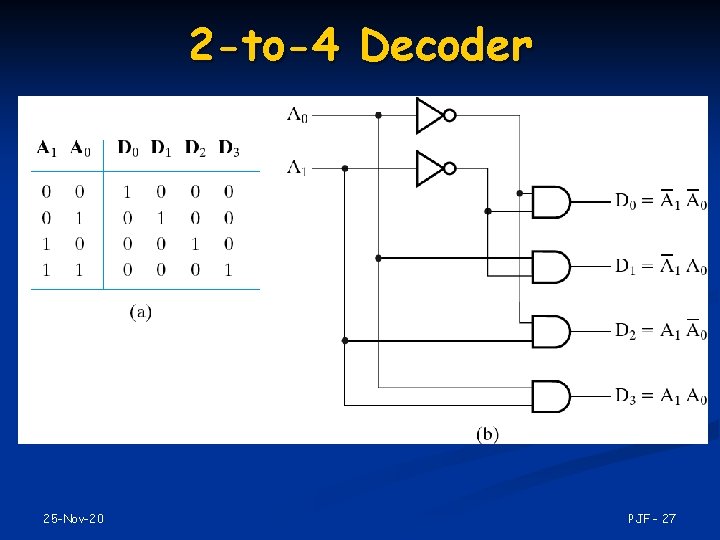

2 -to-4 Decoder 25 -Nov-20 PJF - 27

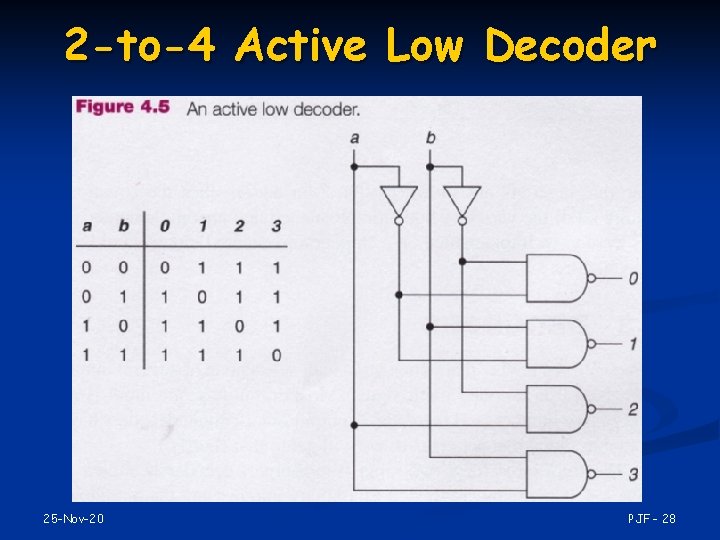

2 -to-4 Active Low Decoder 25 -Nov-20 PJF - 28

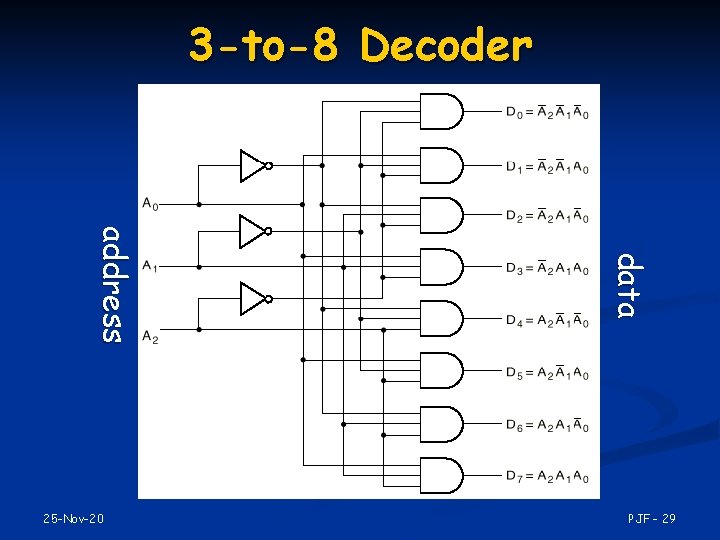

3 -to-8 Decoder d a ta a ddre s s 25 -Nov-20 PJF - 29

3 -to-8 Decoder (cont. ) n n n Three inputs, A 0, A 1, A 2, are decoded into eight outputs, D 0 through D 7 Each output Di represents one of the minterms of the 3 input variables. Di = 1 when the binary number A 2 A 1 A 0 = i Shorthand: Di = mi The output variables are mutually exclusive; exactly one output has the value 1 at any time, and the other seven are 0. 25 -Nov-20 PJF - 30

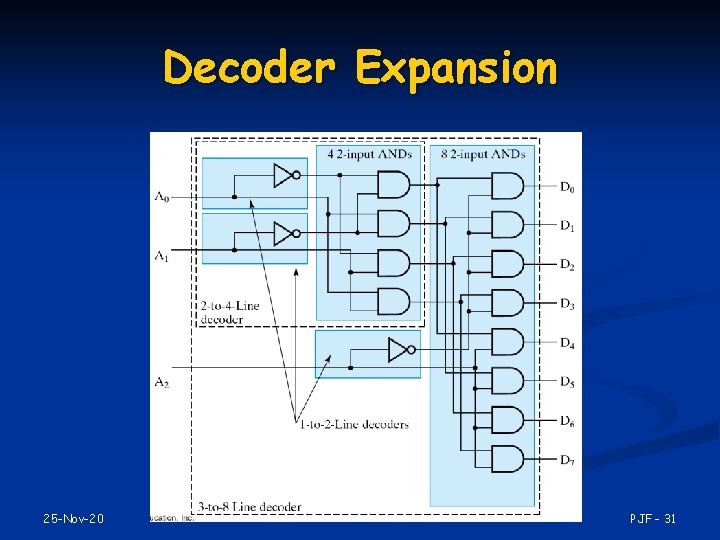

Decoder Expansion 25 -Nov-20 PJF - 31

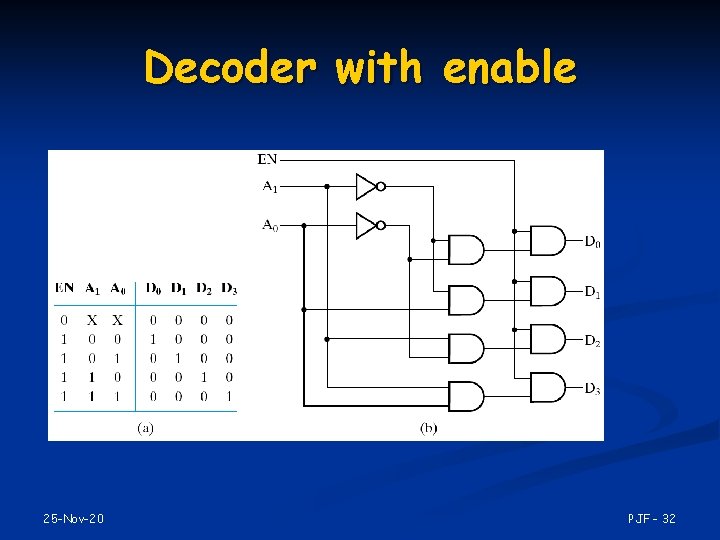

Decoder with enable 25 -Nov-20 PJF - 32

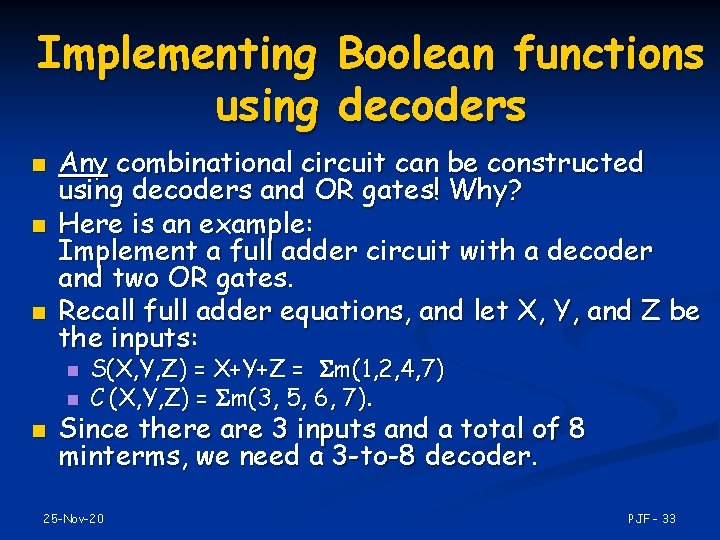

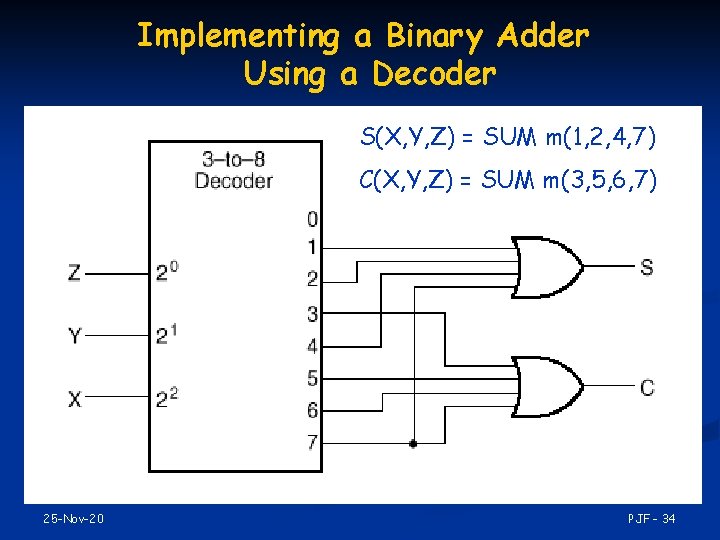

Implementing Boolean functions using decoders n n n Any combinational circuit can be constructed using decoders and OR gates! Why? Here is an example: Implement a full adder circuit with a decoder and two OR gates. Recall full adder equations, and let X, Y, and Z be the inputs: n n n S(X, Y, Z) = X+Y+Z = m(1, 2, 4, 7) C (X, Y, Z) = m(3, 5, 6, 7). Since there are 3 inputs and a total of 8 minterms, we need a 3 -to-8 decoder. 25 -Nov-20 PJF - 33

Implementing a Binary Adder Using a Decoder S(X, Y, Z) = SUM m(1, 2, 4, 7) C(X, Y, Z) = SUM m(3, 5, 6, 7) 25 -Nov-20 PJF - 34

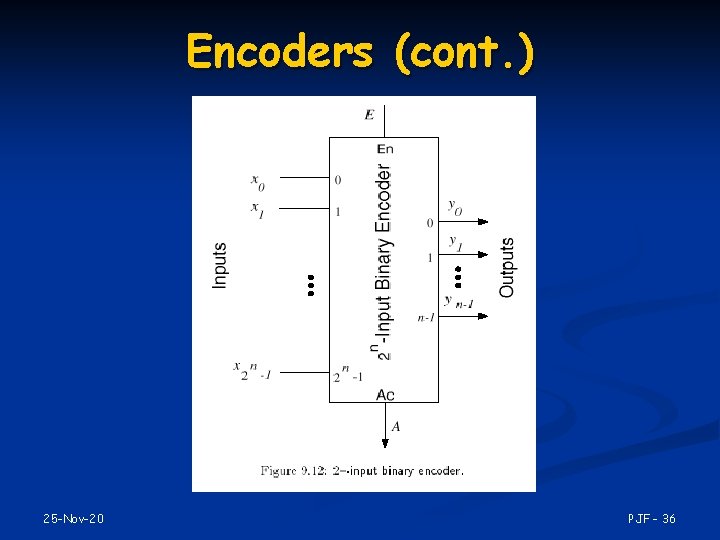

Encoders An encoder is a digital circuit that performs the inverse operation of a decoder. An encoder has 2 n input lines and n output lines. n The output lines generate the binary equivalent to the input line whose value is 1. n 25 -Nov-20 PJF - 35

Encoders (cont. ) 25 -Nov-20 PJF - 36

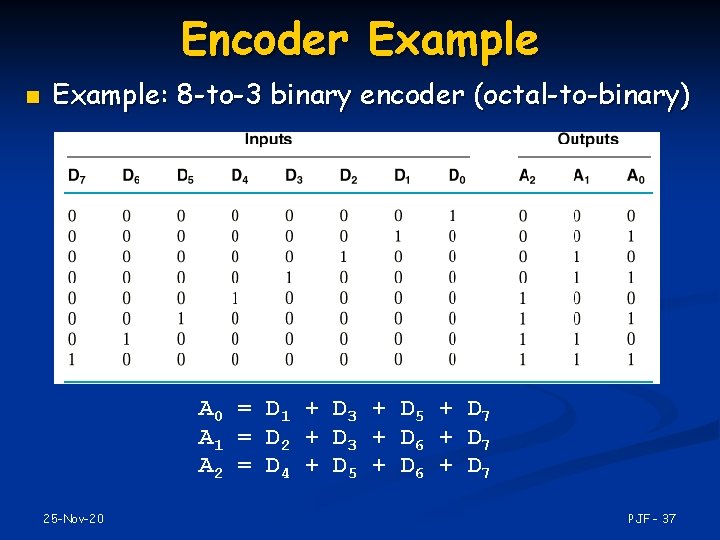

Encoder Example n Example: 8 -to-3 binary encoder (octal-to-binary) A 0 = D 1 + D 3 + D 5 + D 7 A 1 = D 2 + D 3 + D 6 + D 7 A 2 = D 4 + D 5 + D 6 + D 7 25 -Nov-20 PJF - 37

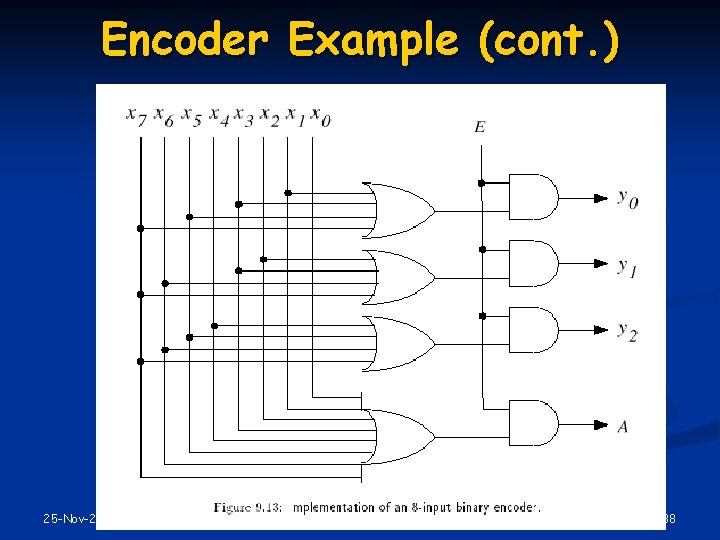

Encoder Example (cont. ) 25 -Nov-20 PJF - 38

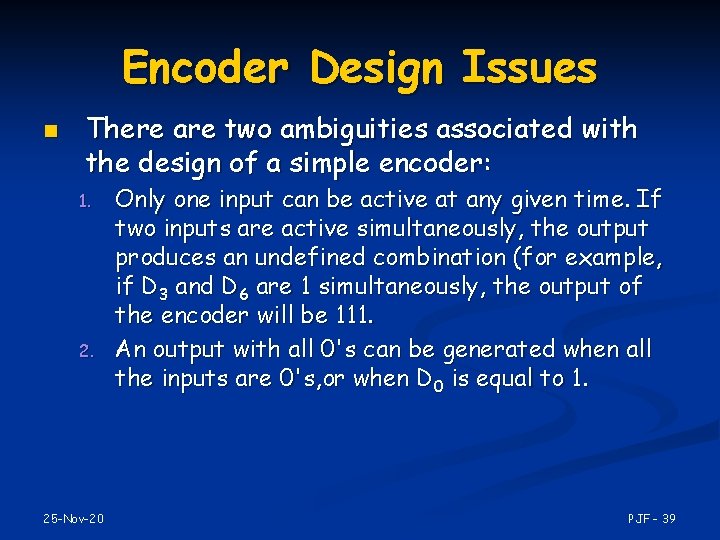

Encoder Design Issues n There are two ambiguities associated with the design of a simple encoder: 1. 25 -Nov-20 Only one input can be active at any given time. If two inputs are active simultaneously, the output produces an undefined combination (for example, if D 3 and D 6 are 1 simultaneously, the output of the encoder will be 111. An output with all 0's can be generated when all the inputs are 0's, or when D 0 is equal to 1. PJF - 39

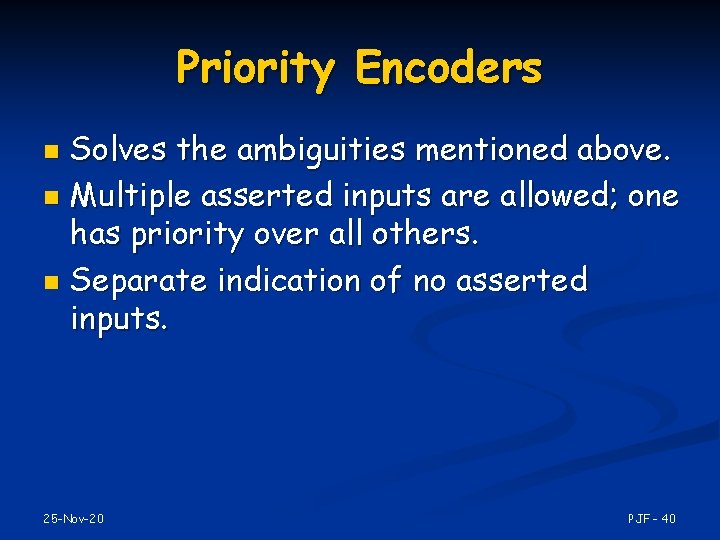

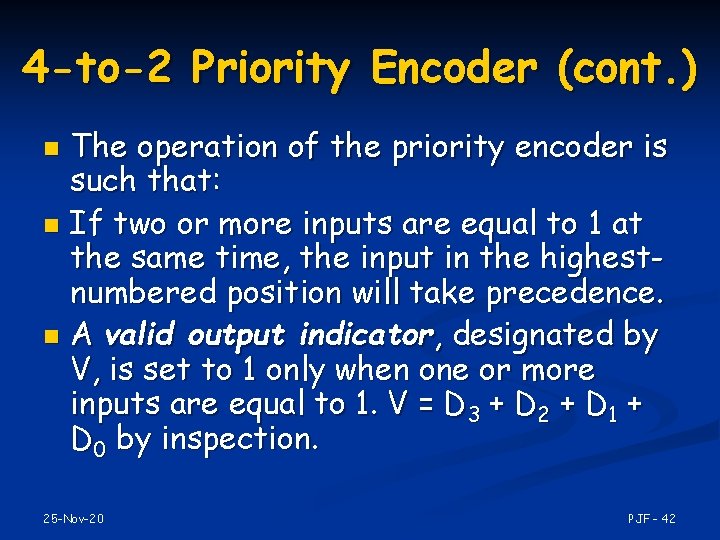

Priority Encoders Solves the ambiguities mentioned above. n Multiple asserted inputs are allowed; one has priority over all others. n Separate indication of no asserted inputs. n 25 -Nov-20 PJF - 40

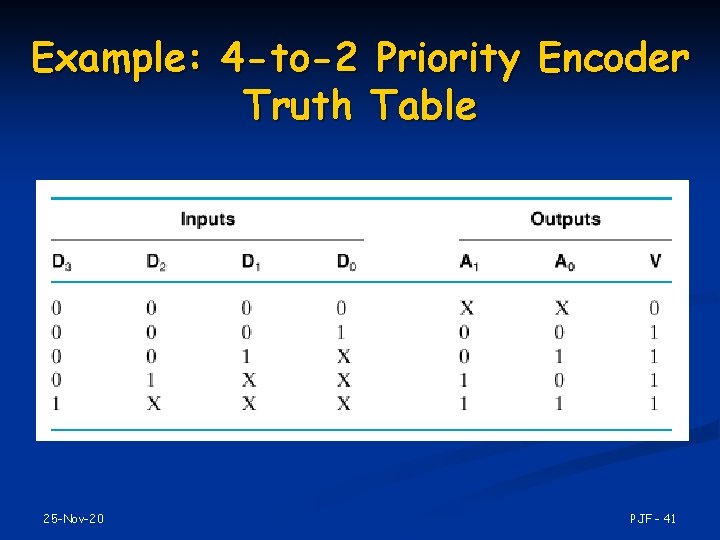

Example: 4 -to-2 Priority Encoder Truth Table 25 -Nov-20 PJF - 41

4 -to-2 Priority Encoder (cont. ) The operation of the priority encoder is such that: n If two or more inputs are equal to 1 at the same time, the input in the highestnumbered position will take precedence. n A valid output indicator, designated by V, is set to 1 only when one or more inputs are equal to 1. V = D 3 + D 2 + D 1 + D 0 by inspection. n 25 -Nov-20 PJF - 42

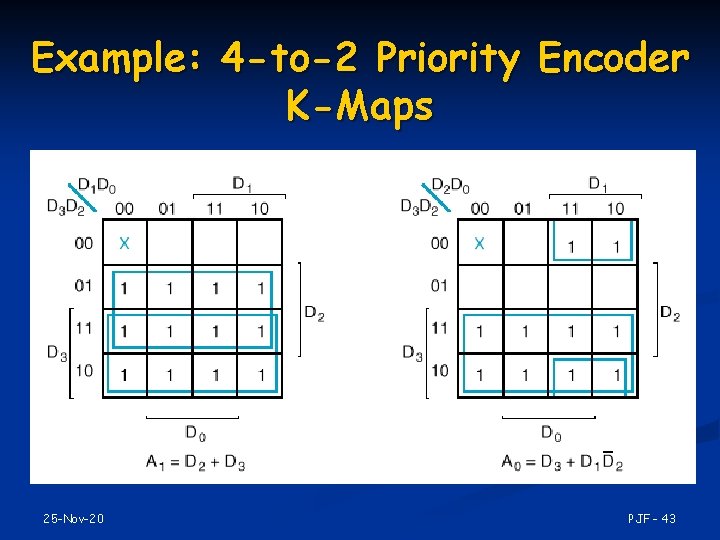

Example: 4 -to-2 Priority Encoder K-Maps 25 -Nov-20 PJF - 43

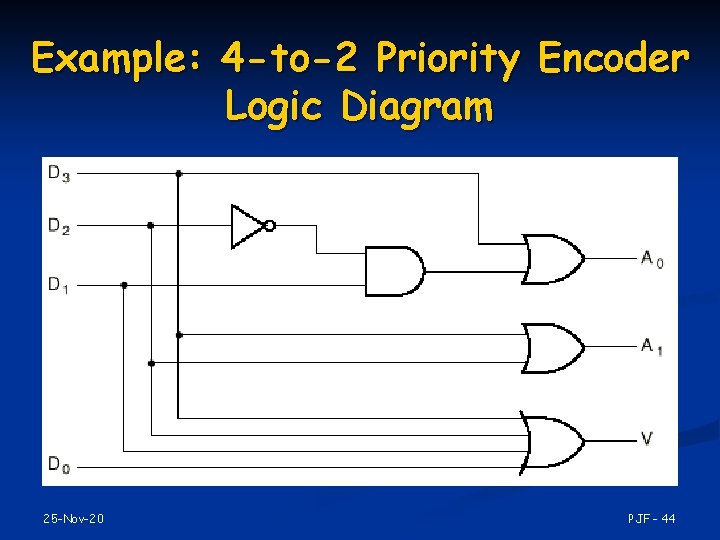

Example: 4 -to-2 Priority Encoder Logic Diagram 25 -Nov-20 PJF - 44

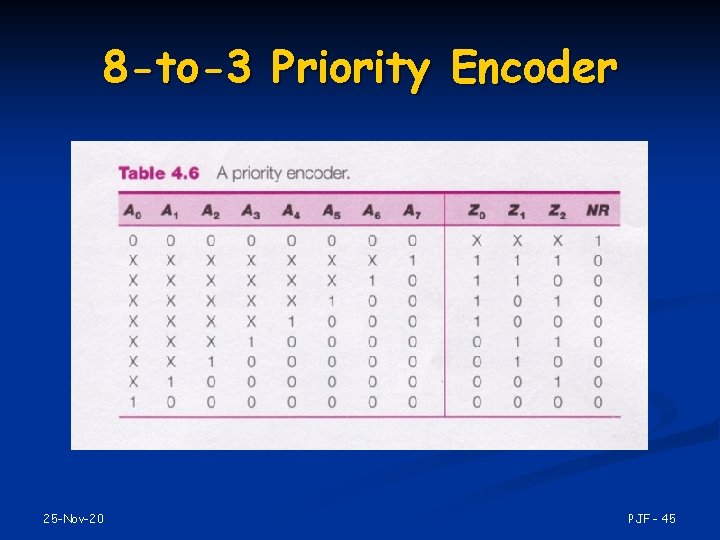

8 -to-3 Priority Encoder 25 -Nov-20 PJF - 45

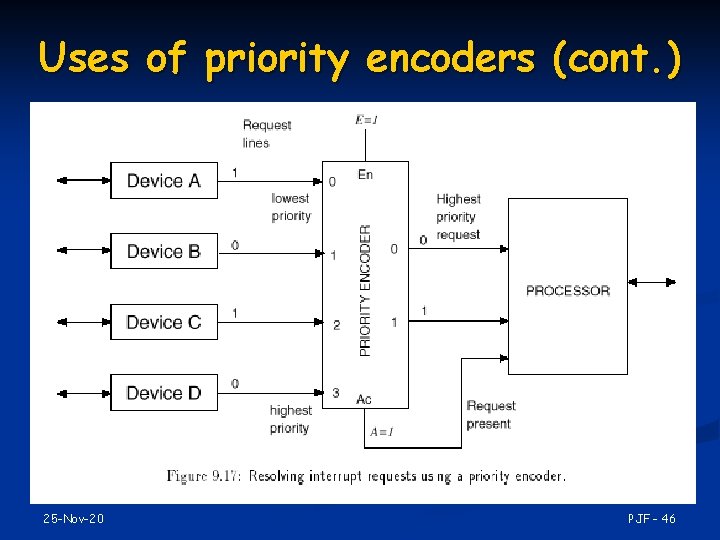

Uses of priority encoders (cont. ) 25 -Nov-20 PJF - 46

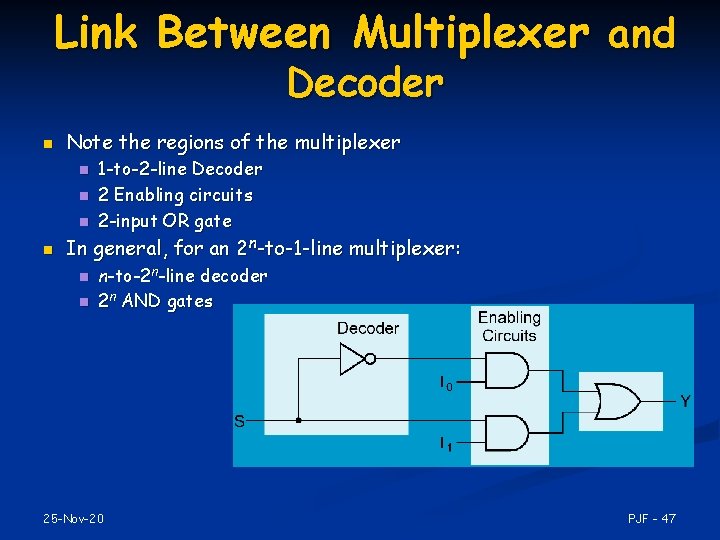

Link Between Multiplexer and Decoder n Note the regions of the multiplexer n n 1 -to-2 -line Decoder 2 Enabling circuits 2 -input OR gate In general, for an 2 n-to-1 -line multiplexer: n n n-to-2 n-line decoder 2 n AND gates 25 -Nov-20 PJF - 47

Summary of Encoder and Decoder n n n MUX Gate Rudimentary functions Binary Decoders n n 25 -Nov-20 Expansion Circuit implementation Binary Encoders Priority Encoders PJF - 48

- Slides: 48