ECE 5462 HDL Design and Verification Copyright 2012

- Slides: 24

ECE 5462 HDL Design and Verification Copyright 2012 Joanne De. Groat, ECE, OSU 1

Lecture Overview • Course Intro/ Syllabus/ Grading Policy • General Intro to Digital Design • Backgound Copyright 2012 Joanne De. Groat, ECE, OSU 2

Syllabus • The topics list is a guide. Not a class by class syllabus. • Note course objective. • Note grading policy. • There are many, many books on HDLs and a lot on VHDL. Most are not texts; these books are more for reference and often assume you know the language. • There also several books on verification. No verification text is required. Material will be provided. • Note general policies on syllabus. Copyright 2012 Joanne De. Groat, ECE, OSU 3

Intro • What is a digital system? – Digital (Webster) – System Copyright 2012 Joanne De. Groat, ECE, OSU 4

Intro • What is a digital system? • Digital (Webster) – Of or relating to the technology of computers and data communications wherein all information is encoded as bits of 1 s and 0 s that represent on or off states. Contrast with analog. Digital implies discrete states. • System – A composite of equipment, skills, techniques, and information capable of performing and/or supporting an operational role in attaining specified management objectives. A complete system includes related facilities, equipment, material, services, personnel, and information required for its operation to the degree that it can be considered a self-sufficient unit in its intended operational and/or support environment. Copyright 2012 Joanne De. Groat, ECE, OSU 5

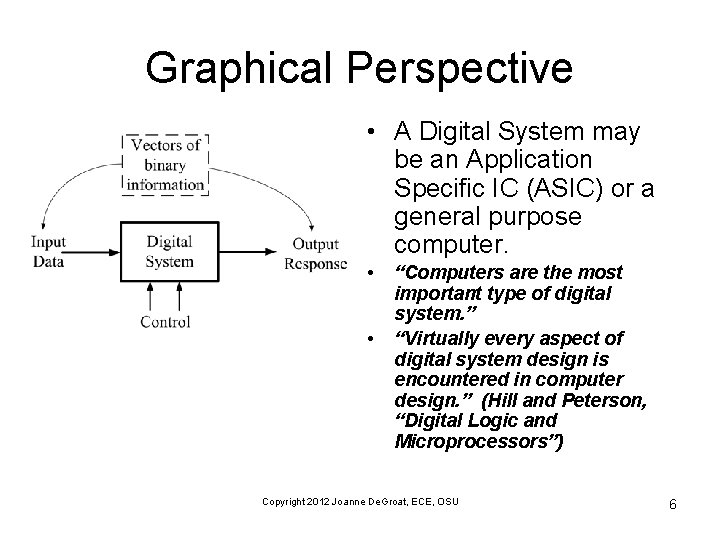

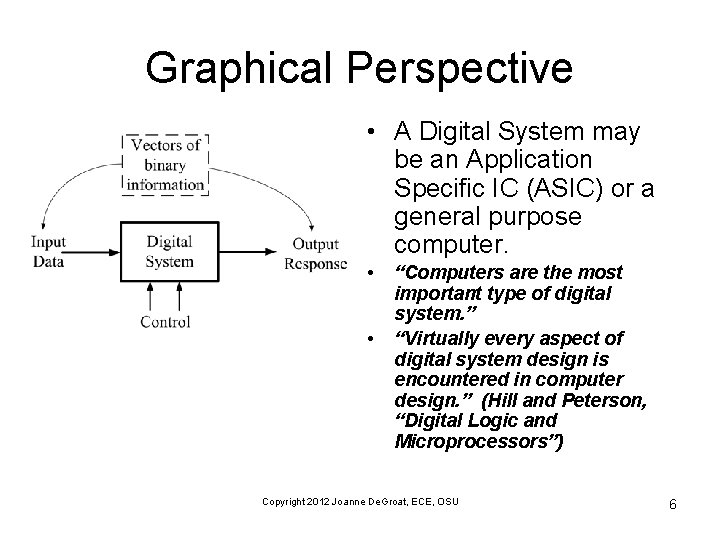

Graphical Perspective • A Digital System may be an Application Specific IC (ASIC) or a general purpose computer. • • “Computers are the most important type of digital system. ” “Virtually every aspect of digital system design is encountered in computer design. ” (Hill and Peterson, “Digital Logic and Microprocessors”) Copyright 2012 Joanne De. Groat, ECE, OSU 6

Digital System Design Process • “Design is a series of transformations. ” At each step decisions are made that bind the design, moving it toward an implementation. Design begins at a high level of abstraction and moves to a very detailed level of abstraction. (De. Groat 2005) Copyright 2012 Joanne De. Groat, ECE, OSU 7

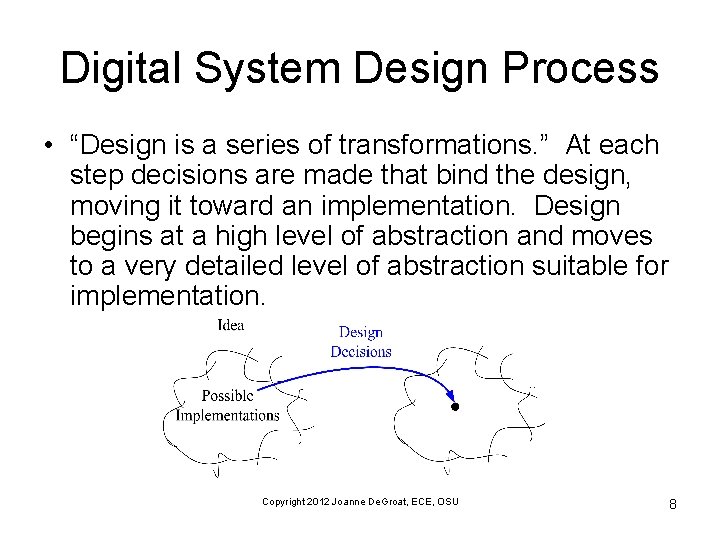

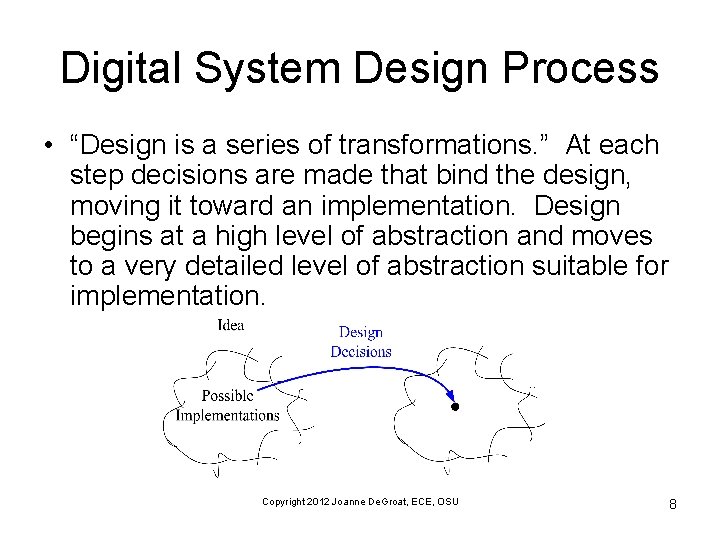

Digital System Design Process • “Design is a series of transformations. ” At each step decisions are made that bind the design, moving it toward an implementation. Design begins at a high level of abstraction and moves to a very detailed level of abstraction suitable for implementation. Copyright 2012 Joanne De. Groat, ECE, OSU 8

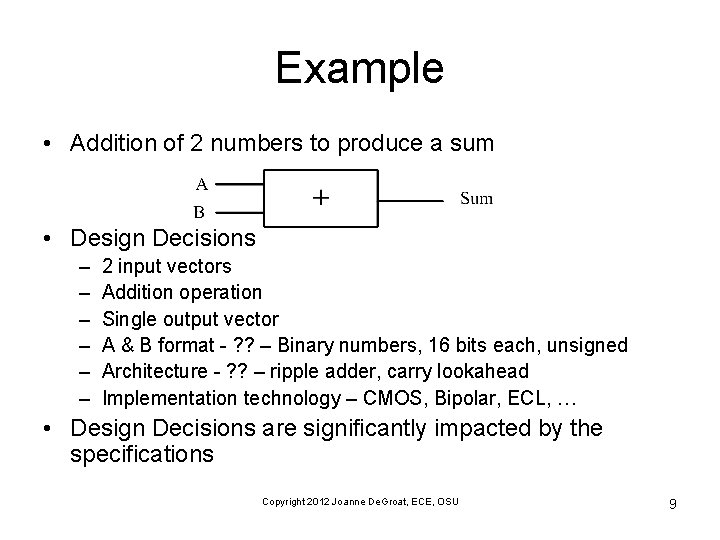

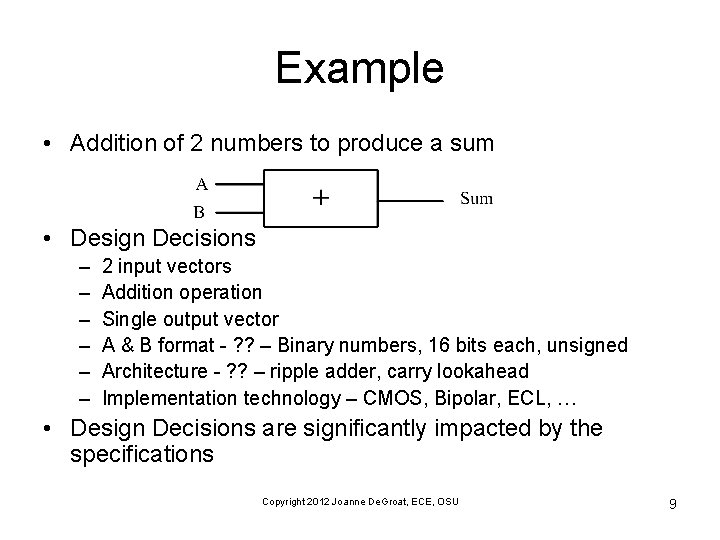

Example • Addition of 2 numbers to produce a sum • Design Decisions – – – 2 input vectors Addition operation Single output vector A & B format - ? ? – Binary numbers, 16 bits each, unsigned Architecture - ? ? – ripple adder, carry lookahead Implementation technology – CMOS, Bipolar, ECL, … • Design Decisions are significantly impacted by the specifications Copyright 2012 Joanne De. Groat, ECE, OSU 9

HDL Design Process • Start with design idea • Do a behavioral design for reference • RTL level design – Design data path – Design control path • Use a synthesis tool to produce a gate netlist • Physical Design – place gates and wire so IC can be fabricated • Production Copyright 2012 Joanne De. Groat, ECE, OSU 10

An example • From ASi. C Technology & News – “Why ASICs fail in the system. ” – Listen to story about a design that …. • Key points from story. – “Designers knew design was right” – “found a functional error” – Re-fab and still Chips exploded. – Months passed slowly. Copyright 2012 Joanne De. Groat, ECE, OSU 11

Story line • A narration by the CEO – Design was completed – HDL written, chip design generated, design sent to fab – First chip came back and sent to test. – When tested – the chip package blew the top off. – Why, oh, why? – Design was checked for power-ground short – nope. – More and more checks done. Nothing significant found. – Did find a few errors and re-fabbed the chip. – Chips still exploded!!!! – Another investigation. – Now the time passed very, very slowly. – Finally found out that extra metal was added by foundry to enable even metal deposition. Added metal was not grounded!!! Copyright 2012 Joanne De. Groat, ECE, OSU 12

HDL motivations • HDL used to describe hardware for purpose of: – – – Simulation Documentation Modeling Testing Design Ensuring design satisfies specifications (new) • HDLs provide a convenient and compact format for the hierarchical representation of function and wiring details of digital systems. Copyright 2012 Joanne De. Groat, ECE, OSU 13

PAST HDLs • ISPS – Instruction Set Processor Specification – Language for describing the behavior of digital systems – Developed at CMU – Based on ISP notation Copyright 2012 Joanne De. Groat, ECE, OSU 14

PAST HDLs • AHPL – A Hardware Programming Language – Designed for representation in an academic environment – Developed at the University of Arizona. Copyright 2012 Joanne De. Groat, ECE, OSU 15

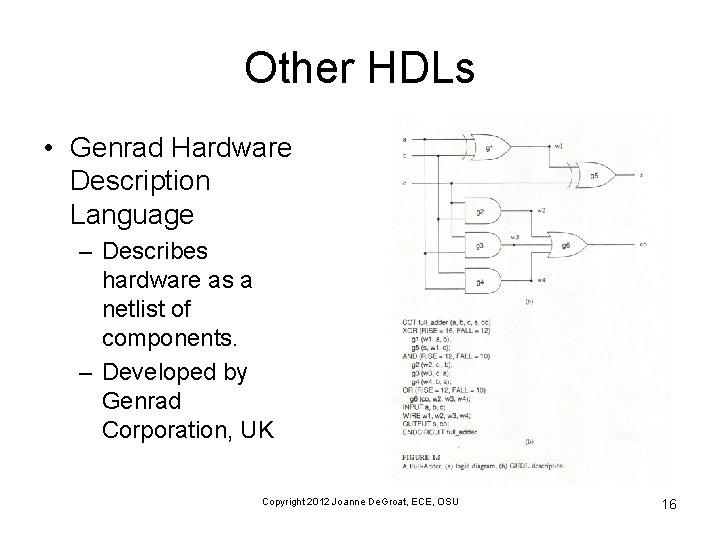

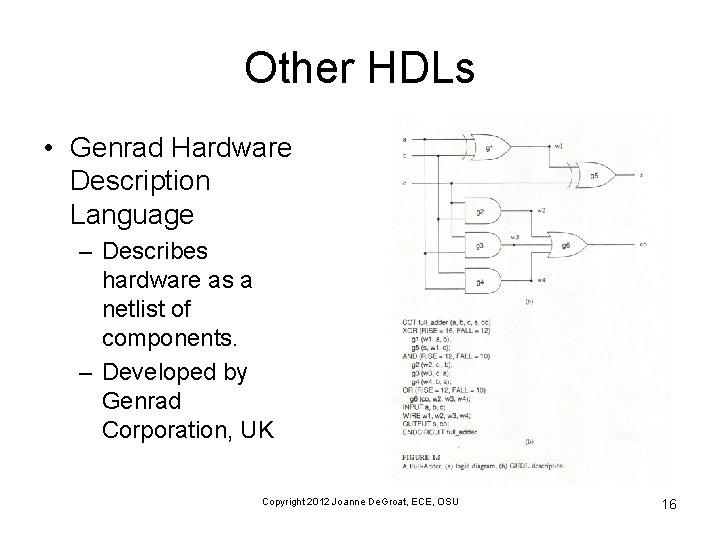

Other HDLs • Genrad Hardware Description Language – Describes hardware as a netlist of components. – Developed by Genrad Corporation, UK Copyright 2012 Joanne De. Groat, ECE, OSU 16

Other HDLs • CDL – Computer Design Language – A dataflow language – no hierarchy • CONLAN – Consensus Language – Attempt to establish a standard language. Family of languages for describing hardware at various levels of abstraction. • IDL – Interactive Design Language – Internal IBM – Supports Hierarchy – Originally designed for generation of PLAs, then extended • TEGAS – Texas Instruments Hardware Description Language – Internal TI – Multilevel language for design and description – hierarchical Copyright 2012 Joanne De. Groat, ECE, OSU 17

Other HDLs (cont) • ZEUS – GE language – hierarchical – functional descriptions – structural descriptions – No provision for gate delay specification or timing constraints – Does not support asynchronous designs. • Verilog – Hierarchical – Developed by Cadence Design Systems – Procedural descriptions for behavior – Built in features for timing and a fixed logic value system. Now also a standard. Used by ~60% of market. • UDL 1 – Standard language that was developed in Japan – hierarchical – 1 to 1 mapping of language constructs to hardware structures – Designed for synthesis • System C – NEWEST – now also a standard and supported by tools – has penetrated to about 10% to 15 % of the market. Copyright 2012 Joanne De. Groat, ECE, OSU 18

VHDL • • • VHDL – VHSIC Hardware Description Language A standard language – the first. Development began in 1980. Language Requirements set in 1981. 1 st Version – Version 7. 2 with prototype simulation tools – 1985 -1987 • 1 st Standard – IEEE Standard 1076 -1987 approved in 1987. • New version in 1993. Also versions in 1997, 2000, 2002, and a new version was approved in September 2008. Work on a new version is progressing – language will have some new features. Copyright 2012 Joanne De. Groat, ECE, OSU 19

VHDL features • Procedural Features – Would make a very good concurrent programming language. Up until now file I/O support was poor. • Dataflow design • Structural – Hierarchy • Self defined Value System and capability to design your own if you would need to. – A valuable feature of the language – Some recent work created to ability to do fault simulation in VHDL through creation of a custom value system package. • Semantics and Paradigm formally defined in LRM Copyright 2012 Joanne De. Groat, ECE, OSU 20

In Summary • There is no way we would have systems of today’s complexity without the development and evolution of HDLs. • Has allowed for design methodology change and refinement as new capabilities such a synthesis became available. • HDLs are living languages. – Evolution shown in 2008 standard – 140% increase. • Today’s systems are just too complex to stay with the design methodologies of the 1980 s and even to early 1990 s. – Consider the time to design a modern processor! Copyright 2012 Joanne De. Groat, ECE, OSU 21

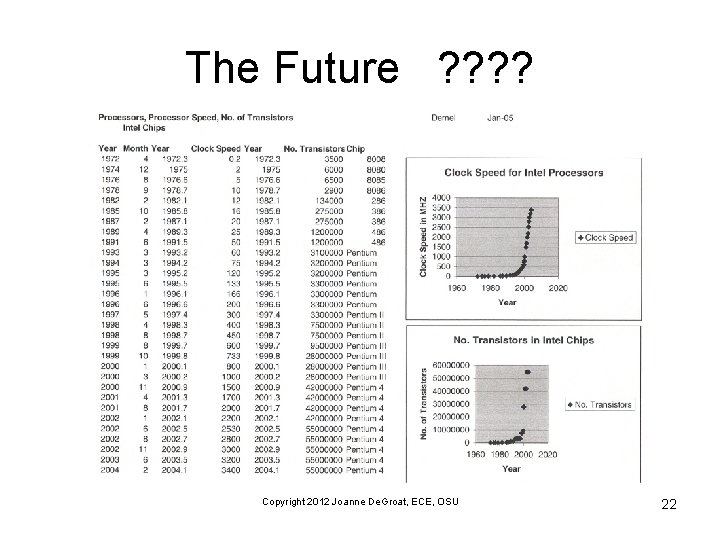

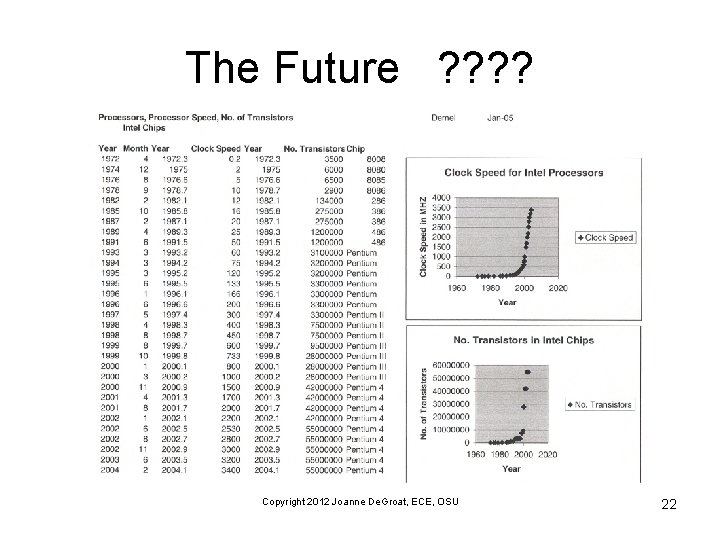

The Future ? ? Copyright 2012 Joanne De. Groat, ECE, OSU 22

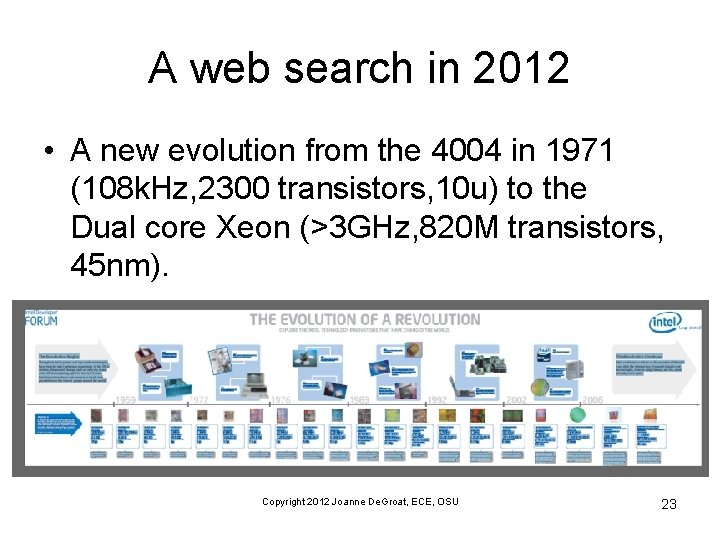

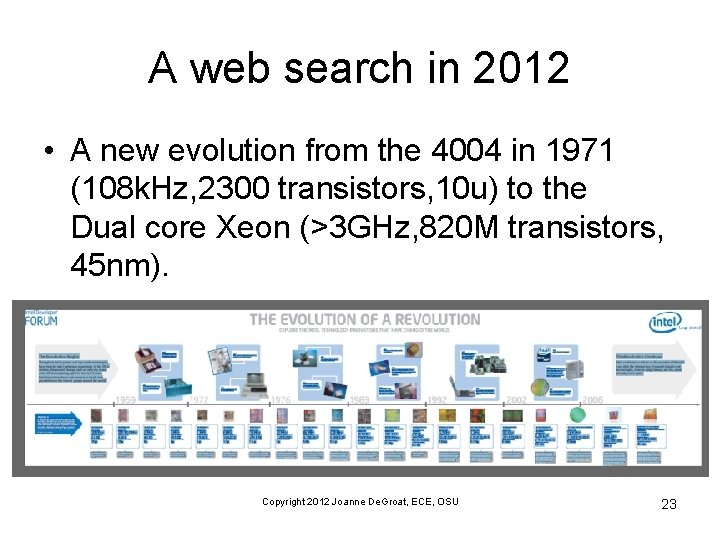

A web search in 2012 • A new evolution from the 4004 in 1971 (108 k. Hz, 2300 transistors, 10 u) to the Dual core Xeon (>3 GHz, 820 M transistors, 45 nm). Copyright 2012 Joanne De. Groat, ECE, OSU 23

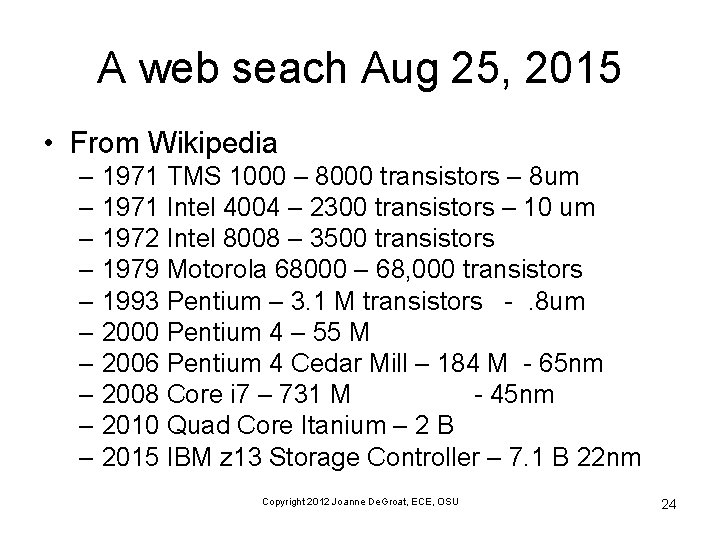

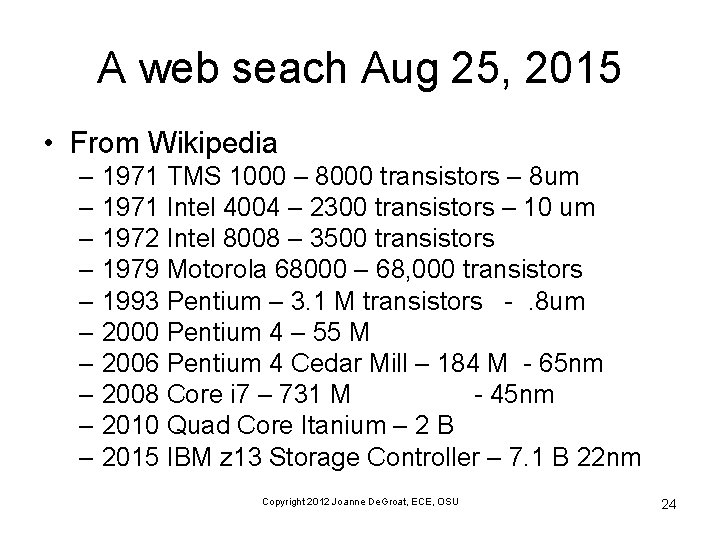

A web seach Aug 25, 2015 • From Wikipedia – 1971 TMS 1000 – 8000 transistors – 8 um – 1971 Intel 4004 – 2300 transistors – 10 um – 1972 Intel 8008 – 3500 transistors – 1979 Motorola 68000 – 68, 000 transistors – 1993 Pentium – 3. 1 M transistors -. 8 um – 2000 Pentium 4 – 55 M – 2006 Pentium 4 Cedar Mill – 184 M - 65 nm – 2008 Core i 7 – 731 M - 45 nm – 2010 Quad Core Itanium – 2 B – 2015 IBM z 13 Storage Controller – 7. 1 B 22 nm Copyright 2012 Joanne De. Groat, ECE, OSU 24