Verification Plan Levels of Verification The Verification Plan

- Slides: 17

Verification Plan & Levels of Verification • • • The Verification Plan Yesterdays and today’s design environment Design specification document Verification success Levels of verification EE 694 v-Verification-Lect 7 -1 -

The Verification Plan • Just as a design meets a specification, the verification plan is the specification for the verification effort. • Defines – – – What is success How a design is to be verified Functional correctness Which programs and testbenches to write Schedule for verification effort EE 694 v-Verification-Lect 7 -2 -

In The Past • Verification was left to each designer to do as they wished • Verification was done as time allowed • Emphasis was “does chip work? ” • Have progressed from “does chip work? ” to – Does chip work in the system? – Does chip work in the system as specified? – Does the system work as specified? EE 694 v-Verification-Lect 7 -3 -

Today’s Environment • Wish to have system integration go smoothly • Simulate chip(s) in system environment to identify problems early, preferably during design and prior to fabrication • Tools that, if effectively used, can help – Simulation – Linting – Other tools EE 694 v-Verification-Lect 7 -4 -

Specifying the Verification • When will verification of design be completed to the required degree of confidence • Must determine – How much work verification will require – How many people are needed for the verification effort – How long will the verification effort take EE 694 v-Verification-Lect 7 -5 -

Design Specification Document • Verification effort relies on a complete specification document • Must be a written document • Is the common source for both the design’s implementation and its verification • When design’s output is not as expected this document helps determine whether the design is correct (verification in error) or not (verification correct) EE 694 v-Verification-Lect 7 -6 -

The Plan & 1 st Time Success • The verification plan defines what success is • Insures all essential features of design are appropriately verified • Documents which features are essential and which are optional • Not all features of the final design need be included in defining 1 st time success • Final success requires that all features in the final design are working and verified so. EE 694 v-Verification-Lect 7 -7 -

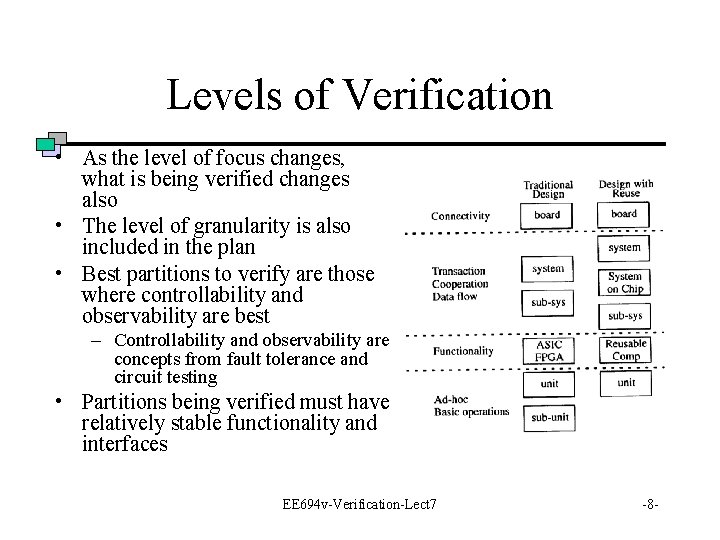

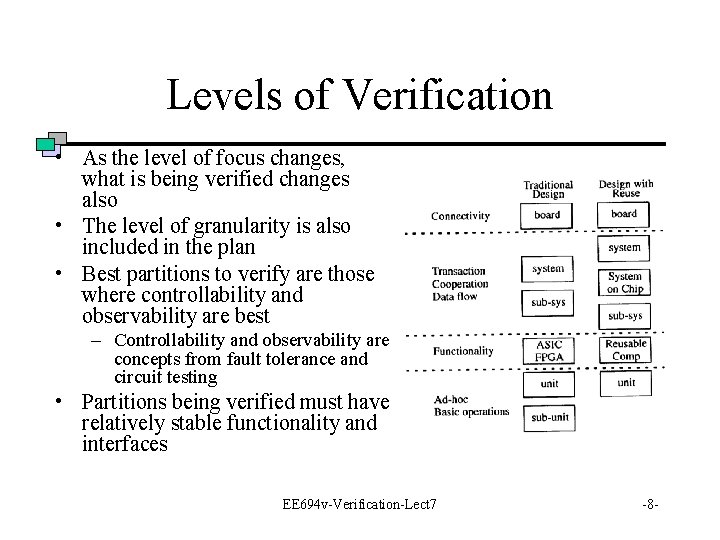

Levels of Verification • As the level of focus changes, what is being verified changes also • The level of granularity is also included in the plan • Best partitions to verify are those where controllability and observability are best – Controllability and observability are concepts from fault tolerance and circuit testing • Partitions being verified must have relatively stable functionality and interfaces EE 694 v-Verification-Lect 7 -8 -

Unit-Level Verification • Design units are logical partitions and vary from small to large, simple to complex – Small/Simple - FIFO, small state machine – Large/Complex - PCI slave interface, DSP datapath • Often have interfaces that are not fixed and firm – The interface many be configurable for the application • Often functionality is not yet fixed and firm • Any reasonable size project will have a large number of design units • Verification of the entire design at this level would probably be too time consuming EE 694 v-Verification-Lect 7 -9 -

Reusable Component Verification • Component is designed to its own specification • Component intended to be used as-is in many different designs • Typically the component implements a common function or allows connection to a standardized interface • Component is used in many designs - focus is on its functionality • Potential users must have confidence that design is indeed correct EE 694 v-Verification-Lect 7 -10 -

ASIC & FPGA Verification • These units form a physical and possibly a logical partition • Often have their own specification • Often contain a collection of independently designed and verified components • Todays ASICs and FPGAs are too complex to verify and debug during integration. Need verification for them prior to synthesis or downloading the programming. EE 694 v-Verification-Lect 7 -11 -

System-Level Verification • There are many definitions for a system!!! • In the book - “a system is a logical partition composed of independently verified components. ” • System could be – composed of a few reusable components – a subset of an So. C ASIC – ASICs (or part of ASICs) on different boards • Focuses on interaction between components • Relies on individual components being functionally correct EE 694 v-Verification-Lect 7 -12 -

Board-Level Verification • Confirm that component connectivity is correct • Some components on boards, such as capacitors, do not translate easily to digital domain • Depending on the complexity level, could be used to verify functionality (as with any other level) • Must make sure what is verified is what is manufactured (as with all levels) EE 694 v-Verification-Lect 7 -13 -

Development of a Verification Plan • Factors that are important – Level of verification – Level of complexity of the unit/system – Type of unit/system – Level of confidence needed • Must analyze the operational space in analyzing the level of confidence that can be placed in the verification effort. EE 694 v-Verification-Lect 7 -14 -

Plan Content • What goes into verification plan? – Description of what is to be verified – Analysis of tests to be applied • Divided up into sets to test the various aspects of the test domain space • An analysis of the complete test space and how the various aspects interface • For example – two normalized numbers can produce overflow to infinity, zero, a denormalized number even though in most cases it results in a normalized result. EE 694 v-Verification-Lect 7 -15 -

Plan Content – How are the tests to be generated • Test sets and the program(s) to generate them are specified. • Test to adequately tests for the regions identified • Most likely also generate the expected result so that self checking can be done. – The Testbench(s) that will be used to apply the tests and check the results. (self checking) • How will it be constructed. Will the tests be integral to the testbench or read from a file. EE 694 v-Verification-Lect 7 -16 -

The Plan (cont) • Essential elements of the plan – Definition of Verification Success • How do you know you are done? When have you tested enough? • This is formally defined in the Verification Plan – Verification Schedule • A pert chart with the tasks and a schedule for the tasks assigned to members of the team. • A failure to plan is a plan to ……. . EE 694 v-Verification-Lect 7 -17 -