Design Specification BehavioralRTL Description HDL Functional Verification Logic

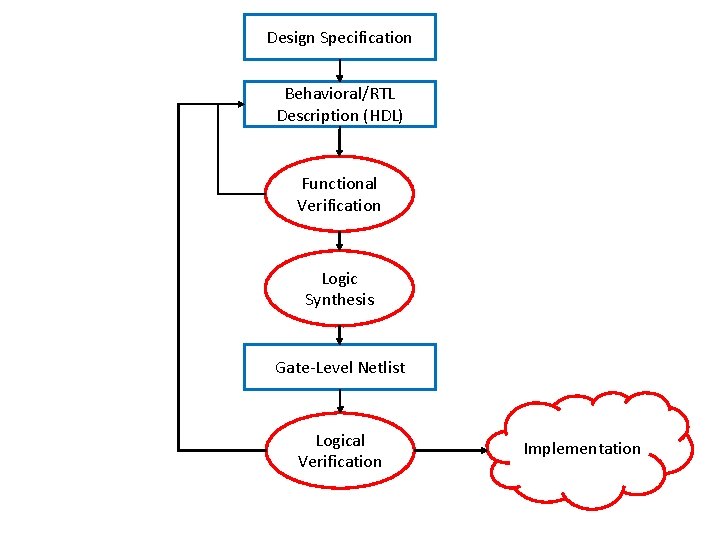

Design Specification Behavioral/RTL Description (HDL) Functional Verification Logic Synthesis Gate-Level Netlist Logical Verification Implementation

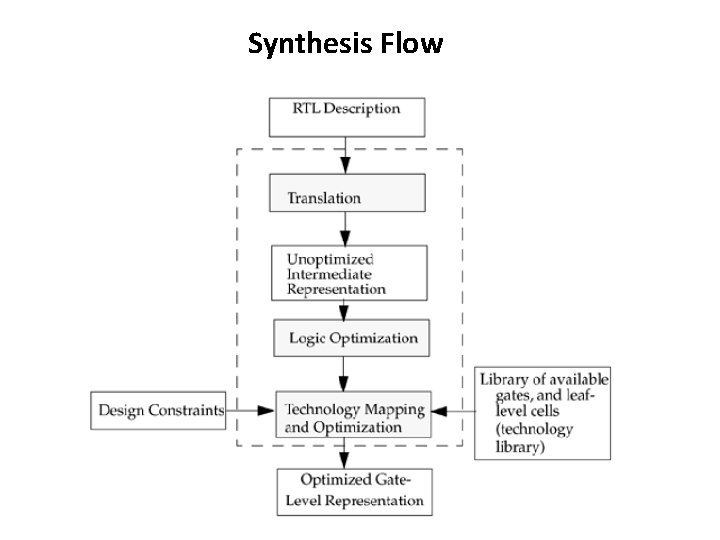

Synthesis Flow

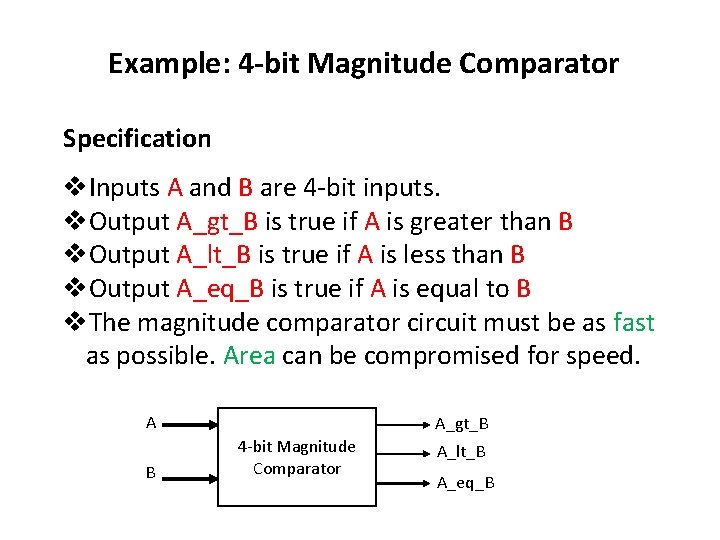

Example: 4 -bit Magnitude Comparator Specification v. Inputs A and B are 4 -bit inputs. v. Output A_gt_B is true if A is greater than B v. Output A_lt_B is true if A is less than B v. Output A_eq_B is true if A is equal to B v. The magnitude comparator circuit must be as fast as possible. Area can be compromised for speed. A B A_gt_B 4 -bit Magnitude Comparator A_lt_B A_eq_B

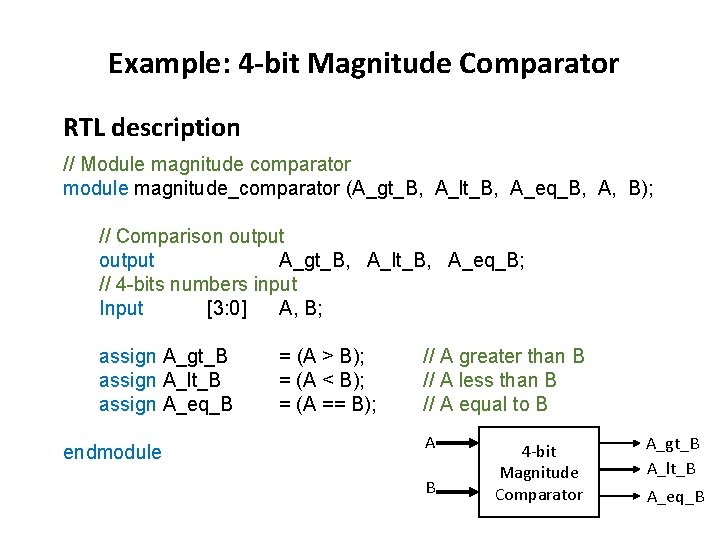

Example: 4 -bit Magnitude Comparator RTL description // Module magnitude comparator module magnitude_comparator (A_gt_B, A_lt_B, A_eq_B, A, B); // Comparison output A_gt_B, A_lt_B, A_eq_B; // 4 -bits numbers input Input [3: 0] A, B; assign A_gt_B assign A_lt_B assign A_eq_B endmodule = (A > B); = (A < B); = (A == B); // A greater than B // A less than B // A equal to B A B 4 -bit Magnitude Comparator A_gt_B A_lt_B A_eq_B

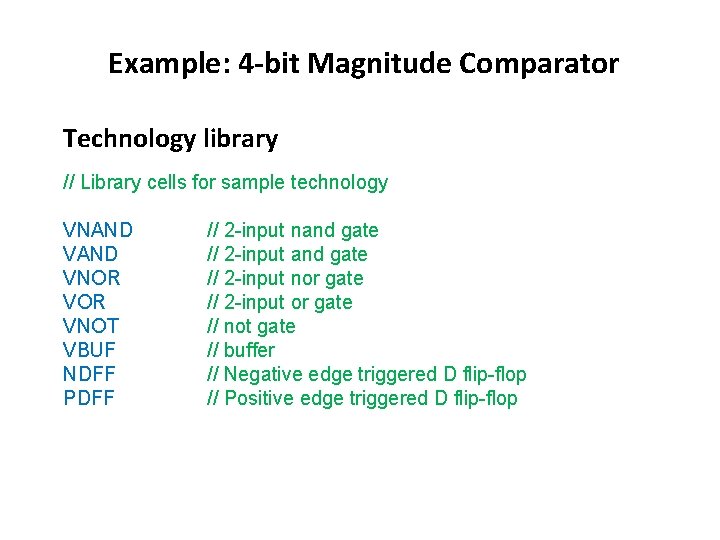

Example: 4 -bit Magnitude Comparator Technology library // Library cells for sample technology VNAND VNOR VNOT VBUF NDFF PDFF // 2 -input nand gate // 2 -input nor gate // 2 -input or gate // not gate // buffer // Negative edge triggered D flip-flop // Positive edge triggered D flip-flop

Example: 4 -bit Magnitude Comparator Design Constraints Optimize the final circuit for fastest timing.

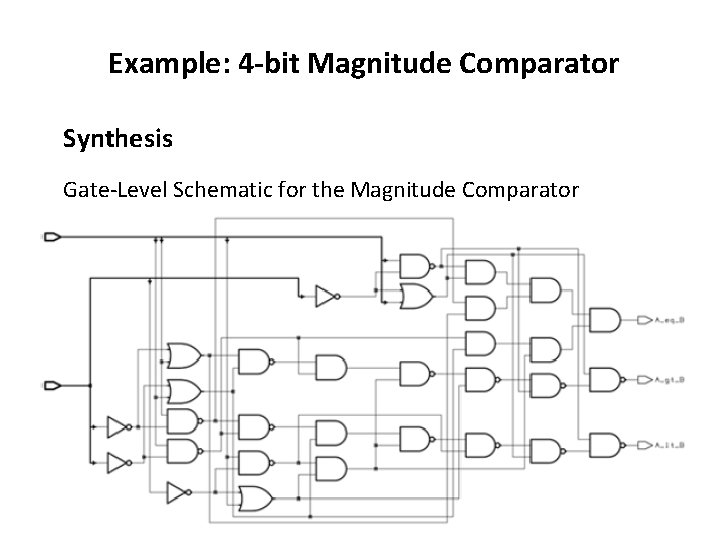

Example: 4 -bit Magnitude Comparator Synthesis Gate-Level Schematic for the Magnitude Comparator

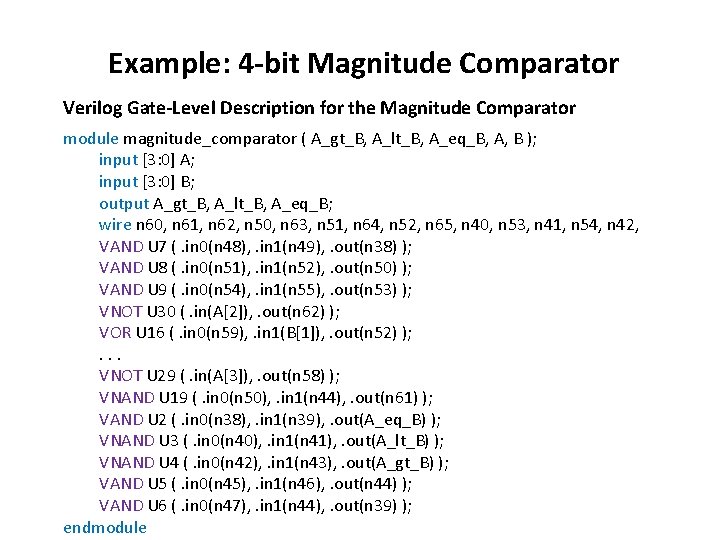

Example: 4 -bit Magnitude Comparator Verilog Gate-Level Description for the Magnitude Comparator module magnitude_comparator ( A_gt_B, A_lt_B, A_eq_B, A, B ); input [3: 0] A; input [3: 0] B; output A_gt_B, A_lt_B, A_eq_B; wire n 60, n 61, n 62, n 50, n 63, n 51, n 64, n 52, n 65, n 40, n 53, n 41, n 54, n 42, VAND U 7 (. in 0(n 48), . in 1(n 49), . out(n 38) ); VAND U 8 (. in 0(n 51), . in 1(n 52), . out(n 50) ); VAND U 9 (. in 0(n 54), . in 1(n 55), . out(n 53) ); VNOT U 30 (. in(A[2]), . out(n 62) ); VOR U 16 (. in 0(n 59), . in 1(B[1]), . out(n 52) ); . . . VNOT U 29 (. in(A[3]), . out(n 58) ); VNAND U 19 (. in 0(n 50), . in 1(n 44), . out(n 61) ); VAND U 2 (. in 0(n 38), . in 1(n 39), . out(A_eq_B) ); VNAND U 3 (. in 0(n 40), . in 1(n 41), . out(A_lt_B) ); VNAND U 4 (. in 0(n 42), . in 1(n 43), . out(A_gt_B) ); VAND U 5 (. in 0(n 45), . in 1(n 46), . out(n 44) ); VAND U 6 (. in 0(n 47), . in 1(n 44), . out(n 39) ); endmodule

- Slides: 8