ECE 3130 Digital Electronics and Design Lab 6

ECE 3130 – Digital Electronics and Design Lab 6 Latch and Flip-Flops Fall 2016

What are latches and flip-flops? � Sequential circuits that store information (i. e. memory elements – output depends not only on present inputs but also previous inputs) � Latches – output responds to input immediately as long as the enable signal (high level or low level) is asserted � Flip flops – output responds only to the rising and falling edge of the enable signal

Today’s lab Build and test the following latch and flip-flop �D Latch �D Flip Flop �JK Flip Flop �T Flip Flop

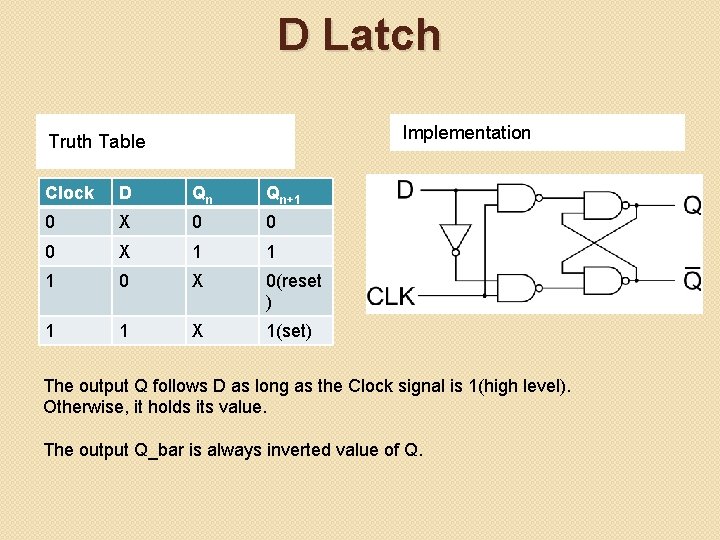

D Latch Implementation Truth Table Clock D Qn Qn+1 0 X 0 0 0 X 1 1 1 0 X 0(reset ) 1 1 X 1(set) The output Q follows D as long as the Clock signal is 1(high level). Otherwise, it holds its value. The output Q_bar is always inverted value of Q.

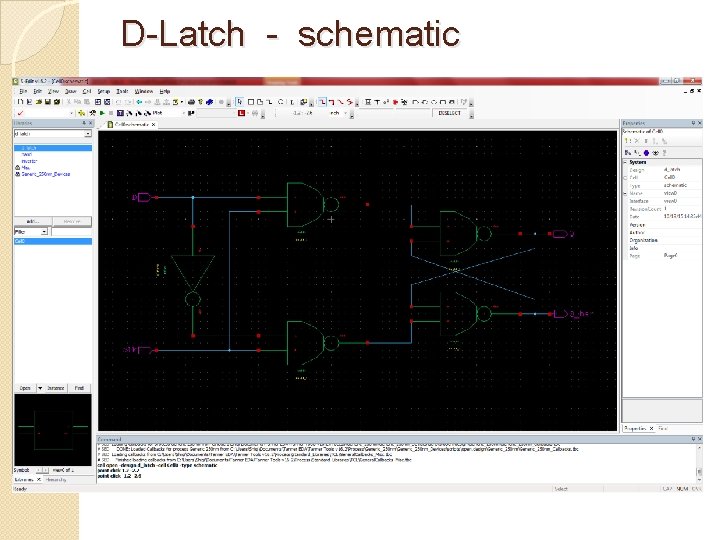

D-Latch - schematic

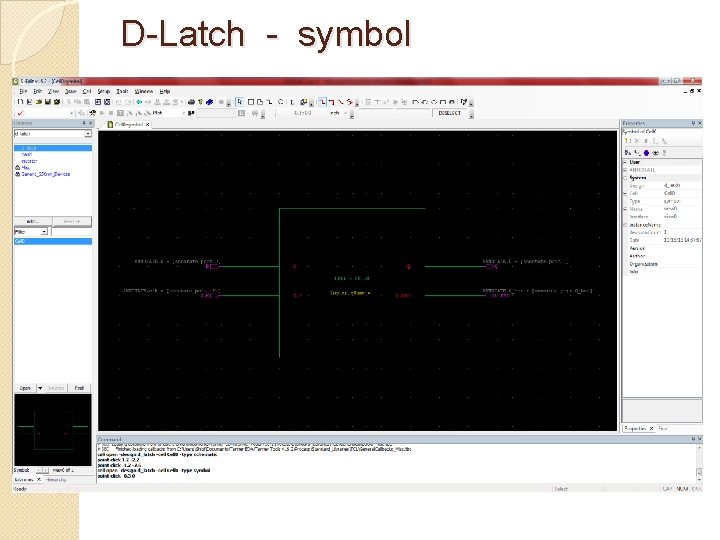

D-Latch - symbol

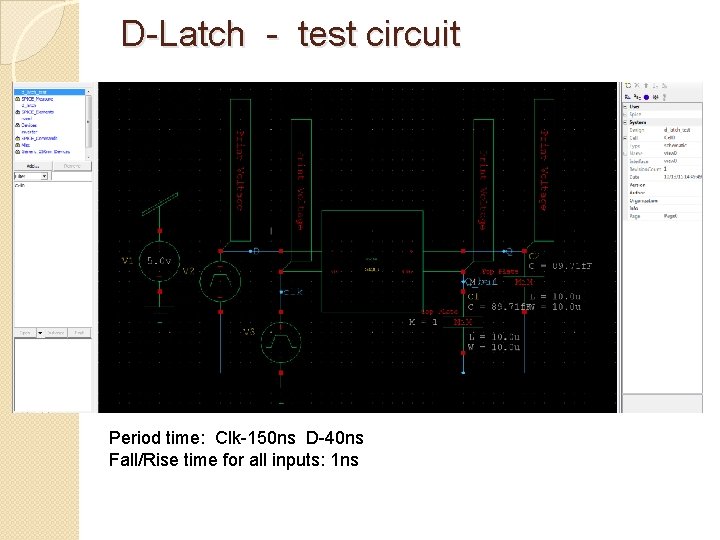

D-Latch - test circuit Period time: Clk-150 ns D-40 ns Fall/Rise time for all inputs: 1 ns

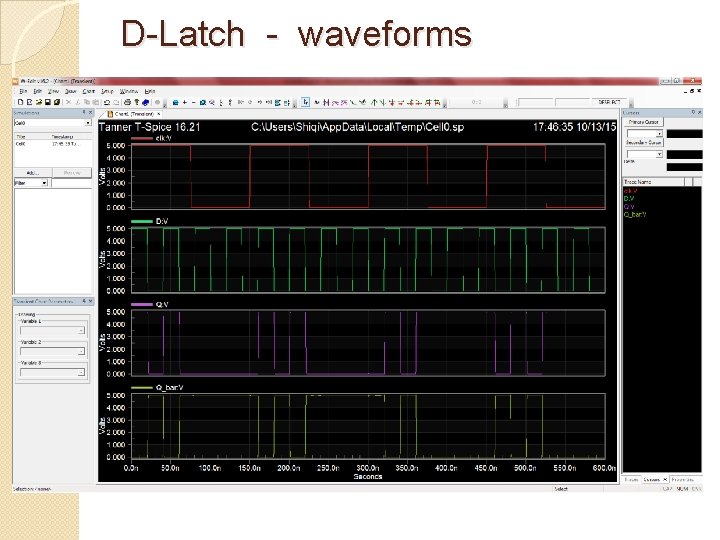

D-Latch - waveforms

D Flip-Flop (DFF) �The value of input D is stored on either the rising or falling clock edge. �The figure below shows a positive-edge triggered DFF. Clock D Q

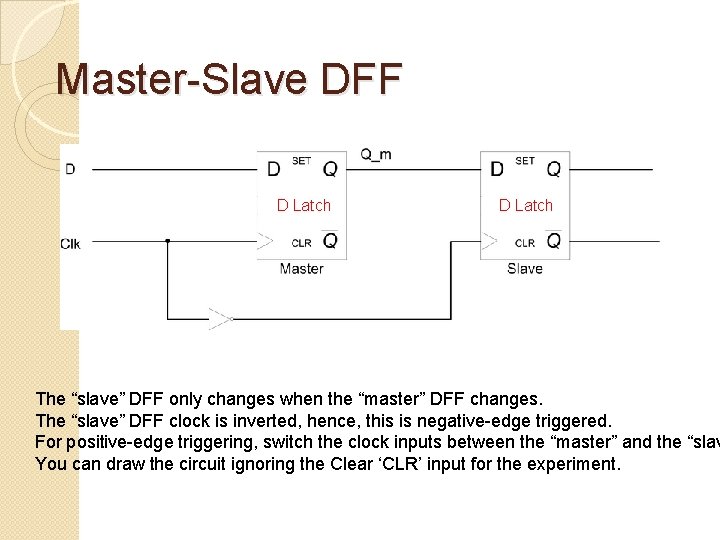

Master-Slave DFF D Latch The “slave” DFF only changes when the “master” DFF changes. The “slave” DFF clock is inverted, hence, this is negative-edge triggered. For positive-edge triggering, switch the clock inputs between the “master” and the “slav You can draw the circuit ignoring the Clear ‘CLR’ input for the experiment.

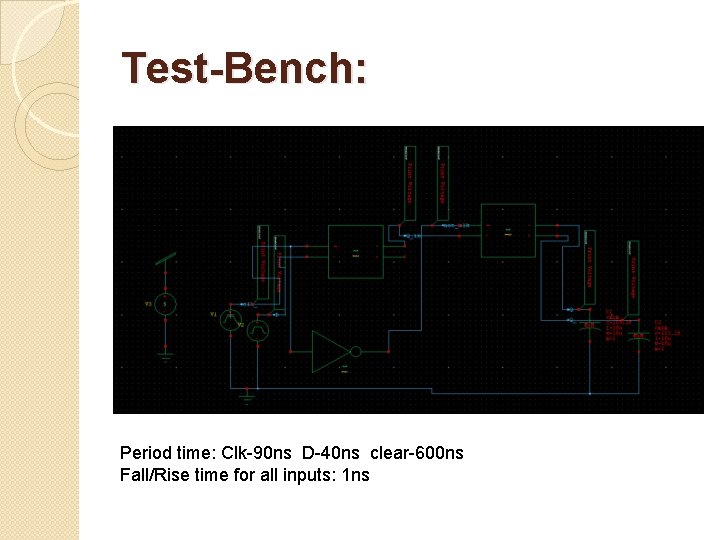

Test-Bench: Period time: Clk-90 ns D-40 ns clear-600 ns Fall/Rise time for all inputs: 1 ns

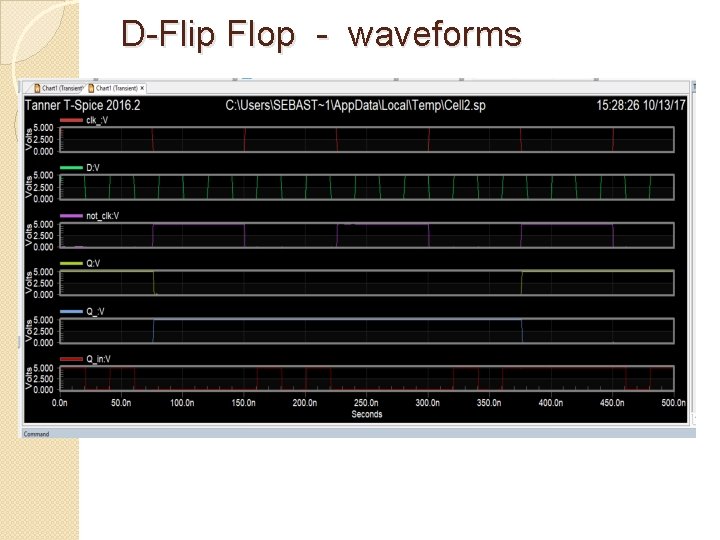

D-Flip Flop - waveforms

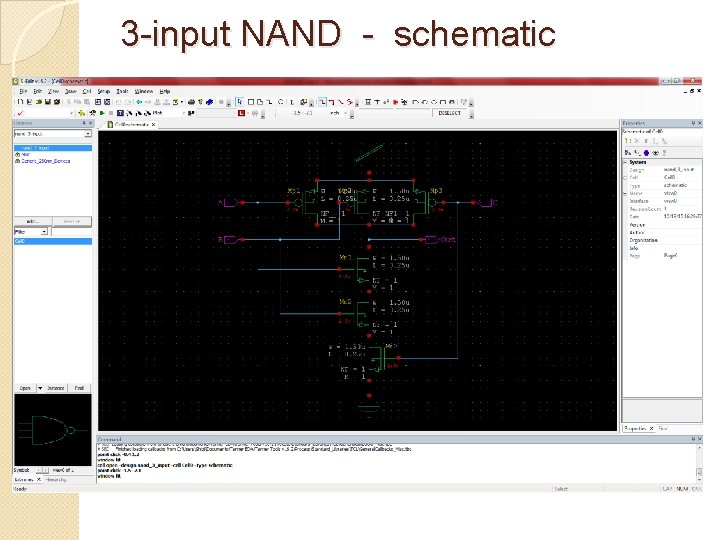

3 -input NAND - schematic

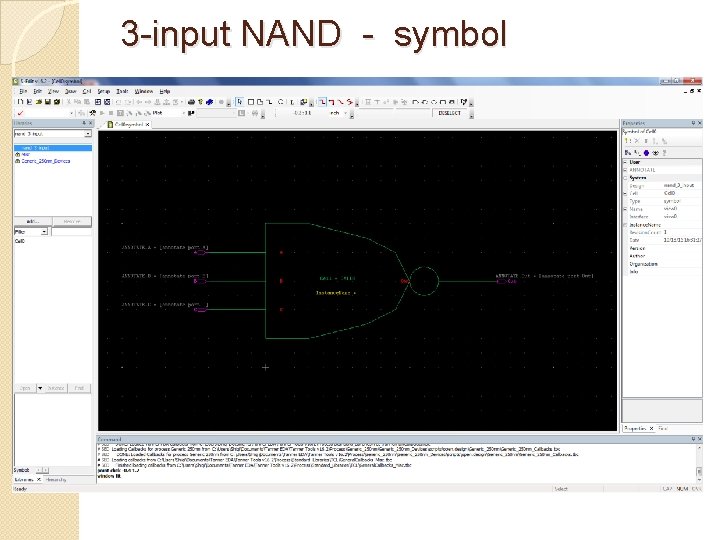

3 -input NAND - symbol

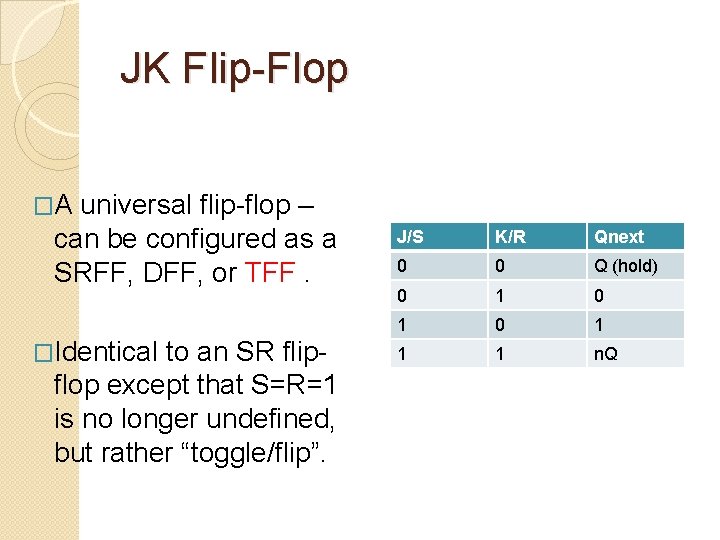

JK Flip-Flop �A universal flip-flop – can be configured as a SRFF, DFF, or TFF. �Identical to an SR flipflop except that S=R=1 is no longer undefined, but rather “toggle/flip”. J/S K/R Qnext 0 0 Q (hold) 0 1 0 1 1 1 n. Q

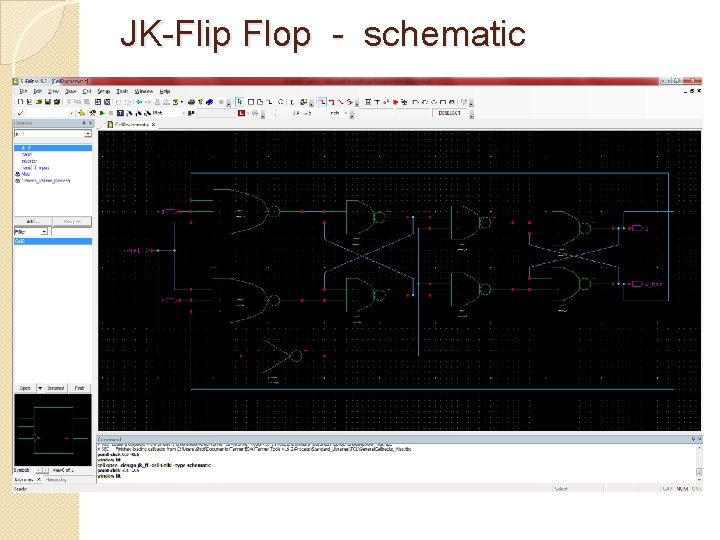

JK-Flip Flop - schematic

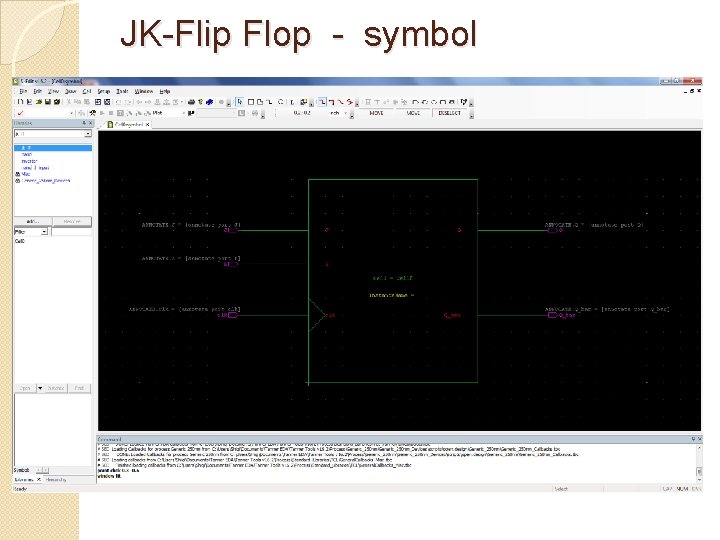

JK-Flip Flop - symbol

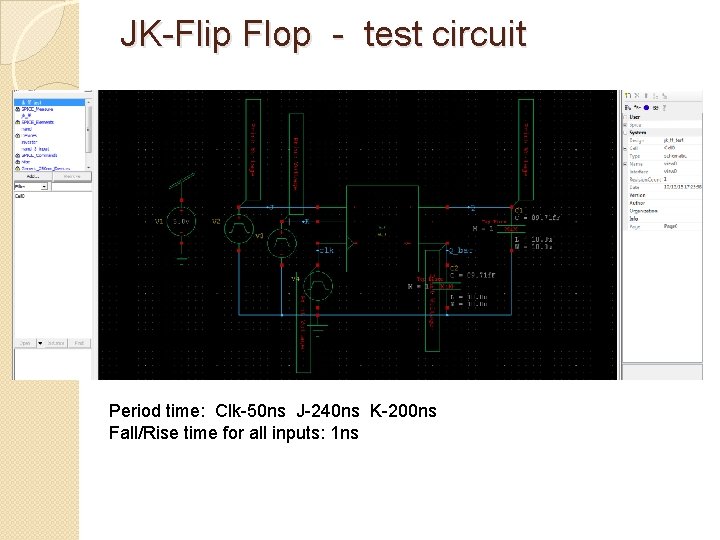

JK-Flip Flop - test circuit Period time: Clk-50 ns J-240 ns K-200 ns Fall/Rise time for all inputs: 1 ns

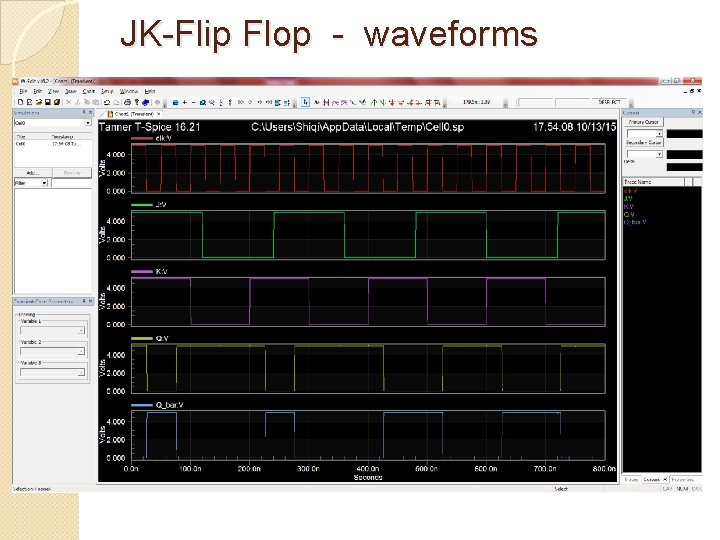

JK-Flip Flop - waveforms

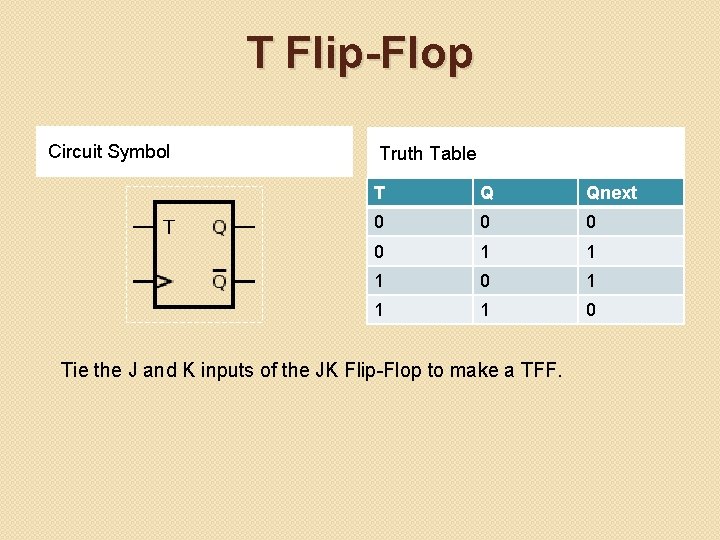

T Flip-Flop Circuit Symbol Truth Table T Q Qnext 0 0 1 1 1 0 Tie the J and K inputs of the JK Flip-Flop to make a TFF.

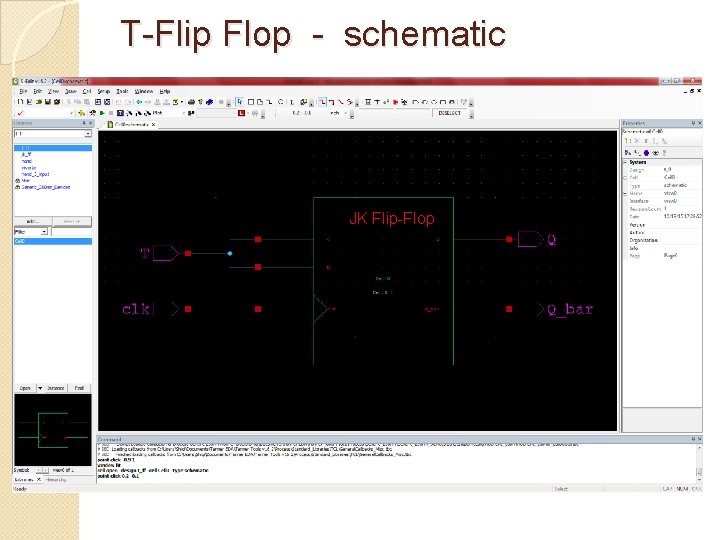

T-Flip Flop - schematic JK Flip-Flop

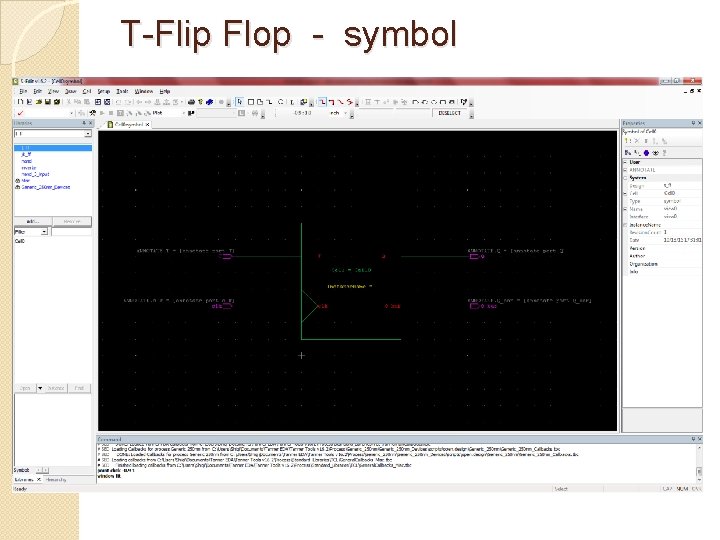

T-Flip Flop - symbol

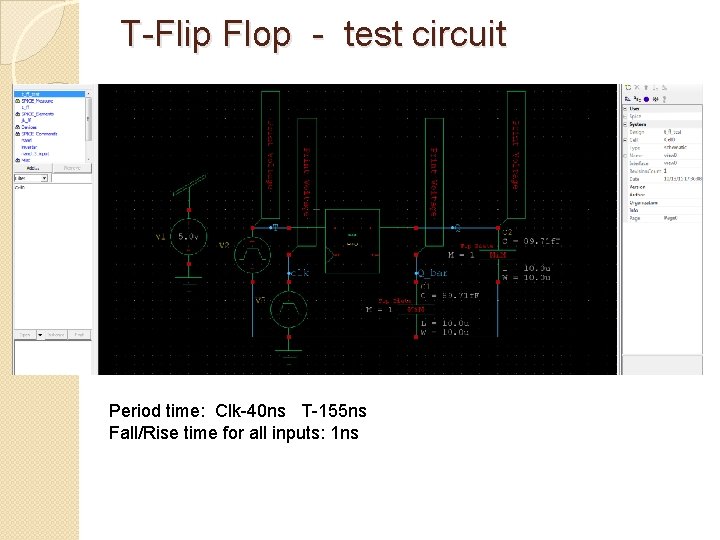

T-Flip Flop - test circuit Period time: Clk-40 ns T-155 ns Fall/Rise time for all inputs: 1 ns

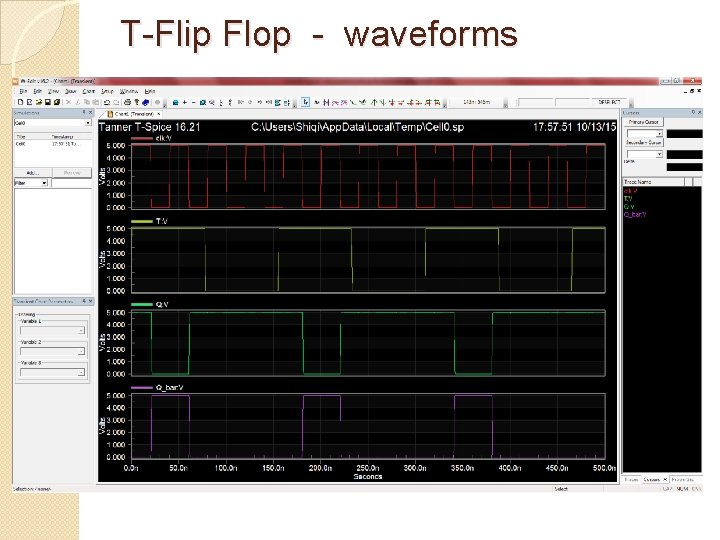

T-Flip Flop - waveforms

- Slides: 24