Combinational Logic Computer Organization Ellen Walker Hiram College

Combinational Logic Computer Organization Ellen Walker Hiram College Figures from Computer Organization and Design 3 ed, D. A. Patterson & J. L. Hennessey, Morgan Kauffman © 2005 unless otherwise specified

Types of Logic • Combinational Logic – Outputs depend only on inputs – Outputs change (after delay) as inputs change • Sequential Logic – Outputs depend on inputs and memory (including previous output) – Memory values called state – Outputs (and state) change synchronously based on a clock signal

Truth Tables • Completely describe combinational logic • Column for each input and output • Row for each possible combination of inputs – For n inputs, there are 2^n entries

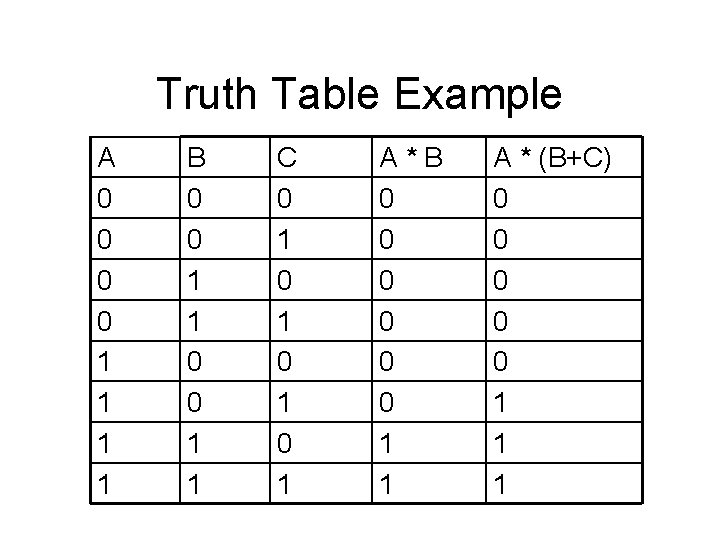

Truth Table Example A 0 0 1 1 B 0 0 1 1 C 0 1 0 1 A*B 0 0 0 1 1 A * (B+C) 0 0 0 1 1 1

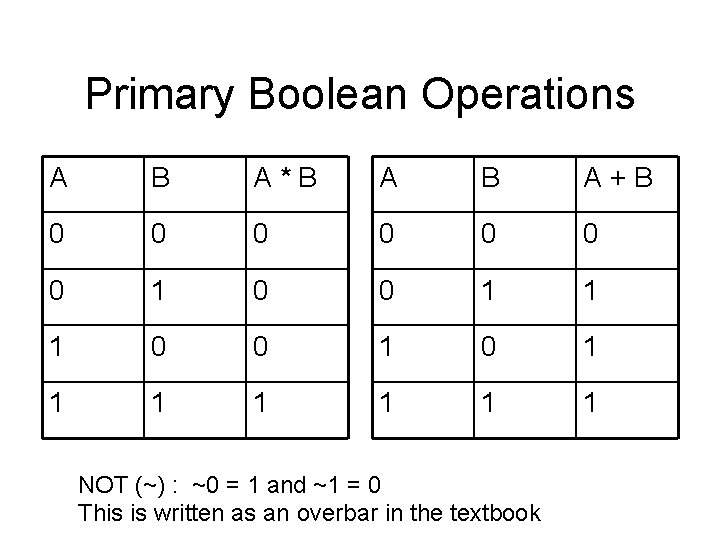

Primary Boolean Operations A B A*B A B A+B 0 0 0 0 1 1 1 0 0 1 1 1 1 NOT (~) : ~0 = 1 and ~1 = 0 This is written as an overbar in the textbook

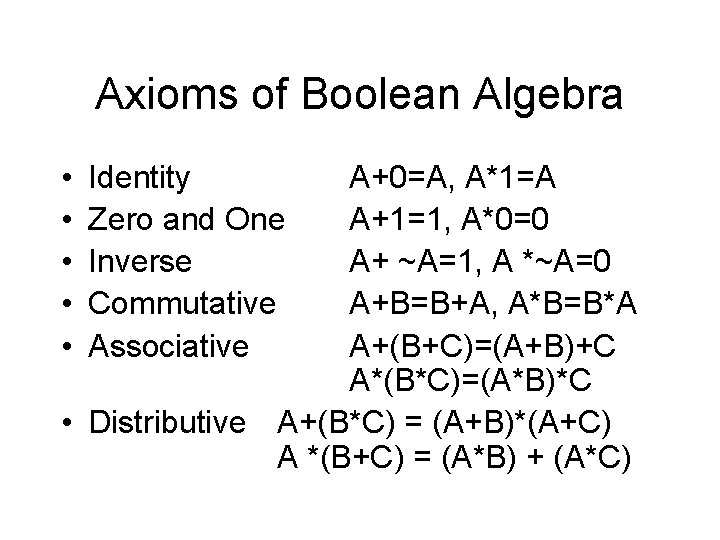

Axioms of Boolean Algebra • • • Identity Zero and One Inverse Commutative Associative A+0=A, A*1=A A+1=1, A*0=0 A+ ~A=1, A *~A=0 A+B=B+A, A*B=B*A A+(B+C)=(A+B)+C A*(B*C)=(A*B)*C • Distributive A+(B*C) = (A+B)*(A+C) A *(B+C) = (A*B) + (A*C)

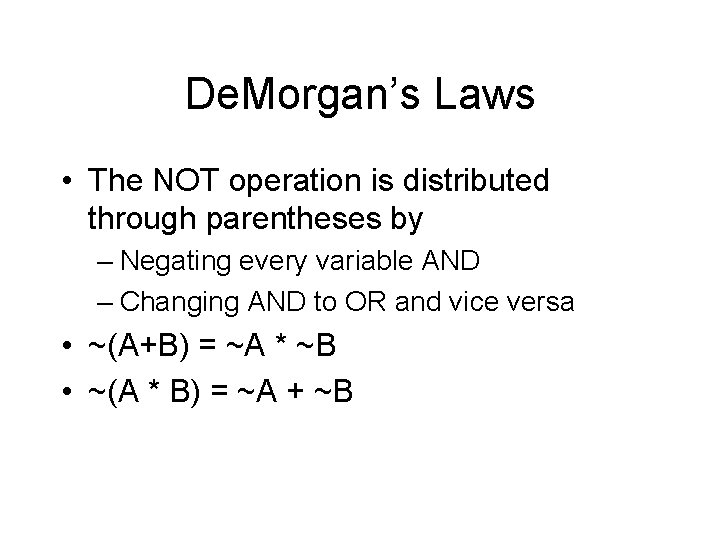

De. Morgan’s Laws • The NOT operation is distributed through parentheses by – Negating every variable AND – Changing AND to OR and vice versa • ~(A+B) = ~A * ~B • ~(A * B) = ~A + ~B

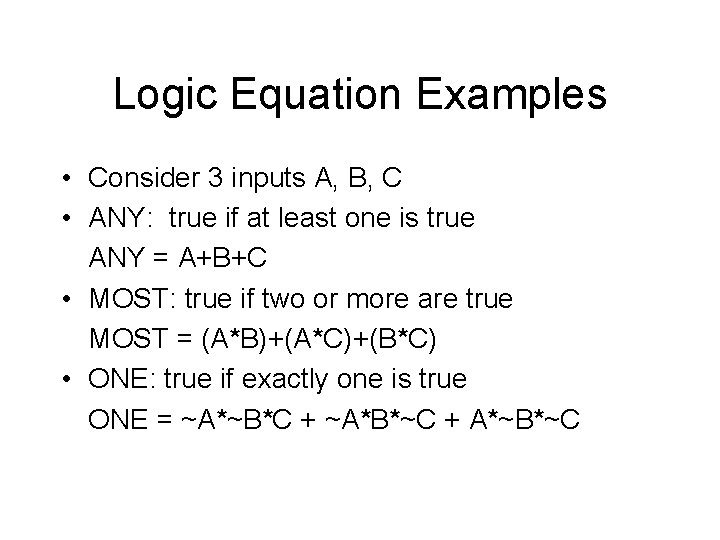

Logic Equation Examples • Consider 3 inputs A, B, C • ANY: true if at least one is true ANY = A+B+C • MOST: true if two or more are true MOST = (A*B)+(A*C)+(B*C) • ONE: true if exactly one is true ONE = ~A*~B*C + ~A*B*~C + A*~B*~C

Many Possible Equations • TWO: Exactly TWO of A, B, C are true TWO = A*B*~C + A*~B*C + ~A*B*C TWO = (A*B + A*C + B*C). ~(A*B*C) • Can we prove these expressions are equivalent? – Yes, if their truth tables are identical – Yes, if we can find a sequence of axioms to transform one to the other

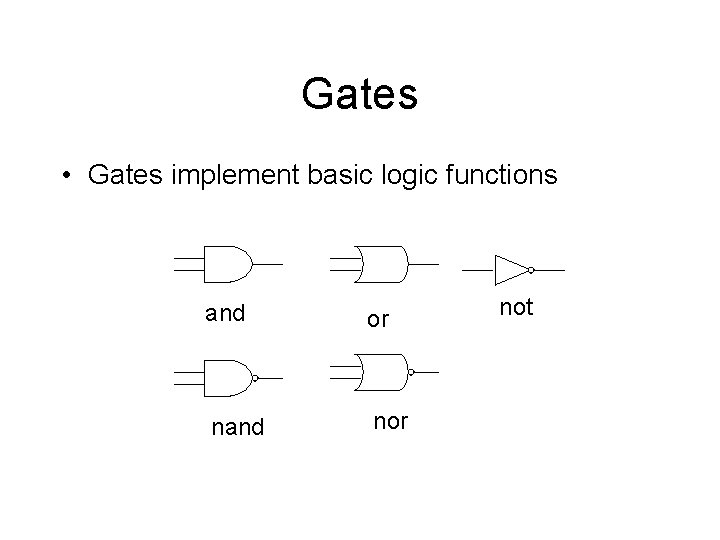

Gates • Gates implement basic logic functions and or nand nor not

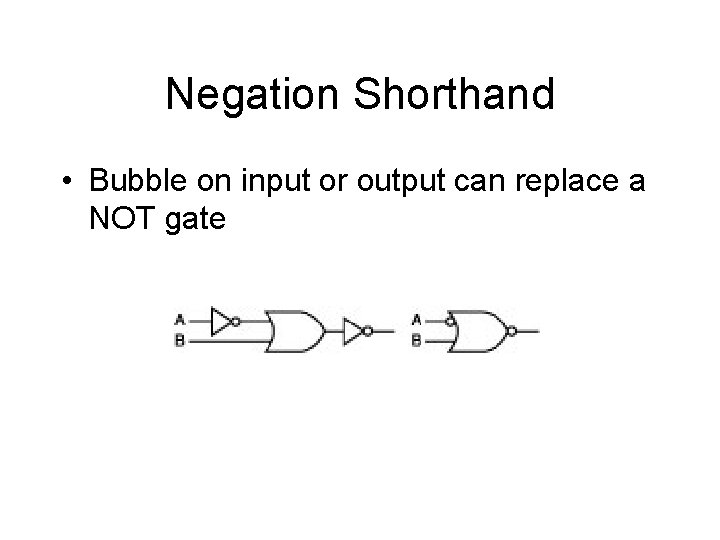

Negation Shorthand • Bubble on input or output can replace a NOT gate

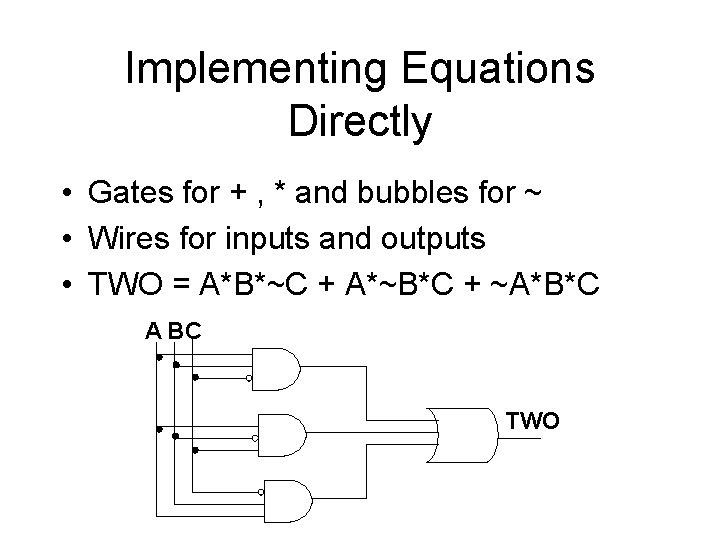

Implementing Equations Directly • Gates for + , * and bubbles for ~ • Wires for inputs and outputs • TWO = A*B*~C + A*~B*C + ~A*B*C A BC TWO

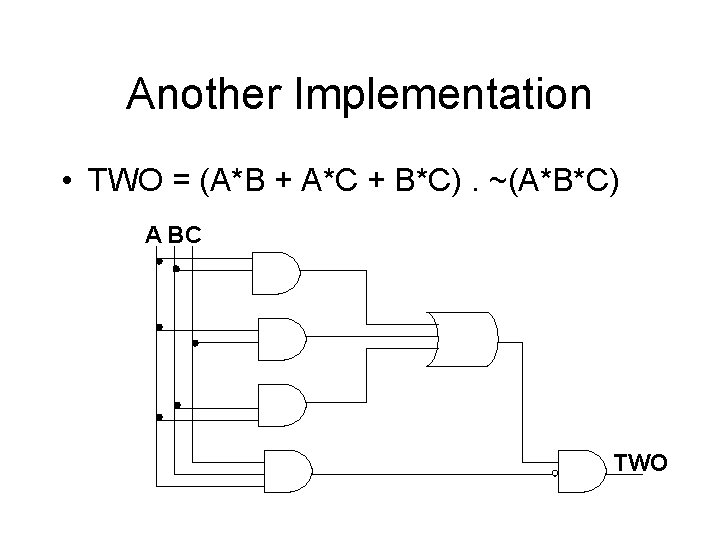

Another Implementation • TWO = (A*B + A*C + B*C). ~(A*B*C) A BC TWO

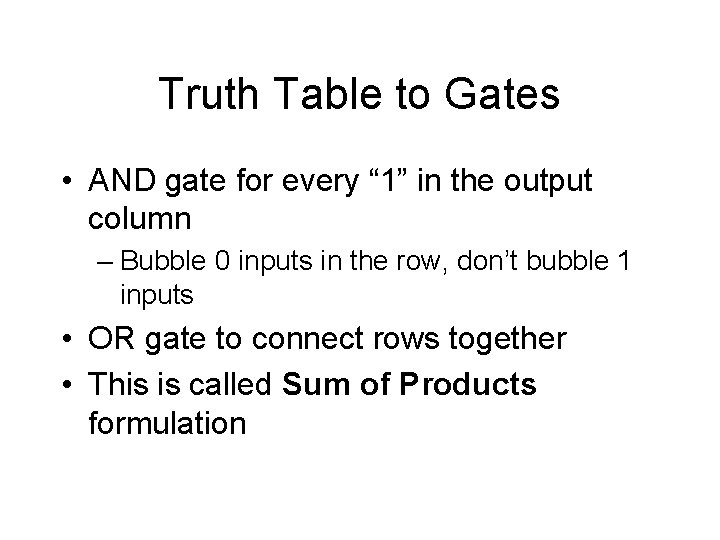

Truth Table to Gates • AND gate for every “ 1” in the output column – Bubble 0 inputs in the row, don’t bubble 1 inputs • OR gate to connect rows together • This is called Sum of Products formulation

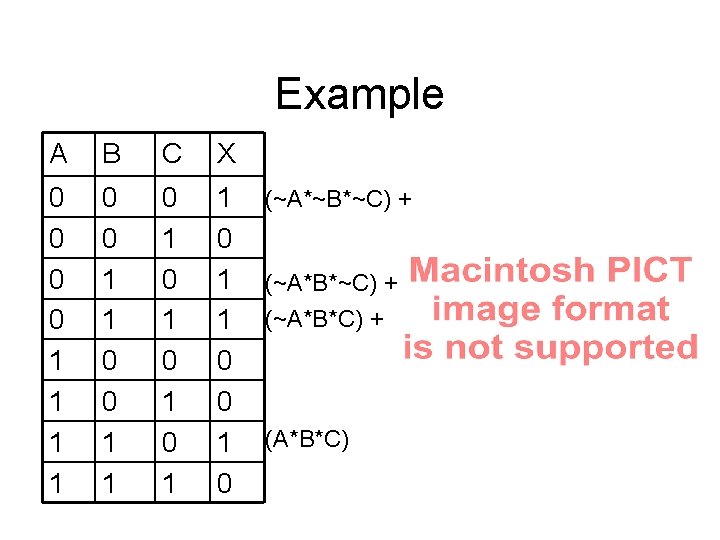

Example A B C X 0 0 1 1 0 1 0 1 1 0 0 1 0 (~A*~B*~C) + (~A*B*C) + (A*B*C)

Simplifying • Group together expressions with common elements • ~A~B~C + ~AB~C = ~A~C • ~AB~C + ~ABC = ~AB • ~ABC + ABC = BC

Simplified Circuit Fewer gates and fewer inputs

Karnaugh Map • Rewrite truth table in a rectangular matrix • “Rows” with common subexpressions are adjacent • Find simplifications by circling adjacent 1’s – Circles can wrap around top/bottom

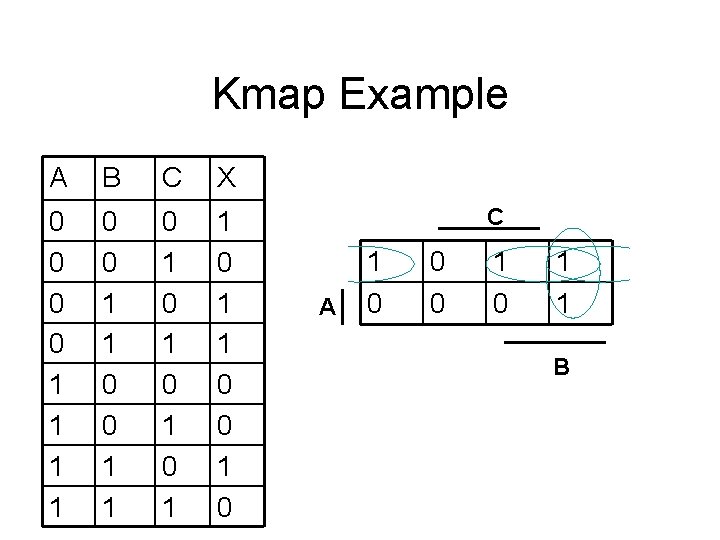

Kmap Example A B C X 0 0 1 1 0 1 0 1 1 0 0 1 0 C A 1 0 0 0 1 1 B

4 -Variable Kmap • Numbers indicate row of truth table

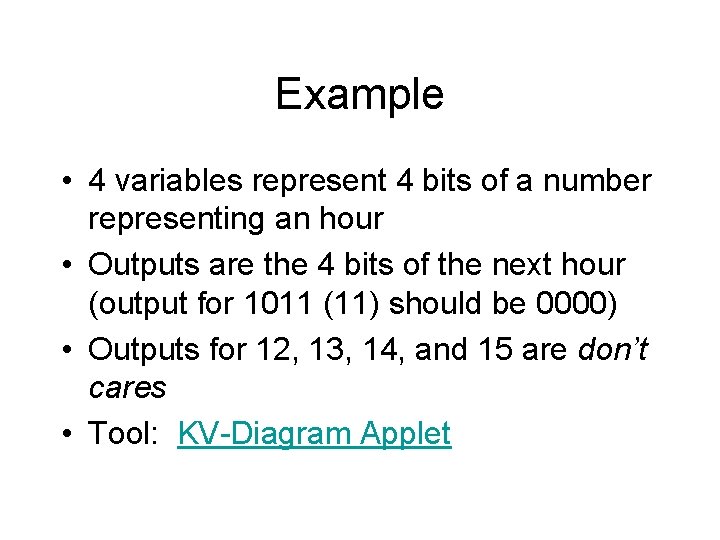

Example • 4 variables represent 4 bits of a number representing an hour • Outputs are the 4 bits of the next hour (output for 1011 (11) should be 0000) • Outputs for 12, 13, 14, and 15 are don’t cares • Tool: KV-Diagram Applet

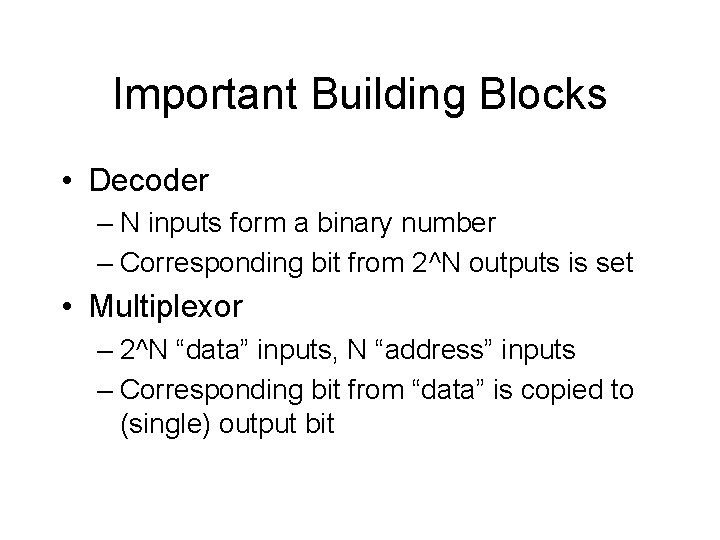

Important Building Blocks • Decoder – N inputs form a binary number – Corresponding bit from 2^N outputs is set • Multiplexor – 2^N “data” inputs, N “address” inputs – Corresponding bit from “data” is copied to (single) output bit

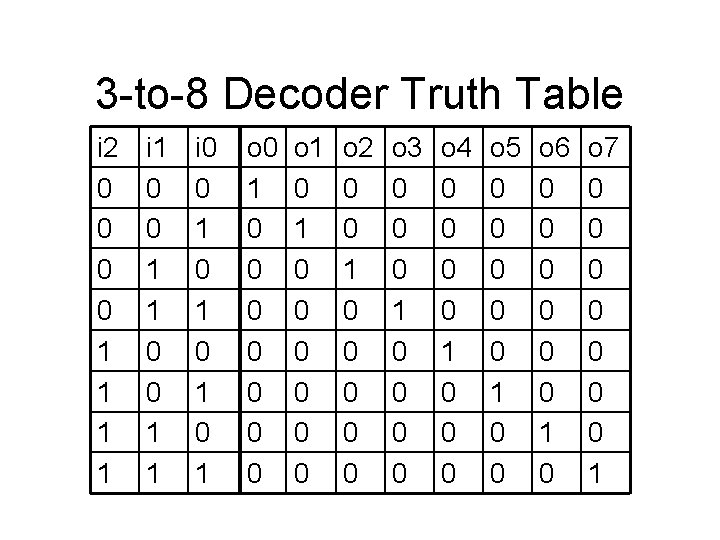

3 -to-8 Decoder Truth Table i 2 0 0 1 1 i 1 0 0 1 1 i 0 0 1 0 1 o 0 1 0 0 0 0 o 2 0 0 1 0 0 0 o 3 0 0 0 1 0 0 o 4 0 0 1 0 0 0 o 5 0 0 0 1 0 0 o 6 0 0 0 1 0 o 7 0 0 0 0 1

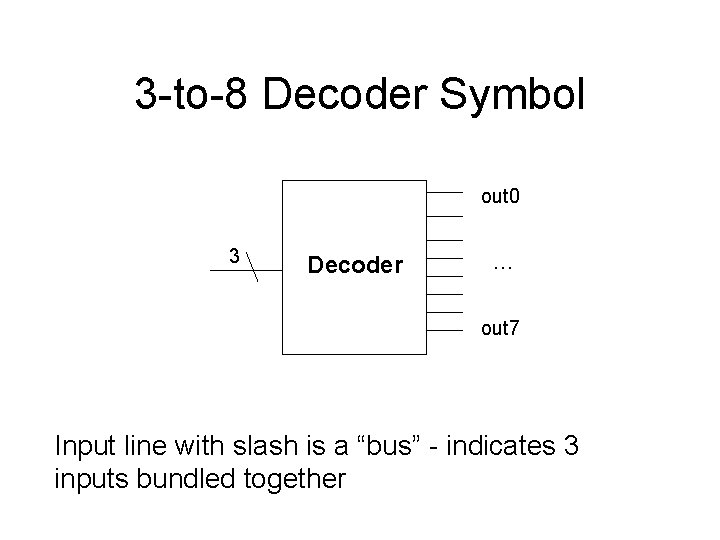

3 -to-8 Decoder Symbol out 0 3 Decoder … out 7 Input line with slash is a “bus” - indicates 3 inputs bundled together

Multiplexor (2 -bit selector) • Circuit to “select” one of its data inputs based on address inputs • Simplest multiplexor has 2 data inputs (A&B), 1 address (or selector) input Out = ~S * A + S * B

General Multiplexors • Build using N to 2^N decoder – Address bits are input to decoder – N AND gates, each gets 1 data input, and corresponding decoder output – OR gate connecting the AND gates • O = d 0*i 0+d 1*i 1+i 2*i 2+… – dj is j’th output of decoder – ij is j’th input to the multiplexor

Multiplexor as Logic Implementor • For N inputs, use an N input multiplexor • Address inputs are actual inputs to circult • Data inputs fixed to corresponding outputs from truth table • Multiplexor “selects” the correct row of the truth table, hence the correct output • Any function can be implemented with 1 multiplexor (of the appropriate size)

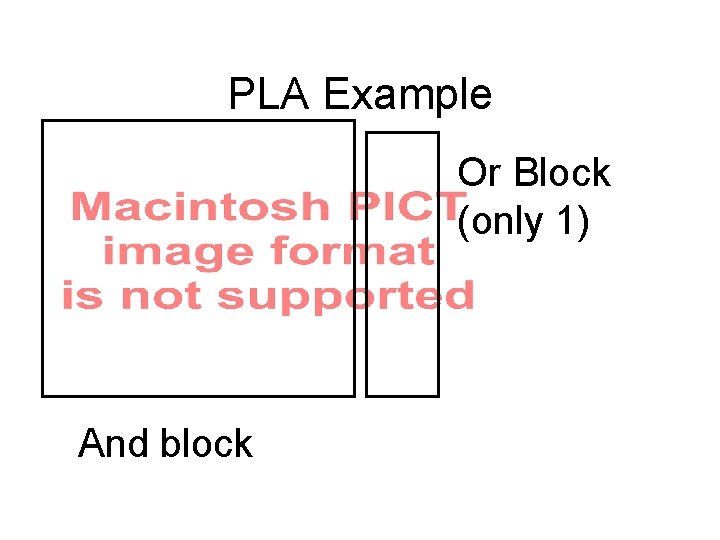

Programmed Logic Array • A Programmed Logic Array implements Sum of Products form directly • AND gates (generate product terms) • OR gates (combine product terms into outputs) • Since structure is so regular, build PLA in silicon, use fuses to connect inputs to gates

PLA Example Or Block (only 1) And block

Read Only Memory • ROM is essentially many multiplexors working in parallel • Address bits (input) – Choose a memory location • Data bits (output) – Value of bits at that memory location

ROM Size • Width = number of bits per address (e. g. word size, number of data lines) • Height = number of addresses (e. g. words in memory) – If there are N input (address) lines, the height is 2^N • Total number of bits stored = height x width

Implementing a Function in ROM • Given N inputs, M outputs • ROM – Height = – Width = • Program each word in ROM with the outputs corresponding to that word’s address • Connect inputs to: • Connect outputs to:

Building ALU • 2 inputs • Operation code • Based on code, performs operation on the given inputs

1 -Bit Logic Unit • Operation Codes: 0=AND, 1=OR

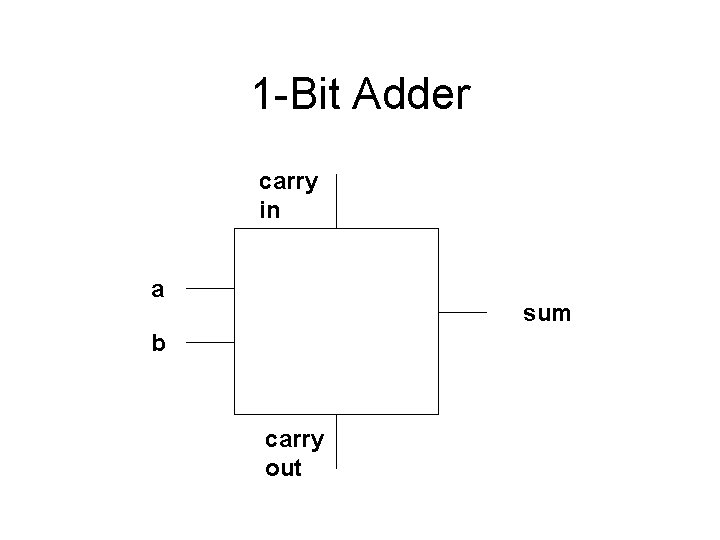

1 -Bit Adder carry in a sum b carry out

1 -Bit ALU (Add, And, Or) • Carry in & out lines • Bigger Multiplexor for opcode • Data inputs to Multiplexor: – AND – OR – Adder

ALU with Subtraction • Ainvert, Binvert operate on negated inputs • For subtraction, set both Carry. In and Binvert to true

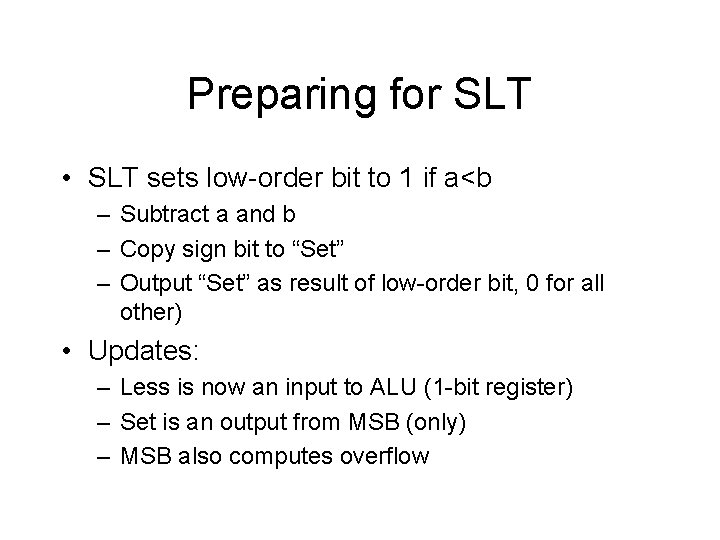

Preparing for SLT • SLT sets low-order bit to 1 if a<b – Subtract a and b – Copy sign bit to “Set” – Output “Set” as result of low-order bit, 0 for all other) • Updates: – Less is now an input to ALU (1 -bit register) – Set is an output from MSB (only) – MSB also computes overflow

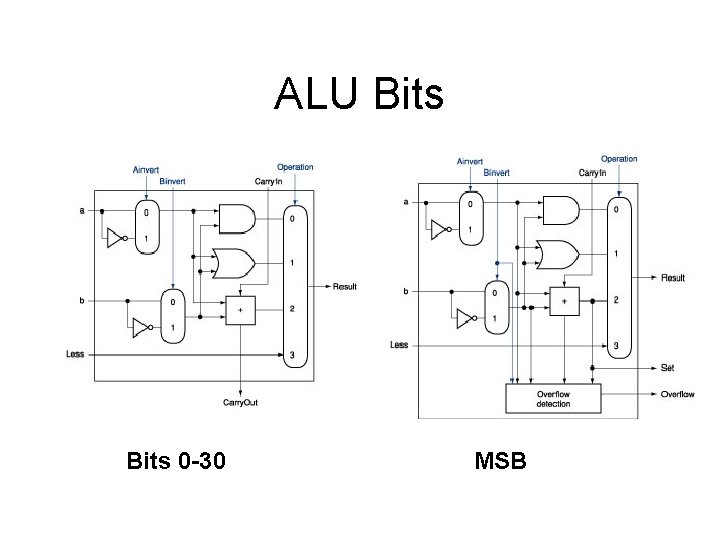

ALU Bits 0 -30 MSB

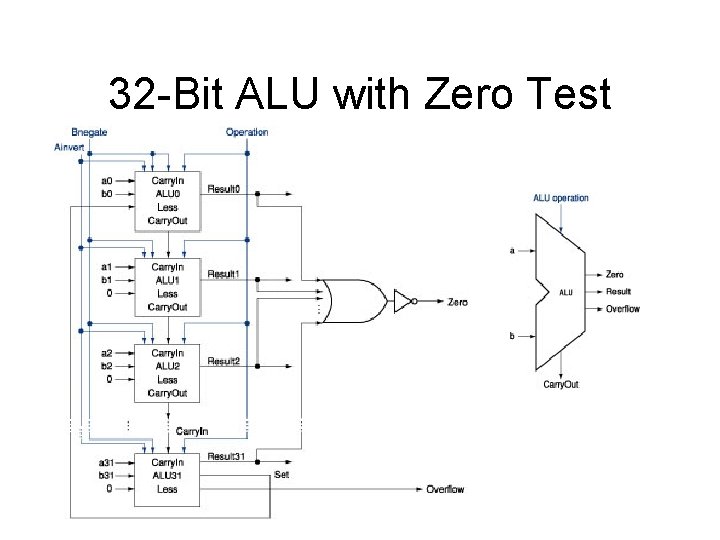

32 -Bit ALU with Zero Test

- Slides: 40