240 208 Fundamental of Computer Architecture Ocbober 25

240 -208 Fundamental of Computer Architecture Ocbober 25, 2004 By Panyayot Chaikan panyayot@coe. psu. ac. th

Chapter 3 ������� The Processing Unit 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 2

�������������� ��������������������� �� 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 3

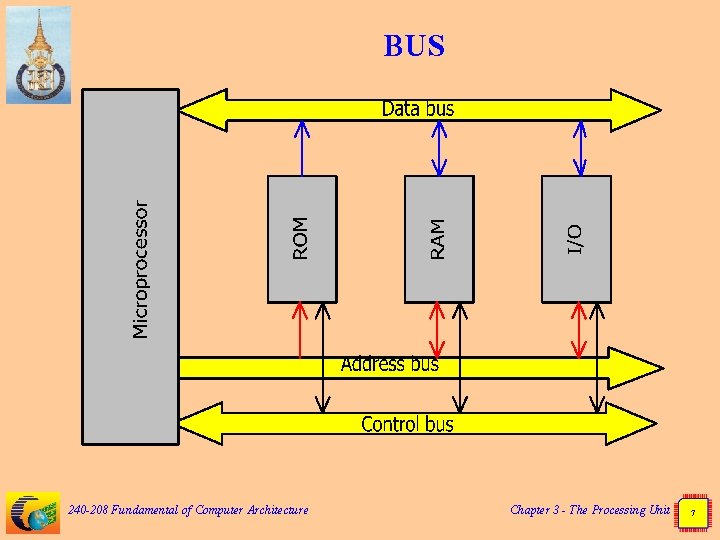

Computer BUS u. A group of wires that connects several devices u. Three types of Bus u. Address bus u. Data bus u. Control bus 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 4

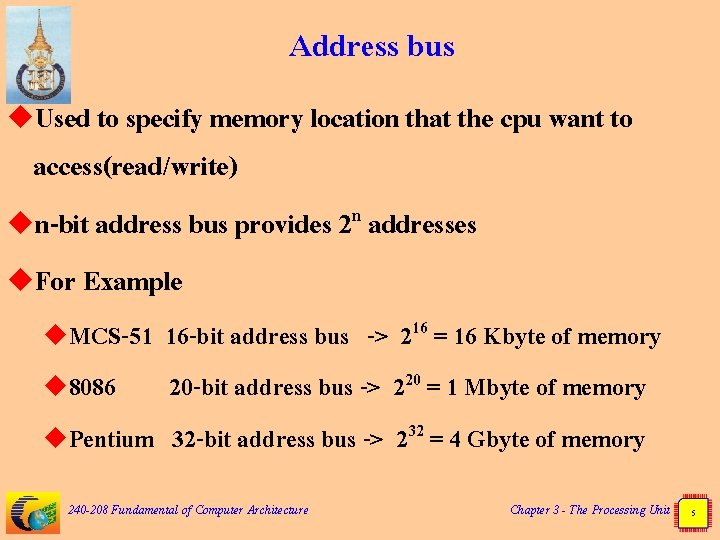

Address bus u. Used to specify memory location that the cpu want to access(read/write) un-bit address bus provides 2 n addresses u. For Example u. MCS-51 16 -bit address bus -> 216 = 16 Kbyte of memory u 8086 20 -bit address bus -> 220 = 1 Mbyte of memory u. Pentium 32 -bit address bus -> 232 = 4 Gbyte of memory 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 5

Databus u. Used to sent data between CPU and peripheral(memory, i/o) u. The more bit of data bus, the more speed achieved u. For Example u. MCS-51 8 -bit data bus u 8086 16 -bit data bus u. Pentium 64 -bit data bus 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 6

BUS 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 7

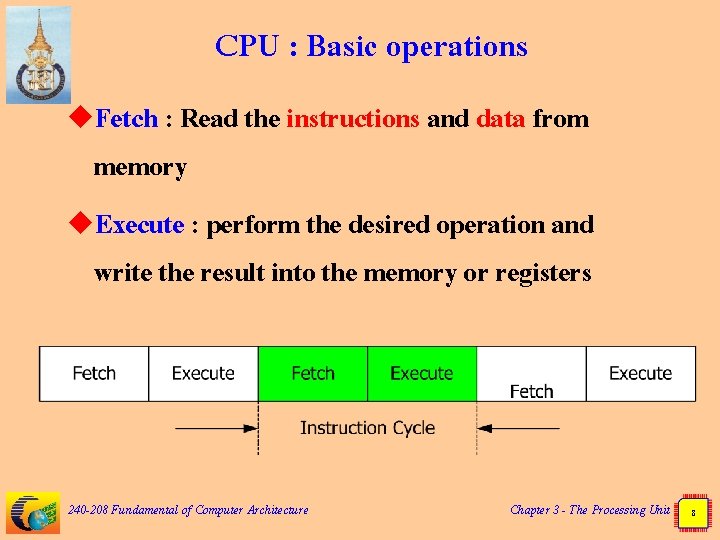

CPU : Basic operations u. Fetch : Read the instructions and data from memory u. Execute : perform the desired operation and write the result into the memory or registers 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 8

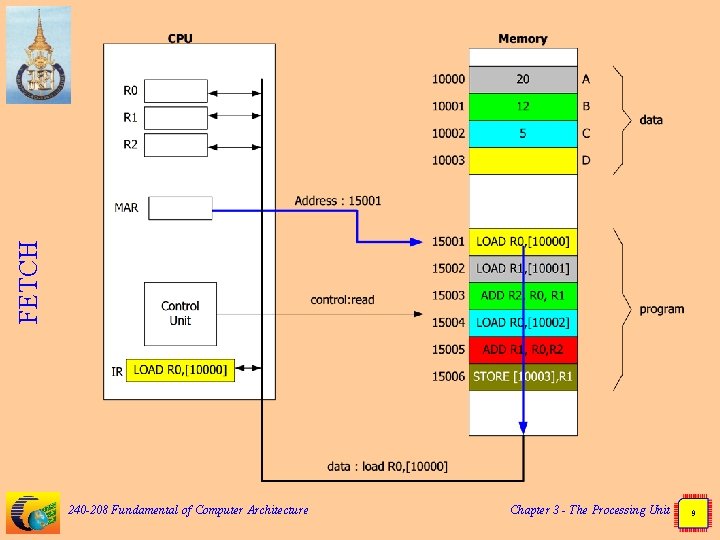

FETCH 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 9

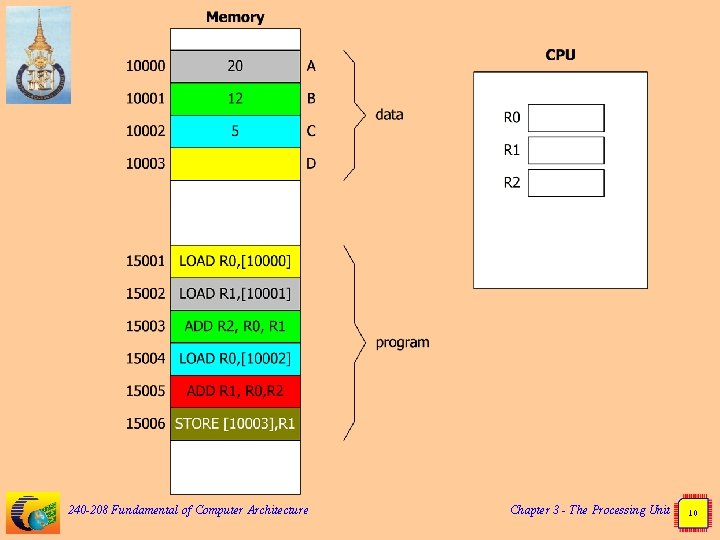

240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 10

Terminology u. IR : Instruction Register u. MAR : Memory Address Register 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 11

Instructions of CPU u. There are 4 types of instructions 1. Data transfer between memory and CPU registers 2. Arithmetic and Logic Operations on data 3. Program Sequencing and Control 4. I/O transfer 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 12

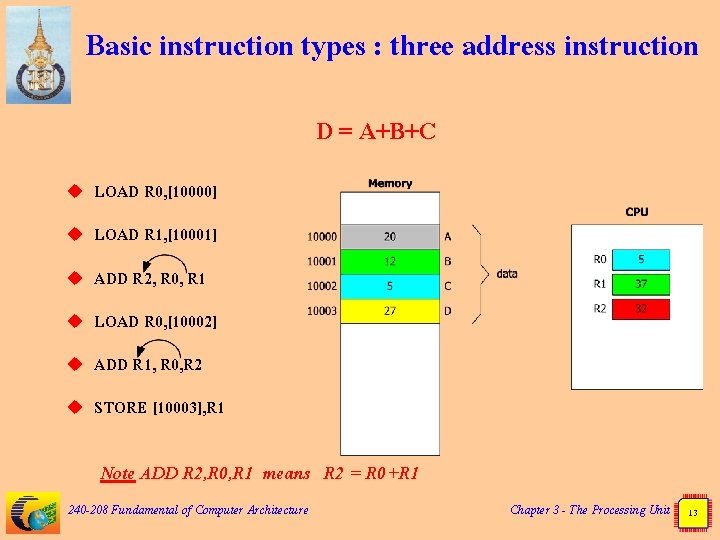

Basic instruction types : three address instruction D = A+B+C u LOAD R 0, [10000] u LOAD R 1, [10001] u ADD R 2, R 0, R 1 u LOAD R 0, [10002] u ADD R 1, R 0, R 2 u STORE [10003], R 1 Note ADD R 2, R 0, R 1 means R 2 = R 0+R 1 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 13

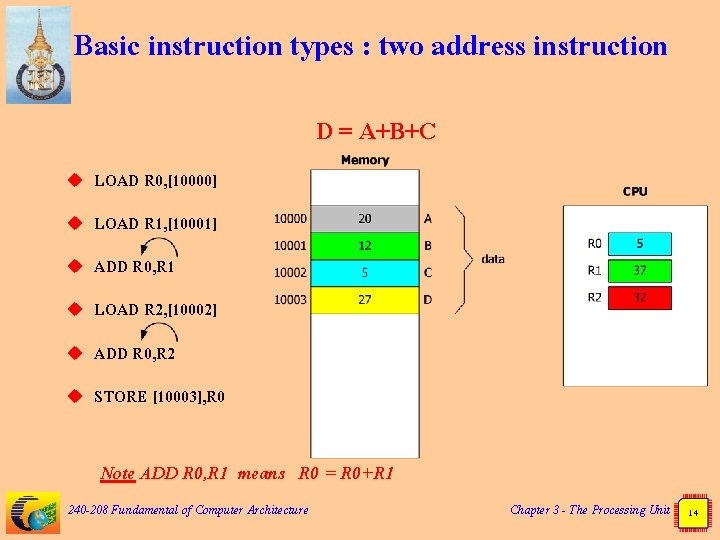

Basic instruction types : two address instruction D = A+B+C u LOAD R 0, [10000] u LOAD R 1, [10001] u ADD R 0, R 1 u LOAD R 2, [10002] u ADD R 0, R 2 u STORE [10003], R 0 Note ADD R 0, R 1 means R 0 = R 0+R 1 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 14

![Basic instruction types : one address instruction D = A+B+C u LOAD [10000] u Basic instruction types : one address instruction D = A+B+C u LOAD [10000] u](http://slidetodoc.com/presentation_image_h/9733d177e7114edd7269c7ad6a785843/image-15.jpg)

Basic instruction types : one address instruction D = A+B+C u LOAD [10000] u ADD [10001] u ADD [10002] u STORE [10003] Note ADD [10001] means Acc = Acc + [10001] 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 15

CPU registers u. General purpose registers u. R 0, R 1…Rn u. A, B, C, …. u. Special purpose register u. PC u. SP u. Accumulator u. Flag or Condition code 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 16

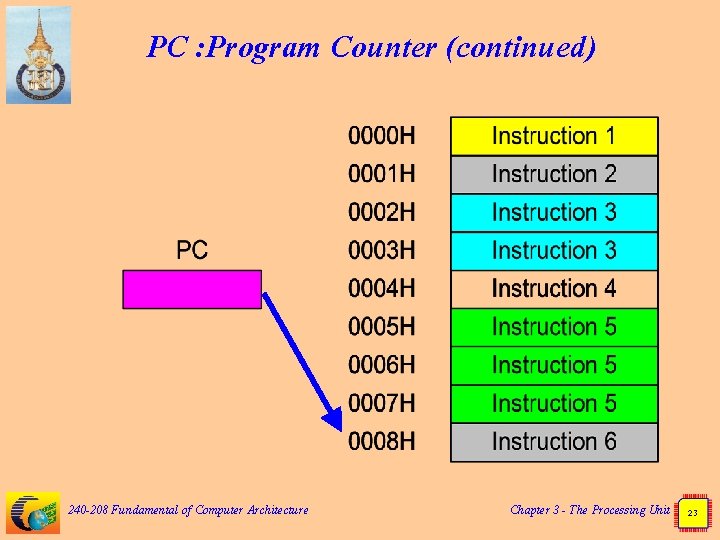

PC : Program Counter register u. Used to keep the next address of memory that CPU want to access u. PC and address-bus have the same size 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 17

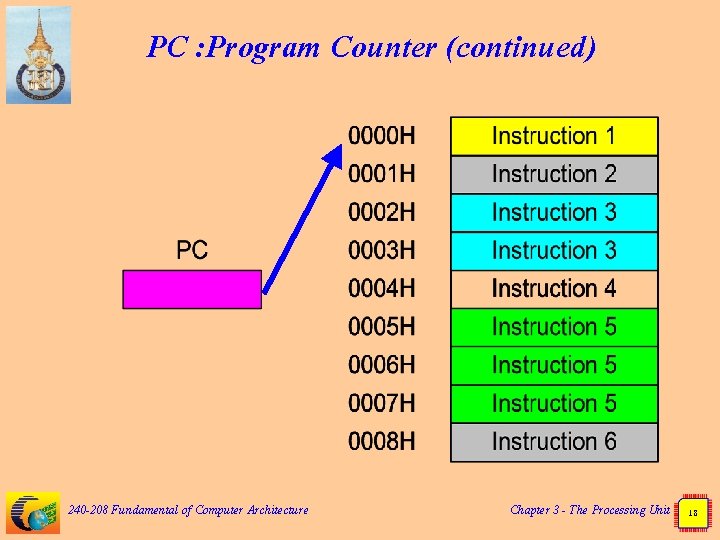

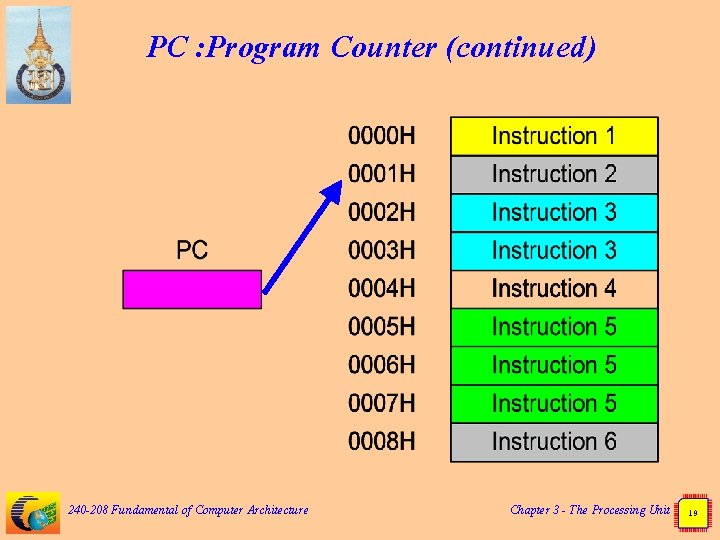

PC : Program Counter (continued) 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 18

PC : Program Counter (continued) 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 19

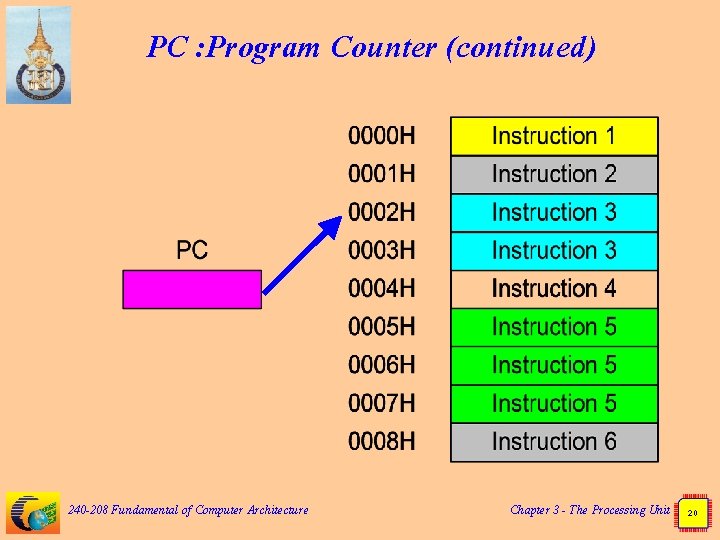

PC : Program Counter (continued) 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 20

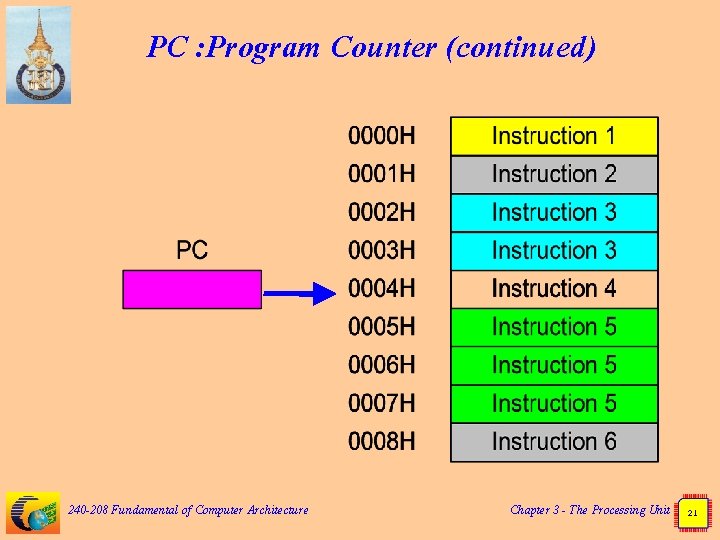

PC : Program Counter (continued) 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 21

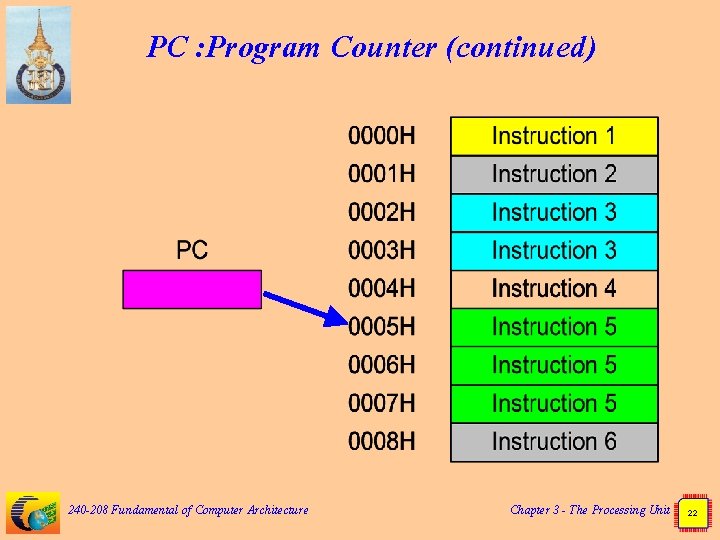

PC : Program Counter (continued) 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 22

PC : Program Counter (continued) 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 23

![Branching [25000] = [10000]+[10002]+[10003]+…. +[24999] LOC 35000: LOAD R 0, #0 LOAD R 1, Branching [25000] = [10000]+[10002]+[10003]+…. +[24999] LOC 35000: LOAD R 0, #0 LOAD R 1,](http://slidetodoc.com/presentation_image_h/9733d177e7114edd7269c7ad6a785843/image-24.jpg)

Branching [25000] = [10000]+[10002]+[10003]+…. +[24999] LOC 35000: LOAD R 0, #0 LOAD R 1, #14999 LOAD R 3, #10000 LOC 35003: LOAD R 2, [R 3] ADD R 0, R 2 INC R 3 DEC R 1 Branch_NZ LOC 35003 STORE [R 3], R 0 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 24

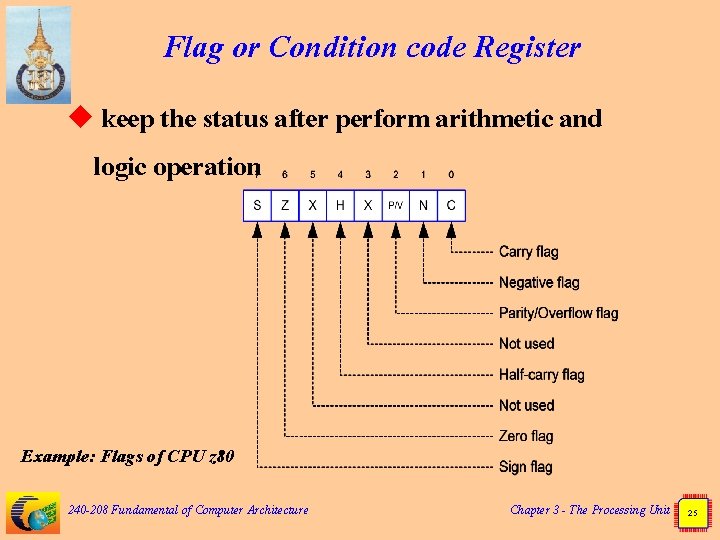

Flag or Condition code Register u keep the status after perform arithmetic and logic operation Example: Flags of CPU z 80 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 25

![Addressing modes of CPU u Immediate #value u Register Ri u Direct(absolute) [mem_loc] u Addressing modes of CPU u Immediate #value u Register Ri u Direct(absolute) [mem_loc] u](http://slidetodoc.com/presentation_image_h/9733d177e7114edd7269c7ad6a785843/image-26.jpg)

Addressing modes of CPU u Immediate #value u Register Ri u Direct(absolute) [mem_loc] u Register indirect [Ri] u Relative X[PC] u Index 240 -208 Fundamental of Computer Architecture load R 0, #00001 load R 0, R 1 load R 0, [100000] load R 0, [R 1] Chapter 3 - The Processing Unit 26

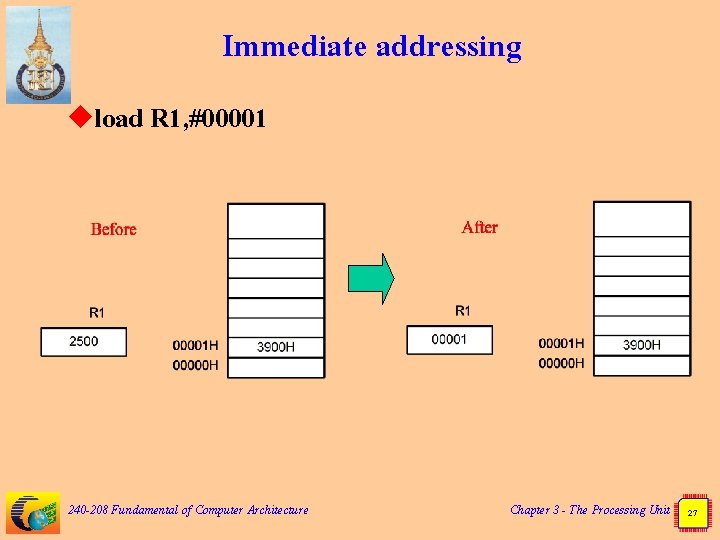

Immediate addressing uload R 1, #00001 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 27

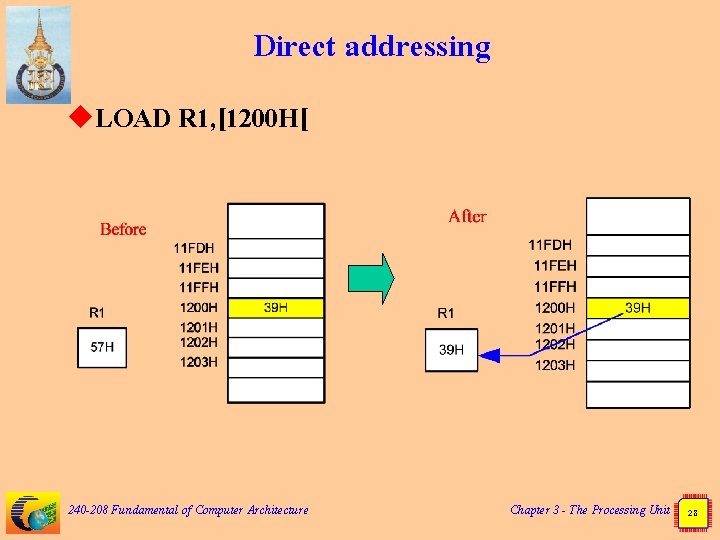

Direct addressing u. LOAD R 1, [1200 H[ 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 28

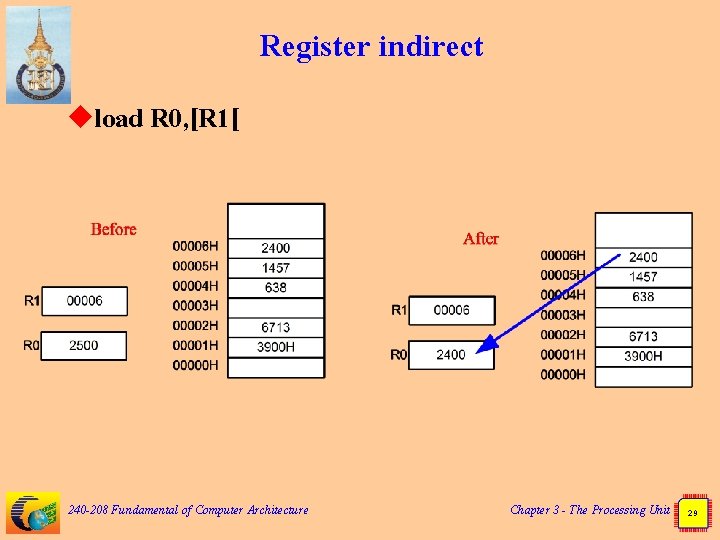

Register indirect uload R 0, [R 1[ 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 29

![Index addressing u. Use index register u. Effective address = X + [Ri] u. Index addressing u. Use index register u. Effective address = X + [Ri] u.](http://slidetodoc.com/presentation_image_h/9733d177e7114edd7269c7ad6a785843/image-30.jpg)

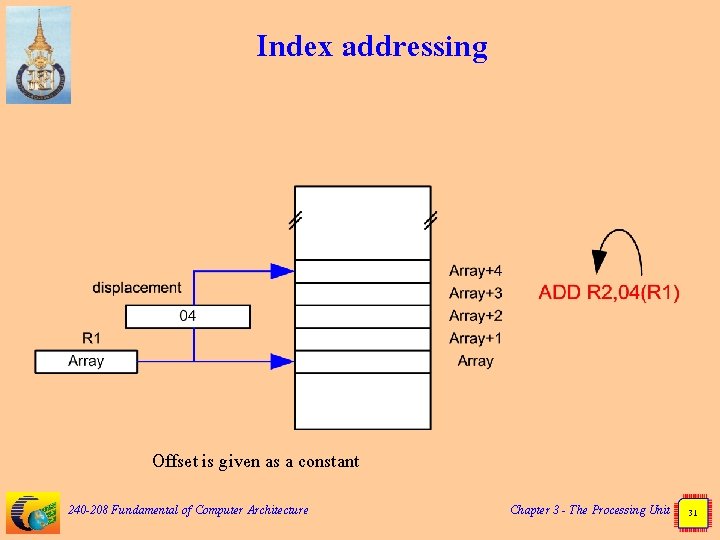

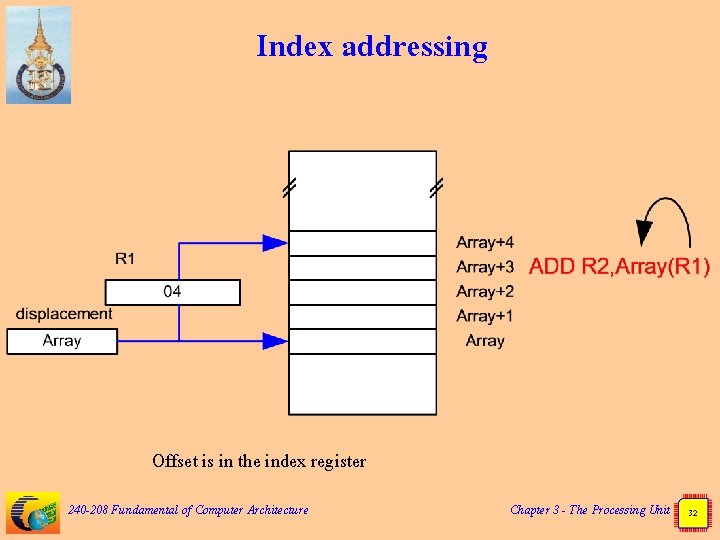

Index addressing u. Use index register u. Effective address = X + [Ri] u. When X = offset (or displacement) u. Ri = index register or Base register 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 30

Index addressing Offset is given as a constant 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 31

Index addressing Offset is in the index register 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 32

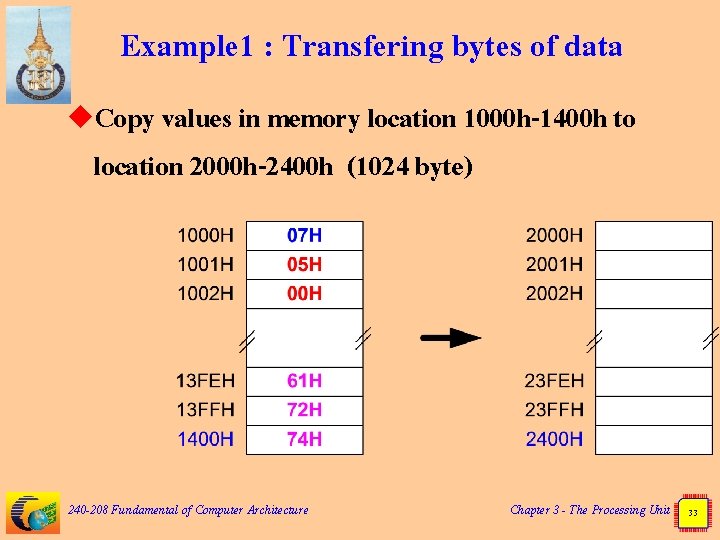

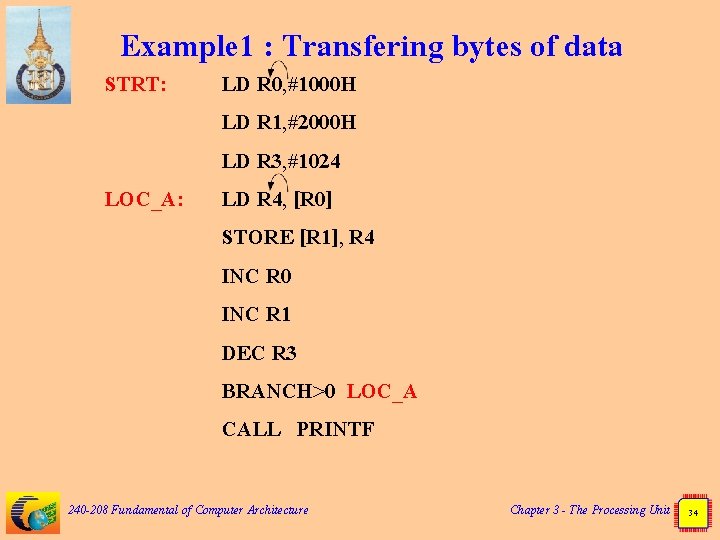

Example 1 : Transfering bytes of data u. Copy values in memory location 1000 h-1400 h to location 2000 h-2400 h (1024 byte) 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 33

Example 1 : Transfering bytes of data STRT: LOC_A: LD R 0, #1000 H LD R 1, #2000 H LD R 3, #1024 LD R 4, [R 0] STORE [R 1], R 4 INC R 0 INC R 1 DEC R 3 BRANCH>0 LOC_A CALL PRINTF 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 34

Example 2: Unsigned Multiplication by Repeated Addition u. Multiply 8 -bit unsigned number u. C = A*B 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 35

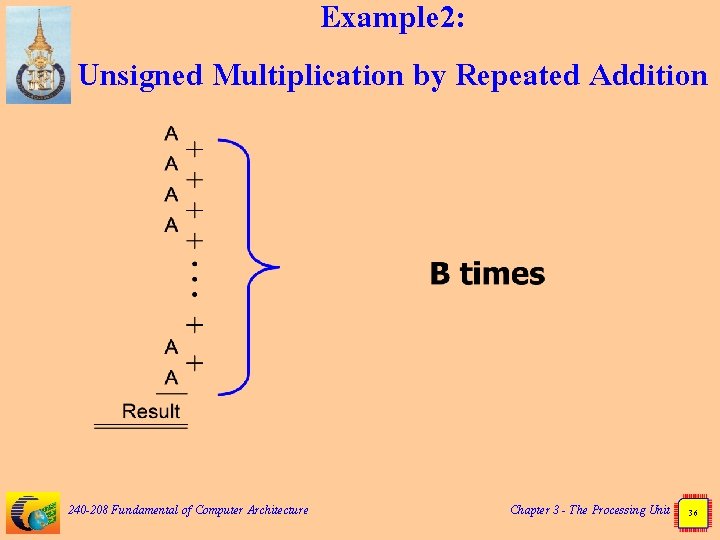

Example 2: Unsigned Multiplication by Repeated Addition 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 36

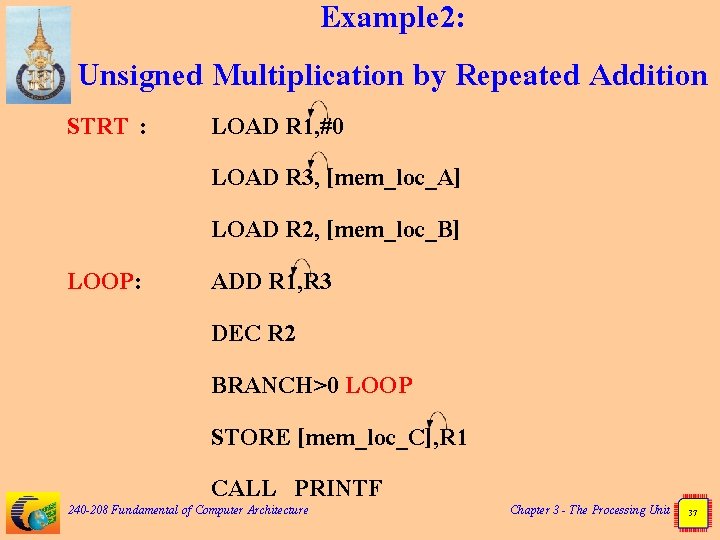

Example 2: Unsigned Multiplication by Repeated Addition STRT : LOOP: LOAD R 1, #0 LOAD R 3, [mem_loc_A] LOAD R 2, [mem_loc_B] ADD R 1, R 3 DEC R 2 BRANCH>0 LOOP STORE [mem_loc_C], R 1 CALL PRINTF 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 37

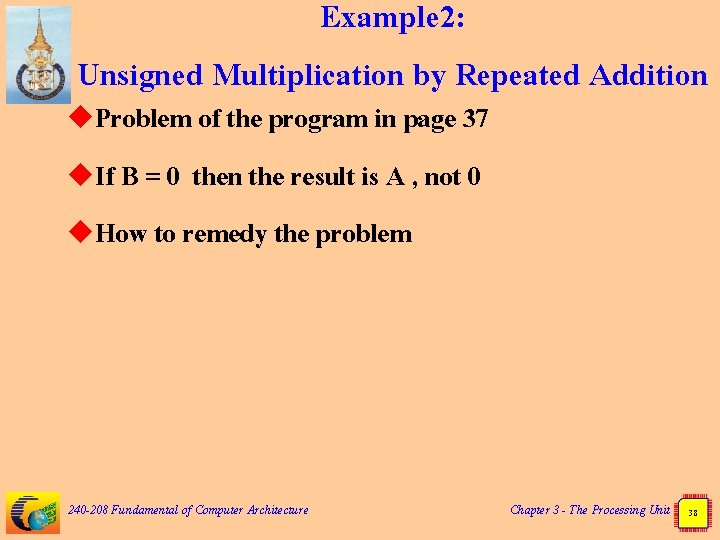

Example 2: Unsigned Multiplication by Repeated Addition u. Problem of the program in page 37 u. If B = 0 then the result is A , not 0 u. How to remedy the problem 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 38

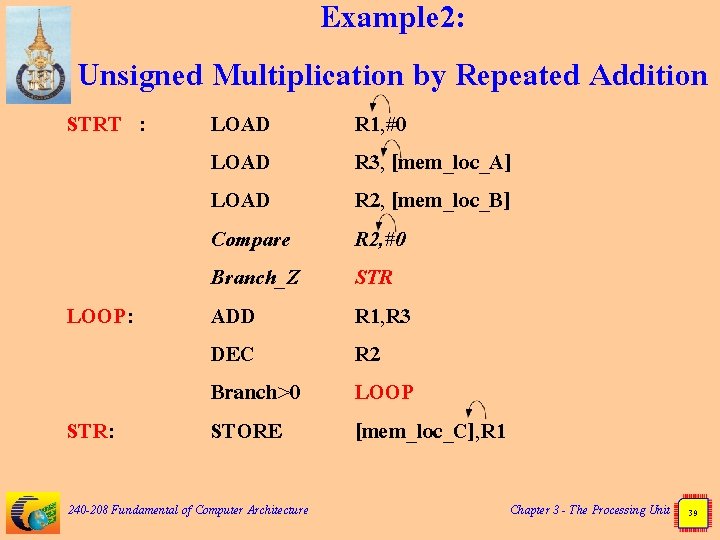

Example 2: Unsigned Multiplication by Repeated Addition STRT : LOOP: STR: LOAD Compare Branch_Z ADD DEC Branch>0 STORE 240 -208 Fundamental of Computer Architecture R 1, #0 R 3, [mem_loc_A] R 2, [mem_loc_B] R 2, #0 STR R 1, R 3 R 2 LOOP [mem_loc_C], R 1 Chapter 3 - The Processing Unit 39

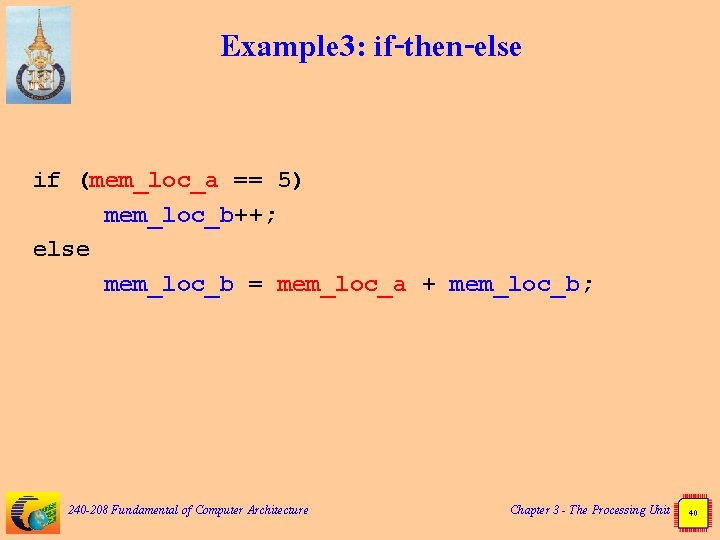

Example 3: if-then-else if (mem_loc_a == 5) mem_loc_b++; else mem_loc_b = mem_loc_a + mem_loc_b; 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 40

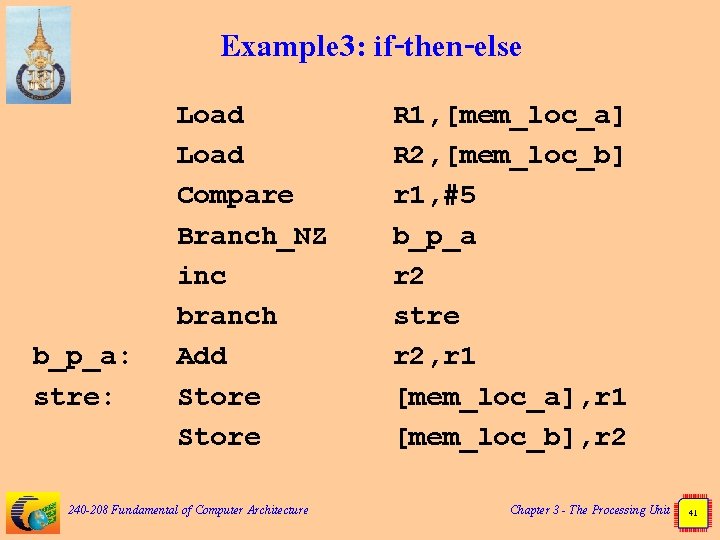

Example 3: if-then-else b_p_a: stre: Load Compare Branch_NZ inc branch Add Store 240 -208 Fundamental of Computer Architecture R 1, [mem_loc_a] R 2, [mem_loc_b] r 1, #5 b_p_a r 2 stre r 2, r 1 [mem_loc_a], r 1 [mem_loc_b], r 2 Chapter 3 - The Processing Unit 41

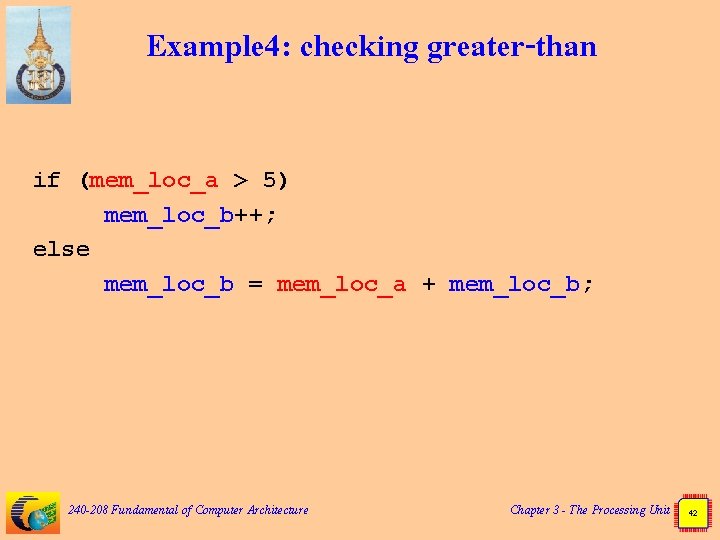

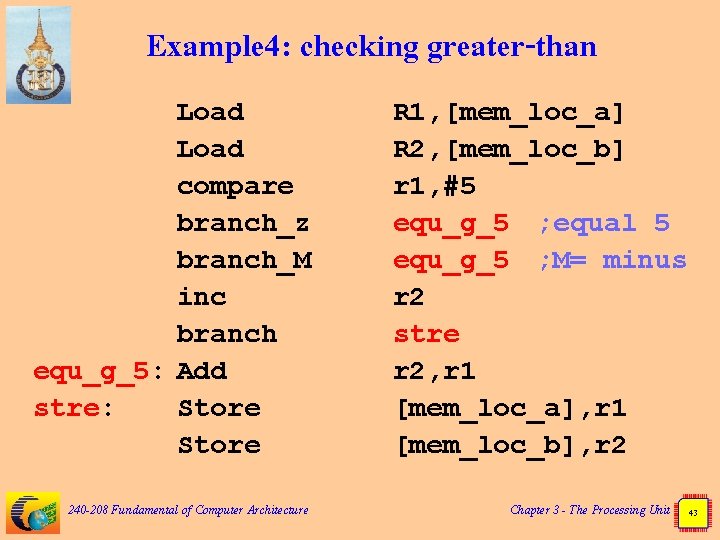

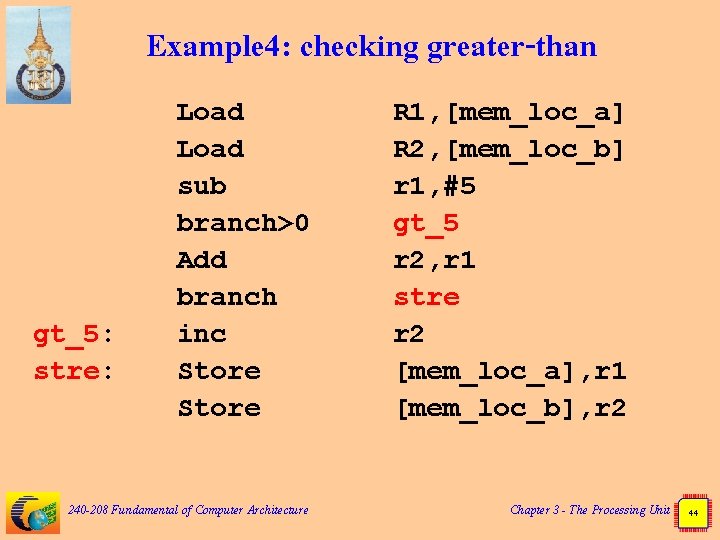

Example 4: checking greater-than if (mem_loc_a > 5) mem_loc_b++; else mem_loc_b = mem_loc_a + mem_loc_b; 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 42

Example 4: checking greater-than Load compare branch_z branch_M inc branch equ_g_5: Add stre: Store 240 -208 Fundamental of Computer Architecture R 1, [mem_loc_a] R 2, [mem_loc_b] r 1, #5 equ_g_5 ; equal 5 equ_g_5 ; M= minus r 2 stre r 2, r 1 [mem_loc_a], r 1 [mem_loc_b], r 2 Chapter 3 - The Processing Unit 43

Example 4: checking greater-than gt_5: stre: Load sub branch>0 Add branch inc Store 240 -208 Fundamental of Computer Architecture R 1, [mem_loc_a] R 2, [mem_loc_b] r 1, #5 gt_5 r 2, r 1 stre r 2 [mem_loc_a], r 1 [mem_loc_b], r 2 Chapter 3 - The Processing Unit 44

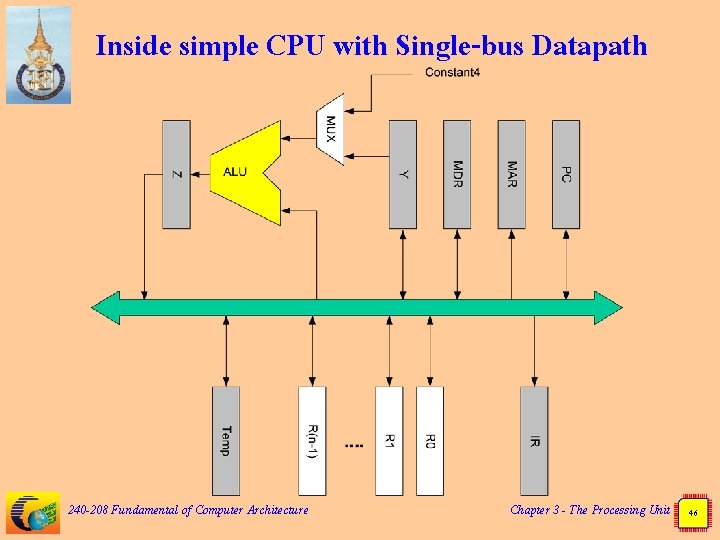

Basic processing unit uthe structure of simple CPU u. How the internal parts of CPU work u. How to design the simple processor u. Datapath u. Control Unit 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 45

Inside simple CPU with Single-bus Datapath 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 46

Single-bus CPU architecture u 32 -bit CPU u 16 instructions u. Fixed length instruction format u 32 general purpose registers(R 0 -R 31( 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 47

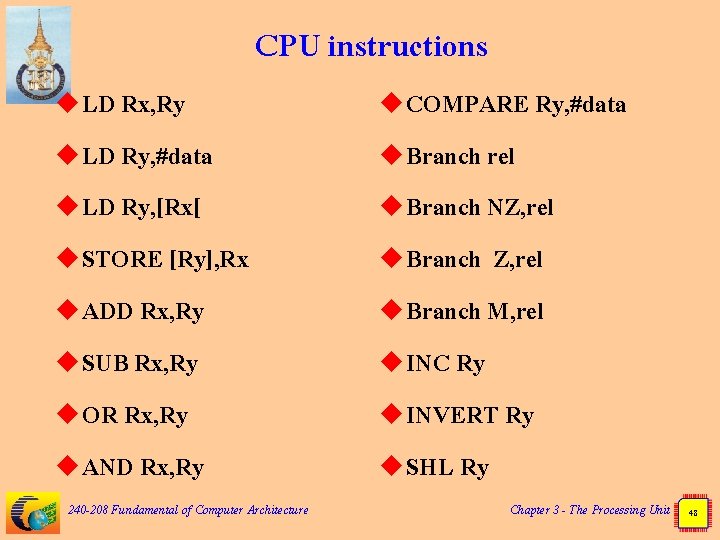

CPU instructions u LD Rx, Ry u COMPARE Ry, #data u LD Ry, #data u Branch rel u LD Ry, [Rx[ u Branch NZ, rel u STORE [Ry], Rx u Branch u ADD Rx, Ry u SUB Rx, Ry u OR Rx, Ry u AND Rx, Ry 240 -208 Fundamental of Computer Architecture Z, rel u Branch M, rel u INC Ry u INVERT Ry u SHL Ry Chapter 3 - The Processing Unit 48

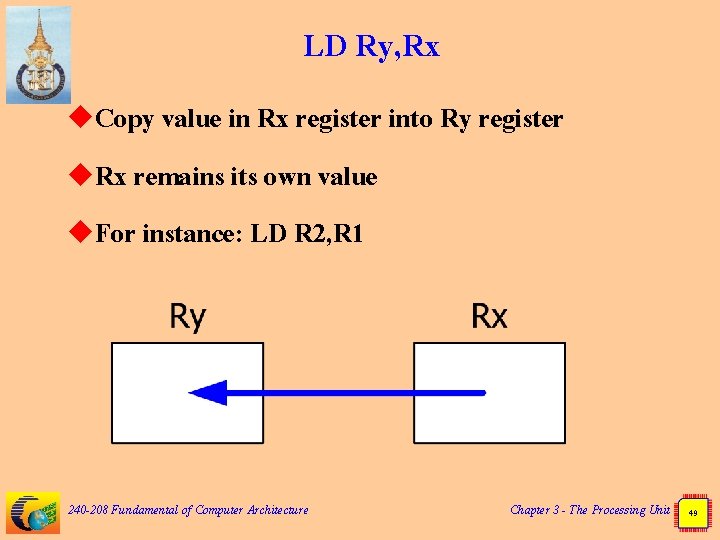

LD Ry, Rx u. Copy value in Rx register into Ry register u. Rx remains its own value u. For instance: LD R 2, R 1 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 49

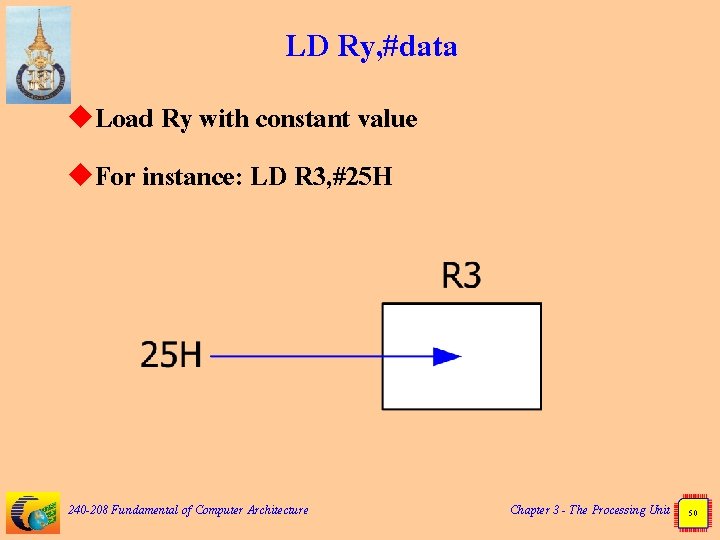

LD Ry, #data u. Load Ry with constant value u. For instance: LD R 3, #25 H 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 50

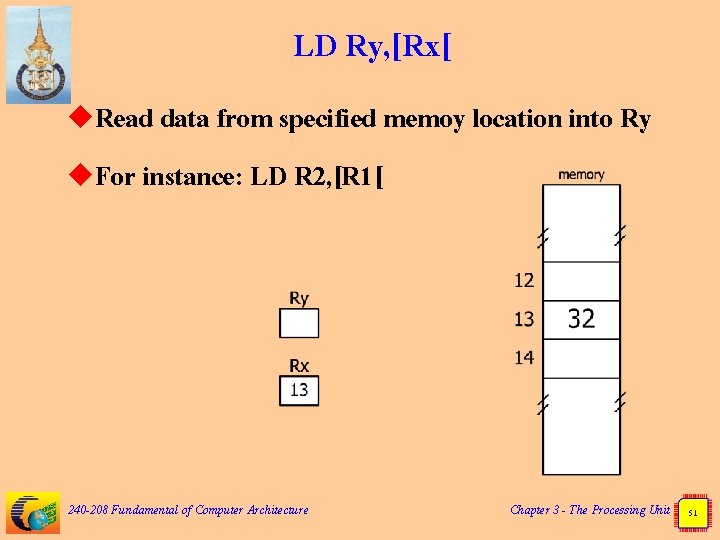

LD Ry, [Rx[ u. Read data from specified memoy location into Ry u. For instance: LD R 2, [R 1[ 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 51

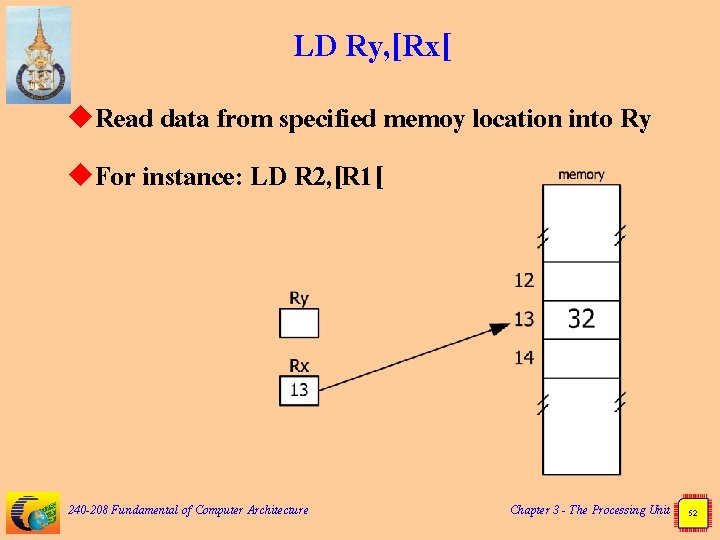

LD Ry, [Rx[ u. Read data from specified memoy location into Ry u. For instance: LD R 2, [R 1[ 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 52

LD Ry, [Rx[ u. Read data from specified memoy location into Ry u. For instance: LD R 2, [R 1[ 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 53

![STORE [Ry], Rx u. Copy data in Rx register into memory location pointed by STORE [Ry], Rx u. Copy data in Rx register into memory location pointed by](http://slidetodoc.com/presentation_image_h/9733d177e7114edd7269c7ad6a785843/image-54.jpg)

STORE [Ry], Rx u. Copy data in Rx register into memory location pointed by Ry register u. For instance: STORE [R 6], R 1 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 54

![STORE [Ry], Rx u. Copy data in Rx register into memory location pointed by STORE [Ry], Rx u. Copy data in Rx register into memory location pointed by](http://slidetodoc.com/presentation_image_h/9733d177e7114edd7269c7ad6a785843/image-55.jpg)

STORE [Ry], Rx u. Copy data in Rx register into memory location pointed by Ry register u. For instance: STORE [R 6], R 1 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 55

![STORE [Ry], Rx u. Copy data in Rx register into memory location pointed by STORE [Ry], Rx u. Copy data in Rx register into memory location pointed by](http://slidetodoc.com/presentation_image_h/9733d177e7114edd7269c7ad6a785843/image-56.jpg)

STORE [Ry], Rx u. Copy data in Rx register into memory location pointed by Ry register u. For instance: STORE [R 6], R 1 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 56

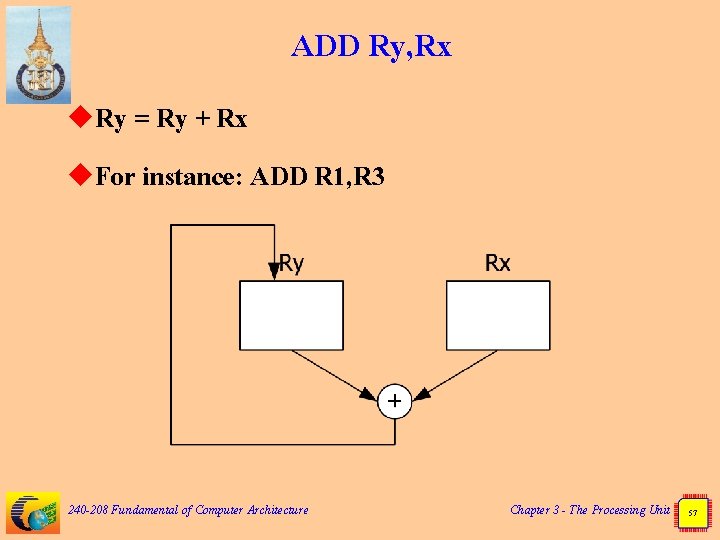

ADD Ry, Rx u. Ry = Ry + Rx u. For instance: ADD R 1, R 3 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 57

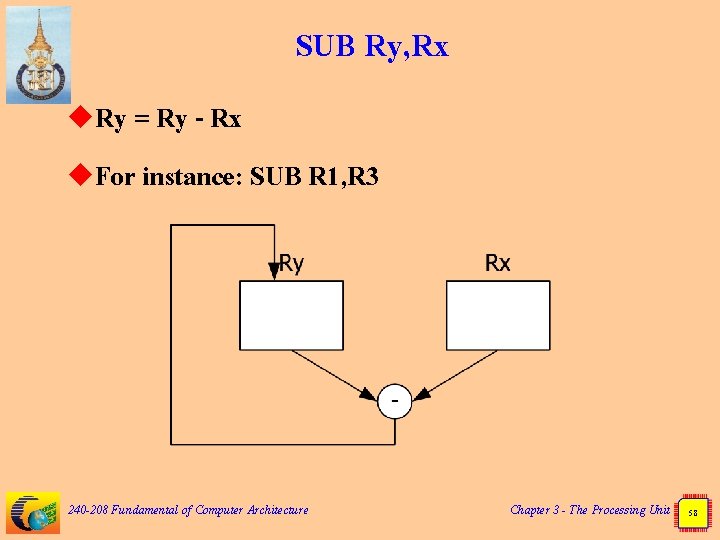

SUB Ry, Rx u. Ry = Ry - Rx u. For instance: SUB R 1, R 3 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 58

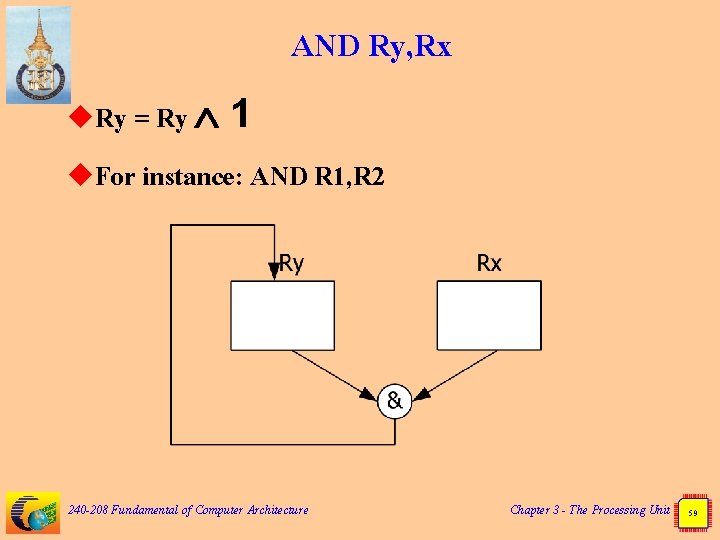

AND Ry, Rx u. Ry = Ry 1 u. For instance: AND R 1, R 2 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 59

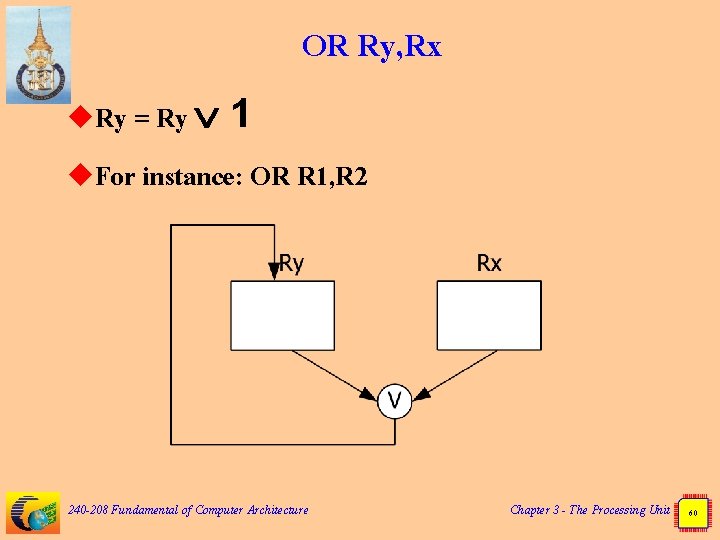

OR Ry, Rx u. Ry = Ry 1 u. For instance: OR R 1, R 2 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 60

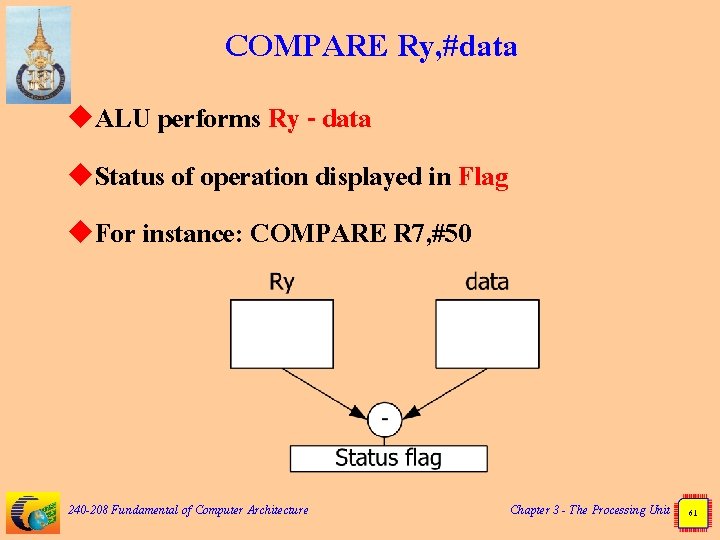

COMPARE Ry, #data u. ALU performs Ry - data u. Status of operation displayed in Flag u. For instance: COMPARE R 7, #50 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 61

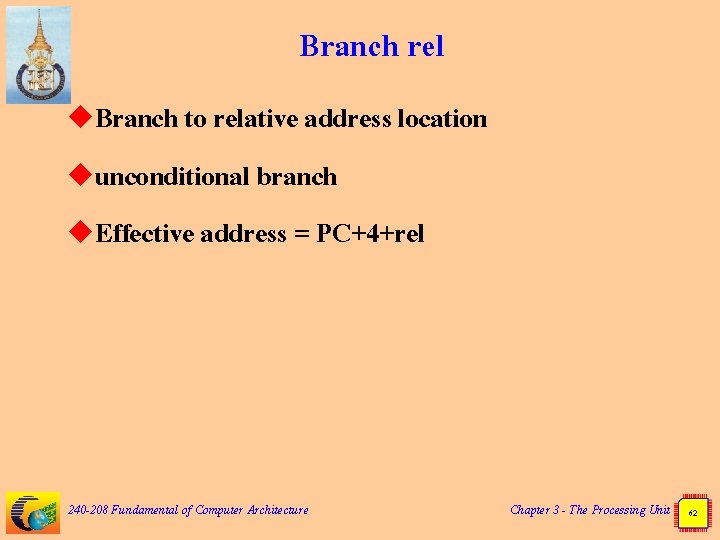

Branch rel u. Branch to relative address location uunconditional branch u. Effective address = PC+4+rel 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 62

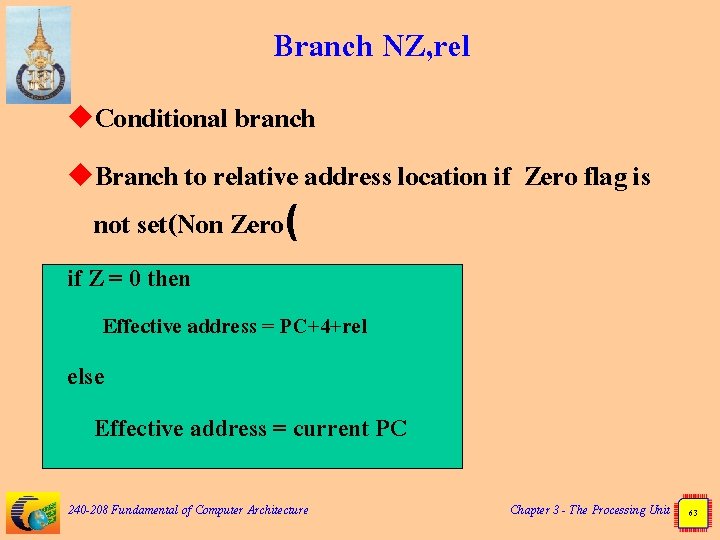

Branch NZ, rel u. Conditional branch u. Branch to relative address location if not set(Non Zero( Zero flag is if Z = 0 then Effective address = PC+4+rel else Effective address = current PC 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 63

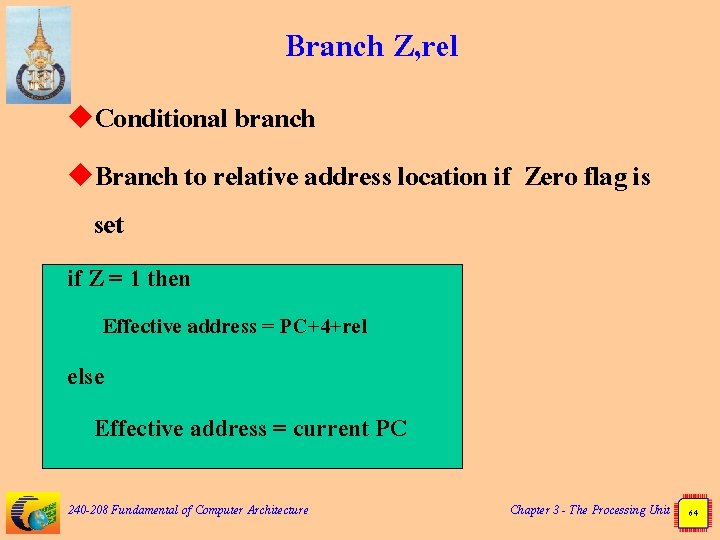

Branch Z, rel u. Conditional branch u. Branch to relative address location if set Zero flag is if Z = 1 then Effective address = PC+4+rel else Effective address = current PC 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 64

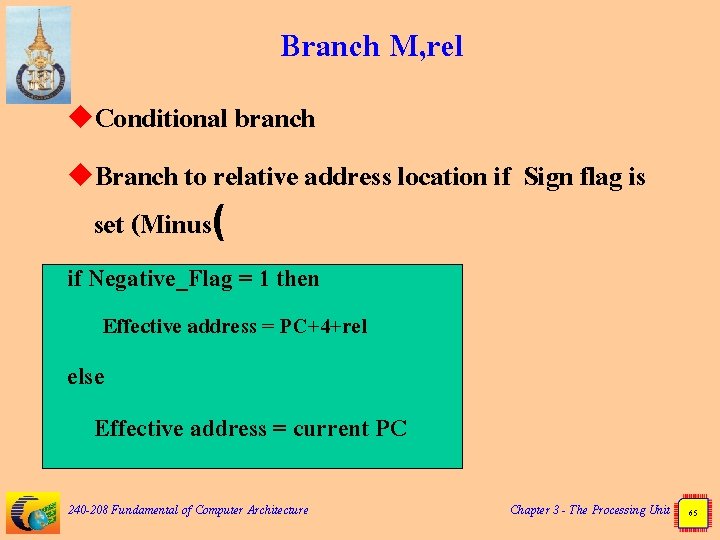

Branch M, rel u. Conditional branch u. Branch to relative address location if set (Minus( Sign flag is if Negative_Flag = 1 then Effective address = PC+4+rel else Effective address = current PC 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 65

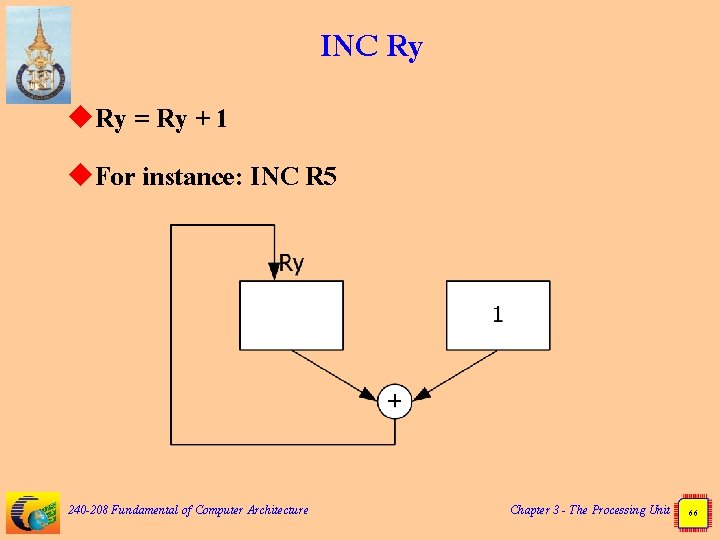

INC Ry u. Ry = Ry + 1 u. For instance: INC R 5 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 66

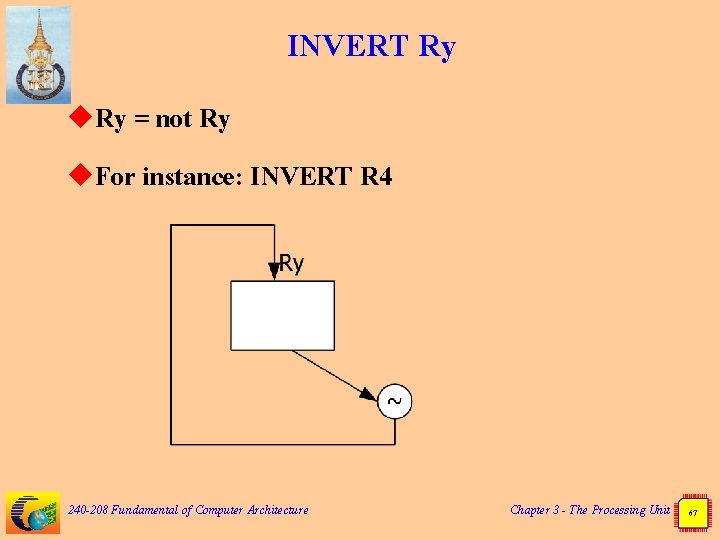

INVERT Ry u. Ry = not Ry u. For instance: INVERT R 4 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 67

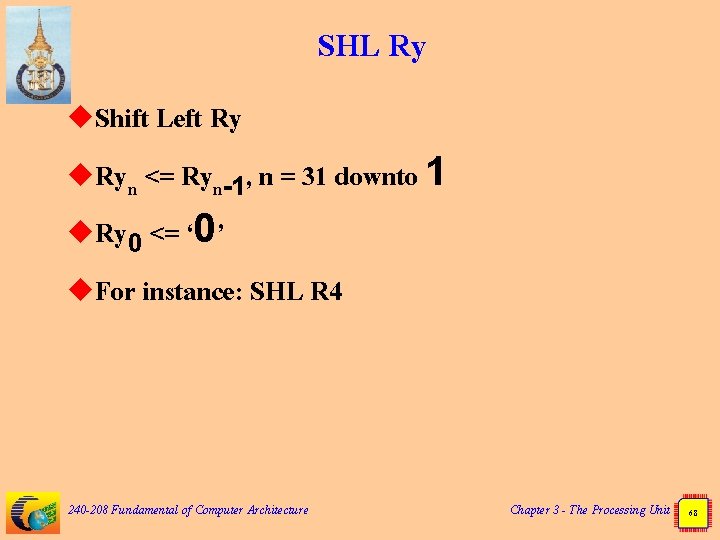

SHL Ry u. Shift Left Ry u. Ryn <= Ryn-1, n = 31 downto 1 u. Ry 0 <= ‘ 0’ u. For instance: SHL R 4 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 68

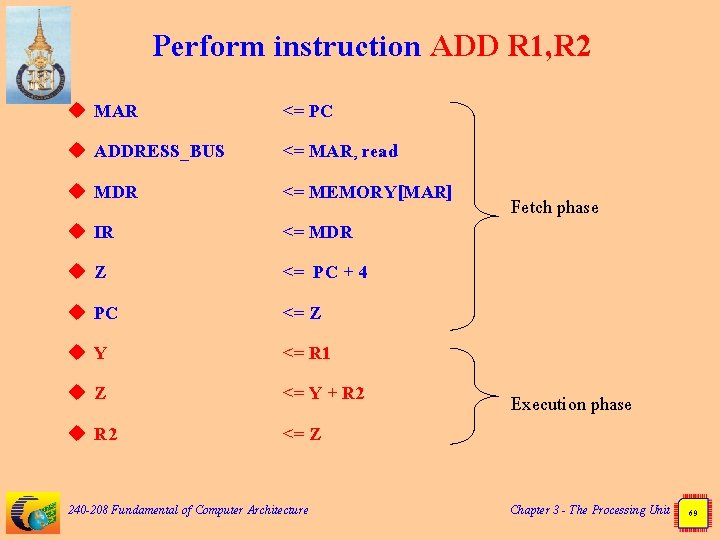

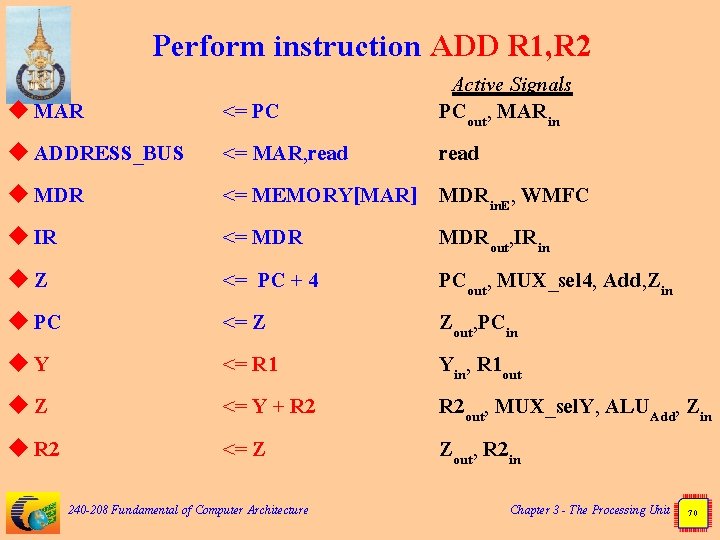

Perform instruction ADD R 1, R 2 MAR u ADDRESS_BUS u MDR u IR u. Z u PC u. Y u. Z u R 2 u <= PC <= MAR, read <= MEMORY[MAR] <= MDR <= PC + 4 <= Z <= R 1 <= Y + R 2 <= Z 240 -208 Fundamental of Computer Architecture Fetch phase Execution phase Chapter 3 - The Processing Unit 69

Perform instruction ADD R 1, R 2 u MAR u ADDRESS_BUS u MDR u IR u. Z u PC u. Y u. Z u R 2 Active Signals <= PC PCout, MARin <= MAR, read <= MEMORY[MAR] MDRin. E, WMFC <= MDRout, IRin <= PC + 4 PCout, MUX_sel 4, Add, Zin <= Z Zout, PCin <= R 1 Yin, R 1 out <= Y + R 2 out, MUX_sel. Y, ALUAdd, Zin <= Z Zout, R 2 in 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 70

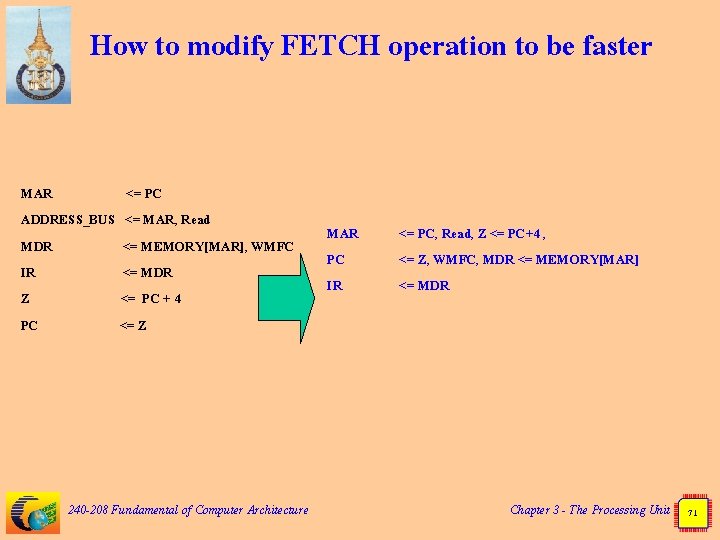

How to modify FETCH operation to be faster MAR <= PC ADDRESS_BUS <= MAR, Read MDR <= MEMORY[MAR], WMFC IR <= MDR Z <= PC + 4 PC <= Z 240 -208 Fundamental of Computer Architecture MAR PC IR <= PC, Read, Z <= PC+4 , <= Z, WMFC, MDR <= MEMORY[MAR] <= MDR Chapter 3 - The Processing Unit 71

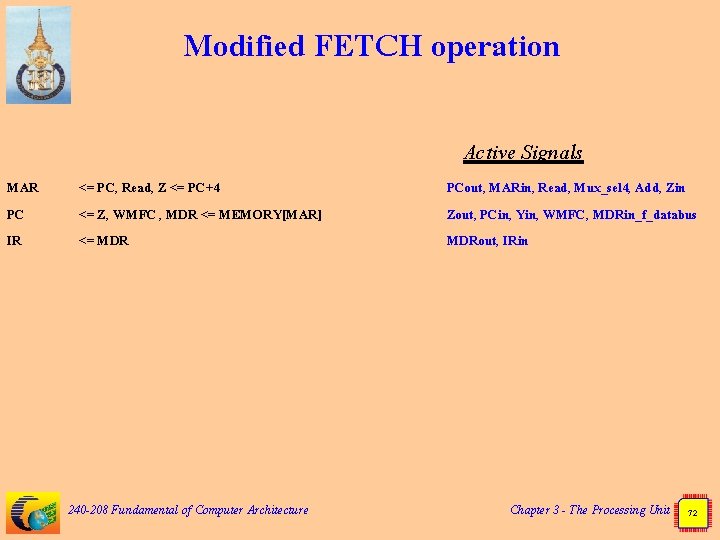

Modified FETCH operation Active Signals MAR PC IR <= PC, Read, Z <= PC+4 <= Z, WMFC , MDR <= MEMORY[MAR] <= MDR 240 -208 Fundamental of Computer Architecture PCout, MARin, Read, Mux_sel 4, Add, Zin Zout, PCin, Yin, WMFC, MDRin_f_databus MDRout, IRin Chapter 3 - The Processing Unit 72

![Perform instruction LD R 1, [R 2] MAR <= PC, Read, Z <= PC+4 Perform instruction LD R 1, [R 2] MAR <= PC, Read, Z <= PC+4](http://slidetodoc.com/presentation_image_h/9733d177e7114edd7269c7ad6a785843/image-73.jpg)

Perform instruction LD R 1, [R 2] MAR <= PC, Read, Z <= PC+4 u PC <= Z, WMFC, MDR <= MEMORY[MAR] u IR <= MDR u u MAR ADDRESS_BUS R 1 <= R 2 <= MAR, MDR <= MEMORY[MAR] <= MDR 240 -208 Fundamental of Computer Architecture Fetch phase Execution phase Chapter 3 - The Processing Unit 73

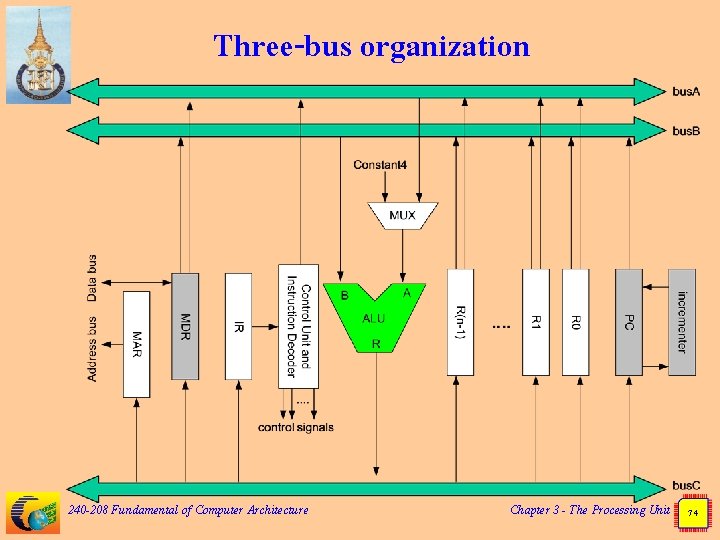

Three-bus organization 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 74

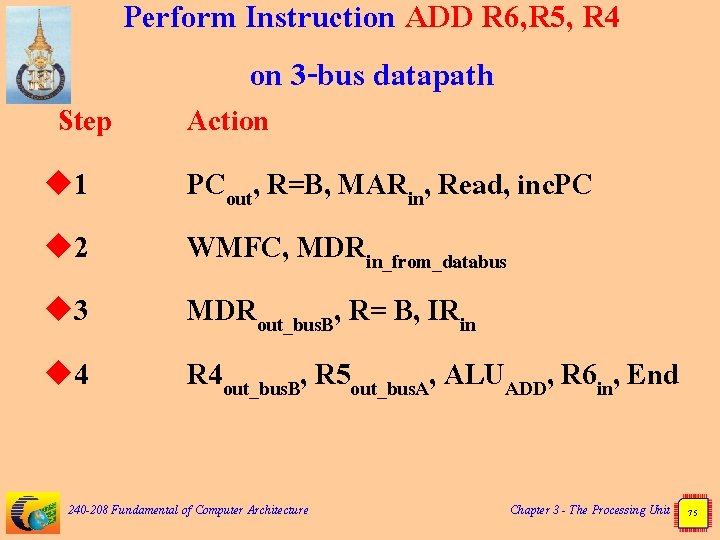

Step u 1 u 2 u 3 u 4 Perform Instruction ADD R 6, R 5, R 4 on 3 -bus datapath Action PCout, R=B, MARin, Read, inc. PC WMFC, MDRin_from_databus MDRout_bus. B, R= B, IRin R 4 out_bus. B, R 5 out_bus. A, ALUADD, R 6 in, End 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 75

Control Units u 2 types of Control units u. Hardwired u. Microprogrammed 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 76

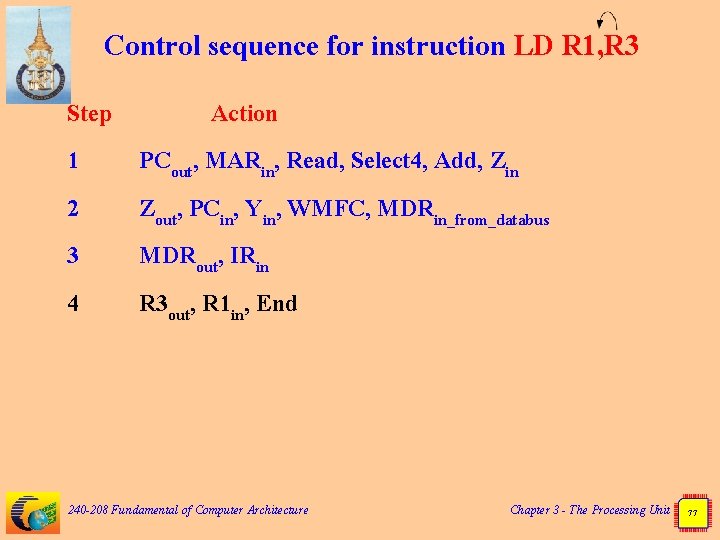

Control sequence for instruction LD R 1, R 3 Step 1 2 3 4 Action PCout, MARin, Read, Select 4, Add, Zin Zout, PCin, Yin, WMFC, MDRin_from_databus MDRout, IRin R 3 out, R 1 in, End 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 77

![Control sequence for instruction LD R 1, [R 3] Step 1 2 3 4 Control sequence for instruction LD R 1, [R 3] Step 1 2 3 4](http://slidetodoc.com/presentation_image_h/9733d177e7114edd7269c7ad6a785843/image-78.jpg)

Control sequence for instruction LD R 1, [R 3] Step 1 2 3 4 5 6 Action PCout, MARin, Read, Select 4, Add, Zin Zout, PCin, Yin, WMFC, MDRin_from_databus MDRout, IRin R 3 out, MARin, Read MDRin_f_databus, WMFC MDRout, R 1 in , End 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 78

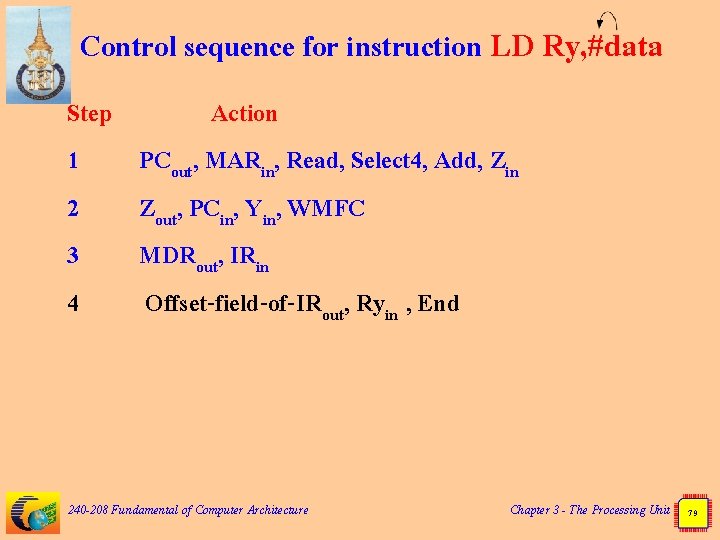

Control sequence for instruction LD Ry, #data Step 1 2 3 4 Action PCout, MARin, Read, Select 4, Add, Zin Zout, PCin, Yin, WMFC MDRout, IRin Offset-field-of-IRout, Ryin , End 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 79

![Control sequence for STORE [Ry], Rx instruction Step 1 2 3 4 5 6 Control sequence for STORE [Ry], Rx instruction Step 1 2 3 4 5 6](http://slidetodoc.com/presentation_image_h/9733d177e7114edd7269c7ad6a785843/image-80.jpg)

Control sequence for STORE [Ry], Rx instruction Step 1 2 3 4 5 6 Action PCout, MARin, Read, Select 4, Add, Zin Zout, PCin, Yin, WMFC MDRout, IRin Ryout, MARin Rxout, MDRin_f_internalbus Write, WMFC, End 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 80

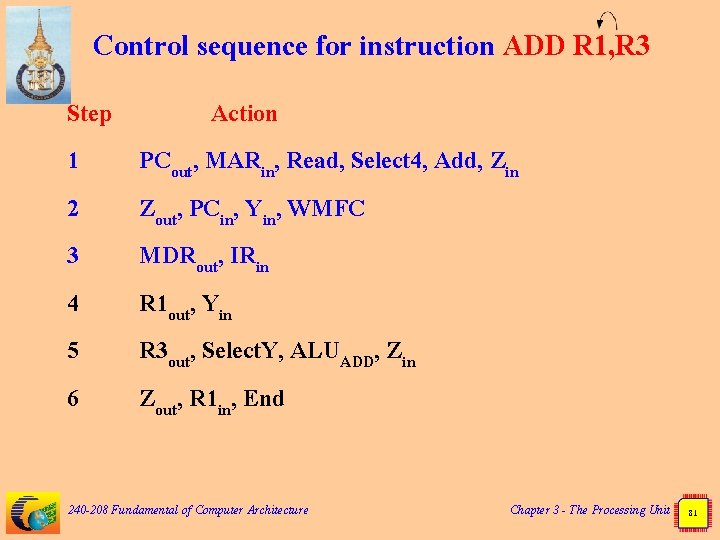

Control sequence for instruction ADD R 1, R 3 Step 1 2 3 4 5 6 Action PCout, MARin, Read, Select 4, Add, Zin Zout, PCin, Yin, WMFC MDRout, IRin R 1 out, Yin R 3 out, Select. Y, ALUADD, Zin Zout, R 1 in, End 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 81

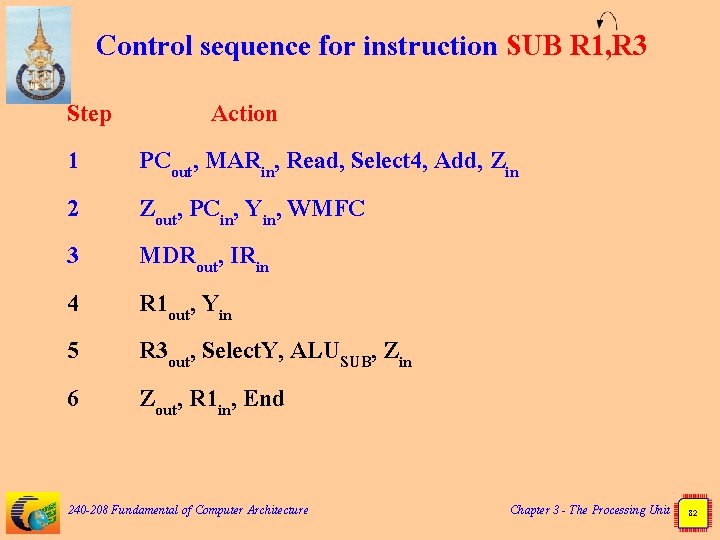

Control sequence for instruction SUB R 1, R 3 Step 1 2 3 4 5 6 Action PCout, MARin, Read, Select 4, Add, Zin Zout, PCin, Yin, WMFC MDRout, IRin R 1 out, Yin R 3 out, Select. Y, ALUSUB, Zin Zout, R 1 in, End 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 82

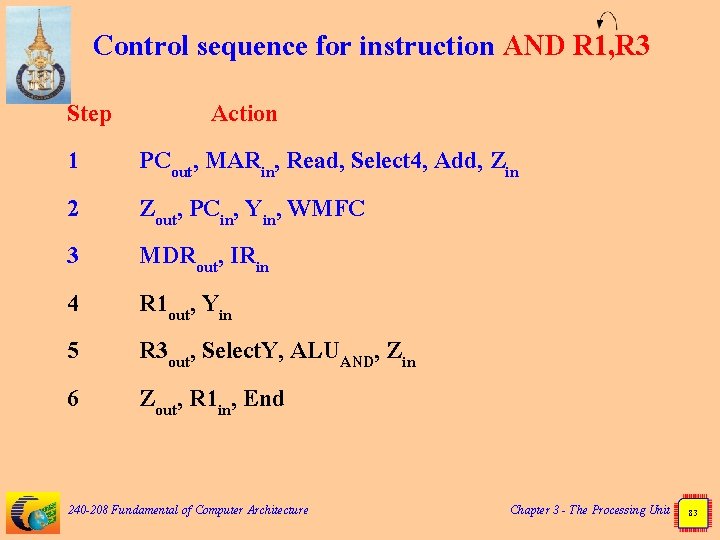

Control sequence for instruction AND R 1, R 3 Step 1 2 3 4 5 6 Action PCout, MARin, Read, Select 4, Add, Zin Zout, PCin, Yin, WMFC MDRout, IRin R 1 out, Yin R 3 out, Select. Y, ALUAND, Zin Zout, R 1 in, End 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 83

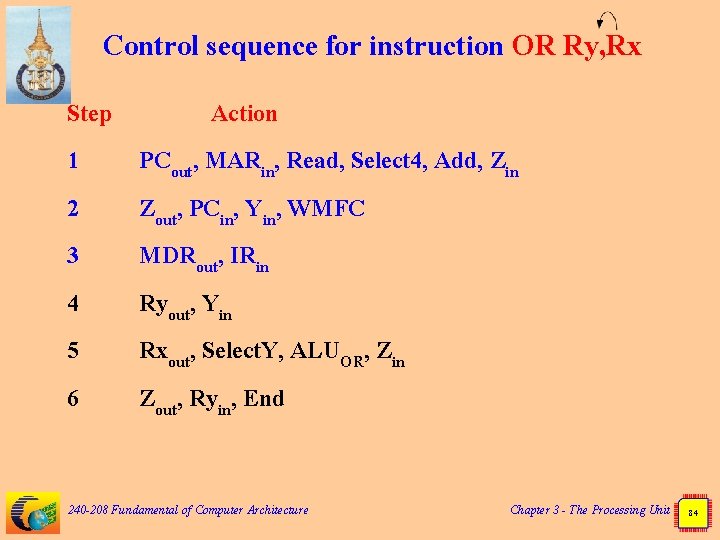

Control sequence for instruction OR Ry, Rx Step 1 2 3 4 5 6 Action PCout, MARin, Read, Select 4, Add, Zin Zout, PCin, Yin, WMFC MDRout, IRin Ryout, Yin Rxout, Select. Y, ALUOR, Zin Zout, Ryin, End 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 84

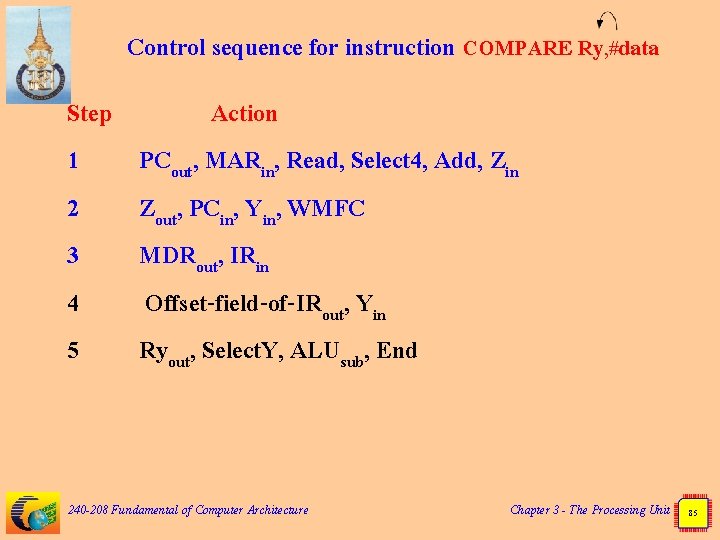

Control sequence for instruction COMPARE Ry, #data Step 1 2 3 4 5 Action PCout, MARin, Read, Select 4, Add, Zin Zout, PCin, Yin, WMFC MDRout, IRin Offset-field-of-IRout, Yin Ryout, Select. Y, ALUsub, End 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 85

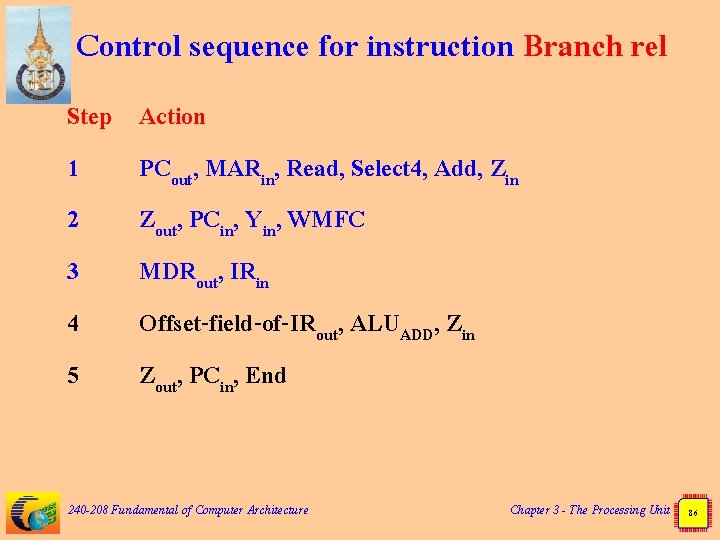

Control sequence for instruction Branch rel Step 1 2 3 4 5 Action PCout, MARin, Read, Select 4, Add, Zin Zout, PCin, Yin, WMFC MDRout, IRin Offset-field-of-IRout, ALUADD, Zin Zout, PCin, End 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 86

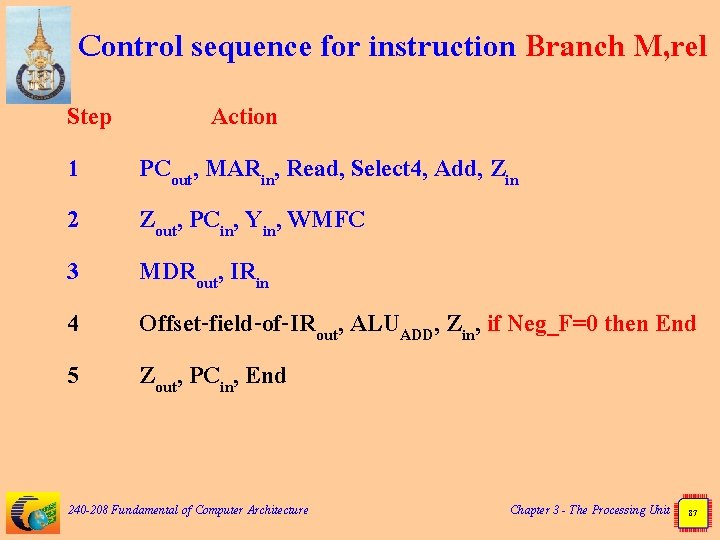

Control sequence for instruction Branch M, rel Step 1 2 3 4 5 Action PCout, MARin, Read, Select 4, Add, Zin Zout, PCin, Yin, WMFC MDRout, IRin Offset-field-of-IRout, ALUADD, Zin, if Neg_F=0 then End Zout, PCin, End 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 87

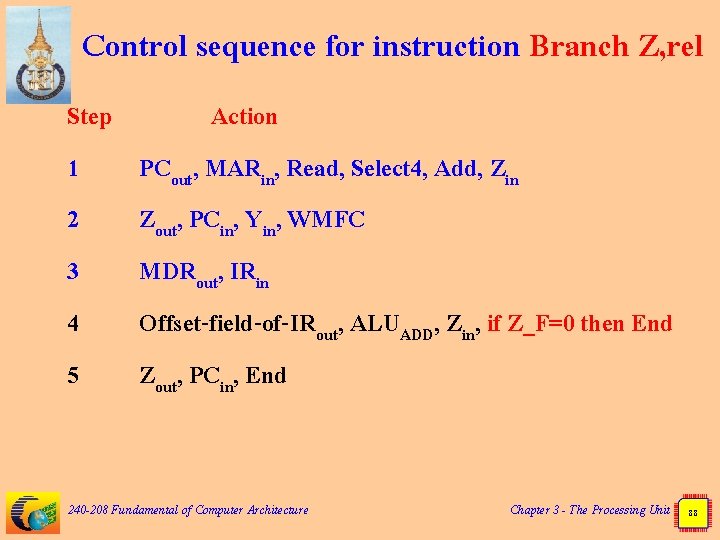

Control sequence for instruction Branch Z, rel Step 1 2 3 4 5 Action PCout, MARin, Read, Select 4, Add, Zin Zout, PCin, Yin, WMFC MDRout, IRin Offset-field-of-IRout, ALUADD, Zin, if Z_F=0 then End Zout, PCin, End 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 88

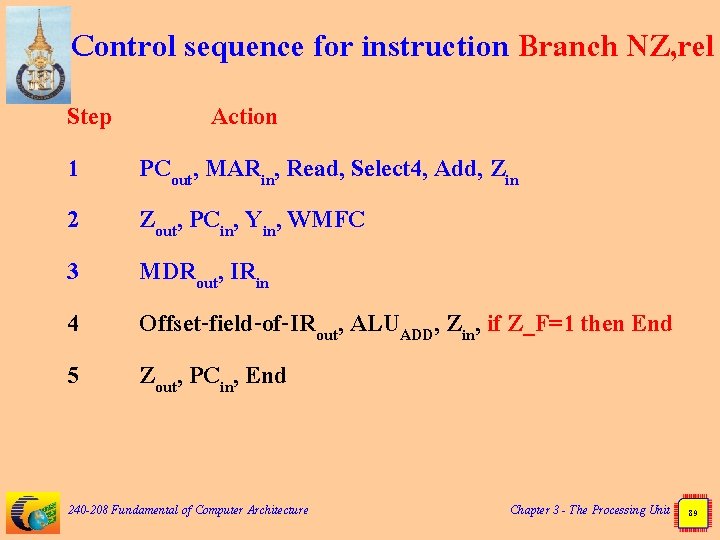

Control sequence for instruction Branch NZ, rel Step 1 2 3 4 5 Action PCout, MARin, Read, Select 4, Add, Zin Zout, PCin, Yin, WMFC MDRout, IRin Offset-field-of-IRout, ALUADD, Zin, if Z_F=1 then End Zout, PCin, End 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 89

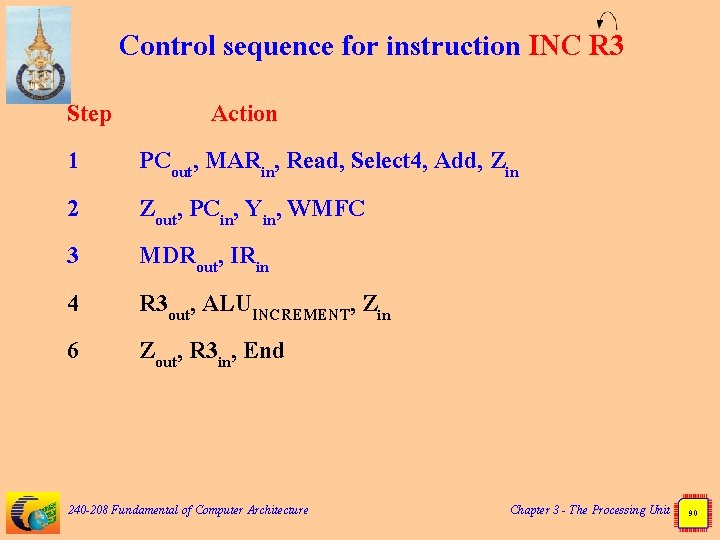

Control sequence for instruction INC R 3 Step 1 2 3 4 6 Action PCout, MARin, Read, Select 4, Add, Zin Zout, PCin, Yin, WMFC MDRout, IRin R 3 out, ALUINCREMENT, Zin Zout, R 3 in, End 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 90

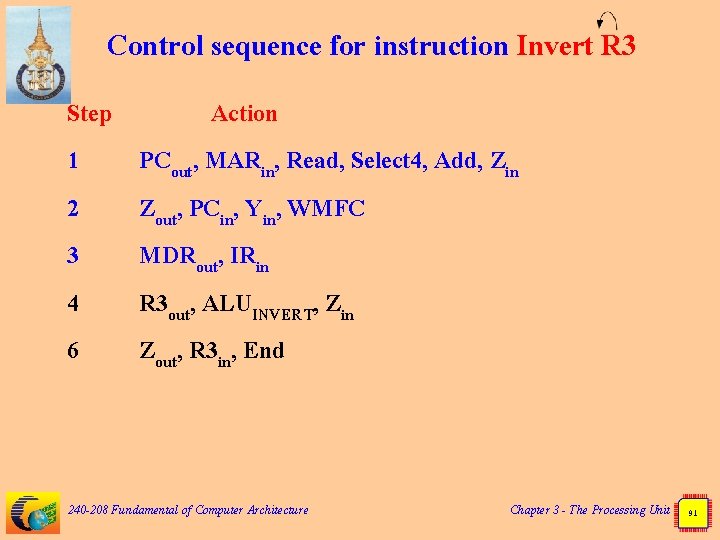

Control sequence for instruction Invert R 3 Step 1 2 3 4 6 Action PCout, MARin, Read, Select 4, Add, Zin Zout, PCin, Yin, WMFC MDRout, IRin R 3 out, ALUINVERT, Zin Zout, R 3 in, End 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 91

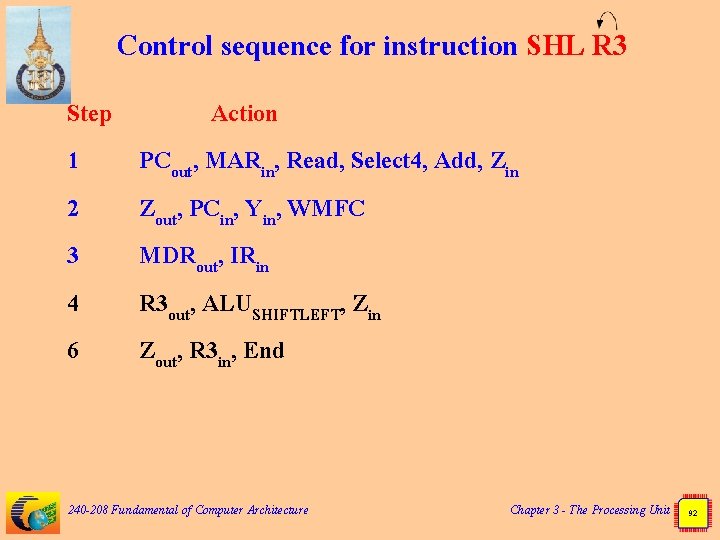

Control sequence for instruction SHL R 3 Step 1 2 3 4 6 Action PCout, MARin, Read, Select 4, Add, Zin Zout, PCin, Yin, WMFC MDRout, IRin R 3 out, ALUSHIFTLEFT, Zin Zout, R 3 in, End 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 92

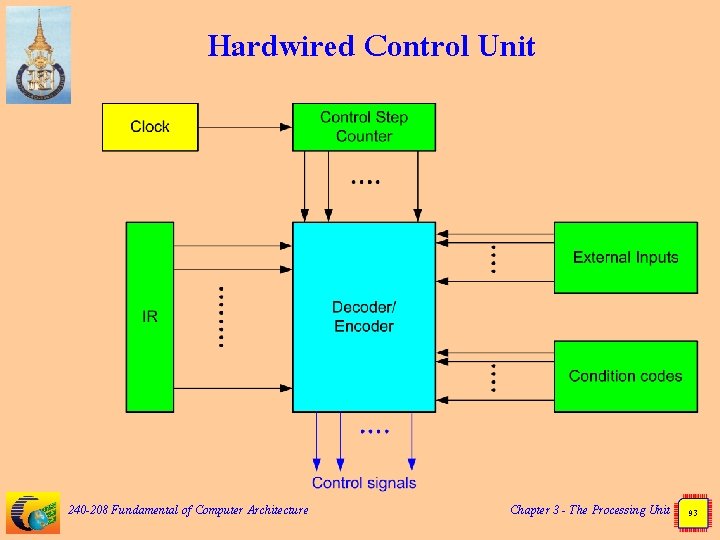

Hardwired Control Unit 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 93

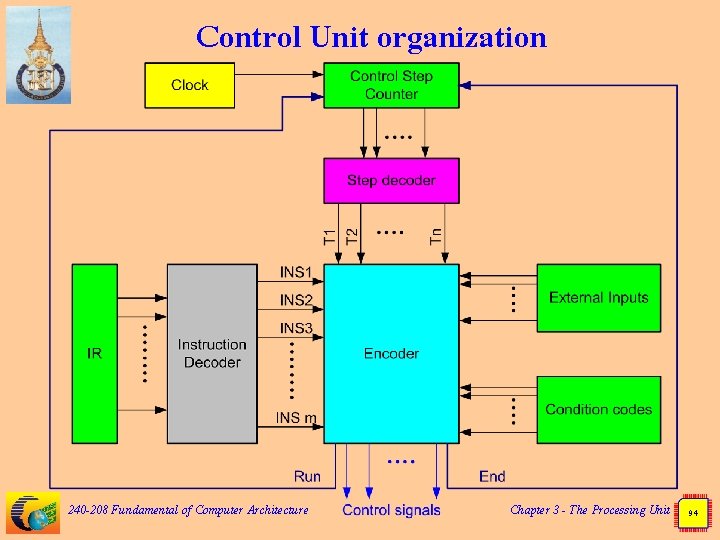

Control Unit organization 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 94

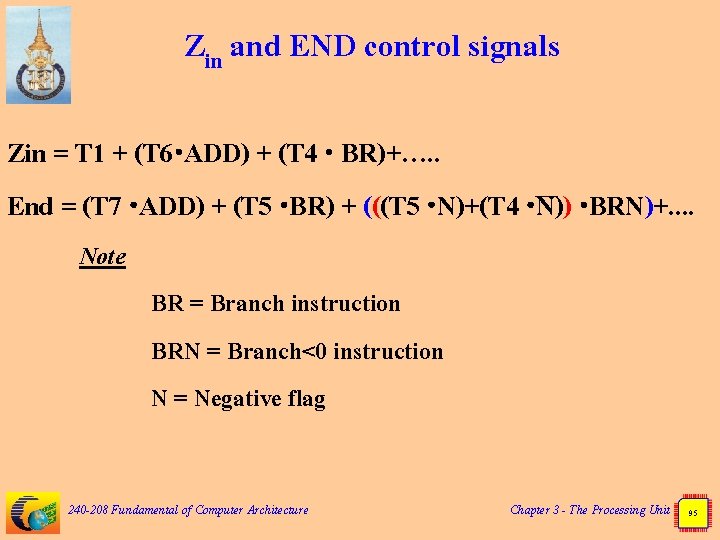

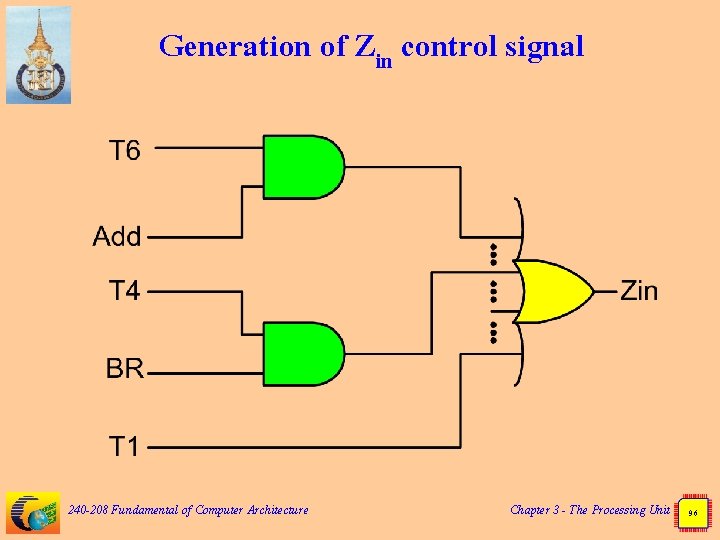

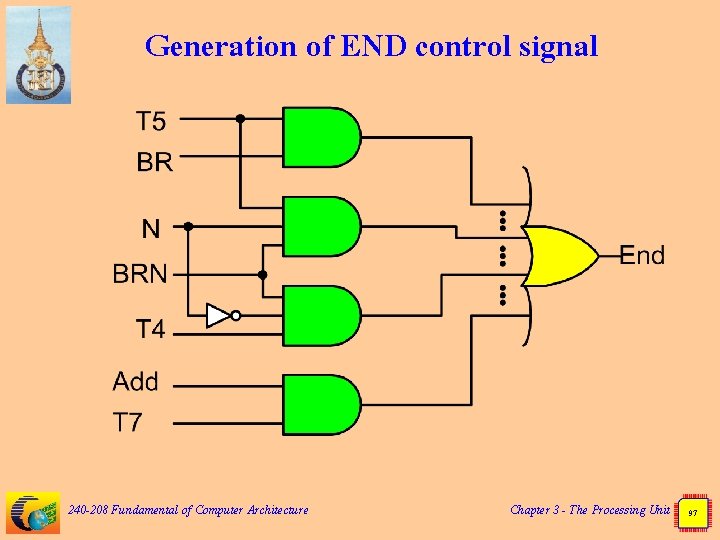

Zin and END control signals Zin = T 1 + (T 6 ADD) + (T 4 BR)+…. . End = (T 7 ADD) + (T 5 BR) + (((T 5 N)+(T 4 N)) BRN)+. . Note BR = Branch instruction BRN = Branch<0 instruction N = Negative flag 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 95

Generation of Zin control signal 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 96

Generation of END control signal 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 97

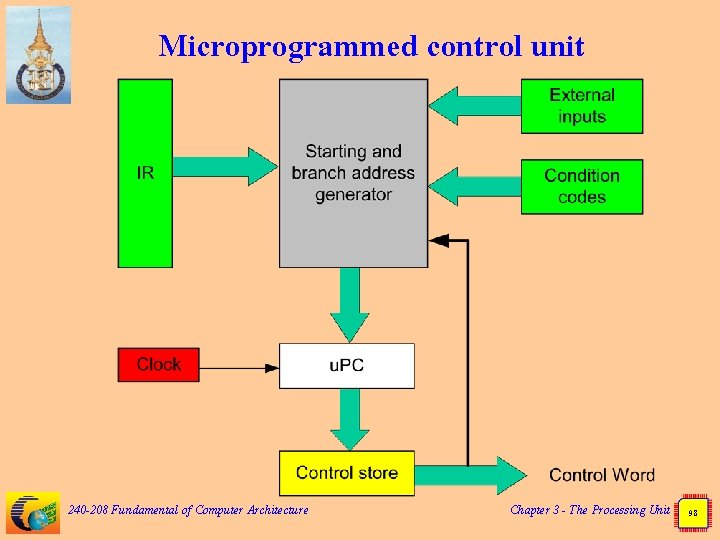

Microprogrammed control unit 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 98

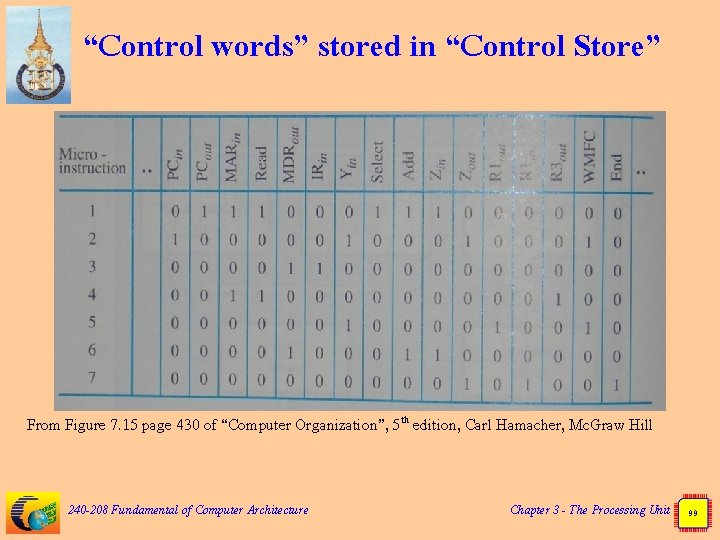

“Control words” stored in “Control Store” From Figure 7. 15 page 430 of “Computer Organization”, 5 th edition, Carl Hamacher, Mc. Graw Hill 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 99

�� ����� 3 240 -208 Fundamental of Computer Architecture Chapter 3 - The Processing Unit 100

- Slides: 100