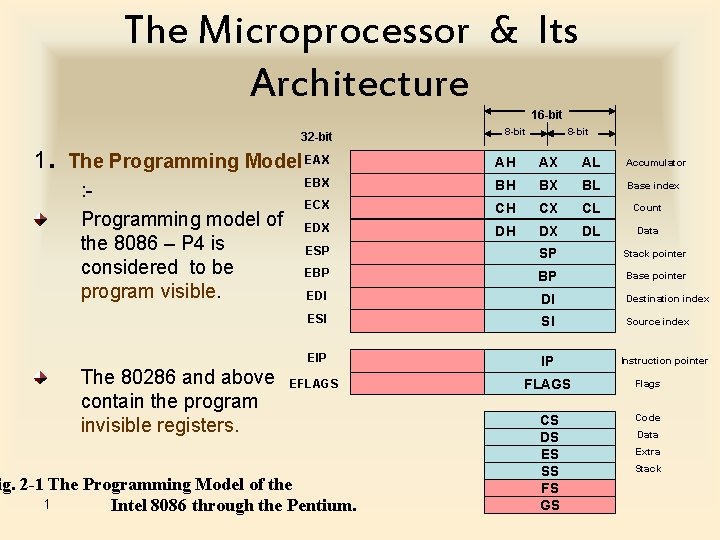

The Microprocessor Its Architecture 16 bit 32 bit

The Microprocessor & Its Architecture 16 -bit 32 -bit . 8 -bit 1 The Programming Model EAX AH AX AL Accumulator EBX BH BX BL Base index ECX CH CX CL Count EDX DH DX DL Data : Programming model of the 8086 – P 4 is considered to be program visible. The 80286 and above contain the program invisible registers. ESP SP Stack pointer EBP BP Base pointer EDI DI Destination index ESI SI Source index EIP IP EFLAGS Flags CS DS ES SS FS GS Code ig. 2 -1 The Programming Model of the 1 Intel 8086 through the Pentium. Instruction pointer Data Extra Stack

Multipurpose Registers 1. EAX (Accumulator). Used for instructions such as multiplication, division, and some of the adjustment instructions (special purpose). In the 80386 and above, the EAX register may also hold the offset address of a location in the memory system. 2. EBX (base index). BX sometimes holds the offset address of a location in the memory system in all versions of the µp. In the 80386 and above, EBX also can address memory data. 2

3. ECX (count). Holds the count for various instructions. In the 80386 and above, EXC also can hold the offset address of memory data. Instructions that can use a count are the repeated string instructions ( REP/REPE/REPNE); and shift, rotate, and LOOP/LOOPD instructions. Shift and rotate use CL. Repeated string instructions use CX. LOOP/LOOPD use either CX or ECX. 4. 3 EDX (data). Holds a part of the result from a multiplication or part of the dividend before division. In the 80386 and above, this register can address memory data.

5. EBP (base pointer). Points to a memory location in all versions of the µp for memory data transfers. Addressed as either BP or EBP. 6. EDI ( destination index). Addresses string destination data for the string instructions. It also functions as either DI or EDI (G-P R). 7. ESI (source index). Addresses source string data for the string instructions. Used as either SI or ESI (G-P R). 4

Special Purpose Registers 1. EIP (instruction pointer). Addresses the next instruction in a section of memory defined as a code segment. IP (16 bits) when µp operates in the real mode. EIP (32 bits) when the 80386 and above operate in the protected mode. EIP, or IP can be modified with a jump or a call instruction. 2. ESP (stack pointer). Addresses an area of memory called the stack. SP (16 bits), and EPS (32 bits). 5

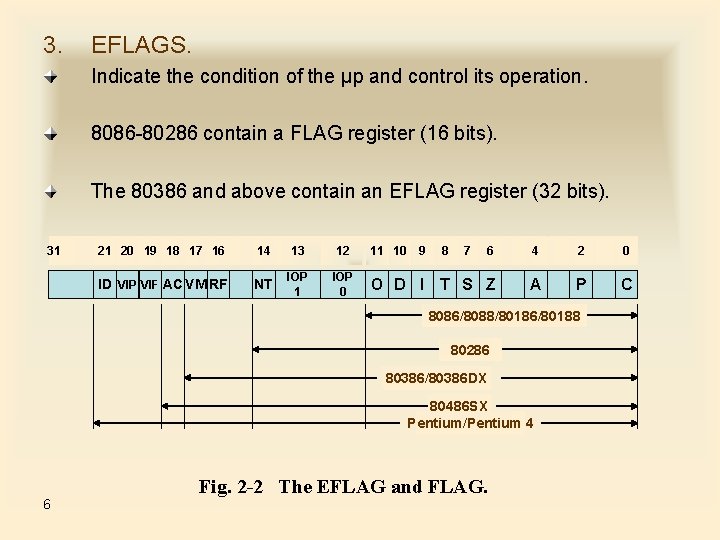

3. EFLAGS. Indicate the condition of the µp and control its operation. 8086 -80286 contain a FLAG register (16 bits). The 80386 and above contain an EFLAG register (32 bits). 31 21 20 19 18 17 16 14 13 12 ID VIP VIF AC VM RF NT IOP 1 IOP 0 11 10 9 8 7 6 4 2 0 O D I T S Z A P C 8086/8088/80186/80188 80286 80386/80386 DX 80486 SX Pentium/Pentium 4 6 Fig. 2 -2 The EFLAG and FLAG.

C (carry) : holds the carry after addition or the borrow after subtraction. C=1 carry, or borrow. C=0 no( carry, or borrow). P (parity) : is the count of ones in a number expressed as even or odd. P=0 odd parity. P=1 even parity. A (auxiliary carry) : holds the carry (half-carry) after addition or the borrow after subtraction between bit 3 and 4 of the result. A=1 half – carry. A=0 no half – carry. Z (zero) : shows that the result of an arithmetic or logic operation is zero Z=1 result is zero. Z=0 result isn’t zero. 7

S (sign) : holds the arithmetic sign of the result after an arithmetic or logic instruction executes. S=1 negative. S=0 positive. T (trap) : enables trapping through an on chip debugging feature. T=1 enables. T=0 disable. I (interrupt) : controls the operation of the INTR (interrupt request) input pin. I=1 pin is enabled. I=0 pin is disabled. D (direction) : selects either the increment or decrement mode for the DI and/or SI registers during string instructions. D=1 decrement. D=0 increment. O (overflow) : indicates that the result has exceeded the capacity of the machine. O=1 overflow. O=0 no overflow. 8

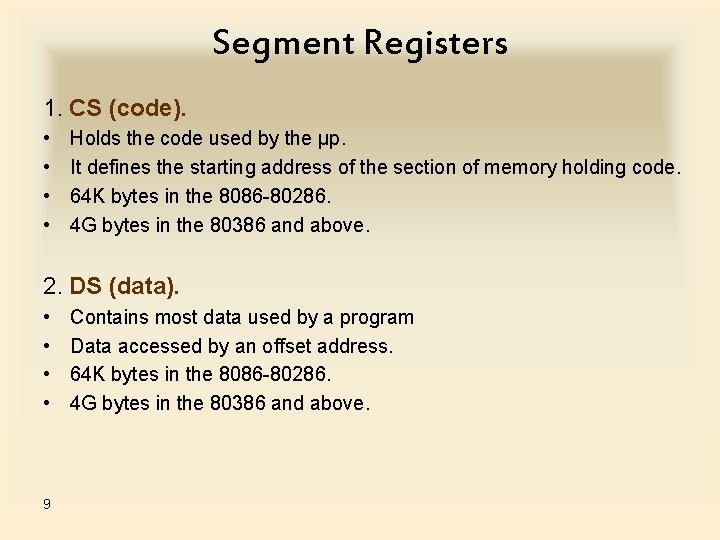

Segment Registers 1. CS (code). • • Holds the code used by the µp. It defines the starting address of the section of memory holding code. 64 K bytes in the 8086 -80286. 4 G bytes in the 80386 and above. 2. DS (data). • • 9 Contains most data used by a program Data accessed by an offset address. 64 K bytes in the 8086 -80286. 4 G bytes in the 80386 and above.

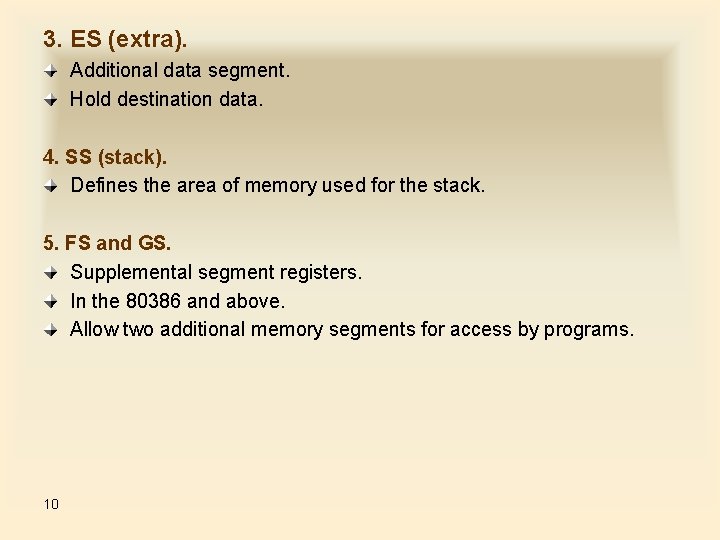

3. ES (extra). Additional data segment. Hold destination data. 4. SS (stack). Defines the area of memory used for the stack. 5. FS and GS. Supplemental segment registers. In the 80386 and above. Allow two additional memory segments for access by programs. 10

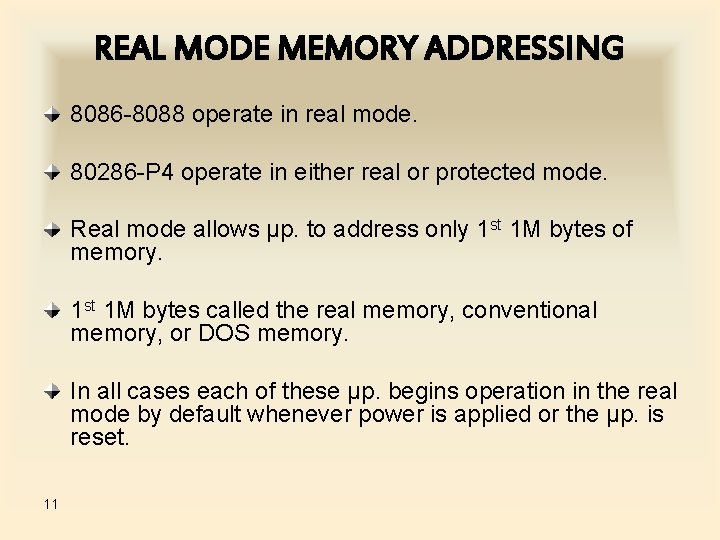

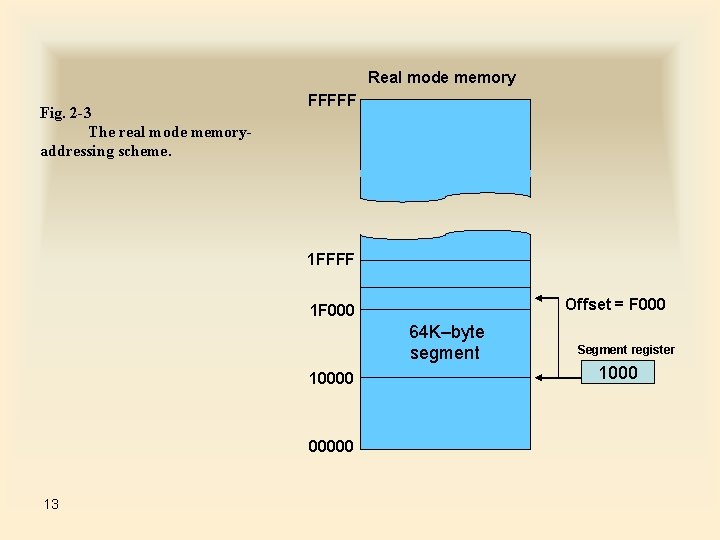

REAL MODE MEMORY ADDRESSING 8086 -8088 operate in real mode. 80286 -P 4 operate in either real or protected mode. Real mode allows µp. to address only 1 st 1 M bytes of memory. 1 st 1 M bytes called the real memory, conventional memory, or DOS memory. In all cases each of these µp. begins operation in the real mode by default whenever power is applied or the µp. is reset. 11

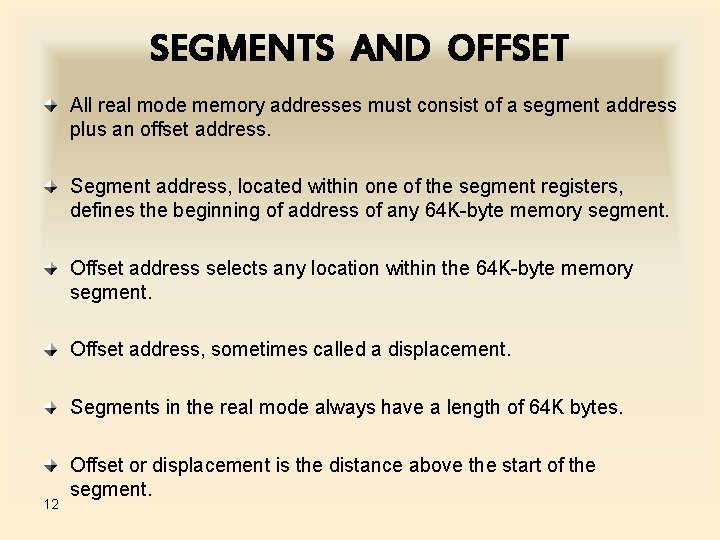

SEGMENTS AND OFFSET All real mode memory addresses must consist of a segment address plus an offset address. Segment address, located within one of the segment registers, defines the beginning of address of any 64 K-byte memory segment. Offset address selects any location within the 64 K-byte memory segment. Offset address, sometimes called a displacement. Segments in the real mode always have a length of 64 K bytes. 12 Offset or displacement is the distance above the start of the segment.

Real mode memory Fig. 2 -3 The real mode memoryaddressing scheme. FFFFF 1 FFFF Offset = F 000 1 F 000 64 K–byte segment 100000 13 Segment register 1000

Real mode segments can begin only at a 16 - byte boundary (paragraph) in the memory system. (1000 H + 2000 H)= (10000 H + 2000 H) = 12000 H 1000: 2000 In the 80286 (with special external circuitry) and through the Pentium 4, an extra 64 K minus 16 bytes of memory is addressable when segment address is FFFFH and the HIMEM. SYS driver for DOS is installed in the system. (0 FFFF 0 H-10 FFEFH) high memory 14

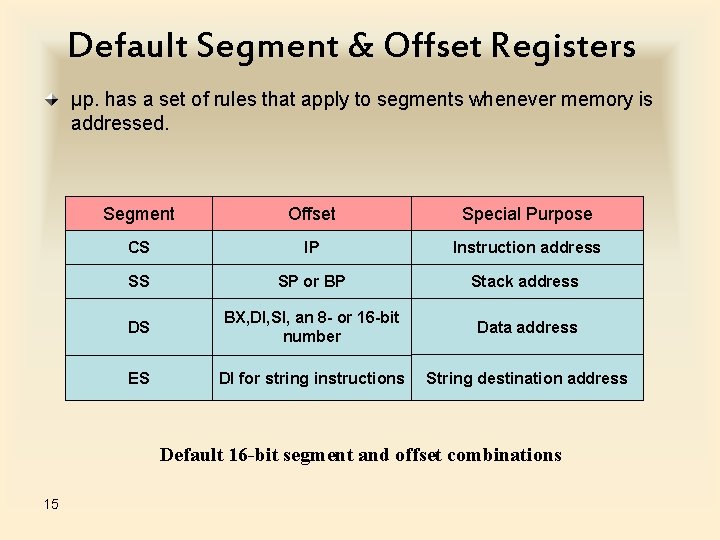

Default Segment & Offset Registers µp. has a set of rules that apply to segments whenever memory is addressed. Segment Offset Special Purpose CS IP Instruction address SS SP or BP Stack address DS BX, DI, SI, an 8 - or 16 -bit number Data address ES DI for string instructions String destination address Default 16 -bit segment and offset combinations 15

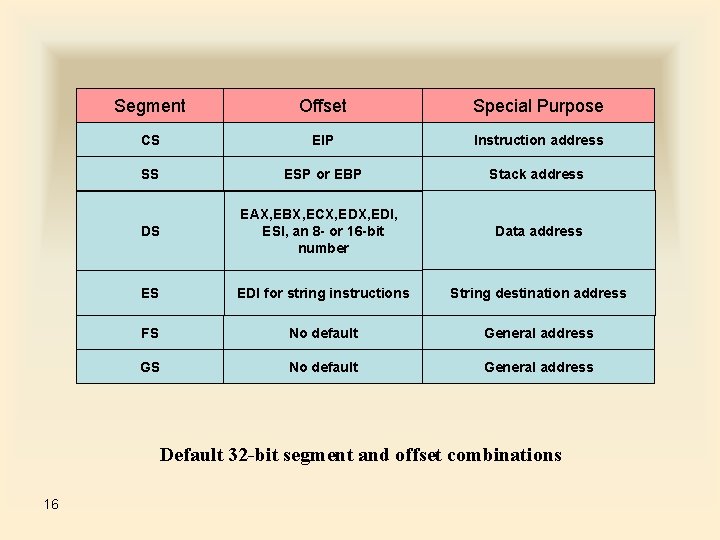

Segment Offset Special Purpose CS EIP Instruction address SS ESP or EBP Stack address DS EAX, EBX, ECX, EDI, ESI, an 8 - or 16 -bit number Data address ES EDI for string instructions String destination address FS No default General address GS No default General address Default 32 -bit segment and offset combinations 16

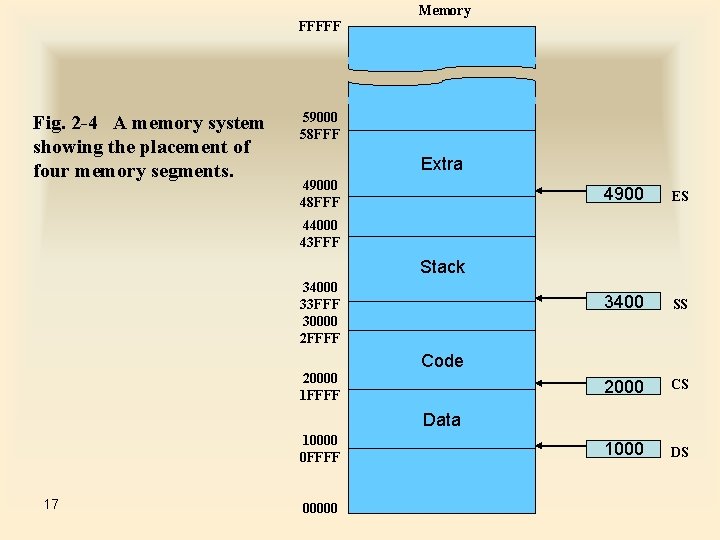

Memory FFFFF Fig. 2 -4 A memory system showing the placement of four memory segments. 59000 58 FFF Extra 49000 48 FFF 4900 ES 3400 SS 2000 CS 1000 DS 44000 43 FFF Stack 34000 33 FFF 30000 2 FFFF 20000 1 FFFF Code Data 10000 0 FFFF 17 00000

Segment and Offset Addressing Scheme Allows Relocation A Relocatable program is one that can be placed into any area of memory and executed without change. Relocatable data are data that can be placed in any area of memory and used without any change to the program. 18

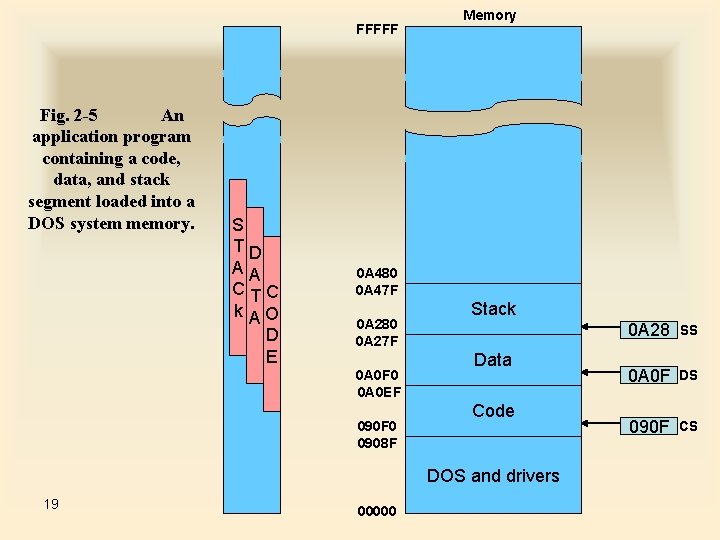

FFFFF Fig. 2 -5 An application program containing a code, data, and stack segment loaded into a DOS system memory. S TD AA CTC k AO D E Memory 0 A 480 0 A 47 F 0 A 280 0 A 27 F 0 A 0 F 0 0 A 0 EF 090 F 0 0908 F Stack Data Code DOS and drivers 19 00000 0 A 28 SS 0 A 0 F DS 090 F CS

- Slides: 19