Basic Microprocessor Timing ECE 611 Microprocessor Systems Dr

Basic Microprocessor Timing ECE 611 Microprocessor Systems Dr. Roger L. Haggard, Associate Professor Department of Electrical and Computer Engineering Tennessee Technological University Spring 1998 1

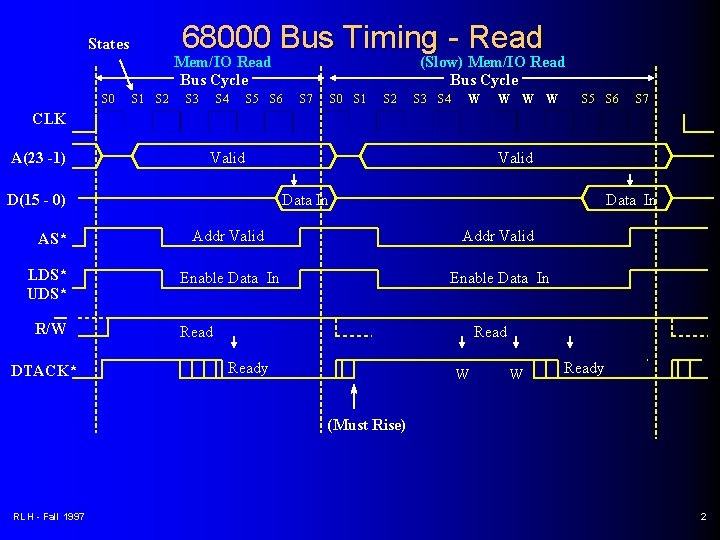

68000 Bus Timing - Read States Mem/IO Read Bus Cycle S 0 S 1 S 2 S 3 S 4 (Slow) Mem/IO Read Bus Cycle S 5 S 6 S 7 S 0 S 1 S 2 S 3 S 4 W W S 5 S 6 S 7 CLK A(23 -1) Valid D(15 - 0) AS* LDS* UDS* R/W DTACK* Valid Data In Addr Valid Enable Data In Ready W W Ready (Must Rise) RLH - Fall 1997 2

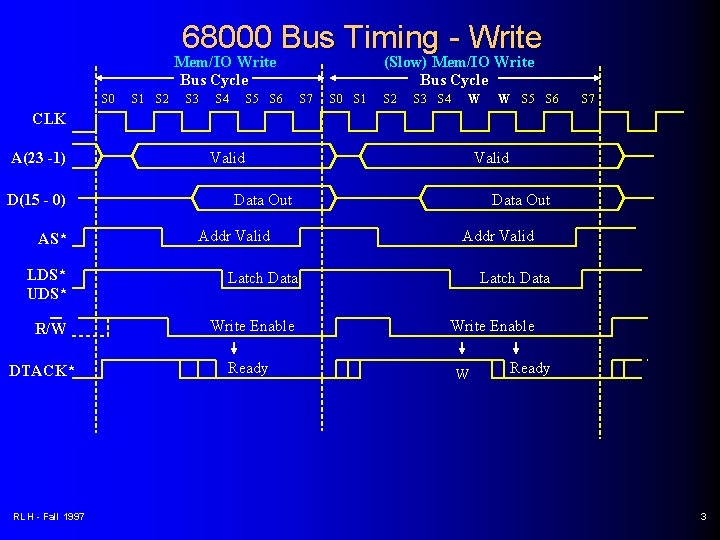

68000 Bus Timing - Write Mem/IO Write Bus Cycle S 0 S 1 S 2 S 3 S 4 S 5 S 6 (Slow) Mem/IO Write Bus Cycle S 7 S 0 S 1 S 2 S 3 S 4 W W S 5 S 6 S 7 CLK A(23 -1) D(15 - 0) AS* Valid Data Out Addr Valid LDS* UDS* Latch Data R/W Write Enable DTACK* RLH - Fall 1997 Valid Ready Data Out Addr Valid Latch Data Write Enable W Ready 3

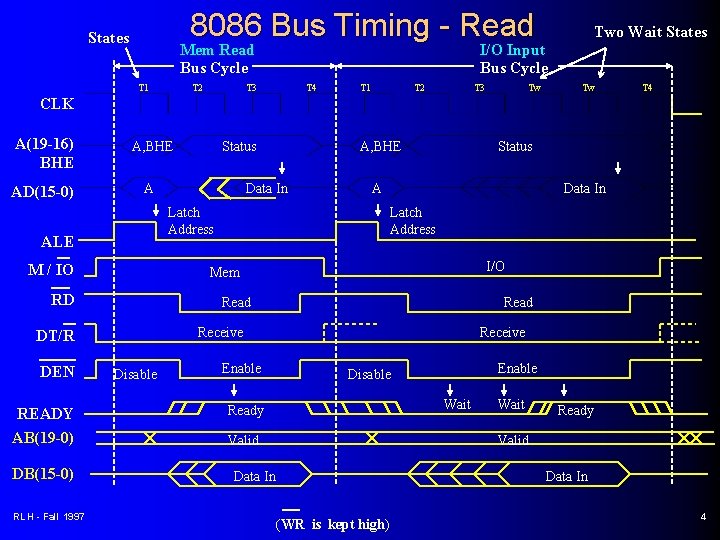

8086 Bus Timing - Read States Mem Read Bus Cycle T 1 T 2 Two Wait States I/O Input Bus Cycle T 3 T 4 T 1 T 2 T 3 Tw Tw T 4 CLK A(19 -16) BHE A, BHE AD(15 -0) A M / IO Data In A Data In Latch Address I/O Read Receive DT/R Disable Enable READY Ready AB(19 -0) Valid RLH - Fall 1997 Status Mem RD DB(15 -0) A, BHE Latch Address ALE DEN Status Receive Enable Disable Wait Ready Valid Data In (WR is kept high) 4

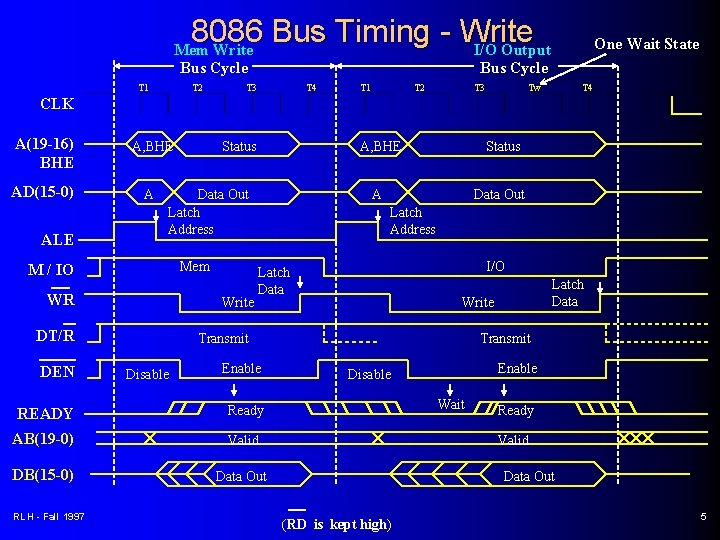

8086 Bus Timing - Write I/O Output Mem Write Bus Cycle T 1 T 2 One Wait State Bus Cycle T 3 T 4 T 1 T 2 T 3 Tw T 4 CLK A(19 -16) BHE AD(15 -0) ALE A, BHE A A, BHE Data Out Latch Address Mem M / IO WR Write DT/R DEN Status A Data Out Latch Address I/O Latch Data Disable Enable Ready AB(19 -0) Valid DB(15 -0) Data Out Latch Data Write Transmit READY RLH - Fall 1997 Status Transmit Enable Disable Wait Ready Valid Data Out (RD is kept high) 5

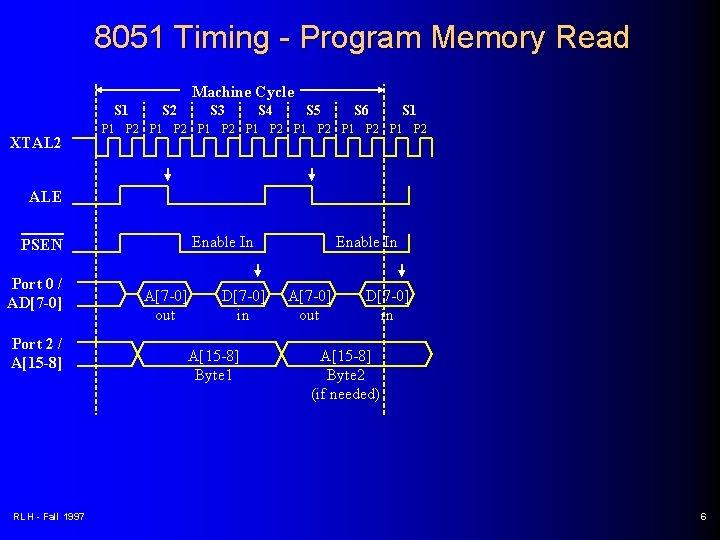

8051 Timing - Program Memory Read Machine Cycle S 1 XTAL 2 S 3 S 4 S 5 S 6 S 1 P 2 P 1 P 2 P 1 P 2 ALE Enable In PSEN Port 0 / AD[7 -0] Port 2 / A[15 -8] RLH - Fall 1997 A[7 -0] out D[7 -0] in A[15 -8] Byte 1 Enable In A[7 -0] out D[7 -0] in A[15 -8] Byte 2 (if needed) 6

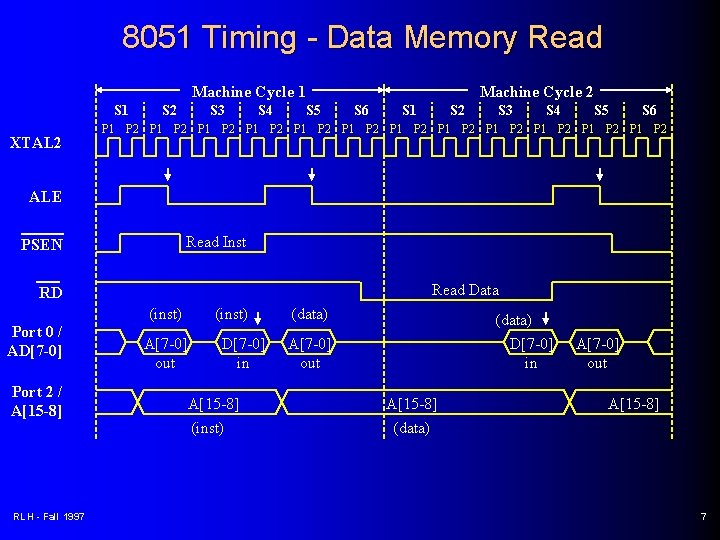

8051 Timing - Data Memory Read Machine Cycle 1 S 1 XTAL 2 S 3 S 4 Machine Cycle 2 S 5 S 6 S 1 S 2 S 3 S 4 S 5 S 6 P 1 P 2 P 1 P 2 P 1 P 2 ALE Read Inst PSEN Read Data RD (inst) Port 0 / AD[7 -0] Port 2 / A[15 -8] RLH - Fall 1997 A[7 -0] out (inst) D[7 -0] in A[15 -8] (inst) (data) D[7 -0] in A[7 -0] out A[15 -8] (data) 7

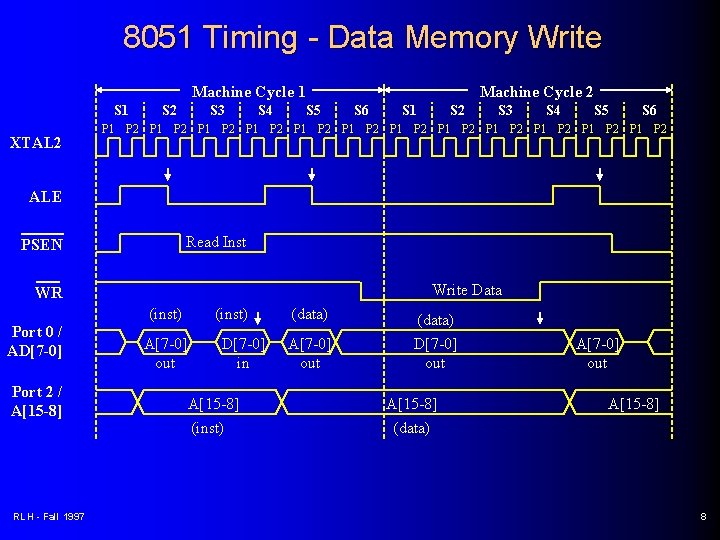

8051 Timing - Data Memory Write Machine Cycle 1 S 1 XTAL 2 S 3 S 4 Machine Cycle 2 S 5 S 6 S 1 S 2 S 3 S 4 S 5 S 6 P 1 P 2 P 1 P 2 P 1 P 2 ALE Read Inst PSEN Write Data WR (inst) Port 0 / AD[7 -0] Port 2 / A[15 -8] RLH - Fall 1997 A[7 -0] out (inst) D[7 -0] in A[15 -8] (inst) (data) A[7 -0] out (data) D[7 -0] out A[15 -8] A[7 -0] out A[15 -8] (data) 8

Memory Interfacing and Timing 9

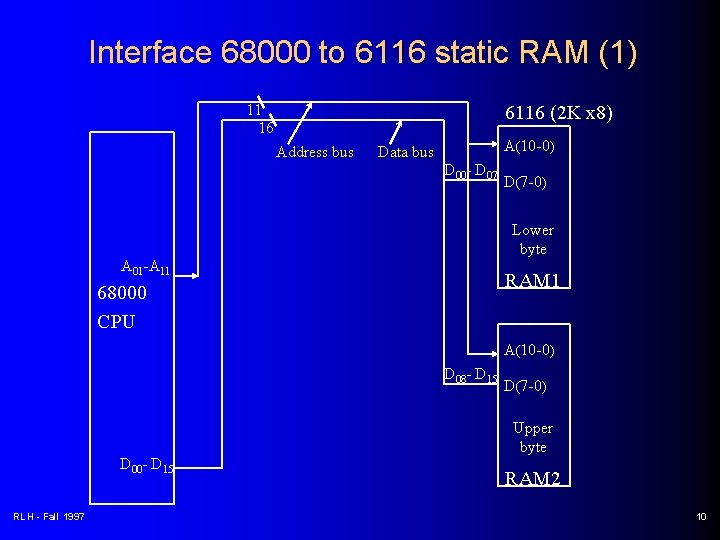

Interface 68000 to 6116 static RAM (1) 11 16 6116 (2 K x 8) Address bus A(10 -0) Data bus D 00 - D 07 D(7 -0) Lower byte A 01 -A 11 RAM 1 68000 CPU A(10 -0) D 08 - D 15 D 00 - D 15 RLH - Fall 1997 D(7 -0) Upper byte RAM 2 10

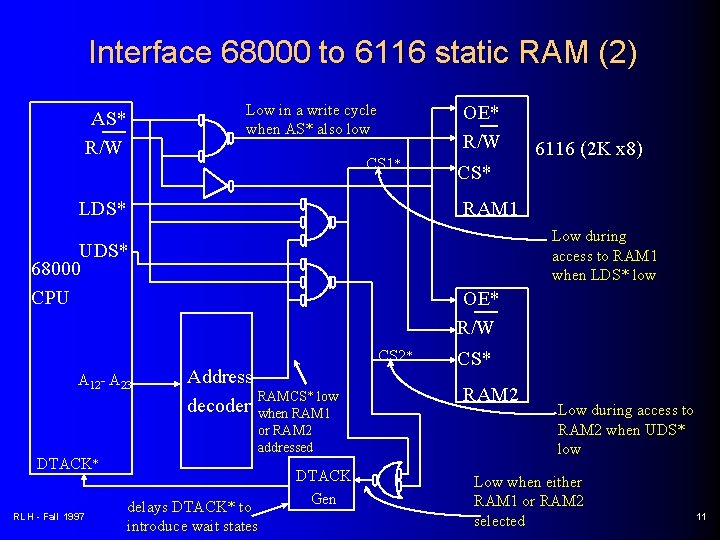

Interface 68000 to 6116 static RAM (2) Low in a write cycle when AS* also low AS* R/W OE* R/W CS 1* LDS* CS* RAM 1 Low during access to RAM 1 when LDS* low UDS* 68000 CPU OE* R/W CS 2* A 12 - A 23 Address RAMCS* low decoder when RAM 1 or RAM 2 addressed DTACK* RLH - Fall 1997 6116 (2 K x 8) delays DTACK* to introduce wait states DTACK Gen CS* RAM 2 Low during access to RAM 2 when UDS* low Low when either RAM 1 or RAM 2 selected 11

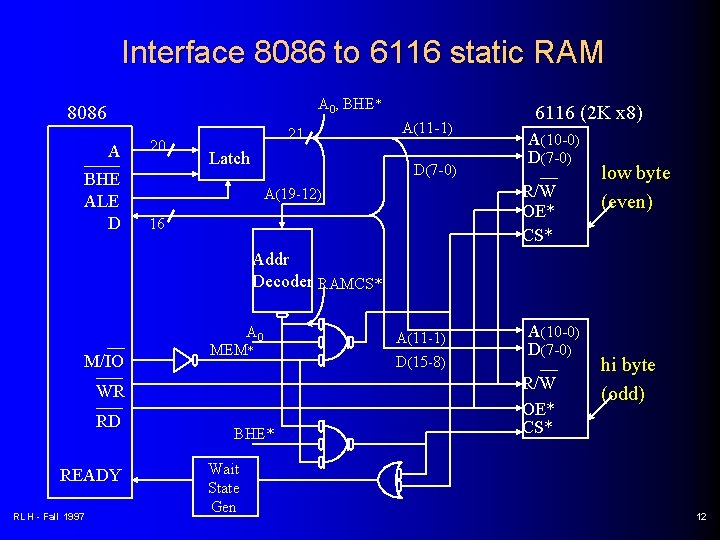

Interface 8086 to 6116 static RAM A 0, BHE* 8086 A ____ BHE ALE D 20 21 Latch A(11 -1) D(7 -0) A(19 -12) 16 6116 (2 K x 8) A(10 -0) D(7 -0) __ R/W OE* CS* low byte (even) A(10 -0) D(7 -0) __ R/W OE* CS* hi byte (odd) Addr Decoder RAMCS* __ M/IO ___ WR ___ RD READY RLH - Fall 1997 A 0 MEM* BHE* Wait State Gen A(11 -1) D(15 -8) 12

- Slides: 12