Basic Microprocessor Hardware ECE 611 Microprocessor Systems Dr

Basic Microprocessor Hardware ECE 611 Microprocessor Systems Dr. Roger L. Haggard, Associate Professor Department of Electrical and Computer Engineering Tennessee Technological University Spring 1998 1

Outline l l l Microprocessor Applications Computer System Structure Generic CPU, Memory, I/O Specific Microprocessor Pinouts Specific Microprocessor Timing 2

Introduction l l Computer System - Hardware and Software Typical Processors: – – 8086 Microprocessor 68000 Microprocessor 8051 Microcomputer or Microcontroller Why different? 3

Applications of Microprocessors 2 Broad Applications: l General purpose computer – runs user programs – big memory, big peripherals – modular, complex, expandable l Embedded Computer – – RLH - Fall 1997 invisible to user dedicated application, limited hardware single board, less complex our project and most designs 4

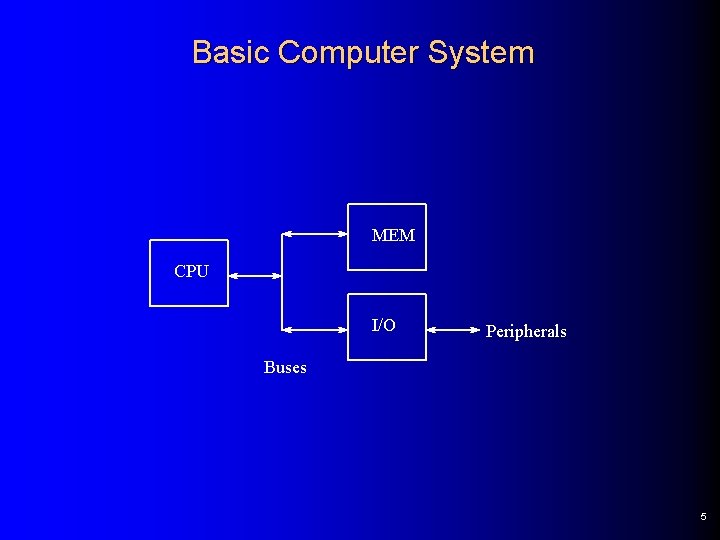

Basic Computer System MEM CPU I/O Peripherals Buses 5

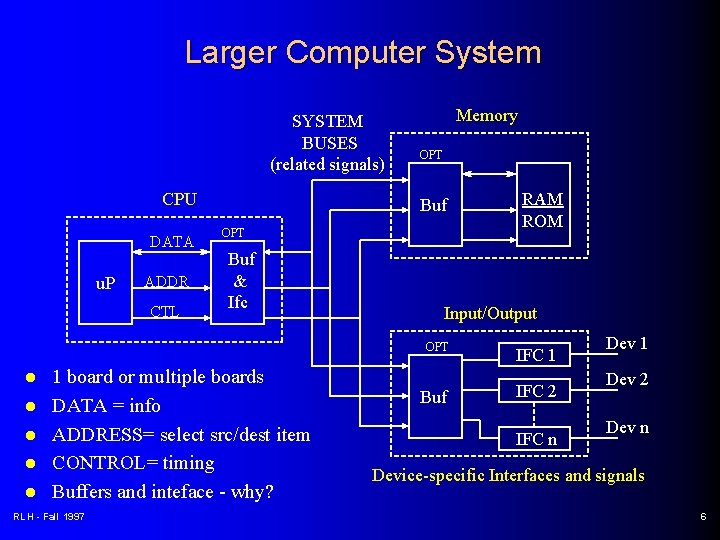

Larger Computer System SYSTEM BUSES (related signals) CPU DATA u. P ADDR CTL l l l OPT Buf & Ifc 1 board or multiple boards DATA = info ADDRESS= select src/dest item CONTROL= timing Buffers and inteface - why? RLH - Fall 1997 Memory RAM ROM Input/Output OPT IFC 1 Buf IFC 2 IFC n Dev 1 Dev 2 Dev n Device-specific Interfaces and signals 6

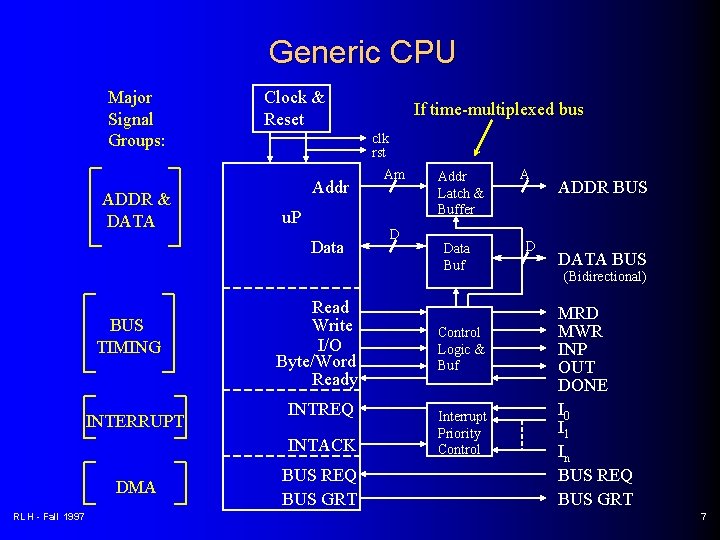

Generic CPU Major Signal Groups: ADDR & DATA Clock & Reset clk rst Addr u. P Data BUS TIMING INTERRUPT Read Write I/O Byte/Word Ready INTREQ INTACK DMA RLH - Fall 1997 If time-multiplexed bus BUS REQ BUS GRT Am D Addr Latch & Buffer Data Buf Control Logic & Buf Interrupt Priority Control A D ADDR BUS DATA BUS (Bidirectional) MRD MWR INP OUT DONE I 0 I 1 In BUS REQ BUS GRT 7

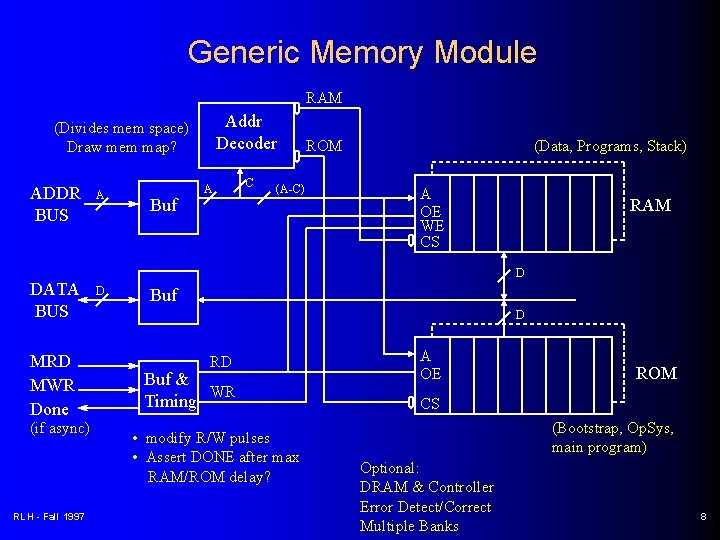

Generic Memory Module RAM Addr Decoder (Divides mem space) Draw mem map? ADDR BUS DATA BUS MRD MWR Done (if async) RLH - Fall 1997 A Buf A C (A-C) ROM (Data, Programs, Stack) A OE WE CS RAM D D Buf D RD Buf & WR Timing • modify R/W pulses • Assert DONE after max RAM/ROM delay? A OE ROM CS (Bootstrap, Op. Sys, main program) Optional: DRAM & Controller Error Detect/Correct Multiple Banks 8

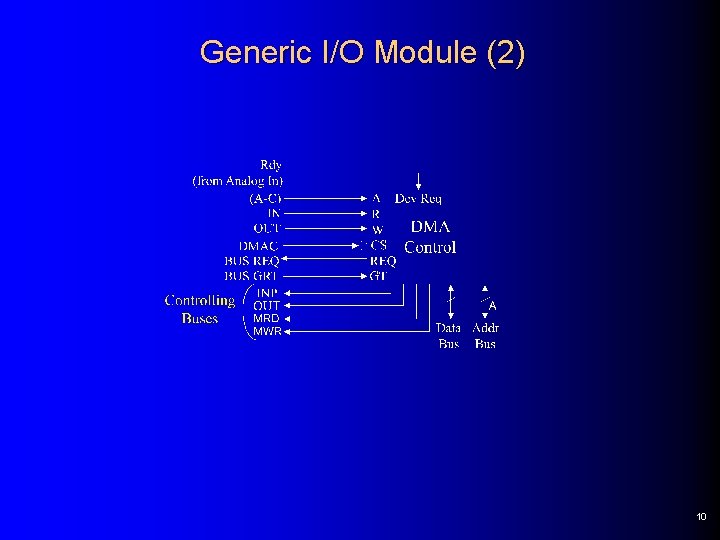

Generic I/O Module (1) 9

Generic I/O Module (2) 10

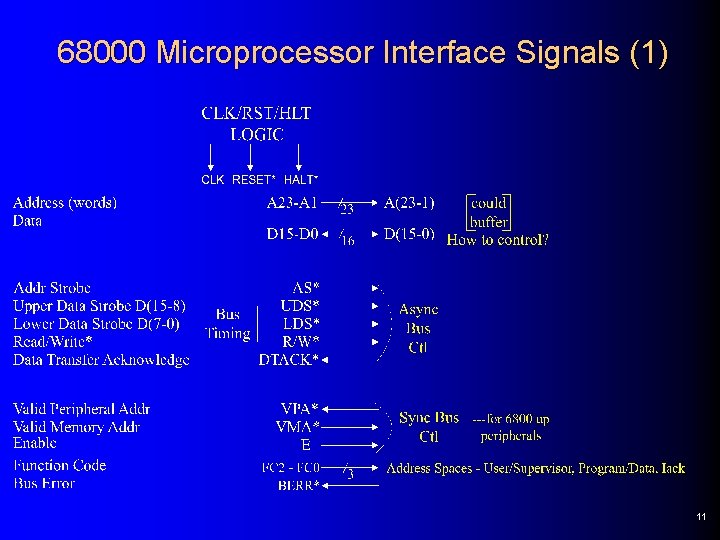

68000 Microprocessor Interface Signals (1) 11

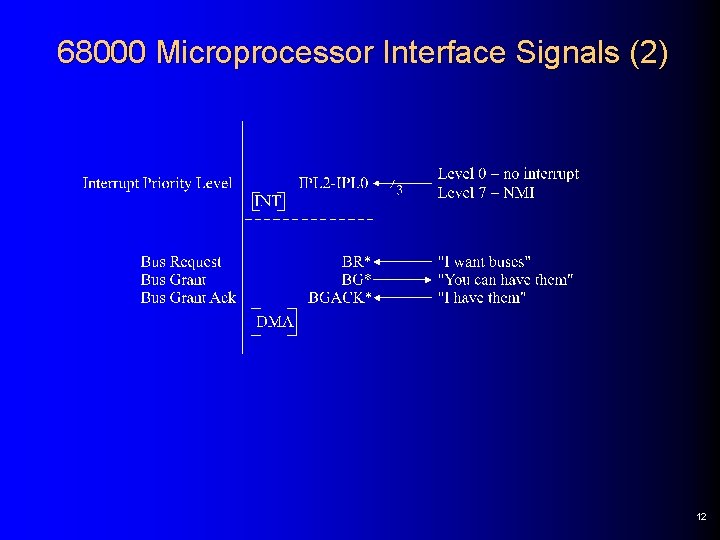

68000 Microprocessor Interface Signals (2) 12

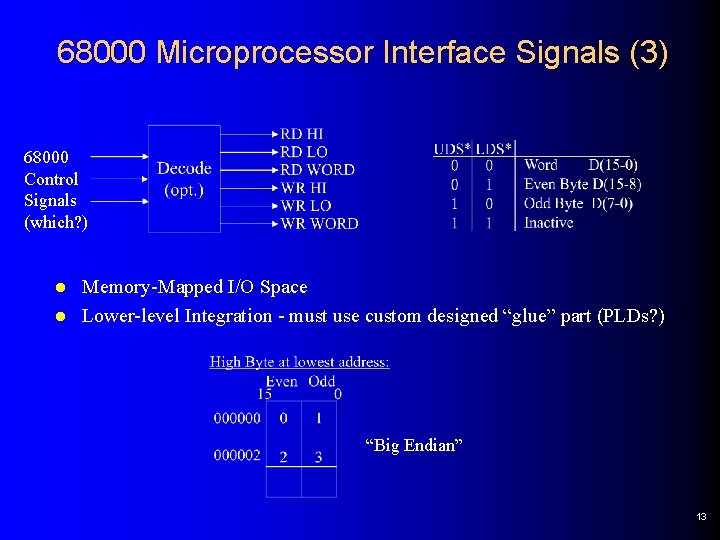

68000 Microprocessor Interface Signals (3) 68000 Control Signals (which? ) l l Memory-Mapped I/O Space Lower-level Integration - must use custom designed “glue” part (PLDs? ) “Big Endian” 13

8086 Micropocessor Interface Signals (1) 14

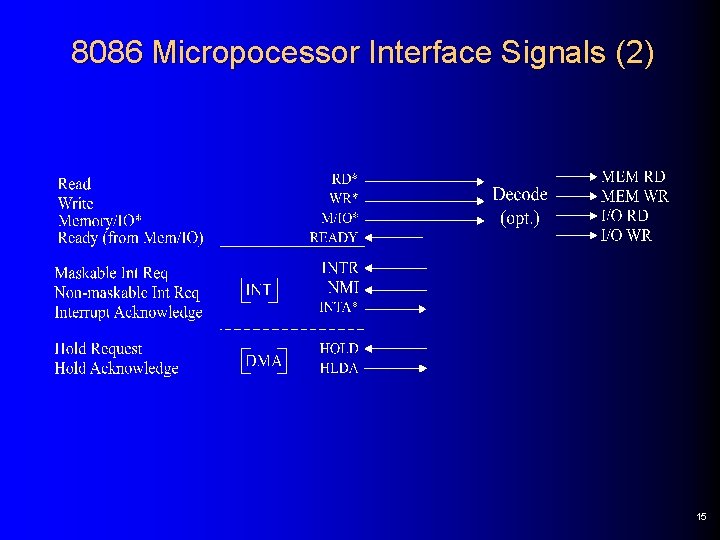

8086 Micropocessor Interface Signals (2) 15

8086 Micropocessor Interface Signals (3) l 2 Interface Configurations – Minimum Mode - small, single processor – Maximum Mode - large, multi-processor or coprocessor l l Separate (port-mapped) I/O space Highly integrated “glue” parts available “Little Endian” 16

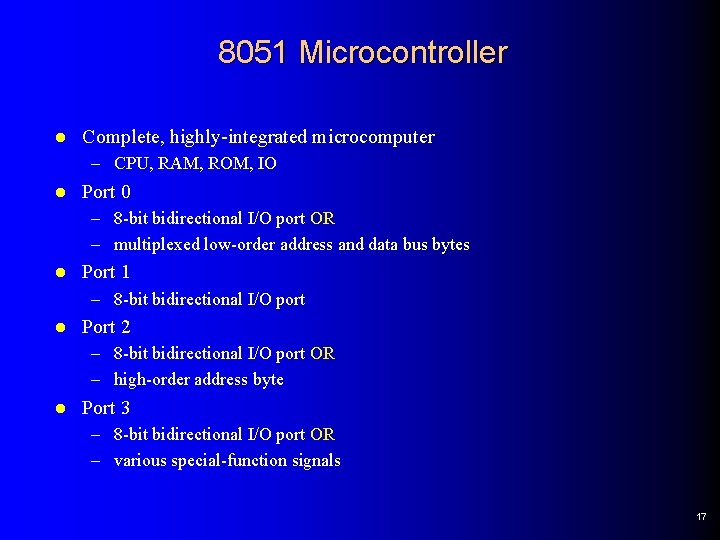

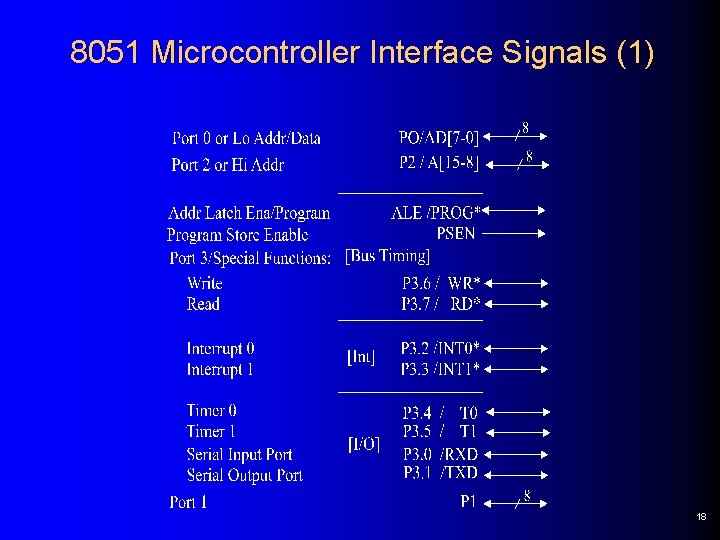

8051 Microcontroller l Complete, highly-integrated microcomputer – CPU, RAM, ROM, IO l Port 0 – 8 -bit bidirectional I/O port OR – multiplexed low-order address and data bus bytes l Port 1 – 8 -bit bidirectional I/O port l Port 2 – 8 -bit bidirectional I/O port OR – high-order address byte l Port 3 – 8 -bit bidirectional I/O port OR – various special-function signals 17

8051 Microcontroller Interface Signals (1) 18

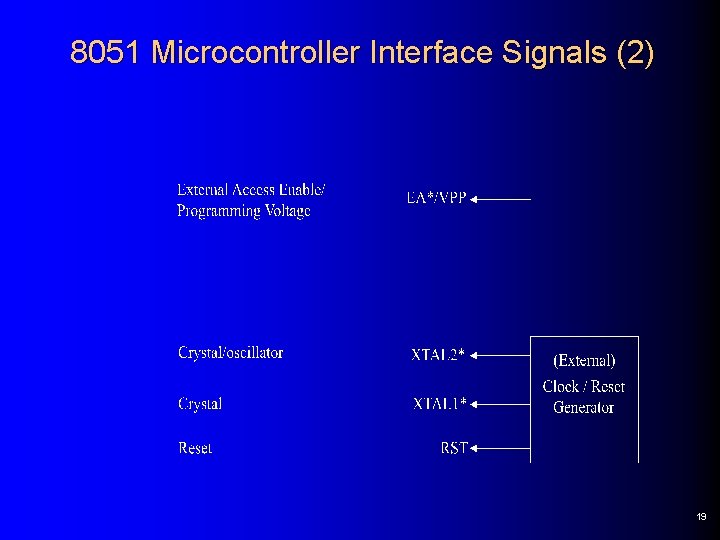

8051 Microcontroller Interface Signals (2) 19

- Slides: 19