Unit9 SUN SPARC Microprocessor Prof Swati Sharma swati

- Slides: 19

Unit-9 SUN SPARC Microprocessor Prof. Swati Sharma swati. sharma@darshan. ac. in Microprocessor Unit-9 SUN SPARC & Interfacing Microprocessor - 2150707 Darshan Institute of Engineering & Technology

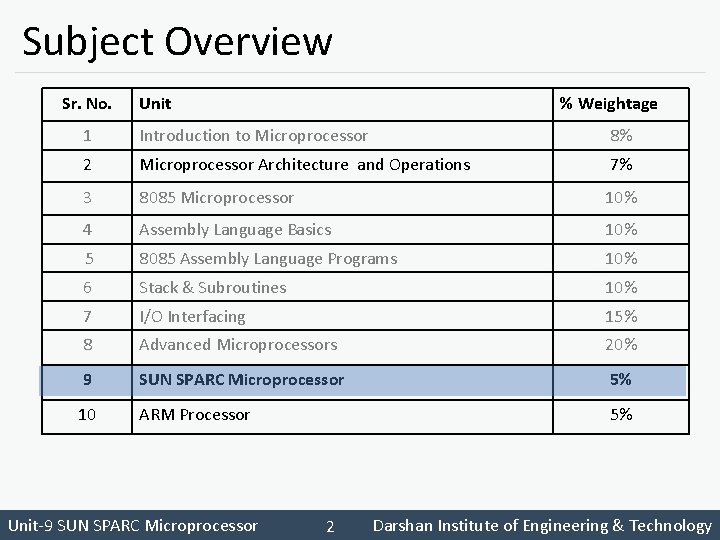

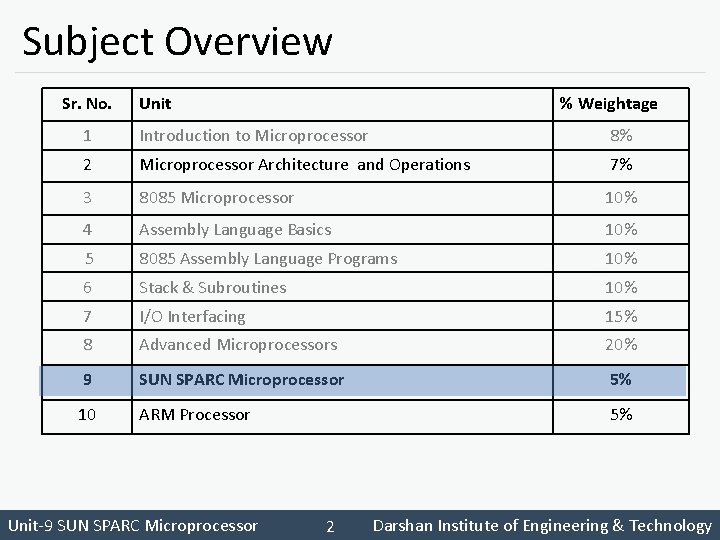

Subject Overview Sr. No. Unit % Weightage 1 Introduction to Microprocessor 8% 2 Microprocessor Architecture and Operations 7% 3 8085 Microprocessor 10% 4 Assembly Language Basics 10% 5 8085 Assembly Language Programs 10% 6 Stack & Subroutines 10% 7 I/O Interfacing 15% 8 Advanced Microprocessors 20% 9 SUN SPARC Microprocessor 5% 10 ARM Processor 5% Unit-9 SUN SPARC Microprocessor 2 Darshan Institute of Engineering & Technology

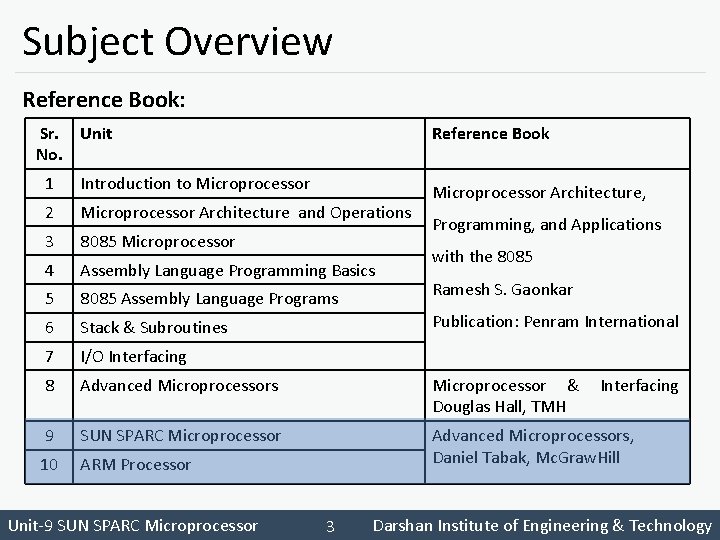

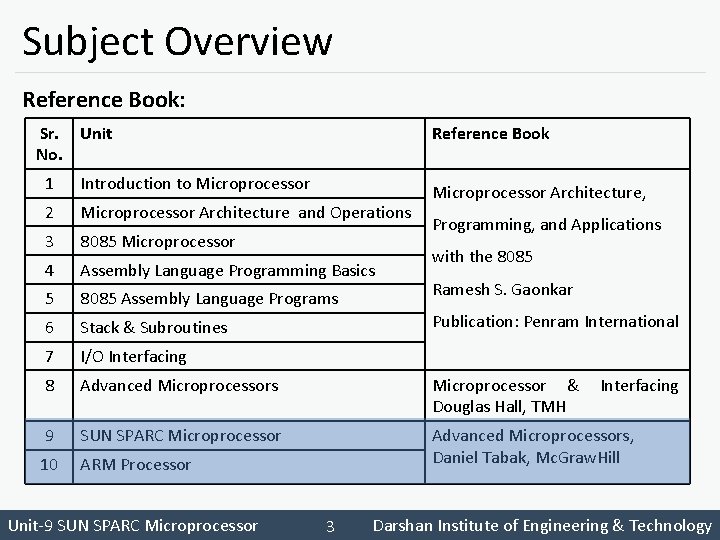

Subject Overview Reference Book: Sr. Unit No. Reference Book 1 Introduction to Microprocessor 2 Microprocessor Architecture and Operations 3 8085 Microprocessor 4 Assembly Language Programming Basics 5 8085 Assembly Language Programs 6 Stack & Subroutines 7 I/O Interfacing 8 Advanced Microprocessors Microprocessor & Douglas Hall, TMH 9 SUN SPARC Microprocessor 10 ARM Processor Advanced Microprocessors, Daniel Tabak, Mc. Graw. Hill Unit-9 SUN SPARC Microprocessor Architecture, Programming, and Applications with the 8085 Ramesh S. Gaonkar Publication: Penram International 3 Interfacing Darshan Institute of Engineering & Technology

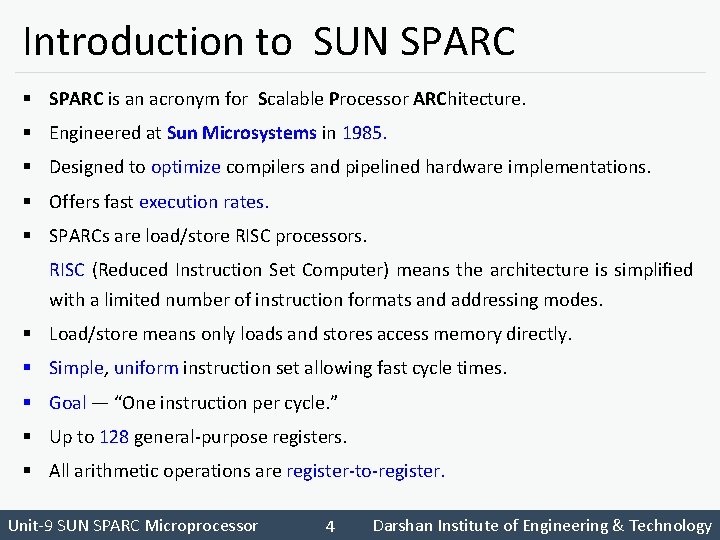

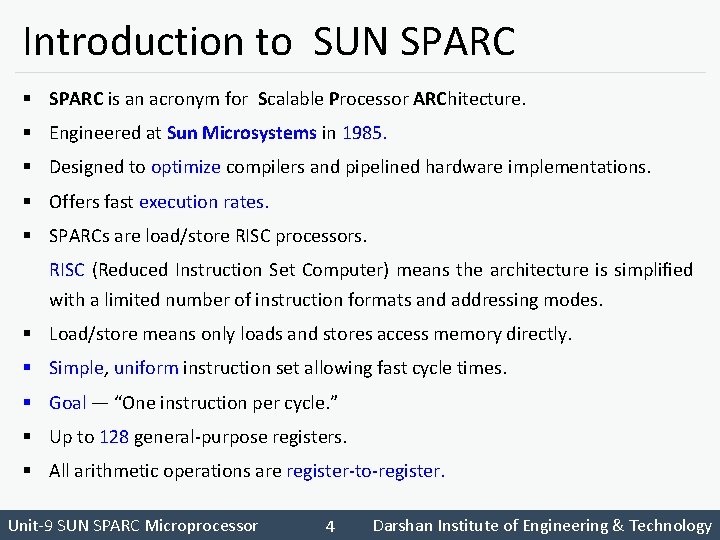

Introduction to SUN SPARC § SPARC is an acronym for Scalable Processor ARChitecture. § Engineered at Sun Microsystems in 1985. § Designed to optimize compilers and pipelined hardware implementations. § Offers fast execution rates. § SPARCs are load/store RISC processors. RISC (Reduced Instruction Set Computer) means the architecture is simplified with a limited number of instruction formats and addressing modes. § Load/store means only loads and stores access memory directly. § Simple, uniform instruction set allowing fast cycle times. § Goal — “One instruction per cycle. ” § Up to 128 general-purpose registers. § All arithmetic operations are register-to-register. Unit-9 SUN SPARC Microprocessor 4 Darshan Institute of Engineering & Technology

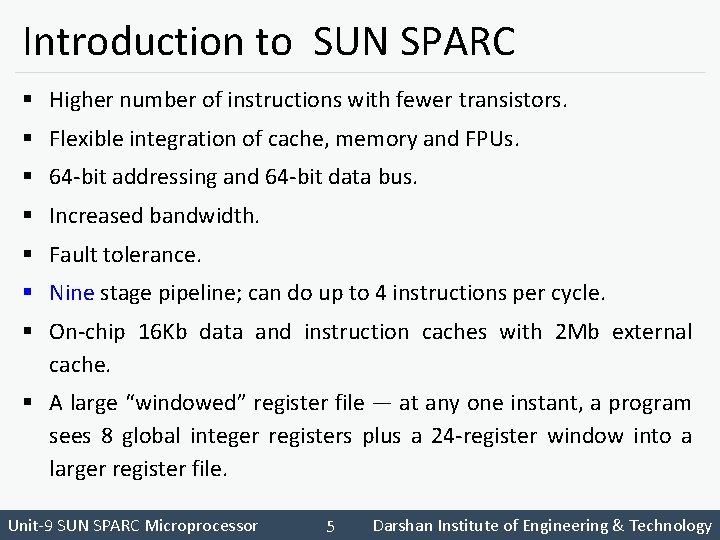

Introduction to SUN SPARC § Higher number of instructions with fewer transistors. § Flexible integration of cache, memory and FPUs. § 64 -bit addressing and 64 -bit data bus. § Increased bandwidth. § Fault tolerance. § Nine stage pipeline; can do up to 4 instructions per cycle. § On-chip 16 Kb data and instruction caches with 2 Mb external cache. § A large “windowed” register file — at any one instant, a program sees 8 global integer registers plus a 24 -register window into a larger register file. Unit-9 SUN SPARC Microprocessor 5 Darshan Institute of Engineering & Technology

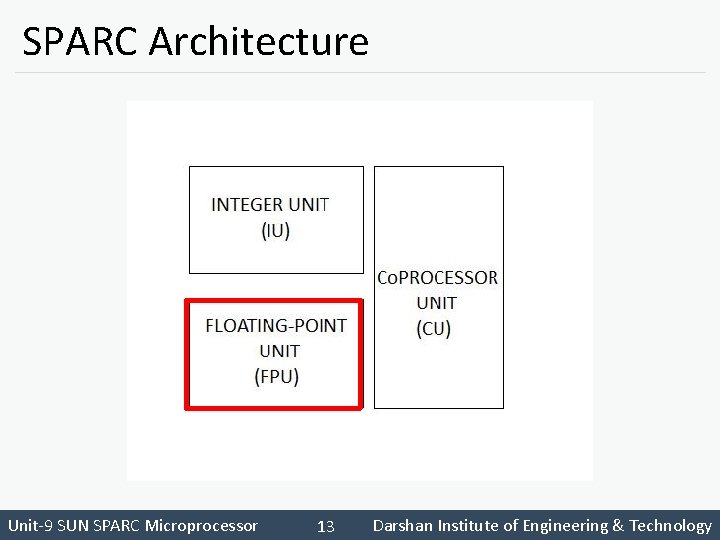

SPARC Architecture Unit-9 SUN SPARC Microprocessor Darshan Institute of Engineering & Technology

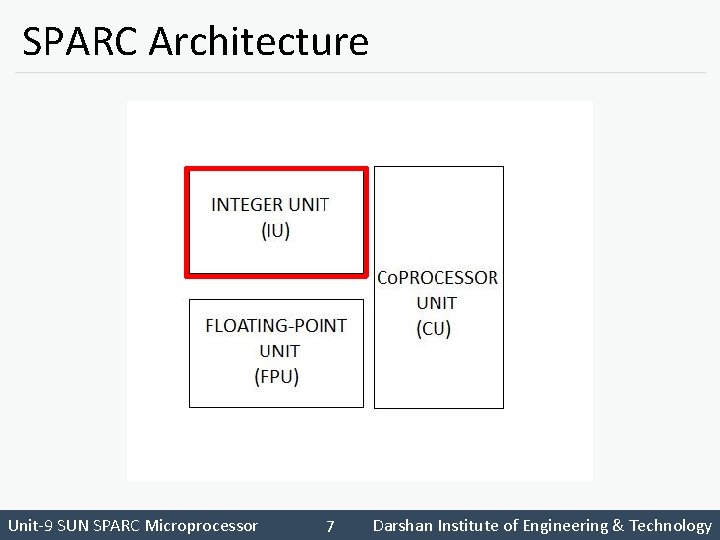

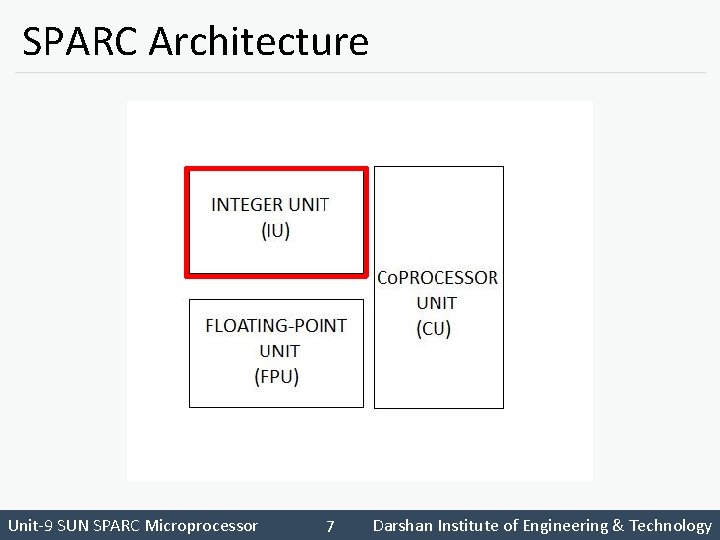

SPARC Architecture Unit-9 SUN SPARC Microprocessor 7 Darshan Institute of Engineering & Technology

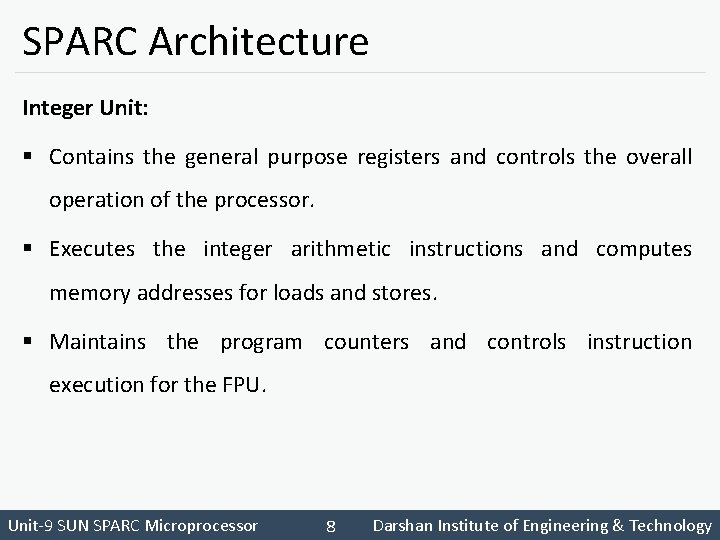

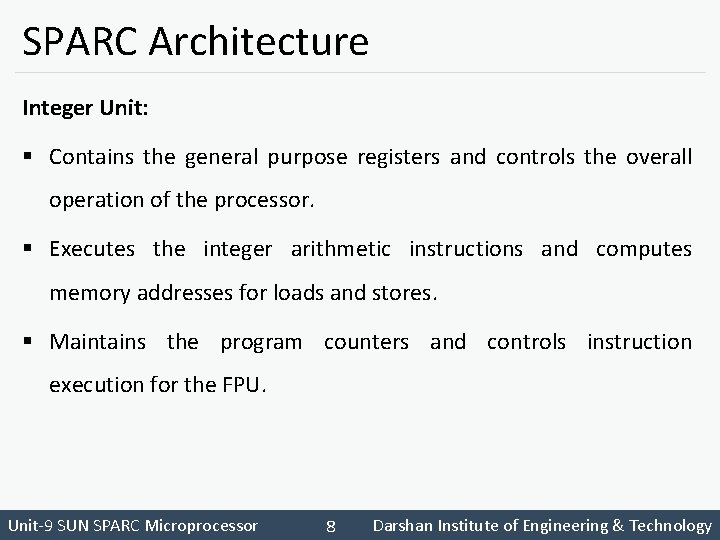

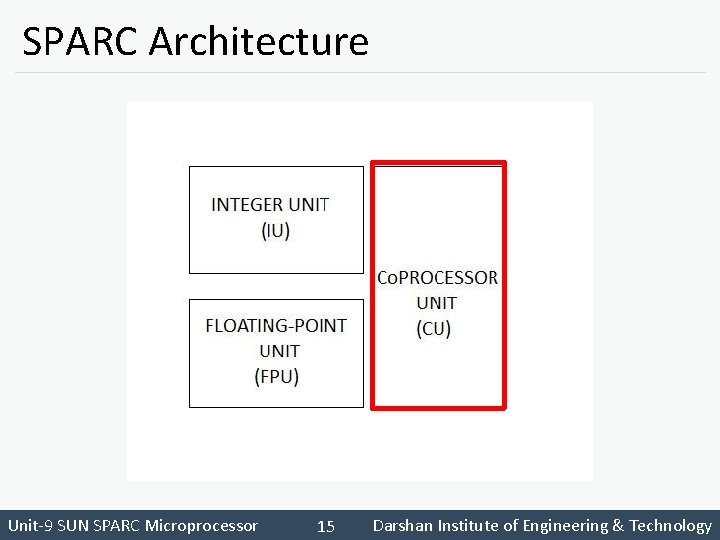

SPARC Architecture Integer Unit: § Contains the general purpose registers and controls the overall operation of the processor. § Executes the integer arithmetic instructions and computes memory addresses for loads and stores. § Maintains the program counters and controls instruction execution for the FPU. Unit-9 SUN SPARC Microprocessor 8 Darshan Institute of Engineering & Technology

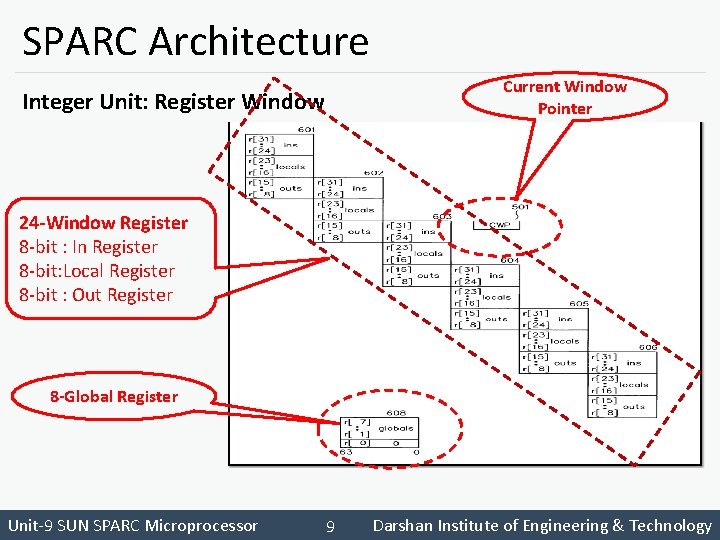

SPARC Architecture Current Window Pointer Integer Unit: Register Window 24 -Window Register 8 -bit : In Register 8 -bit: Local Register 8 -bit : Out Register 8 -Global Register Unit-9 SUN SPARC Microprocessor 9 Darshan Institute of Engineering & Technology

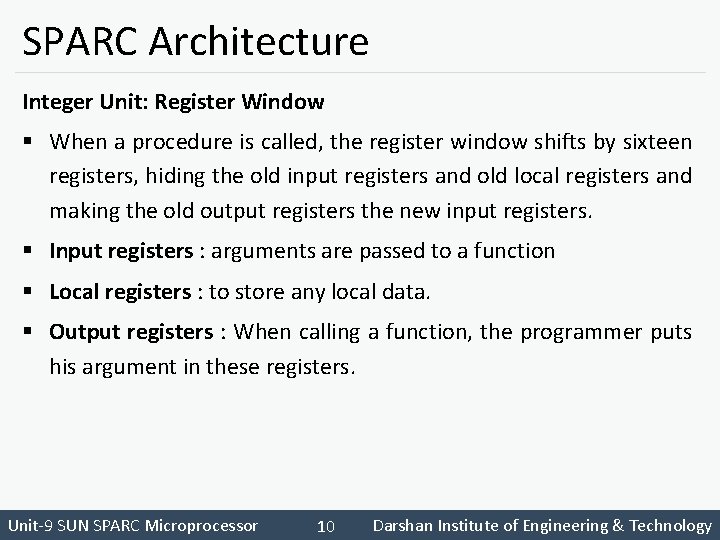

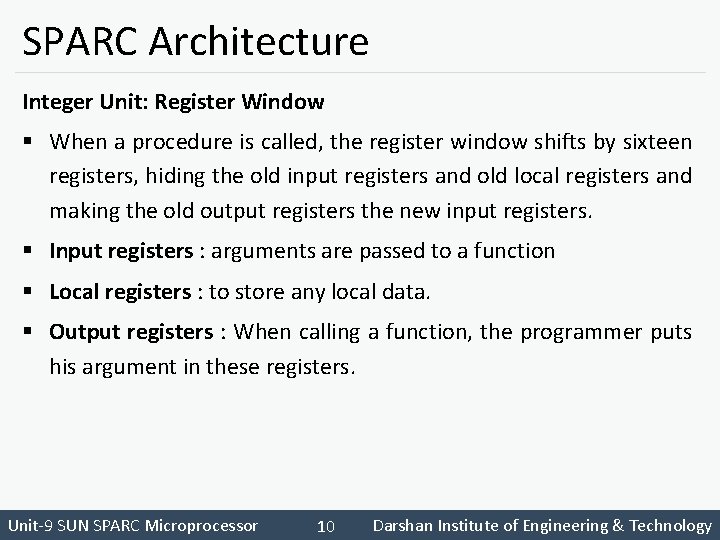

SPARC Architecture Integer Unit: Register Window § When a procedure is called, the register window shifts by sixteen registers, hiding the old input registers and old local registers and making the old output registers the new input registers. § Input registers : arguments are passed to a function § Local registers : to store any local data. § Output registers : When calling a function, the programmer puts his argument in these registers. Unit-9 SUN SPARC Microprocessor 10 Darshan Institute of Engineering & Technology

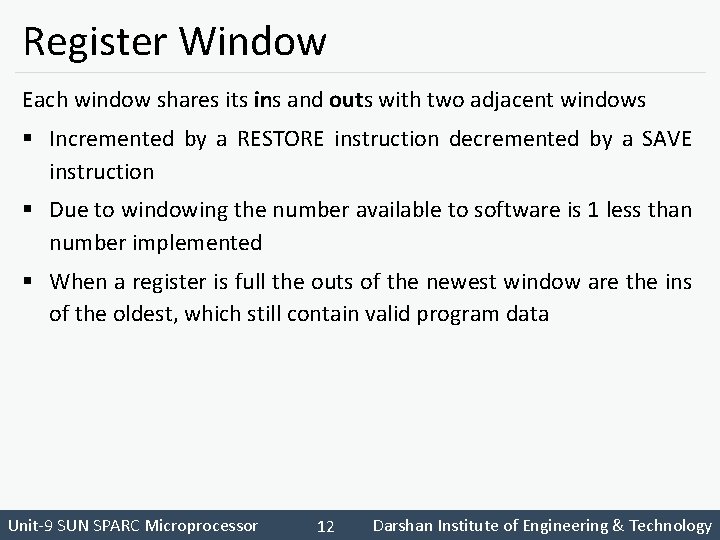

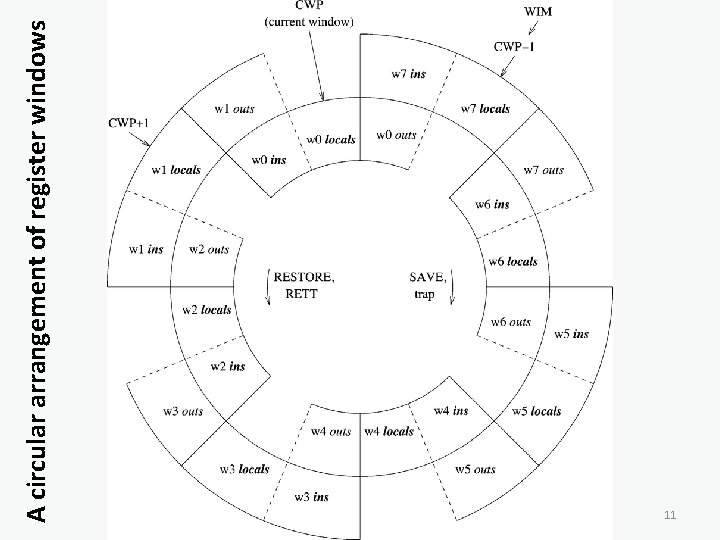

A circular arrangement of register windows 11

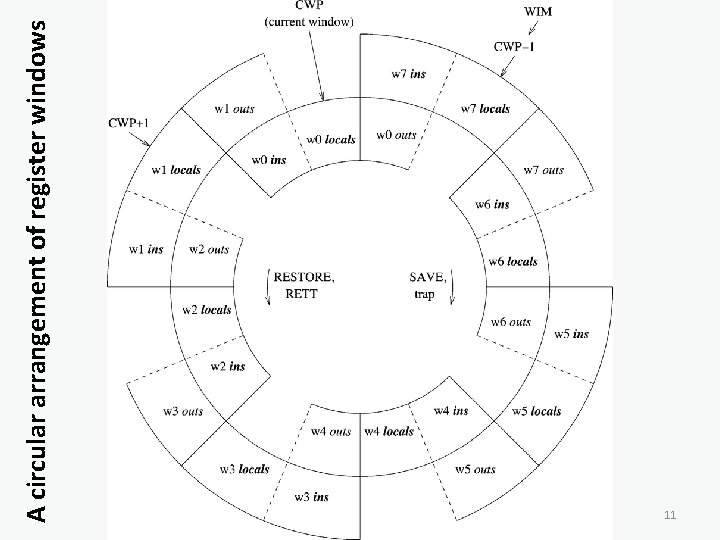

Register Window Each window shares its ins and outs with two adjacent windows § Incremented by a RESTORE instruction decremented by a SAVE instruction § Due to windowing the number available to software is 1 less than number implemented § When a register is full the outs of the newest window are the ins of the oldest, which still contain valid program data Unit-9 SUN SPARC Microprocessor 12 Darshan Institute of Engineering & Technology

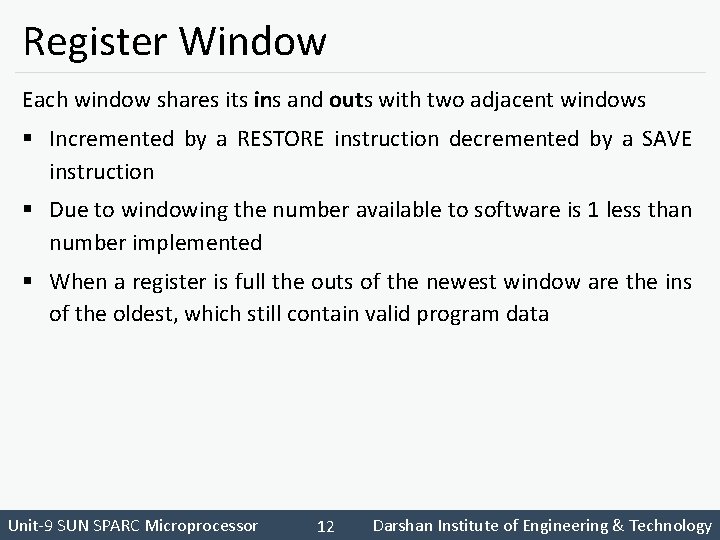

SPARC Architecture Unit-9 SUN SPARC Microprocessor 13 Darshan Institute of Engineering & Technology

The Floating-point Unit (FPU) § The FPU has 1. 32 Registers (32 -bit single-precision floating-point registers) 2. 32 Registers (64 -bit double-precision floating-point registers) 3. 16 Registers (128 -bit quad-precision floating-point registers) § Floating-point load/store instructions are used to move data between the FPU and memory. § The memory address is calculated by the IU. § Floating-Point operate (FPop) instructions perform the floatingpoint arithmetic operations and comparisons. Unit-9 SUN SPARC Microprocessor 14 Darshan Institute of Engineering & Technology

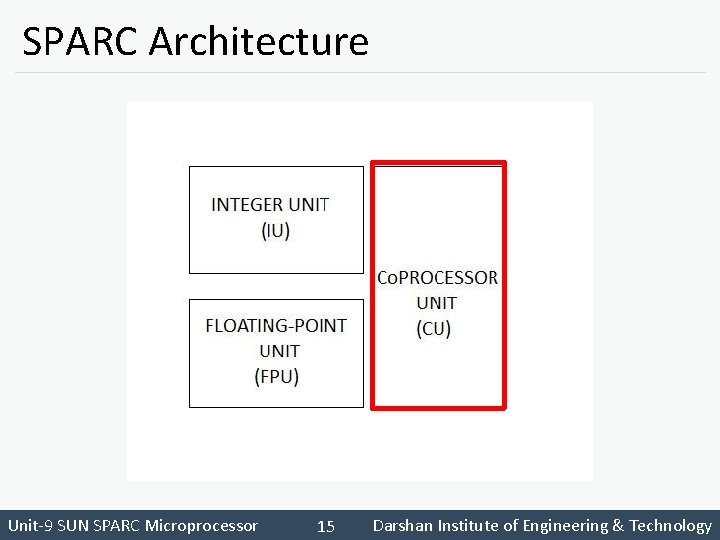

SPARC Architecture Unit-9 SUN SPARC Microprocessor 15 Darshan Institute of Engineering & Technology

Coprocessor Unit (CU) § The instruction set includes support for a single, implementationdependent coprocessor. § The coprocessor has its own set of registers. § Coprocessor load/store instructions are used to move data between the coprocessor registers and memory. Unit-9 SUN SPARC Microprocessor 16 Darshan Institute of Engineering & Technology

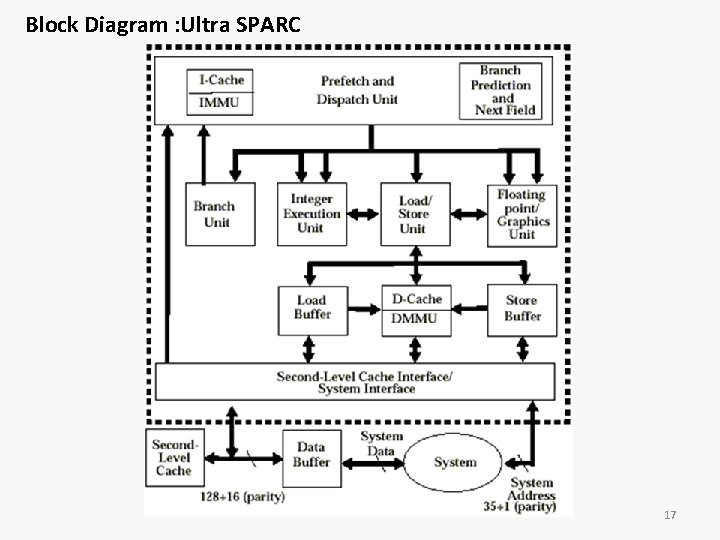

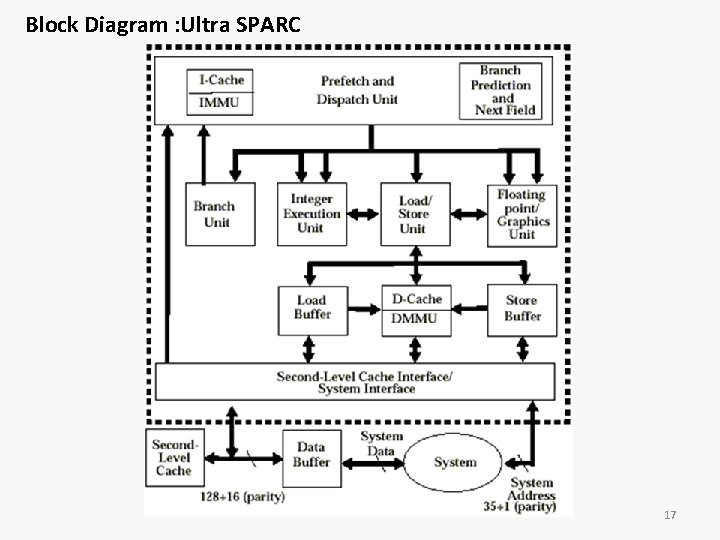

Block Diagram : Ultra SPARC 17

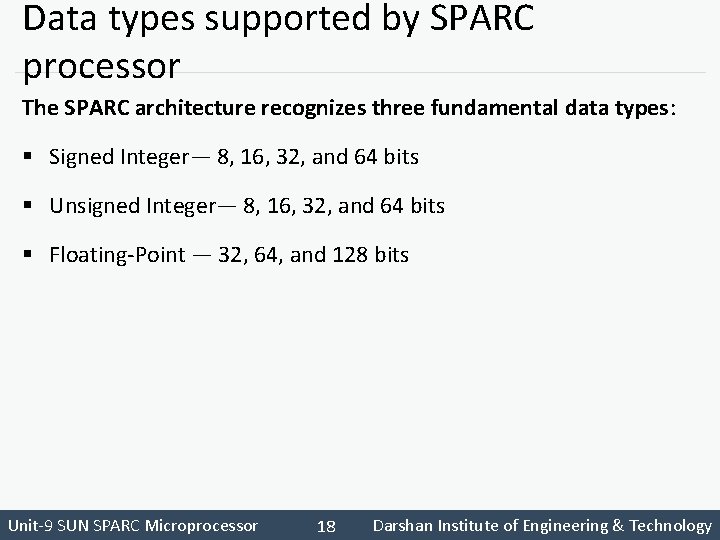

Data types supported by SPARC processor The SPARC architecture recognizes three fundamental data types: § Signed Integer— 8, 16, 32, and 64 bits § Unsigned Integer— 8, 16, 32, and 64 bits § Floating-Point — 32, 64, and 128 bits Unit-9 SUN SPARC Microprocessor 18 Darshan Institute of Engineering & Technology

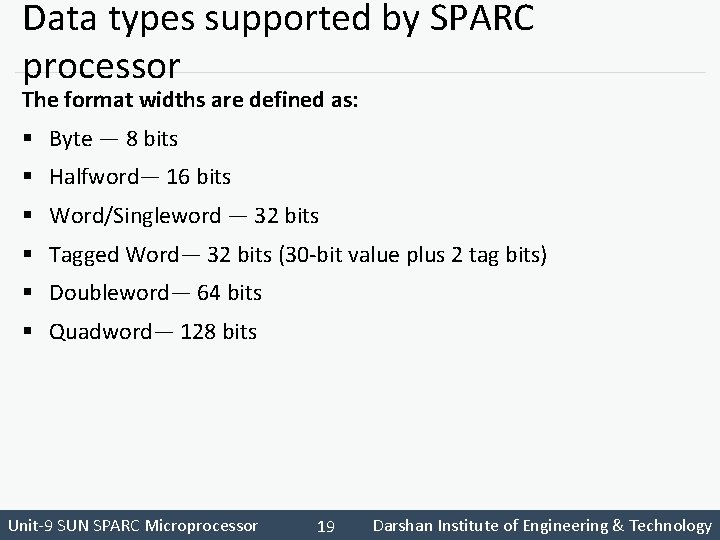

Data types supported by SPARC processor The format widths are defined as: § Byte — 8 bits § Halfword— 16 bits § Word/Singleword — 32 bits § Tagged Word— 32 bits (30 -bit value plus 2 tag bits) § Doubleword— 64 bits § Quadword— 128 bits Unit-9 SUN SPARC Microprocessor 19 Darshan Institute of Engineering & Technology