TDAQ for 2012 runs Gianluca Lamanna CERN Annual

- Slides: 29

“TDAQ for 2012 runs” Gianluca Lamanna (CERN) Annual review meeting 02. 04. 2012

Dry Run & Technical run • The October Technical Run is a good opportunity to test the TDAQ structure and to readout data for detector calibration. • The TDAQ is a relatively complex system • To better take advantage of the beam time available, it’s mandatory to test all electronics equipments that will be used in the technical run Dry Run will start July 15 (for 1 month) • Some amendment to this law is possible in case of no interference with other systems.

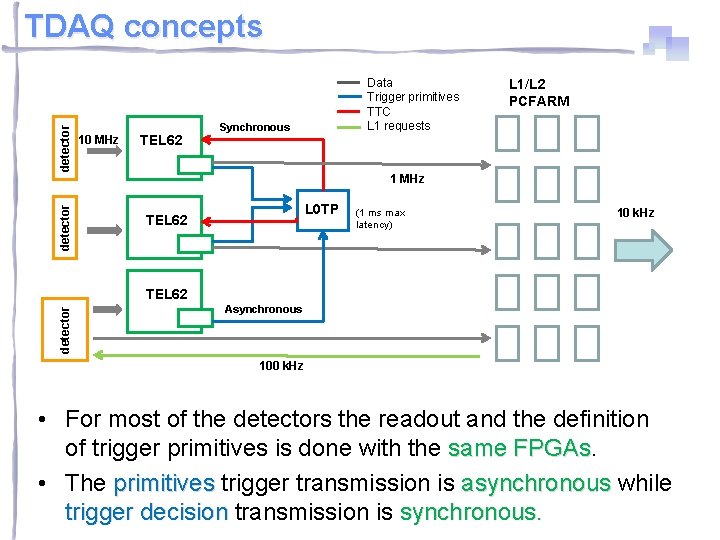

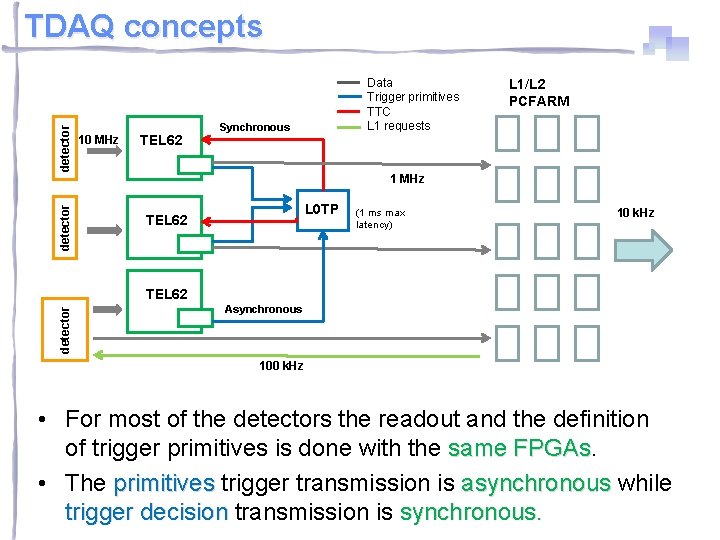

detector TDAQ concepts 10 MHz TEL 62 Data Trigger primitives TTC L 1 requests Synchronous L 1/L 2 PCFARM detector 1 MHz L 0 TP TEL 62 (1 ms max latency) 10 k. Hz detector TEL 62 Asynchronous 100 k. Hz • For most of the detectors the readout and the definition of trigger primitives is done with the same FPGAs • The primitives trigger transmission is asynchronous while trigger decision transmission is synchronous.

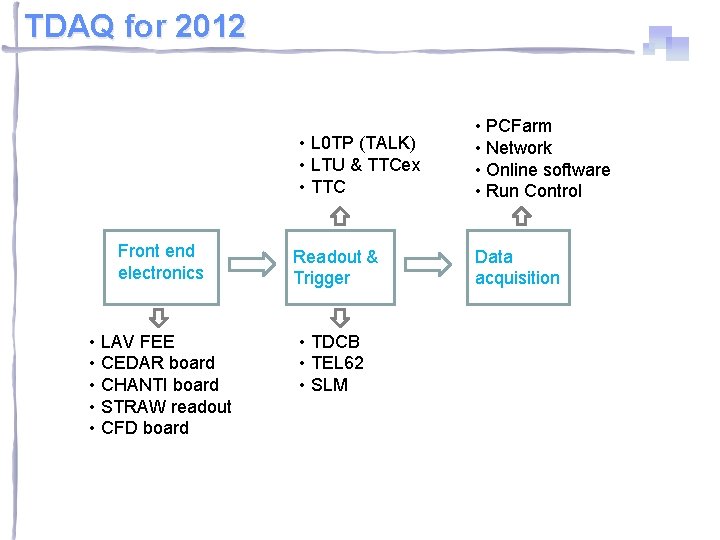

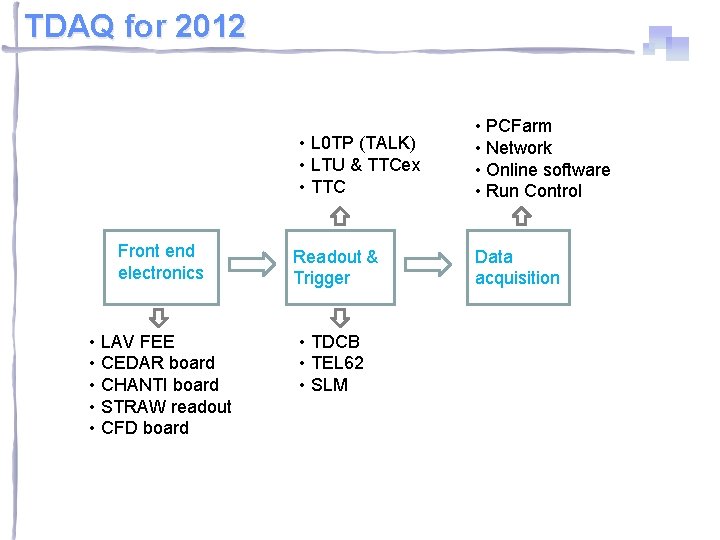

TDAQ for 2012 • L 0 TP (TALK) • LTU & TTCex • TTC Front end electronics Readout & Trigger • LAV FEE • CEDAR board • CHANTI board • STRAW readout • CFD board • TDCB • TEL 62 • SLM • PCFarm • Network • Online software • Run Control Data acquisition

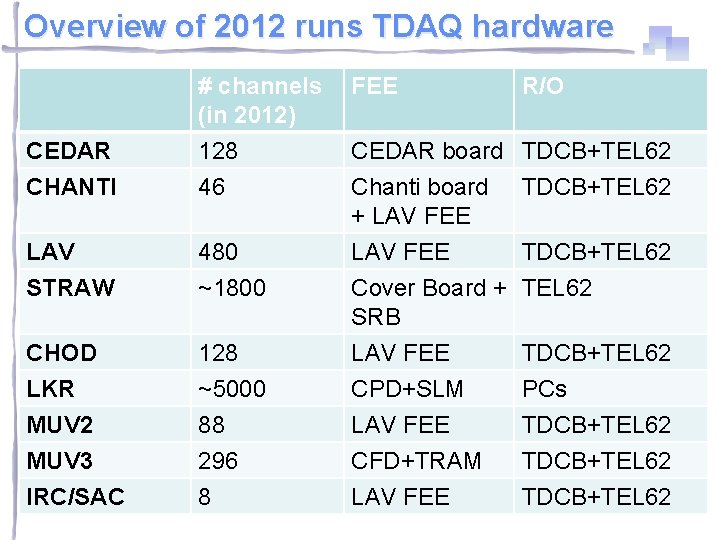

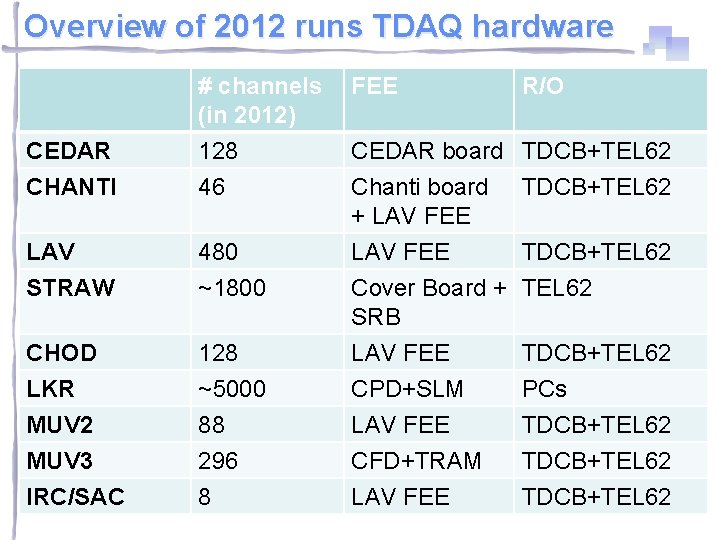

Overview of 2012 runs TDAQ hardware FEE CEDAR CHANTI # channels (in 2012) 128 46 R/O LAV 480 LAV FEE TDCB+TEL 62 STRAW ~1800 TEL 62 CHOD LKR MUV 2 MUV 3 IRC/SAC 128 ~5000 88 296 8 Cover Board + SRB LAV FEE CPD+SLM LAV FEE CFD+TRAM LAV FEE CEDAR board TDCB+TEL 62 Chanti board TDCB+TEL 62 + LAV FEE TDCB+TEL 62 PCs TDCB+TEL 62

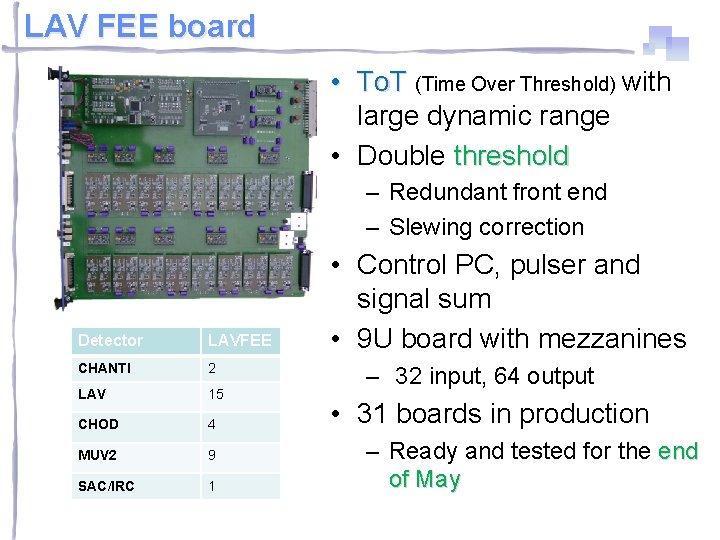

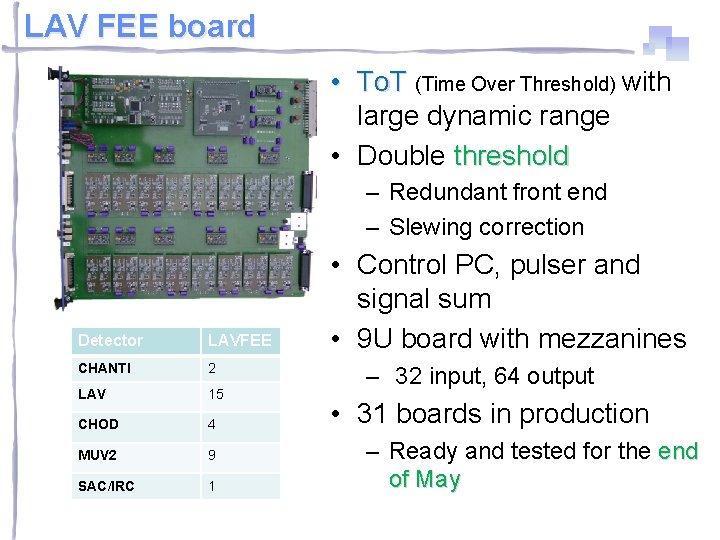

LAV FEE board • To. T (Time Over Threshold) with large dynamic range • Double threshold – Redundant front end – Slewing correction Detector LAVFEE CHANTI 2 LAV 15 CHOD 4 MUV 2 9 SAC/IRC 1 • Control PC, pulser and signal sum • 9 U board with mezzanines – 32 input, 64 output • 31 boards in production – Ready and tested for the end of May

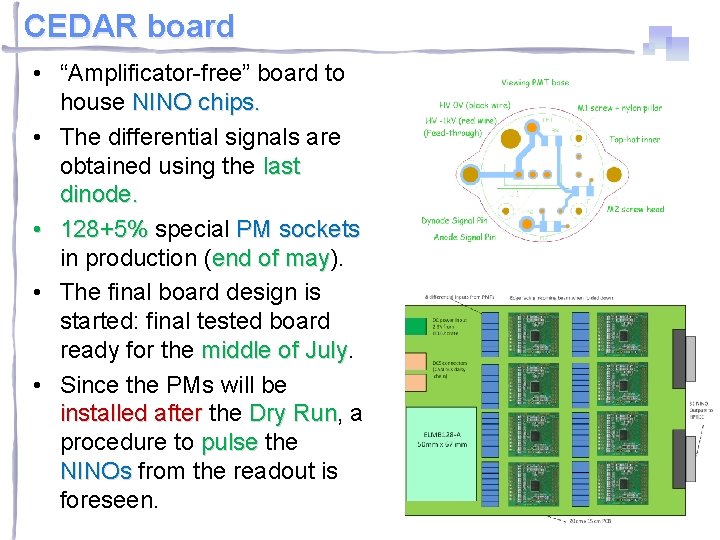

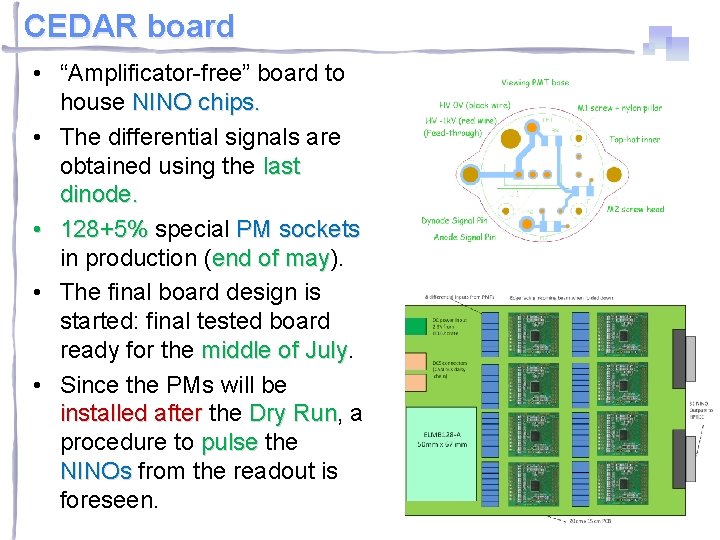

CEDAR board • “Amplificator-free” board to house NINO chips. • The differential signals are obtained using the last dinode. • 128+5% special PM sockets in production (end of may). may • The final board design is started: final tested board ready for the middle of July • Since the PMs will be installed after the Dry Run, Run a procedure to pulse the NINOs from the readout is foreseen.

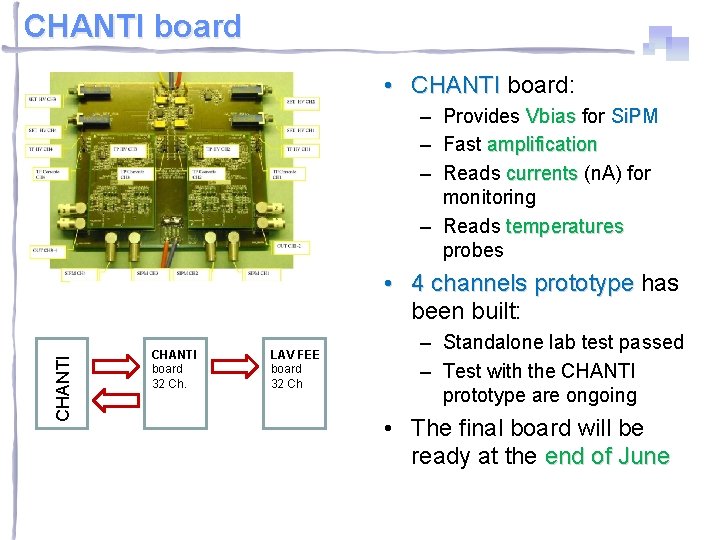

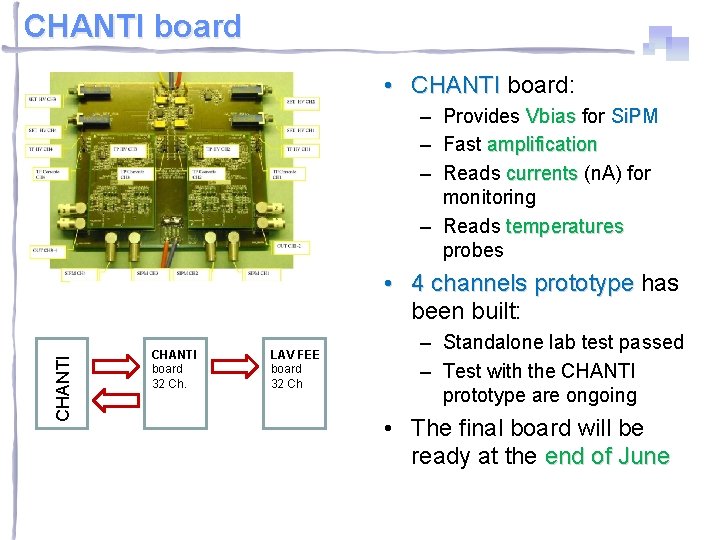

CHANTI board • CHANTI board: – Provides Vbias for Si. PM – Fast amplification – Reads currents (n. A) for monitoring – Reads temperatures probes CHANTI • 4 channels prototype has been built: CHANTI board 32 Ch. LAV FEE board 32 Ch – Standalone lab test passed – Test with the CHANTI prototype are ongoing • The final board will be ready at the end of June

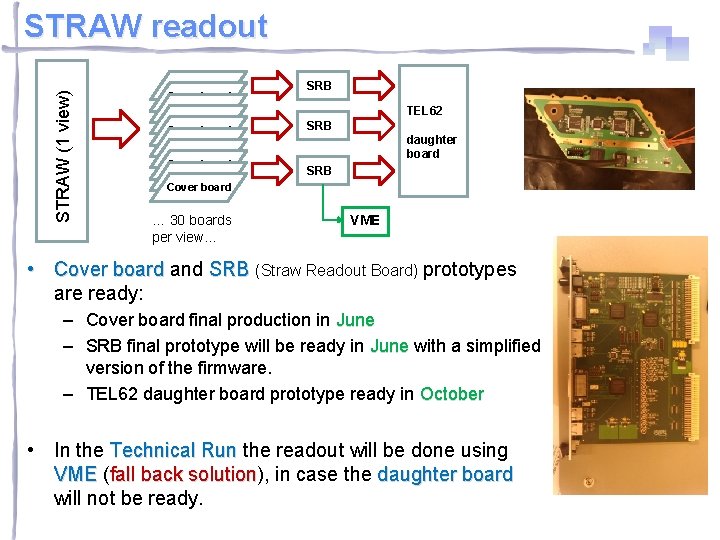

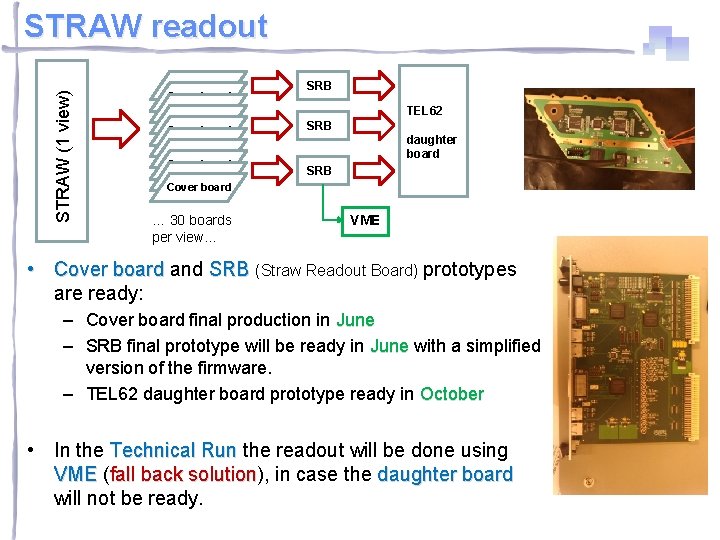

STRAW (1 view) STRAW readout Cover board Cover board Cover board … 30 boards per view… SRB TEL 62 SRB daughter board SRB VME • Cover board and SRB (Straw Readout Board) prototypes are ready: – Cover board final production in June – SRB final prototype will be ready in June with a simplified version of the firmware. – TEL 62 daughter board prototype ready in October • In the Technical Run the readout will be done using VME (fall back solution), solution in case the daughter board will not be ready.

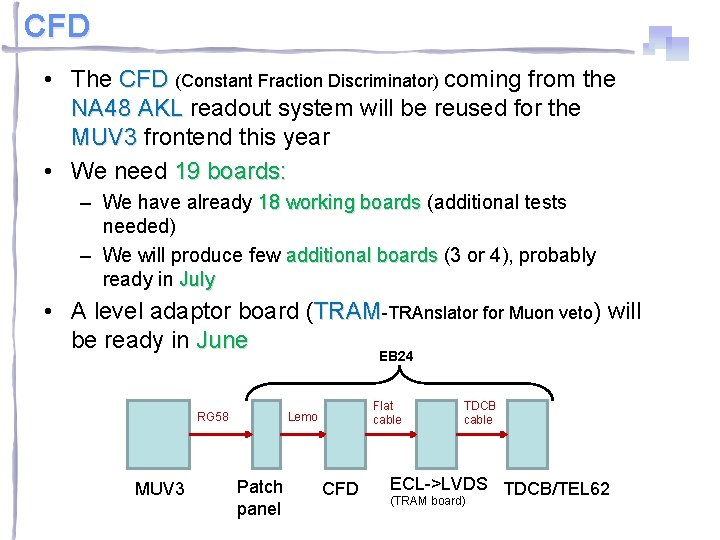

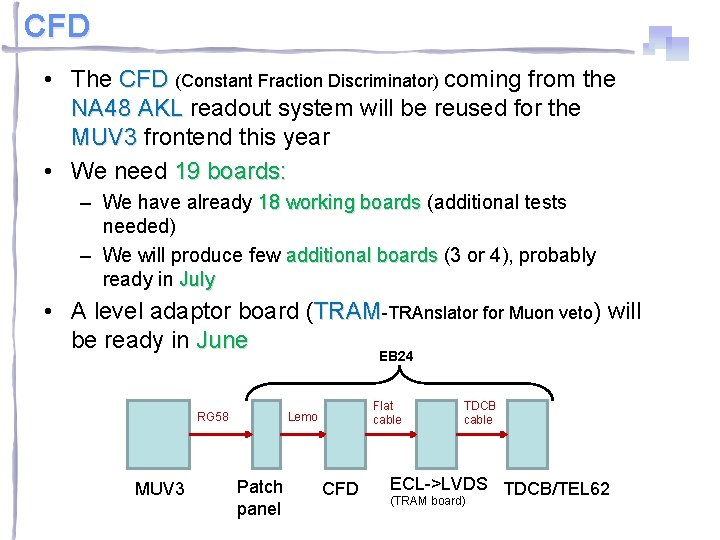

CFD • The CFD (Constant Fraction Discriminator) coming from the NA 48 AKL readout system will be reused for the MUV 3 frontend this year • We need 19 boards: – We have already 18 working boards (additional tests needed) – We will produce few additional boards (3 or 4), probably ready in July • A level adaptor board (TRAM-TRAnslator for Muon veto) will be ready in June EB 24 RG 58 MUV 3 Flat cable Lemo Patch panel CFD TDCB cable ECL->LVDS TDCB/TEL 62 (TRAM board)

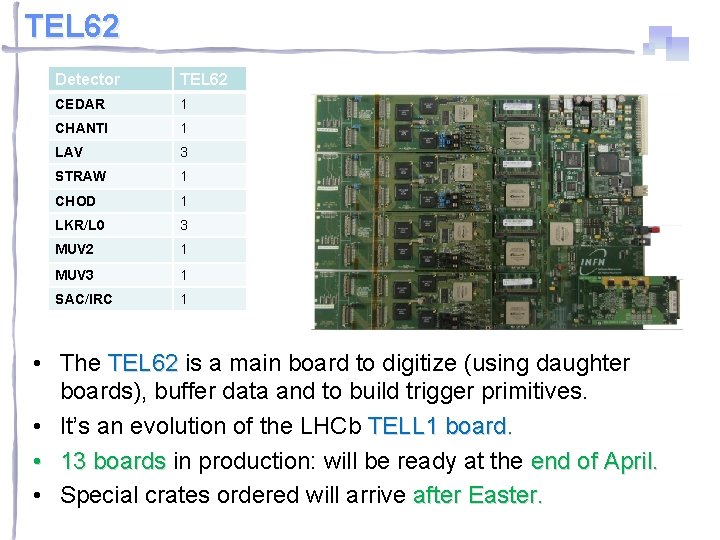

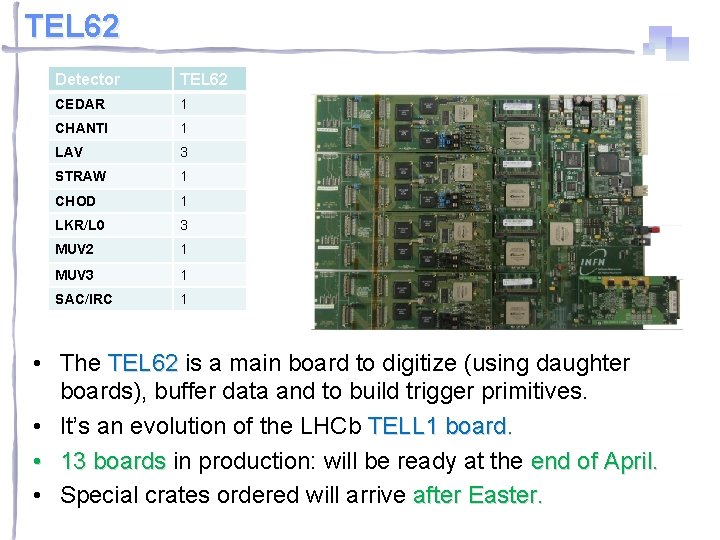

TEL 62 Detector TEL 62 CEDAR 1 CHANTI 1 LAV 3 STRAW 1 CHOD 1 LKR/L 0 3 MUV 2 1 MUV 3 1 SAC/IRC 1 • The TEL 62 is a main board to digitize (using daughter boards), buffer data and to build trigger primitives. • It’s an evolution of the LHCb TELL 1 board. • 13 boards in production: will be ready at the end of April. • Special crates ordered will arrive after Easter.

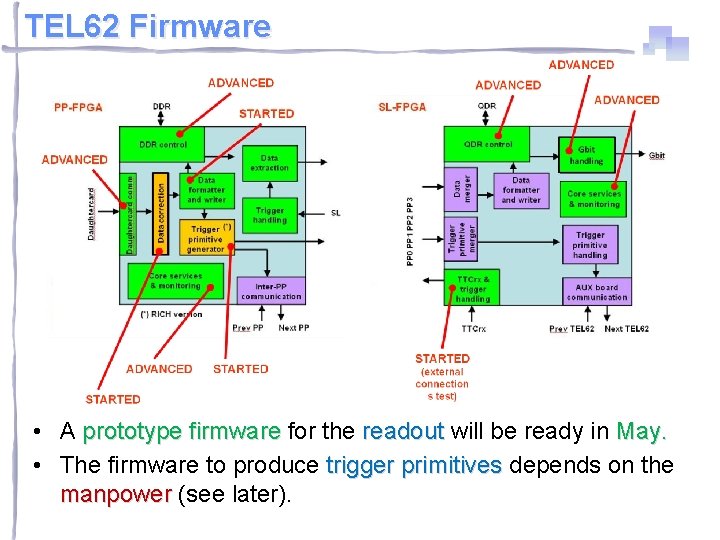

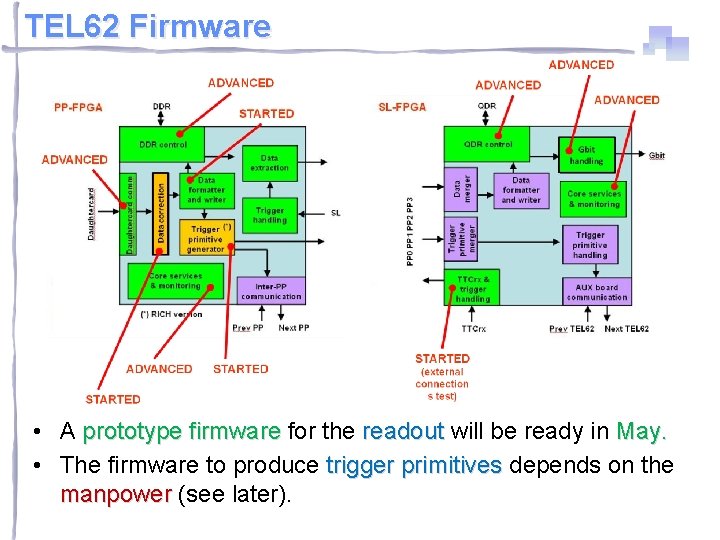

TEL 62 Firmware • A prototype firmware for the readout will be ready in May. • The firmware to produce trigger primitives depends on the manpower (see later).

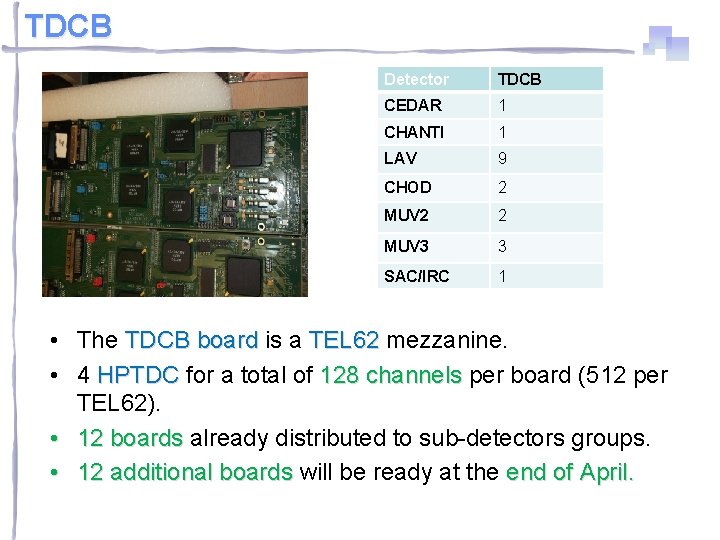

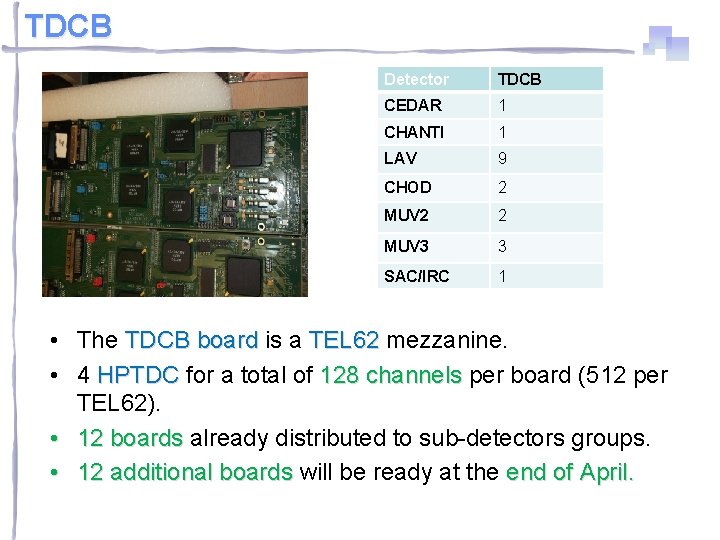

TDCB Detector TDCB CEDAR 1 CHANTI 1 LAV 9 CHOD 2 MUV 2 2 MUV 3 3 SAC/IRC 1 • The TDCB board is a TEL 62 mezzanine. • 4 HPTDC for a total of 128 channels per board (512 per TEL 62). • 12 boards already distributed to sub-detectors groups. • 12 additional boards will be ready at the end of April.

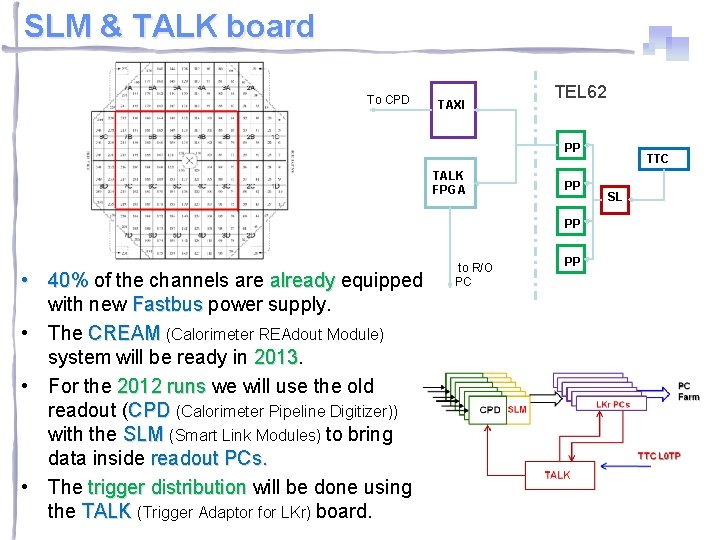

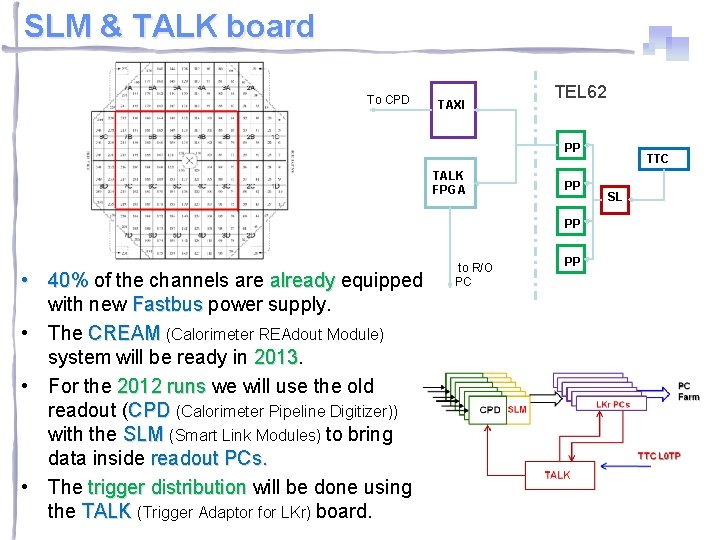

SLM & TALK board To CPD TAXI TEL 62 PP TALK FPGA PP PP • 40% of the channels are already equipped with new Fastbus power supply. • The CREAM (Calorimeter REAdout Module) system will be ready in 2013 • For the 2012 runs we will use the old readout (CPD (Calorimeter Pipeline Digitizer)) with the SLM (Smart Link Modules) to bring data inside readout PCs. • The trigger distribution will be done using the TALK (Trigger Adaptor for LKr) board. to R/O PC PP TTC SL

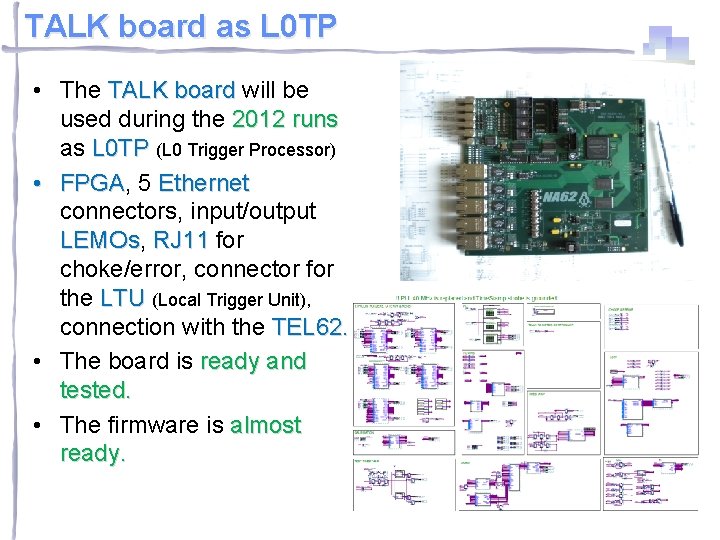

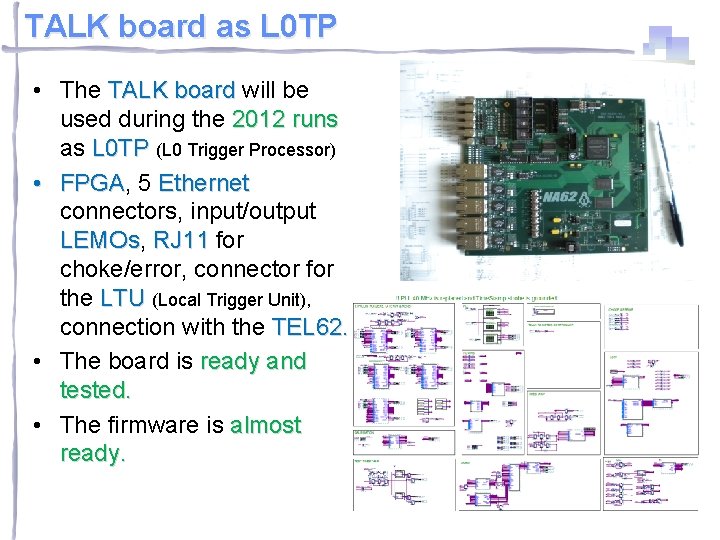

TALK board as L 0 TP • The TALK board will be used during the 2012 runs as L 0 TP (L 0 Trigger Processor) • FPGA, FPGA 5 Ethernet connectors, input/output LEMOs, LEMOs RJ 11 for choke/error, connector for the LTU (Local Trigger Unit), connection with the TEL 62. • The board is ready and tested. • The firmware is almost ready.

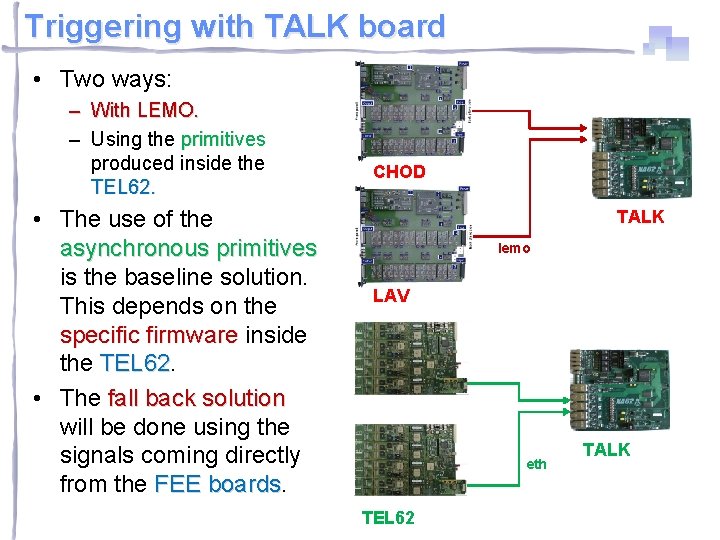

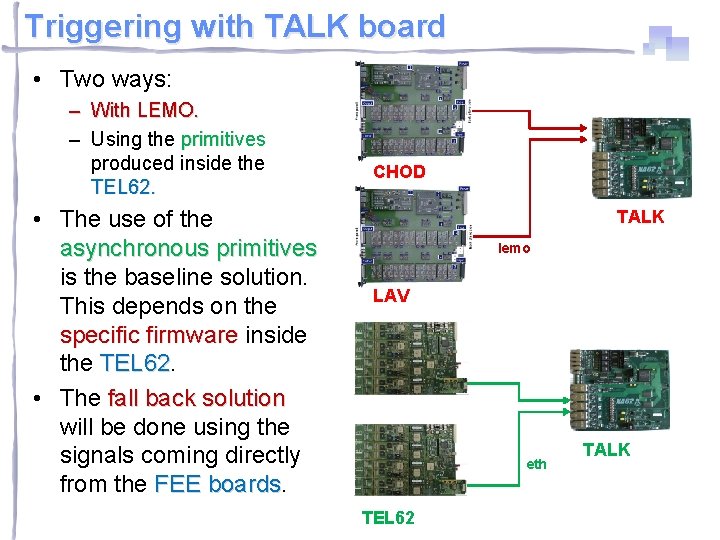

Triggering with TALK board • Two ways: – With LEMO. – Using the primitives produced inside the TEL 62. • The use of the asynchronous primitives is the baseline solution. This depends on the specific firmware inside the TEL 62 • The fall back solution will be done using the signals coming directly from the FEE boards CHOD TALK lemo LAV eth TEL 62 TALK

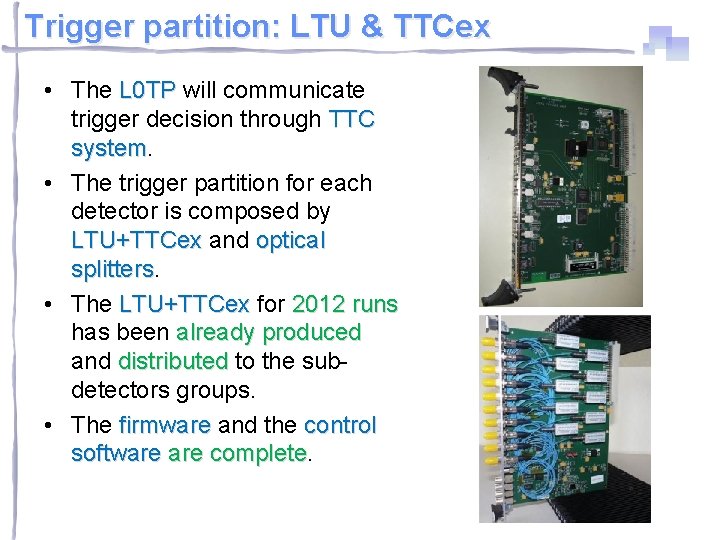

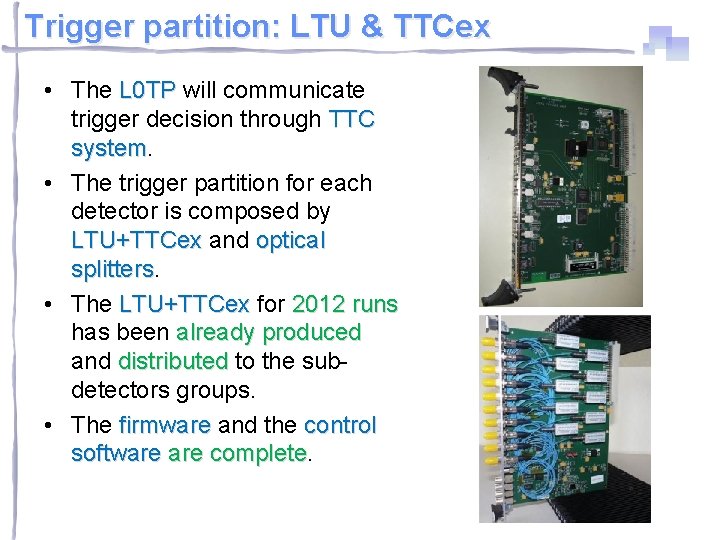

Trigger partition: LTU & TTCex • The L 0 TP will communicate trigger decision through TTC system • The trigger partition for each detector is composed by LTU+TTCex and optical splitters • The LTU+TTCex for 2012 runs has been already produced and distributed to the subdetectors groups. • The firmware and the control software complete

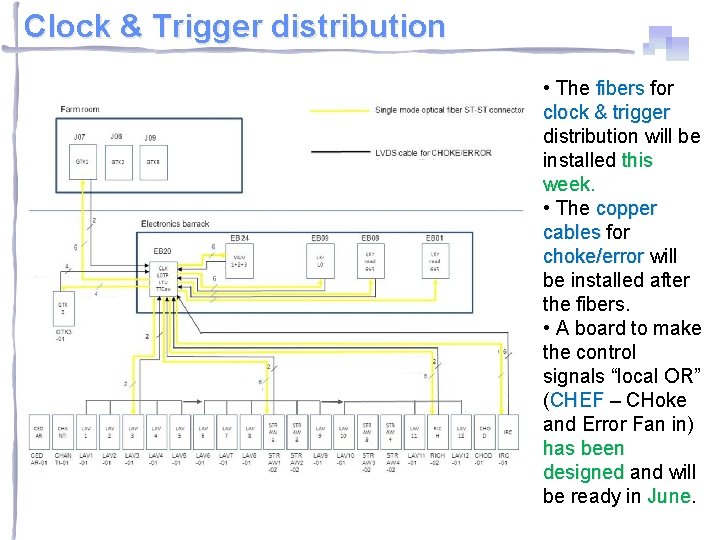

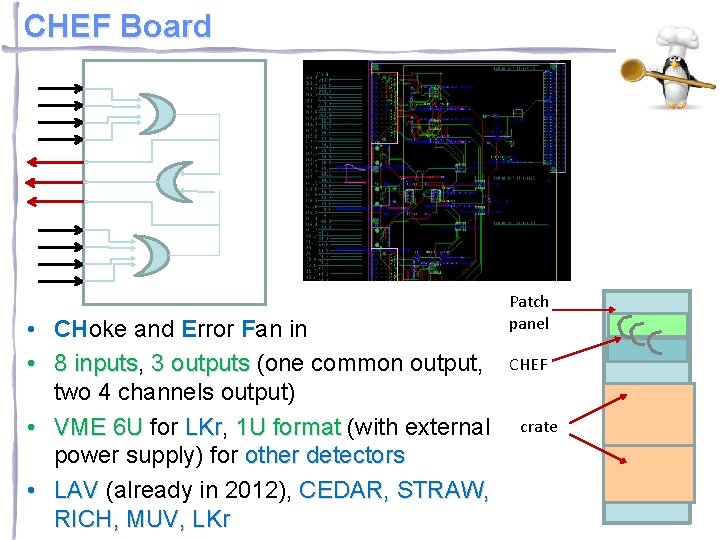

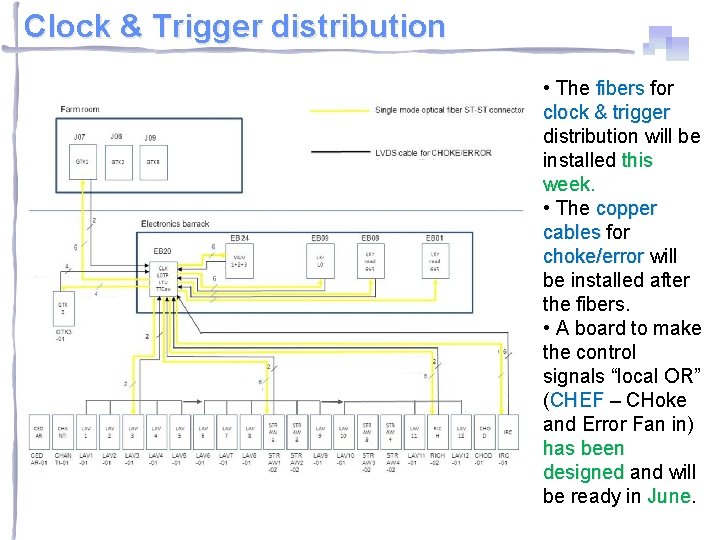

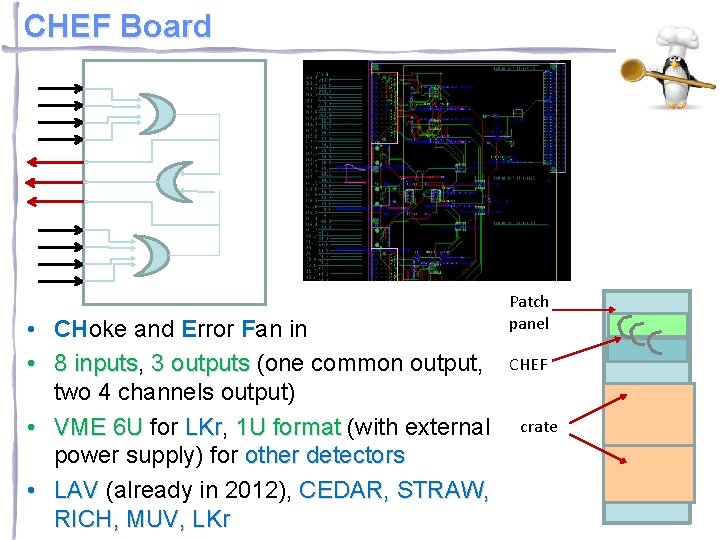

Clock & Trigger distribution • The fibers for clock & trigger distribution will be installed this week. • The copper cables for choke/error will be installed after the fibers. • A board to make the control signals “local OR” (CHEF – CHoke and Error Fan in) has been designed and will be ready in June

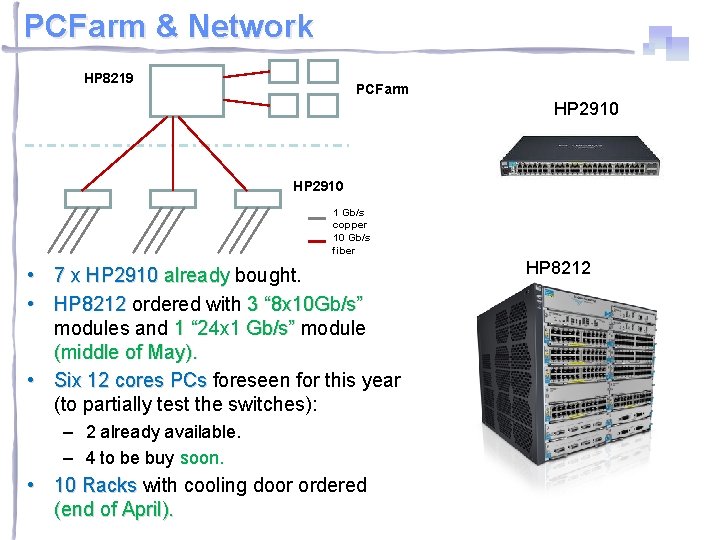

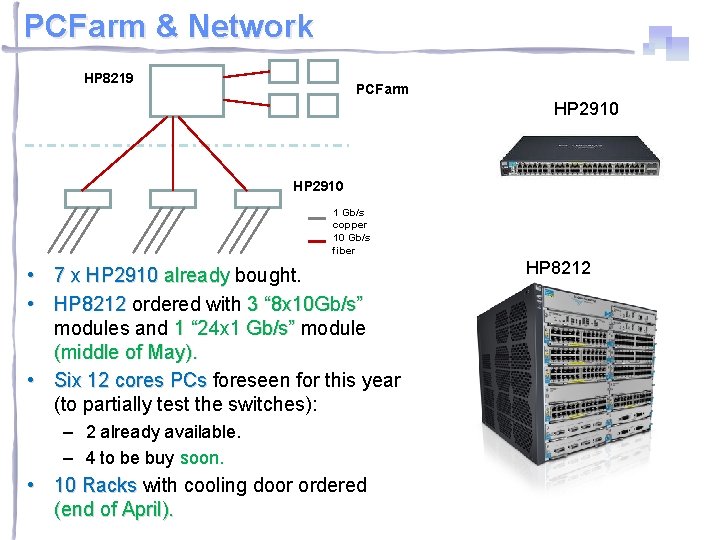

PCFarm & Network HP 8219 PCFarm HP 2910 1 Gb/s copper 10 Gb/s fiber • 7 x HP 2910 already bought. • HP 8212 ordered with 3 “ 8 x 10 Gb/s” modules and 1 “ 24 x 1 Gb/s” module (middle of May). • Six 12 cores PCs foreseen for this year (to partially test the switches): – 2 already available. – 4 to be buy soon. • 10 Racks with cooling door ordered (end of April). HP 8212

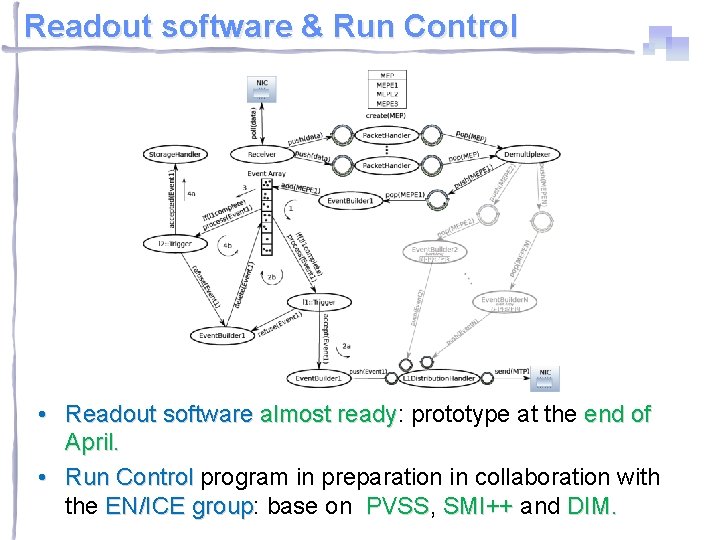

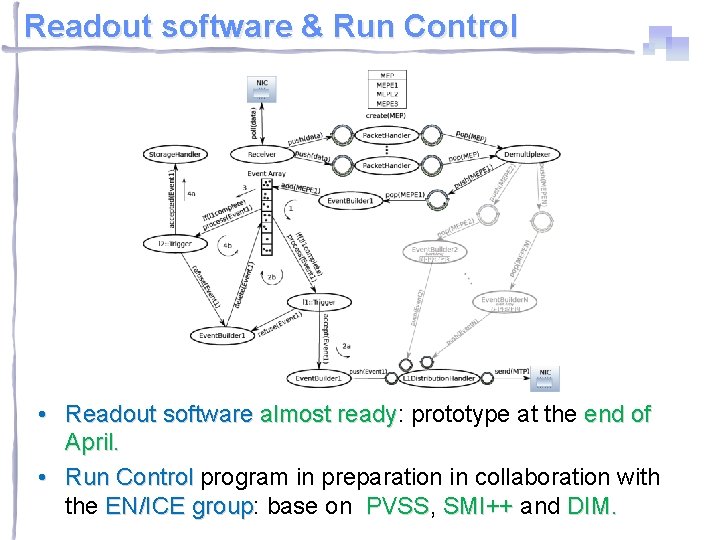

Readout software & Run Control • Readout software almost ready: ready prototype at the end of April. • Run Control program in preparation in collaboration with the EN/ICE group: group base on PVSS, PVSS SMI++ and DIM.

Summary • Most of the Hardware will be ready in June • We will have readout firmware for TEL 62 in May We hope to have the firmware to test the asynchronous part of the TDAQ system (it depends on man power). power • Network, trigger distribution and control lines infrastructure will be completed in April. • The PCFarm and the software will be tested in May

SPARES

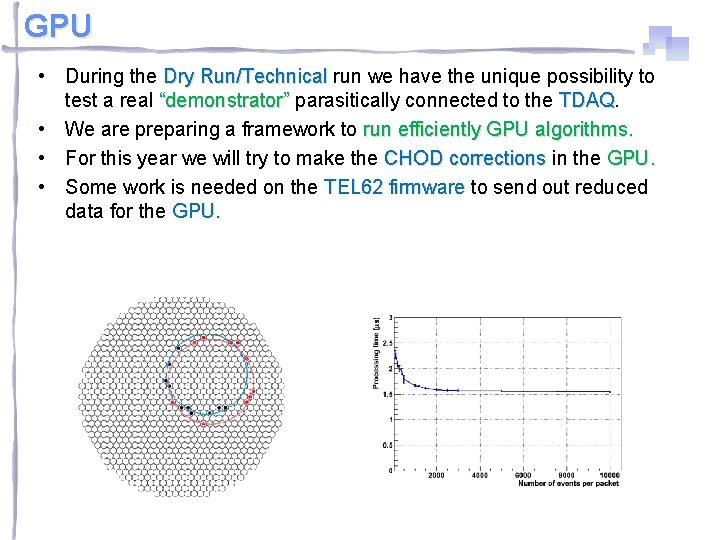

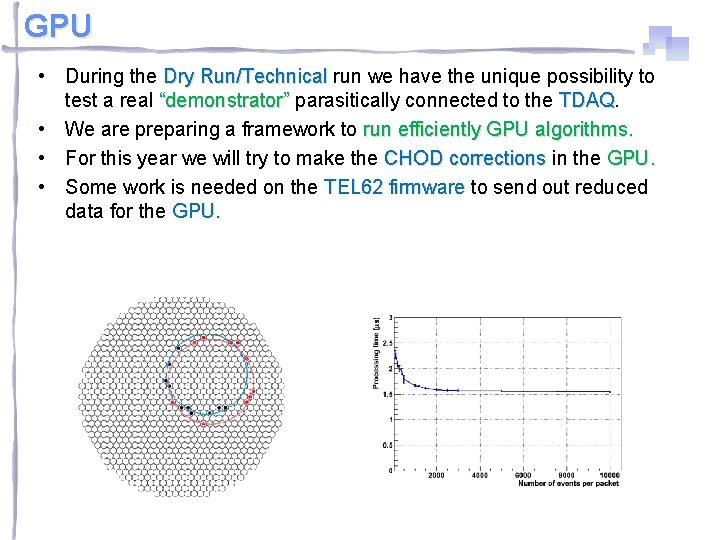

GPU • During the Dry Run/Technical run we have the unique possibility to test a real “demonstrator” parasitically connected to the TDAQ • We are preparing a framework to run efficiently GPU algorithms. • For this year we will try to make the CHOD corrections in the GPU. • Some work is needed on the TEL 62 firmware to send out reduced data for the GPU.

TRAM board • TRAnslator for Muon veto • ECL TTL LVDS • Each board: 64 inputs on 4 cables, two TDCB standard cable in outputs • 9 U TEL 62 format (+5 V, +3. 3 V from the connector) • The schematic has been prepared by Riccardo and my self • Mainz will take care to make the layout and to produce the board

CHEF Board • CHoke and Error Fan in • 8 inputs, inputs 3 outputs (one common output, two 4 channels output) • VME 6 U for LKr, LKr 1 U format (with external power supply) for other detectors • LAV (already in 2012), CEDAR, STRAW, RICH, MUV, LKr Patch panel CHEF crate

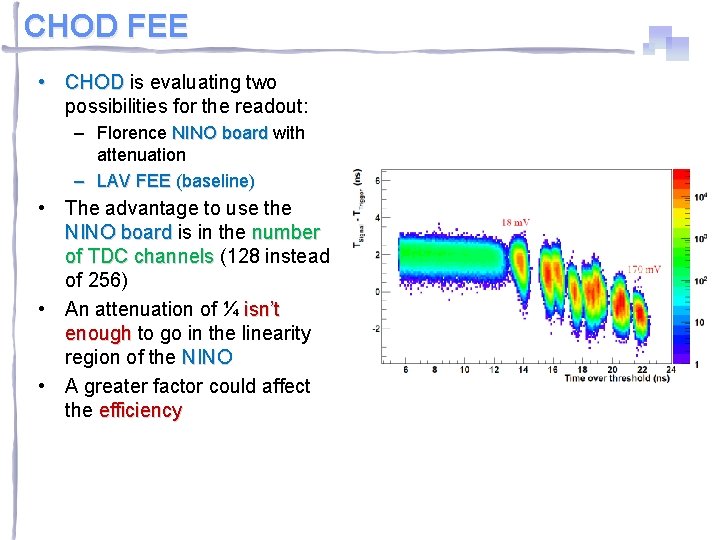

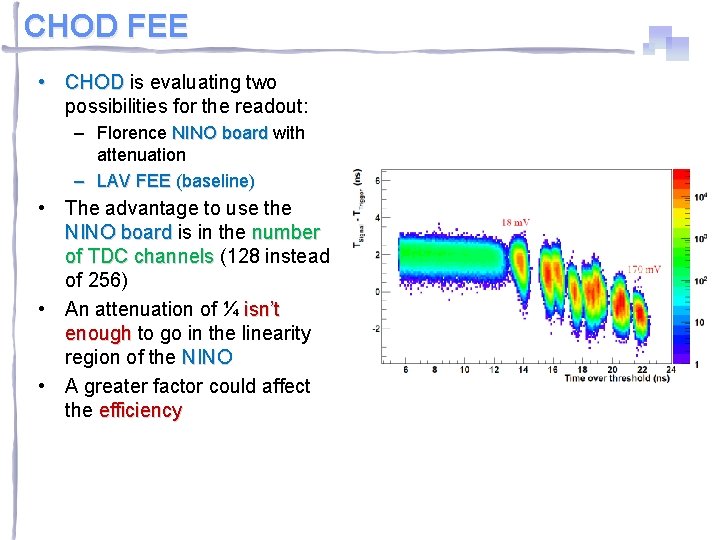

CHOD FEE • CHOD is evaluating two possibilities for the readout: – Florence NINO board with attenuation – LAV FEE (baseline) • The advantage to use the NINO board is in the number of TDC channels (128 instead of 256) • An attenuation of ¼ isn’t enough to go in the linearity region of the NINO • A greater factor could affect the efficiency

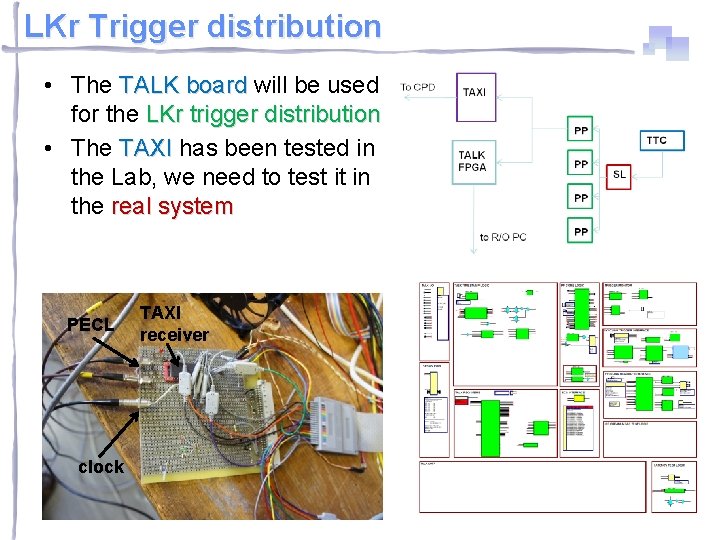

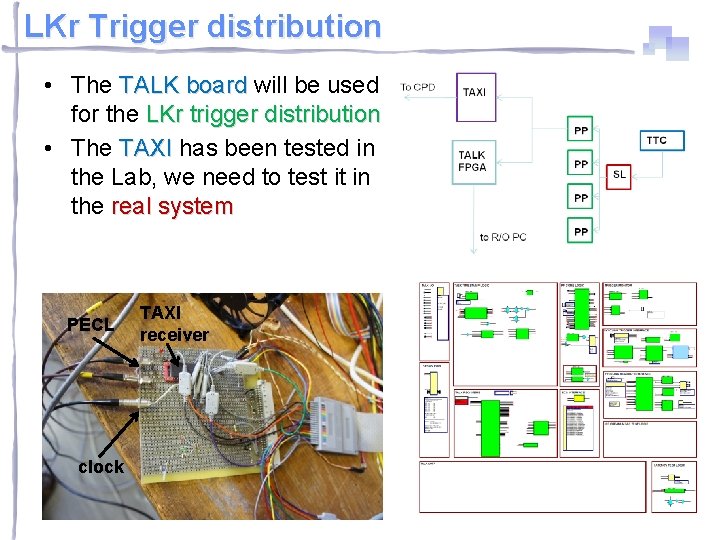

LKr Trigger distribution • The TALK board will be used for the LKr trigger distribution • The TAXI has been tested in the Lab, we need to test it in the real system PECL clock TAXI receiver

TALK firmware

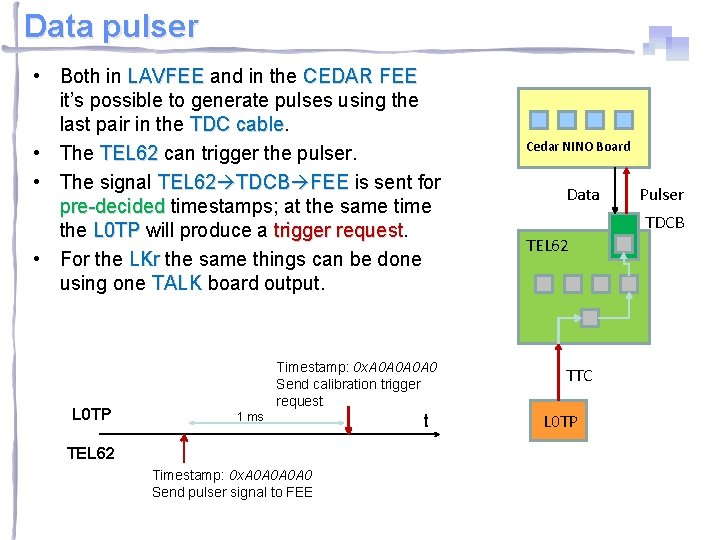

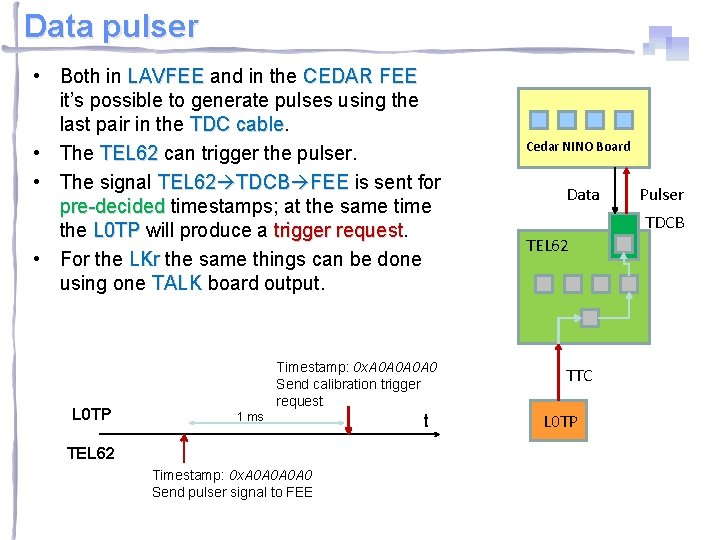

Data pulser • Both in LAVFEE and in the CEDAR FEE it’s possible to generate pulses using the last pair in the TDC cable • The TEL 62 can trigger the pulser. • The signal TEL 62 TDCB FEE is sent for pre-decided timestamps; at the same time the L 0 TP will produce a trigger request • For the LKr the same things can be done using one TALK board output. L 0 TP Timestamp: 0 x. A 0 A 0 Send calibration trigger request 1 ms TEL 62 Timestamp: 0 x. A 0 A 0 Send pulser signal to FEE t Cedar NINO Board Data Pulser TDCB TEL 62 TTC L 0 TP