TDAQ SLIM 5 TDAQ WP 3 Trigger and

- Slides: 15

TDAQ SLIM 5 TDAQ WP 3: Trigger and Data Acquisition LA PRIMA TAPPA Pisa - June 9, 2006 Mauro Dell'Orso - SLIM 5 Meeting 1

SLIM 5 TDAQ Milestone 2006 Novembre 2005 TDAQ • 31/12/06 Definizione dell’architettura TDAQ • Milestones correlate: – 30/6/06 Definizione dell’interfacciamento del pixel con la logica di lettura sparsificata – 30/9/06 Studio dei chip di lettura per strips esistenti, selezione di un chip per i test su fascio – 31/12/06 Definizione dell’architettura del Data Output Interface Pisa - June 9, 2006 Mauro Dell'Orso - SLIM 5 Meeting 2

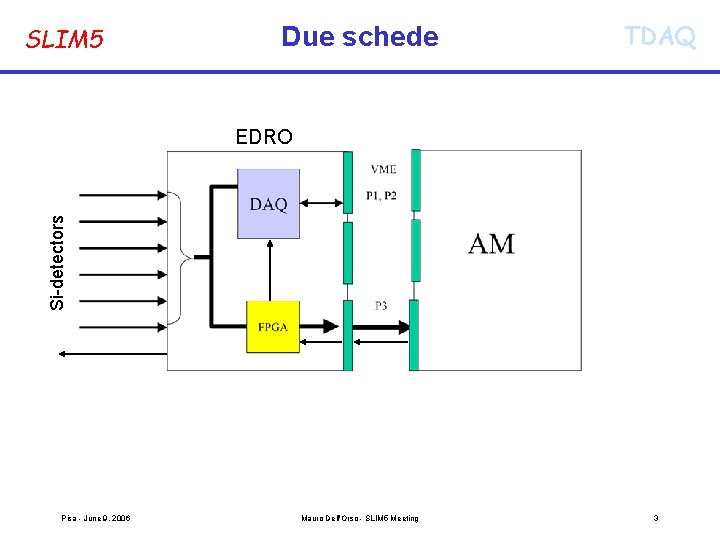

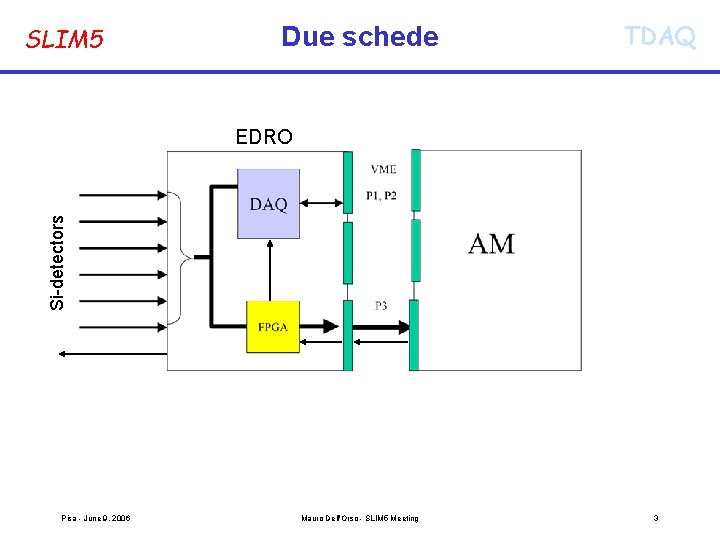

SLIM 5 Due schede TDAQ Si-detectors EDRO Pisa - June 9, 2006 Mauro Dell'Orso - SLIM 5 Meeting 3

Timing SLIM 5 Novembre 2005 TDAQ • Responsabilita` congiunta Pisa-Bologna • Questioni in sospeso: – Riferimento a un tipo di macchina definito (Super-B, ILC, SLHC, …) – Determinazione EE – Segnali di enable/reset al detector e al FE • Sincronia con l’estrazione del fascio • Acquisizione dell’intero spill o di frazione – Quali segnali sono necessari ai detector e per cosa • Per time stamp e per altre esigenze • Ai rivelatori in senso stretto e al front-end – Come “emulare” al test beam le condizioni alla macchina prescelta • Interazione stretta con WP 1 – Morsani e Ratti, Re, Rizzo, Ro… • Milestone proposta (interna): 10/6/2005 Pisa - June 9, 2006 Mauro Dell'Orso - SLIM 5 Meeting 4

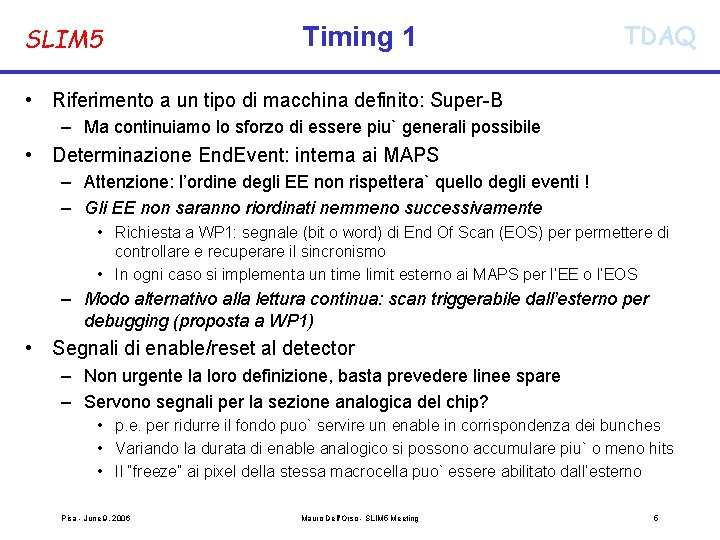

SLIM 5 Timing 1 TDAQ • Riferimento a un tipo di macchina definito: Super-B – Ma continuiamo lo sforzo di essere piu` generali possibile • Determinazione End. Event: interna ai MAPS – Attenzione: l’ordine degli EE non rispettera` quello degli eventi ! – Gli EE non saranno riordinati nemmeno successivamente • Richiesta a WP 1: segnale (bit o word) di End Of Scan (EOS) permettere di controllare e recuperare il sincronismo • In ogni caso si implementa un time limit esterno ai MAPS per l’EE o l’EOS – Modo alternativo alla lettura continua: scan triggerabile dall’esterno per debugging (proposta a WP 1) • Segnali di enable/reset al detector – Non urgente la loro definizione, basta prevedere linee spare – Servono segnali per la sezione analogica del chip? • p. e. per ridurre il fondo puo` servire un enable in corrispondenza dei bunches • Variando la durata di enable analogico si possono accumulare piu` o meno hits • Il “freeze” ai pixel della stessa macrocella puo` essere abilitato dall’esterno Pisa - June 9, 2006 Mauro Dell'Orso - SLIM 5 Meeting 5

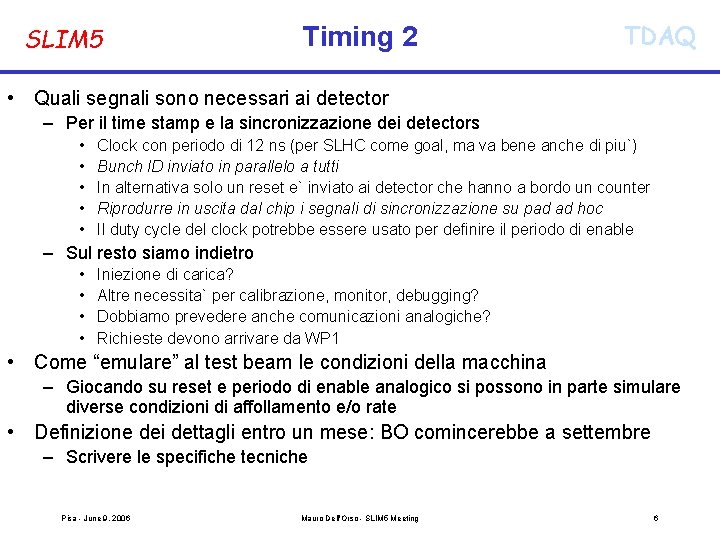

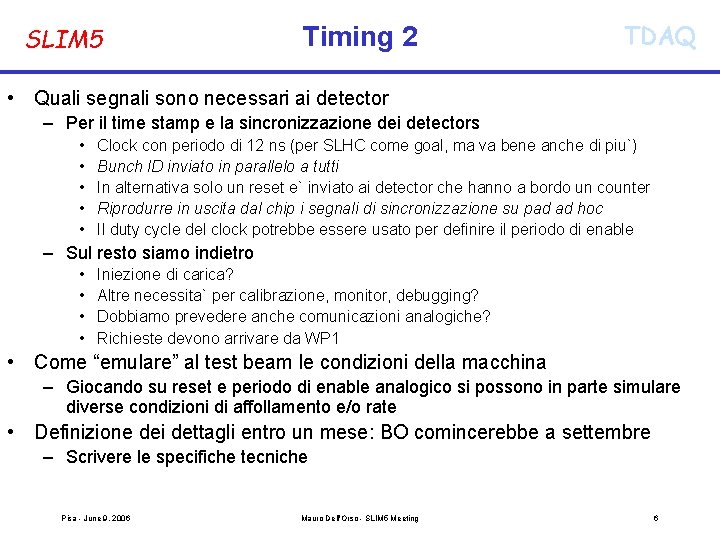

SLIM 5 Timing 2 TDAQ • Quali segnali sono necessari ai detector – Per il time stamp e la sincronizzazione dei detectors • • • Clock con periodo di 12 ns (per SLHC come goal, ma va bene anche di piu`) Bunch ID inviato in parallelo a tutti In alternativa solo un reset e` inviato ai detector che hanno a bordo un counter Riprodurre in uscita dal chip i segnali di sincronizzazione su pad ad hoc Il duty cycle del clock potrebbe essere usato per definire il periodo di enable – Sul resto siamo indietro • • Iniezione di carica? Altre necessita` per calibrazione, monitor, debugging? Dobbiamo prevedere anche comunicazioni analogiche? Richieste devono arrivare da WP 1 • Come “emulare” al test beam le condizioni della macchina – Giocando su reset e periodo di enable analogico si possono in parte simulare diverse condizioni di affollamento e/o rate • Definizione dei dettagli entro un mese: BO comincerebbe a settembre – Scrivere le specifiche tecniche Pisa - June 9, 2006 Mauro Dell'Orso - SLIM 5 Meeting 6

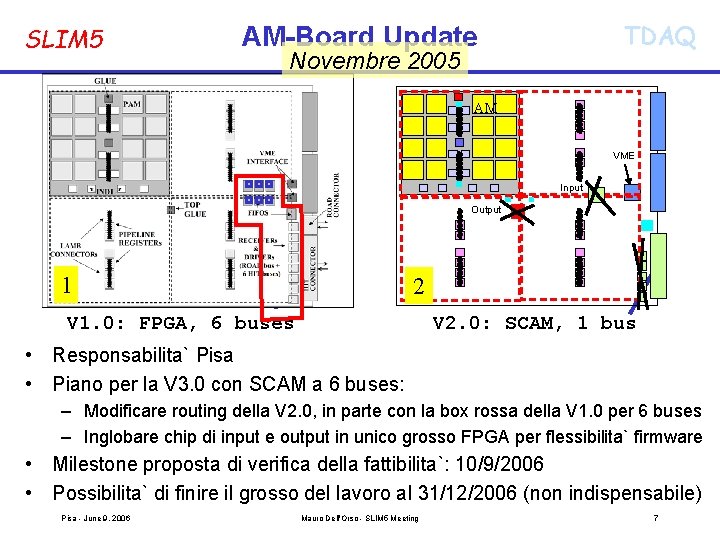

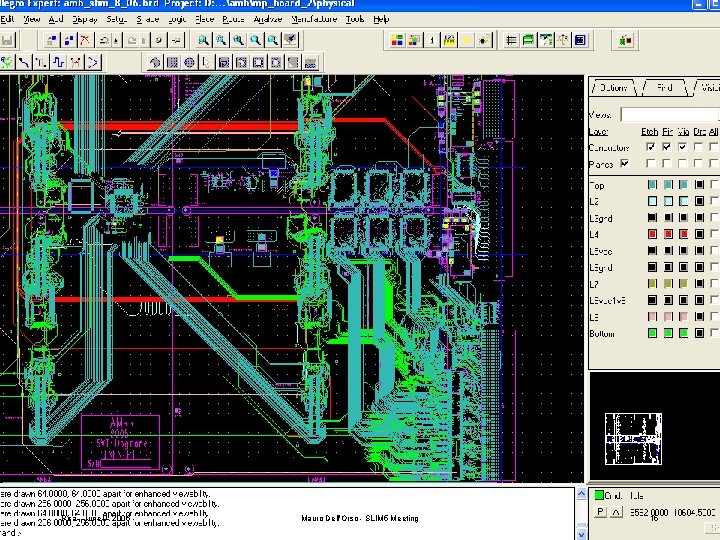

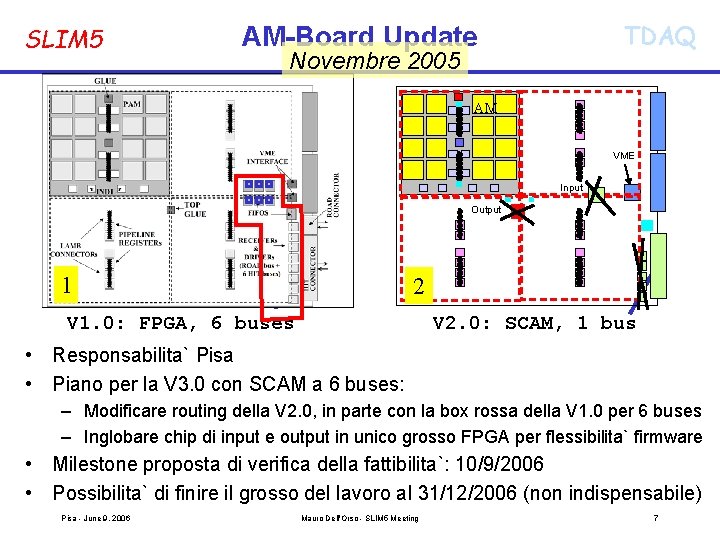

SLIM 5 TDAQ AM-Board Update Novembre 2005 AM VME Input Output 1 2 V 1. 0: FPGA, 6 buses V 2. 0: SCAM, 1 bus • Responsabilita` Pisa • Piano per la V 3. 0 con SCAM a 6 buses: – Modificare routing della V 2. 0, in parte con la box rossa della V 1. 0 per 6 buses – Inglobare chip di input e output in unico grosso FPGA per flessibilita` firmware • Milestone proposta di verifica della fattibilita`: 10/9/2006 • Possibilita` di finire il grosso del lavoro al 31/12/2006 (non indispensabile) Pisa - June 9, 2006 Mauro Dell'Orso - SLIM 5 Meeting 7

TDAQ SLIM 5 Pisa - June 9, 2006 Mauro Dell'Orso - SLIM 5 Meeting 8

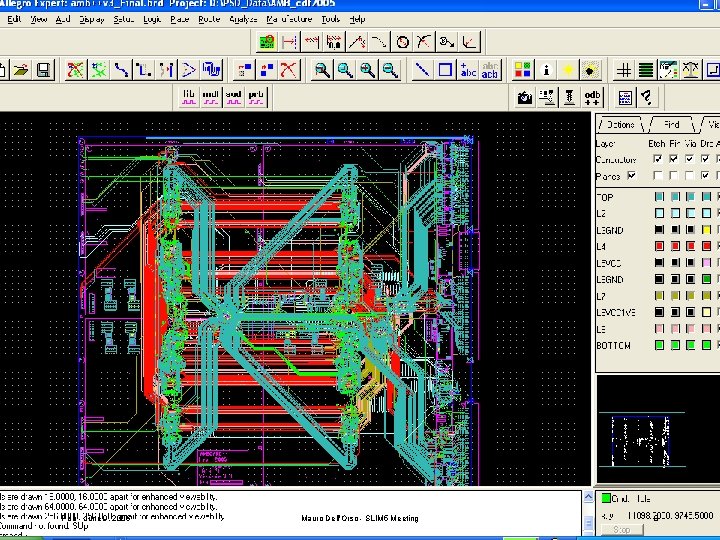

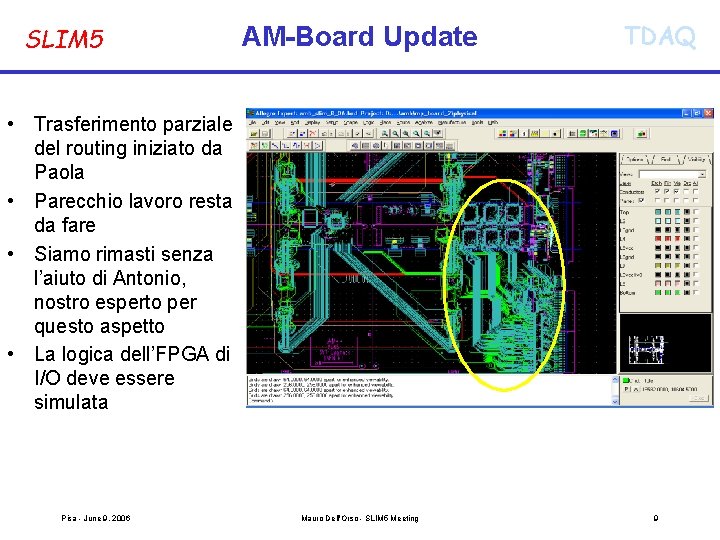

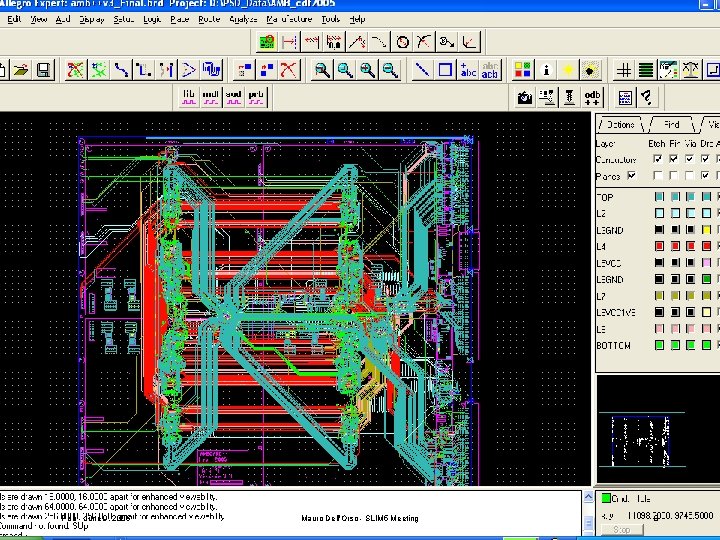

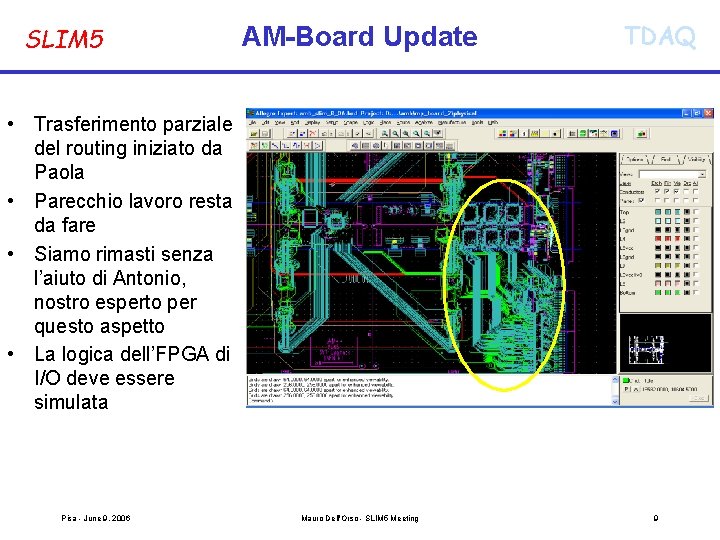

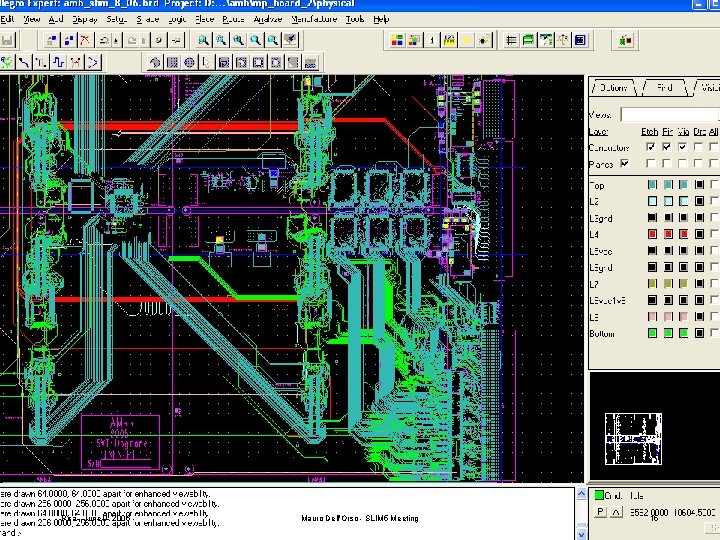

SLIM 5 AM-Board Update TDAQ • Trasferimento parziale del routing iniziato da Paola • Parecchio lavoro resta da fare • Siamo rimasti senza l’aiuto di Antonio, nostro esperto per questo aspetto • La logica dell’FPGA di I/O deve essere simulata Pisa - June 9, 2006 Mauro Dell'Orso - SLIM 5 Meeting 9

SLIM 5 EDRO Novembre 2005 TDAQ • Responsabilita` Bologna • Questioni in sospeso: – – – • • Scelta del tipo di scheda (CDF Pulsar, CERN, …) Interfaccia controllo e DAQ (VME? ) Buffering (profondita`) Handshake con FE … Non abbiamo ancora pensato abbastanza Incontro a Pisa col gruppo di Bologna a meta` gennaio ’ 06 Possibilmente un’idea precisa per Gruppo V settembre ’ 06 Simulazione ? Milestone: 31/12/06 Pisa - June 9, 2006 Mauro Dell'Orso - SLIM 5 Meeting 10

SLIM 5 Sistema Novembre 2005 TDAQ • Responsabilita` congiunta Bologna-Pisa ma anche degli altri • Definizione dell’architettura complessiva • Simulazione: e` necessaria? – Decisione appena definite le questioni del timing – Computo dei pattern • A priori oppure on-line – Allineamento • Milestone: 31/12/06 Giugno 2006 • Milestone proposta per l’INFN 2007: Prime versioni delle schede EDRO e AM testate – 31/12/2007 – Questo ci darebbe il tempo di apportare eventuali correzioni per il test beam dell’estate 2008 Pisa - June 9, 2006 Mauro Dell'Orso - SLIM 5 Meeting 11

SLIM 5 Pisa - June 9, 2006 Backup Mauro Dell'Orso - SLIM 5 Meeting TDAQ 12

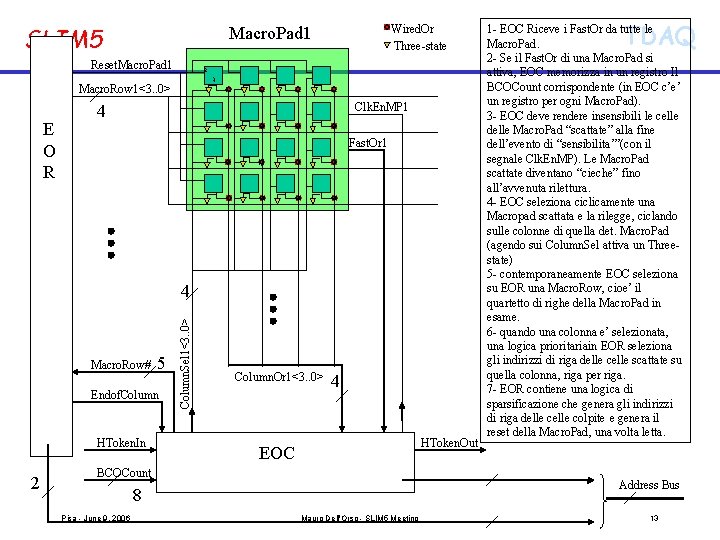

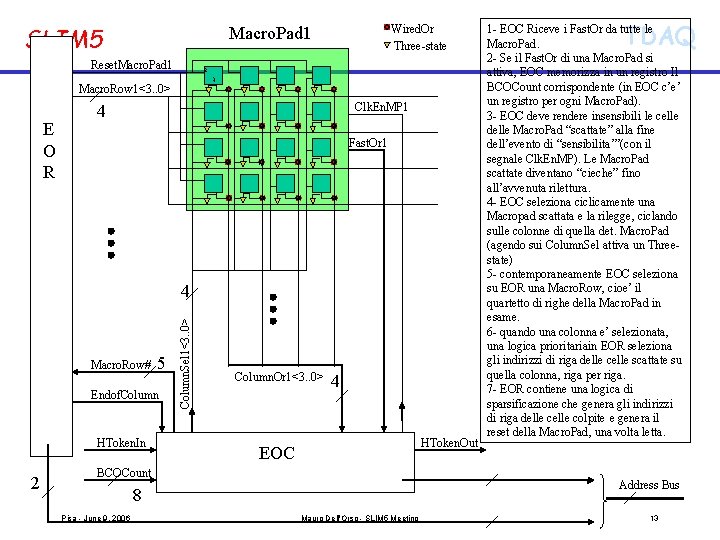

SLIM 5 Wired. Or Three-state Macro. Pad 1 Reset. Macro. Pad 1 R Q Macro. Row 1<3. . 0> E O R Clk. En. MP 1 4 Fast. Or 1 Macro. Row# 5 Endof. Column R o w 2 HToken. In BCOCount Column. Sel 1<3. . 0> 4 Column. Or 1<3. . 0> 4 HToken. Out EOC Macro. Row+Column+Timestamp 8 Pisa - June 9, 2006 Mauro Dell'Orso - SLIM 5 Meeting TDAQ 1 - EOC Riceve i Fast. Or da tutte le Macro. Pad. 2 - Se il Fast. Or di una Macro. Pad si attiva, EOC memorizza in un registro Il BCOCount corrispondente (in EOC c’e’ un registro per ogni Macro. Pad). 3 - EOC deve rendere insensibili le celle delle Macro. Pad “scattate” alla fine dell’evento di “sensibilita’”(con il segnale Clk. En. MP). Le Macro. Pad scattate diventano “cieche” fino all’avvenuta rilettura. 4 - EOC seleziona ciclicamente una Macropad scattata e la rilegge, ciclando sulle colonne di quella det. Macro. Pad (agendo sui Column. Sel attiva un Threestate) 5 - contemporaneamente EOC seleziona su EOR una Macro. Row, cioe’ il quartetto di righe della Macro. Pad in esame. 6 - quando una colonna e’ selezionata, una logica prioritariain EOR seleziona gli indirizzi di riga delle celle scattate su quella colonna, riga per riga. 7 - EOR contiene una logica di sparsificazione che genera gli indirizzi di riga delle colpite e genera il reset della Macro. Pad, una volta letta. Address Bus 13

TDAQ SLIM 5 Note varie: 1 - La Macro. Pad si considera letta (e torna “sensibile”) quando il suo Fast. Or torna a 0 (in conseguenza di cio’ si riabilita il suo Clk. En. MP). 2 - i Row. OR sono uno per riga del rivelatore: EOR puo’ fare la sparsificazione sulle righe. 3 - I Column. Or permettono di fare sparsificazione in EOC, sulle colonne. Si puo’ fare a meno dei Column. Or, pagando con qualche ciclo di clock a vuoto sulle colonne vuote. . . 3 - vogliamo leggere una Macro Pad alla volta o tutta una colonna? Cosi’ come e’ disegnato si legge Tutta la Macro. Pad, Nel caso in figura, EOR genera l’Endof. Column alla fine della quarta riga della Macro. Pad in esame. EOC abilita allora la prossima colonna, fino alla quarta-> fine della Macro. Pad. Si resetta tutta la Macro. Pad con un unico segnale. Si ottiene cosi’ di liberare velocemente le Macro. Pad Se si vuol leggere l’intera colonna, una volta letta tutta una colonna, EOR genera un segnale di Endof. Column verso EOC abilita la prossima colonna. Si resettano tutte le celle sulla colonna con un unico segnale(uno per colonna) il segnale Macro. Row va da EOR a EOC, per comunicargli quale Macro. Pad sta leggendo (ai fini della generazione del giusto Time. Stamp). 4 - Le linee ai pixel sono quindi, in prima approssimazione: Clk. En. MP Fast. Or per ciascuna Macro. Pad Reset. Macro. Pad Macro. Row -> Tante quante sono le righe Column. Sel Column. Or Tante quante sono le colonne 5 - il numero di linee puo’ essere ridotto a spese di qualche porta nelle Macro. Pad. . . ma questo va valutato. ad esempio il Clk. En. MP puo’ essere generato all’interno della Macro. Pad con un FF in piu’. . . Pisa - June 9, 2006 Mauro Dell'Orso - SLIM 5 Meeting 14

TDAQ SLIM 5 Pisa - June 9, 2006 Mauro Dell'Orso - SLIM 5 Meeting 15