TDAQ SLIM 5 TDAQ WP 3 Trigger and

- Slides: 17

TDAQ SLIM 5 TDAQ WP 3: Trigger and Data Acquisition It’s time to set specs Bergamo - November 22, 2006 Mauro Dell'Orso - SLIM 5 Meeting 1

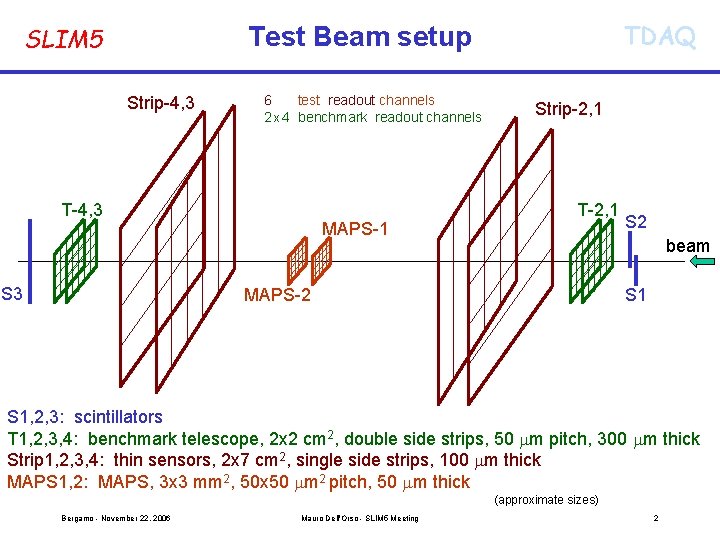

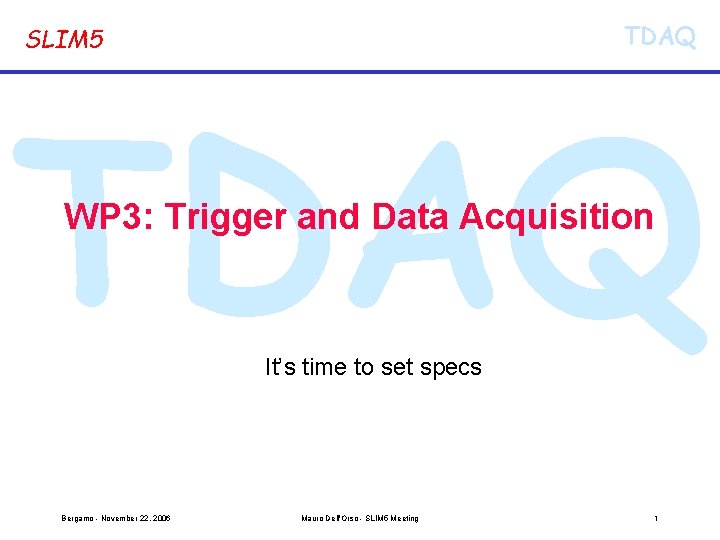

TDAQ Test Beam setup SLIM 5 Strip-4, 3 6 test readout channels 2 x 4 benchmark readout channels T-4, 3 S 3 MAPS-1 Strip-2, 1 T-2, 1 S 2 beam MAPS-2 S 1, 2, 3: scintillators T 1, 2, 3, 4: benchmark telescope, 2 x 2 cm 2, double side strips, 50 mm pitch, 300 mm thick Strip 1, 2, 3, 4: thin sensors, 2 x 7 cm 2, single side strips, 100 mm thick MAPS 1, 2: MAPS, 3 x 3 mm 2, 50 x 50 mm 2 pitch, 50 mm thick (approximate sizes) Bergamo - November 22, 2006 Mauro Dell'Orso - SLIM 5 Meeting 2

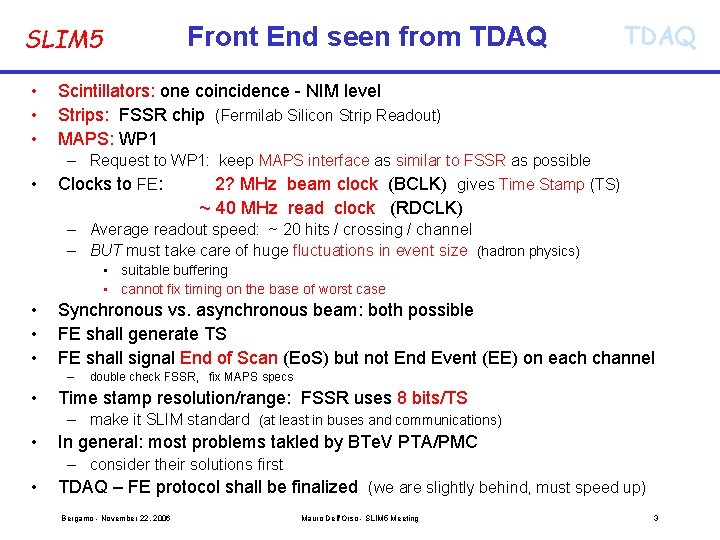

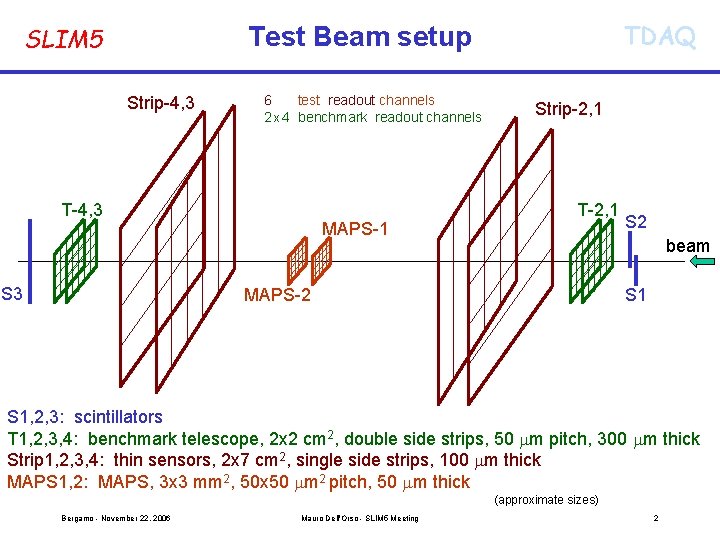

Front End seen from TDAQ SLIM 5 • • • Scintillators: one coincidence - NIM level Strips: FSSR chip (Fermilab Silicon Strip Readout) MAPS: WP 1 • – Request to WP 1: keep MAPS interface as similar to FSSR as possible Clocks to FE: 2? MHz beam clock (BCLK) gives Time Stamp (TS) TDAQ ~ 40 MHz read clock (RDCLK) – Average readout speed: ~ 20 hits / crossing / channel – BUT must take care of huge fluctuations in event size (hadron physics) • suitable buffering • cannot fix timing on the base of worst case • • • Synchronous vs. asynchronous beam: both possible FE shall generate TS FE shall signal End of Scan (Eo. S) but not End Event (EE) on each channel – • double check FSSR, fix MAPS specs Time stamp resolution/range: FSSR uses 8 bits/TS – make it SLIM standard (at least in buses and communications) • In general: most problems takled by BTe. V PTA/PMC – consider their solutions first • TDAQ – FE protocol shall be finalized (we are slightly behind, must speed up) Bergamo - November 22, 2006 Mauro Dell'Orso - SLIM 5 Meeting 3

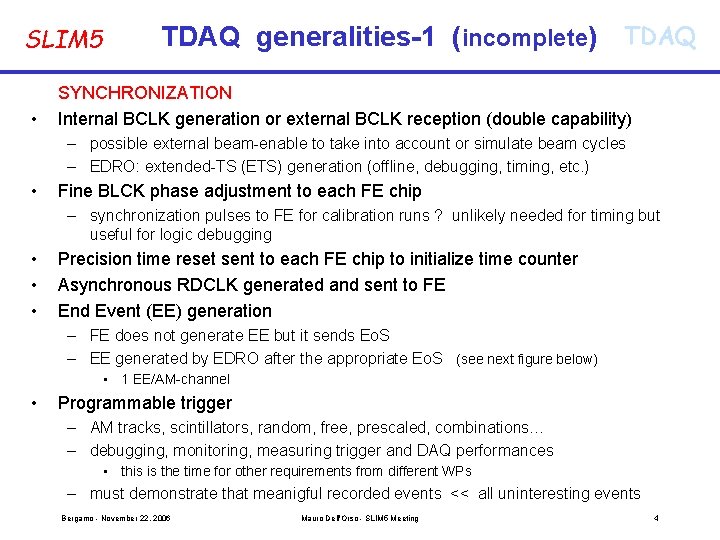

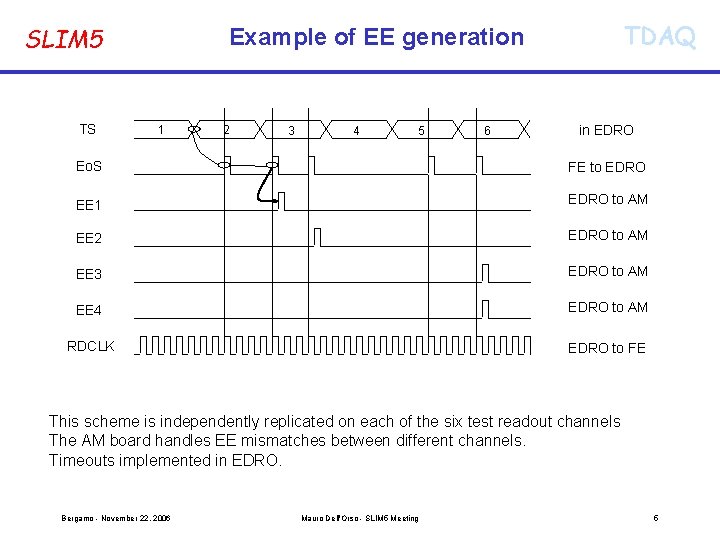

SLIM 5 • TDAQ generalities-1 (incomplete) TDAQ SYNCHRONIZATION Internal BCLK generation or external BCLK reception (double capability) – possible external beam-enable to take into account or simulate beam cycles – EDRO: extended-TS (ETS) generation (offline, debugging, timing, etc. ) • Fine BLCK phase adjustment to each FE chip – synchronization pulses to FE for calibration runs ? unlikely needed for timing but useful for logic debugging • • • Precision time reset sent to each FE chip to initialize time counter Asynchronous RDCLK generated and sent to FE End Event (EE) generation – FE does not generate EE but it sends Eo. S – EE generated by EDRO after the appropriate Eo. S (see next figure below) • 1 EE/AM-channel • Programmable trigger – AM tracks, scintillators, random, free, prescaled, combinations… – debugging, monitoring, measuring trigger and DAQ performances • this is the time for other requirements from different WPs – must demonstrate that meanigful recorded events << all uninteresting events Bergamo - November 22, 2006 Mauro Dell'Orso - SLIM 5 Meeting 4

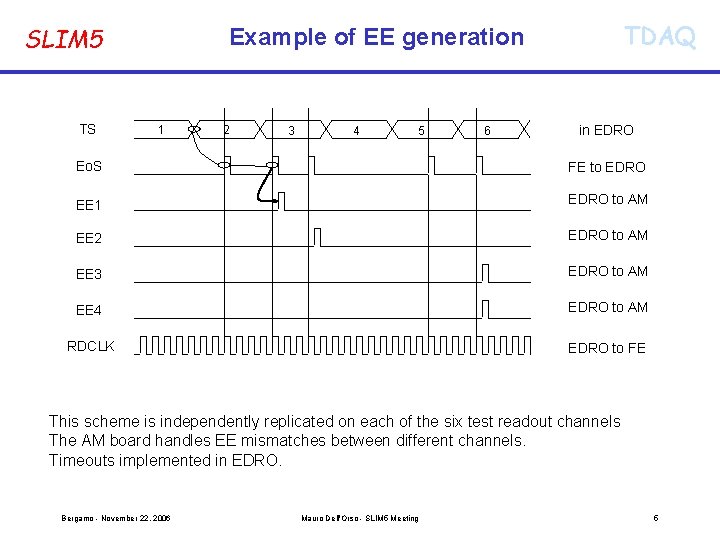

SLIM 5 TS TDAQ Example of EE generation 1 2 3 4 5 6 in EDRO Eo. S FE to EDRO EE 1 EDRO to AM EE 2 EDRO to AM EE 3 EDRO to AM EE 4 EDRO to AM RDCLK EDRO to FE This scheme is independently replicated on each of the six test readout channels The AM board handles EE mismatches between different channels. Timeouts implemented in EDRO. Bergamo - November 22, 2006 Mauro Dell'Orso - SLIM 5 Meeting 5

SLIM 5 • TDAQ generalities-2 (incomplete) TDAQ Use of scintillator coincidence (EXternal TRigger, EXTR) – event tag • Tag events following EXTR and within a programmable interval – event trigger • Record events following EXTR and within a programmable interval • Possible use of Fine Time Stamp (FTS) in EDRO for precision record of scintillator times – can’t see any application, need input from WPs • Other tools: still much to think about – Error Handling • Tag errors and make them trackable – Debugging • Internal to DAQ and facilities provided to other WPs (please input) – – Event overflow Monitoring (mainly dead time and all that) Spy Buffers: duplicate all I/O traffic into deep VME-interfaced FIFOs VME-writable input FIFOs Bergamo - November 22, 2006 Mauro Dell'Orso - SLIM 5 Meeting 6

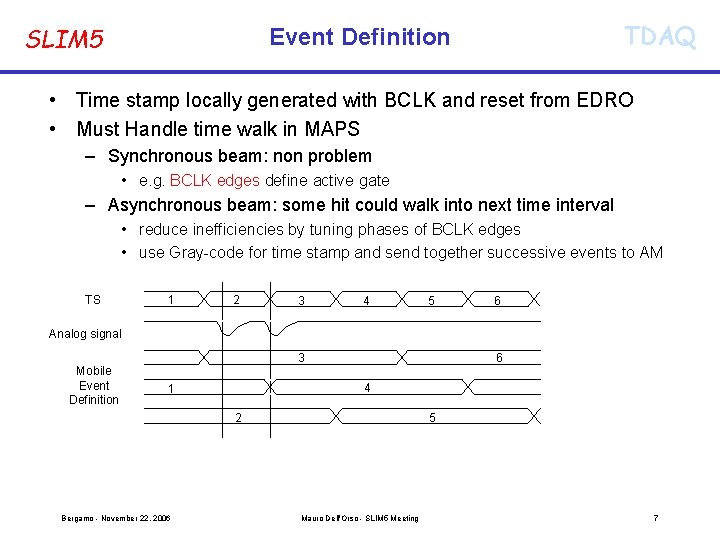

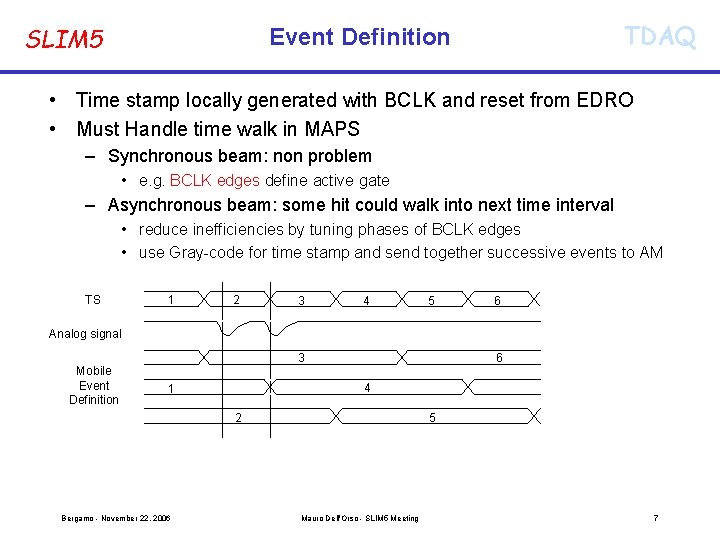

SLIM 5 TDAQ Event Definition • Time stamp locally generated with BCLK and reset from EDRO • Must Handle time walk in MAPS – Synchronous beam: non problem • e. g. BCLK edges define active gate – Asynchronous beam: some hit could walk into next time interval • reduce inefficiencies by tuning phases of BCLK edges • use Gray-code for time stamp and send together successive events to AM TS 1 2 3 4 5 6 Analog signal Mobile Event Definition 3 6 4 1 5 2 Bergamo - November 22, 2006 Mauro Dell'Orso - SLIM 5 Meeting 7

SLIM 5 Bergamo - November 22, 2006 BACKUP SLIDES Mauro Dell'Orso - SLIM 5 Meeting TDAQ 8

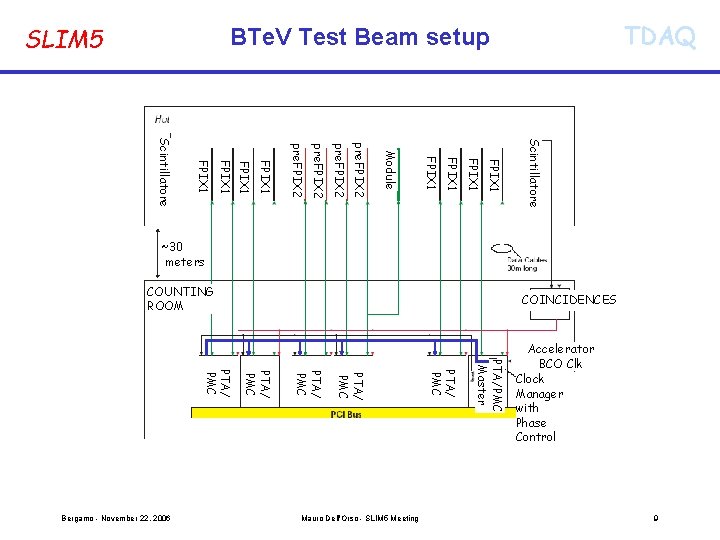

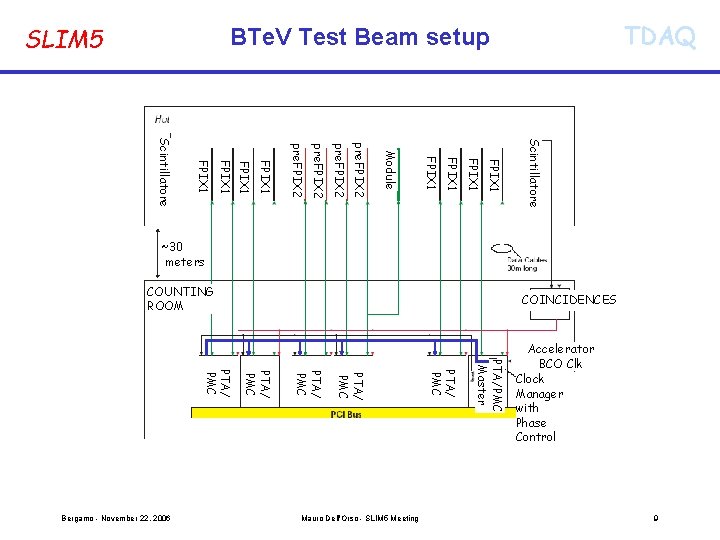

SLIM 5 TDAQ BTe. V Test Beam setup Scintillatore FPIX 1 Module pre. FPIX 2 FPIX 1 Scintillatore ~30 meters COUNTING ROOM PTA/PMC Master Mauro Dell'Orso - SLIM 5 Meeting PTA/ PMC PTA/ PMC Bergamo - November 22, 2006 COINCIDENCES Accelerator BCO Clk Clock Manager with Phase Control 9

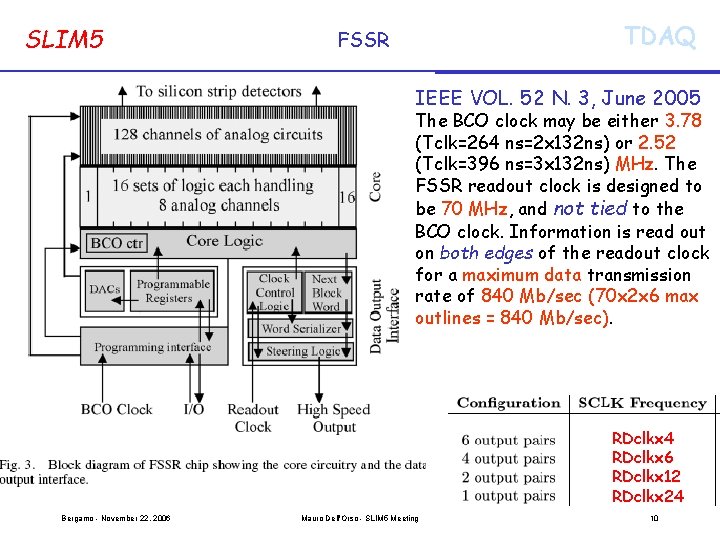

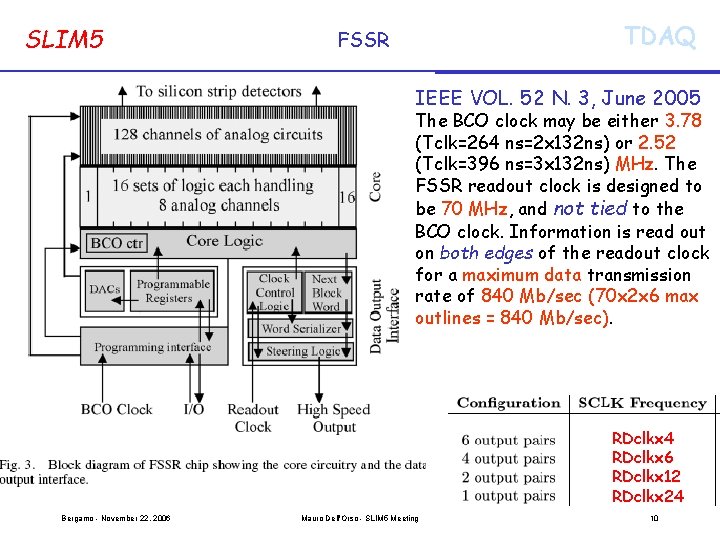

SLIM 5 TDAQ FSSR IEEE VOL. 52 N. 3, June 2005 The BCO clock may be either 3. 78 (Tclk=264 ns=2 x 132 ns) or 2. 52 (Tclk=396 ns=3 x 132 ns) MHz. The FSSR readout clock is designed to be 70 MHz, and not tied to the BCO clock. Information is read out on both edges of the readout clock for a maximum data transmission rate of 840 Mb/sec (70 x 2 x 6 max outlines = 840 Mb/sec). RDclkx 4 RDclkx 6 RDclkx 12 RDclkx 24 Bergamo - November 22, 2006 Mauro Dell'Orso - SLIM 5 Meeting 10

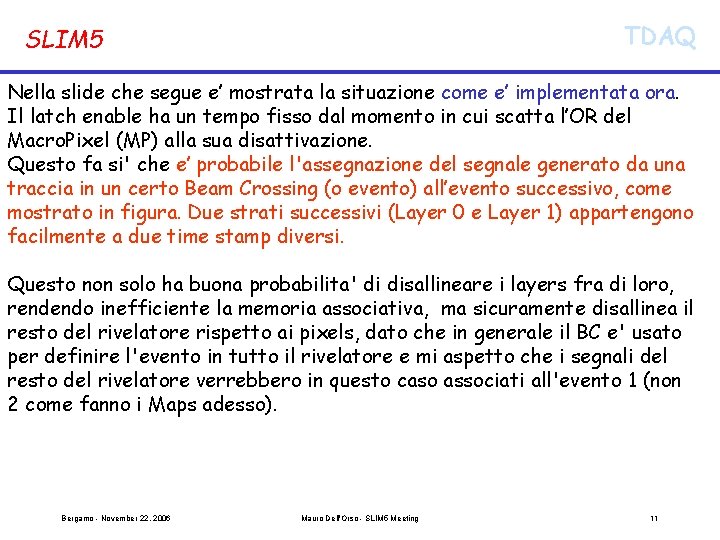

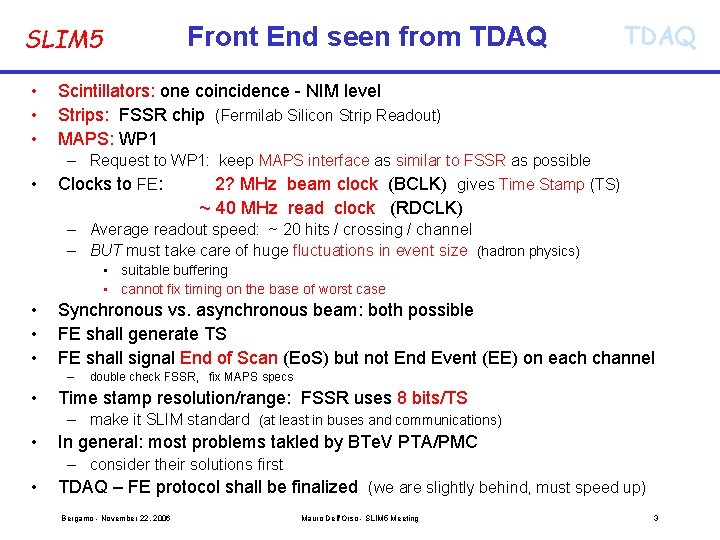

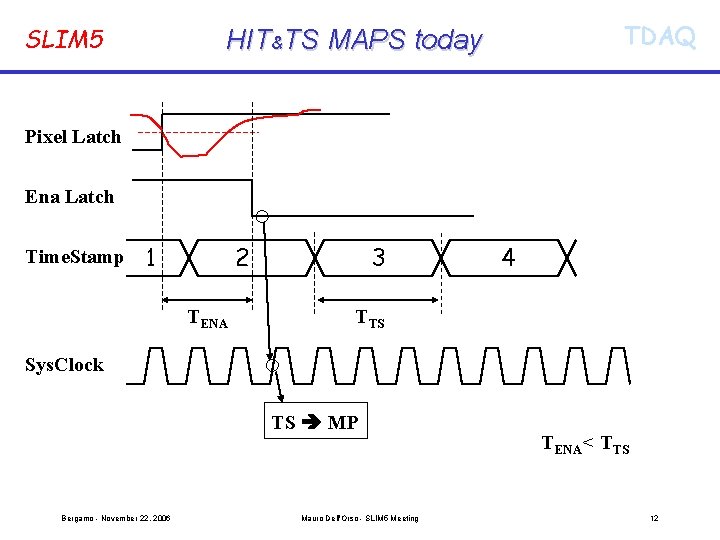

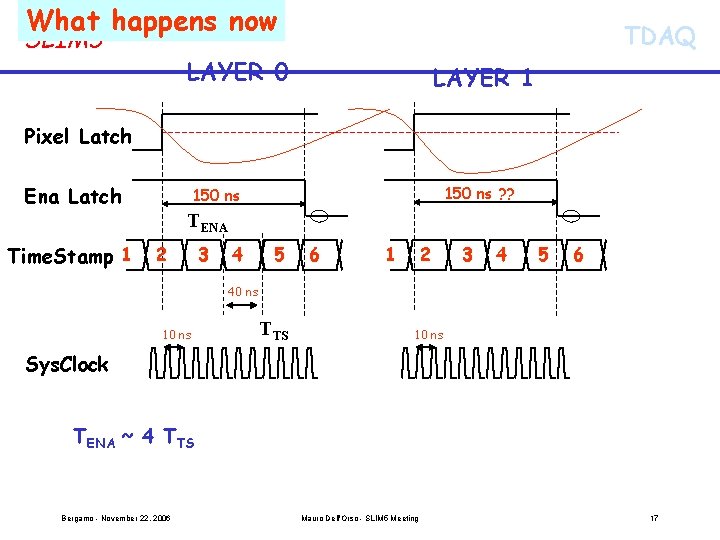

TDAQ SLIM 5 Nella slide che segue e’ mostrata la situazione come e’ implementata ora. Il latch enable ha un tempo fisso dal momento in cui scatta l’OR del Macro. Pixel (MP) alla sua disattivazione. Questo fa si' che e’ probabile l'assegnazione del segnale generato da una traccia in un certo Beam Crossing (o evento) all’evento successivo, come mostrato in figura. Due strati successivi (Layer 0 e Layer 1) appartengono facilmente a due time stamp diversi. Questo non solo ha buona probabilita' di disallineare i layers fra di loro, rendendo inefficiente la memoria associativa, ma sicuramente disallinea il resto del rivelatore rispetto ai pixels, dato che in generale il BC e' usato per definire l'evento in tutto il rivelatore e mi aspetto che i segnali del resto del rivelatore verrebbero in questo caso associati all'evento 1 (non 2 come fanno i Maps adesso). Bergamo - November 22, 2006 Mauro Dell'Orso - SLIM 5 Meeting 11

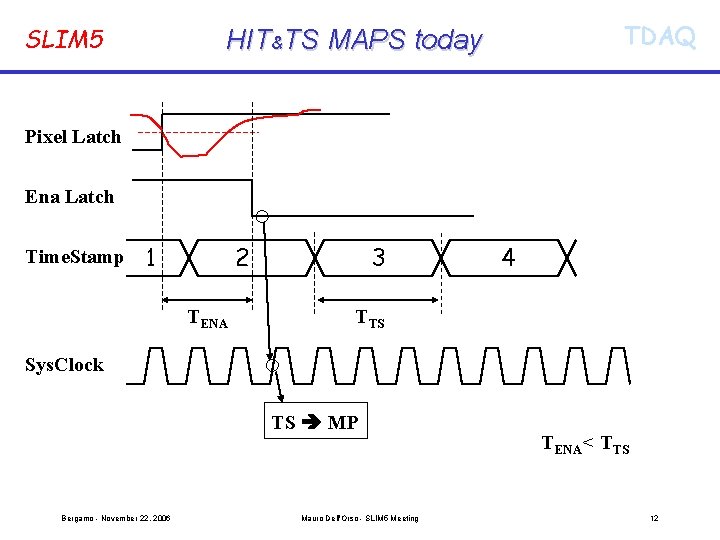

SLIM 5 TDAQ HIT&TS MAPS today Pixel Latch Ena Latch Time. Stamp 1 2 TENA 3 4 TTS Sys. Clock TS MP Bergamo - November 22, 2006 Mauro Dell'Orso - SLIM 5 Meeting TENA < TTS 12

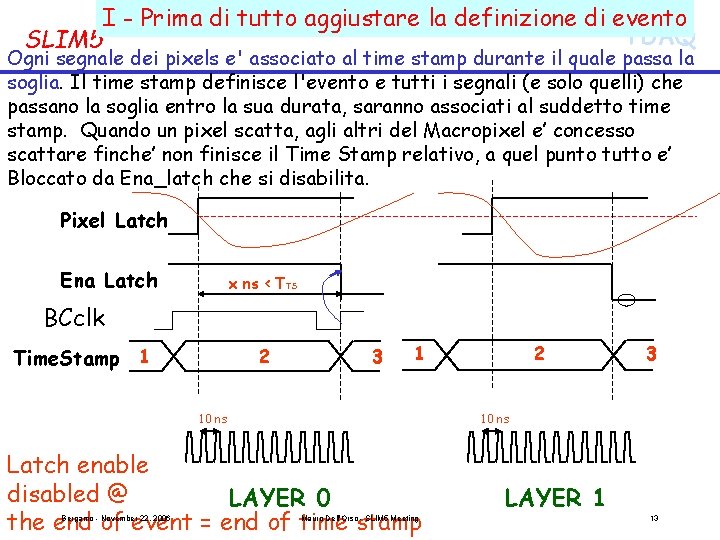

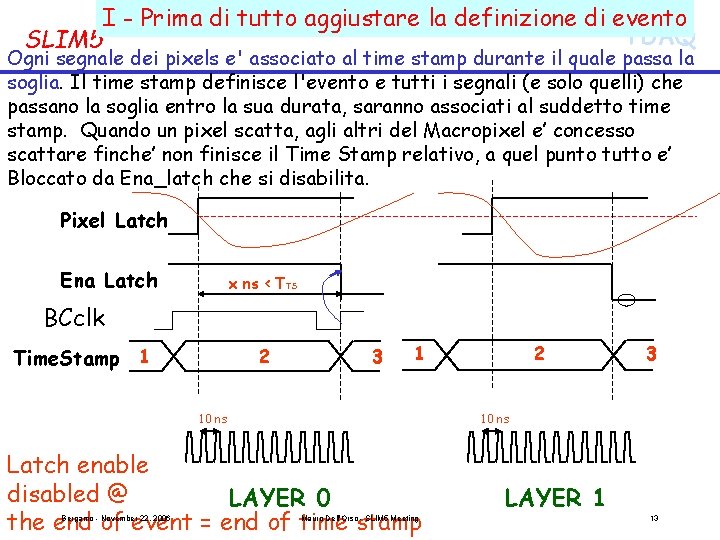

I - Prima di tutto aggiustare la definizione di evento TDAQ SLIM 5 Ogni segnale dei pixels e' associato al time stamp durante il quale passa la soglia. Il time stamp definisce l'evento e tutti i segnali (e solo quelli) che passano la soglia entro la sua durata, saranno associati al suddetto time stamp. Quando un pixel scatta, agli altri del Macropixel e’ concesso scattare finche’ non finisce il Time Stamp relativo, a quel punto tutto e’ Bloccato da Ena_latch che si disabilita. Pixel Latch Ena Latch x ns < TTS BCclk Time. Stamp 1 2 3 1 10 ns 3 10 ns Latch enable disabled @ LAYER 0 the end of event = end of time stamp Bergamo - November 22, 2006 2 Mauro Dell'Orso - SLIM 5 Meeting LAYER 1 13

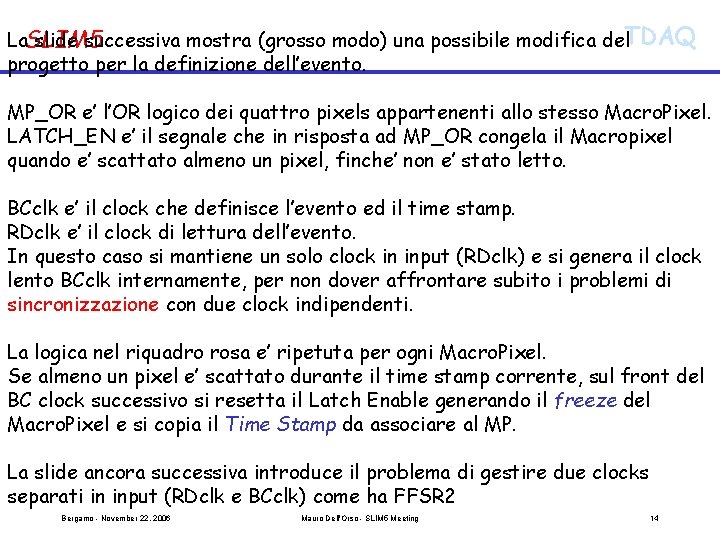

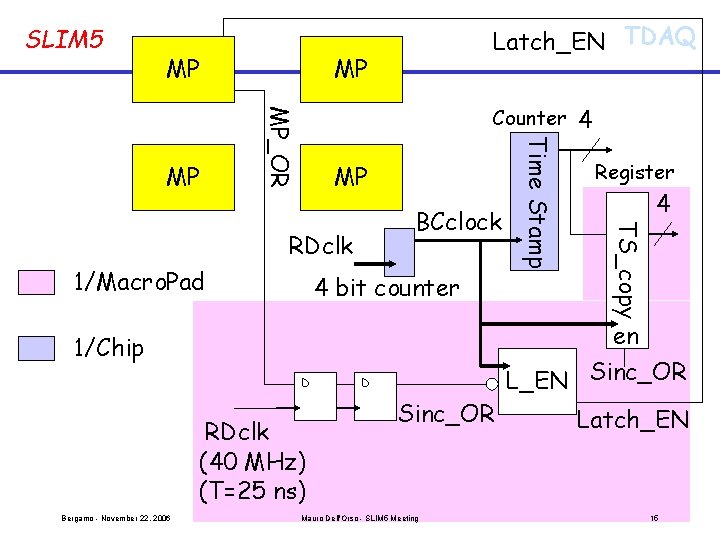

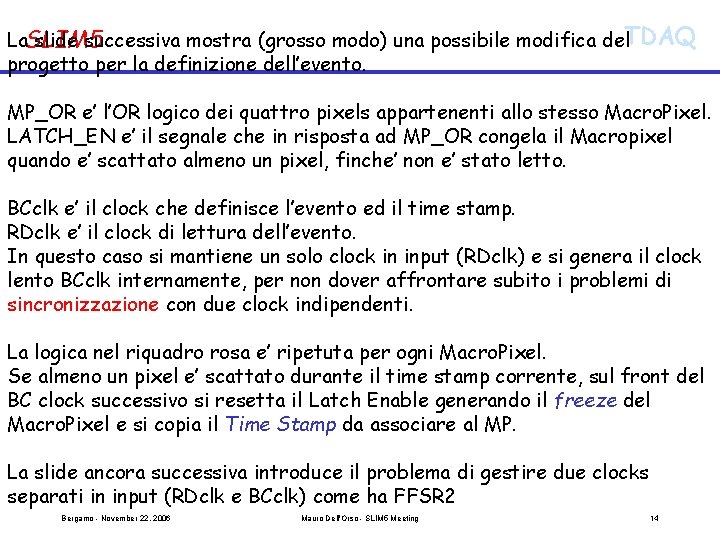

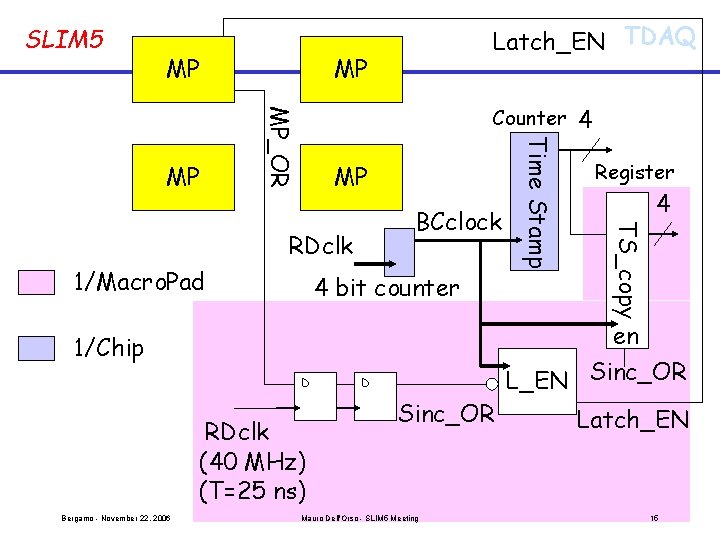

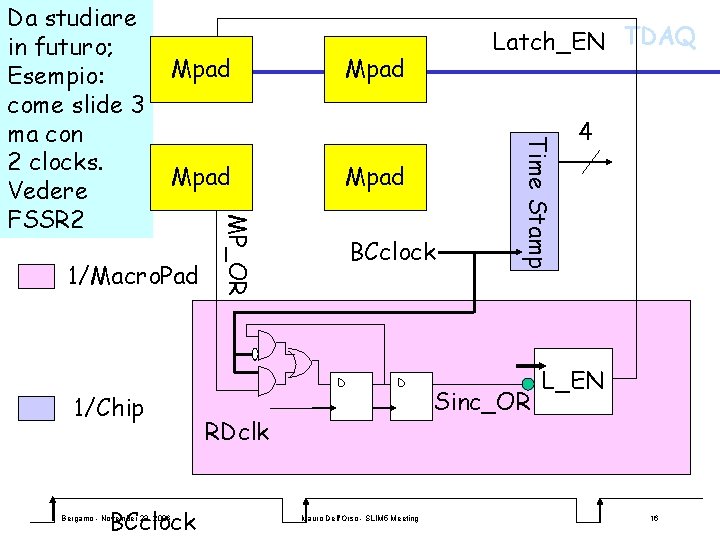

La. SLIM 5 slide successiva mostra (grosso modo) una possibile modifica del. TDAQ progetto per la definizione dell’evento. MP_OR e’ l’OR logico dei quattro pixels appartenenti allo stesso Macro. Pixel. LATCH_EN e’ il segnale che in risposta ad MP_OR congela il Macropixel quando e’ scattato almeno un pixel, finche’ non e’ stato letto. BCclk e’ il clock che definisce l’evento ed il time stamp. RDclk e’ il clock di lettura dell’evento. In questo caso si mantiene un solo clock in input (RDclk) e si genera il clock lento BCclk internamente, per non dover affrontare subito i problemi di sincronizzazione con due clock indipendenti. La logica nel riquadro rosa e’ ripetuta per ogni Macro. Pixel. Se almeno un pixel e’ scattato durante il time stamp corrente, sul front del BC clock successivo si resetta il Latch Enable generando il freeze del Macro. Pixel e si copia il Time Stamp da associare al MP. La slide ancora successiva introduce il problema di gestire due clocks separati in input (RDclk e BCclk) come ha FFSR 2 Bergamo - November 22, 2006 Mauro Dell'Orso - SLIM 5 Meeting 14

SLIM 5 MP MP Counter MP RDclk 1/Macro. Pad 4 bit counter 1/Chip D RDclk (40 MHz) (T=25 ns) Bergamo - November 22, 2006 D Sinc_OR Mauro Dell'Orso - SLIM 5 Meeting 4 Register 4 TS_copy BCclock Time Stamp MP_OR MP Latch_EN TDAQ en L_EN Sinc_OR Latch_EN 15

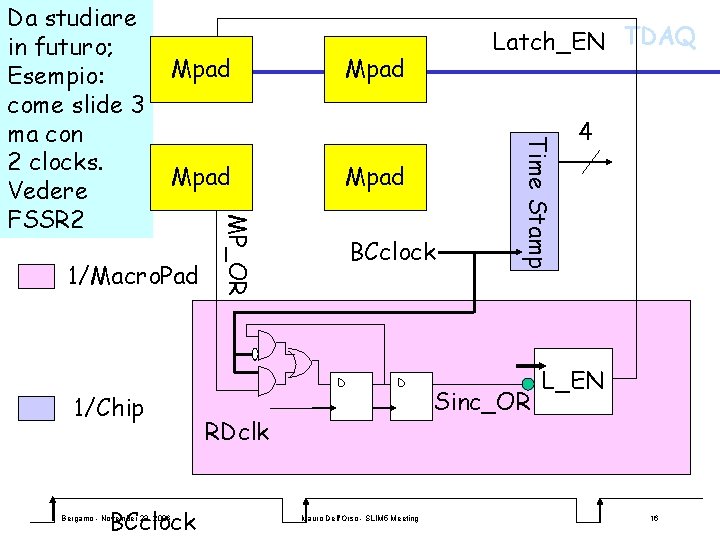

Mpad 1/Macro. Pad 1/Chip BCclock Bergamo - November 22, 2006 Mpad BCclock D D RDclk Mauro Dell'Orso - SLIM 5 Meeting Time Stamp Mpad Latch_EN TDAQ Mpad MP_OR Da studiare in. SLIM 5 futuro; Esempio: come slide 3 ma con 2 clocks. Vedere FSSR 2 Sinc_OR 4 L_EN 16

What happens now SLIM 5 TDAQ LAYER 0 LAYER 1 Pixel Latch Ena Latch 150 ns ? ? 150 ns TENA Time. Stamp 1 2 3 4 5 6 40 ns 10 ns TTS 10 ns Sys. Clock TENA ~ 4 TTS Bergamo - November 22, 2006 Mauro Dell'Orso - SLIM 5 Meeting 17