System Block Diagram IO Pins IO Pins IO

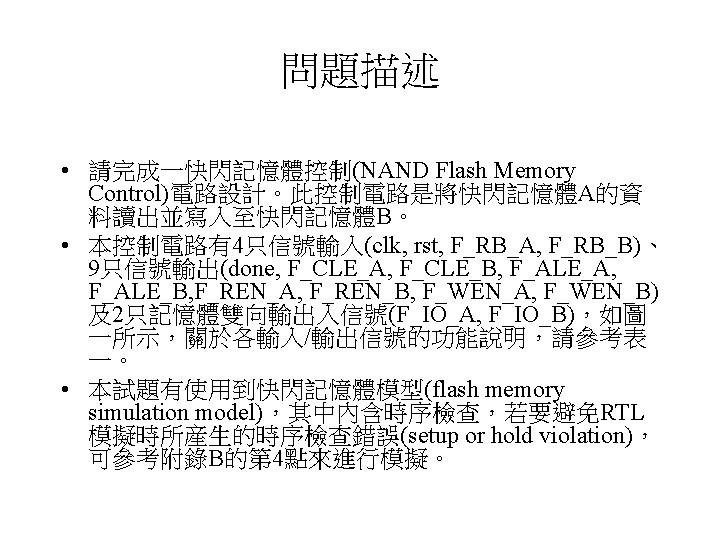

System Block Diagram

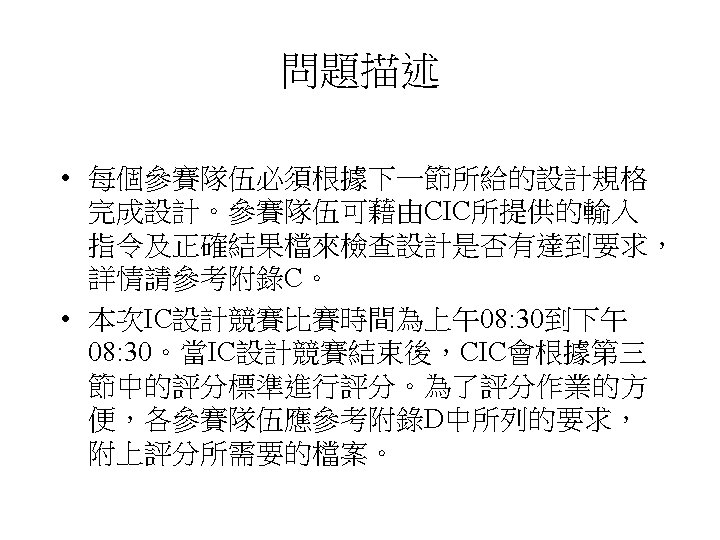

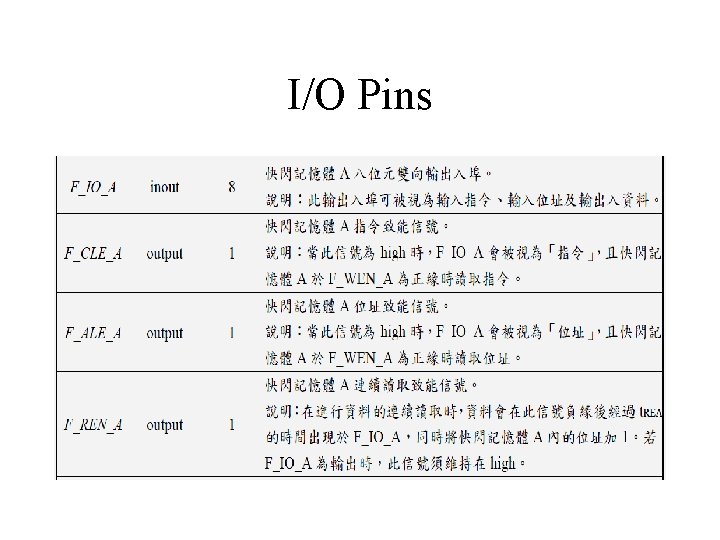

I/O Pins

I/O Pins

I/O Pins

I/O Pins

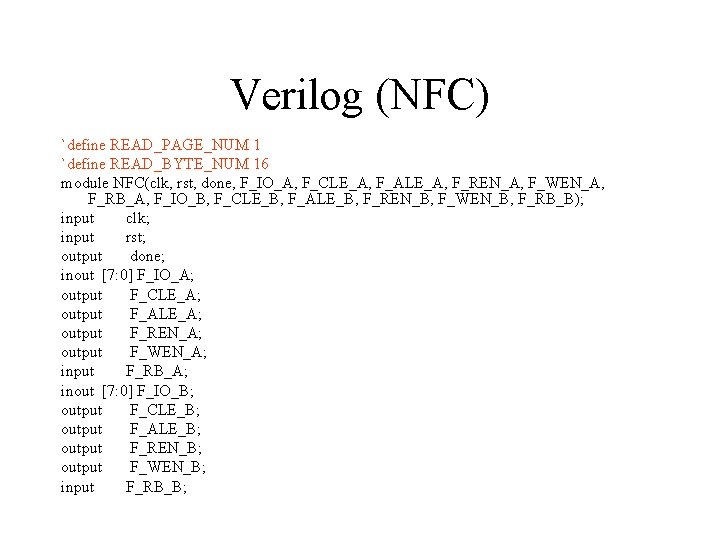

Verilog (NFC) `define READ_PAGE_NUM 1 `define READ_BYTE_NUM 16 module NFC(clk, rst, done, F_IO_A, F_CLE_A, F_ALE_A, F_REN_A, F_WEN_A, F_RB_A, F_IO_B, F_CLE_B, F_ALE_B, F_REN_B, F_WEN_B, F_RB_B); input clk; input rst; output done; inout [7: 0] F_IO_A; output F_CLE_A; output F_ALE_A; output F_REN_A; output F_WEN_A; input F_RB_A; inout [7: 0] F_IO_B; output F_CLE_B; output F_ALE_B; output F_REN_B; output F_WEN_B; input F_RB_B;

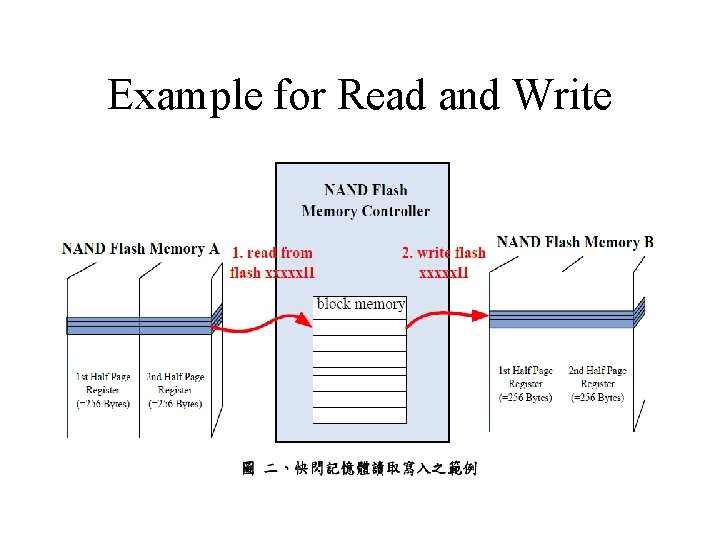

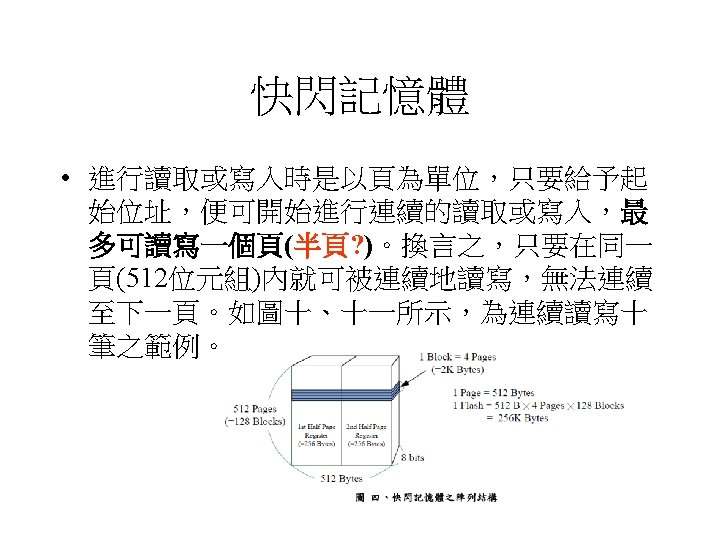

Example for Read and Write

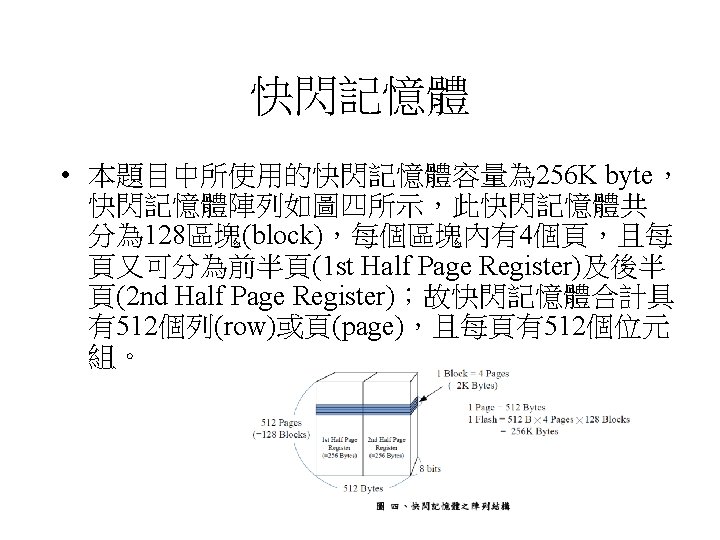

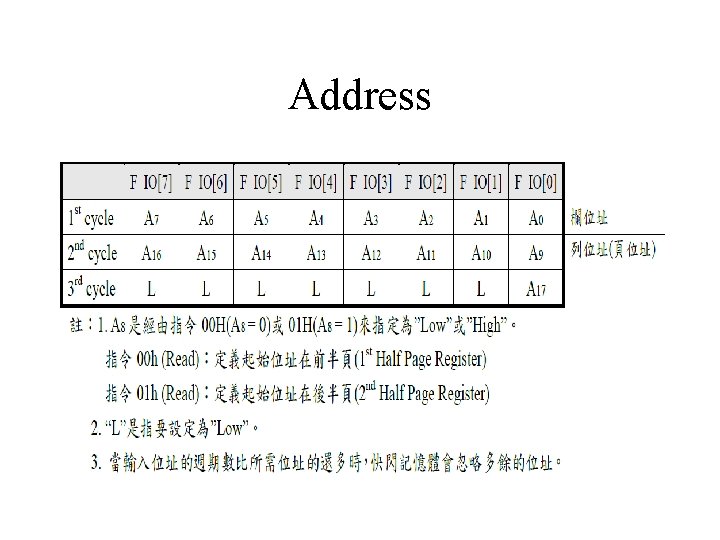

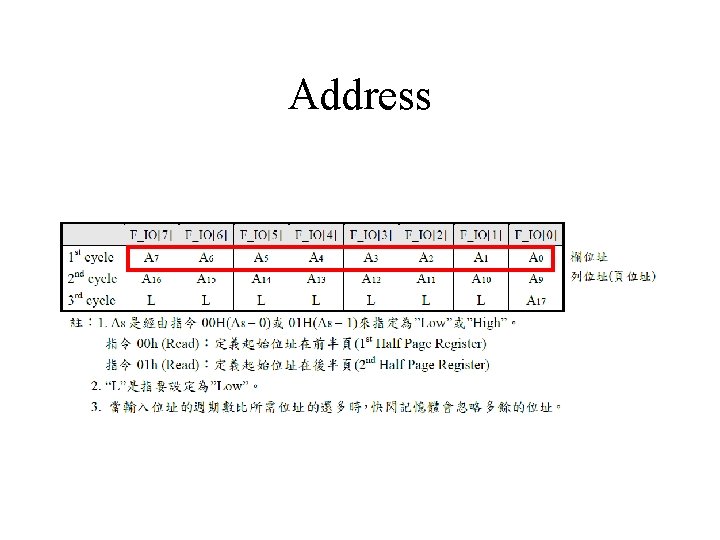

Address

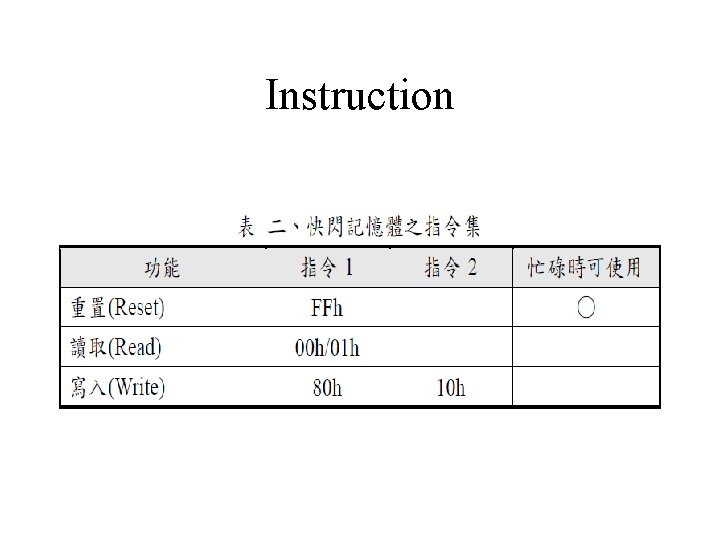

Instruction

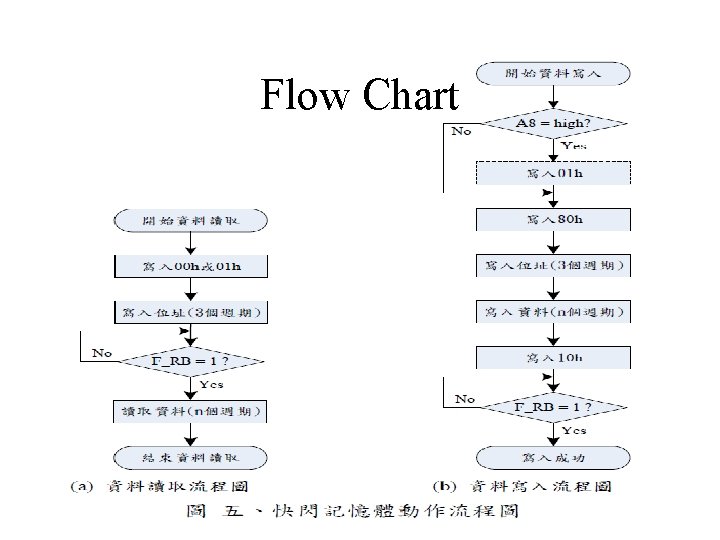

Flow Chart

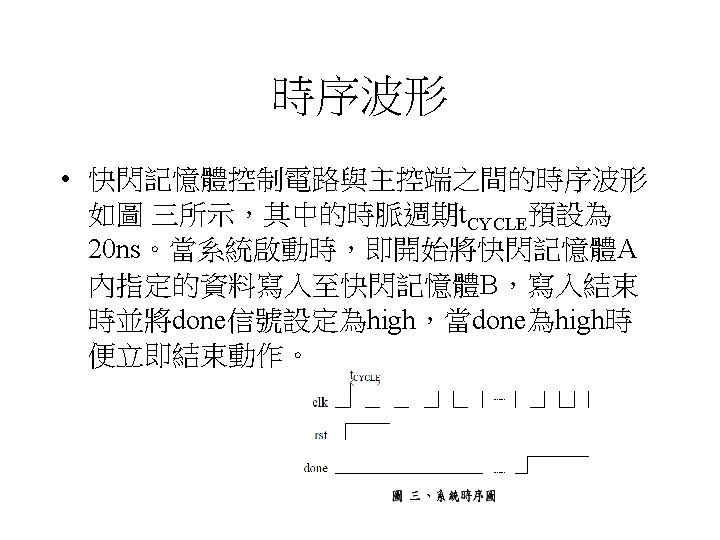

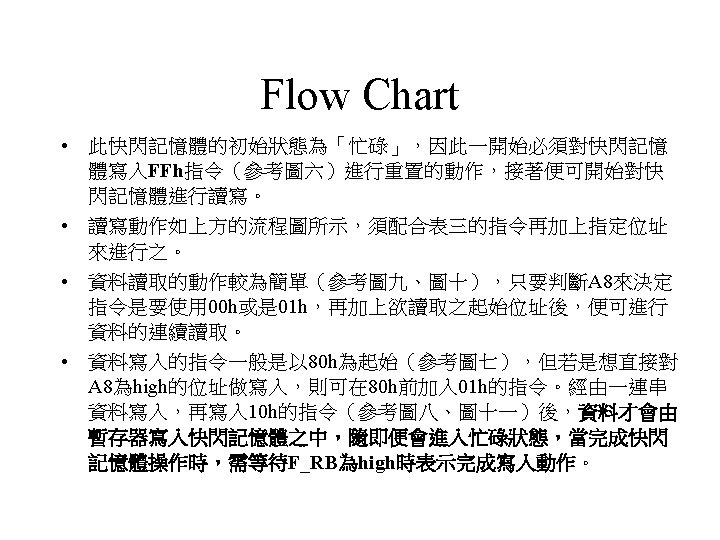

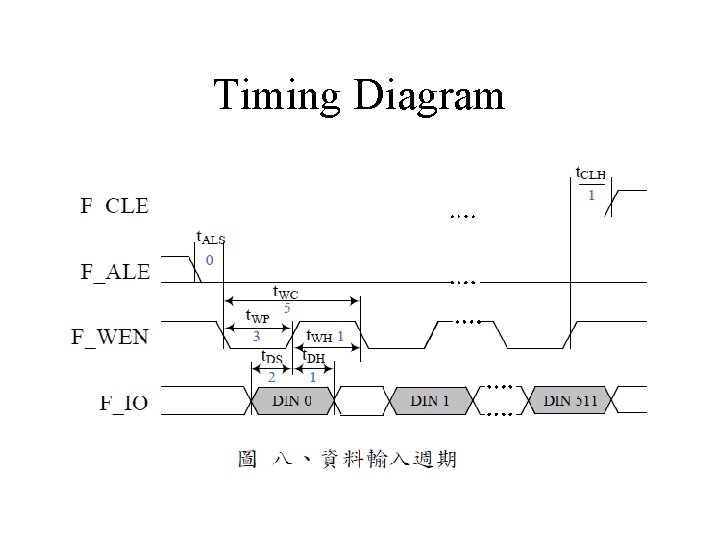

Timing Diagram

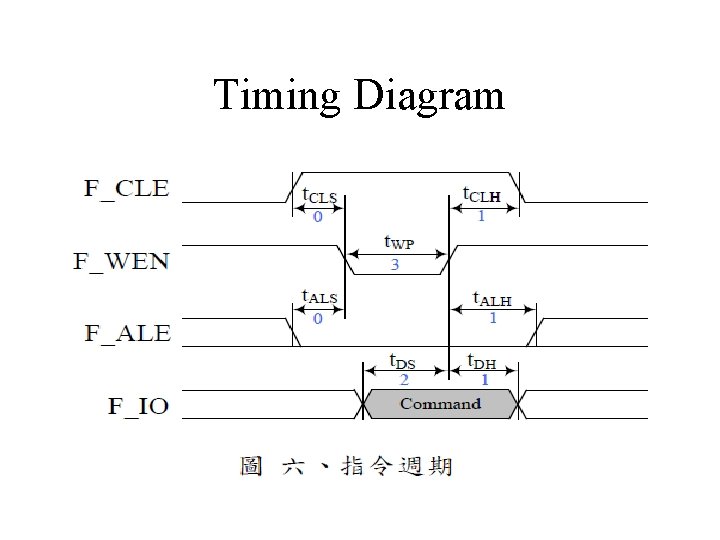

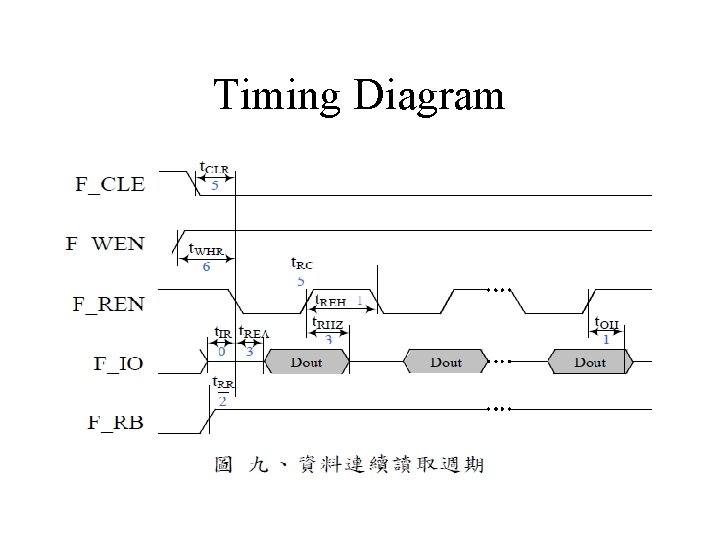

Timing Diagram

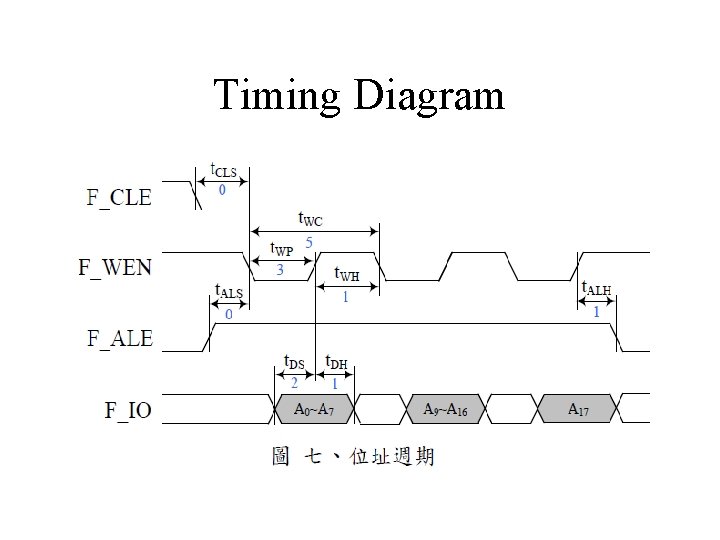

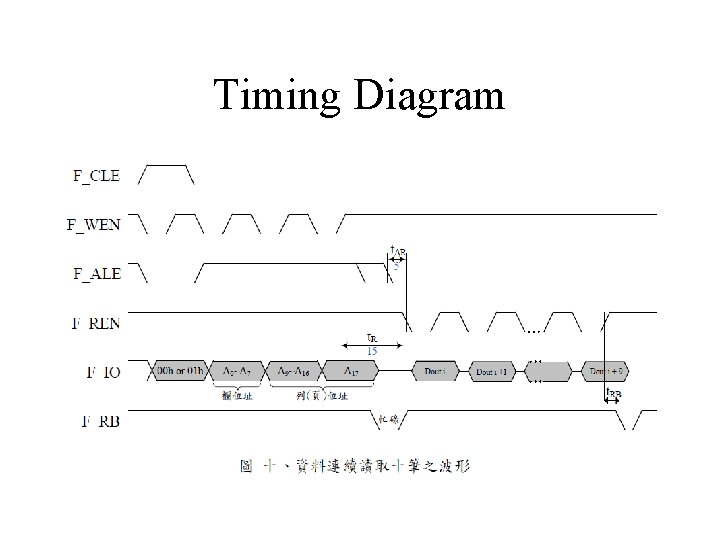

Timing Diagram

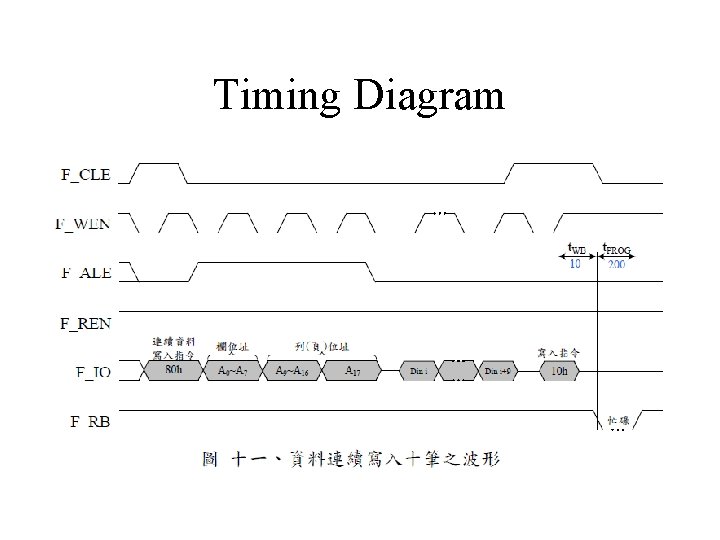

Timing Diagram

Timing Diagram

Timing Diagram

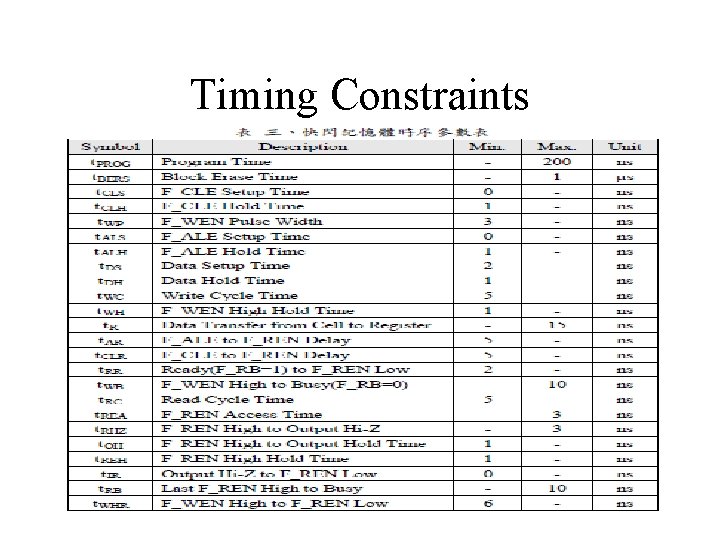

Timing Constraints

![Verilog (NFC) reg [4: 0] read_state; reg do_cmd_A; reg [7: 0] A_cmd; reg F_REN_A; Verilog (NFC) reg [4: 0] read_state; reg do_cmd_A; reg [7: 0] A_cmd; reg F_REN_A;](http://slidetodoc.com/presentation_image_h2/63e0ef8d6e4d440f8bbd1bf8f12a6d8e/image-28.jpg)

Verilog (NFC) reg [4: 0] read_state; reg do_cmd_A; reg [7: 0] A_cmd; reg F_REN_A; reg m_F_CLE_A, m_F_WEN_A, m_F_ALE_A; reg[7: 0] m_F_IO_A; wire[7: 0] U 1_F_IO_A; reg [7: 0] a 16_a 9; reg a 17; reg[7: 0] data[0: 511]; //Modify the maximum subscript of data[0: 262143] for other applications reg[17: 0] byte_cnt; reg done;

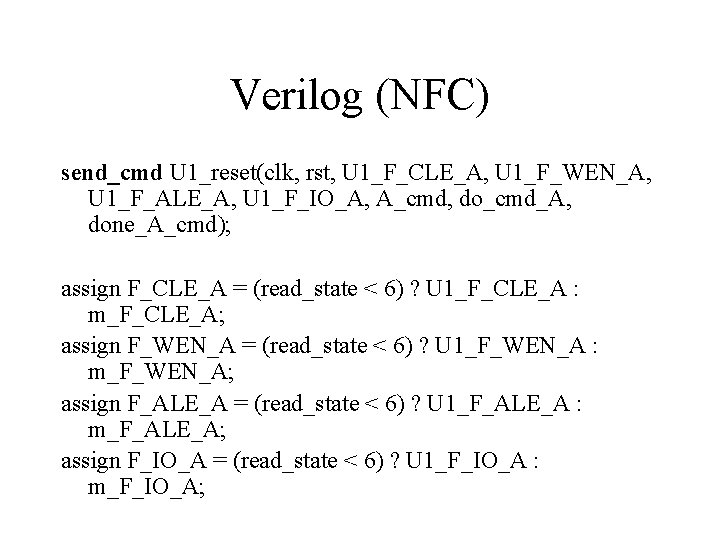

Verilog (NFC) send_cmd U 1_reset(clk, rst, U 1_F_CLE_A, U 1_F_WEN_A, U 1_F_ALE_A, U 1_F_IO_A, A_cmd, do_cmd_A, done_A_cmd); assign F_CLE_A = (read_state < 6) ? U 1_F_CLE_A : m_F_CLE_A; assign F_WEN_A = (read_state < 6) ? U 1_F_WEN_A : m_F_WEN_A; assign F_ALE_A = (read_state < 6) ? U 1_F_ALE_A : m_F_ALE_A; assign F_IO_A = (read_state < 6) ? U 1_F_IO_A : m_F_IO_A;

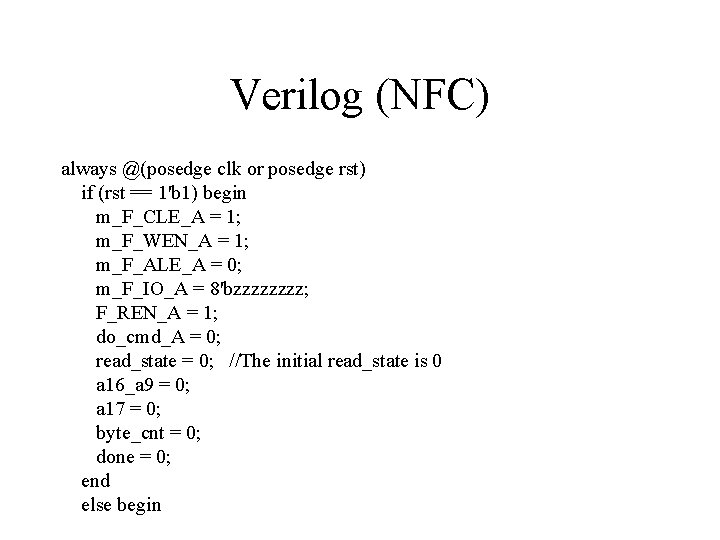

Verilog (NFC) always @(posedge clk or posedge rst) if (rst == 1'b 1) begin m_F_CLE_A = 1; m_F_WEN_A = 1; m_F_ALE_A = 0; m_F_IO_A = 8'bzzzz; F_REN_A = 1; do_cmd_A = 0; read_state = 0; //The initial read_state is 0 a 16_a 9 = 0; a 17 = 0; byte_cnt = 0; done = 0; end else begin

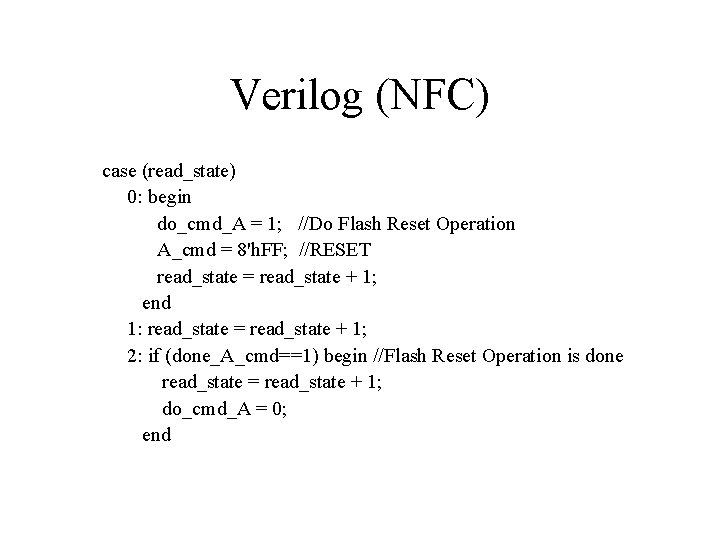

Verilog (NFC) case (read_state) 0: begin do_cmd_A = 1; //Do Flash Reset Operation A_cmd = 8'h. FF; //RESET read_state = read_state + 1; end 1: read_state = read_state + 1; 2: if (done_A_cmd==1) begin //Flash Reset Operation is done read_state = read_state + 1; do_cmd_A = 0; end

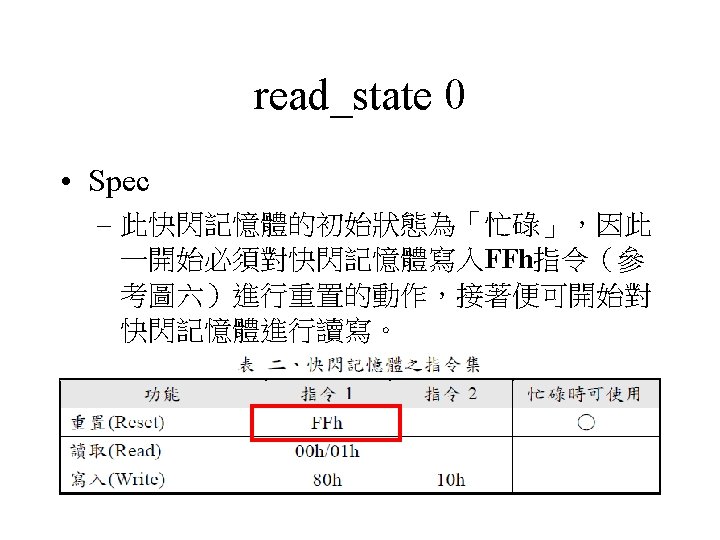

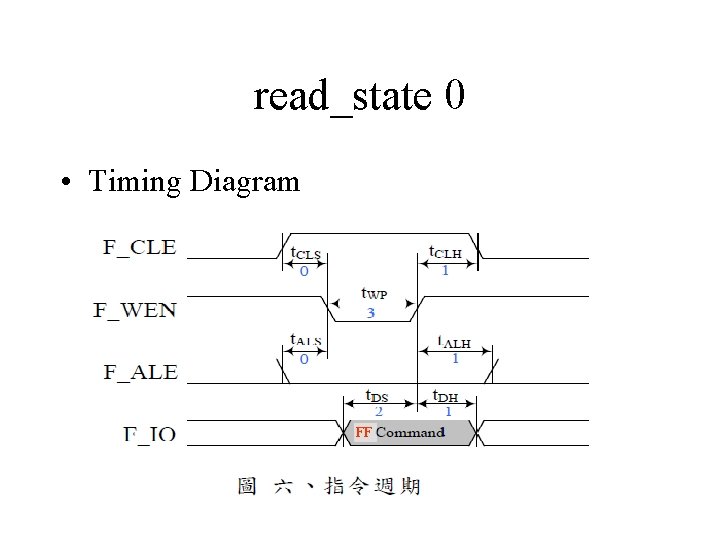

read_state 0 • Timing Diagram FF

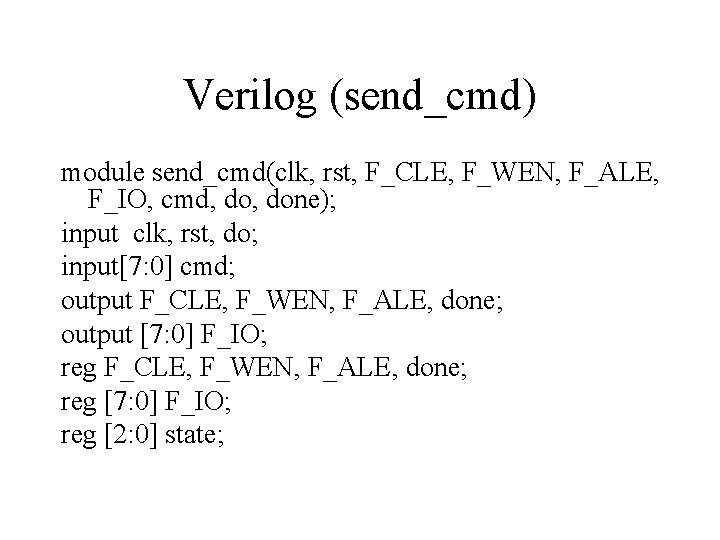

Verilog (send_cmd) module send_cmd(clk, rst, F_CLE, F_WEN, F_ALE, F_IO, cmd, done); input clk, rst, do; input[7: 0] cmd; output F_CLE, F_WEN, F_ALE, done; output [7: 0] F_IO; reg F_CLE, F_WEN, F_ALE, done; reg [7: 0] F_IO; reg [2: 0] state;

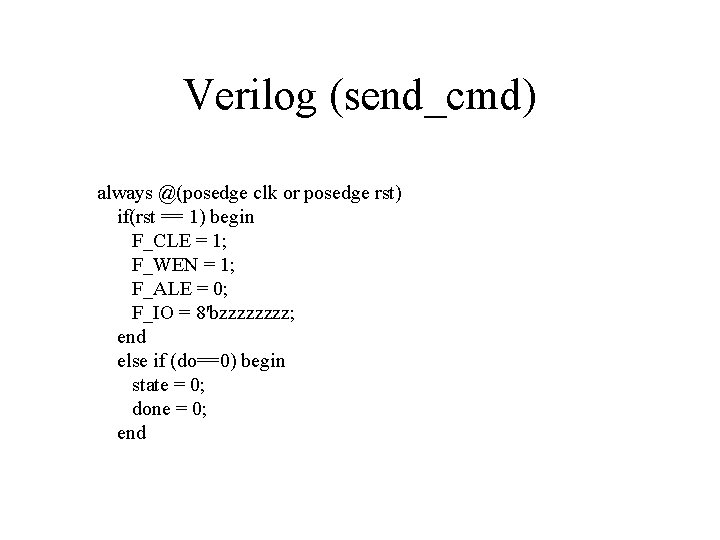

Verilog (send_cmd) always @(posedge clk or posedge rst) if(rst == 1) begin F_CLE = 1; F_WEN = 1; F_ALE = 0; F_IO = 8'bzzzz; end else if (do==0) begin state = 0; done = 0; end

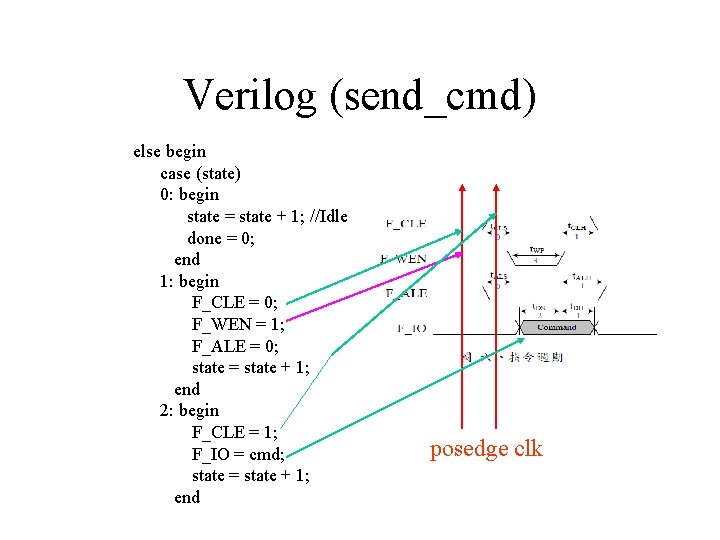

Verilog (send_cmd) else begin case (state) 0: begin state = state + 1; //Idle done = 0; end 1: begin F_CLE = 0; F_WEN = 1; F_ALE = 0; state = state + 1; end 2: begin F_CLE = 1; F_IO = cmd; state = state + 1; end posedge clk

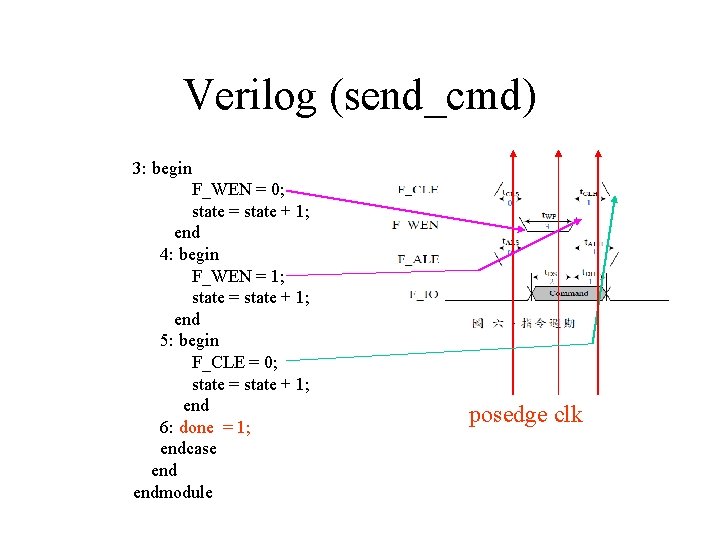

Verilog (send_cmd) 3: begin F_WEN = 0; state = state + 1; end 4: begin F_WEN = 1; state = state + 1; end 5: begin F_CLE = 0; state = state + 1; end 6: done = 1; endcase endmodule posedge clk

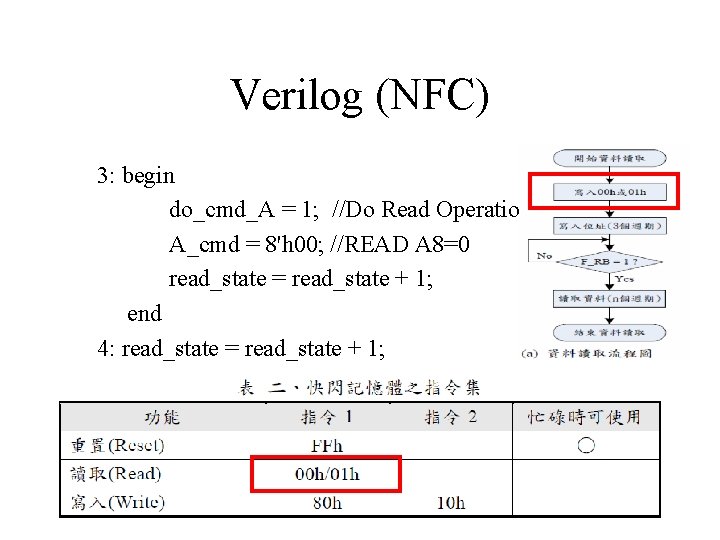

Verilog (NFC) 3: begin do_cmd_A = 1; //Do Read Operation A_cmd = 8'h 00; //READ A 8=0 read_state = read_state + 1; end 4: read_state = read_state + 1;

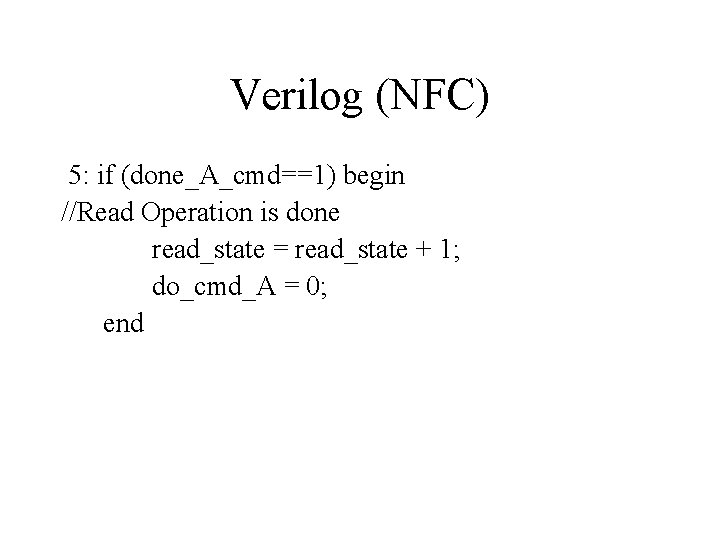

Verilog (NFC) 5: if (done_A_cmd==1) begin //Read Operation is done read_state = read_state + 1; do_cmd_A = 0; end

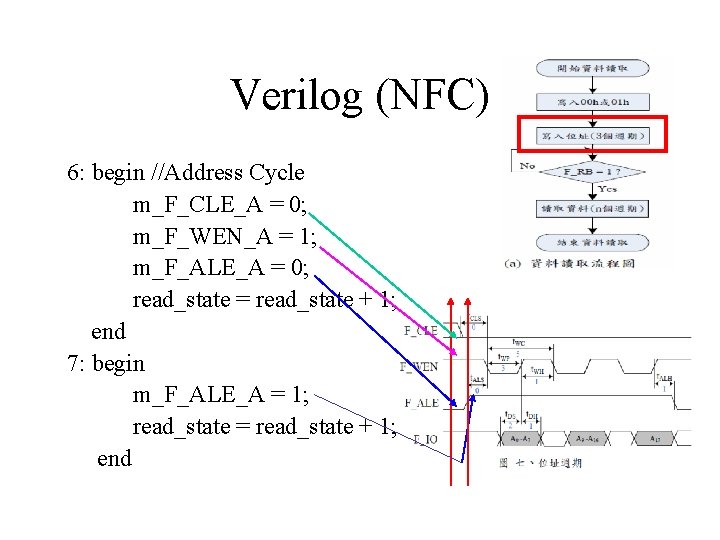

Verilog (NFC) 6: begin //Address Cycle m_F_CLE_A = 0; m_F_WEN_A = 1; m_F_ALE_A = 0; read_state = read_state + 1; end 7: begin m_F_ALE_A = 1; read_state = read_state + 1; end

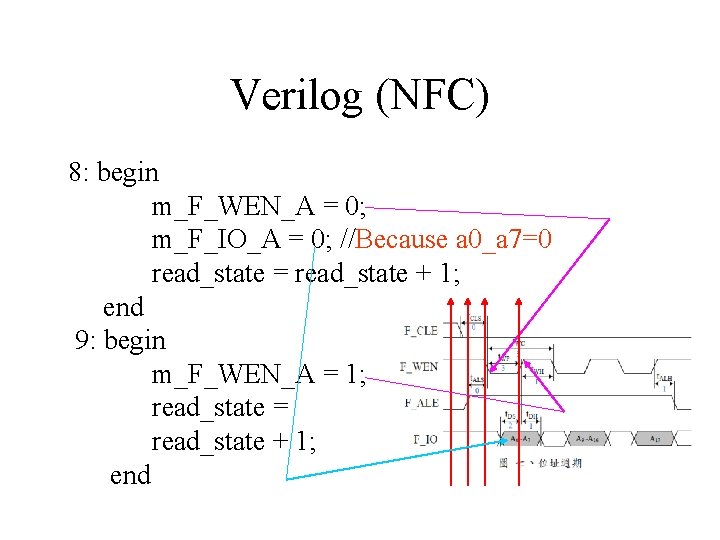

Verilog (NFC) 8: begin m_F_WEN_A = 0; m_F_IO_A = 0; //Because a 0_a 7=0 read_state = read_state + 1; end 9: begin m_F_WEN_A = 1; read_state = read_state + 1; end

Address

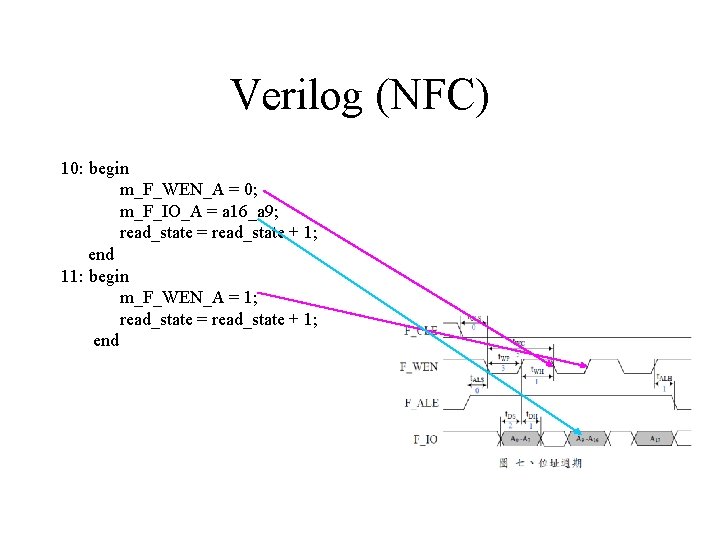

Verilog (NFC) 10: begin m_F_WEN_A = 0; m_F_IO_A = a 16_a 9; read_state = read_state + 1; end 11: begin m_F_WEN_A = 1; read_state = read_state + 1; end

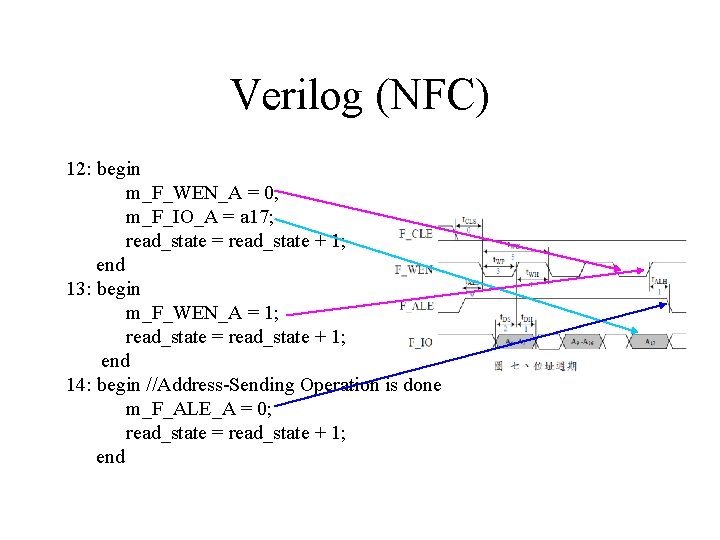

Verilog (NFC) 12: begin m_F_WEN_A = 0; m_F_IO_A = a 17; read_state = read_state + 1; end 13: begin m_F_WEN_A = 1; read_state = read_state + 1; end 14: begin //Address-Sending Operation is done m_F_ALE_A = 0; read_state = read_state + 1; end

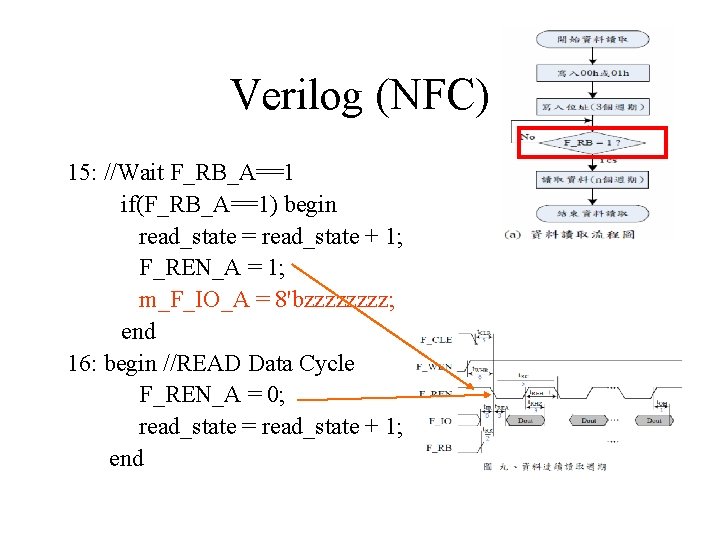

Verilog (NFC) 15: //Wait F_RB_A==1 if(F_RB_A==1) begin read_state = read_state + 1; F_REN_A = 1; m_F_IO_A = 8'bzzzz; end 16: begin //READ Data Cycle F_REN_A = 0; read_state = read_state + 1; end

![Verilog (NFC) 17: begin F_REN_A = 1; data[byte_cnt] = F_IO_A; //Modify byte_cnt if it Verilog (NFC) 17: begin F_REN_A = 1; data[byte_cnt] = F_IO_A; //Modify byte_cnt if it](http://slidetodoc.com/presentation_image_h2/63e0ef8d6e4d440f8bbd1bf8f12a6d8e/image-46.jpg)

Verilog (NFC) 17: begin F_REN_A = 1; data[byte_cnt] = F_IO_A; //Modify byte_cnt if it is nessary byte_cnt = byte_cnt + 1; //READ 512 Bytes if (byte_cnt != `READ_BYTE_NUM) read_state = 16; //LOOP else read_state=18; end

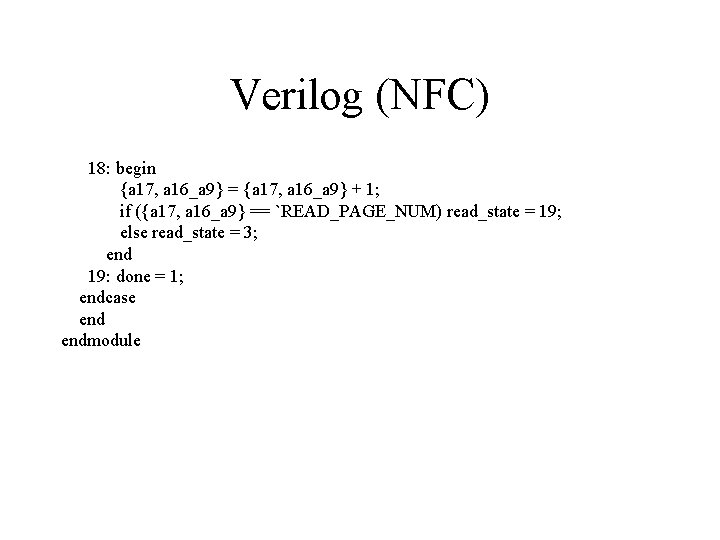

Verilog (NFC) 18: begin {a 17, a 16_a 9} = {a 17, a 16_a 9} + 1; if ({a 17, a 16_a 9} == `READ_PAGE_NUM) read_state = 19; else read_state = 3; end 19: done = 1; endcase endmodule

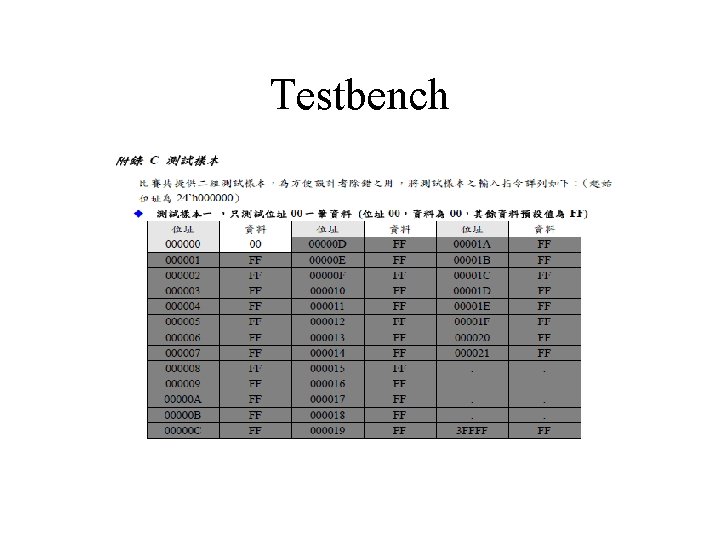

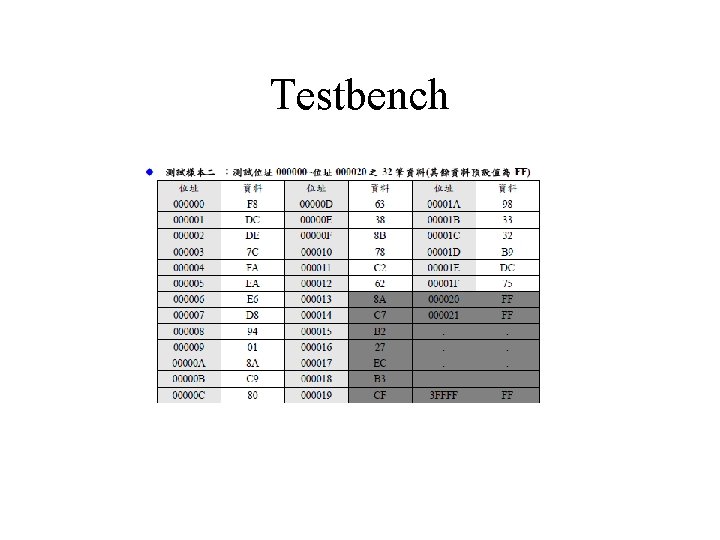

Testbench

Testbench

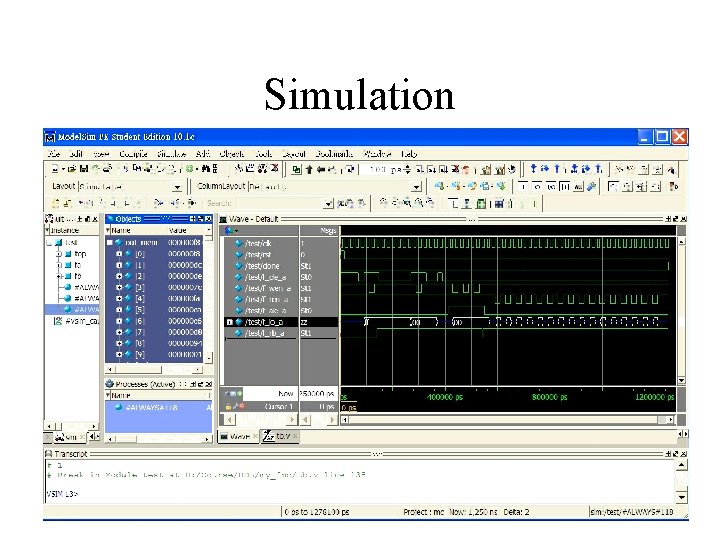

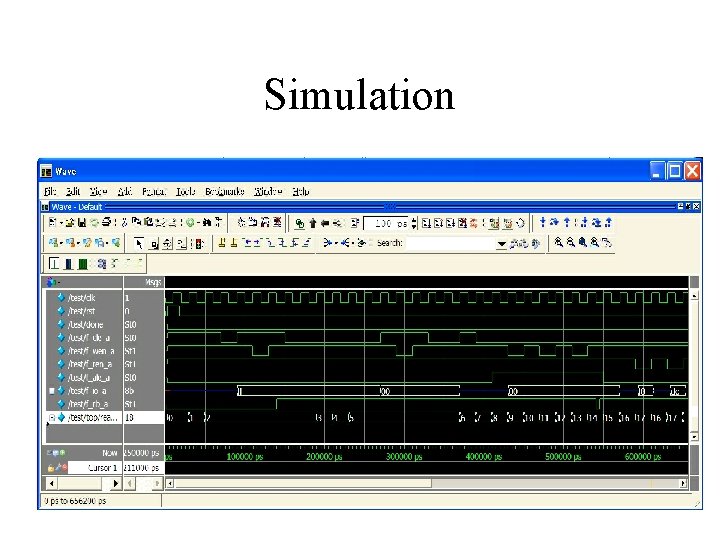

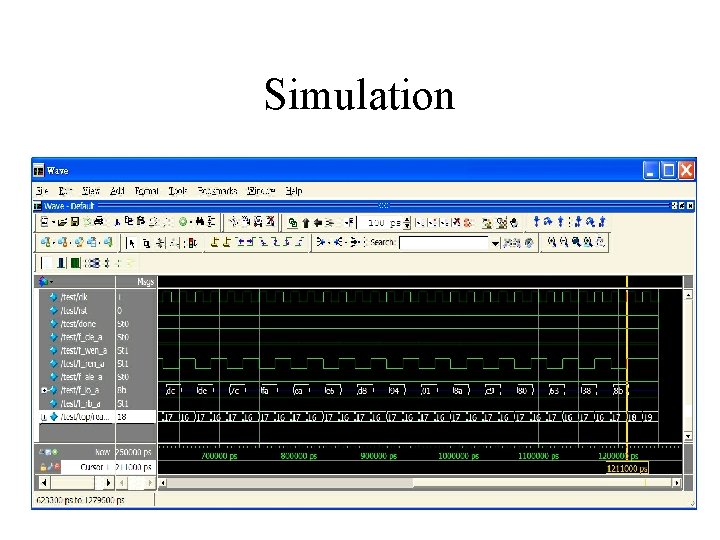

Simulation

Simulation

Simulation

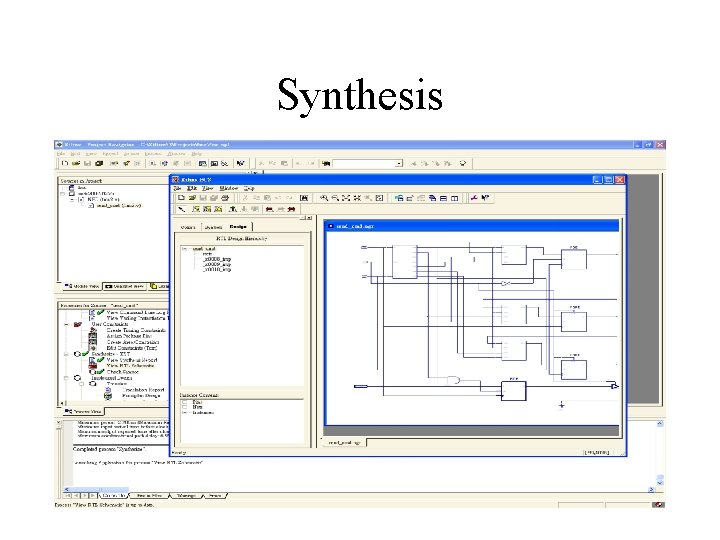

Synthesis

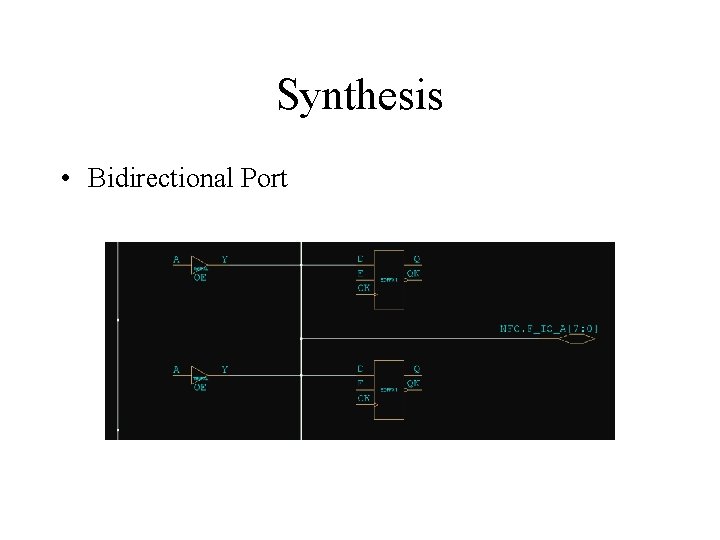

Synthesis • Bidirectional Port

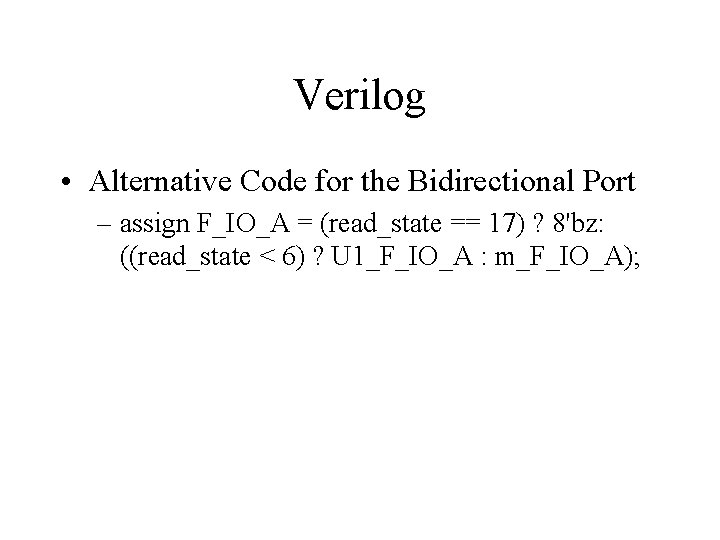

Verilog • Alternative Code for the Bidirectional Port – assign F_IO_A = (read_state == 17) ? 8'bz: ((read_state < 6) ? U 1_F_IO_A : m_F_IO_A);

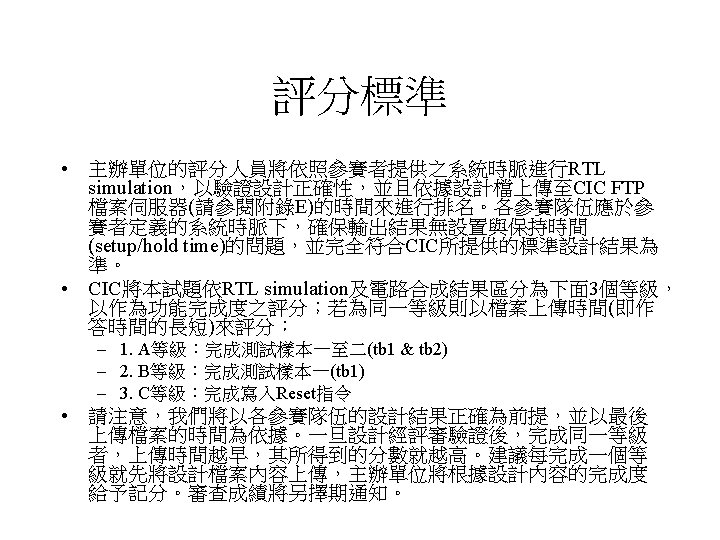

- Slides: 56