Requirements from CALICEDAQ for WP 5 Taikan Suehara

- Slides: 25

Requirements from CALICE-DAQ for WP 5 Taikan Suehara (Kyushu University, Japan) Taikan Suehara, AIDA-2020 kickoff meeting, 3 Jun. 2015 page 1

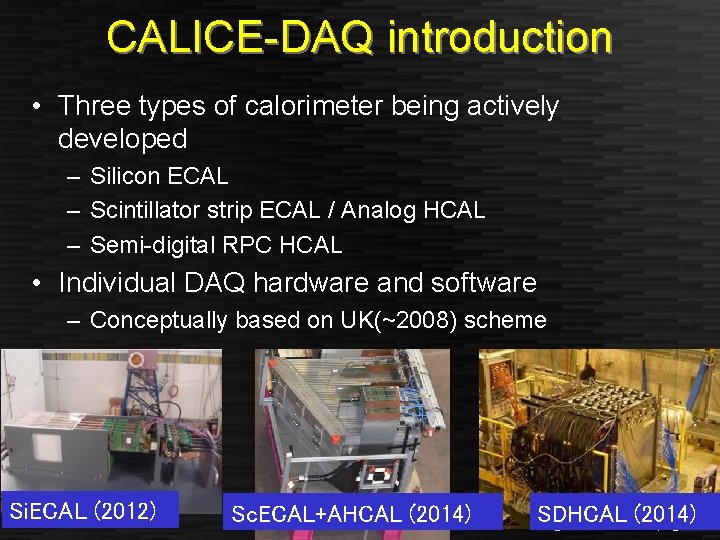

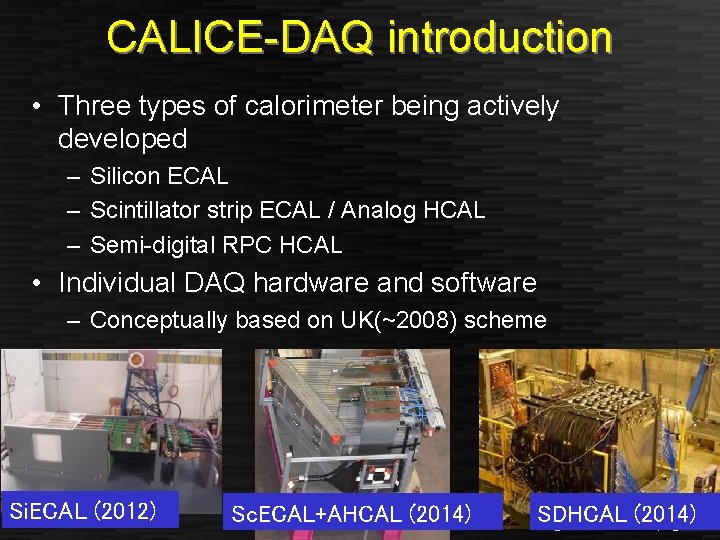

CALICE-DAQ introduction • Three types of calorimeter being actively developed – Silicon ECAL – Scintillator strip ECAL / Analog HCAL – Semi-digital RPC HCAL • Individual DAQ hardware and software – Conceptually based on UK(~2008) scheme Si. ECAL (2012) Sc. ECAL+AHCAL (2014)kickoff meeting, SDHCAL (2014) Taikan Suehara, AIDA-2020 3 Jun. 2015 page 2

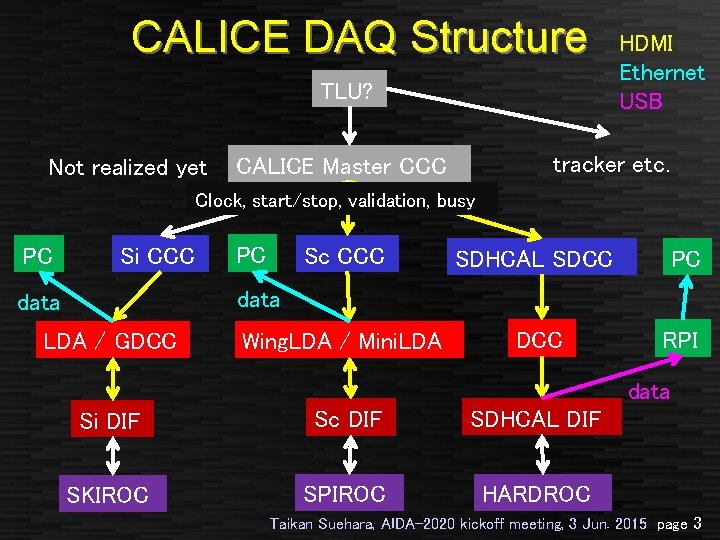

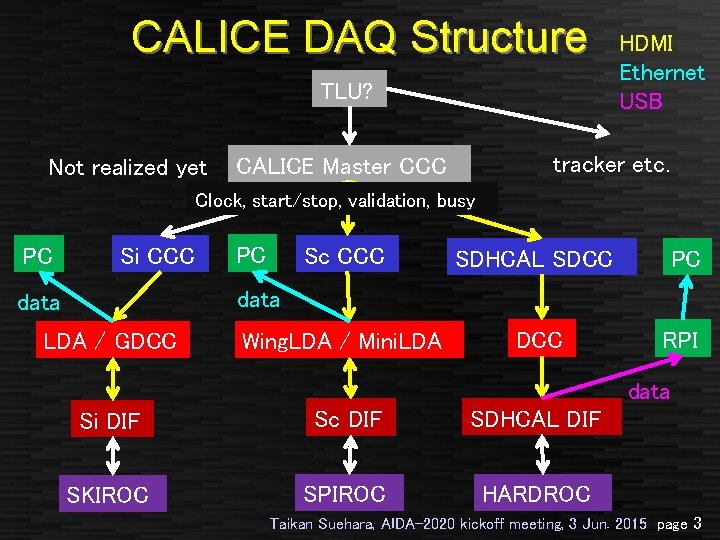

CALICE DAQ Structure TLU? Not realized yet HDMI Ethernet USB tracker etc. CALICE Master CCC Clock, start/stop, validation, busy PC Si CCC PC Sc CCC SDHCAL SDCC PC Wing. LDA / Mini. LDA DCC RPI data LDA / GDCC data Si DIF Sc DIF SDHCAL DIF SKIROC SPIROC HARDROC Taikan Suehara, AIDA-2020 kickoff meeting, 3 Jun. 2015 page 3

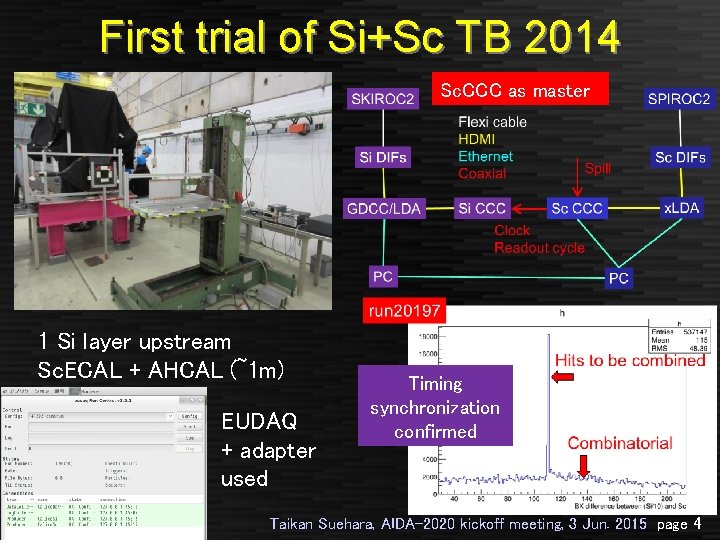

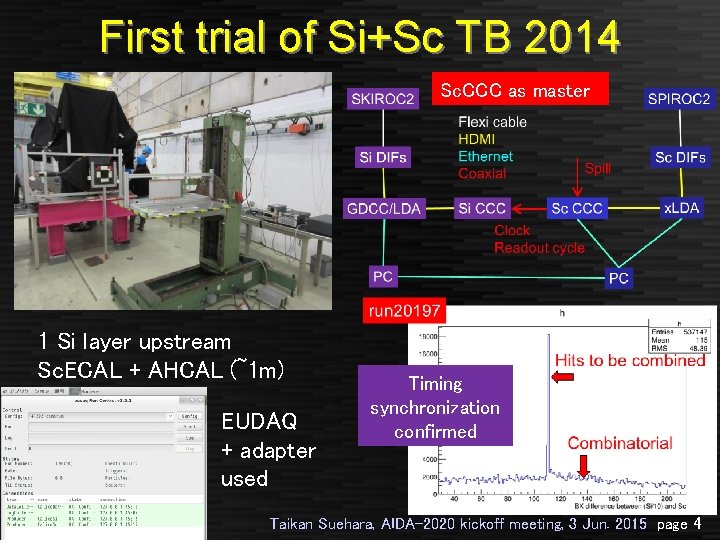

First trial of Si+Sc TB 2014 Sc. CCC as master 1 Si layer upstream Sc. ECAL + AHCAL (~1 m) EUDAQ + adapter used Timing synchronization confirmed Taikan Suehara, AIDA-2020 kickoff meeting, 3 Jun. 2015 page 4

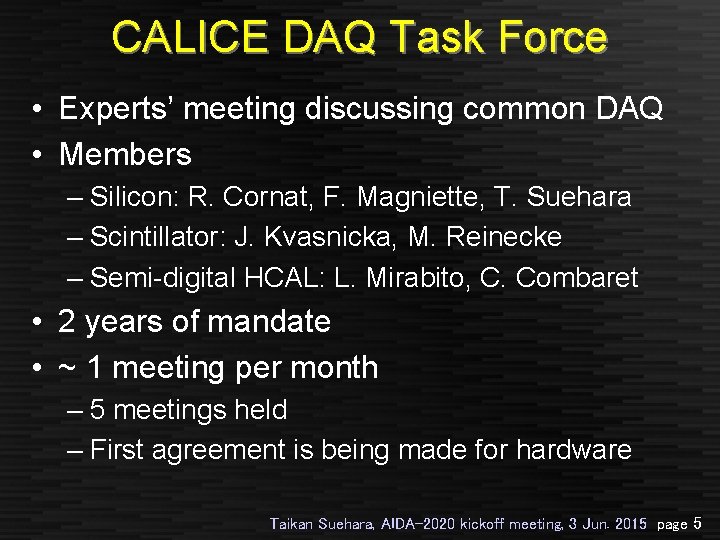

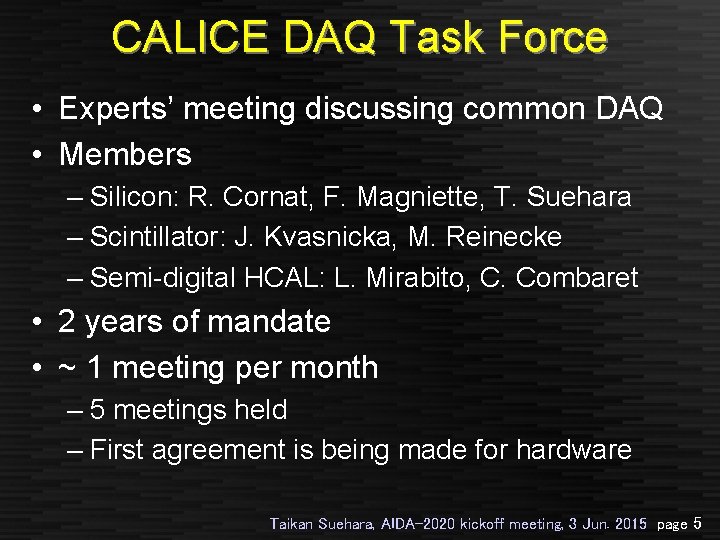

CALICE DAQ Task Force • Experts’ meeting discussing common DAQ • Members – Silicon: R. Cornat, F. Magniette, T. Suehara – Scintillator: J. Kvasnicka, M. Reinecke – Semi-digital HCAL: L. Mirabito, C. Combaret • 2 years of mandate • ~ 1 meeting per month – 5 meetings held – First agreement is being made for hardware Taikan Suehara, AIDA-2020 kickoff meeting, 3 Jun. 2015 page 5

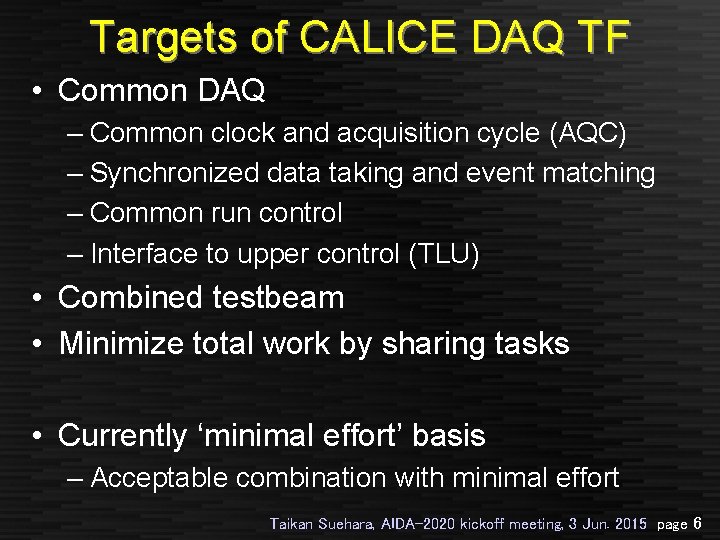

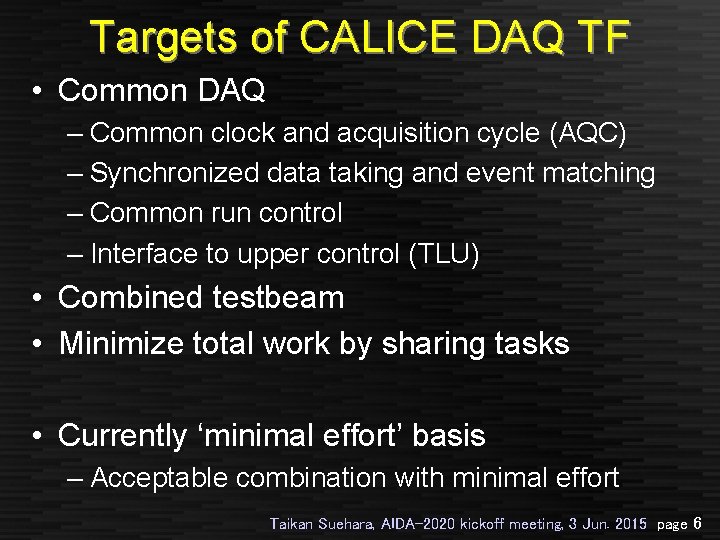

Targets of CALICE DAQ TF • Common DAQ – Common clock and acquisition cycle (AQC) – Synchronized data taking and event matching – Common run control – Interface to upper control (TLU) • Combined testbeam • Minimize total work by sharing tasks • Currently ‘minimal effort’ basis – Acceptable combination with minimal effort Taikan Suehara, AIDA-2020 kickoff meeting, 3 Jun. 2015 page 6

Hardware / Firmware Mainly based on discussion in CALICE DAQ TF with some personal bias Taikan Suehara, AIDA-2020 kickoff meeting, 3 Jun. 2015 page 7

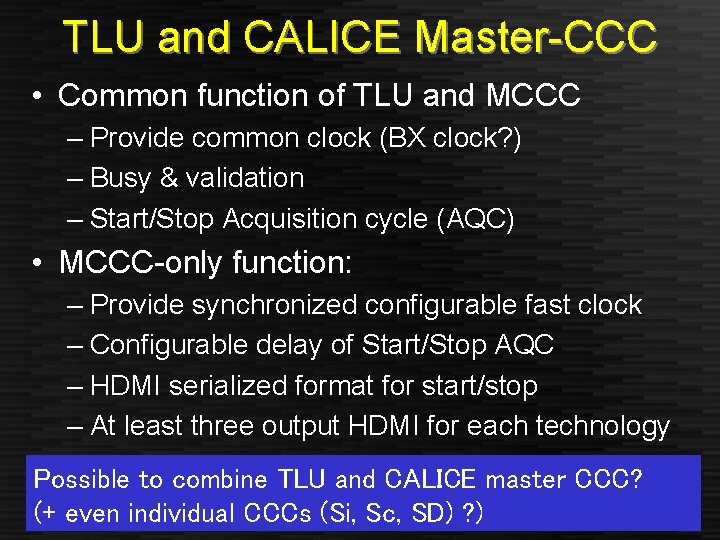

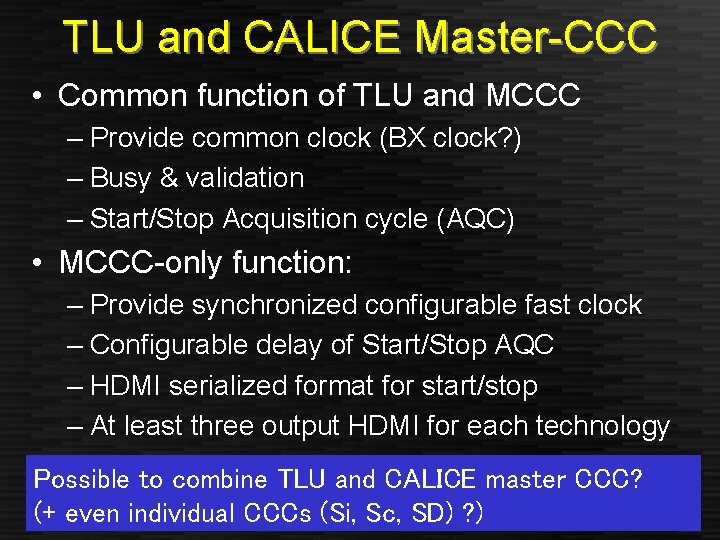

TLU and CALICE Master-CCC • Common function of TLU and MCCC – Provide common clock (BX clock? ) – Busy & validation – Start/Stop Acquisition cycle (AQC) • MCCC-only function: – Provide synchronized configurable fast clock – Configurable delay of Start/Stop AQC – HDMI serialized format for start/stop – At least three output HDMI for each technology Possible to combine TLU and CALICE master CCC? (+ even individual CCCs (Si, Sc, SD) kickoff ? ) meeting, 3 Jun. 2015 Taikan Suehara, AIDA-2020 page 8

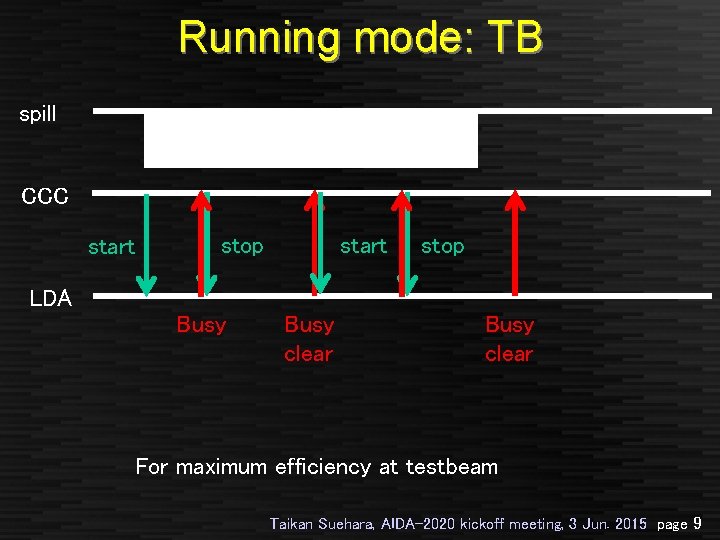

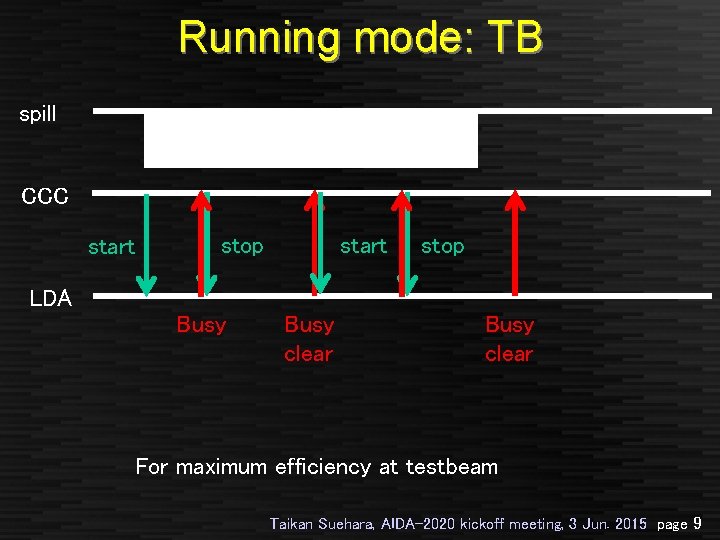

Running mode: TB spill CCC start stop LDA Busy clear For maximum efficiency at testbeam Taikan Suehara, AIDA-2020 kickoff meeting, 3 Jun. 2015 page 9

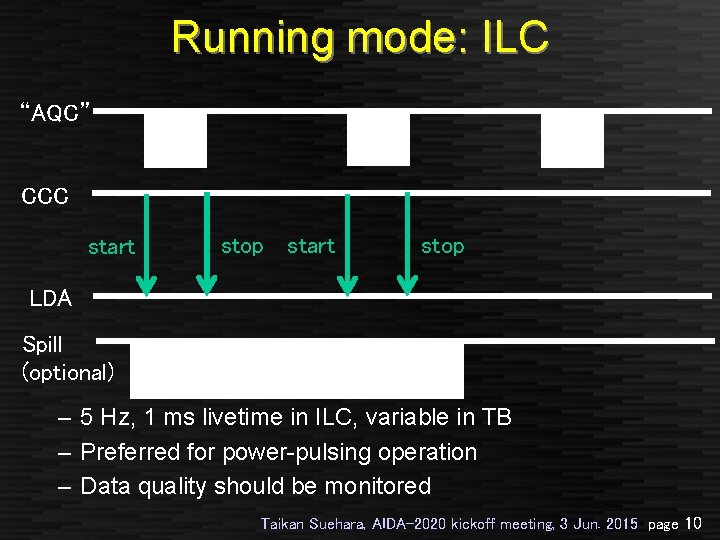

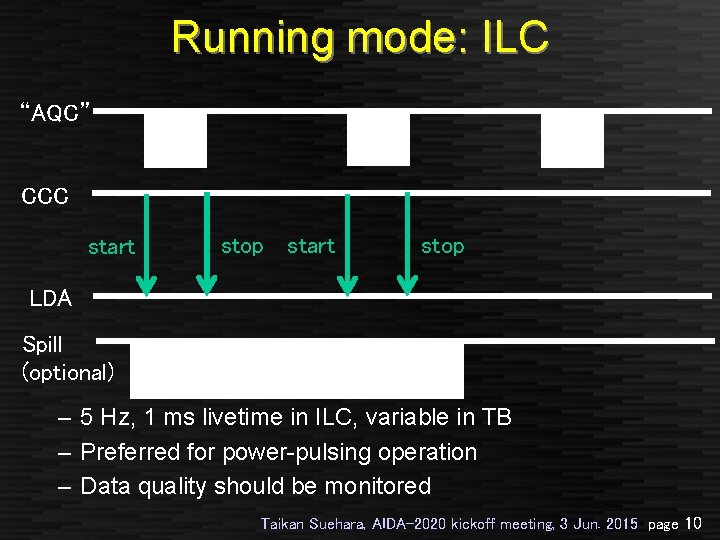

Running mode: ILC “AQC” CCC start stop LDA Spill (optional) – 5 Hz, 1 ms livetime in ILC, variable in TB – Preferred for power-pulsing operation – Data quality should be monitored Taikan Suehara, AIDA-2020 kickoff meeting, 3 Jun. 2015 page 10

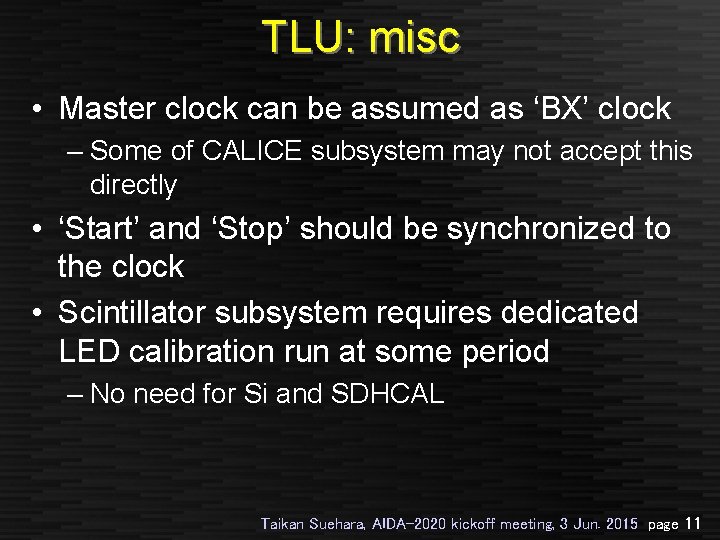

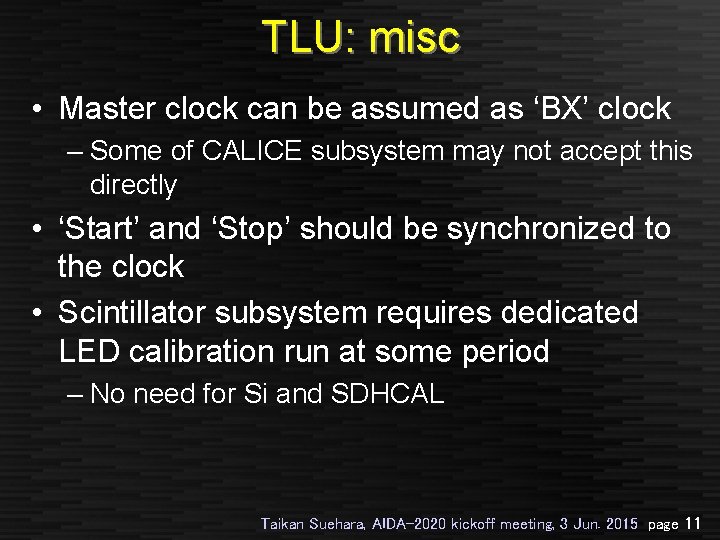

TLU: misc • Master clock can be assumed as ‘BX’ clock – Some of CALICE subsystem may not accept this directly • ‘Start’ and ‘Stop’ should be synchronized to the clock • Scintillator subsystem requires dedicated LED calibration run at some period – No need for Si and SDHCAL Taikan Suehara, AIDA-2020 kickoff meeting, 3 Jun. 2015 page 11

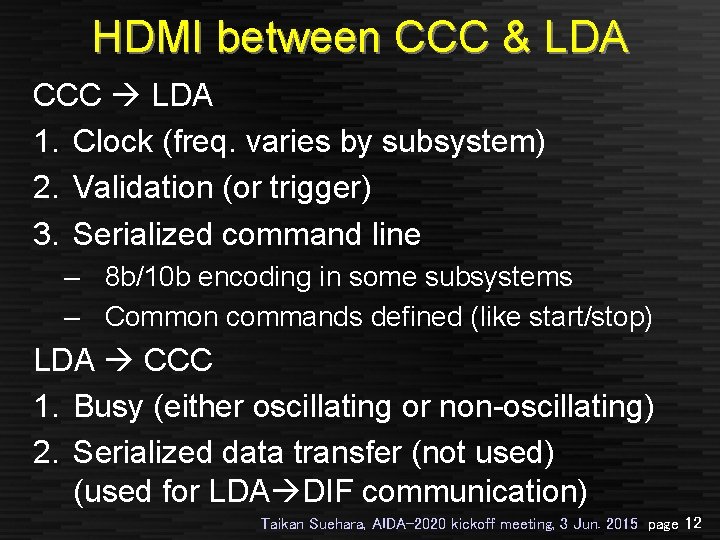

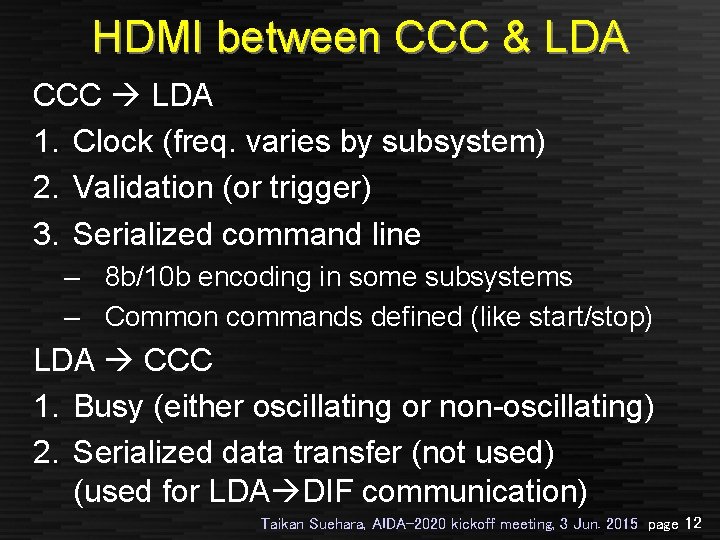

HDMI between CCC & LDA CCC LDA 1. Clock (freq. varies by subsystem) 2. Validation (or trigger) 3. Serialized command line – 8 b/10 b encoding in some subsystems – Common commands defined (like start/stop) LDA CCC 1. Busy (either oscillating or non-oscillating) 2. Serialized data transfer (not used) (used for LDA DIF communication) Taikan Suehara, AIDA-2020 kickoff meeting, 3 Jun. 2015 page 12

Master CCC • Not realized yet (DESY or/and Kyushu will contribute) – Planned to be implemented in Zync FPGA • Overlap of function with TLU – We expect compatibility with non-TLU run and TLU run Taikan Suehara, AIDA-2020 kickoff meeting, 3 Jun. 2015 page 13

Software Not discussed yet in CALICE DAQ TF, so this is mainly my personal opinion… Taikan Suehara, AIDA-2020 kickoff meeting, 3 Jun. 2015 page 14

Software • Common DAQ needs common software for – Run control and configuration – Data integration, monitoring and validation • Requirement for Common DAQ – Flexibility – (At least some) support – Scalability to at least full layer prototype • Multiple DAQ machine – Upgradability to real ILC DAQ Taikan Suehara, AIDA-2020 kickoff meeting, 3 Jun. 2015 page 15

LCIO trasfer • LCIO is our common data format • LCIO cannot be easily transferred via TCP – SIO uses stream but hard-coded to file IO – ‘Major effort’ needed to modify that but we desire to do so • Can be contributed by this WP? Taikan Suehara, AIDA-2020 kickoff meeting, 3 Jun. 2015 page 16

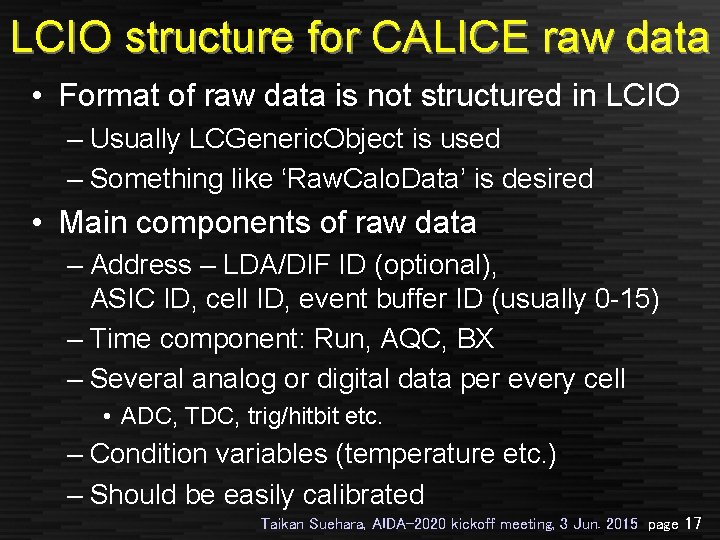

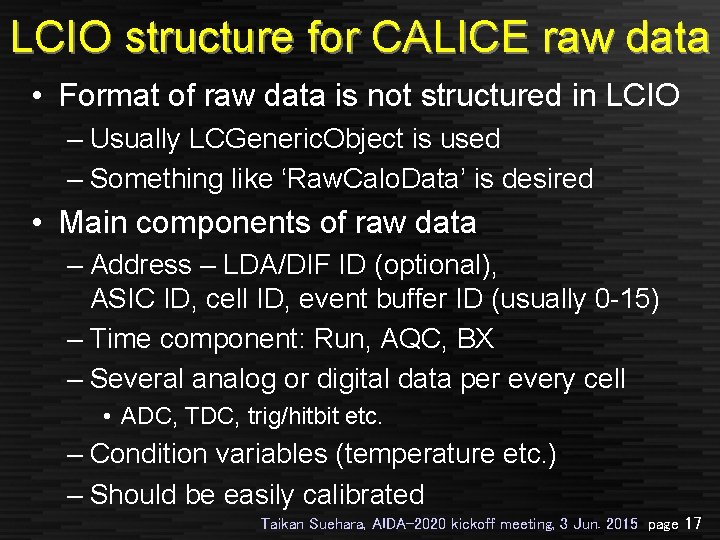

LCIO structure for CALICE raw data • Format of raw data is not structured in LCIO – Usually LCGeneric. Object is used – Something like ‘Raw. Calo. Data’ is desired • Main components of raw data – Address – LDA/DIF ID (optional), ASIC ID, cell ID, event buffer ID (usually 0 -15) – Time component: Run, AQC, BX – Several analog or digital data per every cell • ADC, TDC, trig/hitbit etc. – Condition variables (temperature etc. ) – Should be easily calibrated Taikan Suehara, AIDA-2020 kickoff meeting, 3 Jun. 2015 page 17

EUDAQ From my personal observation of EUDAQ 1. 4. 1, not EUDAQ 2 Taikan Suehara, AIDA-2020 kickoff meeting, 3 Jun. 2015 page 18

EUDAQ: structure • In the current EUDAQ structure projectspecific codes are not well separated from core • We want to compile minimum-core + ILC specific + LCIO (and not Eutelescope which requires broader range of ILCsoft) • Dynamic loading of DLL may be necessary Taikan Suehara, AIDA-2020 kickoff meeting, 3 Jun. 2015 page 19

EUDAQ: communication • We would keep the independence of individual DAQ frameworks • Well-defined communication protocol is desired between EUDAQ and individual DAQ • Controlling EUDAQ from scripts is also desired • One proposal – Configuration by xml which can be transferred via TCP as well as gotten from a file – Each control command is communicated with xml structure, can be communicated from scripts as well – Data can be exchanged in a desired format by users, for us LCIO if available… Taikan Suehara, AIDA-2020 kickoff meeting, 3 Jun. 2015 page 20

EUDAQ: scalability • Our (quasi-final) prototype may consist of – ~ 1 k ASICS, ~ 100 k channels per subsystem – Should be acquired by 1 -10 PC per subsystem – Of course integration to 1 PC should be a bottleneck parallel acquisition is necessary – Real ILC: ~ 1 M ASICS, ~ 100 M channels O(1 k) PCs? Taikan Suehara, AIDA-2020 kickoff meeting, 3 Jun. 2015 page 21

EUDAQ: contribution from CALICE • ‘CALICE’ part of EUDAQ should be controlled by us, with support from coredevelopers – Of course contribution from core-developers are mostly very welcome • We want to propose or contribute to corecode as well • We need regular communication for codevelopment of EUDAQ and CALICEEUDAQ Taikan Suehara, AIDA-2020 kickoff meeting, 3 Jun. 2015 page 22

Misc: condition database • Condition should be stored and managed at some good coordination – – – Easy interface (from web, from script, etc. ) Accessibility from the web Access control Safety (backup, conflict, etc. ) Local replication (for testbeam etc. ) Flexible structure (multiple calibration, etc. ) • What to store (example) – Layer structure (LDA#, DIF#, ASIC#. . . ) – Calibration constants and settings (gain, noise, bias HV etc. ) – General condition (place, TB used, failure, repair etc. ) Taikan Suehara, AIDA-2020 kickoff meeting, 3 Jun. 2015 page 23

Misc: beam interface • Communication to facility (accelerator) is usually not well established during the short TB period • Standard interface is important • Desired functions: – Logging various accelerator parameter • Stored on condition database? ? – Easy access online/offline – Time stamping according to run/AQC/(BX) • Maybe receiving TLU Taikan Suehara, AIDA-2020 kickoff meeting, 3 Jun. 2015 page 24

Summary • We recognize that CALICE-DAQ related work is a big part of WP 5, and WP 5 is important for CALICE-DAQ • For hardware, TLU and master CCC should be in close connection • For software, closer collaboration is needed for further development Taikan Suehara, AIDA-2020 kickoff meeting, 3 Jun. 2015 page 25