REPBLICA BOLIVARIANA DE VENEZUELA UNIVERSIDAD NACIONAL EXPERIMENTAL POLITCNICA

REPÚBLICA BOLIVARIANA DE VENEZUELA UNIVERSIDAD NACIONAL EXPERIMENTAL POLITÉCNICA “ANTONIO JOSÉ DE SUCRE” VICE-RECTORADO PUERTO ORDAZ Departamento de Ingeniería Electrónica TEMA VI Control del Enlace de Datos

Sumario 1. ¿Qué es el Control de Flujo? 2. Control de Flujo 3. Detección de Errores 4. Control de Errores 5. Control del Enlace de Datos a Alto Nivel

¿Qué es el Control de Flujo? Es el proceso integral que permite que se realice el proceso de intercambio datos de información para una comunicación en forma eficiente.

Capa Protocolo Enlace de Datos Las funciones de esta capa son: 1. Control de Flujo 2. Detección de Errores 3. Control de Errores

Requisitos y Objetivos para la comunicación de datos 1. Sincronización 2. Control de Flujo 3. Control de Errores 4. Direccionamiento 5. Datos y Control sobre el mismo enlace 6. Gestión de Enlace

Control de Flujo Posibilita que no se desborde la memoria temporal de transferencia del receptor. Ver Figura

Control de Flujo Tiempo de Transmisión: tiempo empleado por una estación para emitir todos los bits de una trama. Es proporcional a la trama. Tiempo de Propagación: tiempo empleado por un bit en atravesar el medio de transmisión desde el origen hasta el destino, se denotará por “a”.

Control de Flujo Los tipos de control de flujo son: 1. Control de Flujo mediante Parada-Espera. 2. Control de Flujo mediante Ventana Deslizante.

Detección de Errores En todo sistema de transmisión habrá ruido, independientemente de cómo haya sido diseñado. El ruido dará lugar a errores que modificaran uno o varios bits de la trama.

Detección de Errores Se definen las probabilidades términos de los errores en tramas transmitidas: en las 1. Pb: Probabilidad de UN BIT erróneo, también denominada tasa de error por BIT BER (Bit Error Rate). 2. P 1: Probabilidad de que una trama llegue sin errores.

Detección de Errores Se define las probabilidades términos de los errores en tramas transmitidas (Cont. ): en las 3. P 2: Probabilidad de que una trama llegue con uno o más errores no detectables. 4. P 3: Probabilidad de que una trama llegue con uno o más errores detectables pero sin errores indetectables.

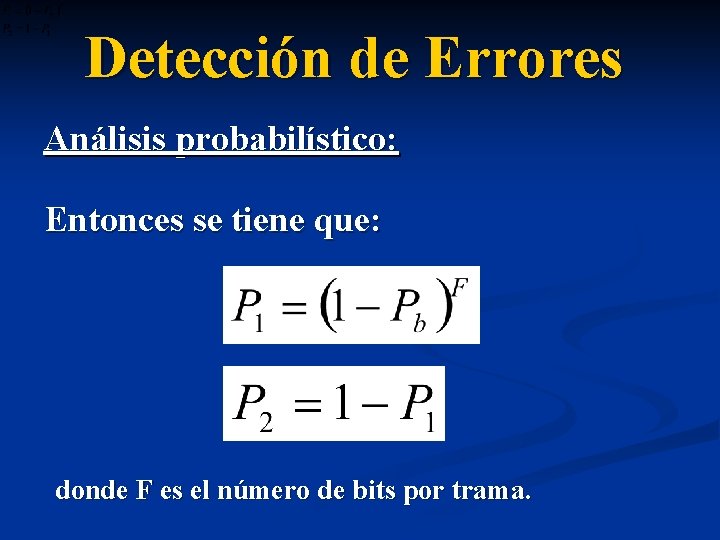

Detección de Errores Análisis probabilístico Si se considera el caso en el que no se toman medidas para detectar errores, la probabilidad de errores detectables (P 3) es cero. Para las otras probabilidades, se supondrá que todos los bits tienen una probabilidad de error (Pb) constante, independientemente de donde estén situados en la trama.

Detección de Errores Análisis probabilístico: Entonces se tiene que: donde F es el número de bits por trama.

Detección de Errores Análisis probabilístico: Se puede Concluir: 1. La probabilidad de que una trama llegue sin ningún BIT erróneo disminuye al aumentar la probabilidad de que un BIT sea erróneo.

Detección de Errores Análisis probabilístico: Se puede Concluir: 2. La probabilidad de que una trama llegue sin errores disminuye al aumentar la longitud de la misma; cuanto mayor es la trama, mayor número de bits tendrá, y mayor será la probabilidad de que alguno de los bits sea erróneo.

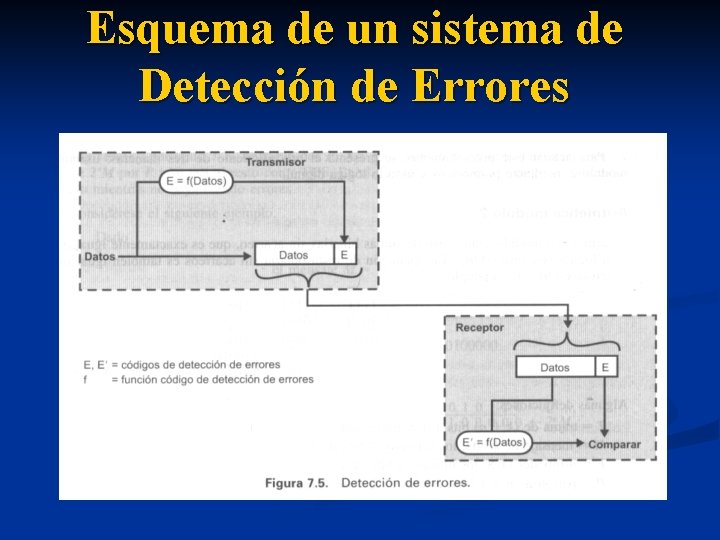

Esquema de un sistema de Detección de Errores

Esquema de un sistema de Detección de Errores Desarrolle el ejemplo de la página 188 del libro de texto.

Detección de Errores Se tienen los siguientes casos: • Comprobación de Paridad • Comprobación de Redundancia Cíclica (CRC)

Control de Errores El control de errores hace referencia a los mecanismos necesarios para la detección y la corrección de errores que aparecen en la transmisión de tramas.

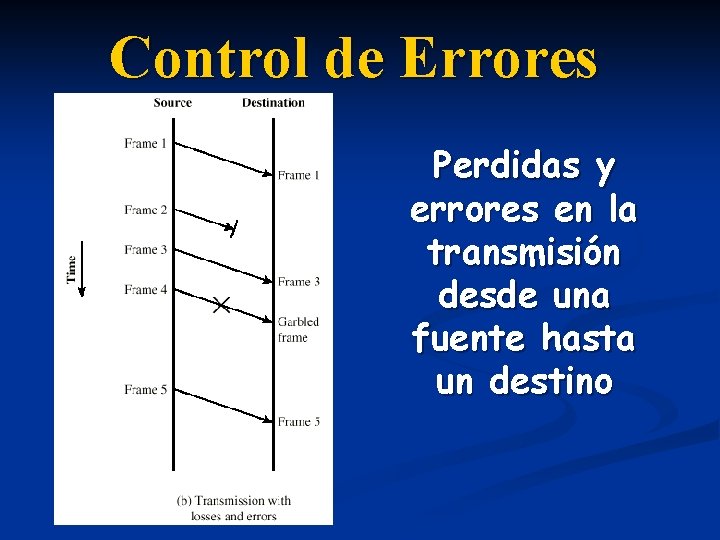

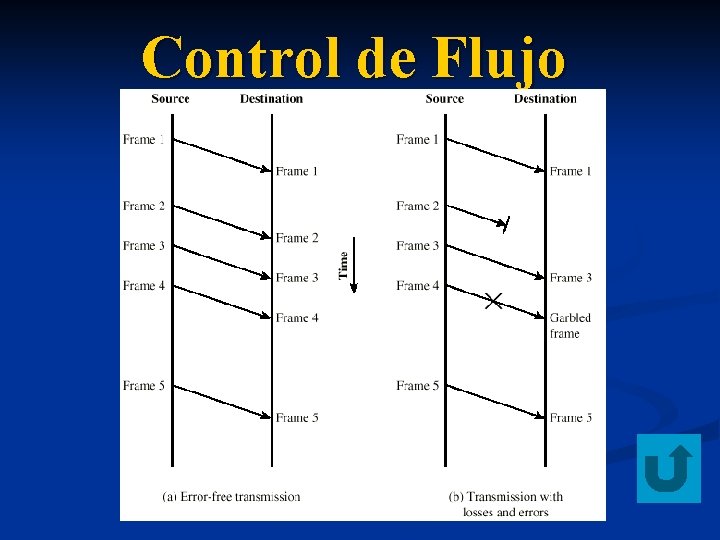

Control de Errores Perdidas y errores en la transmisión desde una fuente hasta un destino

Control de Errores Tipos de Errores potenciales: Trama Perdida: se da cuando una trama enviada no llega al destino. Trama dañada: ocurre cuando llega una trama, pero con algunos bits erróneos (modificados durante la transmisión).

Control de Errores basado en: Detección de errores: discutida previamente. Confirmaciones positivas: el destino devuelve una confirmación positiva por cada trama recibida con éxito y libre de errores. Retransmisión después de la expiración de un intervalo de tiempo: la fuente retransmite las tramas que no se han confirmado tras un período de tiempo predeterminado. Confirmación negativa y retransmisión: el destino devuelve una confirmación negativa al detectar errores en las tramas recibidas. La fuente retransmitirá de nuevo esas tramas.

Tipos de ARQ Los mecanismos de respuestas se conocen genéricamente como Solicitud de Repetición Automática (ARQ, automatic repeat request). Hay tres variantes normalizadas: • ARQ con parada-y-espera • ARQ con vuelta-atrás-N • ARQ con rechazo selectivo

Otros Métodos de Detección de Errores existen otros métodos para la detección de errores que analizaremos a continuación: • Chequeo de Paridad Vertical: VRC • Chequeo de Paridad Longitudinal: LRC • Chequeo de paridad Bidimensional: VRC/LRC

Actividades Realice una lectura general de la sección 7. 4 del libro de texto. (HDLC) Resuelva algunos de los problemas propuestos Lea el apéndice 7 A

Fin Tema VI Gracias

Control de Flujo Posibilita que el receptor regule el flujo de datos enviados por el emisor, con la finalidad que la memoria del receptor no se desborde.

Detección de Errores Se implementa con un código con capacidad de detección de errores y dependerá de los bits transmitidos.

Control de Errores Se lleva a cabo mediante la retransmisión de las tramas dañadas que no hayan sido confirmadas o las que desde el otro extremo se reciba una petición de retransmisión.

Control de Flujo

Control de Flujo mediante Parada-Espera Se envía una trama por el transmisor, el receptor recibe esa trama y le indica al transmisor cuando debe enviar la siguiente.

Control de Flujo mediante Parada-Espera EMISOR RECEPTOR LA SIGUIENTE TRAMA SE TRANSMITE CUANDO SE HAYA RECIBIDO LA CONFIRMACIÓN DE LA TRAMA ANTERIOR

Control de Flujo mediante Parada-Espera Las razones de la construcción de tramas son: 1. El tamaño de la memoria temporal del receptor puede ser limitada 2. Cuanto más larga sea la transmisión, es más probable que haya errores.

Control de Flujo mediante Parada-Espera Las ventajas de la construcción de trama son (Continuación): 3. En medios compartidos, no se permite que una estación ocupe el medio por mucho tiempo.

Control de Flujo mediante Parada-Espera Este esquema tiene problemas, porque cada vez solo puede haber una trama en transito. Se presenta como:

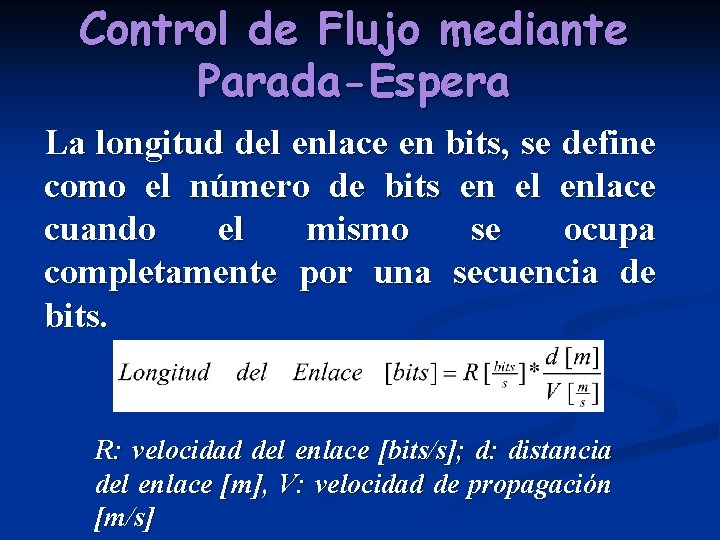

Control de Flujo mediante Parada-Espera La longitud del enlace en bits, se define como el número de bits en el enlace cuando el mismo se ocupa completamente por una secuencia de bits. R: velocidad del enlace [bits/s]; d: distancia del enlace [m], V: velocidad de propagación [m/s]

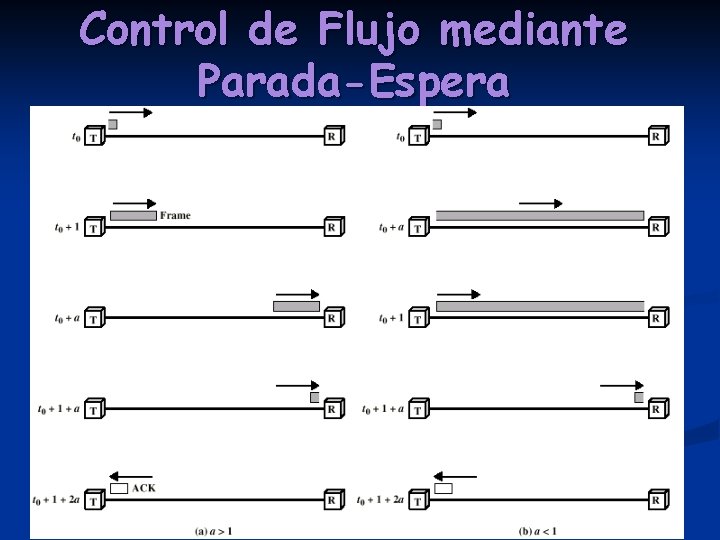

Control de Flujo mediante Parada-Espera

Control de Flujo mediante Parada-Espera Para grandes distancias y/o velocidades de transmisión grandes es aconsejable la utilización de grandes valores de `a´, donde `a´ es el retardo de propagación.

Control de Flujo mediante Parada-Espera NOTA IMPORTANTE: 1. Para a > 1, la línea está siempre infrautilizada. 2. Para a < 1, la línea está utilizada ineficientemente.

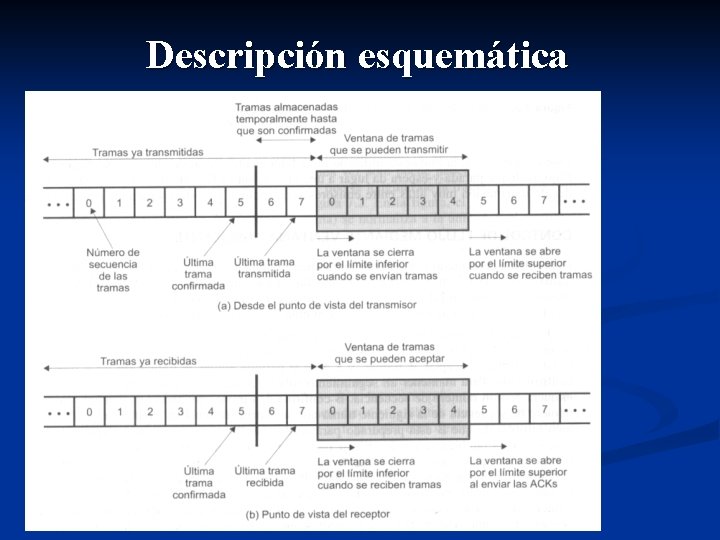

Control de Flujo mediante Ventana Deslizante Características: 1. El sistema permite múltiples tramas en transito 2. El receptor posee una memoria de longitud W 3. El transmisor puede enviar hasta W tramas sin acuse de recibo 4. Cada trama es numerada

Control de Flujo mediante Ventana Deslizante Características (Cont. ): 5. La Confirmación incluye el número de la próxima trama esperada. 6. Para un campo de k bits el rango de números de secuencias ira desde 0 hasta 2 k -1. 7. Las tramas se numerarán modulo 2 k

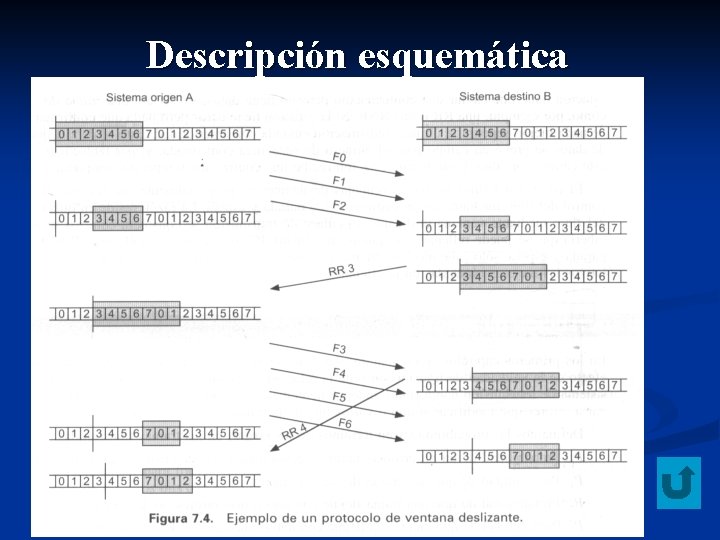

Descripción esquemática

Descripción esquemática

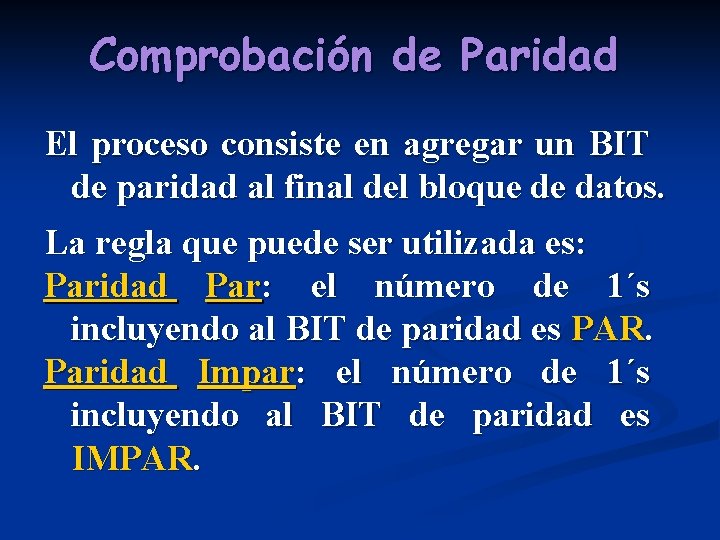

Comprobación de Paridad El proceso consiste en agregar un BIT de paridad al final del bloque de datos. La regla que puede ser utilizada es: Paridad Par: el número de 1´s incluyendo al BIT de paridad es PAR. Paridad Impar: el número de 1´s incluyendo al BIT de paridad es IMPAR.

Comprobación de Paridad Ejemplo: Sea el caracter G=1110001 Si se utiliza paridad para transmitir este carácter, se tendrá: G= 1110001 P a) Si P es paridad par, G= 11100010 b) Si P es paridad impar, G= 11100011

Comprobación de Paridad Generalmente, se utiliza: Paridad Par: para comunicaciones SINCRÓNICAS. Paridad Impar: para comunicaciones ASINCRÓNICAS. ¿Debilidades del método?

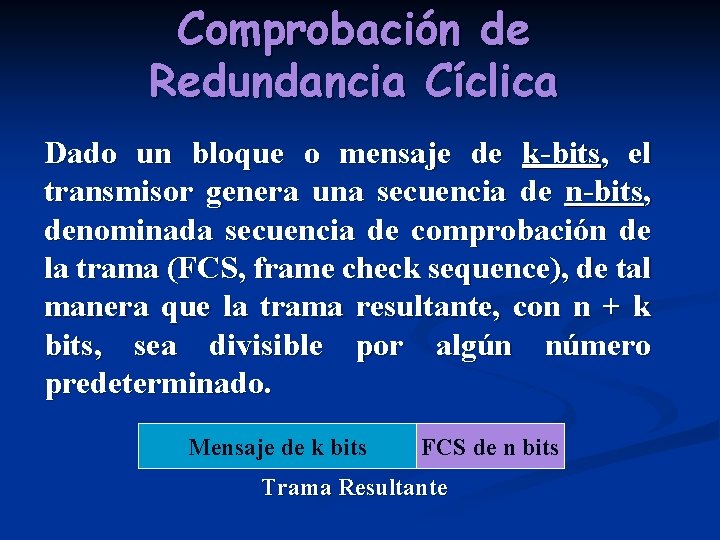

Comprobación de Redundancia Cíclica Dado un bloque o mensaje de k-bits, el transmisor genera una secuencia de n-bits, denominada secuencia de comprobación de la trama (FCS, frame check sequence), de tal manera que la trama resultante, con n + k bits, sea divisible por algún número predeterminado. Mensaje de k bits FCS de n bits Trama Resultante

Comprobación de Redundancia Cíclica Al Recibirlo, el receptor entonces dividirá la trama recibida por ese número y, si no hay resto en la división, se supone que no ha habido errores. Resto = 0 ¡No hay Error !

CRC con Polinomios Analice el proceso de implementación de éstas técnicas en la página 193 del libro de texto.

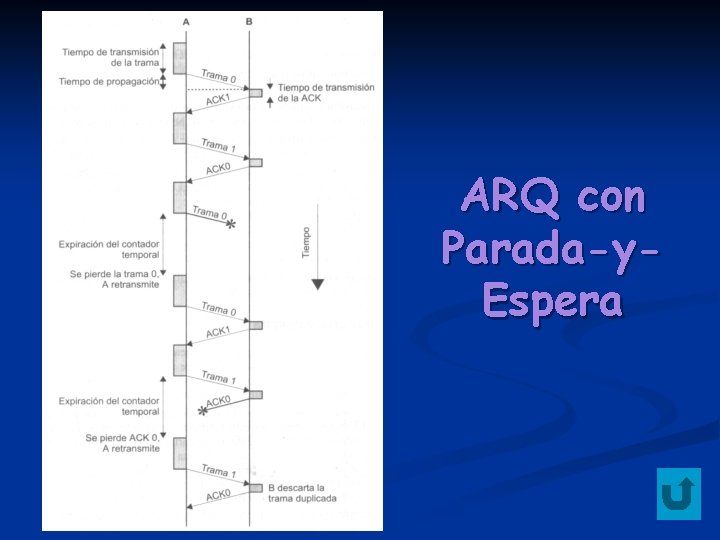

ARQ con Parada-y-Espera La estación fuente transmite una única trama y entonces debe esperar la recepción de una confirmación (ACK, «acknowledgment» ). No se podrá enviar ninguna otra trama hasta que la respuesta de la estación destino vuelva al emisor.

ARQ con Parada-y-Espera Para evitar duplicidad en las tramas de confirmación, estas se numeran alternadamente con “ 0” o “ 1”, y las confirmaciones positivas serán de la forma ACK 0 y ACKl. Se tiene la convención de: Un ACK 0 confirma la recepción de la trama numerada con “ 1” e indica que el receptor está preparado para aceptar la trama numerada con “ 0”.

ARQ con Parada-y. Espera

ARQ con Vuelta-Atrás-N En esta técnica, una estación puede enviar una serie de tramas numeradas secuencialmente módulo algún valor máximo dado. Si la trama llega bien, se envía la confirmación RR (Receive Ready). Si hay error, se envía una confirmación negativa REJ (Reject)

ARQ con Vuelta-Atrás-N Al recibirse una trama con error, se rechaza esa trama y todas las que lleguen después de ella, hasta que se reciba correctamente la trama errónea. Esto indica que se deben re-enviar la trama errónea y todas las tramas enviadas después de ella.

ARQ con Vuelta-Atrás-N Esta técnica tiene en cuenta las siguientes contingencias: 1. TRAMA DETERIORADA 2. UNA RR DETERIORADA 3. UNA TRAMA REJ DETERIORADA

Ejemplos para ARQ Vuelta-Atrás-N

TRAMA DETERIORADA Si la trama recibida es no válida (es decir, B detecta un error), B descarta dicha trama sin más. Llegados a este punto se plantean dos posibilidades: a) “A” envía la trama (i+1) dentro de un periodo de tiempo razonable. B recibe la Trama (i+1) fuera de orden y envía un REJ i. “A” debe retransmitir la trama i y todas las posteriores.

TRAMA DETERIORADA b) “A” no envía tramas adicionales en un breve espacio de tiempo. B no recibe nada, por lo que ni devuelve una RR ni una REJ. Cuando el temporizador de “A” expira, se transmitirá una trama RR que incluirá un bit denominado P, que será puesto a 1. B interpretará la trama RR con el bit P igual a 1, como si fuera una orden que debe ser confirmada enviando una RR para indicar la siguiente trama que se espera recibir, es decir la trama i. Cuando “A” recibe la RR, retransmite la trama i.

RR DETERIORADA a) “B” recibe la trama i y envía RR (i + 1), que se pierde en el camino. Como las confirmaciones son acumulativas, puede ocurrir que “A” reciba una RR posterior para una trama posterior y que llegue antes de que el temporizador asociado a la trama i expire. b) Si el temporizador de “A” expira, se transmite una orden RR, como en el caso 1 b.

TRAMA REJ DETERIORADA La perdida de una trama REJ es equivalente al caso 1 b.

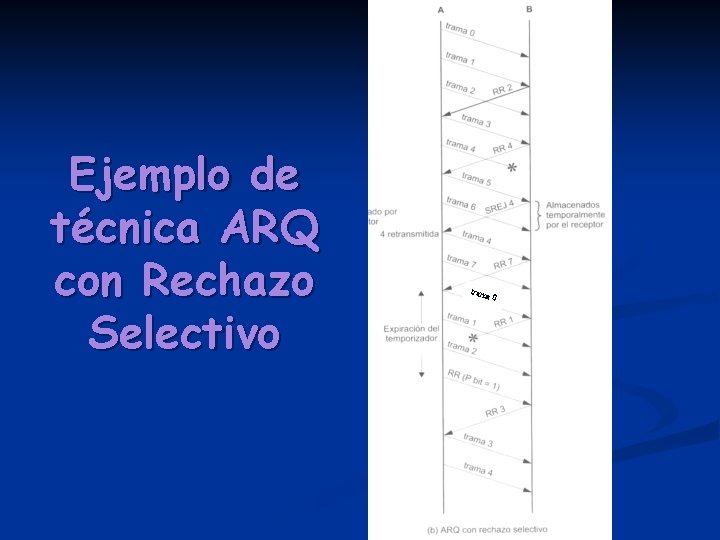

ARQ con Rechazo Selectivo En esta técnica, las únicas tramas que se retransmiten son aquellas para las que se recibe una confirmación negativa, denominada SREJ, o aquellas para las que el temporizador correspondiente expira.

ARQ con Rechazo Selectivo El receptor deberá reservar una zona de memoria temporal lo suficientemente grande para almacenar las tramas tras una SREJ, hasta que la trama errónea se retransmita. Debe tener lógica adicional para reinsertar la trama reenviada en la posición correspondiente.

Ejemplo de técnica ARQ con Rechazo Selectivo tram a 0

Limitaciones de ARQ con Rechazo Selectivo Existe una limitación en cuanto al tamaño máximo de la ventana en el caso del rechazo selectivo Considérese el caso de un rechazo selectivo que utilice 3 bits para los números de secuencia. Permítase un tamaño de ventana igual a 7, y ténganse en cuenta las siguientes consideraciones:

Limitaciones de ARQ con Rechazo Selectivo 1. La estación “A” envía las tramas numeradas desde la 0 hasta la 6 a la estación “B” 2. La estación “B” recibe las siete tramas y las confirma acumulativamente con RR 7 3. Debido a una ráfaga de ruido, la RR 7 se pierde. 4. El temporizador de “A” expira y se retransmite la trama 0.

Limitaciones de ARQ con Rechazo Selectivo 5. “B” ha desplazado su ventana de recepción indicando que acepta las tramas 7, 0, 1, 2, 3, 4, y 5. Al recibir la numero 0 anterior supone que la trama 7 se ha perdido, y que se trata de una trama 0 diferente, por tanto la acepta. Esto se debe a un solapamiento de la ventana de transmisión con la de recepción.

Limitaciones de ARQ con Rechazo Selectivo Para evitar este problema, el tamaño máximo de la ventana no debería ser mayor que la mitad del rango de los números de secuencia. En la situación anterior, si se permitiera que sólo 4 tramas estuvieran pendientes de confirmación, se evitarían las ambigüedades. En general, para un campo de números de secuencia de k bits, es decir, para un rango de 2 k, el tamaño máximo de la ventana se limita a 2 k-1.

Chequeo de Paridad Vertical: VRC Esta técnica se aplica para códigos ASCII, lo cual facilita su empleo a nivel de byte. Consiste en agregar un octavo bit al código de cada carácter que se desea transmitir y calcular dicho bit en función de la paridad deseada, par o impar.

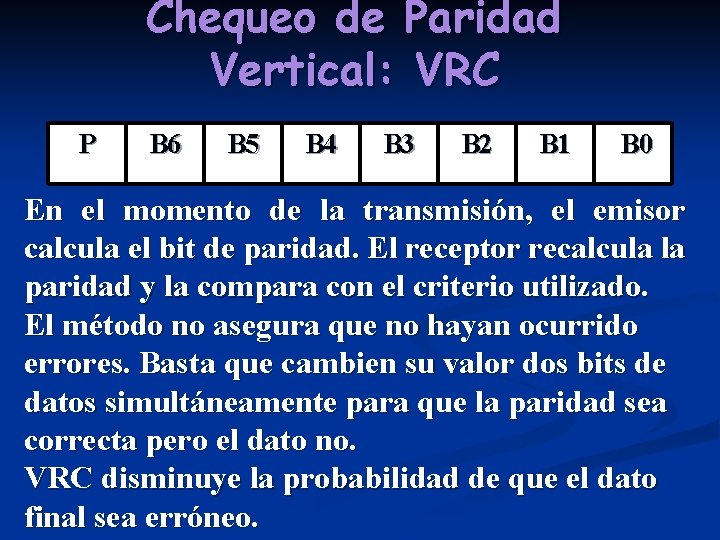

Chequeo de Paridad Vertical: VRC P B 6 B 5 B 4 B 3 B 2 B 1 B 0 En el momento de la transmisión, el emisor calcula el bit de paridad. El receptor recalcula la paridad y la compara con el criterio utilizado. El método no asegura que no hayan ocurrido errores. Basta que cambien su valor dos bits de datos simultáneamente para que la paridad sea correcta pero el dato no. VRC disminuye la probabilidad de que el dato final sea erróneo.

Chequeo de Paridad Vertical: VRC Consideraciones Prácticas: VRC disminuye la probabilidad de que el dato final sea erróneo. Por ejemplo, para líneas telefónicas transmitiendo entre 103 y 104 bps el error es BER=10 -5 (un bit de error en cada 105 bits). Al emplear este método se pueden obtener valores de BER= 10 -7

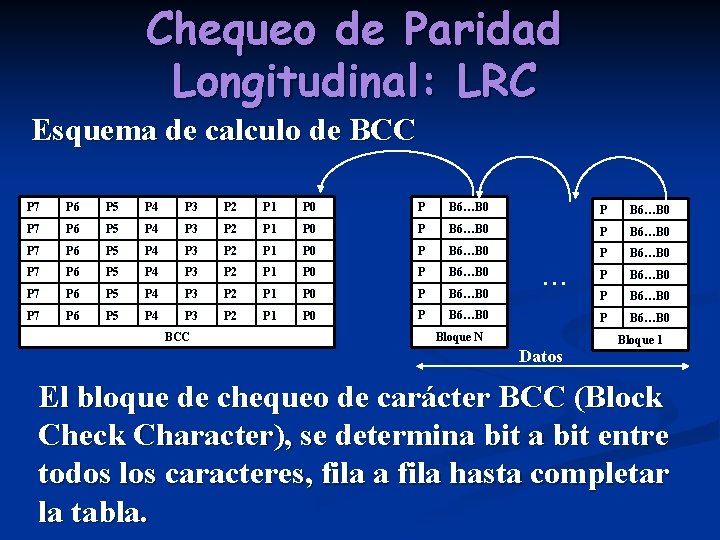

Chequeo de Paridad Longitudinal: LRC Se aplica para un conjunto de caracteres. A cada carácter se le determina su bit de paridad, para posteriormente construir una tabla global de paridad de 8 columnas y “m” filas.

Chequeo de Paridad Longitudinal: LRC Esquema de calculo de BCC P 7 P 6 P 5 P 4 P 3 P 2 P 1 P 0 P B 6…B 0 P B 6…B 0 P 7 P 6 P 5 P 4 P 3 P 2 P 1 P 0 P B 6…B 0 BCC . . . Bloque N Datos Bloque 1 El bloque de chequeo de carácter BCC (Block Check Character), se determina bit entre todos los caracteres, fila a fila hasta completar la tabla.

Chequeo de Paridad Longitudinal: LRC El esquema muestra que se deben transmitir los “n” arreglos de datos más el arreglo BCC. En el receptor se determina de igual manera la paridad del sistema para determinar si hubo o no errores.

Chequeo de Paridad Bidimensional: VRC/LRC Este esquema se obtiene de la combinación de los métodos VRC y LRC. El arreglo tiene dos dimensiones, abscisa y ordenada. Con el VRC se obtiene la abscisa y con el LRC la ordenada.

Chequeo de Paridad Bidimensional: VRC/LRC Ejemplo: LRC (Par) H O L A Bits 0 0 1 B 0 1 0 0 B 1 0 0 1 1 0 B 2 1 1 0 B 3 0 0 0 B 4 0 0 0 B 5 0 1 1 B 6 0 0 1 1 0 VRC (Par)

Chequeo de Paridad Bidimensional: VRC/LRC Error de paridad Ejemplo: si se recibiera con un error: LRC (Par) H O L A Bits 0 0 1 B 0 1 0 0 B 1 0 0 0 1 0 B 2 1 1 0 B 3 0 0 0 B 4 0 0 0 B 5 0 1 1 B 6 0 0 1 1 0 VRC (Par) Error de paridad

Chequeo de Paridad Bidimensional: VRC/LRC Ejemplo: si se recibiera con un error La detección del error se efectúa determinando la paridad de VRC y LRC, la intercepción de la fila y la columna errónea, permite ubicar el error. Algunas combinaciones de más de un error se pueden detectar, otras no.

Chequeo de Paridad Bidimensional: VRC/LRC Ejemplo: Combinación de dos errores LRC (Par) H O L A Bits 0 0 1 B 0 1 0 0 B 1 0 0 1 1 0 B 2 1 1 0 B 3 0 0 1 0 0 B 4 0 0 0 B 5 0 1 1 B 6 0 0 1 1 0 VRC (Par)

Chequeo de Paridad Bidimensional: VRC/LRC Ejemplo: Combinación de tres errores LRC (Par) H O L A Bits 0 0 1 B 0 1 0 0 0 1 B 1 0 0 0 1 0 B 2 1 1 0 B 3 0 0 1 0 0 B 4 0 0 0 B 5 0 1 1 B 6 0 0 1 1 0 VRC (Par)

Chequeo de Paridad Bidimensional: VRC/LRC Ejemplo: Combinación de cuatro errores LRC (Par) H O L A Bits 0 0 1 B 0 1 0 0 0 1 B 1 0 0 0 1 0 B 2 1 1 0 B 3 0 0 1 B 4 0 0 0 B 5 0 1 1 B 6 0 0 1 1 0 VRC (Par)

- Slides: 80