Rendszerarchitektra Sima Dezs 2007 tavaszi flv Ver 2

- Slides: 68

Rendszerarchitektúra Sima Dezső 2007 tavaszi félév (Ver. 2. 0) Sima Dezső, 2007

Felépítés • 1. Introduction to system architectures • 2. The evolution of the system architecture • 3. The evolution of Intel’s x 86 processor bus • 4. Bus innovations introduced in intel’s P 4 chipsets • 5. Chipsets of Intel’s P 4 family • 6. Bandwidth considerations • 7. Special aspects of the implementation

1. Introduction to system architectures

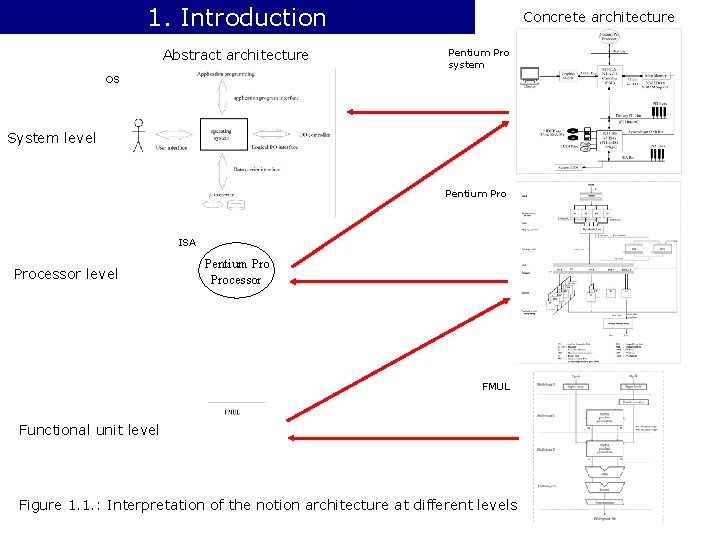

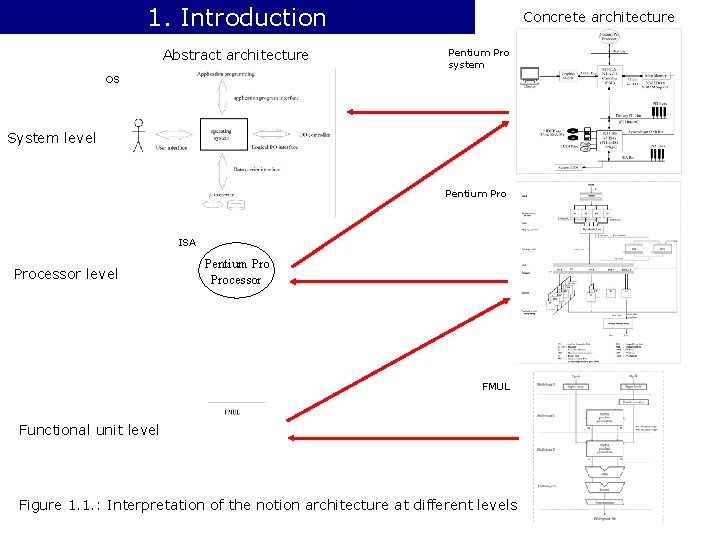

1. Introduction Abstract architecture Concrete architecture Pentium Pro system OS System level Pentium Pro ISA Processor level Pentium Processor FMUL Functional unit level Figure 1. 1. : Interpretation of the notion architecture at different levels

2. The evolution of the system architecture

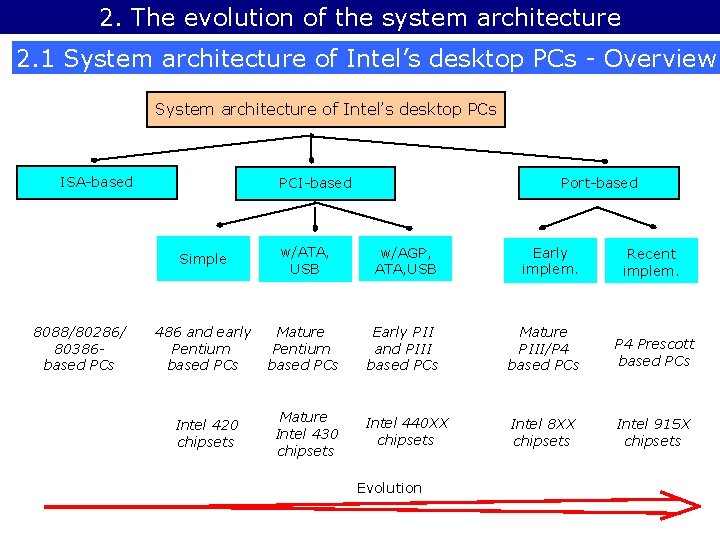

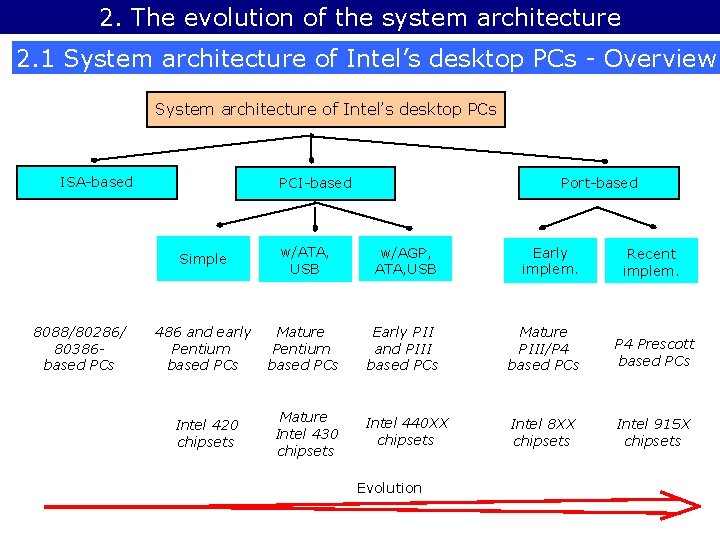

2. The evolution of the system architecture 2. 1 System architecture of Intel’s desktop PCs - Overview System architecture of Intel’s desktop PCs ISA-based 8088/80286/ 80386 based PCs Port-based PCI-based Simple w/ATA, USB w/AGP, ATA, USB Early implem. 486 and early Pentium based PCs Mature Pentium based PCs Early PII and PIII based PCs Mature PIII/P 4 based PCs P 4 Prescott based PCs Intel 420 chipsets Mature Intel 430 chipsets Intel 440 XX chipsets Intel 8 XX chipsets Intel 915 X chipsets Evolution Recent implem.

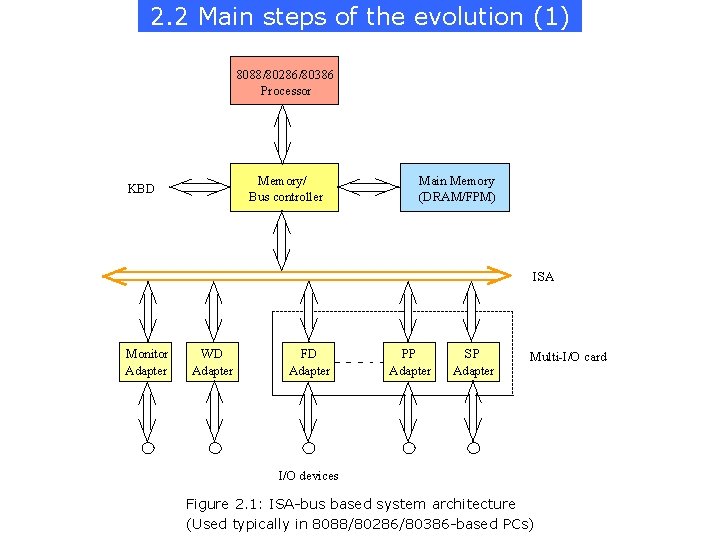

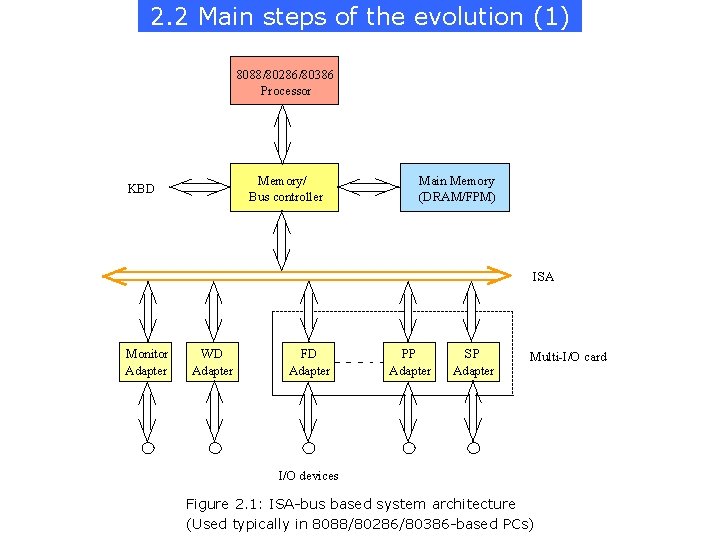

2. 2 Main steps of the evolution (1) 8088/80286/80386 Processor Memory/ Bus controller KBD Main Memory (DRAM/FPM) ISA Monitor Adapter WD Adapter FD Adapter PP Adapter SP Adapter Multi-I/O card I/O devices Figure 2. 1: ISA-bus based system architecture (Used typically in 8088/80286/80386 -based PCs)

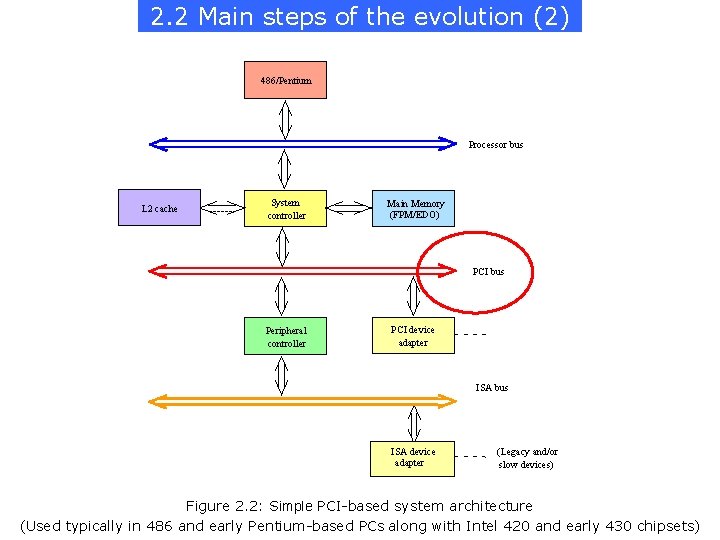

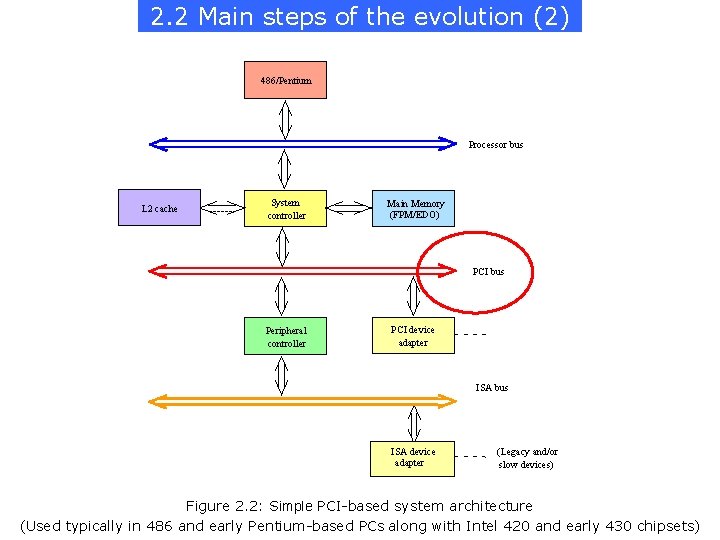

2. 2 Main steps of the evolution (2) 486/Pentium Processor bus L 2 cache System controller Main Memory (FPM/EDO) PCI bus Peripheral controller PCI device adapter ISA bus ISA device adapter (Legacy and/or slow devices) Figure 2. 2: Simple PCI-based system architecture (Used typically in 486 and early Pentium-based PCs along with Intel 420 and early 430 chipsets)

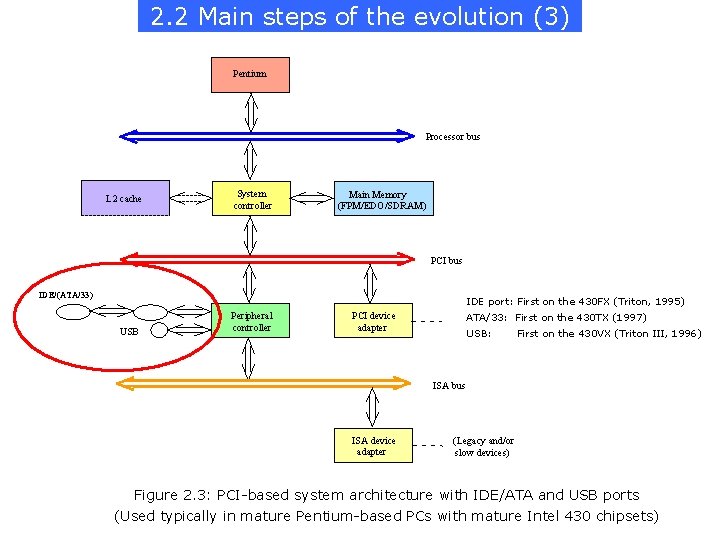

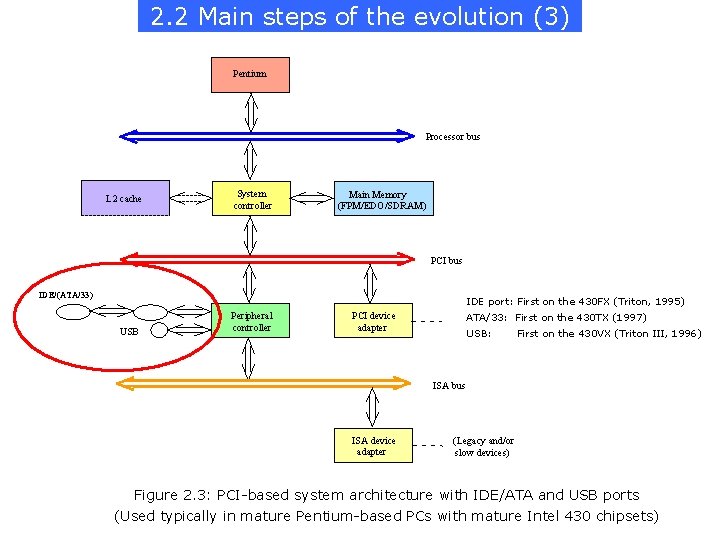

2. 2 Main steps of the evolution (3) Pentium Processor bus L 2 cache System controller Main Memory (FPM/EDO/SDRAM) PCI bus IDE/(ATA/33) IDE port: First on the 430 FX (Triton, 1995) USB Peripheral controller PCI device adapter ATA/33: First on the 430 TX (1997) USB: First on the 430 VX (Triton III, 1996) ISA bus ISA device adapter (Legacy and/or slow devices) Figure 2. 3: PCI-based system architecture with IDE/ATA and USB ports (Used typically in mature Pentium-based PCs with mature Intel 430 chipsets)

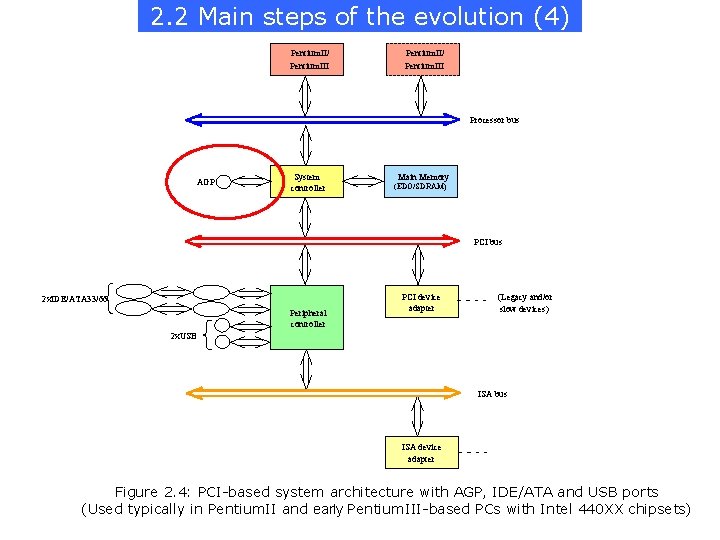

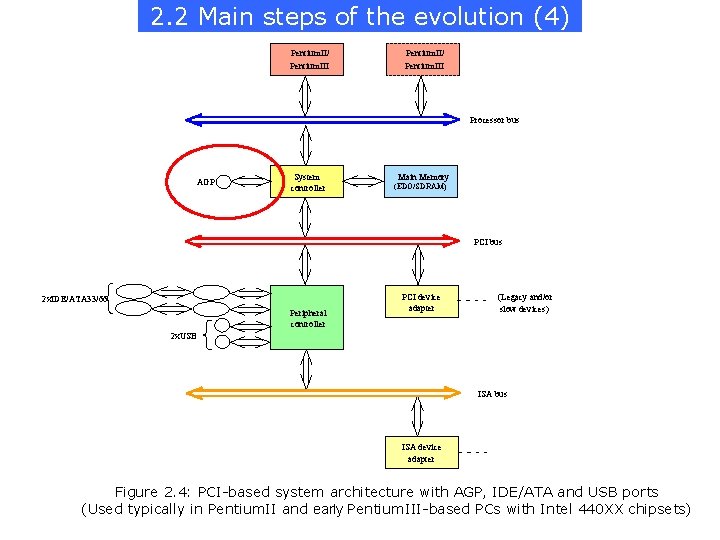

2. 2 Main steps of the evolution (4) Pentium. II/ Pentium. III Processor bus AGP System controller Main Memory (EDO/SDRAM) PCI bus 2 x. IDE/ATA 33/66 Peripheral controller PCI device adapter (Legacy and/or slow devices) 2 x. USB ISA bus ISA device adapter Figure 2. 4: PCI-based system architecture with AGP, IDE/ATA and USB ports (Used typically in Pentium. II and early Pentium. III-based PCs with Intel 440 XX chipsets)

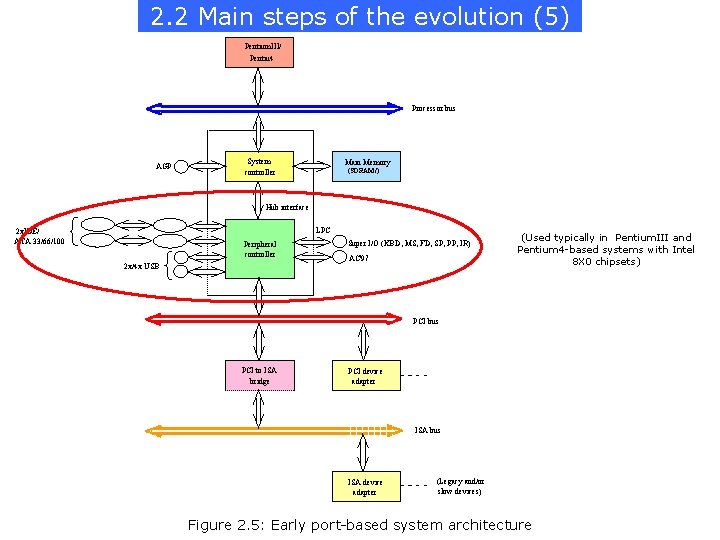

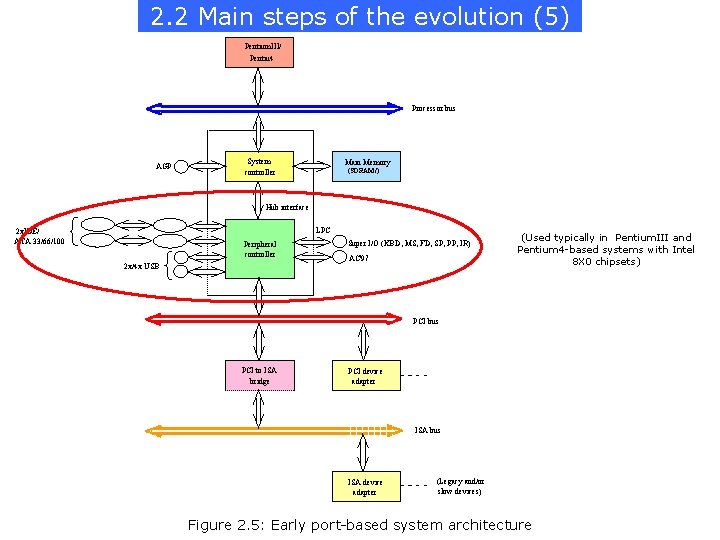

2. 2 Main steps of the evolution (5) Pentium. III/ Pentiu 4 Processor bus AGP System controller Main Memory (SDRAM/) Hub interface LPC 2 x. IDE/ ATA 33/66/100 Peripheral controller 2 x/4 x USB Super I/O (KBD, MS, FD, SP, PP, IR) AC'97 (Used typically in Pentium. III and Pentium 4 -based systems with Intel 8 X 0 chipsets) PCI bus PCI to ISA bridge PCI device adapter ISA bus ISA device adapter (Legacy and/or slow devices) Figure 2. 5: Early port-based system architecture

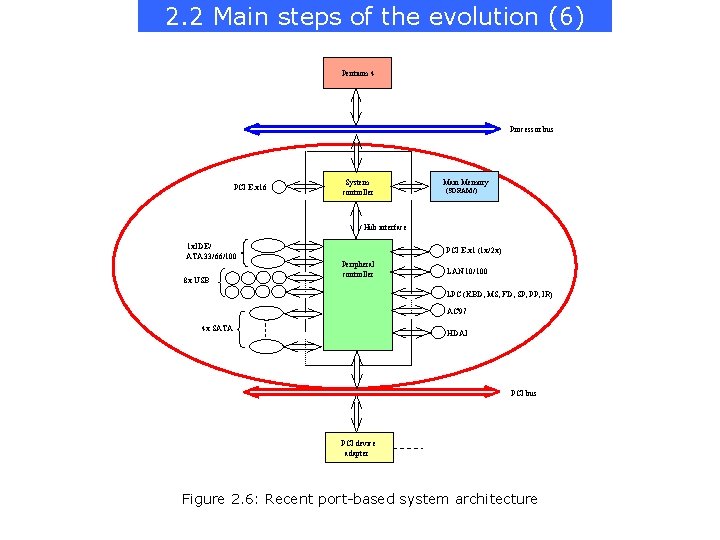

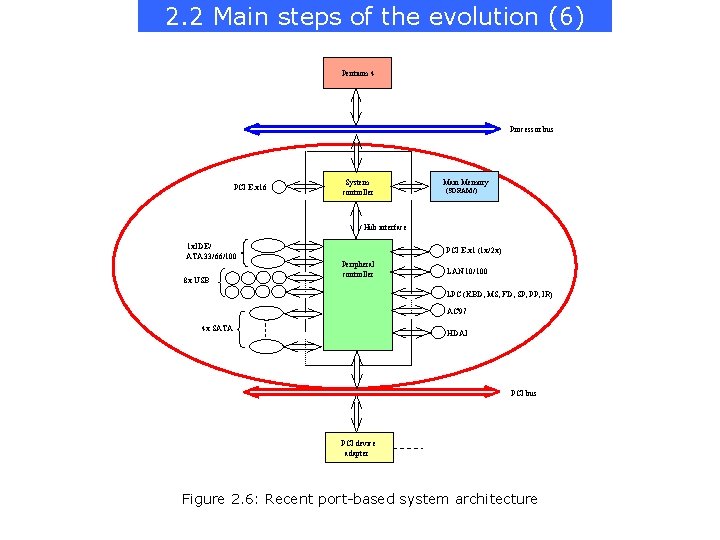

2. 2 Main steps of the evolution (6) Pentium 4 Processor bus PCI E. x 16 System controller Main Memory (SDRAM/) Hub interface 1 x. IDE/ ATA 33/66/100 8 x USB PCI E. x 1 (1 x/2 x) Peripheral controller LAN 10/100 LPC (KBD, MS, FD, SP, PP, IR) AC'97 4 x SATA HDAI PCI bus PCI device adapter Figure 2. 6: Recent port-based system architecture

3. The evolution of Intel’s x 86 processor bus

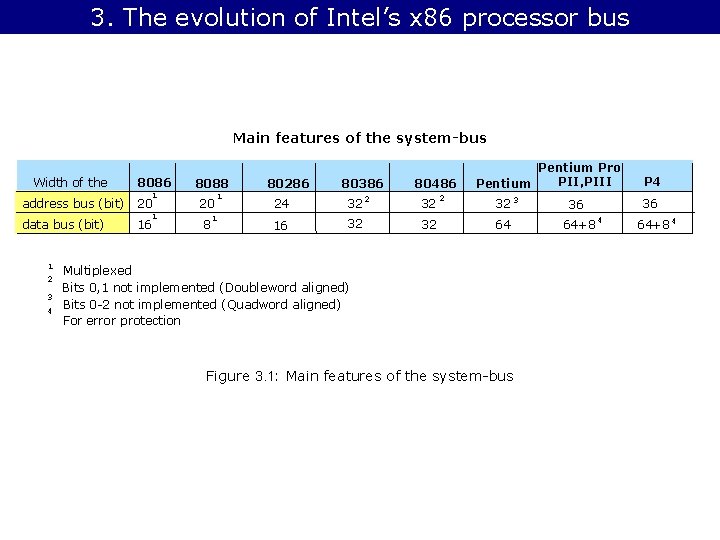

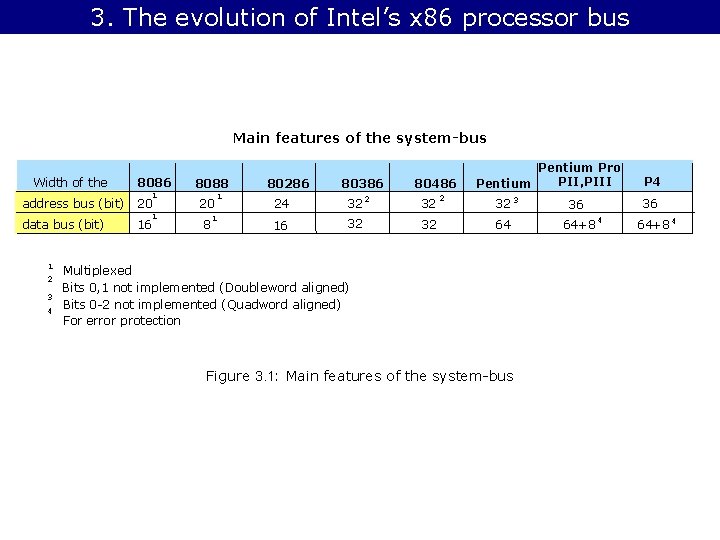

3. The evolution of Intel’s x 86 processor bus Main features of the system-bus Width of the address bus (bit) data bus (bit) 1 2 3 4 8086 1 20 16 1 8088 20 8 1 1 80286 24 16 80386 32 32 2 80486 32 32 2 Pentium Pro PII, PIII Pentium 32 3 64 Multiplexed Bits 0, 1 not implemented (Doubleword aligned) Bits 0 -2 not implemented (Quadword aligned) For error protection Figure 3. 1: Main features of the system-bus 36 36 64+8 P 4 4 64+8 4

4. Bus innovations introduced into Intel’s P 4 chipsets

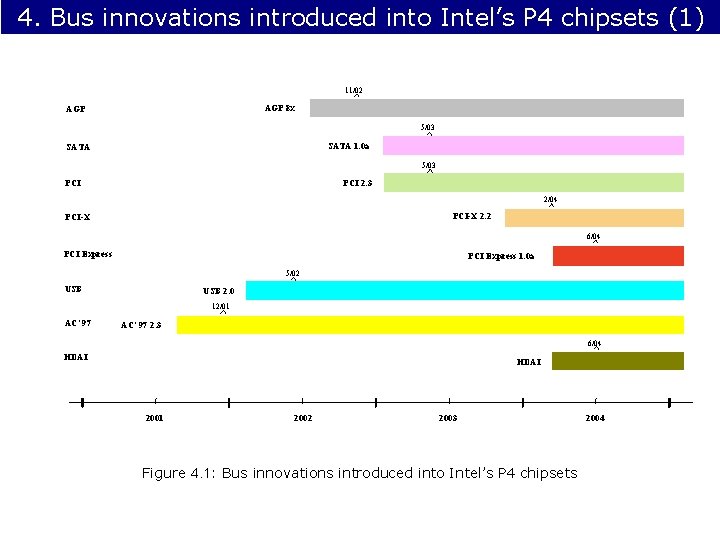

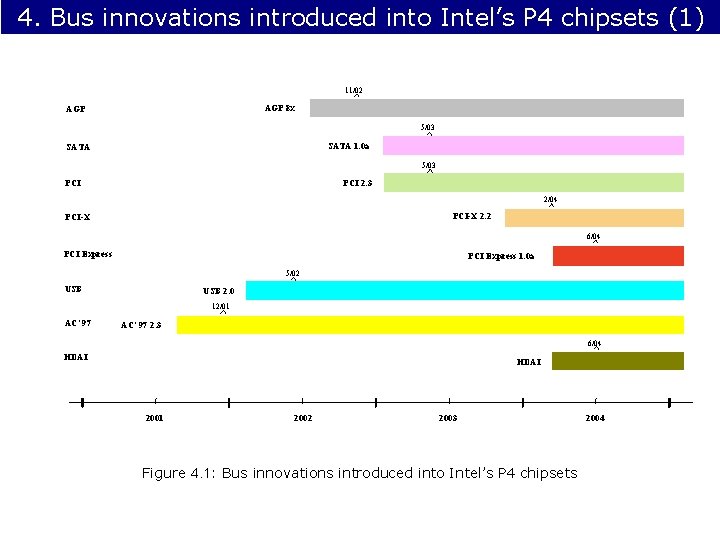

4. Bus innovations introduced into Intel’s P 4 chipsets (1) 11/02 AGP 8 x AGP 5/03 SATA 1. 0 a SATA 5/03 PCI 2/04 PCI-X 2. 2 PCI-X 6/04 PCI Express 1. 0 a 5/02 USB 2. 0 12/01 AC' 97 2. 3 6/04 HDAI 2001 2002 2003 Figure 4. 1: Bus innovations introduced into Intel’s P 4 chipsets 2004

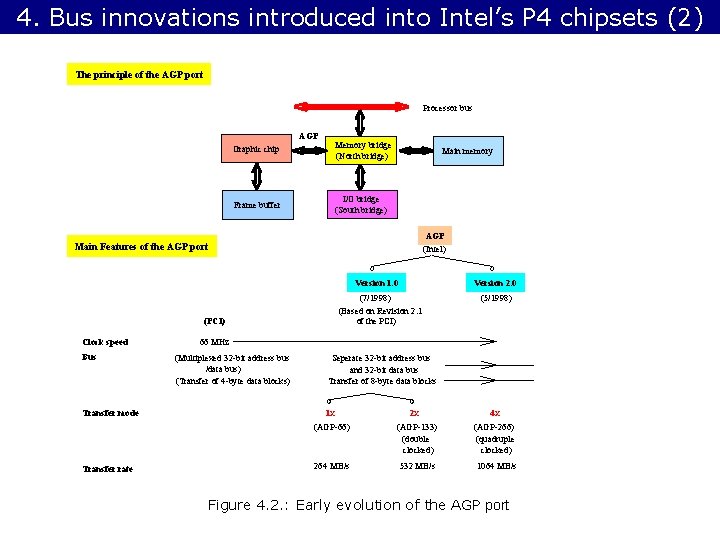

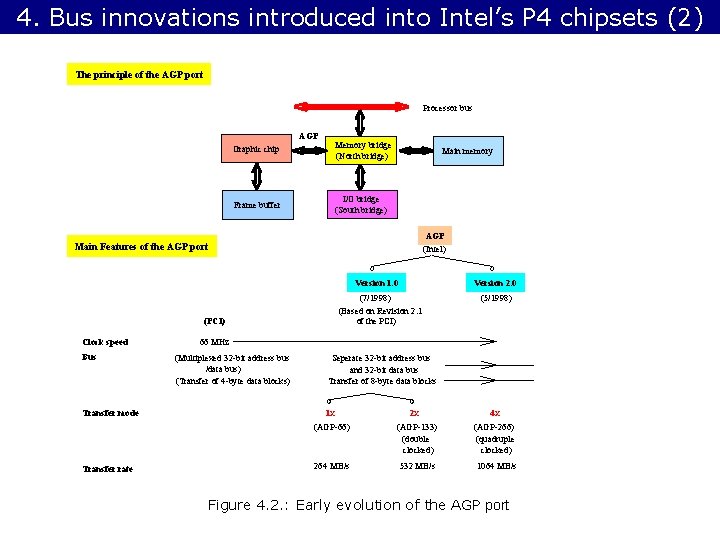

4. Bus innovations introduced into Intel’s P 4 chipsets (2) The principle of the AGP port Processor bus AGP Graphic chip Memory bridge (North bridge) Frame buffer I/O bridge (South bridge) Main memory AGP (Intel) Main Features of the AGP port Version 1. 0 (7/1998) (Based on Revision 2. 1 of the PCI) (PCI) Clock speed Bus Transfer mode Transfer rate Version 2. 0 (5/1998) 66 MHz (Multiplexed 32 -bit address bus /data bus) (Transfer of 4 -byte data blocks) Seperate 32 -bit address bus and 32 -bit data bus Transfer of 8 -byte data blocks 1 x 2 x 4 x (AGP-66) (AGP-133) (double clocked) (AGP-266) (quadruple clocked) 264 MB/s 532 MB/s 1064 MB/s Figure 4. 2. : Early evolution of the AGP port

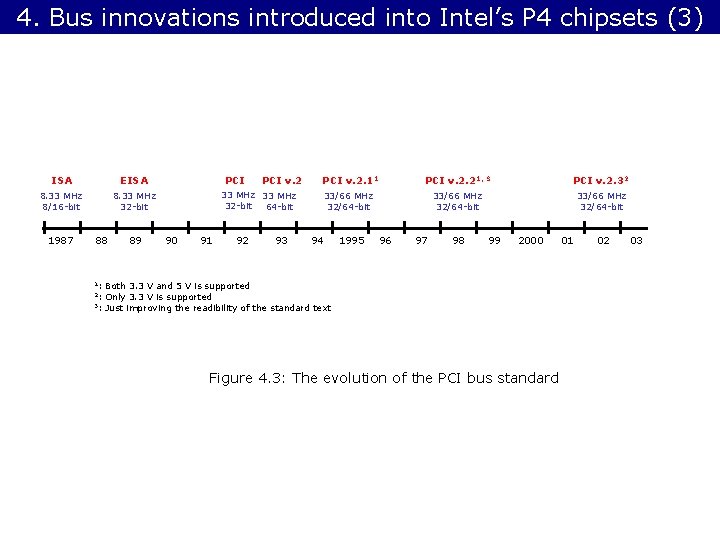

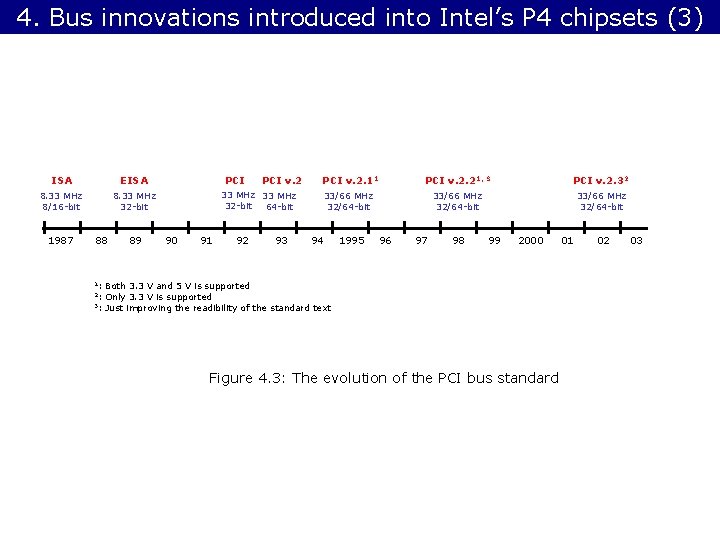

4. Bus innovations introduced into Intel’s P 4 chipsets (3) ISA EISA 8. 33 MHz 8/16 -bit 8. 33 MHz 32 -bit 1987 88 89 PCI v. 2. 11 PCI v. 2. 21, 3 PCI v. 2. 32 33/66 MHz 32/64 -bit 33 MHz 32 -bit 64 -bit 90 91 92 93 94 1995 96 97 98 99 2000 1: Both 3. 3 V and 5 V is supported Only 3. 3 V is supported 3: Just improving the readibility of the standard text 2: Figure 4. 3: The evolution of the PCI bus standard 01 02 03

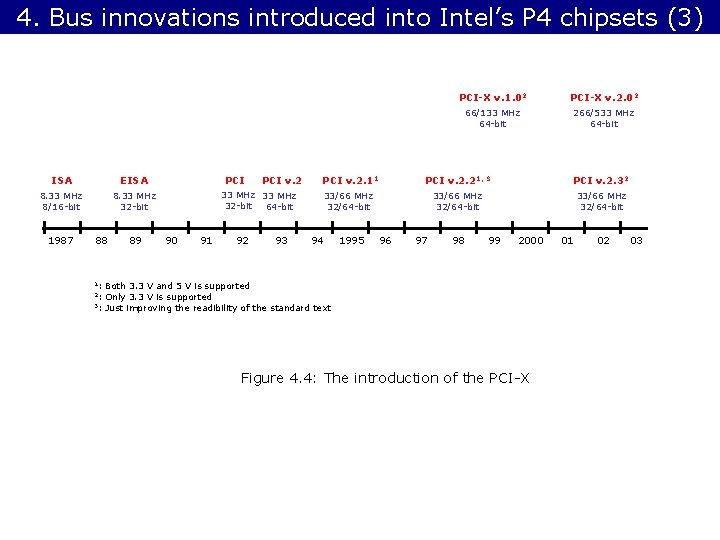

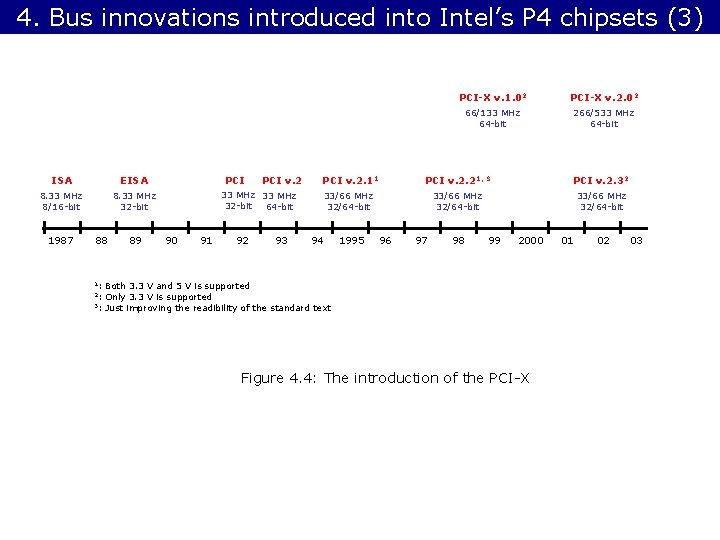

4. Bus innovations introduced into Intel’s P 4 chipsets (3) ISA EISA 8. 33 MHz 8/16 -bit 8. 33 MHz 32 -bit 1987 88 89 PCI v. 2 91 92 93 PCI-X v. 2. 02 66/133 MHz 64 -bit 266/533 MHz 64 -bit PCI v. 2. 11 PCI v. 2. 21, 3 PCI v. 2. 32 33/66 MHz 32/64 -bit 33 MHz 32 -bit 64 -bit 90 PCI-X v. 1. 02 94 1995 96 97 98 99 2000 1: Both 3. 3 V and 5 V is supported Only 3. 3 V is supported 3: Just improving the readibility of the standard text 2: Figure 4. 4: The introduction of the PCI-X 01 02 03

4. Bus innovations introduced into Intel’s P 4 chipsets (5) Figure 4. 5: Slot number limitations of the PCI-X bus Source: PCI Technology overview, Febr. 2003, http: //www. digi. com/pdf/prd_msc_pcitech. pdf

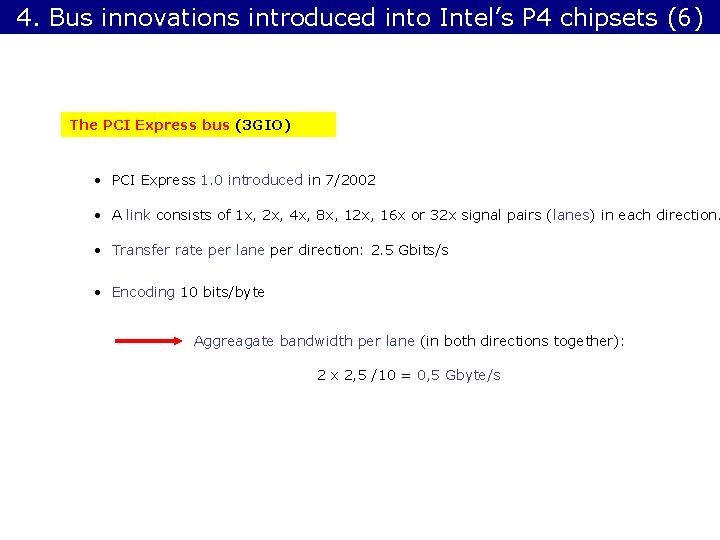

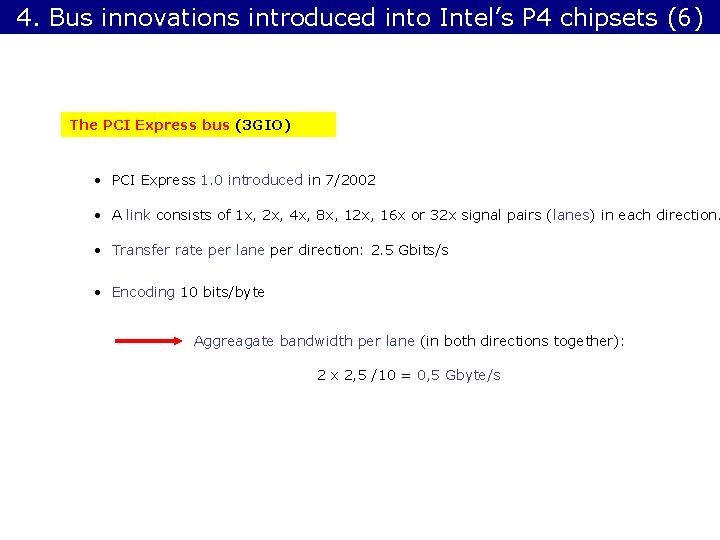

4. Bus innovations introduced into Intel’s P 4 chipsets (6) The PCI Express bus (3 GIO) • PCI Express 1. 0 introduced in 7/2002 • A link consists of 1 x, 2 x, 4 x, 8 x, 12 x, 16 x or 32 x signal pairs (lanes) in each direction. • Transfer rate per lane per direction: 2. 5 Gbits/s • Encoding 10 bits/byte Aggreagate bandwidth per lane (in both directions together): 2 x 2, 5 /10 = 0, 5 Gbyte/s

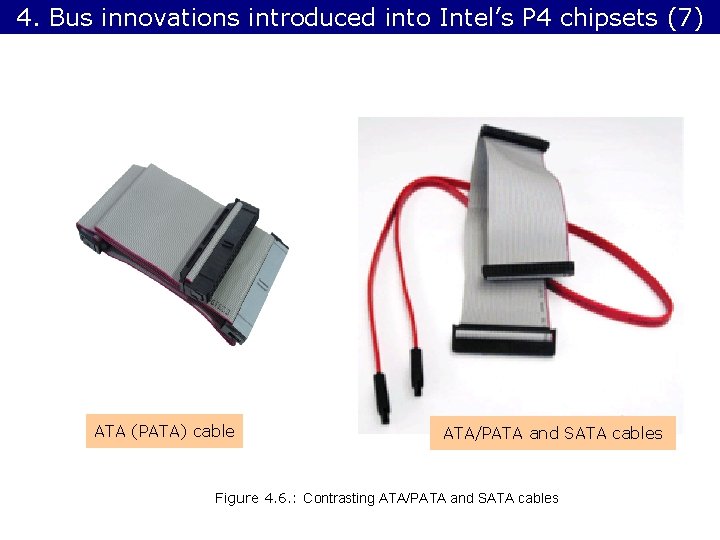

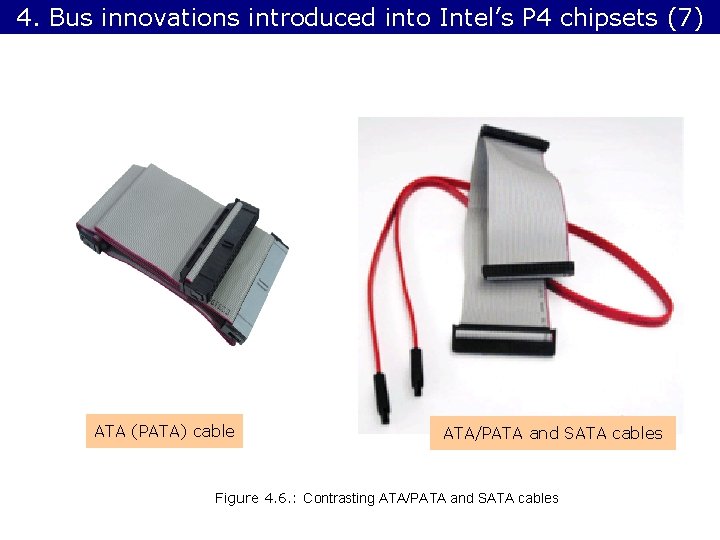

4. Bus innovations introduced into Intel’s P 4 chipsets (7) ATA (PATA) cable ATA/PATA and SATA cables Figure 4. 6. : Contrasting ATA/PATA and SATA cables

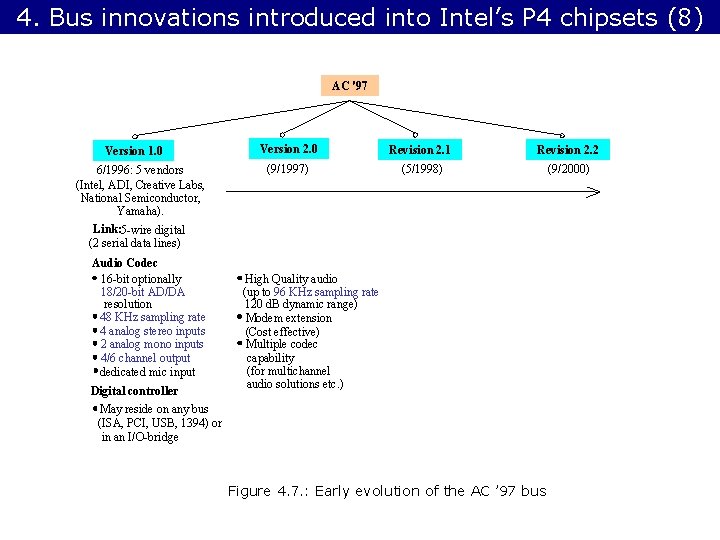

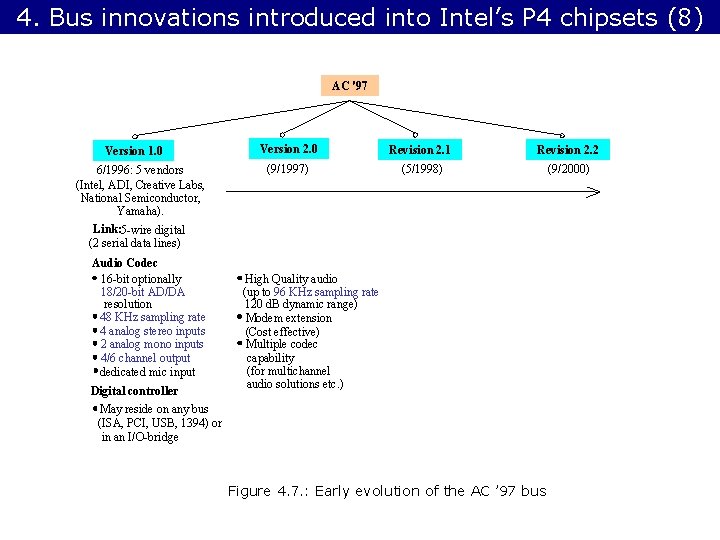

4. Bus innovations introduced into Intel’s P 4 chipsets (8) AC '97 Version 1. 0 6/1996: 5 vendors (Intel, ADI, Creative Labs, National Semiconductor, Yamaha). Version 2. 0 Revision 2. 1 Revision 2. 2 (9/1997) (5/1998) (9/2000) Link: 5 -wire digital (2 serial data lines) Audio Codec 16 -bit optionally 18/20 -bit AD/DA resolution 48 KHz sampling rate 4 analog stereo inputs 2 analog mono inputs 4/6 channel output dedicated mic input Digital controller High Quality audio (up to 96 KHz sampling rate 120 d. B dynamic range) Modem extension (Cost effective) Multiple codec capability (for multichannel audio solutions etc. ) May reside on any bus (ISA, PCI, USB, 1394) or in an I/O-bridge Figure 4. 7. : Early evolution of the AC ’ 97 bus

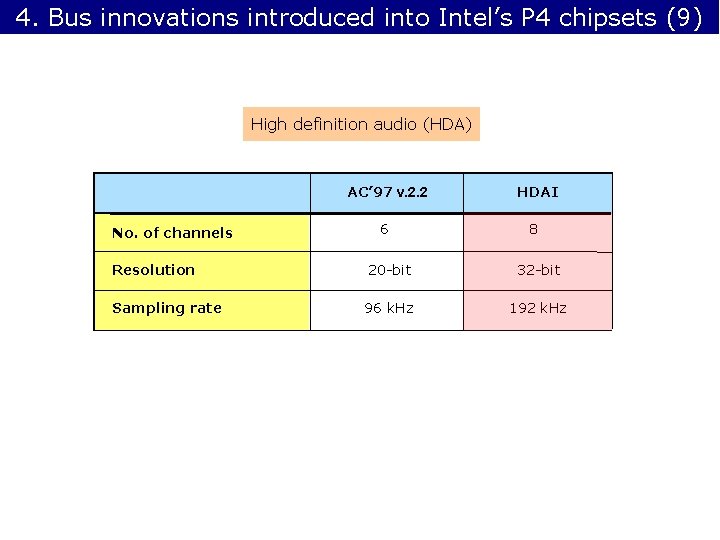

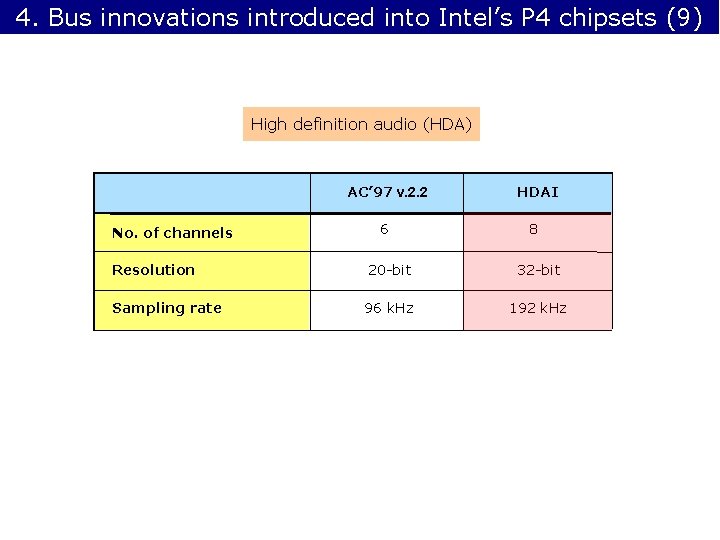

4. Bus innovations introduced into Intel’s P 4 chipsets (9) High definition audio (HDA) AC’ 97 v. 2. 2 No. of channels 6 HDAI 8 Resolution 20 -bit 32 -bit Sampling rate 96 k. Hz 192 k. Hz

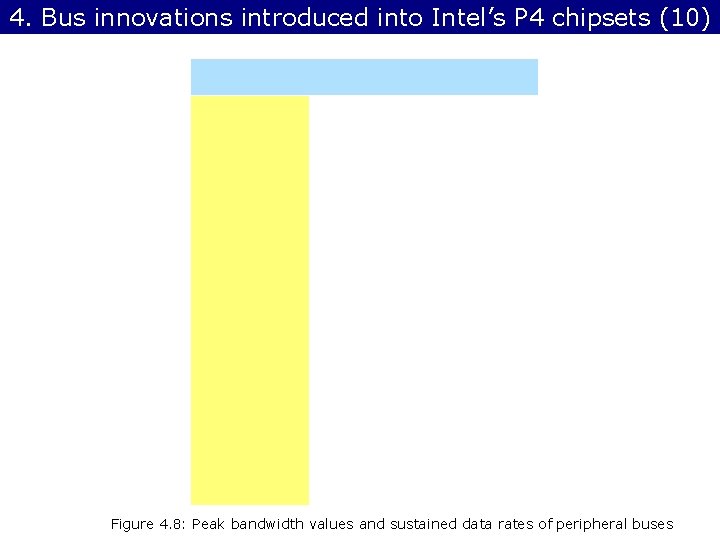

4. Bus innovations introduced into Intel’s P 4 chipsets (10) Figure 4. 8: Peak bandwidth values and sustained data rates of peripheral buses

5. Chipsets of Intel’s P 4 family

5. Chipsets of Intel’s P 4 family 5. 1 Overview of the P 4 family 5. 2 Desktop chipsets 5. 3 Overview of DP server and workstation chipsets 5. 4 DP server chipsets 5. 5 DP workstation chipsets

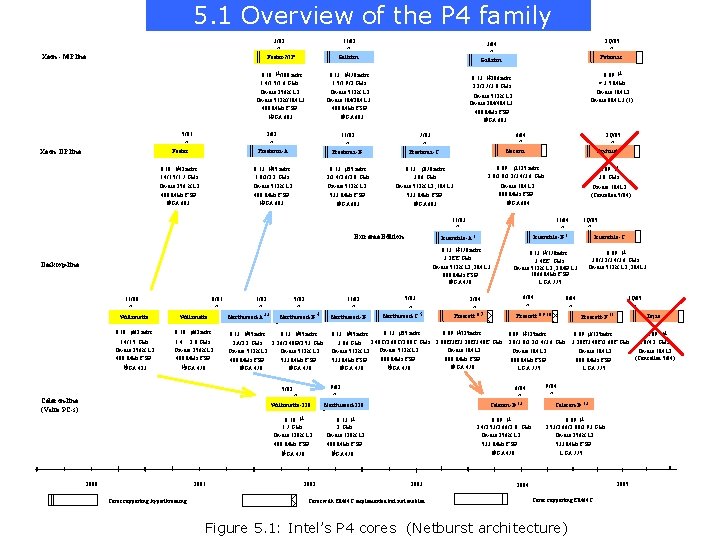

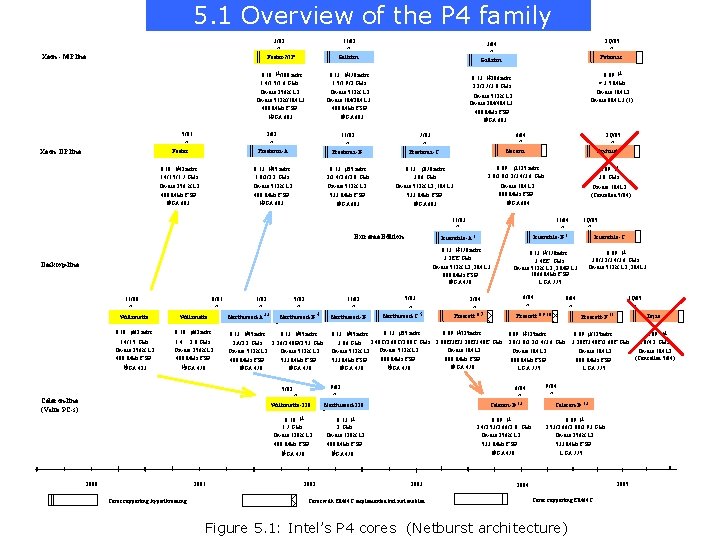

5. 1 Overview of the P 4 family Xeon - MP line 3/02 11/02 ^ ^ Foster-MP Gallatin 0. 18 m /108 mtrs 1. 4/1. 5/1. 6 GHz 0. 13 m/178 mtrs 1. 5/1. 9/2 GHz On-die 256 K L 2 On-die 512 K/1 M L 3 400 MHz FSB On-die 512 K L 2 On-die 1 M/2 M L 3 400 MHz FSB m. PGA 603 Xeon DP line 2 Q/05 3/04 ^ ^ Potomac Gallatin 0. 09 m > 3. 5 MHz 0. 13 m/286 mtrs 2. 2/2. 7/3. 0 GHz On-die 1 M L 2 On-die 8 M L 3 (? ) On-die 512 K L 2 On-die 2 M/4 M L 3 400 MHz FSB m. PGA 603 5/01 2/02 11/02 7/03 6/04 ^ ^ ^ 2 Q/05 ^ Foster Prestonia-A Prestonia-B Prestonia-C Nocona Jayhawk 0. 18 m/42 mtrs 1. 4/1. 5/1. 7 GHz 0. 13 m/55 mtrs 1. 8/2/2. 2 GHz 0. 09 m 3. 8 GHz On-die 512 K L 2 400 MHz FSB m. PGA 603 0. 13 m /178 mtrs 3. 06 GHz On-die 512 K L 2, 1 M L 3 533 MHz FSB m. PGA 603 0. 09 m / 125 mtrs 2. 8/3. 0/3. 2/3. 4/3. 6 GHz On-die 256 K L 2 400 MHz FSB m. PGA 603 0. 13 m/55 mtrs 2/2. 4/2. 6/2. 8 GHz On-die 512 K L 2 533 MHz FSB m. PGA 603 On-die 1 M L 2 800 MHz FSB m. PGA 604 On-die 1 M L 2 (Cancelled 5/04) 11/03 Extreme Edition Irwindale-B 1 0. 13 m/178 mtrs 3. 2 EE GHz On-die 512 K L 2, 2 M L 3 800 MHz FSB m. PGA 478 8/01 1/02 5/02 11/02 5/03 2/04 6/04 ^ ^ ^ ^ ^ Northwood-A 2, 3 Northwood-B 4 Northwood-B 0. 18 m/42 mtrs 0. 13 m/55 mtrs 1. 4/1. 5 GHz On-die 256 K L 2 400 MHz FSB 1. 4. . . 2. 0 GHz On-die 256 K L 2 400 MHz FSB 2 A/2. 2 GHz 2. 26/2. 40 B/2. 53 GHz On-die 512 K L 2 400 MHz FSB 533 MHz FSB m. PGA 478 0. 13 m/55 mtrs 0. 09 m/125 mtrs 2. 40 C/2. 60 C/2. 80 C GHz 2. 80 E/3 E/3. 20 E/3. 40 E GHz 2. 8/3. 0/3. 2/3. 4/3. 6 GHz 3. 06 GHz On-die 512 K L 2 On-die 1 M L 2 800 MHz FSB 533 MHz FSB 800 MHz FSB m m. PGA 478 LGA 775 m. PGA 423 m. PGA 478 5/02 Celeron-line (Value PC-s) 0. 18 m 1. 7 GHz On-die 128 K L 2 400 MHz FSB m. PGA 478 2001 2000 Cores supporting hyperthreading 2002 Northwood-128 Celeron-D 12 0. 13 m 2 GHz On-die 128 K L 2 400 MHz FSB 0. 09 m 2. 4/2. 53/2. 66/2. 8 GHz On-die 256 K L 2 533 MHz FSB m. PGA 478 2003 Cores with EM 64 T implemented but not enabled ^ Prescott-F 11 Celeron-D 13 0. 09 m 2. 53/2. 66/2. 80/2. 93 GHz On-die 256 K L 2 533 MHz FSB LGA 775 2004 Cores supporting EM 64 T Figure 5. 1: Intel’s P 4 cores (Netburst architecture) Tejas 0. 09 m/125 mtrs 4. 0/4. 2 GHz 3. 20 F/3. 40 F/3. 60 F GHz On-die 1 M L 2 (Cancelled 5/04) 800 MHz FSB LGA 775 ^ ^ m. PGA 478 3 Q/05 9/04 6/04 ^ Willamette-128 Prescott 0. 13 m/55 mtrs 9/02 ^ Prescott 6, 7 0. 09 m 3. 0/3. 2/3. 4/3. 6 GHz On-die 512 K L 2, 2 M L 3 8/04 8, 9, 10 Willamette Irwindale-C 0. 13 m/178 mtrs 3. 4 EE GHz On-die 512 K L 2, 2 MB L 3 1066 MHz FSB LGA 775 11/00 Northwood-C 5 ^ ^ Irwindale-A 1 Desktop-line 1 Q/05 11/04 ^

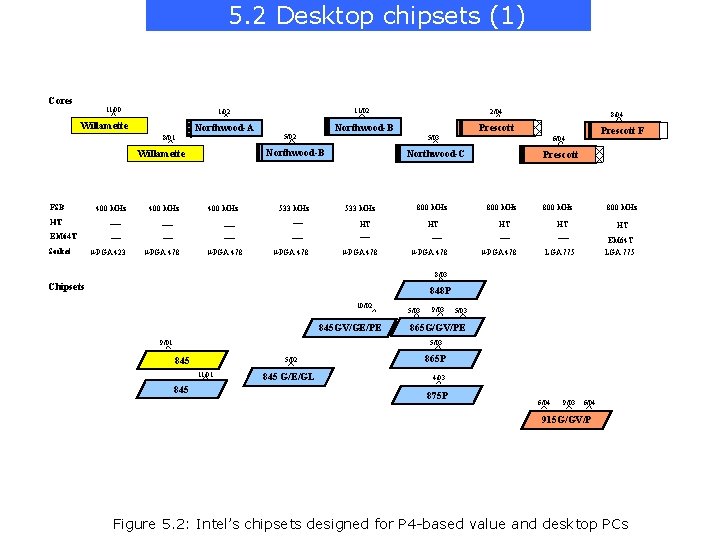

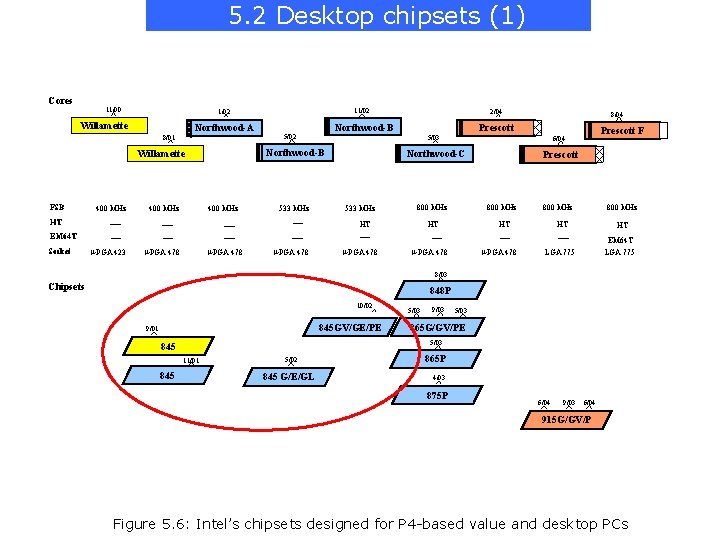

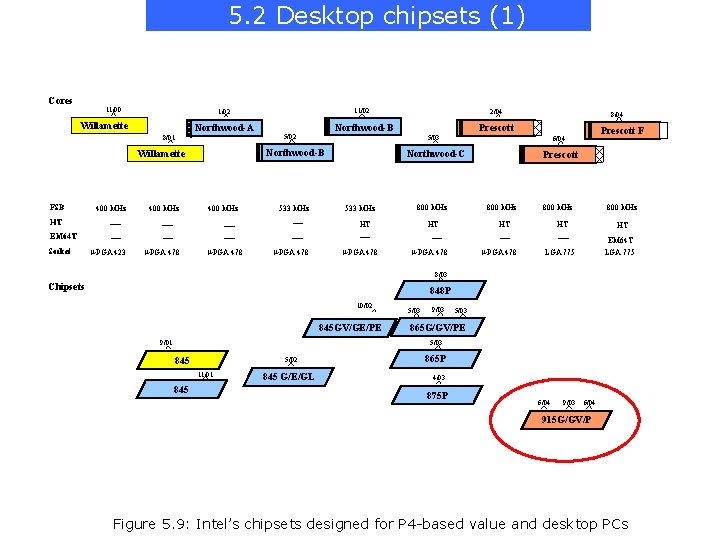

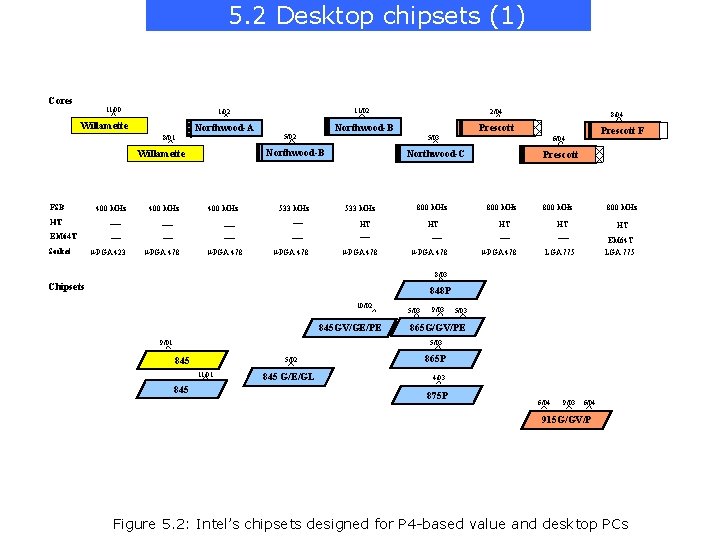

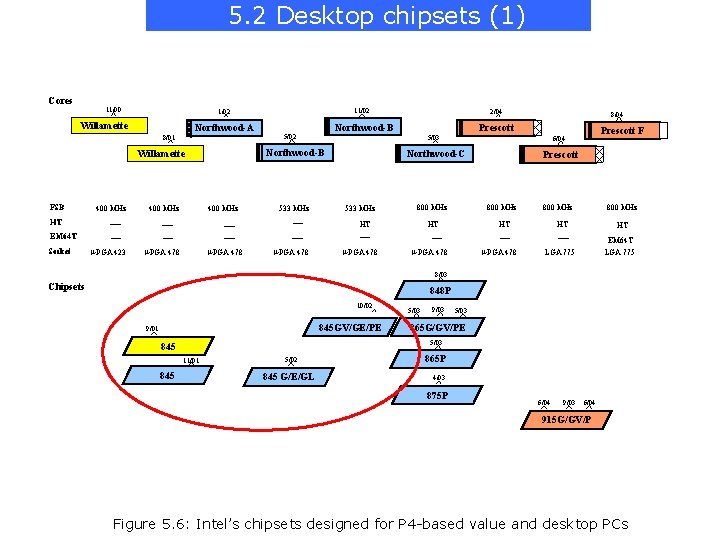

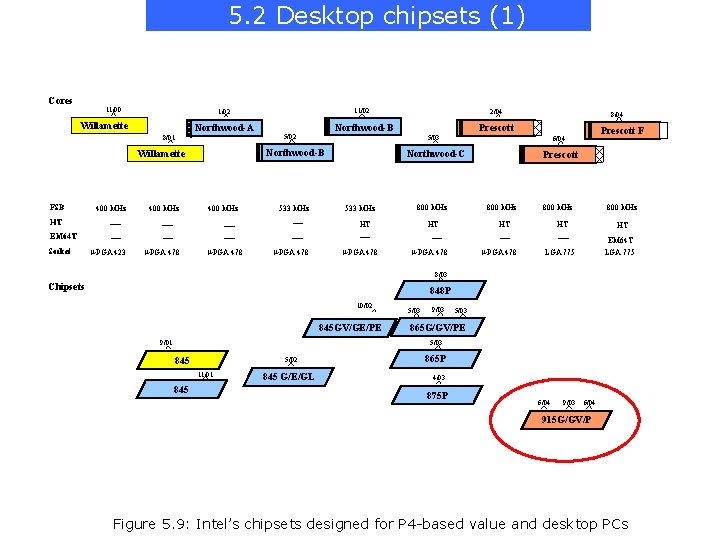

5. 2 Desktop chipsets (1) Cores 11/00 Willamette 8/01 Northwood-A 400 MHz 5/02 533 MHz HT 2/04 Northwood-B Prescott 800 MHz HT HT HT Prescott F 6/04 Northwood-C 533 MHz 8/04 Prescott 5/03 Northwood-B Willamette FSB 11/02 800 MHz HT HT EM 64 T Socket EM 64 T m PGA 423 m PGA 478 m PGA 478 LGA 775 8/03 Chipsets 848 P 10/02 845 GV/GE/PE 5/03 9/03 5/03 865 G/GV/PE 5/03 9/01 845 5/02 11/01 845 G/E/GL 865 P 4/03 875 P 6/04 9/03 6/04 915 G/GV/P Figure 5. 2: Intel’s chipsets designed for P 4 -based value and desktop PCs

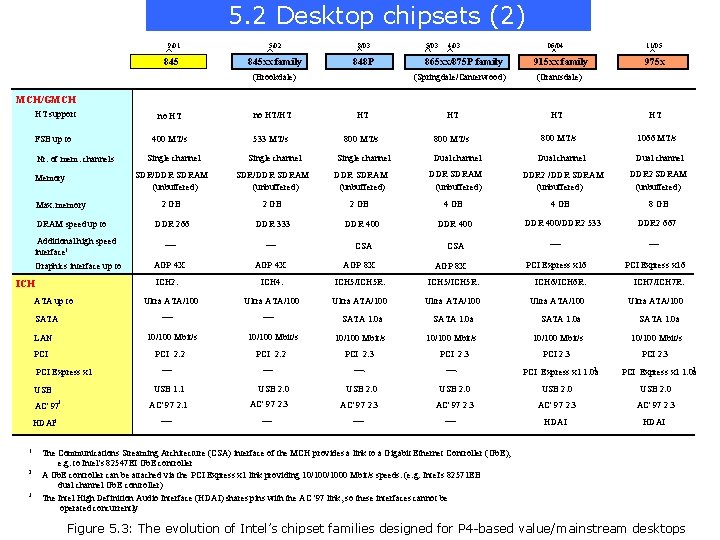

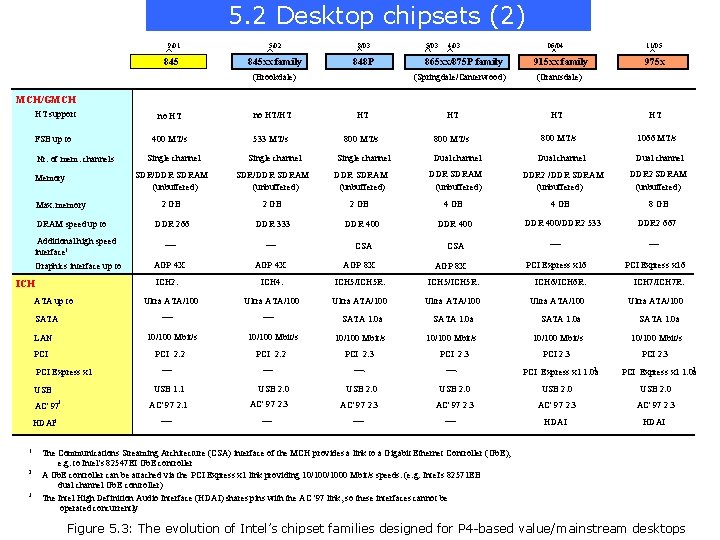

5. 2 Desktop chipsets (2) 9/01 845 5/02 8/03 845 xx family 848 P (Brookdale) 5/03 4/03 865 xx/875 P family (Springdale/Canterwood) 06/04 11/05 915 xx family 975 x (Grantsdale) MCH/GMCH HT support no HT/HT HT HT FSB up to 400 MT/s 533 MT/s 800 MT/s 1066 MT/s Nr. of mem. channels Memory Max. memory DRAM speed up to Single channel Dual channel SDR/DDR SDRAM (unbuffered) DDR 2 /DDR SDRAM (unbuffered) DDR 2 SDRAM (unbuffered) 2 GB 4 GB 8 GB DDR 266 DDR 333 DDR 400/DDR 2 533 DDR 2 667 CSA AGP 8 X Single channel SDR/DDR SDRAM (unbuffered) Additional high speed interface 1 Graphics interface up to ICH ATA up to PCI Express x 16 ICH 5/ICH 5 R: ICH 6/ICH 6 R: ICH 7/ICH 7 R: Ultra ATA/100 SATA 1. 0 a 10/100 Mbit/s AGP 4 X AGP 8 X ICH 2: ICH 4: ICH 5/ICH 5 R: Ultra ATA/100 SATA LAN 10/100 Mbit/s PCI 2. 2 PCI 2. 3 AC' 97 2. 1 2 3 10/100 Mbit/s PCI 2. 3 2 PCI Express x 1 1. 0 a USB 2. 0 AC' 97 2. 3 HDAI 3 1 10/100 Mbit/s PCI Express x 1 1. 0 a USB 1. 1 3 SATA 1. 0 a 2 PCI Express x 1 USB SATA 1. 0 a The Communications Streaming Architecture (CSA) interface of the MCH provides a link to a Gigabit Ethernet Controller (Gb. E), e. g. to Intel's 82547 EI Gb. E controller A Gb. E controller can be attached via the PCI Express x 1 link providing 10/1000 Mbit/s speeds. (e. g. Intel's 82571 EB dual channel Gb. E controller) The Intel High Definition Audio Interface (HDAI) shares pins with the AC '97 link, so these interfaces cannot be operated concurrently Figure 5. 3: The evolution of Intel’s chipset families designed for P 4 -based value/mainstream desktops

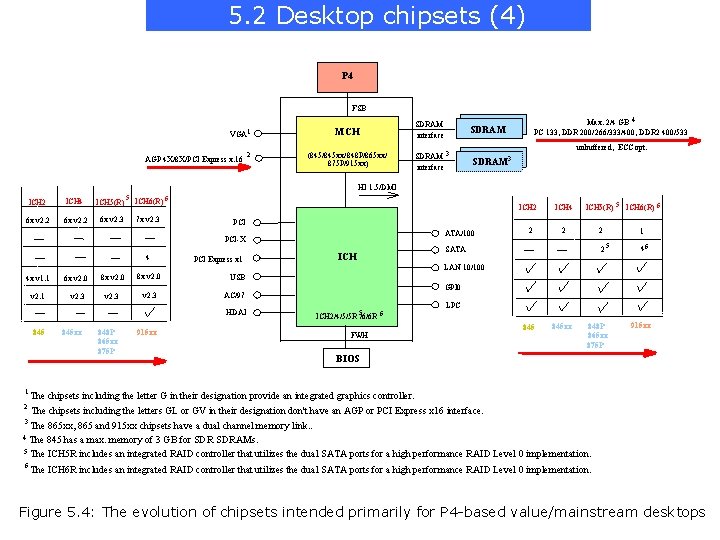

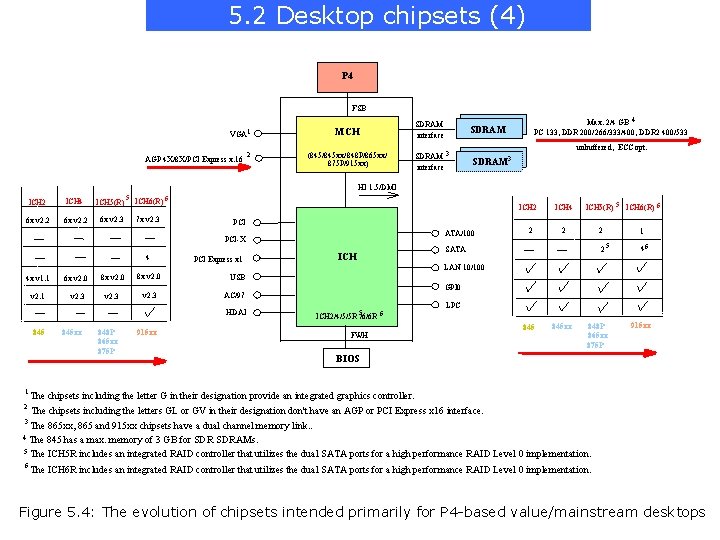

5. 2 Desktop chipsets (4) P 4 FSB VGA AGP 4 X/8 X/PCI Express x. 16 1 MCH SDRAM interface 2 (845/845 xx/848 P/865 xx/ 875 P/915 xx) SDRAM 3 interface Max. 2/4 GB 4 PC 133, DDR 200/266/333/400, DDR 2 400/533 SDRAM unbuffered, ECC opt. 3 SDRAM HI 1. 5/DMI ICH 2 ICH 4 ICH 5(R) 6 x v 2. 2 6 x v 2. 3 5 ICH 6(R) 6 7 x v 2. 3 ICH 2 PCI ATA/100 PCI-X 4 4 x v 1. 1 6 x v 2. 0 8 x v 2. 0 v 2. 1 v 2. 3 PCI Express x 1 1 2 845 xx 848 P 865 xx 875 P 915 xx ICH 5(R) 5 ICH 6(R) 6 2 2 2 SATA 1 5 46 LAN 10/100 USB GPI 0 AC/97 HDAI 845 ICH 2 ICH 4 ICH 2/4/5/5 R 5/6/6 R 6 LPC FWH 845 xx 848 P 865 xx 875 P 915 xx BIOS The chipsets including the letter G in their designation provide an integrated graphics controller. The chipsets including the letters GL or GV in their designation don't have an AGP or PCI Express x 16 interface. 3 The 865 xx, 865 and 915 xx chipsets have a dual channel memory link. . The 845 has a max. memory of 3 GB for SDRAMs. 5 The ICH 5 R includes an integrated RAID controller that utilizes the dual SATA ports for a high performance RAID Level 0 implementation. 4 6 The ICH 6 R includes an integrated RAID controller that utilizes the dual SATA ports for a high performance RAID Level 0 implementation. Figure 5. 4: The evolution of chipsets intended primarily for P 4 -based value/mainstream desktops

5. 2 Desktop chipsets (3) Figure 5. 5: Main features of Intel’s I/O Control Hubs (ICH) used in P 4 -based chipsets

5. 2 Desktop chipsets (1) Cores 11/00 Willamette Northwood-A 8/01 400 MHz 5/02 533 MHz HT 2/04 Northwood-B Prescott 800 MHz HT HT HT Prescott F 6/04 Northwood-C 533 MHz 8/04 Prescott 5/03 Northwood-B Willamette FSB 11/02 800 MHz HT HT EM 64 T Socket EM 64 T m PGA 423 m PGA 478 m PGA 478 LGA 775 8/03 Chipsets 848 P 10/02 845 GV/GE/PE 9/01 9/03 5/03 865 G/GV/PE 5/03 845 11/01 845 5/03 5/02 845 G/E/GL 865 P 4/03 875 P 6/04 9/03 6/04 915 G/GV/P Figure 5. 6: Intel’s chipsets designed for P 4 -based value and desktop PCs

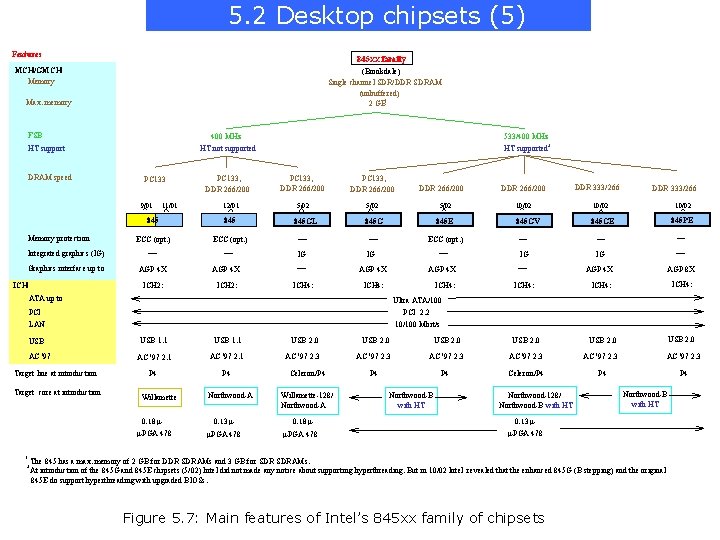

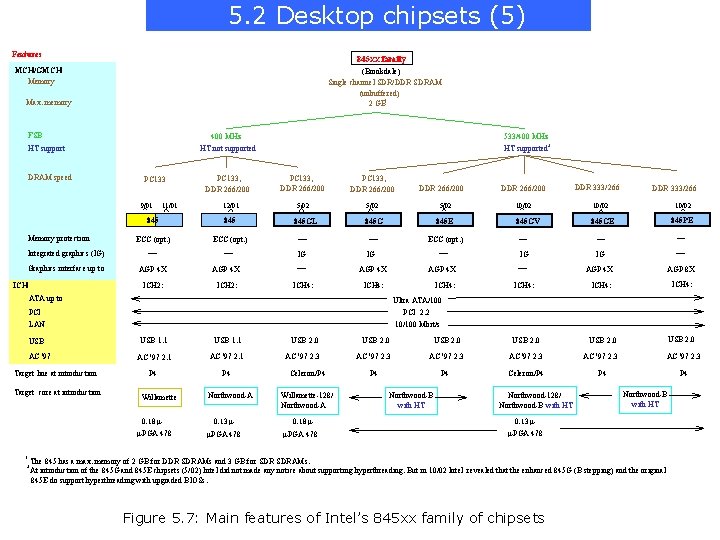

5. 2 Desktop chipsets (5) Features 845 xx family MCH/GMCH Memory (Brookdale) Single channel SDR/DDR SDRAM (unbuffered) 1 2 GB Max. memory FSB HT support DRAM speed 533/400 MHz HT supported PC 133, DDR 266/200 12/01 5/02 845 845 GL 845 G 845 E ECC (opt. ) 11/01 PC 133, DDR 266/200 Integrated graphics (IG) Graphics interface up to ICH 2 PC 133, DDR 266/200 PC 133 9/01 Memory protection 400 MHz HT not supported AGP 4 X ICH 2: IG ICH 4: Ultra ATA/100 PCI 2. 2 10/100 Mbit/s LAN Target line at introduction Target core at introduction 2 DDR 333/266 10/02 845 GE 845 PE IG AGP 4 X AGP 8 X ICH 4: USB 1. 1 USB 2. 0 AC '97 2. 1 AC '97 2. 3 P 4 P 4 Celeron/P 4 P 4 Willamette 0. 18 m m PGA 478 1 845 GV AGP 4 X PCI AC '97 10/02 IG AGP 4 X ATA up to USB DDR 266/200 ECC (opt. ) IG AGP 4 X DDR 266/200 Northwood-A Celeron/P 4 Willamette-128/ Northwood-A 0. 13 m 0. 18 m m PGA 478 Northwood-B with HT Northwood-128/ Northwood-B with HT 0. 13 m m PGA 478 The 845 has a max. memory of 2 GB for DDR SDRAMs and 3 GB for SDRAMs. At introduction of the 845 G and 845 E chipsets (5/02) Intel did not made any notice about supporting hyperthreading. But in 10/02 Intel revealed that the enhanced 845 G (B stepping) and the original 845 E do support hyperthreading with upgraded BIOSs. Figure 5. 7: Main features of Intel’s 845 xx family of chipsets

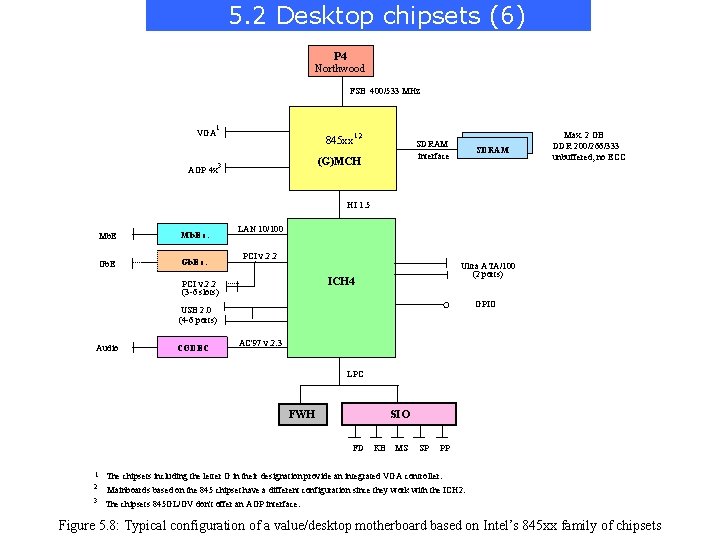

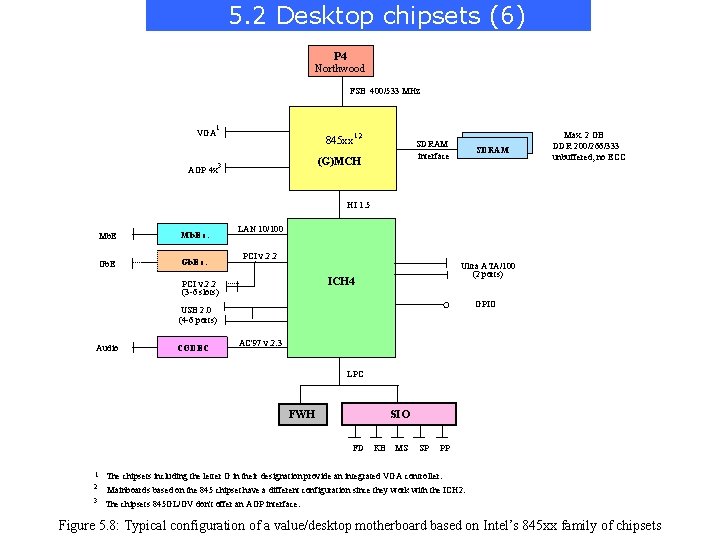

5. 2 Desktop chipsets (6) P 4 Northwood FSB 400/533 MHz 1 VGA AGP 4 x 845 xx 1, 2 SDRAM interface (G)MCH 3 SDRAM Max. 2 GB DDR 200/266/333 unbuffered, no ECC HI 1. 5 Mb. E c. Gb. E c. LAN 10/100 PCI v. 2. 2 Ultra ATA/100 (2 ports) ICH 4 PCI v. 2. 2 (3 -6 slots) GPIO USB 2. 0 (4 -6 ports) Audio CODEC AC'97 v. 2. 3 LPC FWH SIO FD 1 2 3 KB MS SP PP The chipsets including the letter G in their designation provide an integrated VGA controller. Mainboards based on the 845 chipset have a different configuration since they work with the ICH 2. The chipsets 845 GL/GV don't offer an AGP interface. Figure 5. 8: Typical configuration of a value/desktop motherboard based on Intel’s 845 xx family of chipsets

5. 2 Desktop chipsets (1) Cores 11/00 Willamette 8/01 Northwood-A 400 MHz 5/02 533 MHz HT 2/04 Northwood-B Prescott 800 MHz HT HT HT Prescott F 6/04 Northwood-C 533 MHz 8/04 Prescott 5/03 Northwood-B Willamette FSB 11/02 800 MHz HT HT EM 64 T Socket EM 64 T m PGA 423 m PGA 478 m PGA 478 LGA 775 8/03 Chipsets 848 P 10/02 845 GV/GE/PE 5/03 9/03 5/03 865 G/GV/PE 5/03 9/01 845 5/02 11/01 845 G/E/GL 865 P 4/03 875 P 6/04 9/03 6/04 915 G/GV/P Figure 5. 9: Intel’s chipsets designed for P 4 -based value and desktop PCs

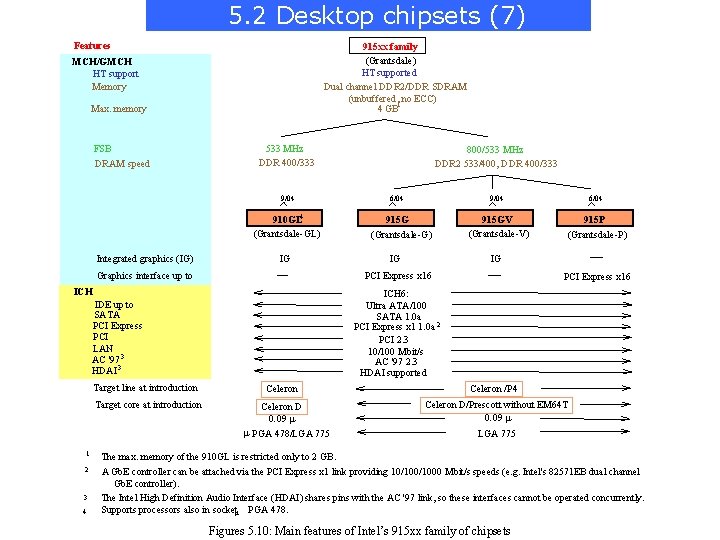

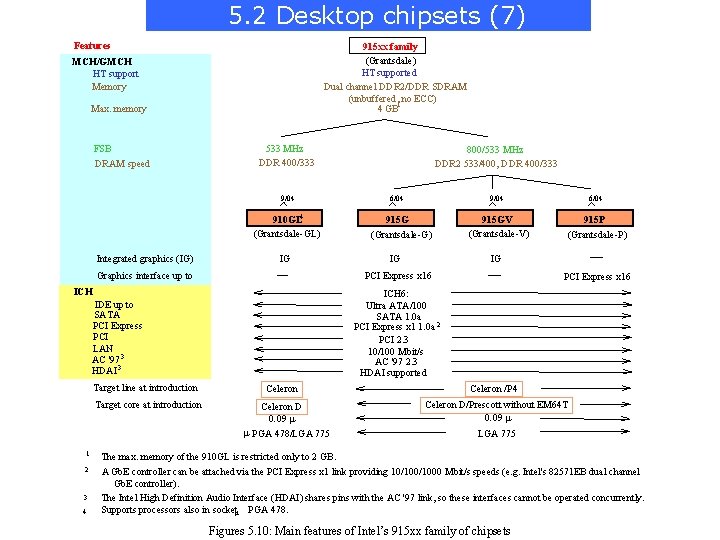

5. 2 Desktop chipsets (7) Features 915 xx family (Grantsdale) HT supported Dual channel DDR 2/DDR SDRAM (unbuffered, no ECC) 1 4 GB MCH/GMCH HT support Memory Max. memory FSB DRAM speed 533 MHz DDR 400/333 9/04 910 GL 4 (Grantsdale-GL) Integrated graphics (IG) IG Graphics interface up to 1 2 3 4 915 G (Grantsdale-G) IG 9/04 6/04 915 GV (Grantsdale-V) 915 P (Grantsdale-P) IG PCI Express x 16 ICH 6: Ultra ATA/100 SATA 1. 0 a PCI Express x 1 1. 0 a 2 PCI 2. 3 10/100 Mbit/s AC '97 2. 3 HDAI supported IDE up to SATA PCI Express PCI LAN AC '97 3 HDAI 3 Target core at introduction 6/04 PCI Express x 16 ICH Target line at introduction 800/533 MHz DDR 2 533/400, DDR 400/333 Celeron D 0. 09 m m PGA 478/LGA 775 Celeron /P 4 Celeron D/Prescott without EM 64 T 0. 09 m LGA 775 The max. memory of the 910 GL is restricted only to 2 GB. A Gb. E controller can be attached via the PCI Express x 1 link providing 10/1000 Mbit/s speeds (e. g. Intel's 82571 EB dual channel Gb. E controller). The Intel High Definition Audio Interface (HDAI) shares pins with the AC '97 link, so these interfaces cannot be operated concurrently. Supports processors also in socketm PGA 478. Figures 5. 10: Main features of Intel’s 915 xx family of chipsets

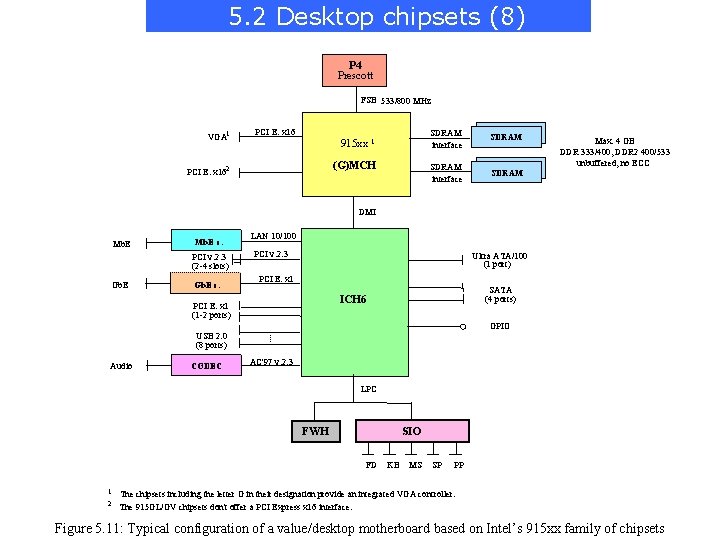

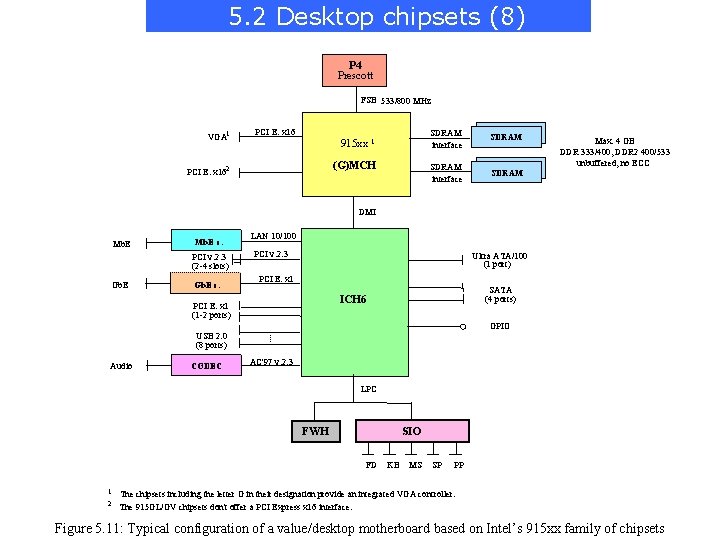

5. 2 Desktop chipsets (8) P 4 Prescott FSB 533/800 MHz VGA 1 PCI E. x 16 915 xx 1 (G)MCH PCI E. x 162 SDRAM interface SDRAM Max. 4 GB DDR 333/400, DDR 2 400/533 unbuffered, no ECC DMI Mb. E c. PCI v. 2. 3 (2 -4 slots) Gb. E c. LAN 10/100 PCI v. 2. 3 Ultra ATA/100 (1 port) PCI E. x 1 SATA (4 ports) ICH 6 PCI E. x 1 (1 -2 ports) GPIO USB 2. 0 (8 ports) Audio CODEC AC'97 v. 2. 3 LPC FWH SIO FD KB MS SP PP 1 The chipsets including the letter G in their designation provide an integrated VGA controller. 2 The 915 GL/GV chipsets don't offer a PCI Express x 16 interface. Figure 5. 11: Typical configuration of a value/desktop motherboard based on Intel’s 915 xx family of chipsets

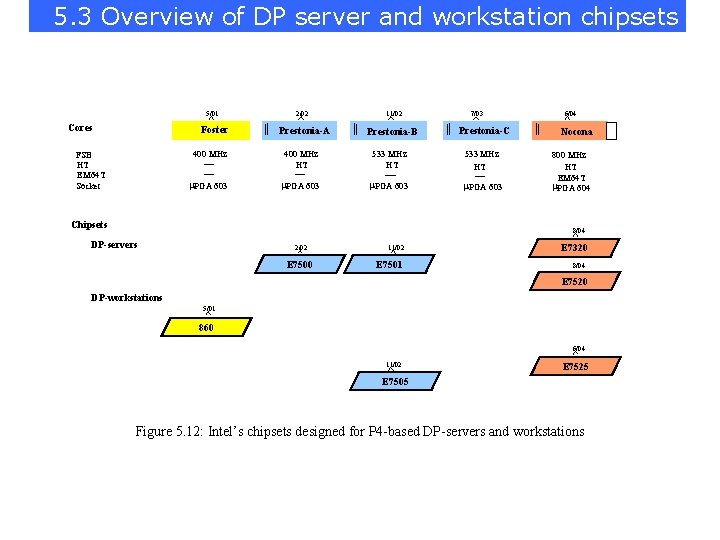

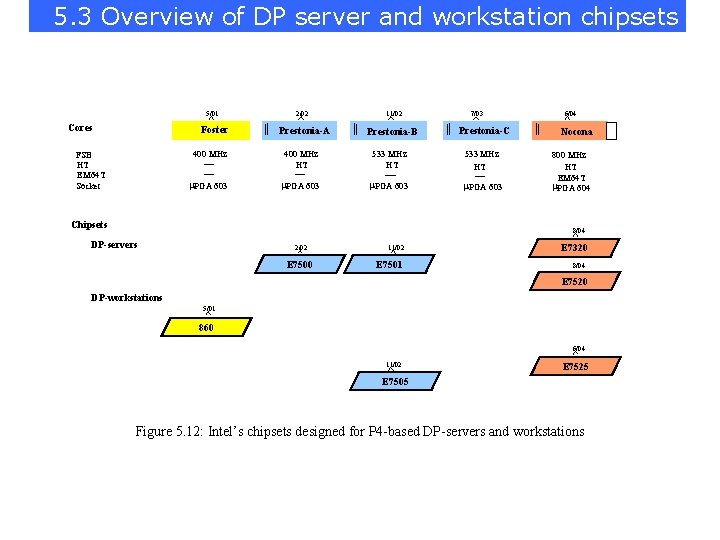

5. 3 Overview of DP server and workstation chipsets 5/01 Cores Foster FSB HT EM 64 T Socket 2/02 Prestonia-A 11/02 Prestonia-B 7/03 Prestonia-C 400 MHz HT 533 MHz HT m PGA 603 Chipsets 6/04 Nocona 800 MHz HT EM 64 T m PGA 604 8/04 DP-servers 2/02 E 7500 11/02 E 7501 E 7320 8/04 E 7520 DP-workstations 5/01 860 6/04 11/02 E 7525 E 7505 Figure 5. 12: Intel’s chipsets designed for P 4 -based DP-servers and workstations

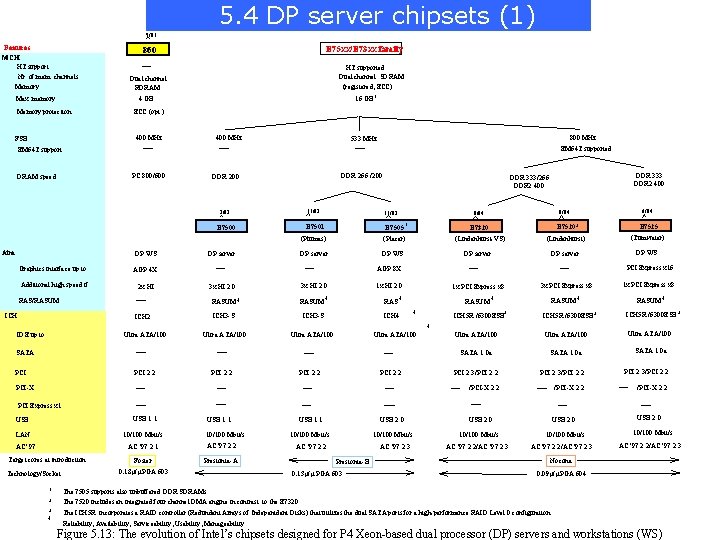

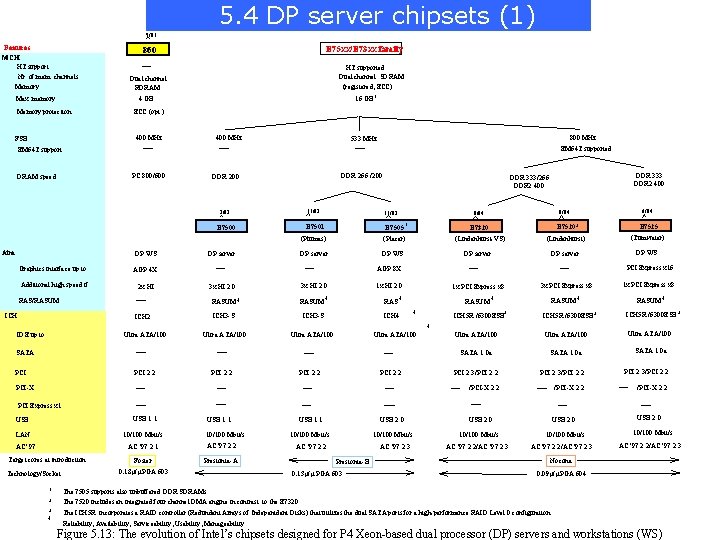

5. 4 DP server chipsets (1) 5/01 Features MCH HT support Nr. of mem. channels Memory Max. memory E 75 xx/E 73 xx family 860 HT supported Dual channel SDRAM (registered, ECC) Dual channel RDRAM 16 GB 1 4 GB Memory protection ECC (opt. ) FSB 400 MHz 800 MHz EM 64 T supported 533 MHz EM 64 T support PC 800/600 DRAM speed DDR 266 /200 DDR 200 11/02 2/02 E 7500 Aim DP WS Graphics interface up to Additional high speed if. DP server RAS/RASUM E 7501 E 7505 (Plumas) (Placer) DP server DP WS 6/04 8/04 1 E 7320 E 75202 E 7525 (Lindenhurst-VS) (Lindenhurst) (Tumwater) DP server DP WS DP server PCI Express x 16 AGP 8 X 3 x HI 2. 0 RASUM 4 ICH 11/02 AGP 4 X 2 x HI DDR 333 DDR 2 400 DDR 333/266 DDR 2 400 ICH 2: ICH 3 -S: Ultra ATA/100 3 x HI 2. 0 1 x HI 2. 0 4 4 RASUM RAS ICH 3 -S: ICH 4: 1 x PCI Express x 8 RASUM 4 4 3 x PCI Express x 8 RASUM 3 4 1 x PCI Express x 8 RASUM 4 ICH 5 R: /6300 ESB: 3 Ultra ATA/100 SATA 1. 0 a 4 IDE up to Ultra ATA/100 SATA PCI 2. 2 PCI-X PCI 2. 3/PCI 2. 2 /PCI-X 2. 2 PCI Express x 1 USB 1. 1 LAN 10/100 Mbit/s AC' 97 Target cores at introduction Technology/Socket 1 2 3 4 USB 1. 1 10/100 Mbit/s AC '97 2. 1 AC '97 2. 2 Foster Prestonia-A 0. 18 m/m PGA 603 USB 1. 1 USB 2. 0 10/100 Mbit/s AC '97 2. 2 AC '97 2. 3 Prestonia-B 0. 13 m/m PGA 603 AC '97 2. 2/AC '97 2. 3 USB 2. 0 10/100 Mbit/s AC '97 2. 2/AC '97 2. 3 Nocona 0. 09 m/m PGA 604 The 7505 supports also unbuffered DDR SDRAMs. The 7520 includes an integrated four channel DMA engine in contrast to the E 7320. The ICH 5 R incorporates a RAID controller (Redundant Arrays of Indepentdent Disks) that utilizes the dual SATA ports for a high-performance RAID Level 0 configuration. Reliability, Availability, Serviceability, Usability, Manageability Figure 5. 13: The evolution of Intel’s chipsets designed for P 4 Xeon-based dual processor (DP) servers and workstations (WS)

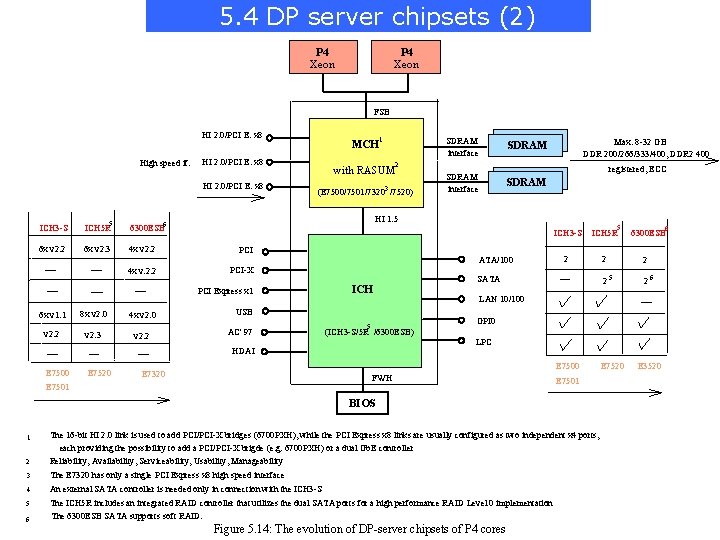

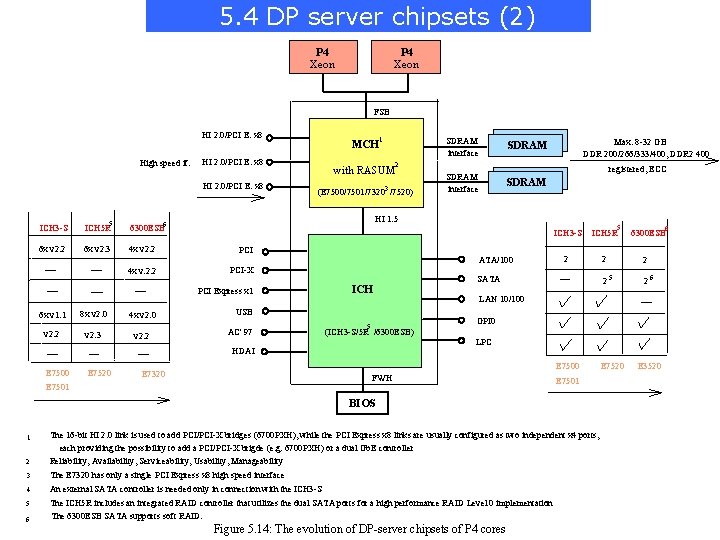

5. 4 DP server chipsets (2) P 4 Xeon FSB HI 2. 0/PCI E. x 8 High speed if. HI 2. 0/PCI E. x 8 5 MCH ICH 5 R 6300 ESB 6 6 x v 2. 2 6 x v 2. 3 4 x v 2. 2 PCI 4 x v. 2. 2 PCI-X 4 x v 2. 0 v 2. 2 v 2. 3 v 2. 2 (E 7500/7501/73203 /7520) E 7520 SDRAM interface SDRAM Max. 8 -32 GB DDR 200/266/333/400, DDR 2 400 registered, ECC ATA/100 ICH USB AC' 97 2 25 26 SATA GPI 0 5 LPC E 7501 BIOS 2 The 16 -bit HI 2. 0 link is used to add PCI/PCI-X bridges (6700 PXH), while the PCI Express x 8 links are usually configured as two independent x 4 ports, each providing the possibility to add a PCI/PCI-X brigde (e. g. 6700 PXH) or a dual Gb. E controller Reliability, Availability, Serviceability, Usability, Manageability 3 The E 7320 has only a single PCI Express x 8 high speed interface 1 4 An external SATA controller is needed only in connection with the ICH 3 -S 5 The ICH 5 R includes an integrated RAID controller that utilizes the dual SATA ports for a high performance RAID Level 0 implementation The 6300 ESB SATA supports soft RAID. 6 6300 ESB LAN 10/100 FWH E 7501 6 ICH 5 R E 7500 E 7320 5 ICH 3 -S (ICH 3 -S/5 R /6300 ESB) HDAI E 7500 SDRAM 2 with RASUM PCI Express x 1 8 x v 2. 0 SDRAM interface HI 1. 5 ICH 3 -S 6 x v 1. 1 1 Figure 5. 14: The evolution of DP-server chipsets of P 4 cores E 7520 E 3520

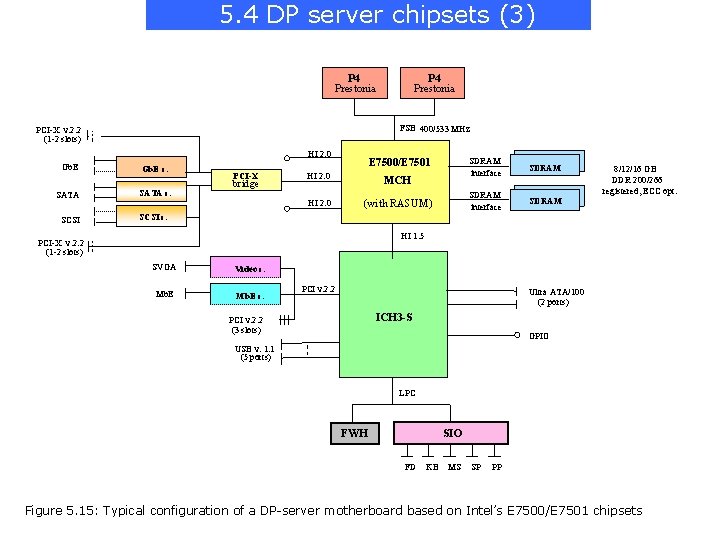

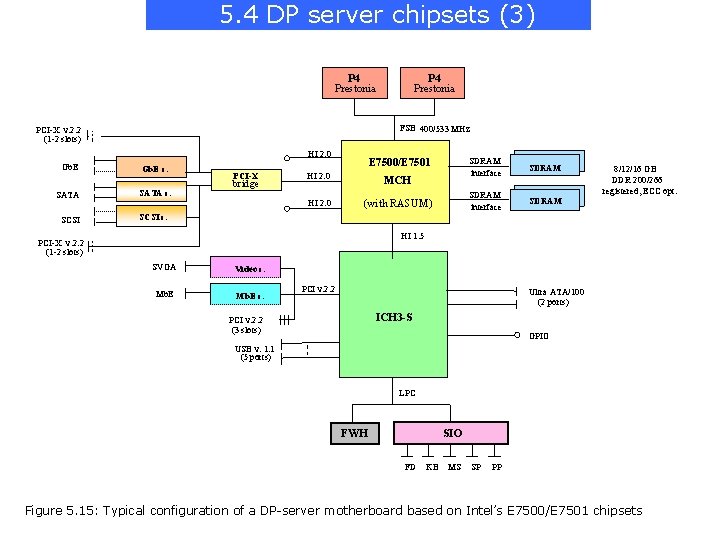

5. 4 DP server chipsets (3) P 4 Prestonia FSB 400/533 MHz PCI-X v. 2. 2 (1 -2 slots) HI 2. 0 Gb. E SATA SCSI Gb. E c. SATA c. PCI-X bridge E 7500/E 7501 HI 2. 0 MCH HI 2. 0 (with RASUM) SDRAM interface SDRAM 8/12/16 GB DDR 200/266 registered, ECC opt. SCSI c. HI 1. 5 PCI-X v. 2. 2 (1 -2 slots) SVGA Video c. Mb. E c. PCI v. 2. 2 Ultra ATA/100 (2 ports) ICH 3 -S PCI v. 2. 2 (3 slots) GPIO USB v. 1. 1 (5 ports) LPC FWH SIO FD KB MS SP PP Figure 5. 15: Typical configuration of a DP-server motherboard based on Intel’s E 7500/E 7501 chipsets

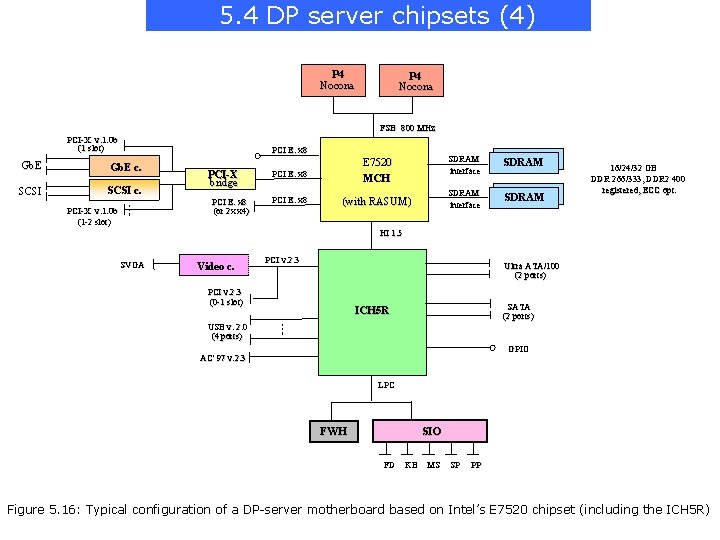

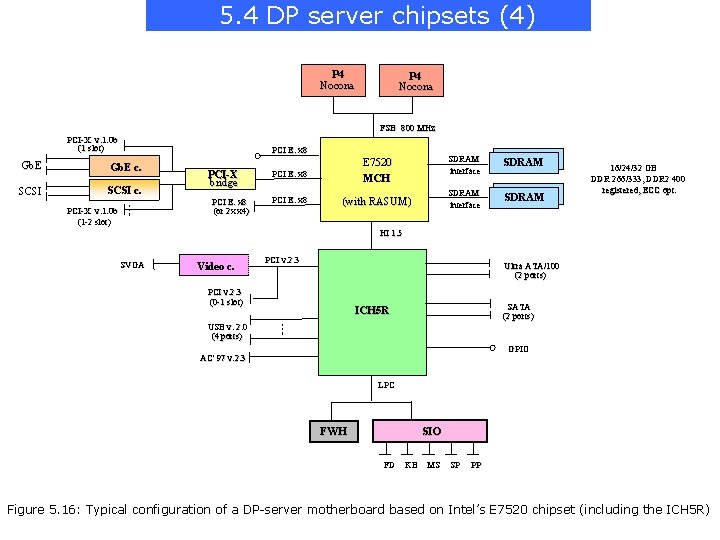

5. 4 DP server chipsets (4) P 4 Nocona FSB 800 MHz PCI-X v. 1. 0 b (1 slot) PCI E. x 8 Gb. E c. SCSI c. PCI-X bridgee PCI E. x 8 (or 2 x x 4) PCI-X v. 1. 0 b (1 -2 slot) PCI E. x 8 E 7520 MCH PCI E. x 8 (with RASUM) SDRAM interface SDRAM 16/24/32 GB DDR 266/333, DDR 2 400 registered, ECC opt. HI 1. 5 SVGA Video c. PCI v. 2. 3 Ultra ATA/100 (2 ports) PCI v. 2. 3 (0 -1 slot) SATA (2 ports) ICH 5 R USB v. 2. 0 (4 ports) GPIO AC' 97 v. 2. 3 LPC FWH SIO FD KB MS SP PP Figure 5. 16: Typical configuration of a DP-server motherboard based on Intel’s E 7520 chipset (including the ICH 5 R)

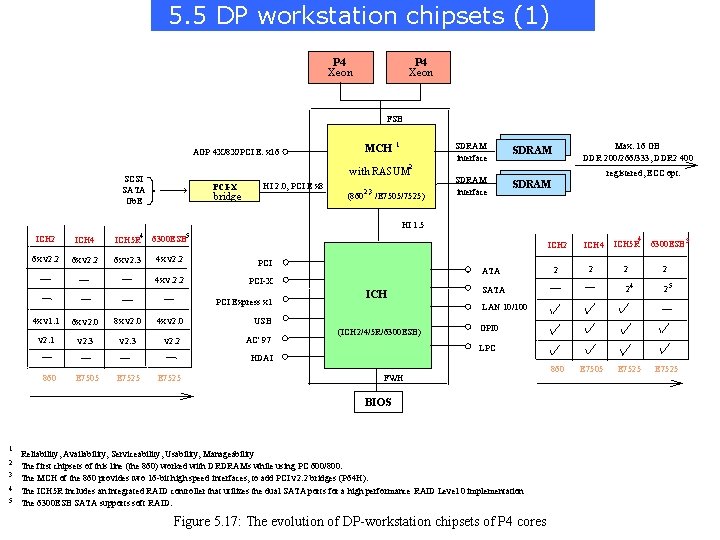

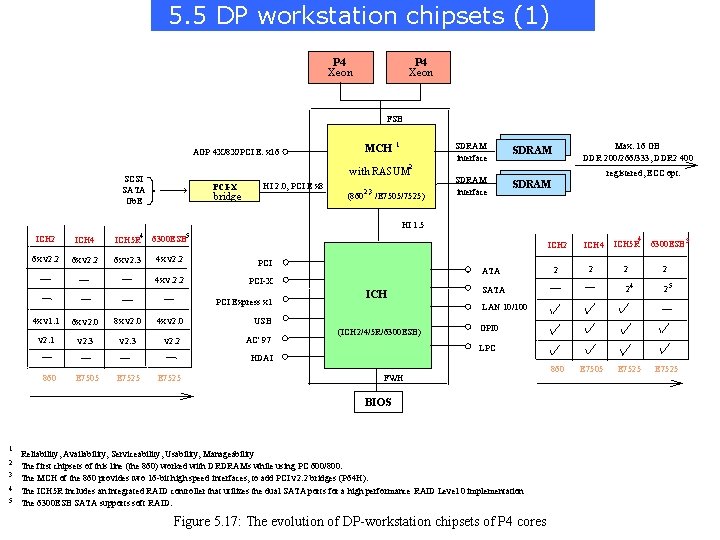

5. 5 DP workstation chipsets (1) P 4 Xeon FSB MCH AGP 4 X/8 X/PCI E. x 16 1 2 with RASUM SCSI SATA Gb. E PCI-X bridge HI 2. 0, PCI E x 8 (860 2, 3 /E 7505/7525) SDRAM interface Max. 16 GB DDR 200/266/333, DDR 2 400 SDRAM registered, ECC opt. SDRAM HI 1. 5 4 5 ICH 2 ICH 4 ICH 5 R 6300 ESB 6 x v 2. 2 6 x v 2. 3 4 x v 2. 2 4 x v. 2. 2 ICH 2 PCI-X PCI Express x 1 4 x v 1. 1 6 x v 2. 0 8 x v 2. 0 4 x v 2. 0 v 2. 1 v 2. 3 v 2. 2 ATA ICH 2 SATA 4 ICH 5 R 6300 ESB 5 2 2 24 25 E 7525 LAN 10/100 USB AC' 97 2 ICH 4 (ICH 2/4/5 R/6300 ESB) GPI 0 LPC HDAI 860 E 7505 E 7525 FWH BIOS 1 2 3 4 5 Reliability, Availability, Serviceability, Usability, Manageability The first chipsets of this line (the 860) worked with DRDRAMs while using PC 600/800. The MCH of the 860 provides two 16 -bit high speed interfaces, to add PCI v 2. 2 bridges (P 64 H). The ICH 5 R includes an integrated RAID controller that utilizes the dual SATA ports for a high performance RAID Level 0 implementation The 6300 ESB SATA supports soft RAID. Figure 5. 17: The evolution of DP-workstation chipsets of P 4 cores 860 E 7505

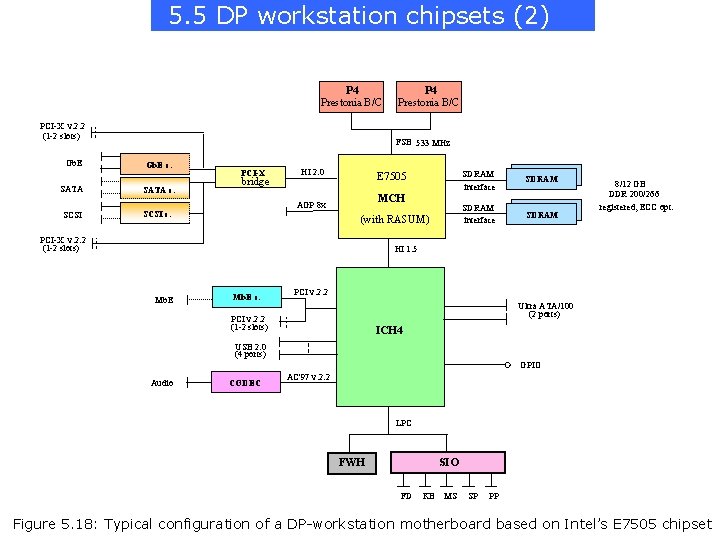

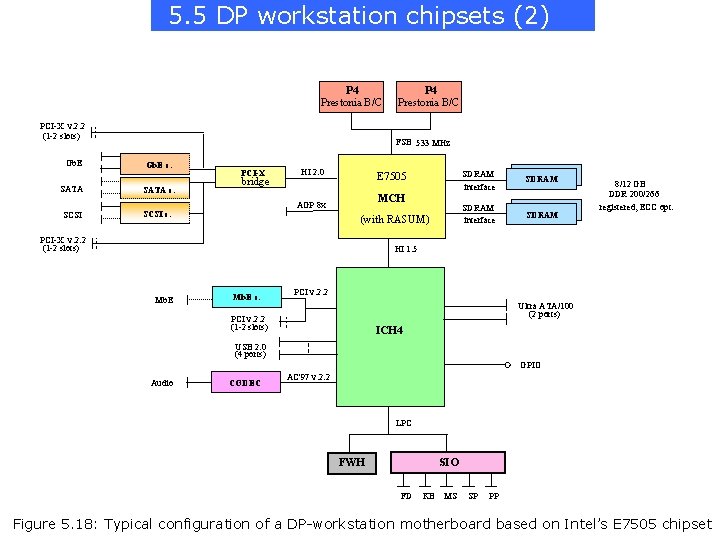

5. 5 DP workstation chipsets (2) P 4 Prestonia B/C PCI-X v. 2. 2 (1 -2 slots) Gb. E SATA SCSI P 4 Prestonia B/C FSB 533 MHz Gb. E c. SATA c. PCI-X bridge HI 2. 0 E 7505 MCH AGP 8 x SCSI c. (with RASUM) PCI-X v. 2. 2 (1 -2 slots) SDRAM interface SDRAM 8/12 GB DDR 200/266 registered, ECC opt. HI 1. 5 Mb. E c. PCI v. 2. 2 Ultra ATA/100 (2 ports) PCI v. 2. 2 (1 -2 slots) ICH 4 USB 2. 0 (4 ports) GPIO Audio CODEC AC'97 v. 2. 2 LPC FWH SIO FD KB MS SP PP Figure 5. 18: Typical configuration of a DP-workstation motherboard based on Intel’s E 7505 chipset

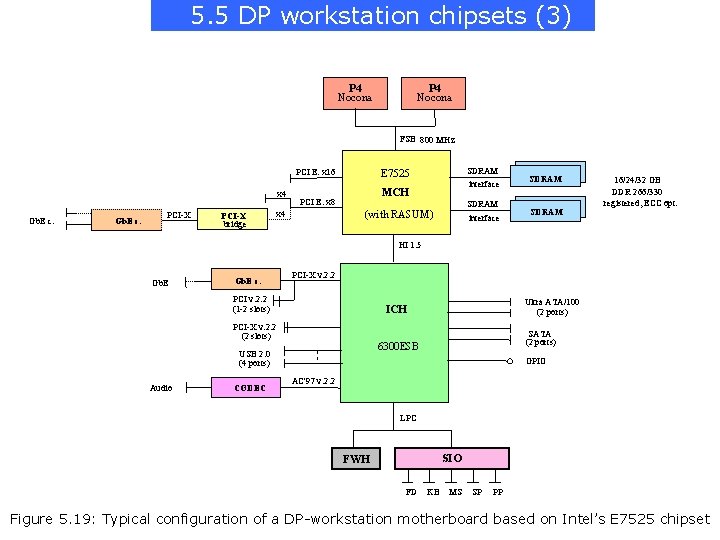

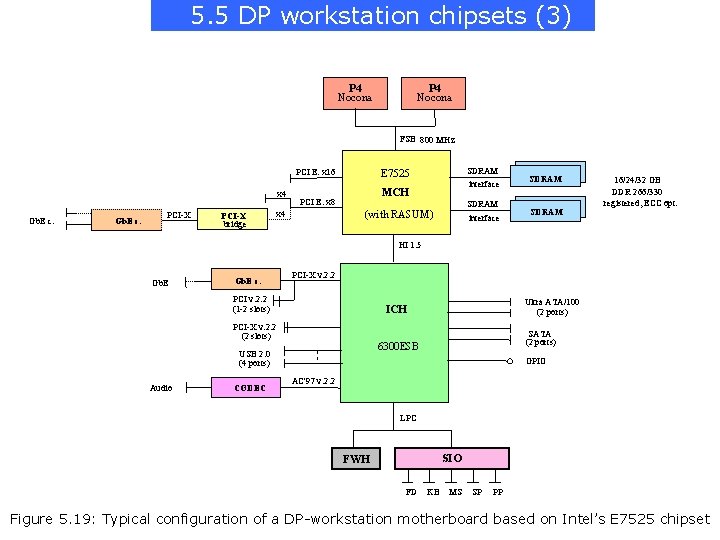

5. 5 DP workstation chipsets (3) P 4 Nocona FSB 800 MHz PCI E. x 16 x 4 Gb. E c. PCI-X bridge SDRAM interface E 7525 MCH PCI E. x 8 SDRAM (with RASUM) x 4 interface SDRAM 16/24/32 GB DDR 266/330 registered, ECC opt. HI 1. 5 Gb. E c. PCI-X v. 2. 2 PCI v. 2. 2 (1 -2 slots) PCI-X v. 2. 2 (2 slots) CODEC SATA (2 ports) 6300 ESB USB 2. 0 (4 ports) Audio Ultra ATA/100 (2 ports) ICH GPIO AC'97 v. 2. 2 LPC SIO FWH FD KB MS SP PP Figure 5. 19: Typical configuration of a DP-workstation motherboard based on Intel’s E 7525 chipset

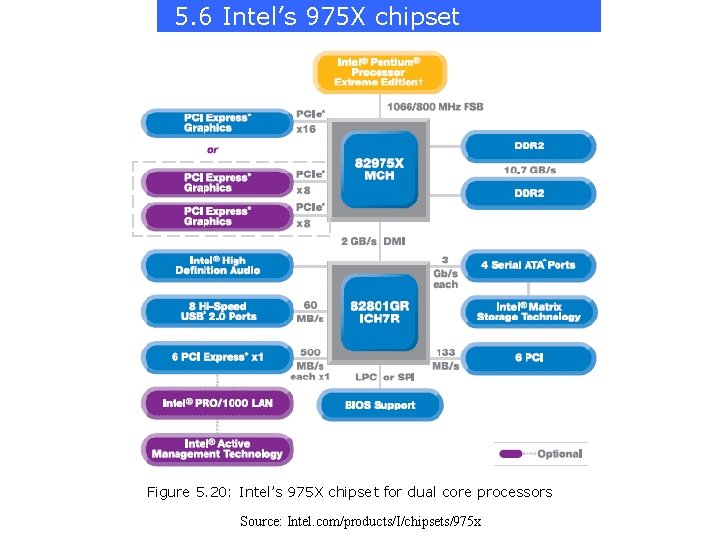

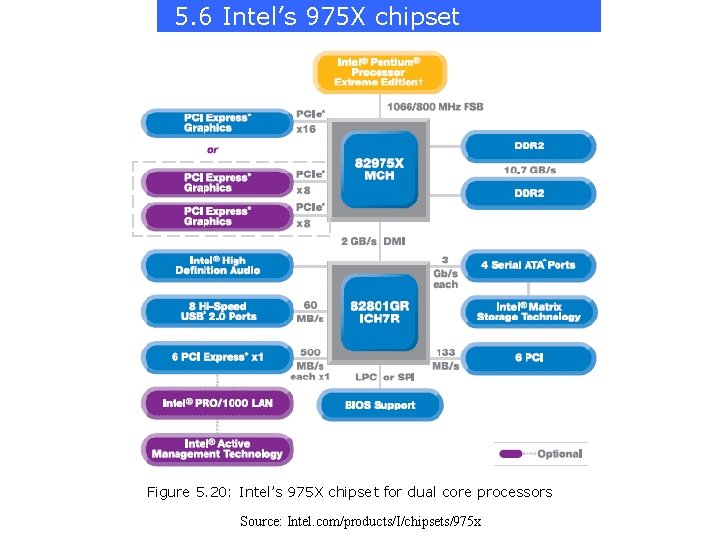

5. 6 Intel’s 975 X chipset Figure 5. 20: Intel’s 975 X chipset for dual core processors Source: Intel. com/products/I/chipsets/975 x

6. Bandwidth considerations

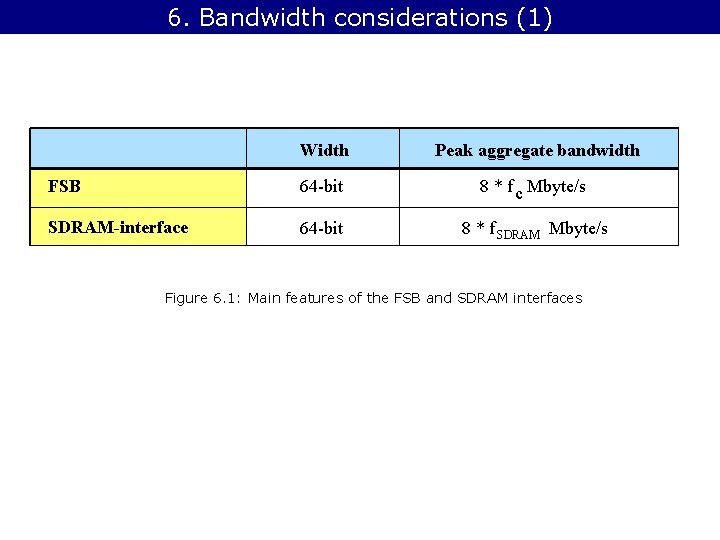

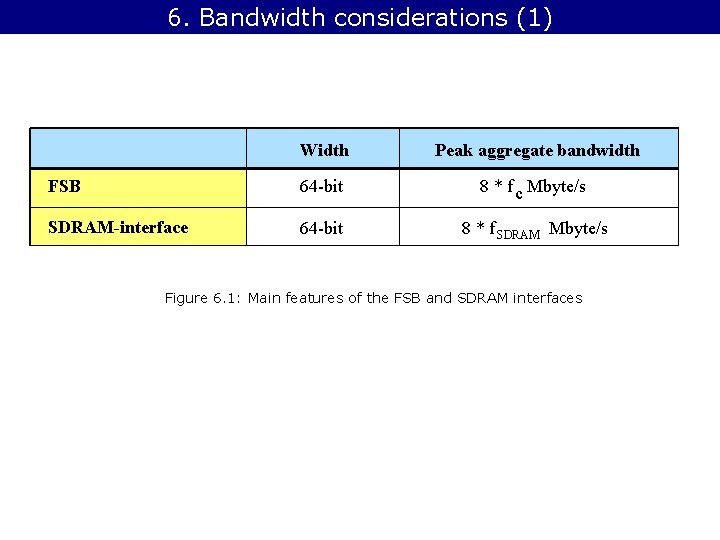

6. Bandwidth considerations (1) Width Peak aggregate bandwidth FSB 64 -bit 8 * f c Mbyte/s SDRAM-interface 64 -bit 8 * f SDRAM Mbyte/s Figure 6. 1: Main features of the FSB and SDRAM interfaces

6. Bandwidth considerations (2) Figure 6. 2: Main features of MCH/ICH interfaces used in Intel’s P 4 -based chipsets

6. Bandwidth considerations (3) Figure 6. 3: Main features of high speed MCH interfaces of Intel’s P 4 -based chipsets

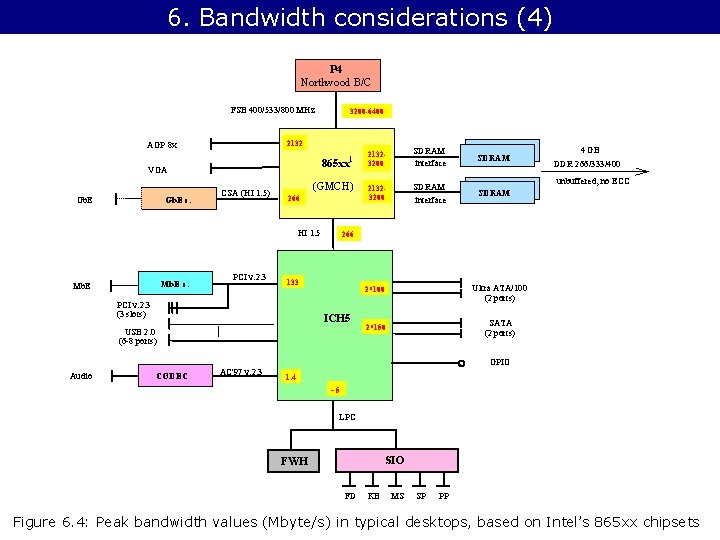

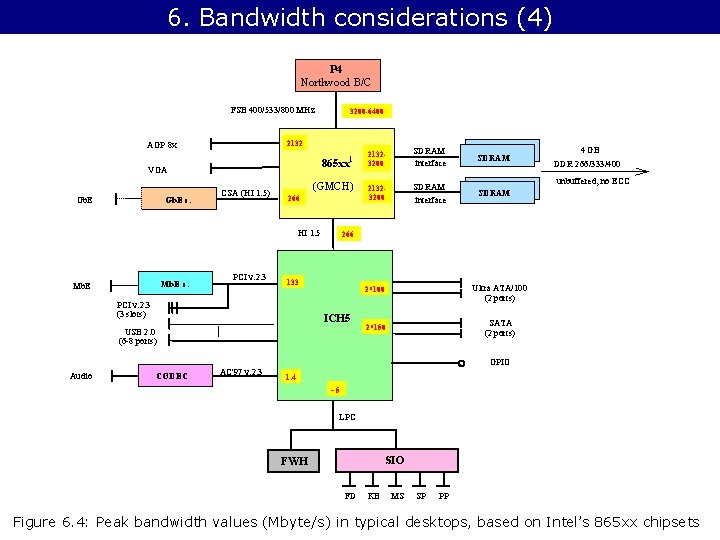

6. Bandwidth considerations (4) P 4 Northwood B/C FSB 400/533/800 MHz 2132 AGP 8 x 865 xx 1 VGA Gb. E c. Gb. E 3200 -6400 CSA (HI 1. 5) (GMCH) 266 HI 1. 5 Mb. E c. Mb. E PCI v. 2. 3 ICH 5 USB 2. 0 (6 -8 ports) Audio CODEC AC'97 v. 2. 3 SDRAM interface SDRAM 21323200 SDRAM interface SDRAM 4 GB DDR 266/333/400 unbuffered, no ECC 266 133 PCI v. 2. 3 (3 slots) 21323200 2*100 Ultra ATA/100 (2 ports) 2*150 SATA (2 ports) GPIO 1. 4 ~5 LPC SIO FWH FD KB MS SP PP Figure 6. 4: Peak bandwidth values (Mbyte/s) in typical desktops, based on Intel’s 865 xx chipsets

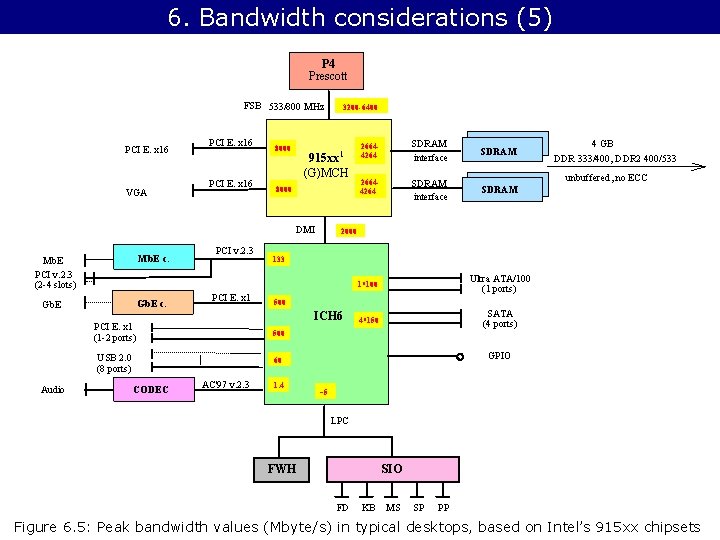

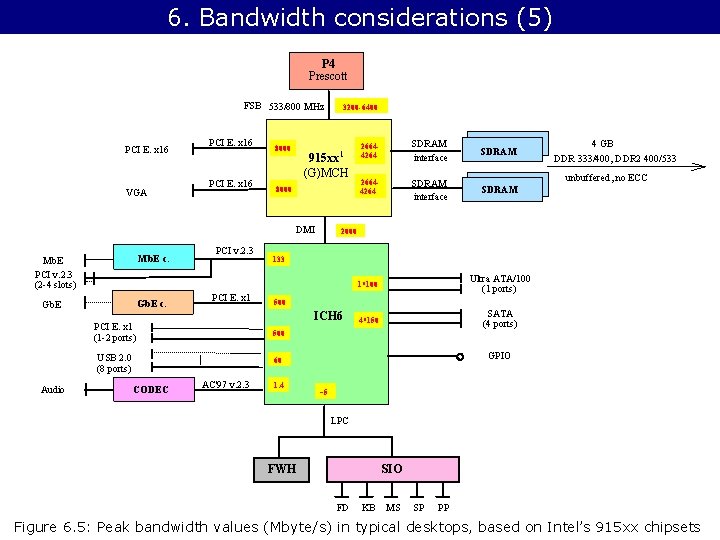

6. Bandwidth considerations (5) P 4 Prescott FSB 533/800 MHz PCI E. x 16 VGA PCI E. x 16 8000 1 915 xx (G)MCH 8000 DMI Mb. E c. Mb. E PCI v. 2. 3 (2 -4 slots) Gb. E c. Gb. E Audio PCI v. 2. 3 PCI E. x 1 SDRAM interface SDRAM 26644264 SDRAM interface SDRAM 4 GB DDR 333/400, DDR 2 400/533 unbuffered, no ECC 2000 1*100 Ultra ATA/100 (1 ports) 4*150 SATA (4 ports) 500 ICH 6 500 USB 2. 0 (8 ports) 60 AC'97 v. 2. 3 26644264 133 PCI E. x 1 (1 -2 ports) CODEC 3200 -6400 1. 4 GPIO ~5 LPC FWH SIO FD KB MS SP PP Figure 6. 5: Peak bandwidth values (Mbyte/s) in typical desktops, based on Intel’s 915 xx chipsets

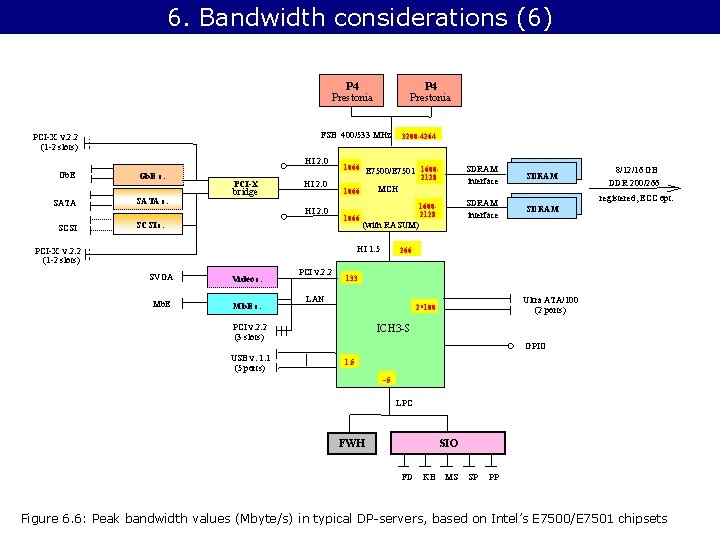

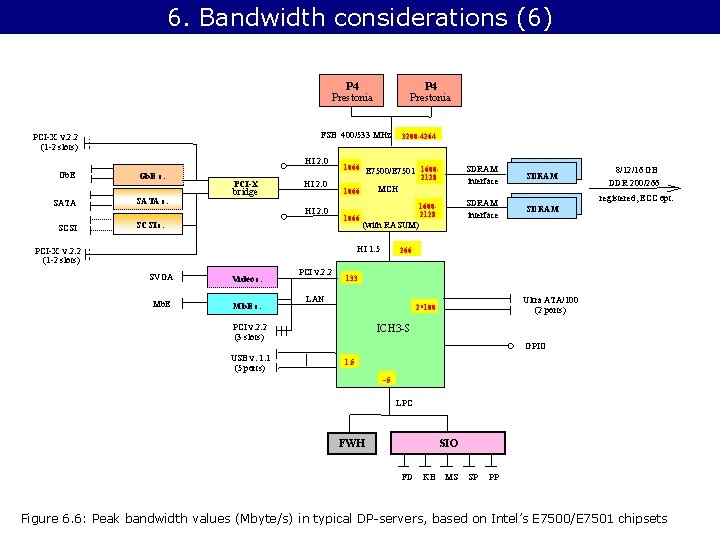

6. Bandwidth considerations (6) P 4 Prestonia FSB 400/533 MHz PCI-X v. 2. 2 (1 -2 slots) HI 2. 0 Gb. E SATA SCSI P 4 Prestonia Gb. E c. SATA c. PCI-X bridge HI 2. 0 SCSI c. 1066 E 7500/E 7501 16002128 MCH 1066 16002128 Video c. Mb. E c. PCI v. 2. 2 SDRAM interface SDRAM 8/12/16 GB DDR 200/266 registered, ECC opt. 266 133 LAN Ultra ATA/100 (2 ports) 2*100 PCI v. 2. 2 (3 slots) USB v. 1. 1 (5 ports) SDRAM interface (with RASUM) HI 1. 5 PCI-X v. 2. 2 (1 -2 slots) SVGA 3200 -4264 ICH 3 -S GPIO 1. 5 ~5 LPC SIO FWH FD KB MS SP PP Figure 6. 6: Peak bandwidth values (Mbyte/s) in typical DP-servers, based on Intel’s E 7500/E 7501 chipsets

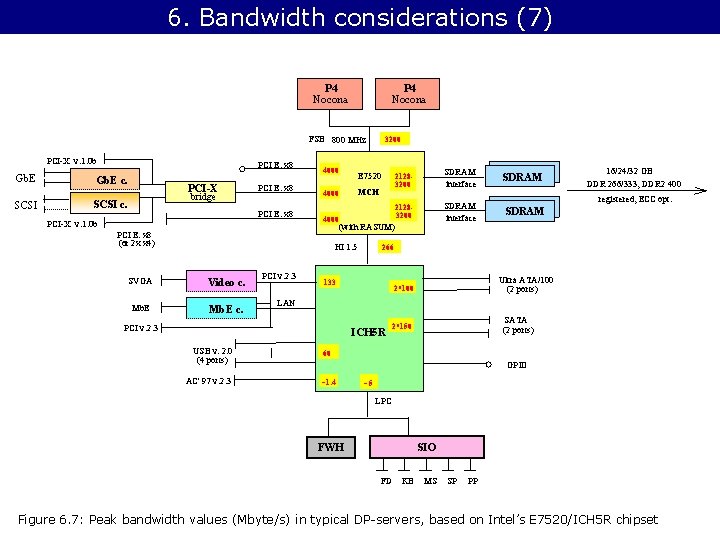

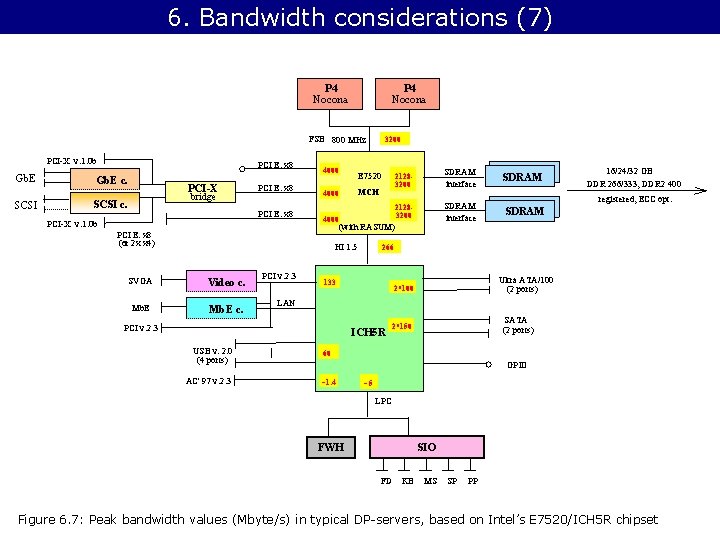

6. Bandwidth considerations (7) P 4 Nocona FSB 800 MHz PCI-X v. 1. 0 b Gb. E SCSI PCI E. x 8 Gb. E c. PCI-X bridge SCSI c. PCI E. x 8 PCI-X v. 1. 0 b 4000 3200 E 7520 MCH 4000 21283200 SDRAM interface SDRAM (with RASUM) PCI E. x 8 (or 2 x x 4) HI 1. 5 SVGA Video c. Mb. E c. PCI v. 2. 3 Ultra ATA/100 (2 ports) 2*100 LAN ICH 5 R AC' 97 v. 2. 3 registered, ECC opt. 266 133 PCI v. 2. 3 USB v. 2. 0 (4 ports) 16/24/32 GB DDR 266/333, DDR 2 400 SATA (2 ports) 2*150 60 GPIO ~1. 4 ~5 LPC SIO FWH FD KB MS SP PP Figure 6. 7: Peak bandwidth values (Mbyte/s) in typical DP-servers, based on Intel’s E 7520/ICH 5 R chipset

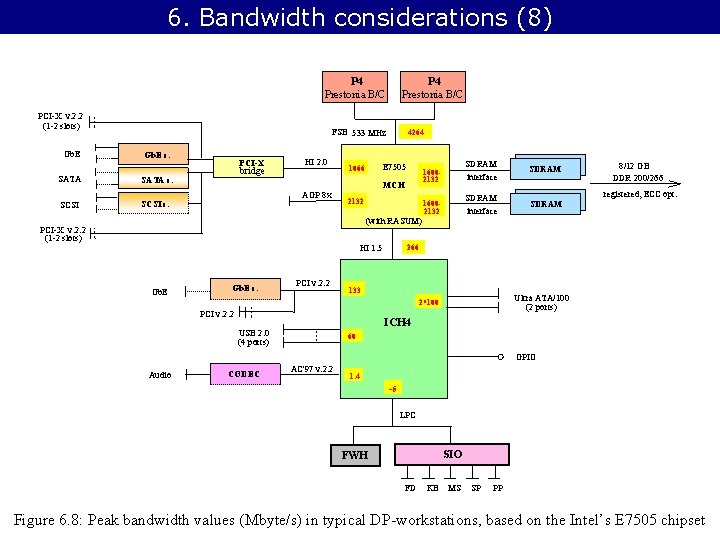

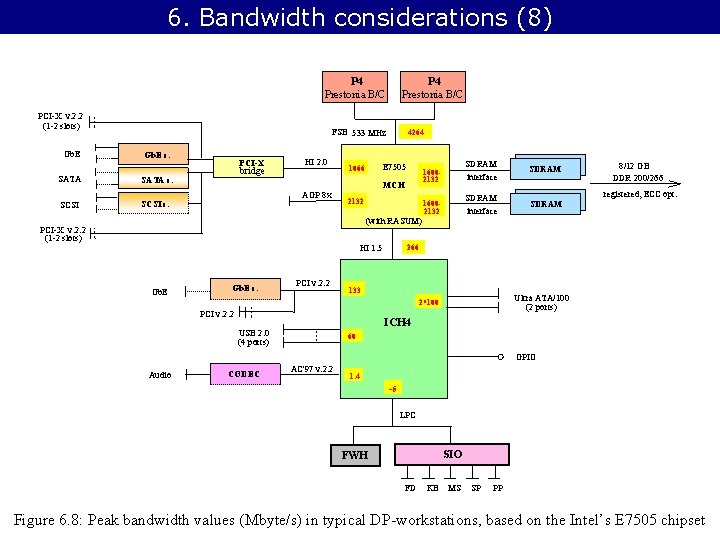

6. Bandwidth considerations (8) P 4 Prestonia B/C PCI-X v. 2. 2 (1 -2 slots) Gb. E SATA SCSI FSB 533 MHz Gb. E c. PCI-X bridge SATA c. HI 2. 0 4264 E 7505 1066 MCH AGP 8 x SCSI c. 2132 16002132 SDRAM interface SDRAM 8/12 GB DDR 200/266 registered, ECC opt. (with RASUM) PCI-X v. 2. 2 (1 -2 slots) HI 1. 5 Gb. E c. PCI v. 2. 2 266 133 Ultra ATA/100 (2 ports) 2*100 PCI v. 2. 2 ICH 4 USB 2. 0 (4 ports) 60 GPIO Audio CODEC AC'97 v. 2. 2 1. 4 ~5 LPC SIO FWH FD KB MS SP PP Figure 6. 8: Peak bandwidth values (Mbyte/s) in typical DP-workstations, based on the Intel’s E 7505 chipset

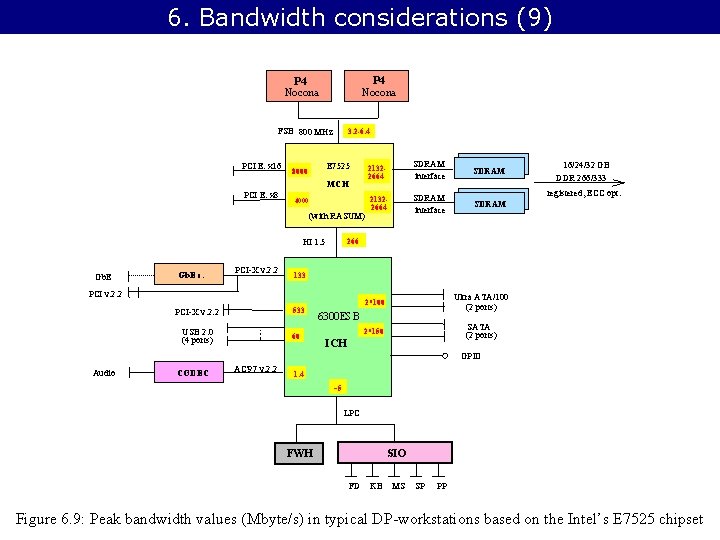

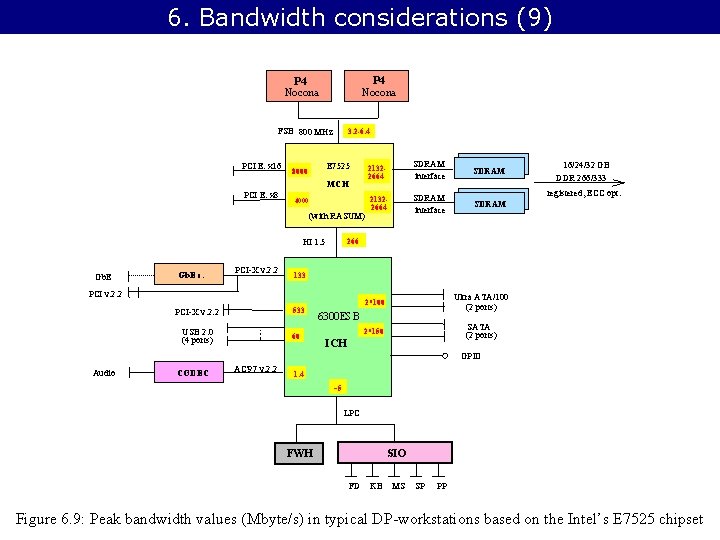

6. Bandwidth considerations (9) P 4 Nocona FSB 800 MHz PCI E. x 16 3. 2 -6. 4 E 7525 8000 MCH PCI E. x 8 4000 (with RASUM) Gb. E c. PCI-X v. 2. 2 533 USB 2. 0 (4 ports) SDRAM 21322664 SDRAM interface SDRAM 16/24/32 GB DDR 266/333 registered, ECC opt. 133 PCI v. 2. 2 PCI-X v. 2. 2 SDRAM interface 266 HI 1. 5 Gb. E 21322664 60 2*100 Ultra ATA/100 (2 ports) 2*150 SATA (2 ports) 6300 ESB ICH GPIO Audio CODEC AC'97 v. 2. 2 1. 4 ~5 LPC SIO FWH FD KB MS SP PP Figure 6. 9: Peak bandwidth values (Mbyte/s) in typical DP-workstations based on the Intel’s E 7525 chipset

7. Special aspects of the implementation

7. Special aspects of the implementation 7. 1 Attaching the display 7. 2 PCI-X bridges 7. 3 Attaching Mb. E/Gb. E controllers 7. 4 Attaching SCSI controllers 7. 5 Implementation of ICHs

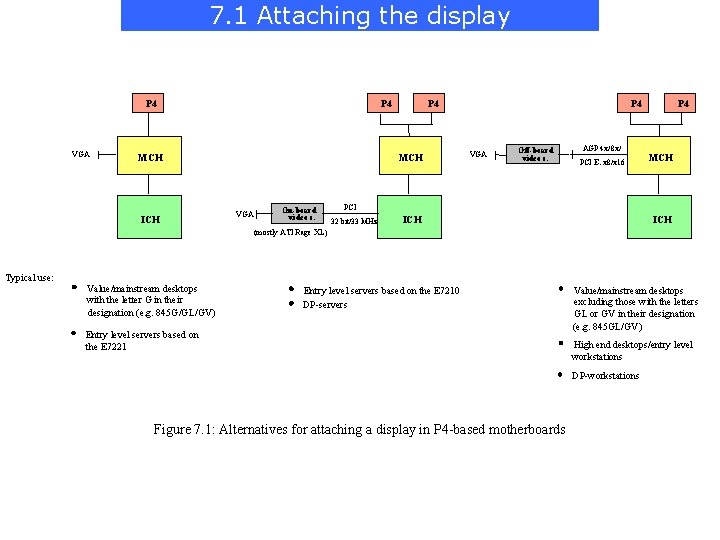

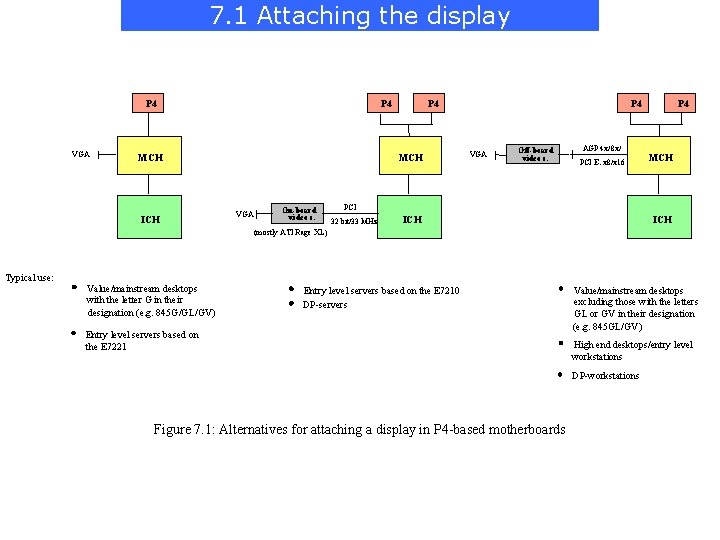

7. 1 Attaching the display P 4 VGA P 4 MCH ICH P 4 MCH VGA On-board video c. P 4 VGA Off-board video c. AGP 4 x/8 x/ PCI E. x 8/x 16 P 4 MCH PCI 32 bit/33 MHz ICH (mostly ATI Rage XL) Typical use: Value/mainstream desktops with the letter G in their designation (e. g. 845 G/GL/GV) Entry level servers based on the E 7210 DP-servers Entry level servers based on the E 7221 Value/mainstream desktops excluding those with the letters GL or GV in their designation (e. g. 845 GL/GV) High end desktops/entry level workstations DP-workstations Figure 7. 1: Alternatives for attaching a display in P 4 -based motherboards

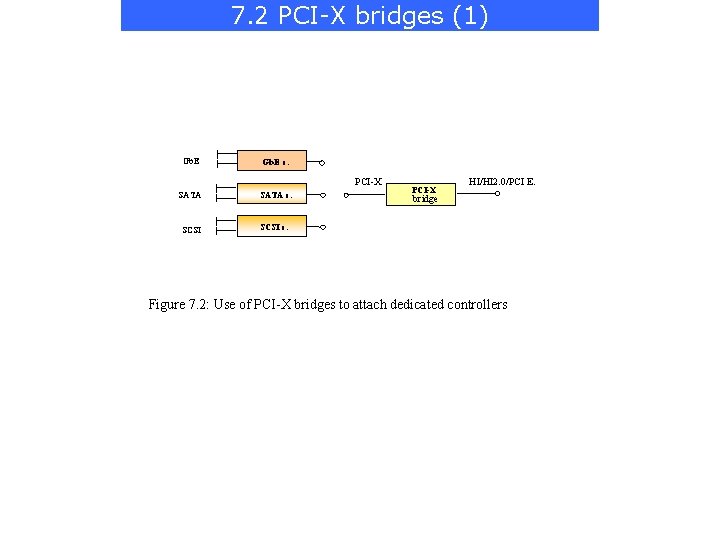

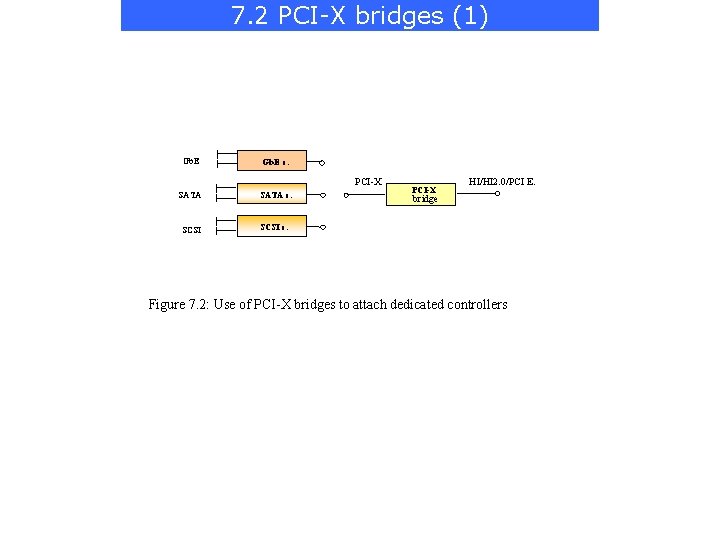

7. 2 PCI-X bridges (1) Gb. E c. SATA c. SCSI c. PCI-X HI/HI 2. 0/PCI E. bridge Figure 7. 2: Use of PCI-X bridges to attach dedicated controllers

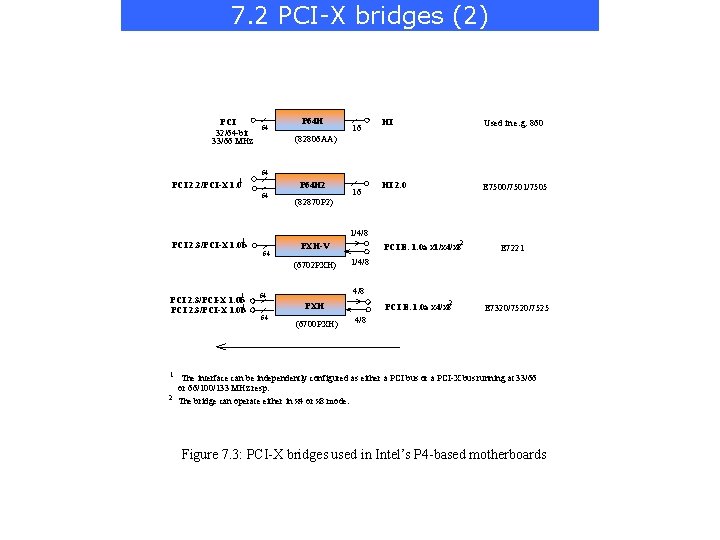

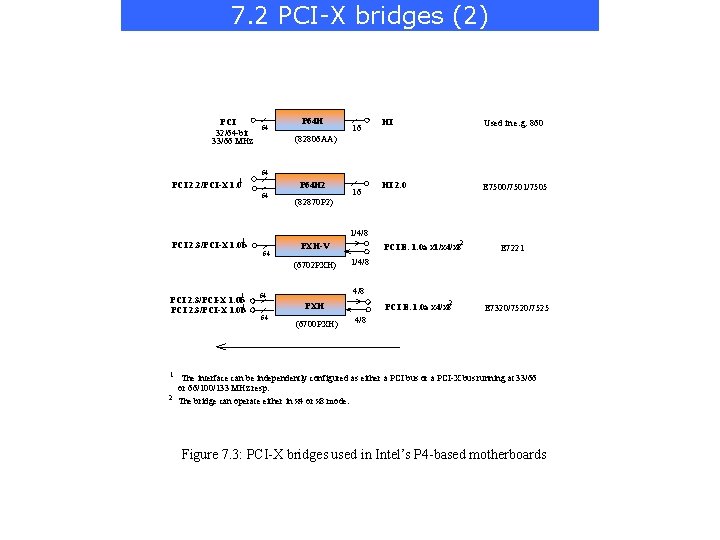

7. 2 PCI-X bridges (2) PCI 32/64 -bit 33/66 MHz 64 P 64 H 16 HI Used in e. g. 860 HI 2. 0 E 7500/7501/7505 (82806 AA) 64 1 PCI 2. 2/PCI-X 1. 0 P 64 H 2 64 (82870 P 2) 1/4/8 1 PCI 2. 3/PCI-X 1. 0 b 64 1 1 2 2 PXH-V (6702 PXH) PCI 2. 3/PCI-X 1. 0 b 16 PCI E. 1. 0 a x 1/x 4/x 8 1/4/8 64 2 PXH 64 E 7221 (6700 PXH) PCI E. 1. 0 a x 4/x 8 E 7320/7525 4/8 The interface can be independently configured as either a PCI bus or a PCI-X bus running at 33/66 or 66/100/133 MHz resp. The bridge can operate either in x 4 or x 8 mode. Figure 7. 3: PCI-X bridges used in Intel’s P 4 -based motherboards

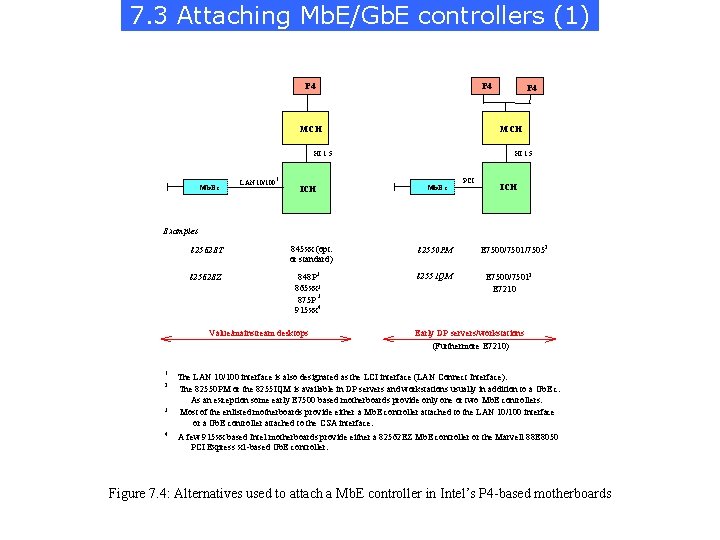

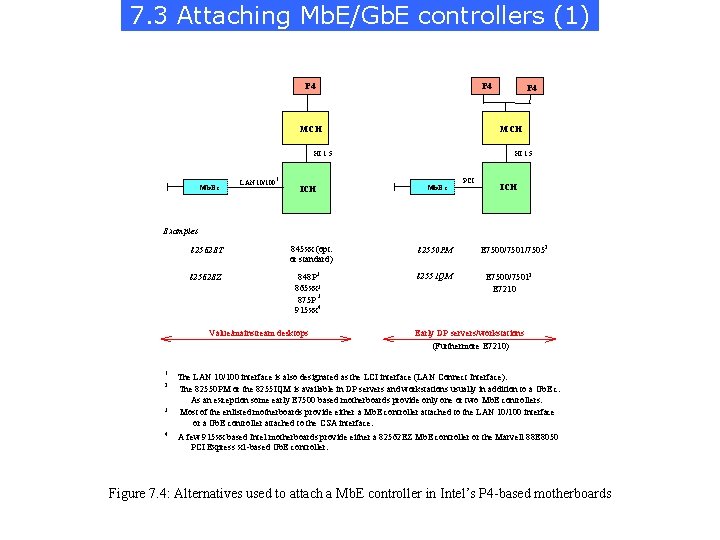

7. 3 Attaching Mb. E/Gb. E controllers (1) P 4 MCH HI 1. 5 1 Mb. E c. LAN 10/100 ICH P 4 Mb. E c. PCI ICH Examples 82562 ET 82562 EZ 845 xx (opt. or standard) 848 P 3 865 xx 3 3 875 P 915 xx 4 Value/mainstream desktops 1 2 3 4 82550 PM 82551 QM E 7500/7501/75052 E 7500/75012 E 7210 Early DP servers/workstations (Furthermore E 7210) The LAN 10/100 interface is also designated as the LCI interface (LAN Connect Interface). The 82550 PM or the 8255 IQM is available in DP servers and workstations usually in addition to a Gb. E c. As an exception some early E 7500 based motherboards provide only one or two Mb. E controllers. Most of the enlisted motherboards provide either a Mb. E controller attached to the LAN 10/100 interface or a Gb. E controller attached to the CSA interface. A few 915 xx based Intel motherboards provide either a 82562 EZ Mb. E controller or the Marvell 88 E 8050 PCI Express x 1 -based Gb. E controller. Figure 7. 4: Alternatives used to attach a Mb. E controller in Intel’s P 4 -based motherboards

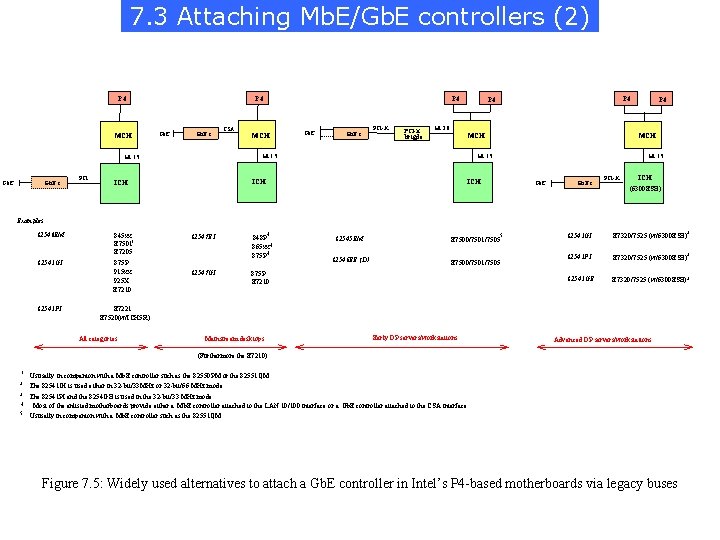

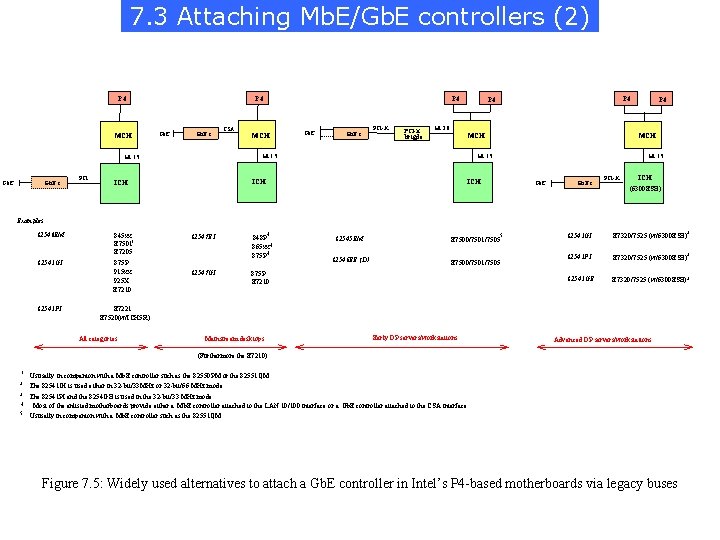

7. 3 Attaching Mb. E/Gb. E controllers (2) P 4 MCH P 4 Gb. E c. PCI MCH Gb. E c. PCI-X P 4 HI 2. 0 MCH brigde MCH HI 1. 5 ICH P 4 HI 1. 5 Gb. E CSA P 4 HI 1. 5 ICH Gb. E c. PCI-X ICH (6300 ESB) Examples 82540 EM 845 xx E 75011 E 7205 82541 GI 875 P 915 xx 925 X E 7210 82541 PI 82547 EI 82547 GI 4 848 P 865 xx 4 875 P 4 5 82545 EM E 7500/7501/7505 82546 EB (D) E 7500/7501/7505 875 P E 7210 2 82541 GI E 7320/7525 (w/6300 ESB) 82541 PI E 7320/7525 (w/6300 ESB) 82541 GB E 7320/7525 (w/6300 ESB) 3 3 E 7221 E 7520(w/ICH 5 R) All categories Mainstream desktops Early DP servers/workstations Advanced DP servers/workstations (Furthermore the E 7210) 1 2 3 4 5 Ususally in companion with a Mb. E controller such as the 82550 PM or the 82551 QM. The 82541 GI is used either in 32 -bit/33 MHz or 32 -bit/66 MHz mode. The 82541 PI and the 8254 GB is used in the 32 -bit/33 MHz mode. Most of the enlisted motherboards provide either a Mb. E controller attached to the LAN 10/100 interface or a Gb. E controller attached to the CSA interface. Ususally in companion with a Mb. E controller such as the 82551 QM. Figure 7. 5: Widely used alternatives to attach a Gb. E controller in Intel’s P 4 -based motherboards via legacy buses

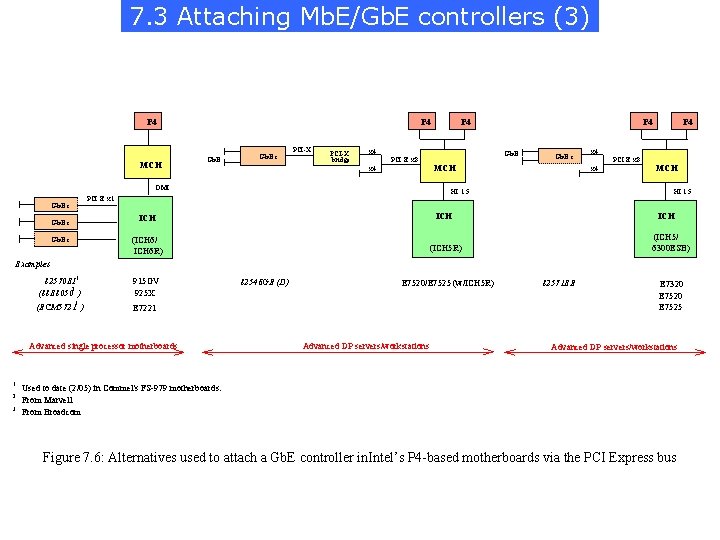

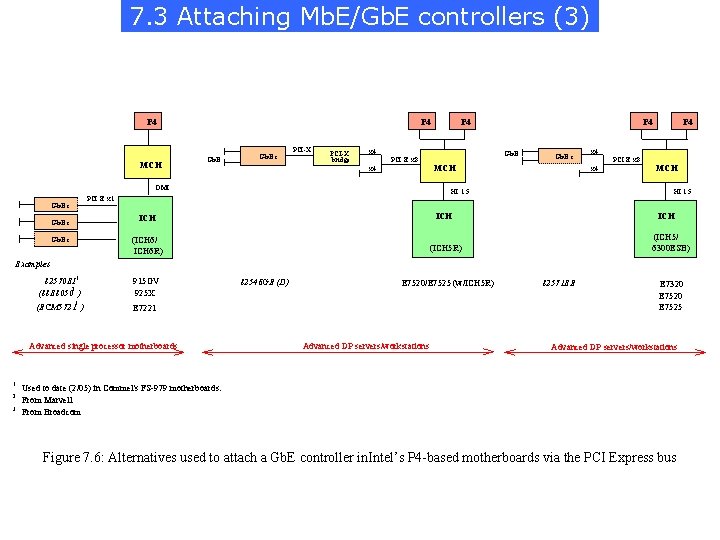

7. 3 Attaching Mb. E/Gb. E controllers (3) P 4 MCH P 4 Gb. E c. PCI-X bridge x 4 PCI E. x 8 x 4 DMI Gb. E c. P 4 Gb. E c. MCH ICH Gb. E c. (ICH 6/ ICH 6 R) (ICH 5 R) 82570 EI 1 2 (88 E 8050 ) 3 (BCM 5721 ) 915 GV 925 X P 4 x 4 PCI E. x 8 x 4 HI 1. 5 PCI E. x 1 ICH Gb. E c. P 4 MCH HI 1. 5 ICH (ICH 5/ 6300 ESB) Examples 2 3 E 7520/E 7525 (w/ICH 5 R) E 7221 Advanced single processor motherboards 1 82546 GB (D) Advanced DP servers/workstations 82571 EB E 7320 E 7525 Advanced DP servers/workstations Used to date (2/05) in Commel's FS-979 motherboards. From Marvell From Broadcom Figure 7. 6: Alternatives used to attach a Gb. E controller in. Intel’s P 4 -based motherboards via the PCI Express bus

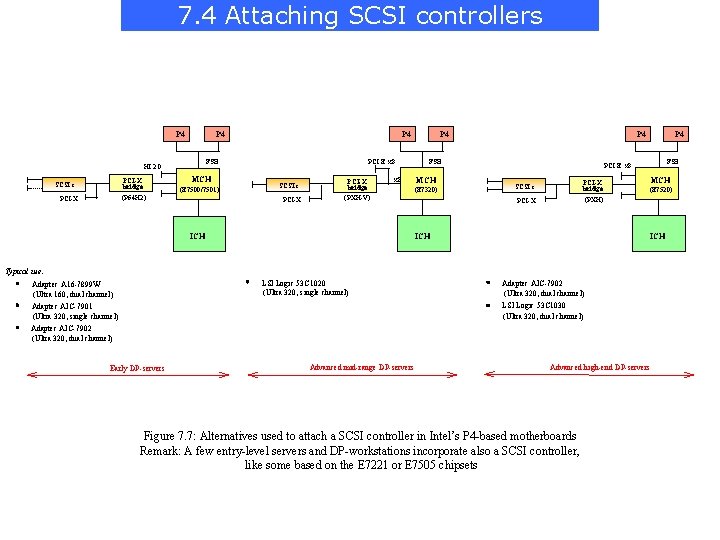

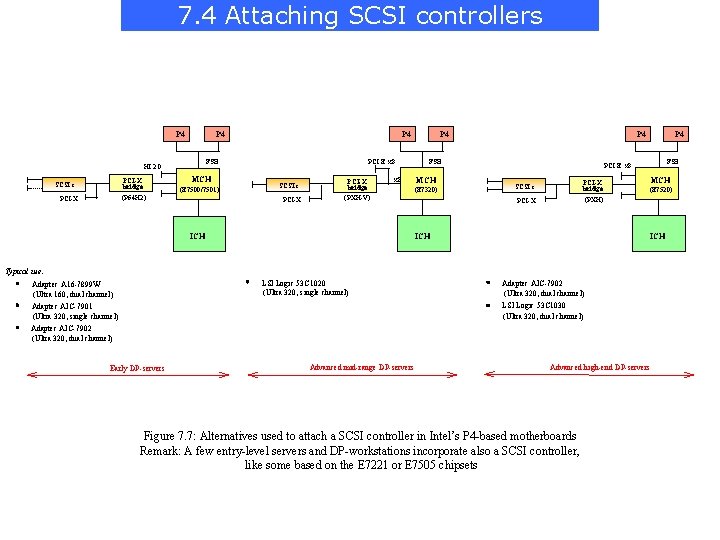

7. 4 Attaching SCSI controllers P 4 FSB HI 2. 0 PCI-X bridge SCSI c. MCH (E 7500/7501) (P 64 H 2) PCI-X P 4 PCI E. x 8 SCSI c. PCI-X bridge (PXH-V) x 8 P 4 FSB MCH (E 7320) FSB PCI E. x 8 SCSI c. PCI-X bridge PCI-X (PXH) ICH P 4 MCH (E 7520) ICH Typical use: LSI Logic 53 C 1020 (Ultra 320, single channel) Adaptec A 16 -7899 W (Ultra 160, dual channel) Adaptec AIC-7901 (Ultra 320, single channel) Adaptec AIC-7902 (Ultra 320, dual channel) Early DP-servers Advanced mid-range DP-servers Adaptec AIC-7902 (Ultra 320, dual channel) LSI Logic 53 C 1030 (Ultra 320, dual channel) Advanced high-end DP-servers Figure 7. 7: Alternatives used to attach a SCSI controller in Intel’s P 4 -based motherboards Remark: A few entry-level servers and DP-workstations incorporate also a SCSI controller, like some based on the E 7221 or E 7505 chipsets

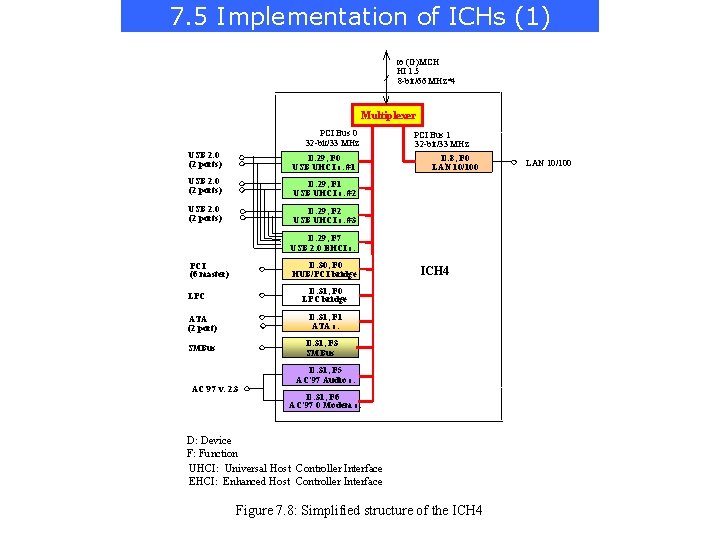

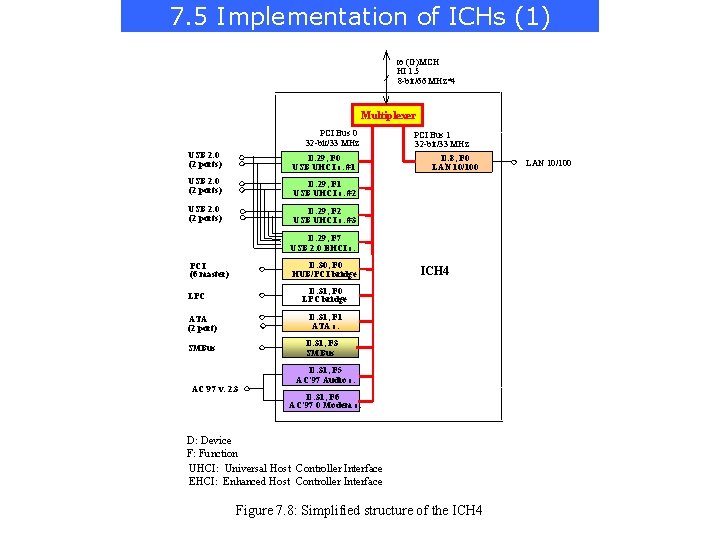

7. 5 Implementation of ICHs (1) to (G)MCH HI 1. 5 8 -bit/66 MHz*4 Multiplexer PCI Bus 0 32 -bit/33 MHz USB 2. 0 (2 ports) D: 29, F 0 USB UHCI c. #1 USB 2. 0 (2 ports) D: 29, F 1 USB UHCI c. #2 USB 2. 0 (2 ports) D: 29, F 2 USB UHCI c. #3 PCI Bus 1 32 -bit/33 MHz D: 8, F 0 LAN 10/100 D: 29, F 7 USB 2. 0 EHCI c. D: 30, F 0 HUB/PCI bridge PCI (6 master) ICH 4 D: 31, F 0 LPC bridge LPC D: 31, F 1 ATA c. ATA (2 port) D: 31, F 3 SMBus AC'97 v. 2. 3 D: 31, F 5 AC'97 Audio c. D: 31, F 6 AC'97 0 Modem c. D: Device F: Function UHCI: Universal Host Controller Interface EHCI: Enhanced Host Controller Interface Figure 7. 8: Simplified structure of the ICH 4 LAN 10/100

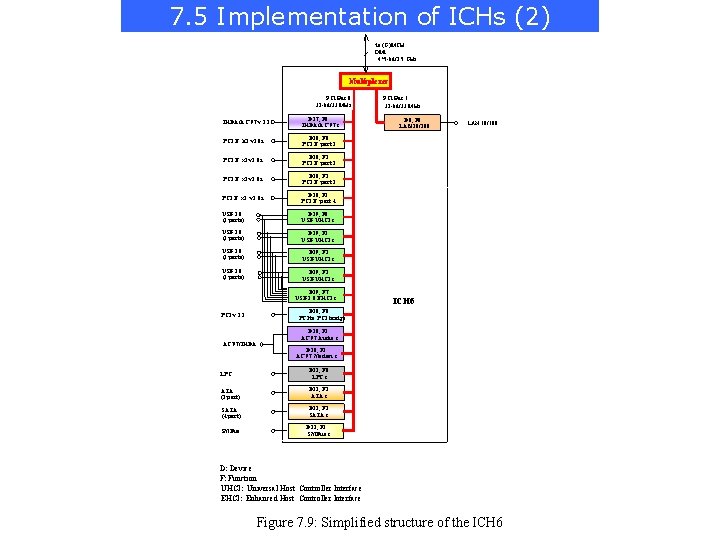

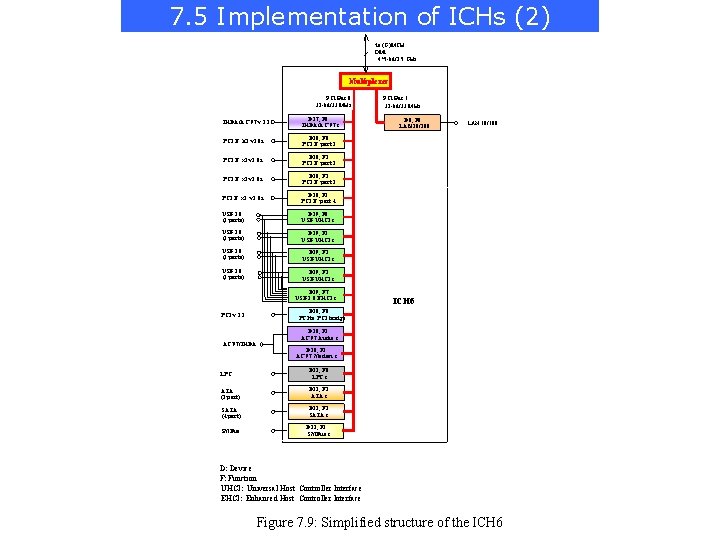

7. 5 Implementation of ICHs (2) to (G)MCH DMI 4*1 -bit/2. 5 GHz Multiplexer PCI Bus 0 32 -bit/33 MHz IHDA/AC'97 v. 2. 3 D 27, F 0 IHDA/AC'97 c. PCI E. X 1 v 1. 0 a D 28, F 0 PCI E. port 1 PCI E. x 1 v 1. 0 a D 28, F 1 PCI E. port 2 PCI E. x 1 v 1. 0 a D 28, F 2 PCI E. port 3 PCI E. x 1. v 1. 0 a D 28, F 3 PCI E. port 4 USB 2. 0 (2 ports) D 29, F 0 USB UHCI c. USB 2. 0 (2 ports) D 29, F 1 USB UHCI c. USB 2. 0 (2 ports) D 29, F 2 USB UHCI c. USB 2. 0 (2 ports) D 29, F 3 USB UHCI c. D 29, F 7 USB 2. 0 EHCI c. PCI v. 2. 3 PCI Bus 1 32 -bit/33 MHz D 8, F 0 LAN 10/100 ICH 6 D 30, F 0 PCI to PCI bridge D 30, F 2 AC'97 Audio c. AC'97/IHDA D 30, F 3 AC'97 Modem c. LPC D 31, F 0 LPC c. ATA (1 port) D 31, F 1 ATA c. SATA (4 port) D 31, F 2 SATA c. SMBus D 31, F 3 SMBus c. D: Device F: Function UHCI: Universal Host Controller Interface EHCI: Enhanced Host Controller Interface Figure 7. 9: Simplified structure of the ICH 6