Module III Processor Organization and Architecture Processor Organization

- Slides: 30

Module III Processor Organization and Architecture

Processor Organization • Requirements of CPU: 1. 2. 3. 4. Fetch instructions (from m/m, reg, cache) Interpret instructions (decoding) Fetch data Process data/Execute (arithmetic/logical operations) 5. Write data

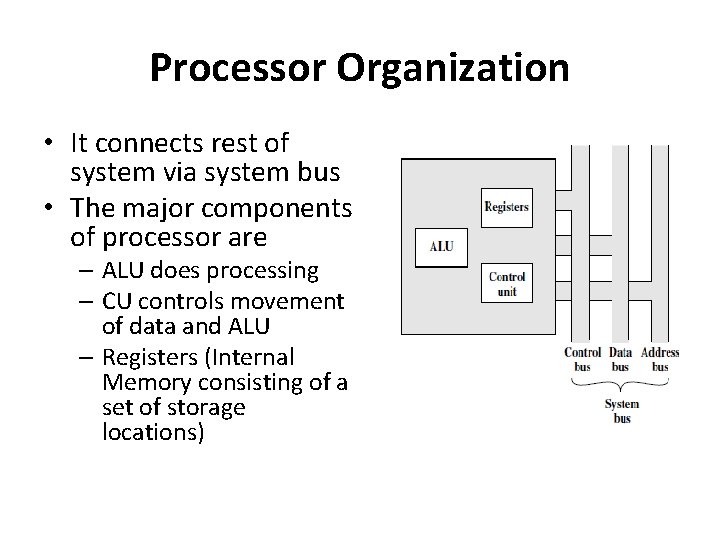

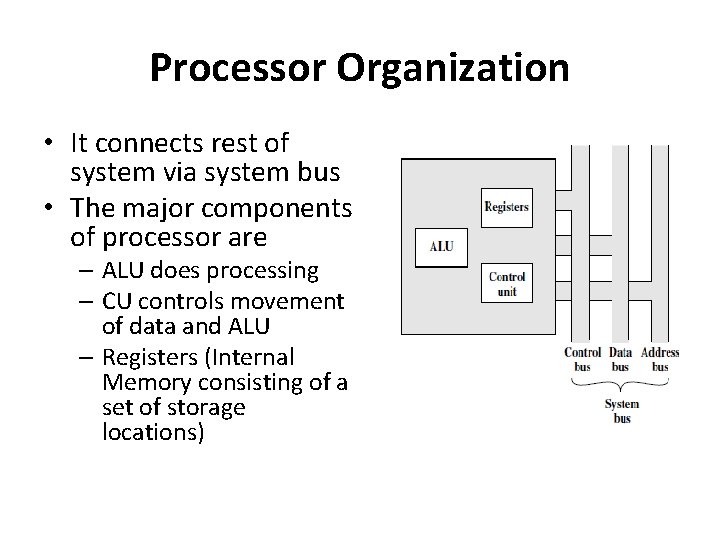

Processor Organization • It connects rest of system via system bus • The major components of processor are – ALU does processing – CU controls movement of data and ALU – Registers (Internal Memory consisting of a set of storage locations)

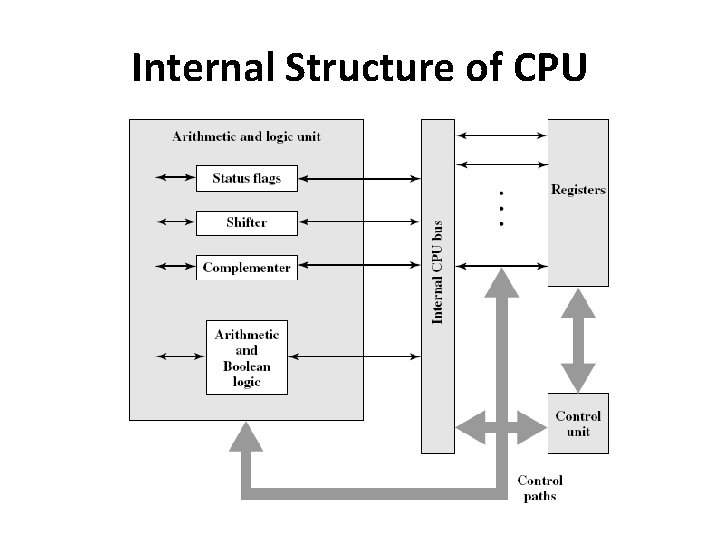

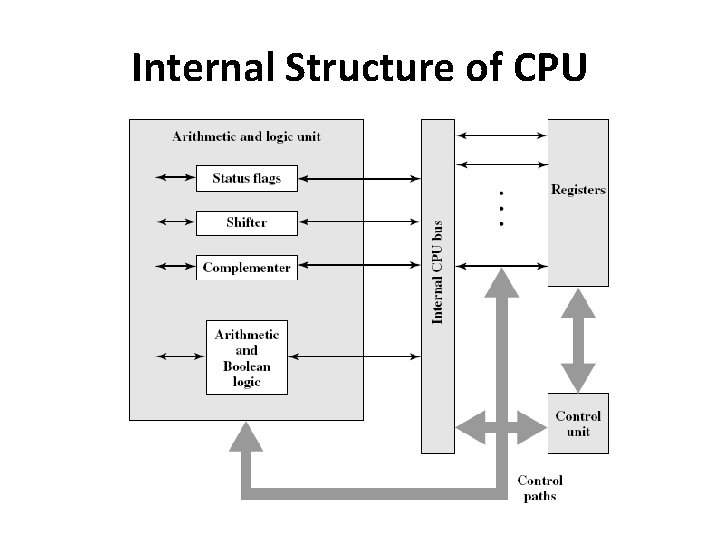

Internal Structure of CPU

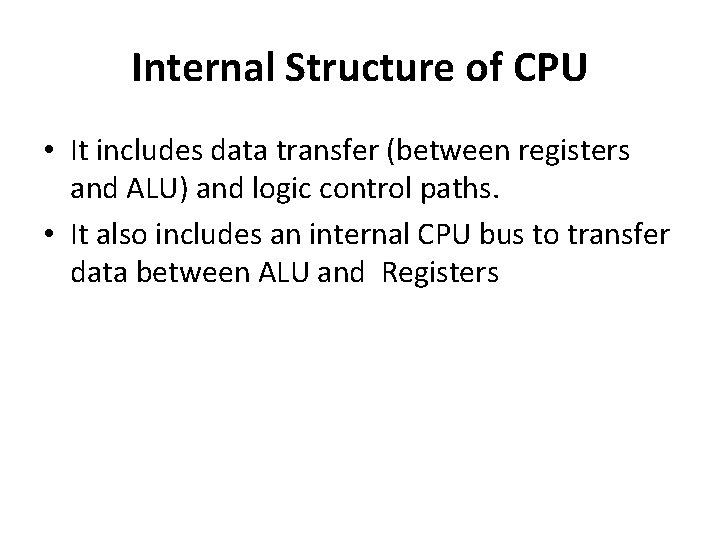

Internal Structure of CPU • It includes data transfer (between registers and ALU) and logic control paths. • It also includes an internal CPU bus to transfer data between ALU and Registers

Register Organization • The registers in the processor performs two roles: 1. User Visible Registers : – Minimize main memory references by optimizing use of registers 2. Control and Status Registers: – Used by control unit to control the operation of processor

User Visible Registers • Referenced by means of machine language • They are categorized as : – General Purpose – Data – Address – Condition Codes

General Purpose Registers • Contain operands • Can be used for addressing functions Data Registers • Used only to hold data

Address Registers • may be general purpose or • devoted to an addressing mode – Example: • Segment Pointers: holds base address of segment • Index Registers: for indexed addressing • Stack Pointer: points to the top of stack.

Condition Codes (Flags) • Bits set by the processor hardware as the result of operations • E. g. Carry, Overflow, Sign • They may be tested as part of conditional branch operation • Condition code bits are collected into one or more registers but the programmer cannot alter them.

Design Issues with Registers • Whether to use general purpose or specialized registers: – Specialized Register : Operand is specified implicit • E. g. PUSH and POP in Stack – Specialization limits programmer’s flexibility • No. of registers to be provided – More registers requires more operand specifier bits – Fewer will result in more memory references.

Design Issues with Registers • Issue of Register Length – Must be long enough to hold • the largest address and • most of the data types

Control and Status Registers • Control Registers : Four registers essential for instruction execution are – Program Counter – Instruction Register – Memory Address Register – Memory Buffer Register

Status Register • A register or set of registers that contain status information is called Program Status Word (PSW) • PSW contains condition codes and other status information • PSW contains : – Sign: Sign bit of last operation – Zero: Set when result is 0. – Carry: Set when a carry/borrow is generated /taken.

Status Register • PSW contains : – Overflow: When arithmetic overflow occurs – Interrupt Enable/Disable: Used to enable / disable interrupts – Supervisor: Indicates whether in supervisor/user mode. • Other registers are : interrupt vector register, system stack pointer

Addressing Modes • How to specify operands • The different modes are: – Immediate – Direct – Indirect – Register Indirect – Displacement (Indexed) – Stack

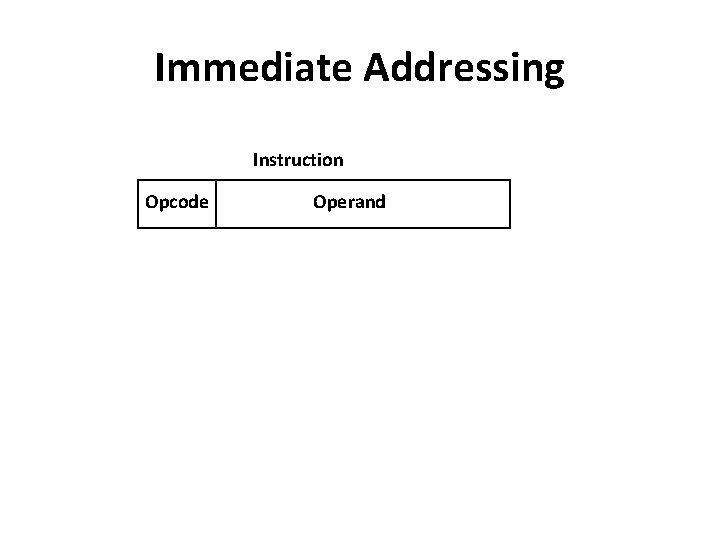

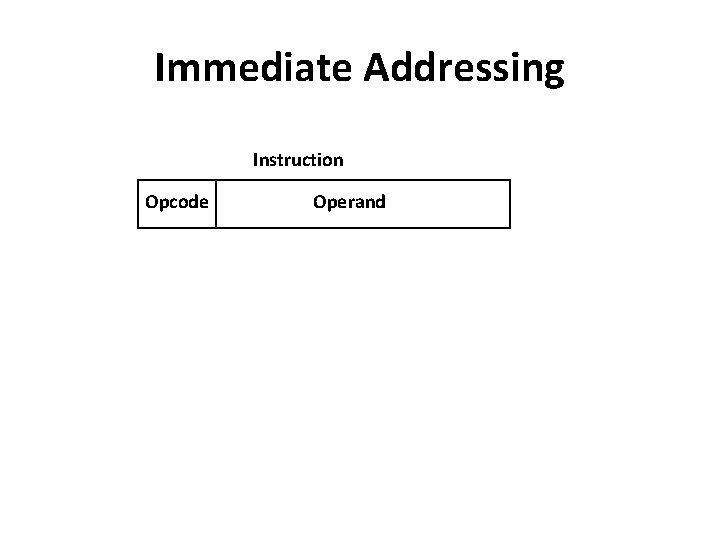

Immediate Addressing • Operand is part of instruction • e. g. ADD 5 – Add 5 to contents of accumulator – 5 is operand • Adv: – No memory reference to fetch data – Fast • Disadv: – Limited range

Immediate Addressing Instruction Opcode Operand

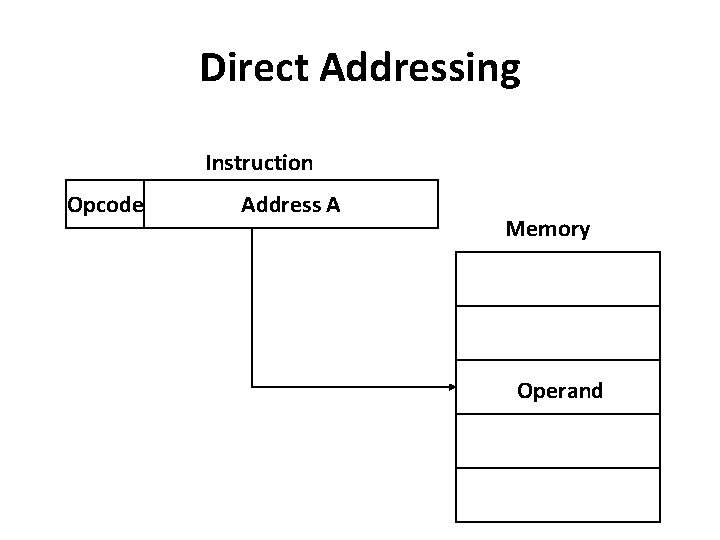

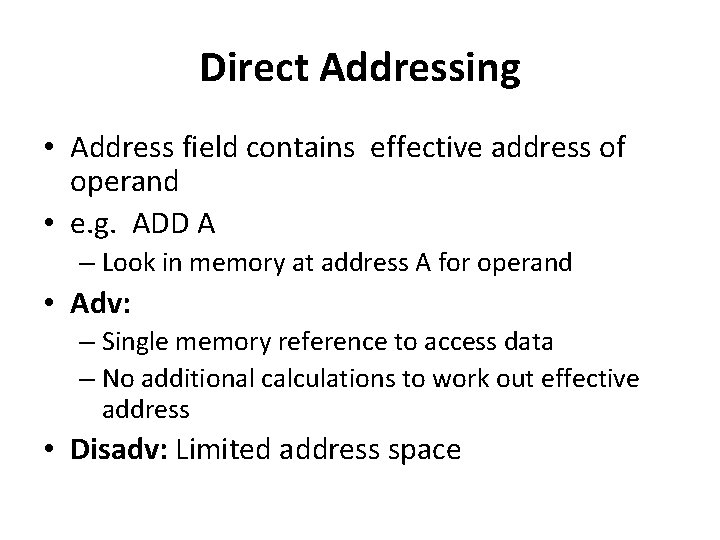

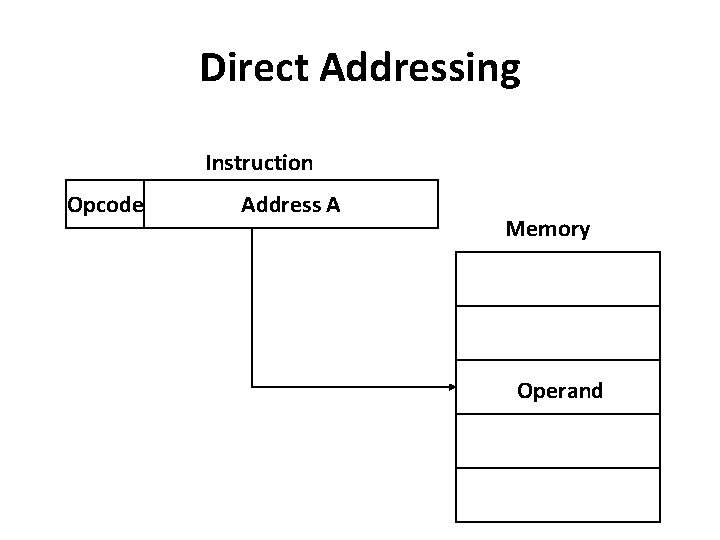

Direct Addressing • Address field contains effective address of operand • e. g. ADD A – Look in memory at address A for operand • Adv: – Single memory reference to access data – No additional calculations to work out effective address • Disadv: Limited address space

Direct Addressing Instruction Opcode Address A Memory Operand

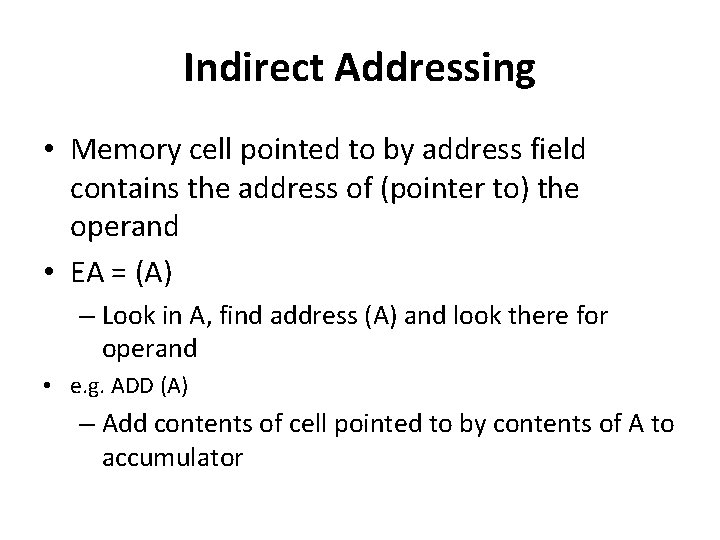

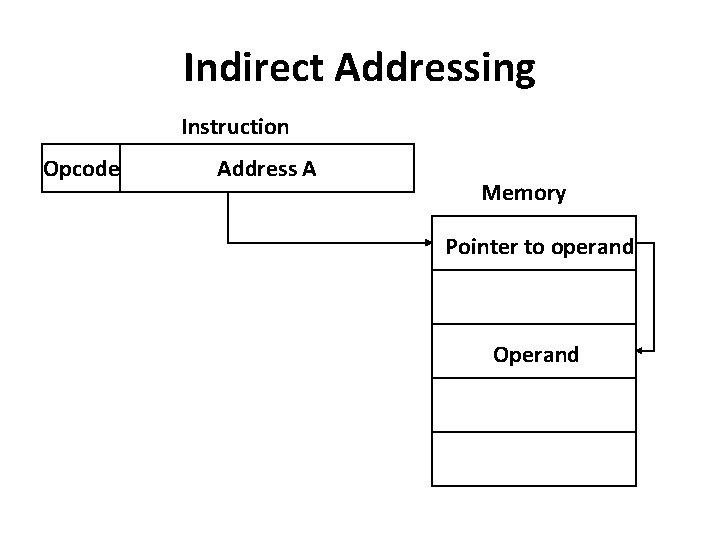

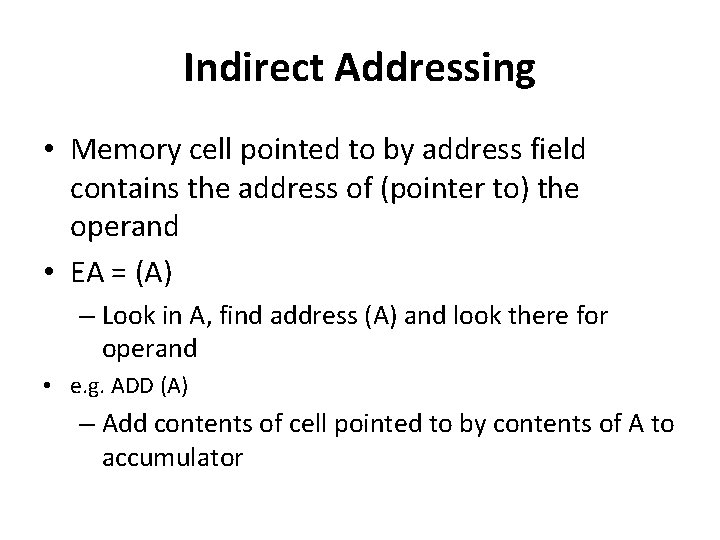

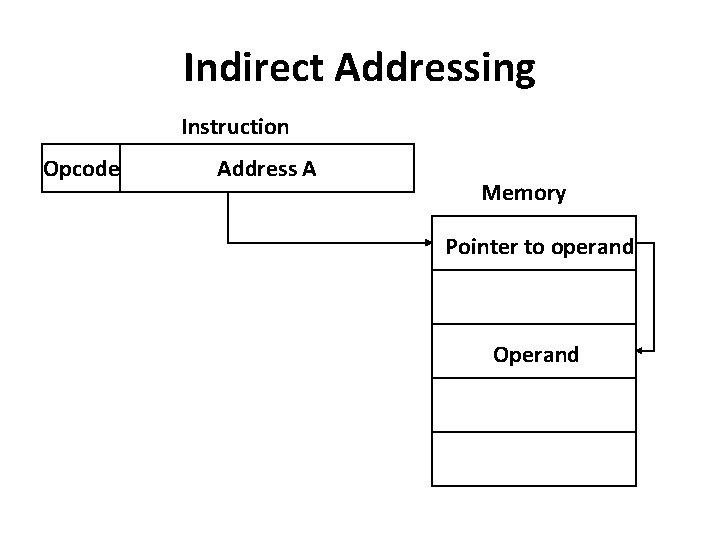

Indirect Addressing • Memory cell pointed to by address field contains the address of (pointer to) the operand • EA = (A) – Look in A, find address (A) and look there for operand • e. g. ADD (A) – Add contents of cell pointed to by contents of A to accumulator

Indirect Addressing Instruction Opcode Address A Memory Pointer to operand Operand

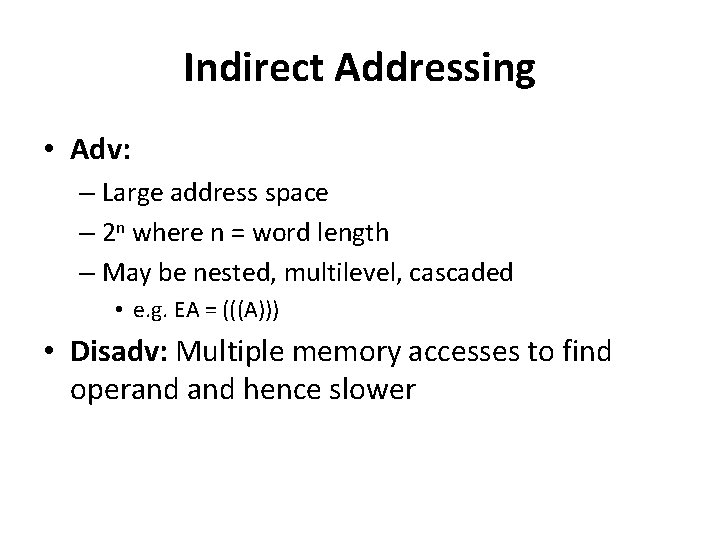

Indirect Addressing • Adv: – Large address space – 2 n where n = word length – May be nested, multilevel, cascaded • e. g. EA = (((A))) • Disadv: Multiple memory accesses to find operand hence slower

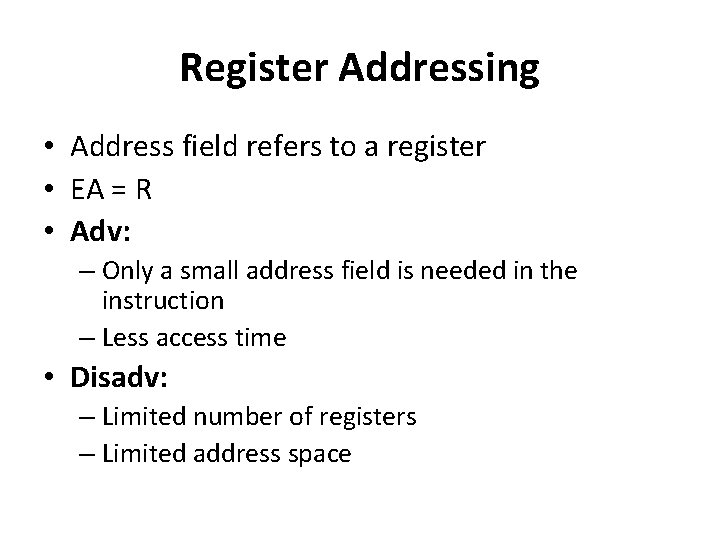

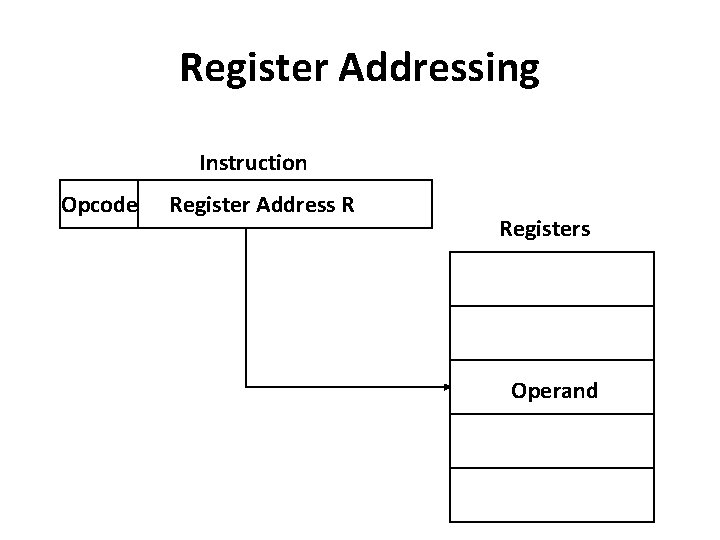

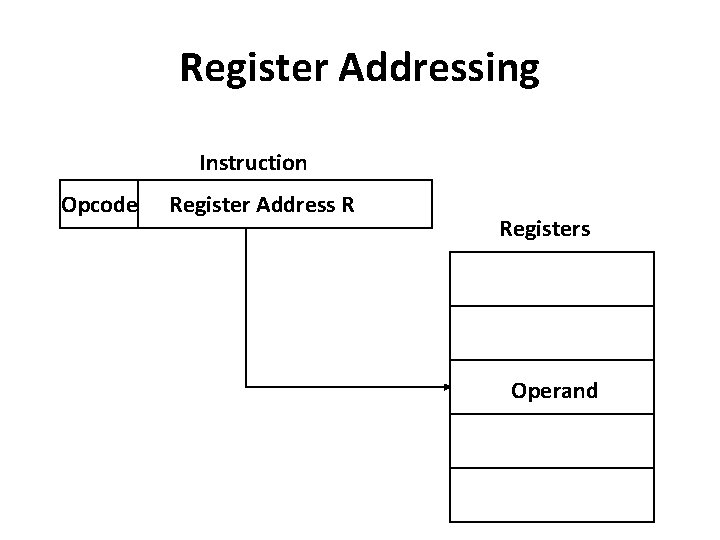

Register Addressing • Address field refers to a register • EA = R • Adv: – Only a small address field is needed in the instruction – Less access time • Disadv: – Limited number of registers – Limited address space

Register Addressing Instruction Opcode Register Address R Registers Operand

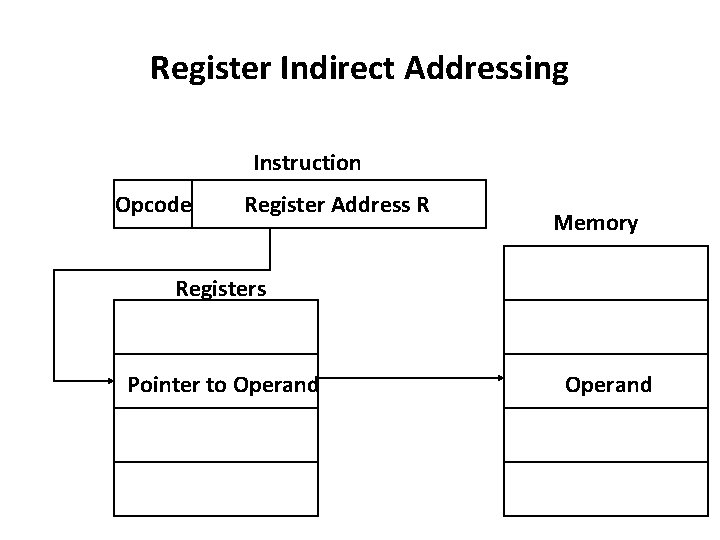

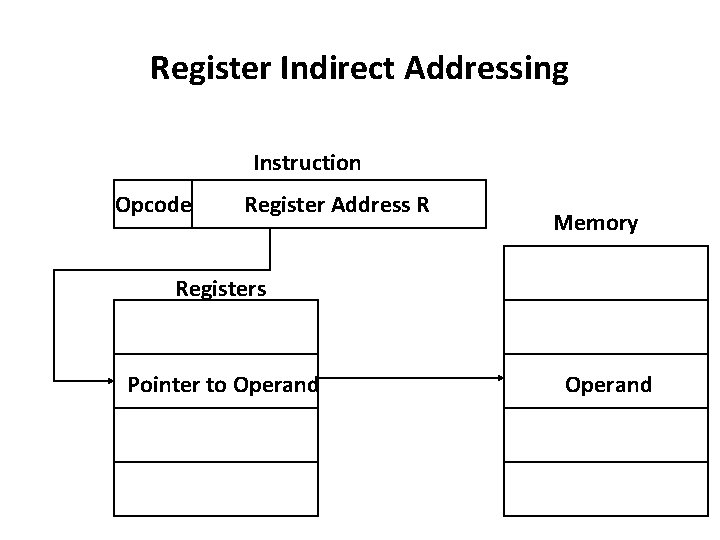

Register Indirect Addressing • Similar to indirect addressing • EA = (R) • Operand is in memory cell pointed to by contents of register R • One fewer memory access than indirect addressing

Register Indirect Addressing Instruction Opcode Register Address R Memory Registers Pointer to Operand

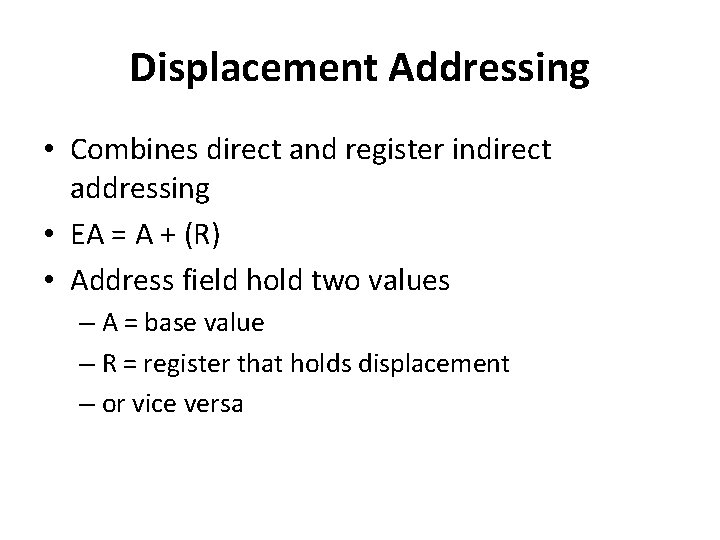

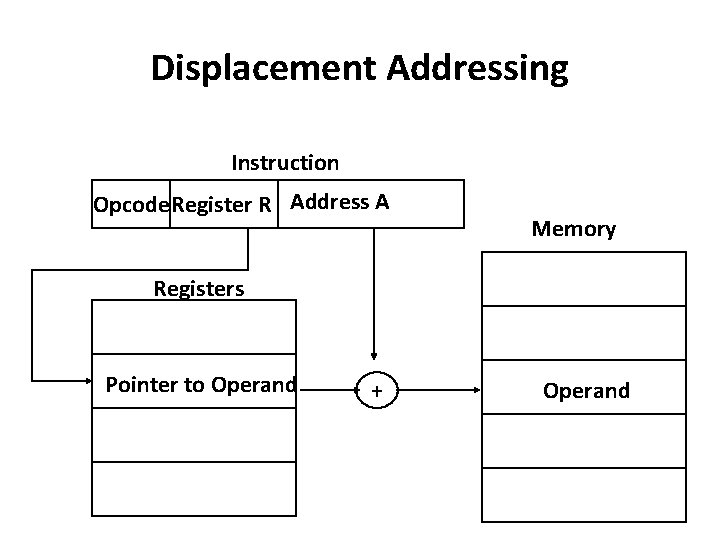

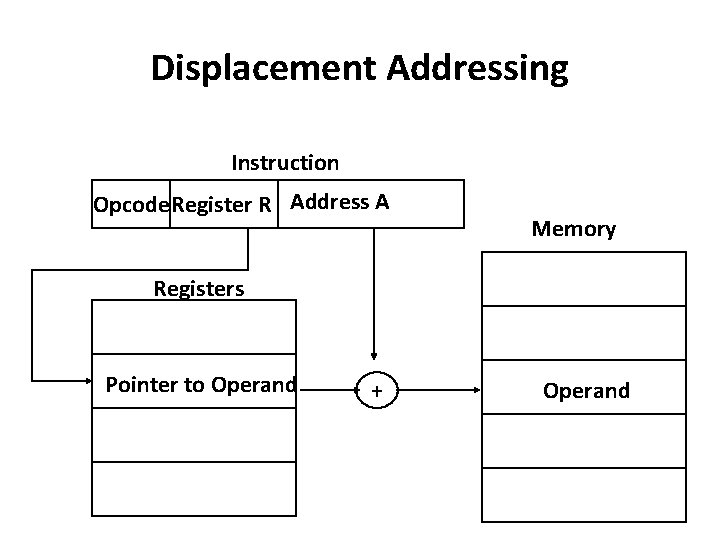

Displacement Addressing • Combines direct and register indirect addressing • EA = A + (R) • Address field hold two values – A = base value – R = register that holds displacement – or vice versa

Displacement Addressing Instruction Opcode Register R Address A Memory Registers Pointer to Operand + Operand

Stack Addressing • Stack is a reserved block of locations • Stack pointer holds the address of the top of the stack. • It is a form of implied addressing: as no memory reference is required but operate on the top of the stack