Module III Processor Organization and Architecture Microinstruction Execution

- Slides: 19

Module III Processor Organization and Architecture

Microinstruction Execution

Microinstruction Encoding • Microinstruction Encoding are of two types – Vertical – Horizontal

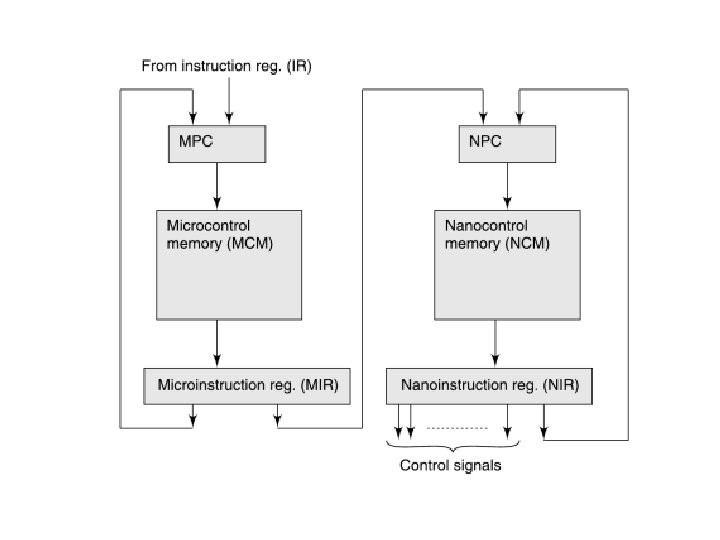

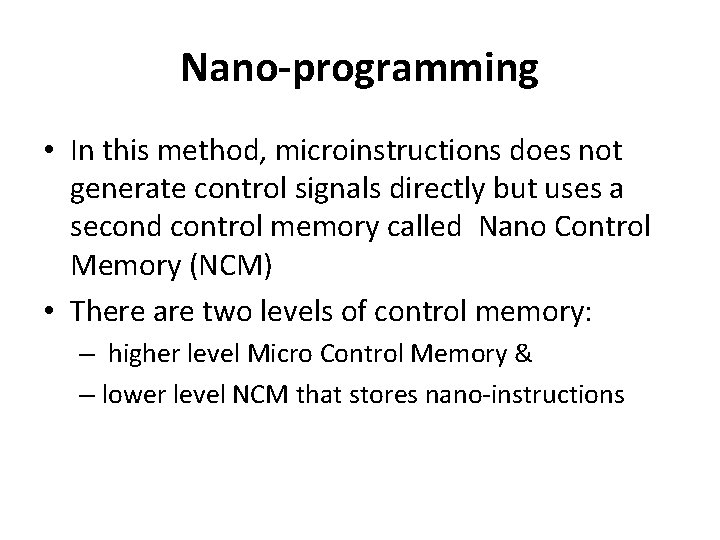

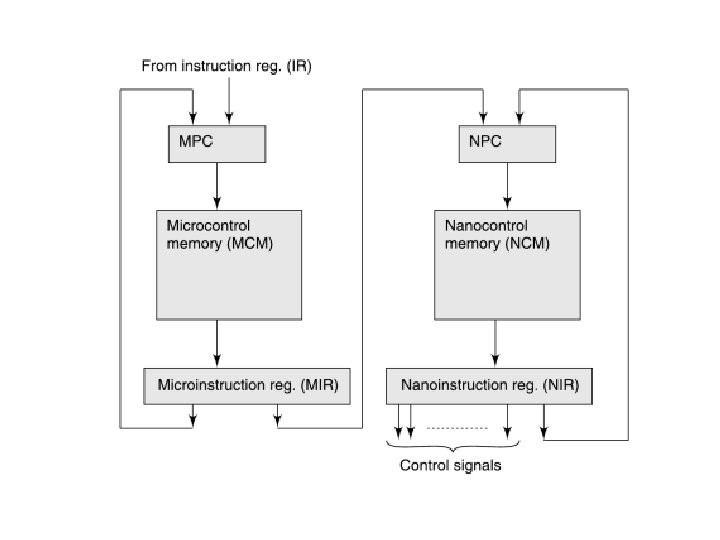

Nano-programming • In this method, microinstructions does not generate control signals directly but uses a second control memory called Nano Control Memory (NCM) • There are two levels of control memory: – higher level Micro Control Memory & – lower level NCM that stores nano-instructions

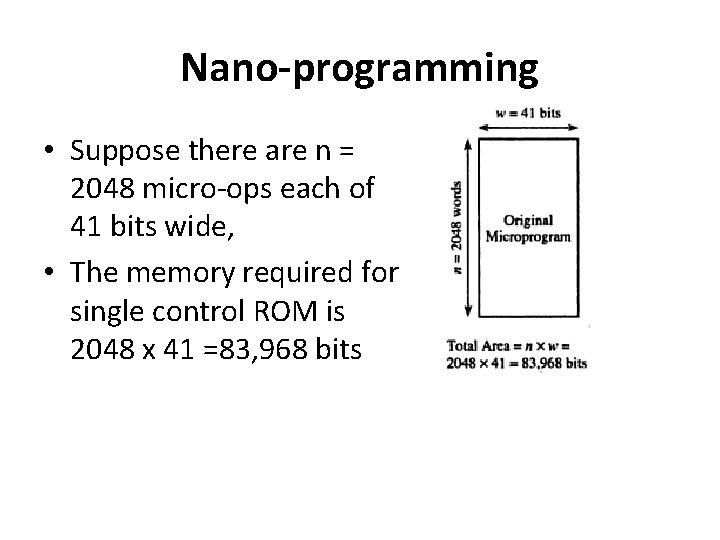

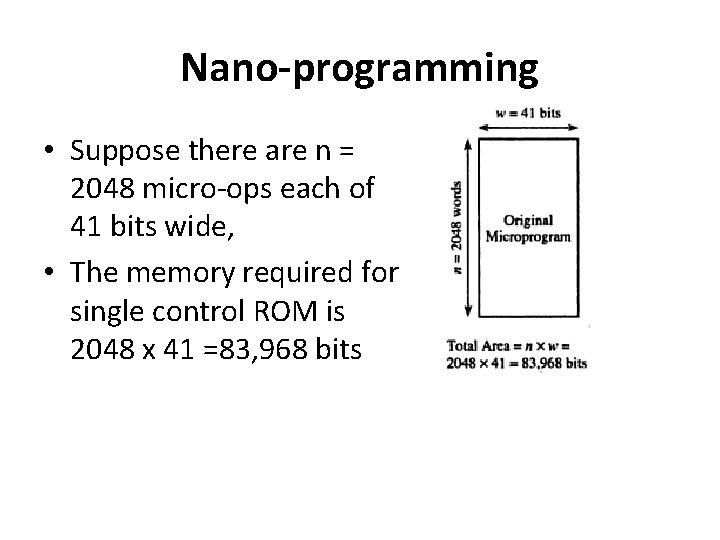

Nano-programming • Suppose there are n = 2048 micro-ops each of 41 bits wide, • The memory required for single control ROM is 2048 x 41 =83, 968 bits

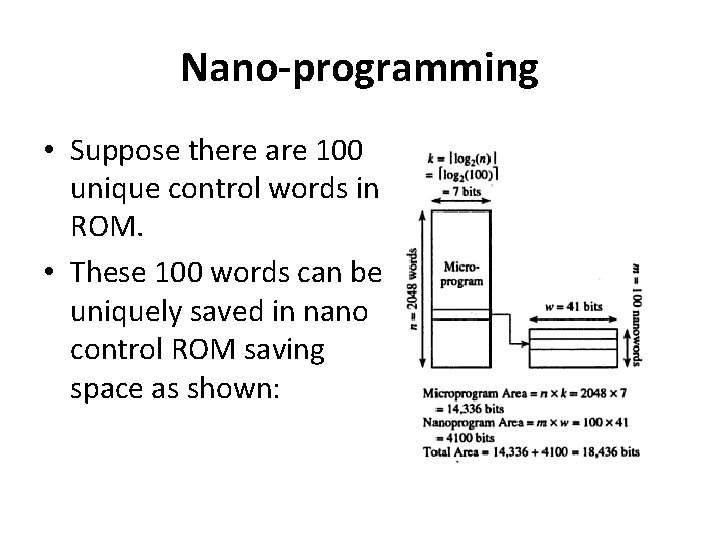

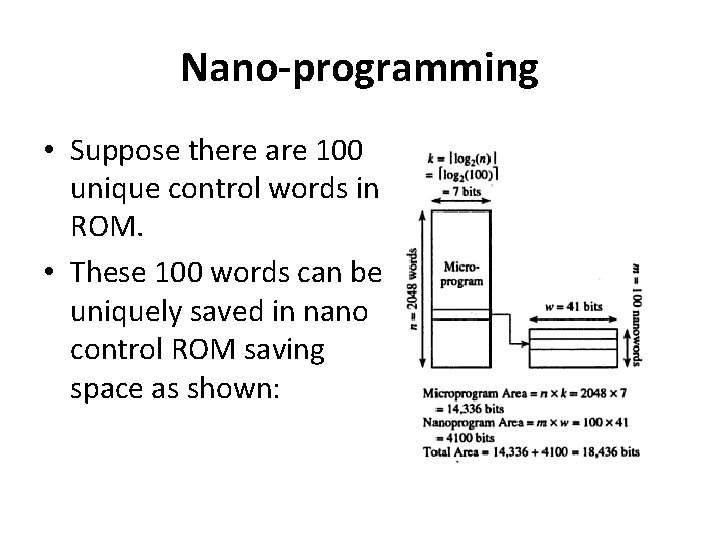

Nano-programming • Suppose there are 100 unique control words in ROM. • These 100 words can be uniquely saved in nano control ROM saving space as shown:

Nano-programming • Advantage: – Reduces total size of required control memory – Greater design flexibility • Disadvantage: – Less speed due to two level memory

Classification based on instruction sets • Complex Instruction Set Computers • Reduced Instruction Set Computers

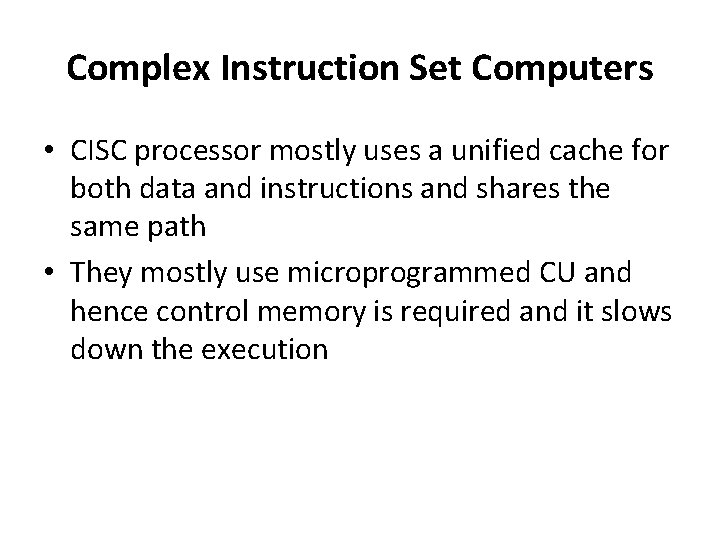

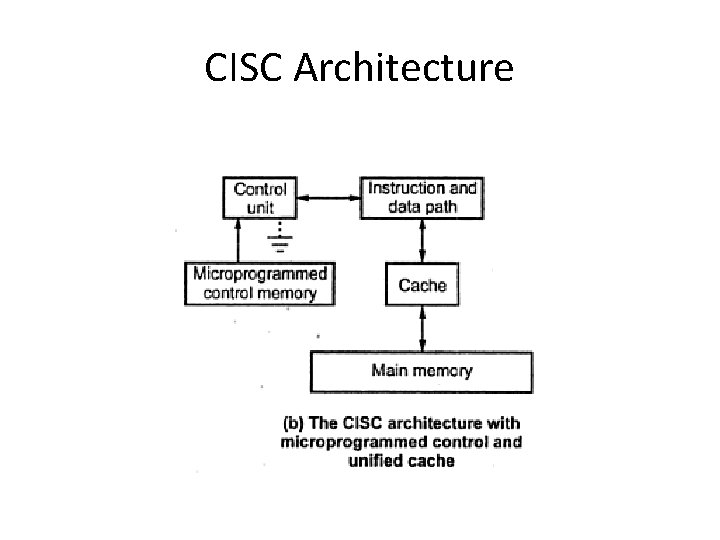

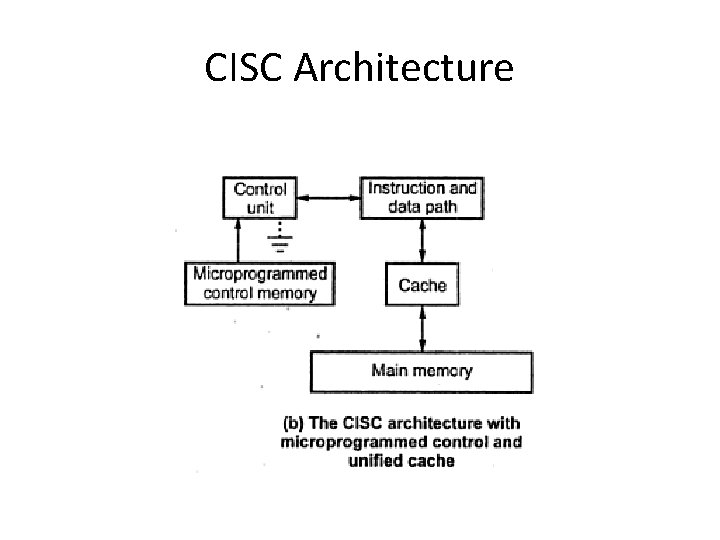

Complex Instruction Set Computers • CISC processor mostly uses a unified cache for both data and instructions and shares the same path • They mostly use microprogrammed CU and hence control memory is required and it slows down the execution

CISC Architecture

CISC Characteristics • It tries to simplify the compilation and improve the overall computer performance. – CISC architecture attempt to provide a single machine instruction for every statement in a highlevel language. • It incorporates variable-length instruction formats. – Packing variable instruction formats in memory requires special decoding circuits.

CISC Characteristics • Instructions manipulate operands in memory • Uses a variety of addressing modes—from 5 to 20 • Uses a large number of instructions—from 100 to 250 • Includes specialized instructions which are used infrequently • Examples : Motorola 68000 family, Intel x 86 CPUs-Pentium

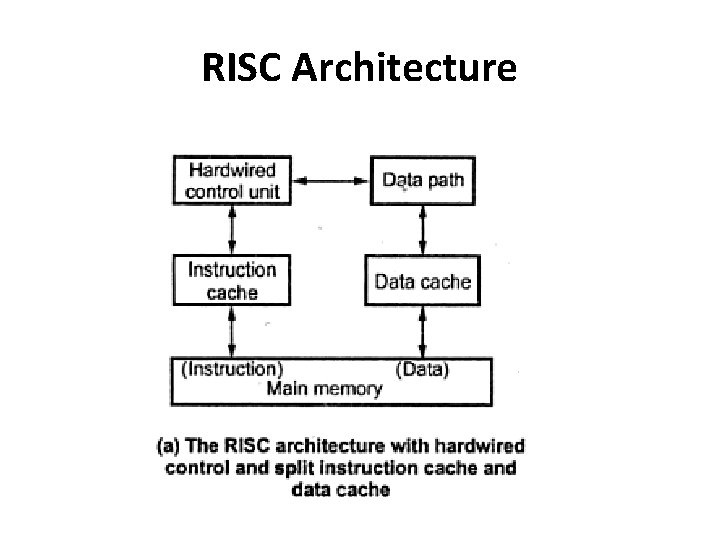

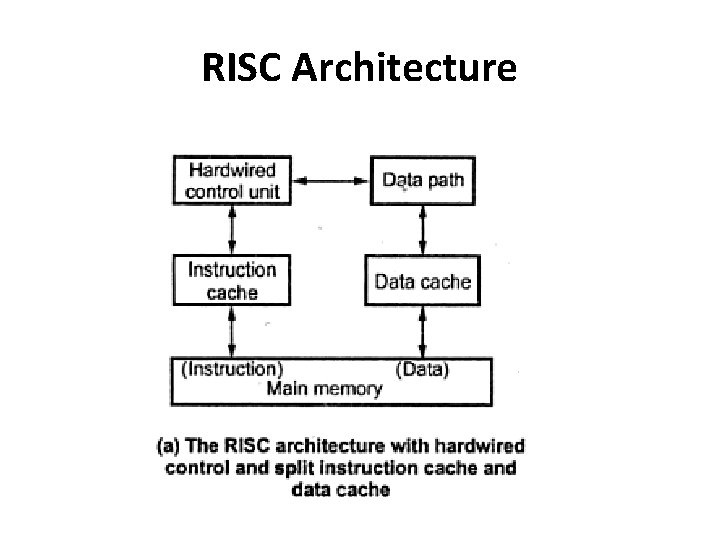

Reduced Instruction Set Computers • It uses separate instruction and data caches and their access paths are different • It uses hardwired control unit and hence faster execution.

RISC Architecture

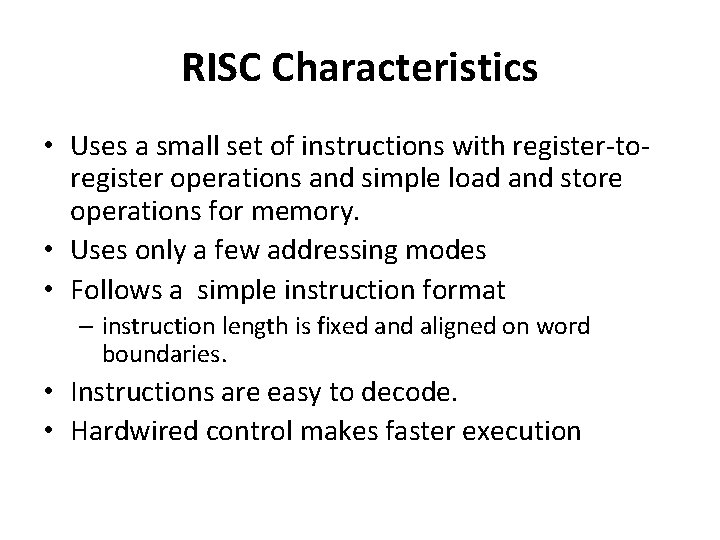

RISC Characteristics • Uses a small set of instructions with register-toregister operations and simple load and store operations for memory. • Uses only a few addressing modes • Follows a simple instruction format – instruction length is fixed and aligned on word boundaries. • Instructions are easy to decode. • Hardwired control makes faster execution

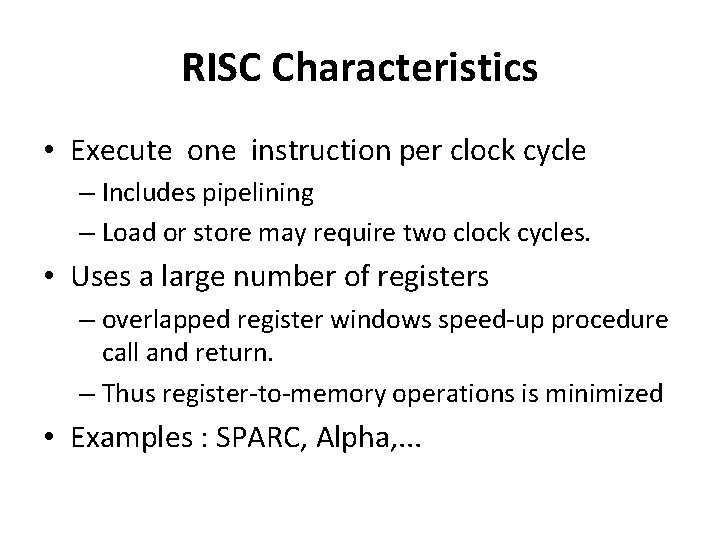

RISC Characteristics • Execute one instruction per clock cycle – Includes pipelining – Load or store may require two clock cycles. • Uses a large number of registers – overlapped register windows speed-up procedure call and return. – Thus register-to-memory operations is minimized • Examples : SPARC, Alpha, . . .

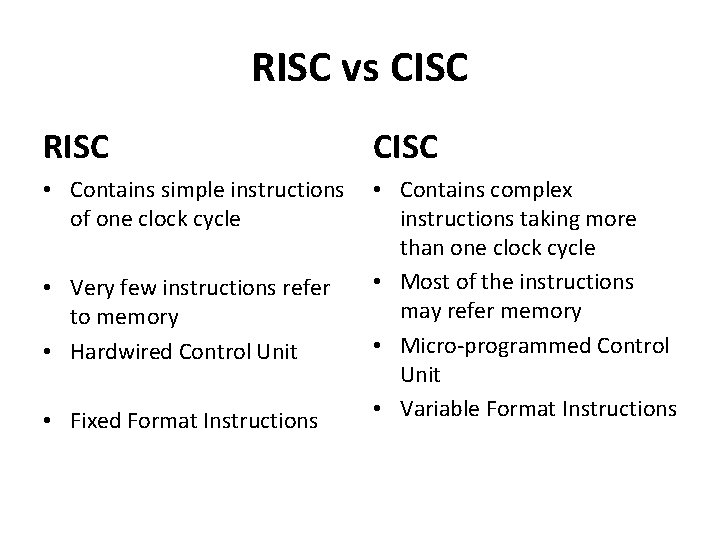

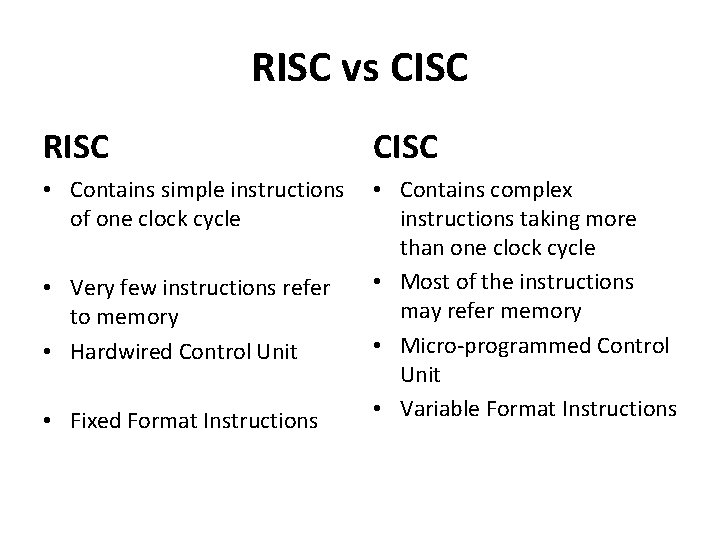

RISC vs CISC RISC CISC • Contains simple instructions of one clock cycle • Contains complex instructions taking more than one clock cycle • Most of the instructions may refer memory • Micro-programmed Control Unit • Variable Format Instructions • Very few instructions refer to memory • Hardwired Control Unit • Fixed Format Instructions

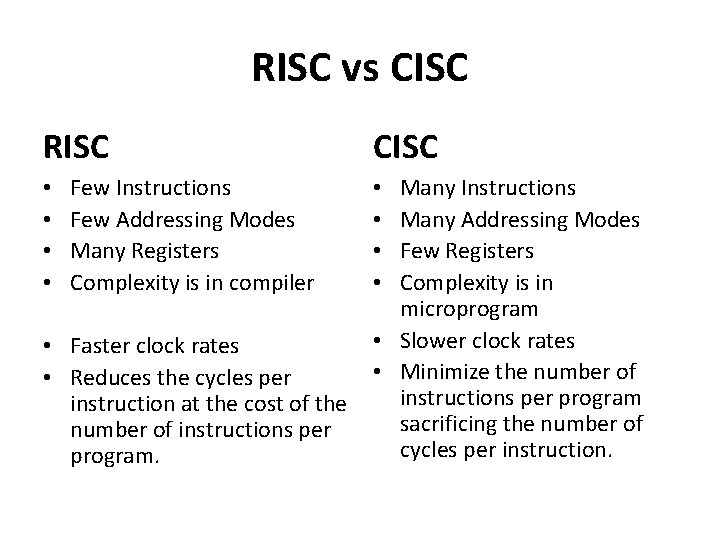

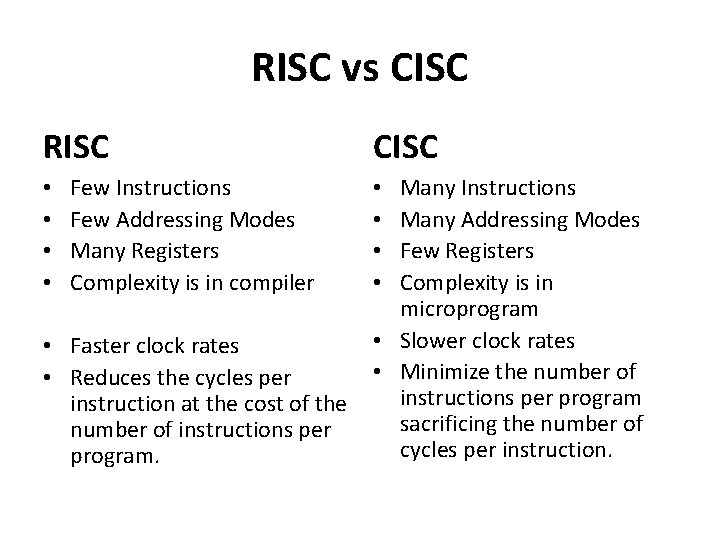

RISC vs CISC RISC • • Few Instructions Few Addressing Modes Many Registers Complexity is in compiler • Faster clock rates • Reduces the cycles per instruction at the cost of the number of instructions per program. CISC Many Instructions Many Addressing Modes Few Registers Complexity is in microprogram • Slower clock rates • Minimize the number of instructions per program sacrificing the number of cycles per instruction. • •