INTRODUCTION TO PENTIUM PROCESSOR ARCHITECTURE IA32 Pentium Processor

- Slides: 19

INTRODUCTION TO PENTIUM PROCESSOR ARCHITECTURE

IA-32 Pentium Processor l Is the processor introduced by Intel Corporation. l Now Intel processor is more known as Pentium Processor

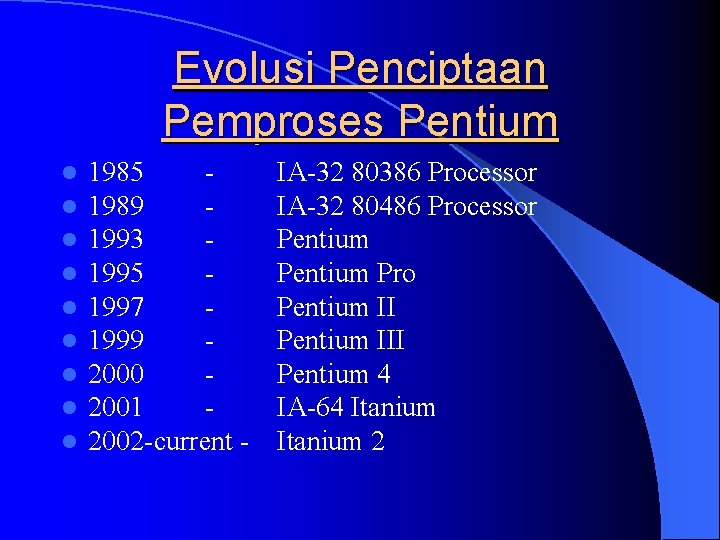

Evolusi Penciptaan Pemproses Pentium l l l l l 1985 1989 1993 1995 1997 1999 2000 2001 2002 -current - IA-32 80386 Processor IA-32 80486 Processor Pentium Pro Pentium III Pentium 4 IA-64 Itanium 2

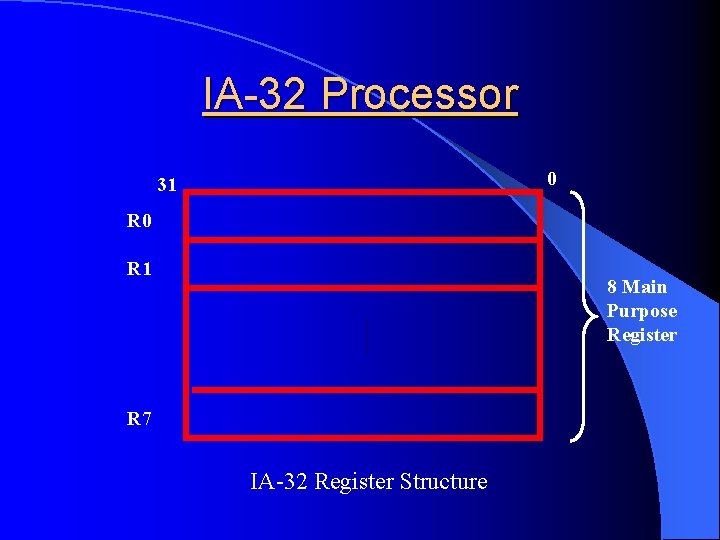

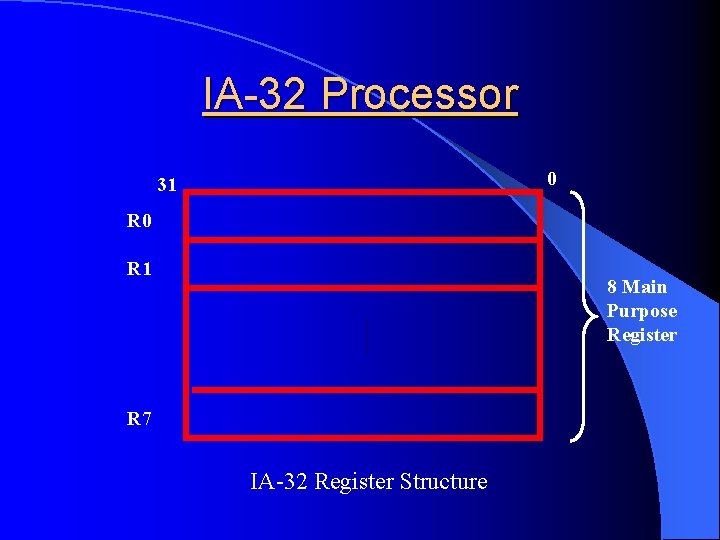

IA-32 Processor 0 31 R 0 R 1 8 Main Purpose Register R 7 IA-32 Register Structure

IA-32 Processor l Eight 32 -bit register mark with (R 0 – R 7) are general purpose register l It is used to hold operand data or addressing information

IA-32 Processor l Architecture based on memory model l Different area combination in memory is called segment

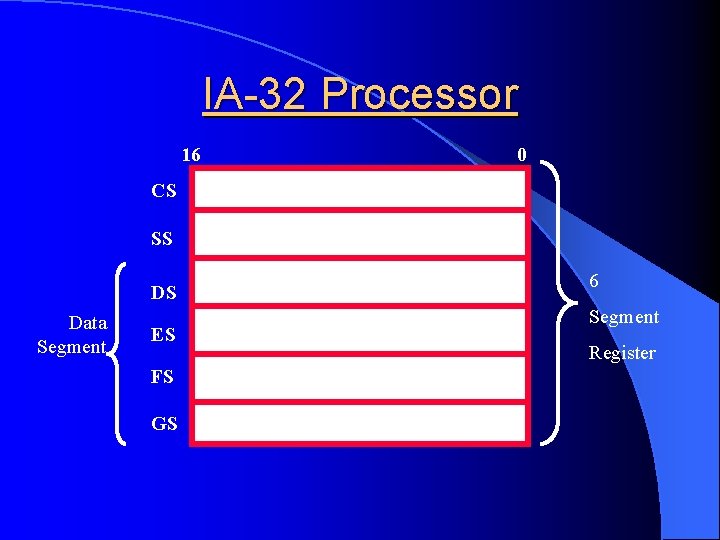

IA-32 Processor l Code Segment (CS) – Hold program instruction l Stack Segment (SS) – Contains processor stack l 4 Data Segment (DS) – To hold operand data

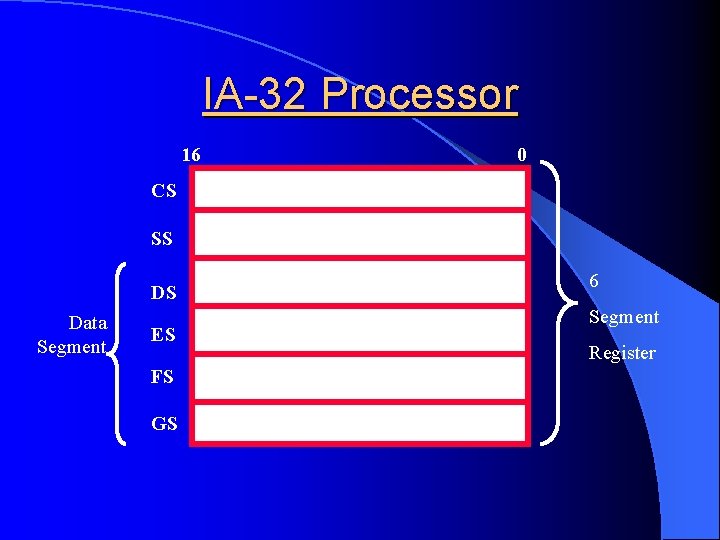

IA-32 Processor 16 0 CS SS DS Data Segment ES FS GS 6 Segment Register

IA-32 Processor l Processor used segment register CS, SS, DS and ES to fetch code, stack and two data segment

80386 and 80486 Processor l 80386 is the first processor which implement IA-32 architecture l 80486 contains integer processing unit and floating point l 80486 memory support is similar to 80386 l 80486 allows parallelism and pipelining

Pentium Processor l Upgraded 80486 l The power is twice 80486 l CISC architecture which achieved high performance by using RISC characteristic processor l Lets two instruction be executed in one clock cycle

Pentium Processor l Use simple dynamic branch prediction form l Select direction either to choose last branch executed l Maximum instruction number can be executed in one cycle is two

Pentium Processor l Increase superscalar and the ability to execute instrcution without sequential Superscalar factor, is also known as maximum instruction can be execute in one clock cycle is three in Pentium Processor

Pentium Processor l Superscalar operation is supported by many execution unit including for integer operation and floating point unit l Ability to execute instruction in different sequence with data stated in program is fetch from memory

Pentium Processor l Lets many instruction executed simultaneously l External bus which control the circuit lets Pentium Pro to be used in multiprocessor system

Pentium II and III Processor l Pentium II Processor add MMX instruction l MMX instruction prepare processor as parallel in multimedia operation towards pixel which describe graphical data

Pentium II and III Processor l Pentium III Processor introduce vector instruction (SIMD) l Is an instruction to process vector operation at floating point data

Pentium 4 Processor l Clock rate between 1. 3 to 1. 5 GHz l IA-32 instruction set fully supported including MMX and SSE instruction l Cache instruction to hold path segment execution, decoded instruction known as trace

Pentium 4 Processor l Trace can be more than one branch in original program l If the path is repeated, execution will be much faster l Test will be done to ensure that the same branch is fetched when trace is repeated