Basic Microprocessor Architecture 8086 Internal Architecture IA32 Registers

Basic Microprocessor Architecture

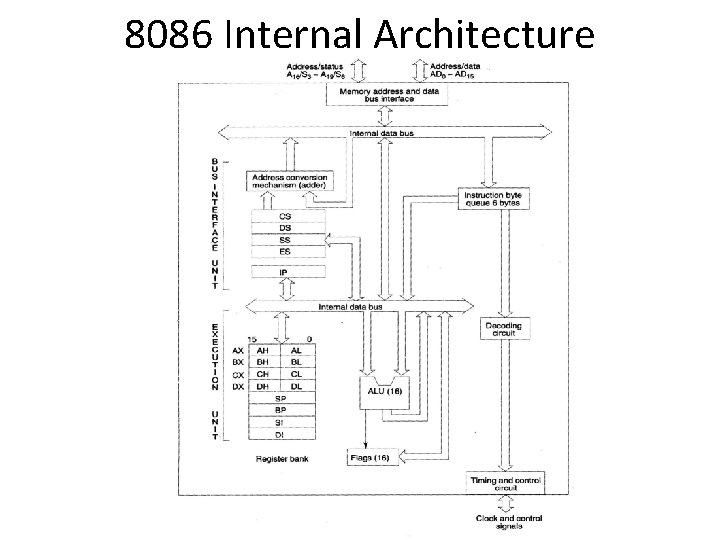

8086 Internal Architecture

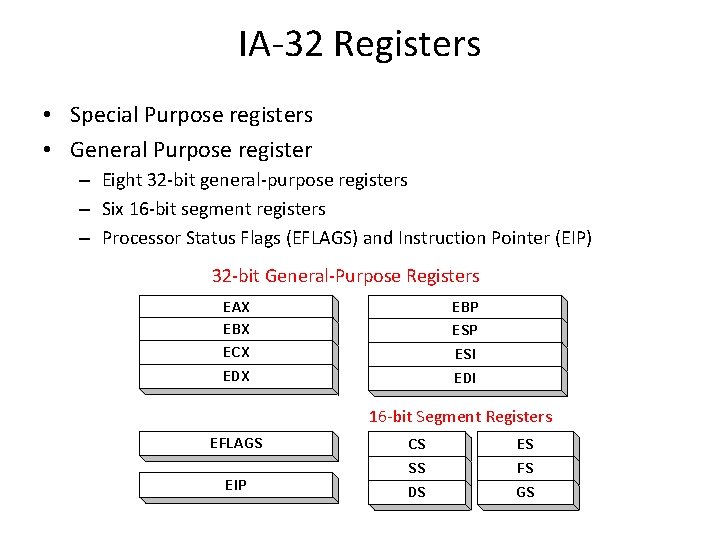

IA-32 Registers • Special Purpose registers • General Purpose register – Eight 32 -bit general-purpose registers – Six 16 -bit segment registers – Processor Status Flags (EFLAGS) and Instruction Pointer (EIP) 32 -bit General-Purpose Registers EAX EBP EBX ESP ECX ESI EDX EDI 16 -bit Segment Registers EFLAGS EIP CS ES SS FS DS GS

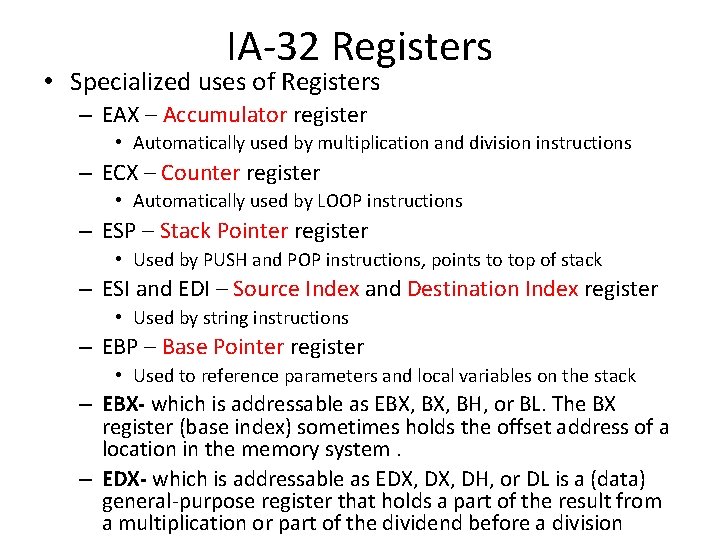

IA-32 Registers • Specialized uses of Registers – EAX – Accumulator register • Automatically used by multiplication and division instructions – ECX – Counter register • Automatically used by LOOP instructions – ESP – Stack Pointer register • Used by PUSH and POP instructions, points to top of stack – ESI and EDI – Source Index and Destination Index register • Used by string instructions – EBP – Base Pointer register • Used to reference parameters and local variables on the stack – EBX- which is addressable as EBX, BH, or BL. The BX register (base index) sometimes holds the offset address of a location in the memory system. – EDX- which is addressable as EDX, DH, or DL is a (data) general-purpose register that holds a part of the result from a multiplication or part of the dividend before a division

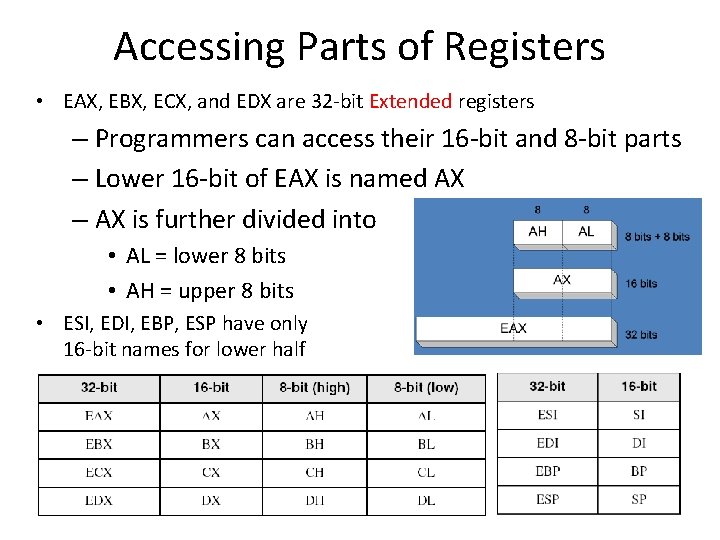

Accessing Parts of Registers • EAX, EBX, ECX, and EDX are 32 -bit Extended registers – Programmers can access their 16 -bit and 8 -bit parts – Lower 16 -bit of EAX is named AX – AX is further divided into • AL = lower 8 bits • AH = upper 8 bits • ESI, EDI, EBP, ESP have only 16 -bit names for lower half

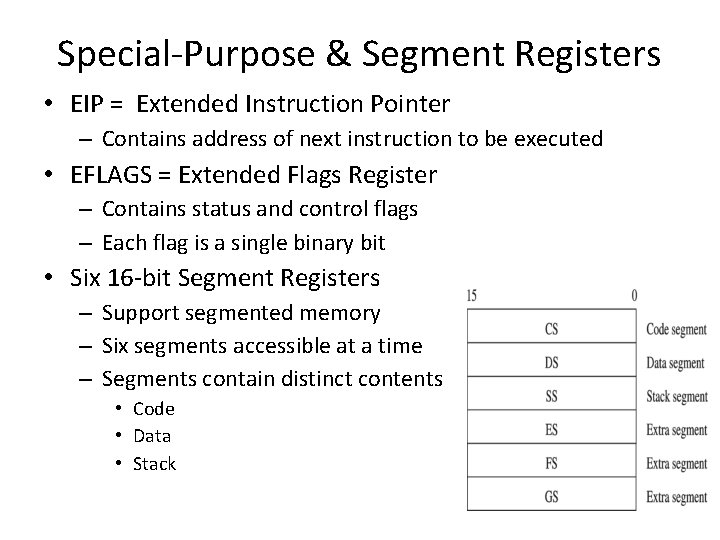

Special-Purpose & Segment Registers • EIP = Extended Instruction Pointer – Contains address of next instruction to be executed • EFLAGS = Extended Flags Register – Contains status and control flags – Each flag is a single binary bit • Six 16 -bit Segment Registers – Support segmented memory – Six segments accessible at a time – Segments contain distinct contents • Code • Data • Stack

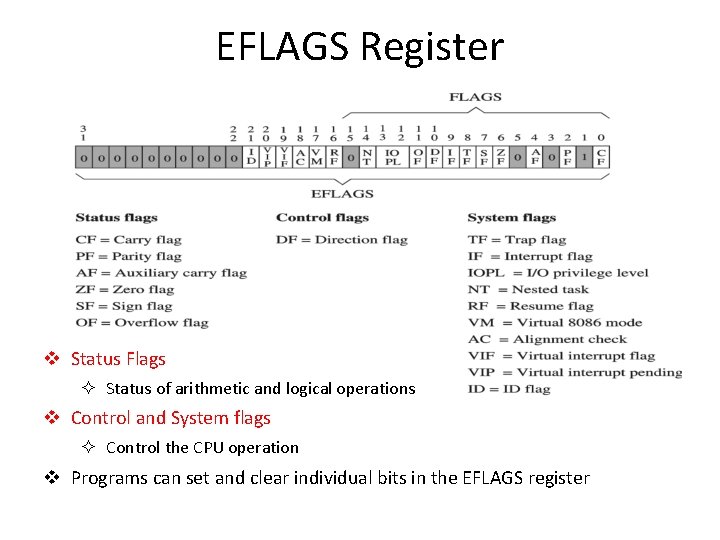

EFLAGS Register v Status Flags ² Status of arithmetic and logical operations v Control and System flags ² Control the CPU operation v Programs can set and clear individual bits in the EFLAGS register

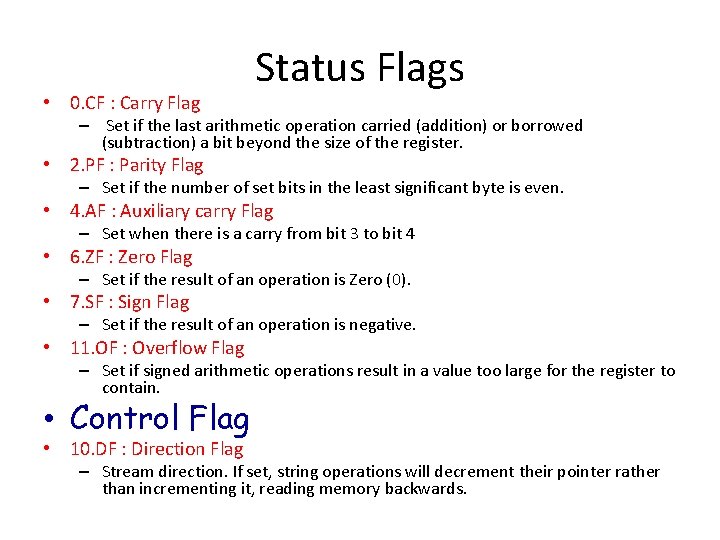

• 0. CF : Carry Flag Status Flags – Set if the last arithmetic operation carried (addition) or borrowed (subtraction) a bit beyond the size of the register. • 2. PF : Parity Flag – Set if the number of set bits in the least significant byte is even. • 4. AF : Auxiliary carry Flag – Set when there is a carry from bit 3 to bit 4 • 6. ZF : Zero Flag – Set if the result of an operation is Zero (0). • 7. SF : Sign Flag – Set if the result of an operation is negative. • 11. OF : Overflow Flag – Set if signed arithmetic operations result in a value too large for the register to contain. • Control Flag • 10. DF : Direction Flag – Stream direction. If set, string operations will decrement their pointer rather than incrementing it, reading memory backwards.

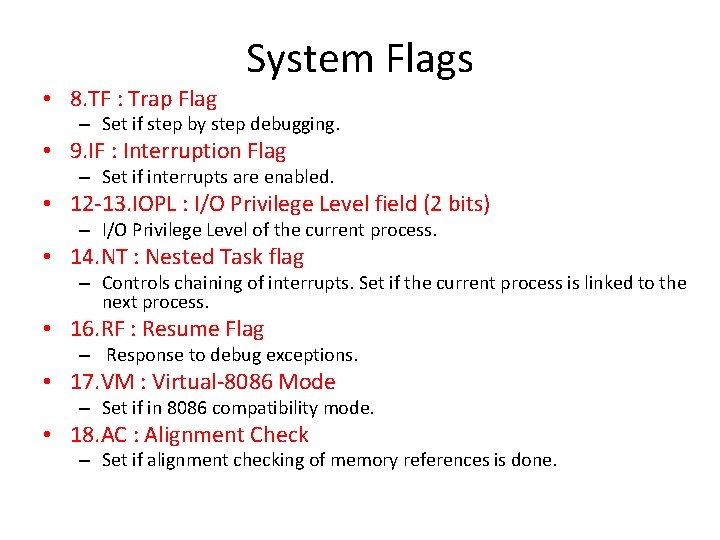

• 8. TF : Trap Flag System Flags – Set if step by step debugging. • 9. IF : Interruption Flag – Set if interrupts are enabled. • 12 -13. IOPL : I/O Privilege Level field (2 bits) – I/O Privilege Level of the current process. • 14. NT : Nested Task flag – Controls chaining of interrupts. Set if the current process is linked to the next process. • 16. RF : Resume Flag – Response to debug exceptions. • 17. VM : Virtual-8086 Mode – Set if in 8086 compatibility mode. • 18. AC : Alignment Check – Set if alignment checking of memory references is done.

System Flags • 19. VIF : Virtual Interrupt Flag – Virtual image of IF. • 20. VIP : Virtual Interrupt Pending flag – Set if an interrupt is pending. • 21. ID : Identification Flag – Support for CPUID instruction if can be set.

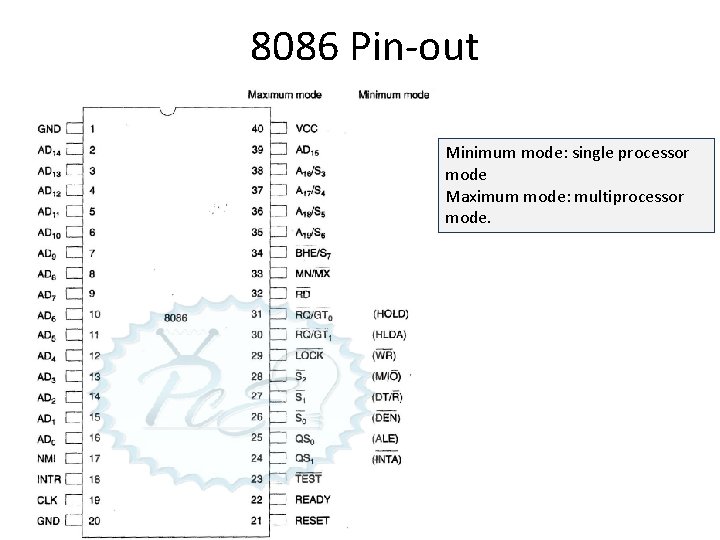

8086 Pin-out Minimum mode: single processor mode Maximum mode: multiprocessor mode.

Pin Description • AD 15 –AD 0: The time multiplexed memory I/O address and data lines • A 19/S 6–A 16/S 3: The address/status bits are multiplexed to provide address signals A 19–A 16 and also status bits S 6–S 3 • RD: Read signal, when low, indicates that the processor is performing a memory or I/O read operation • READY: This is the acknowledgement from the slow devices or memory that they have completed the data transfer • INTR: Interrupt request is used to request a hardware interrupt • NMI : The non-maskable interrupt input is similar to INTR except that the NMI interrupt does not check to see whether the IF flag bit is a logic 1

Pin Description • VCC: This power supply input provides a +5. 0 V • GND: The ground connection is the return for the power supply • CLK: The clock pin provides the basic timing signal to the microprocessor • MN/MX: The minimum/maximum mode pin selects either minimum mode or maximum mode operation for the microprocessor • WR: The write line indicates that the processor is outputting data to a memory or I/O device • M/IO: Selects memory or I/O

- Slides: 13