Intel Pentium II Processor Brent Perry Pat Reagan

Intel Pentium II Processor Brent Perry Pat Reagan Brian Davis Umesh Vemuri

Pentium II Topics • Speed and Performance • Registers • Instruction Set • Factors Affecting Performance • Future of the PII

Overview of Intel Pentium II Microprocessor Speed 1997 - Introduction of the Pentium II Microprocessor • 233 Mhz, 266 Mhz, 300 Mhz • 0. 35 Micron Chip • Based on the 440 LX Chip Set 1998 - Expansion of the Pentium II Microprocessor Family • 333 Mhz, 350 Mhz, 400 Mhz, 450 Mhz • 0. 25 Micron Chip • Based on the 440 BX Chip Set

The Advantage of 0. 25 Micron Technology Increased Processor Speeds by 60% • Lowered of voltage across the processor • Doubled the Density of the 0. 35 Micron Chip • More transistors per chip The Advantage of the 440 BX Chip Set One basic motherboard design: • Supported all Pentium II processor speeds of 233 MHz and higher • Supported both 100 -MHz or 66 -MHz system and memory bus designs.

Pentium II Registers • 16 registers grouped as: – general-purpose registers - 8 registers for operands and pointers – segment registers - hold pointers to specific segments in memory – status and control registers - allow change of state of CPU processing

General Purpose Registers • • EAX - accumulator for results data and operands EBX - pointer for accessing data in DS segment ECX - counter for loop and string operations EDX - Input/Output pointer ESI - source pointer for string operations EDI - destination pointer for string operations EBP - pointer to data on stack pointed to by SS segment ESP - stack pointer(use for other purposes can cause unforeseen complications)

Segment Registers • 16 -bit registers that hold pointers called segment selectors that point to specific segments in memory • These segment registers are called CS, DS, SS, ES, FS, and GS

Segment Registers (con’t) • DS, ES, FS and GS segments point to 4 reserved data segments in memory • CS register is the register for the code segment • SS register is a register that points to a stack segment where procedure stack for executing tasks is stored

EFLAGS Register • Composed of: – set of system flags – set of status flags – a control flag • Bits 1, 3, 5, 15, and 21 -31 are reserved for non-software level access

EFLAGS Register (con’t) • Vital to multi-tasking or task switching operations – EFLAGS register contents saved to the task status segment when suspending or switching from a task – EFLAGS register loaded with task status segment when reactivating or switching to a task

Pentium II Instruction Set • Can be simplified into three major groups: – Integer Instructions – MMX Instructions – Floating Point Instructions

Integer Instructions • perform the integer arithmetic, logic, and program flow control operations necessary for application programmers These instructions can further be broken down into: data transfer binary arithmetic decimal arithmetic logic shift and rotate bit and byte control transfer string, flag control segment register

MMX Instruction Set • New instructions added with creation of late P 5 model and Pentium II processors • utilized by multimedia applications providing enhanced performance • Consists of these sub-categories: – MMX data transfer, MMX conversion, MMX packed arithmetic, MMX comparison, MMX logic, MMX shift and rotate, and MMX state management

Floating Point Instructions • Executed by CPU’s Floating Point Unit (FPU) • operate on floating-point, extended integer, and binary-coded decimal (BCD) operands • Consists of these sub-categories: – data transfer, basic arithmetic, comparison, transcendental, load constants, and FPU control

Factors Affecting Performance • Three-way Superscalar Architecture • Pipelining Architecture • Dynamic Execution

Superscalar Architecture • Parallel Processing – Decoding – Dispatching – Retiring • Implemented through a pipelined architecture

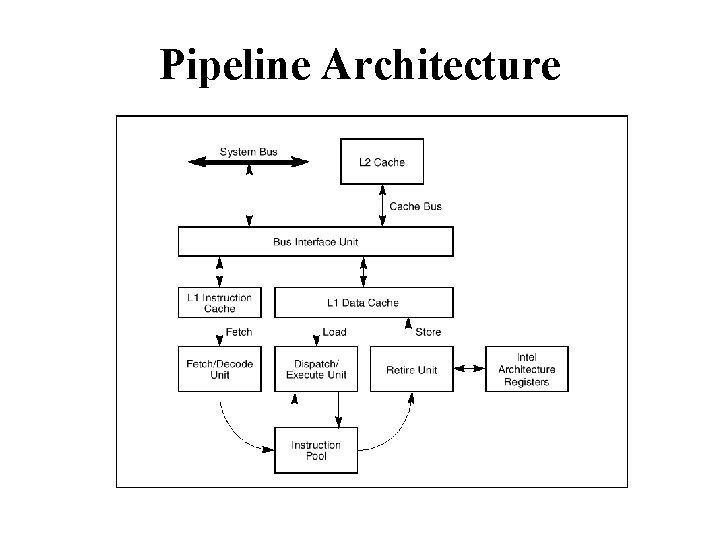

Pipeline Architecture • 12 stages that support execution out of order • 4 components – Fetch/Decode Unit – Dispatch/Execute Unit – Retire Unit – Instruction Pool

Pipeline Architecture

Dynamic Execution • Consists of three facets: – Branch Prediction – Dynamic Data Flow Analysis – Speculative Execution • Keeps Pipeline full and improves performance

Branch Prediction • Keeps processing pipeline full • Decoding of instructions beyond the current instruction set • Follows instruction through calls and returns

Dynamic Data Flow Analysis • Instruction execution out of order • Analysis of registers in processor • Performed by the dispatch/execute unit

Speculative Execution • Ties two previous facets together • Maintains the integrity of instructions • Instructions are committed in the correct order

The Future of Pentium II Microprocessor First quarter of 1999 • Introduction of a processor code named "Katmai” targeted at the desktop market segment • 450 Mhz, 500 MHz Mid to Late-1999 • 600 Mhz “Coppermine” Pentium II chip - will scale up towards 800 Mhz with. 18 micron process • 700 Mhz Pentium II Xeon chip - designed for demanding server use

- Slides: 23