Mega Meet 2007 April 17 2003 Mega Squirt

- Slides: 53

Mega. Meet 2007 April 17, 2003 Mega. Squirt and Mega. Squirt Logo are trademarks of BG Soflex, LLC.

CAN Controller Area Network Bowling & Grippo April 17, 2003 Mega. Squirt and Mega. Squirt Logo are trademarks of BG Soflex, LLC.

Quick CAN Overview April 17, 2003 Mega. Squirt and Mega. Squirt Logo are trademarks of BG Soflex, LLC.

Understanding CAN Ø Simple Serial Communications Protocol Ø Variable Bit Rate: 5 Kbps up to 1 Mbps Ø Un-limited node (limited to max. Electric load and time delay) Ø Multi-Master (any node may initiate transmit any frame) Ø Multi-cast (any node may receive all messages) Ø CSMA/CD standard (Carrier Sense, Multiple Access & Collision Detect) Ø Prioritization of messages via identifier Ø Fault confinement (determine permanent failures then shut off node) Ø Automatic re-transmission of corrupted message 5Ø High level of error detection

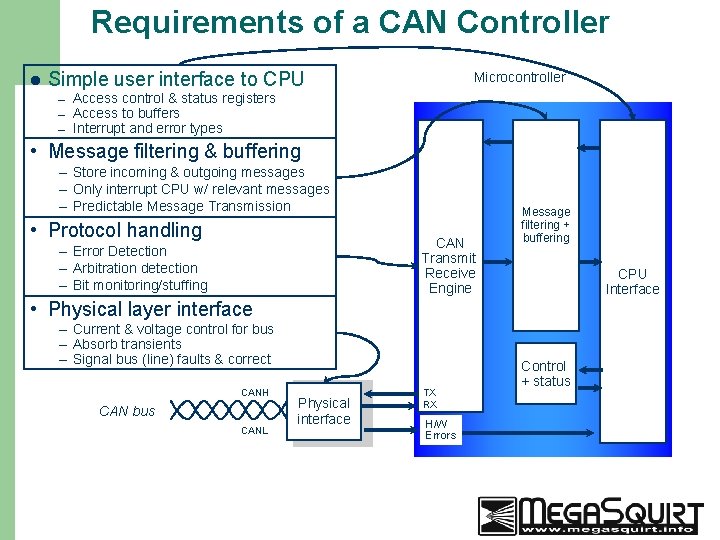

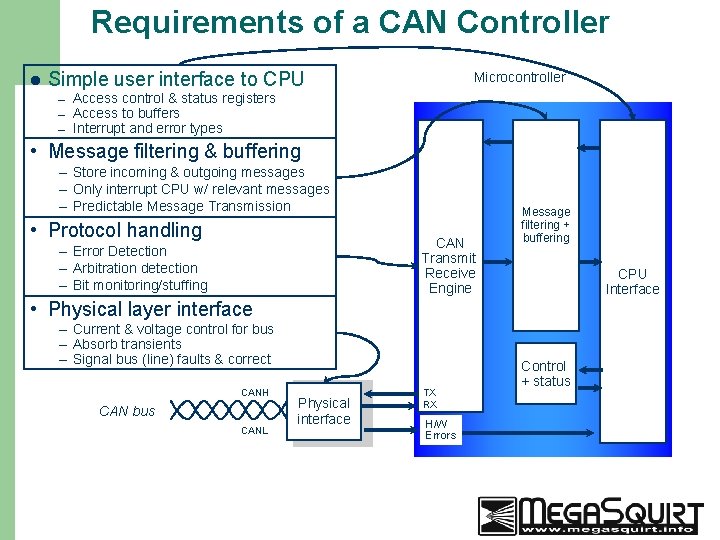

Requirements of a CAN Controller l Simple user interface to CPU – – – Microcontroller Access control & status registers Access to buffers Interrupt and error types • Message filtering & buffering – Store incoming & outgoing messages – Only interrupt CPU w/ relevant messages – Predictable Message Transmission • Protocol handling CAN Transmit Receive Engine – Error Detection – Arbitration detection – Bit monitoring/stuffing Message filtering + buffering CPU Interface • Physical layer interface – Current & voltage control for bus – Absorb transients – Signal bus (line) faults & correct CANH CAN bus CANL 6 Physical interface TX RX H/W Errors Control + status

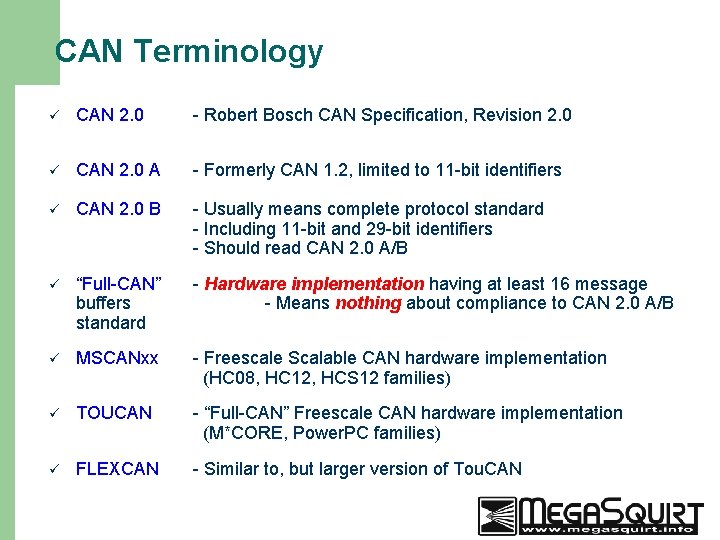

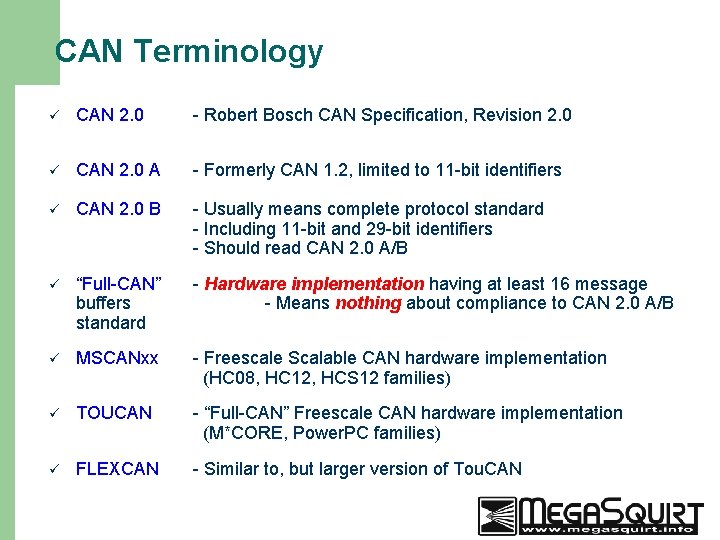

CAN Terminology 7 ü CAN 2. 0 - Robert Bosch CAN Specification, Revision 2. 0 ü CAN 2. 0 A - Formerly CAN 1. 2, limited to 11 -bit identifiers ü CAN 2. 0 B - Usually means complete protocol standard - Including 11 -bit and 29 -bit identifiers - Should read CAN 2. 0 A/B ü “Full-CAN” buffers standard - Hardware implementation having at least 16 message - Means nothing about compliance to CAN 2. 0 A/B ü MSCANxx - Freescale Scalable CAN hardware implementation (HC 08, HC 12, HCS 12 families) ü TOUCAN - “Full-CAN” Freescale CAN hardware implementation (M*CORE, Power. PC families) ü FLEXCAN - Similar to, but larger version of Tou. CAN

CAN Node/Message Structure April 17, 2003 Mega. Squirt and Mega. Squirt Logo are trademarks of BG Soflex, LLC.

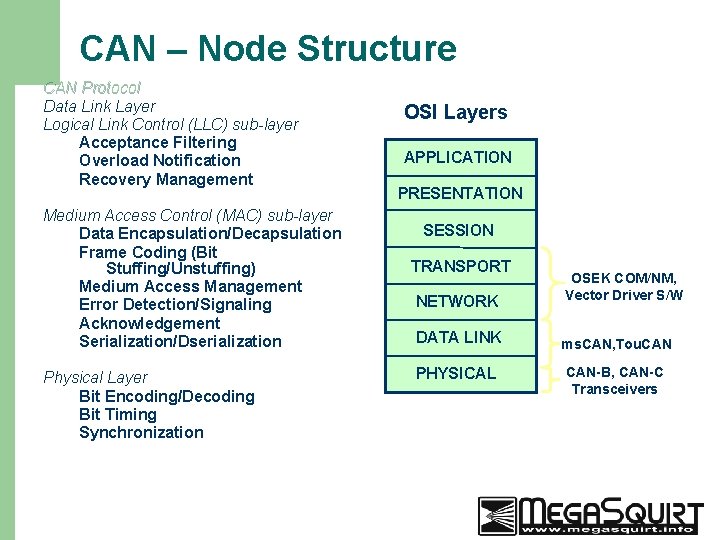

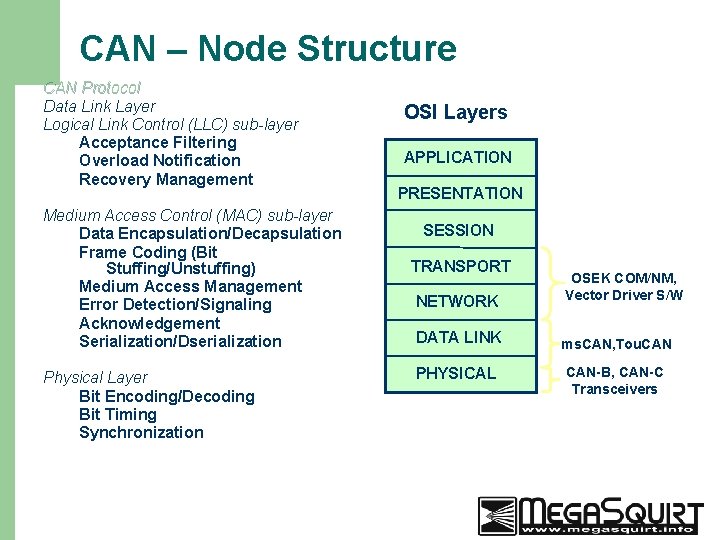

CAN – Node Structure CAN Protocol Data Link Layer Logical Link Control (LLC) sub-layer Acceptance Filtering Overload Notification Recovery Management Medium Access Control (MAC) sub-layer Data Encapsulation/Decapsulation Frame Coding (Bit Stuffing/Unstuffing) Medium Access Management Error Detection/Signaling Acknowledgement Serialization/Dserialization Physical Layer Bit Encoding/Decoding Bit Timing Synchronization 9 OSI Layers APPLICATION PRESENTATION SESSION TRANSPORT NETWORK DATA LINK PHYSICAL OSEK COM/NM, Vector Driver S/W ms. CAN, Tou. CAN-B, CAN-C Transceivers

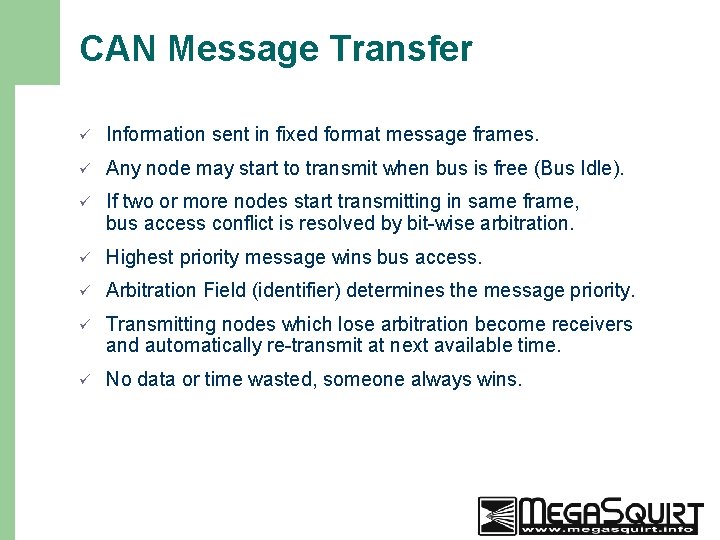

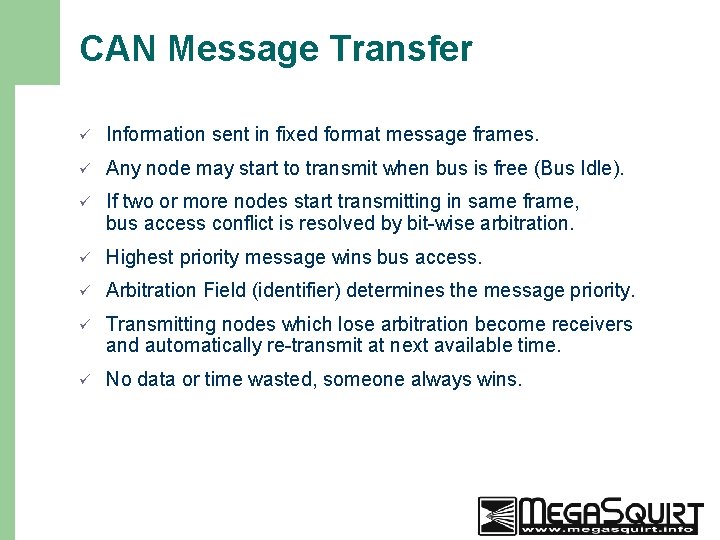

CAN Message Transfer 10 ü Information sent in fixed format message frames. ü Any node may start to transmit when bus is free (Bus Idle). ü If two or more nodes start transmitting in same frame, bus access conflict is resolved by bit-wise arbitration. ü Highest priority message wins bus access. ü Arbitration Field (identifier) determines the message priority. ü Transmitting nodes which lose arbitration become receivers and automatically re-transmit at next available time. ü No data or time wasted, someone always wins.

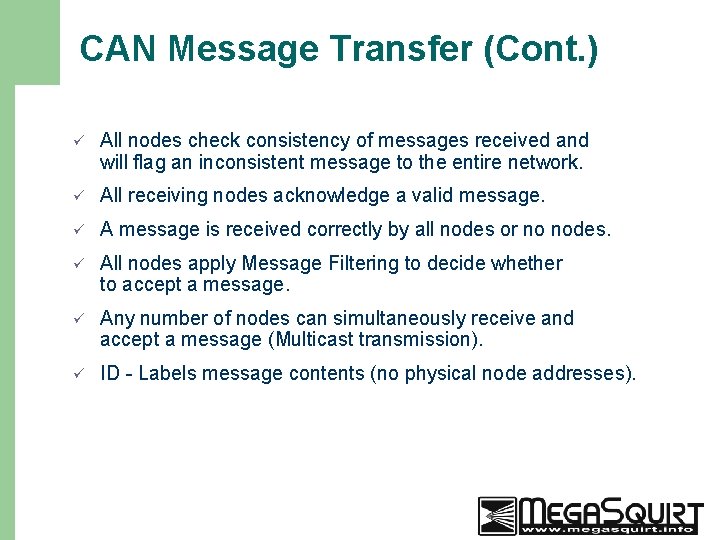

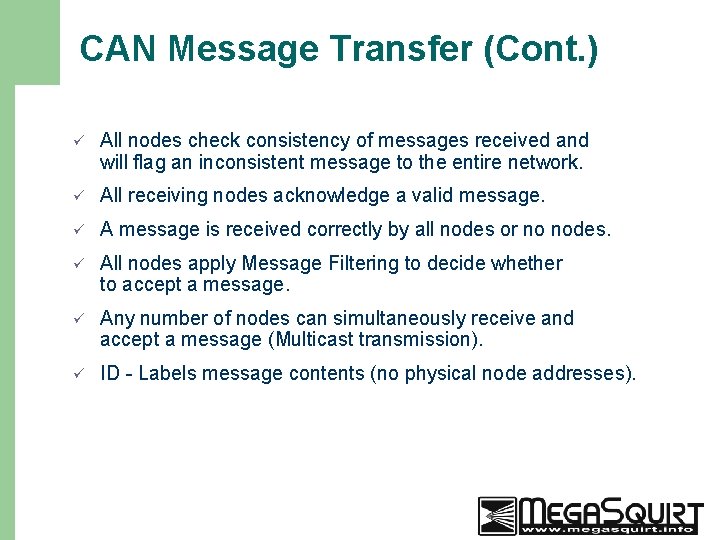

CAN Message Transfer (Cont. ) 11 ü All nodes check consistency of messages received and will flag an inconsistent message to the entire network. ü All receiving nodes acknowledge a valid message. ü A message is received correctly by all nodes or no nodes. ü All nodes apply Message Filtering to decide whether to accept a message. ü Any number of nodes can simultaneously receive and accept a message (Multicast transmission). ü ID - Labels message contents (no physical node addresses).

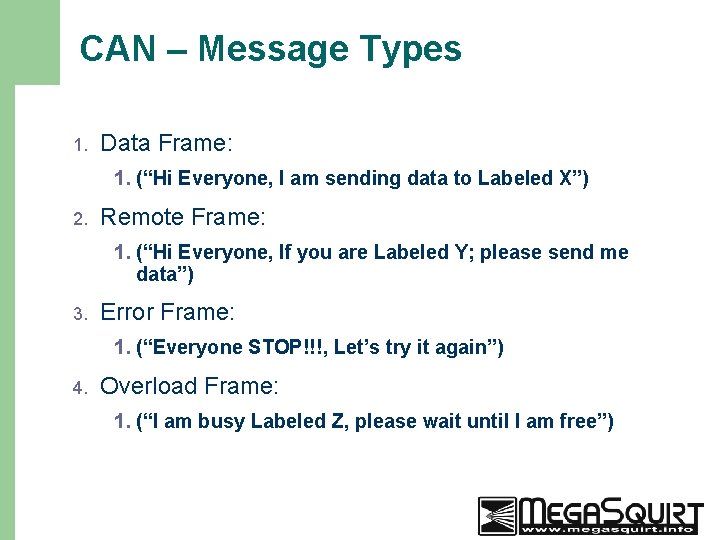

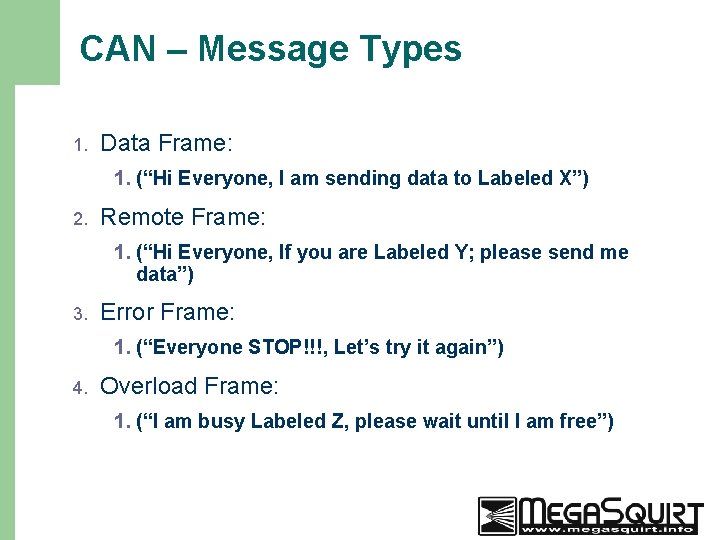

CAN – Message Types 1. Data Frame: 1. (“Hi Everyone, I am sending data to Labeled X”) 2. Remote Frame: 1. (“Hi Everyone, If you are Labeled Y; please send me data”) 3. Error Frame: 1. (“Everyone STOP!!!, Let’s try it again”) 4. Overload Frame: 1. (“I am busy Labeled Z, please wait until I am free”) 12

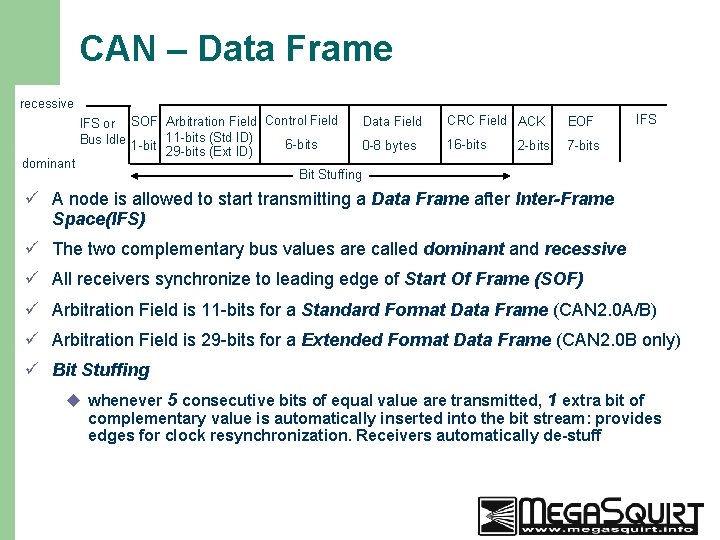

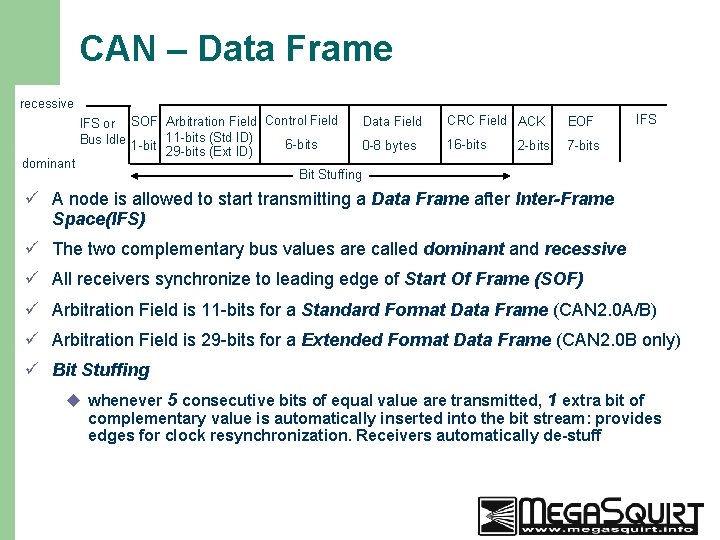

CAN – Data Frame recessive dominant IFS or SOF Arbitration Field Control Field Bus Idle 1 -bit 11 -bits (Std ID) 6 -bits 29 -bits (Ext ID) Data Field CRC Field ACK EOF 0 -8 bytes 16 -bits 7 -bits 2 -bits IFS Bit Stuffing ü A node is allowed to start transmitting a Data Frame after Inter-Frame Space(IFS) ü The two complementary bus values are called dominant and recessive ü All receivers synchronize to leading edge of Start Of Frame (SOF) ü Arbitration Field is 11 -bits for a Standard Format Data Frame (CAN 2. 0 A/B) ü Arbitration Field is 29 -bits for a Extended Format Data Frame (CAN 2. 0 B only) ü Bit Stuffing u whenever 5 consecutive bits of equal value are transmitted, 1 extra bit of complementary value is automatically inserted into the bit stream: provides edges for clock resynchronization. Receivers automatically de-stuff 13

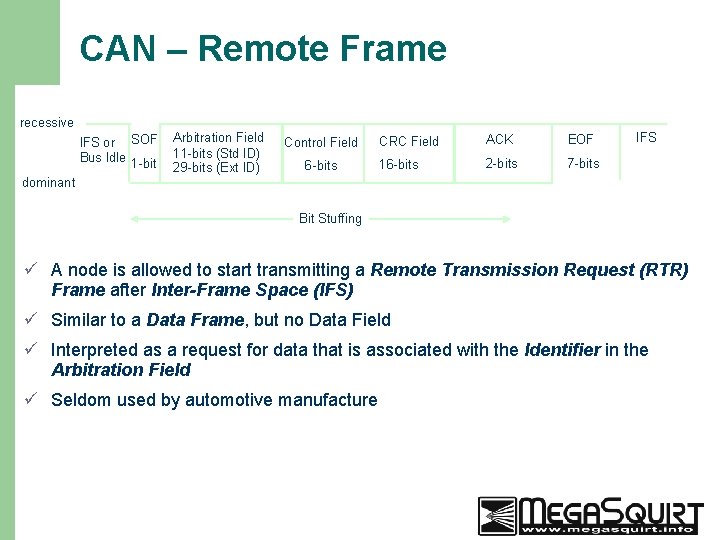

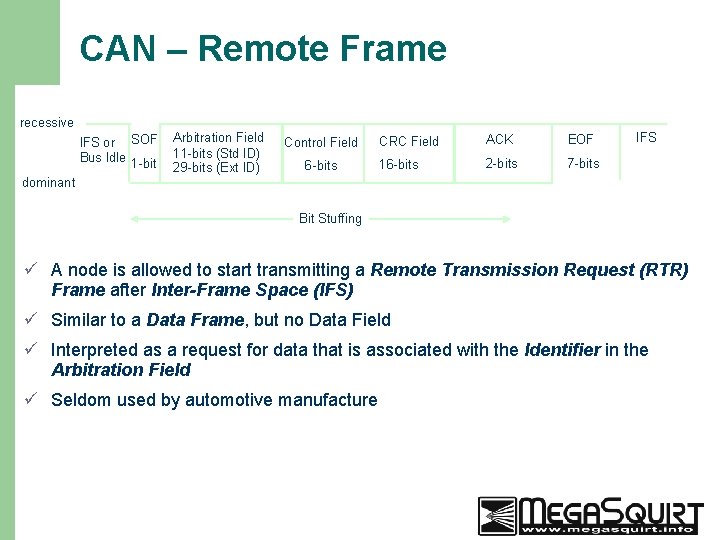

CAN – Remote Frame recessive IFS or SOF Bus Idle 1 -bit dominant Arbitration Field 11 -bits (Std ID) 29 -bits (Ext ID) Control Field 6 -bits CRC Field ACK EOF 16 -bits 2 -bits 7 -bits IFS Bit Stuffing ü A node is allowed to start transmitting a Remote Transmission Request (RTR) Frame after Inter-Frame Space (IFS) ü Similar to a Data Frame, but no Data Field ü Interpreted as a request for data that is associated with the Identifier in the Arbitration Field ü Seldom used by automotive manufacture 14

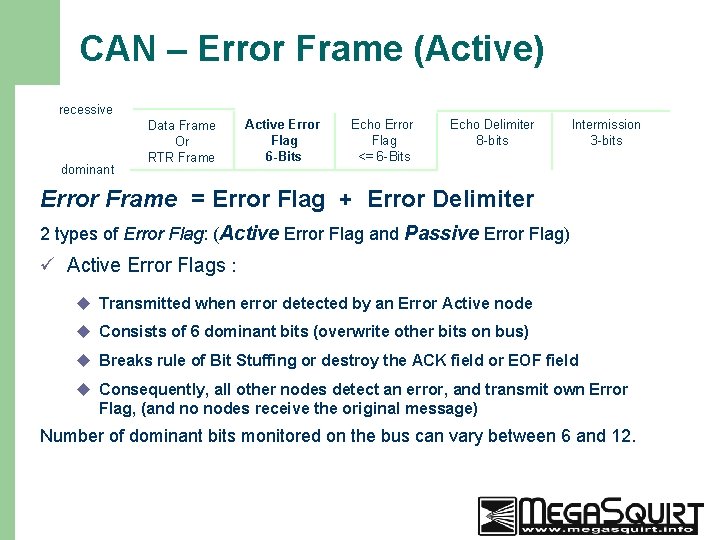

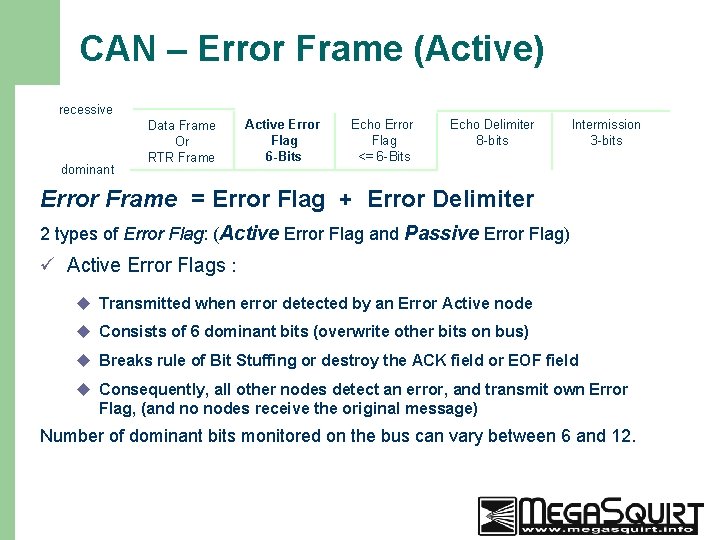

CAN – Error Frame (Active) recessive dominant Data Frame Or RTR Frame Active Error Flag 6 -Bits Echo Error Flag <= 6 -Bits Echo Delimiter 8 -bits Intermission 3 -bits Error Frame = Error Flag + Error Delimiter 2 types of Error Flag: (Active Error Flag and Passive Error Flag) ü Active Error Flags : u Transmitted when error detected by an Error Active node u Consists of 6 dominant bits (overwrite other bits on bus) u Breaks rule of Bit Stuffing or destroy the ACK field or EOF field u Consequently, all other nodes detect an error, and transmit own Error Flag, (and no nodes receive the original message) Number of dominant bits monitored on the bus can vary between 6 and 12. 15

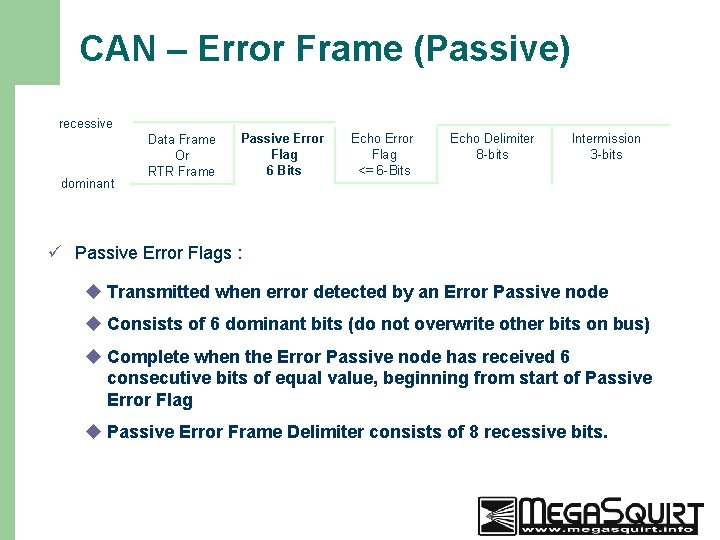

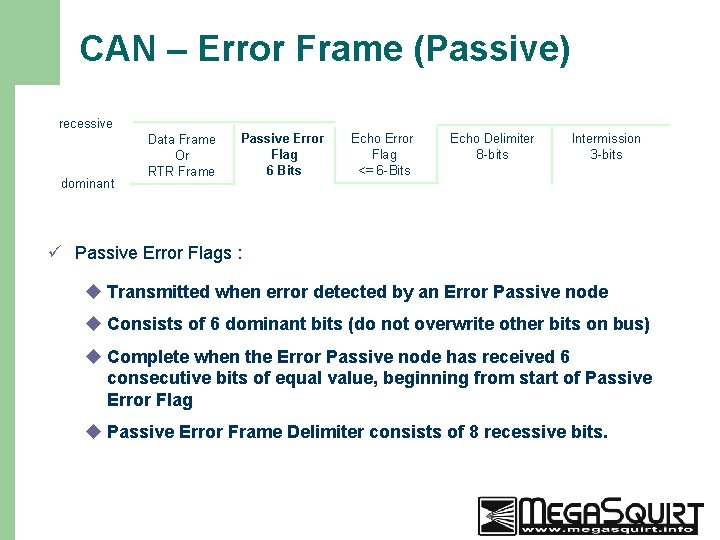

CAN – Error Frame (Passive) recessive dominant Data Frame Or RTR Frame Passive Error Flag 6 Bits Echo Error Flag <= 6 -Bits Echo Delimiter 8 -bits Intermission 3 -bits ü Passive Error Flags : u Transmitted when error detected by an Error Passive node u Consists of 6 dominant bits (do not overwrite other bits on bus) u Complete when the Error Passive node has received 6 consecutive bits of equal value, beginning from start of Passive Error Flag u Passive Error Frame Delimiter consists of 8 recessive bits. 16

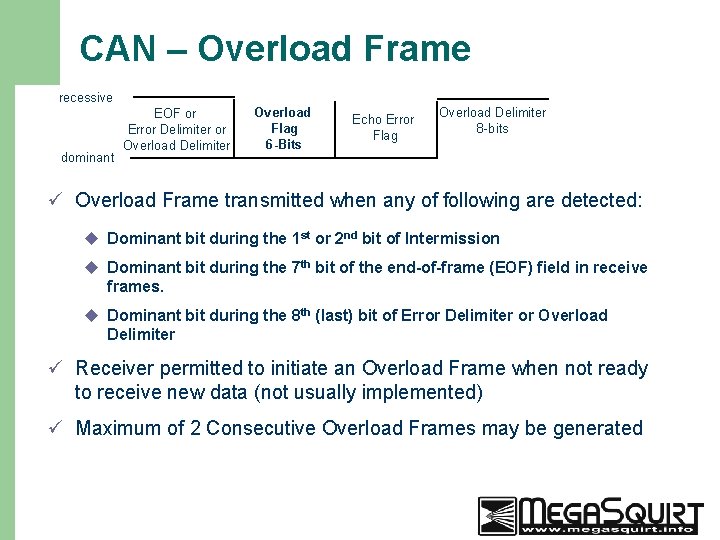

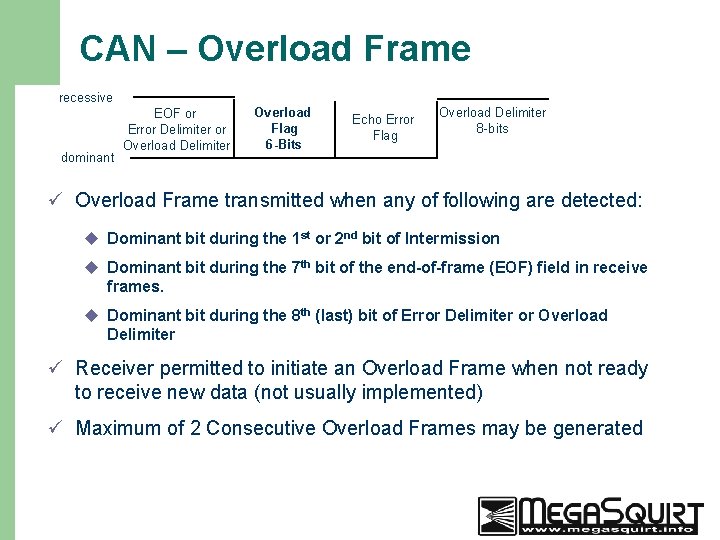

CAN – Overload Frame recessive dominant EOF or Error Delimiter or Overload Delimiter Overload Flag 6 -Bits Echo Error Flag Overload Delimiter 8 -bits ü Overload Frame transmitted when any of following are detected: u Dominant bit during the 1 st or 2 nd bit of Intermission u Dominant bit during the 7 th bit of the end-of-frame (EOF) field in receive frames. u Dominant bit during the 8 th (last) bit of Error Delimiter or Overload Delimiter ü Receiver permitted to initiate an Overload Frame when not ready to receive new data (not usually implemented) ü Maximum of 2 Consecutive Overload Frames may be generated 17

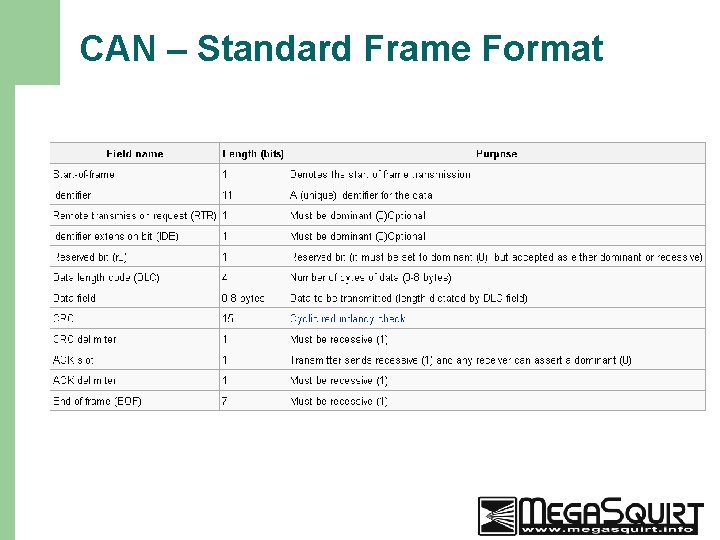

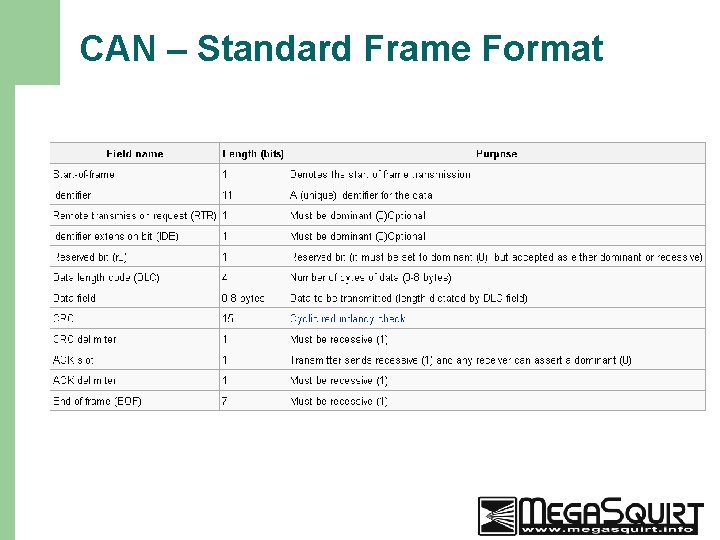

CAN – Standard Frame Format 18

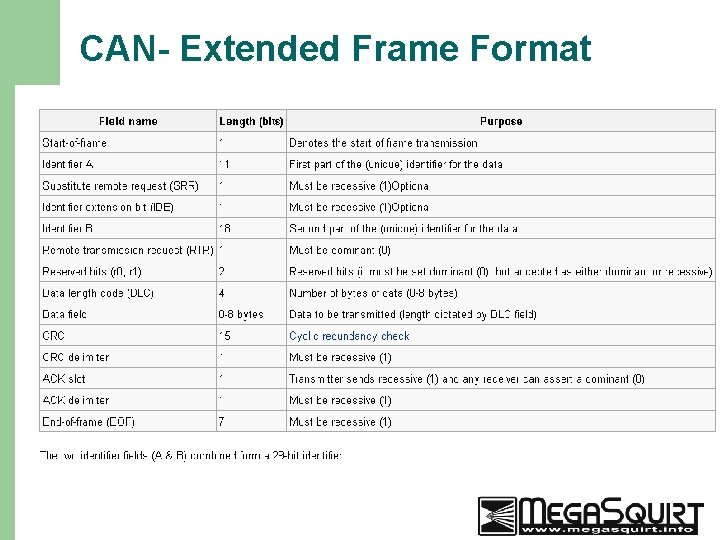

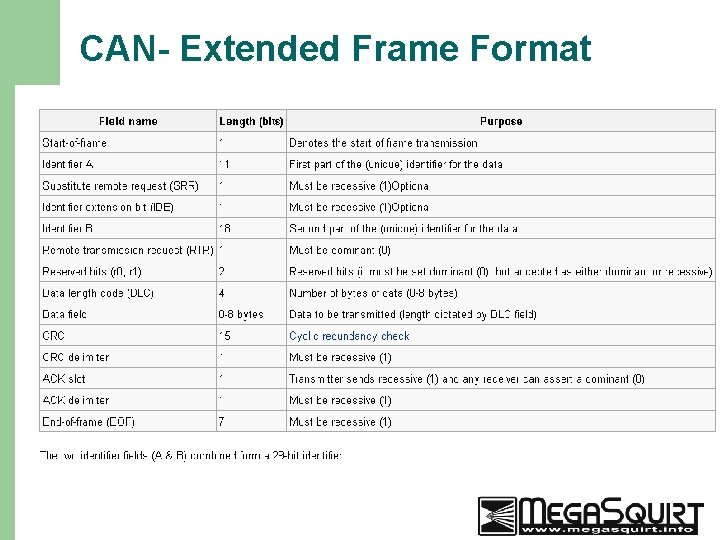

CAN- Extended Frame Format 19

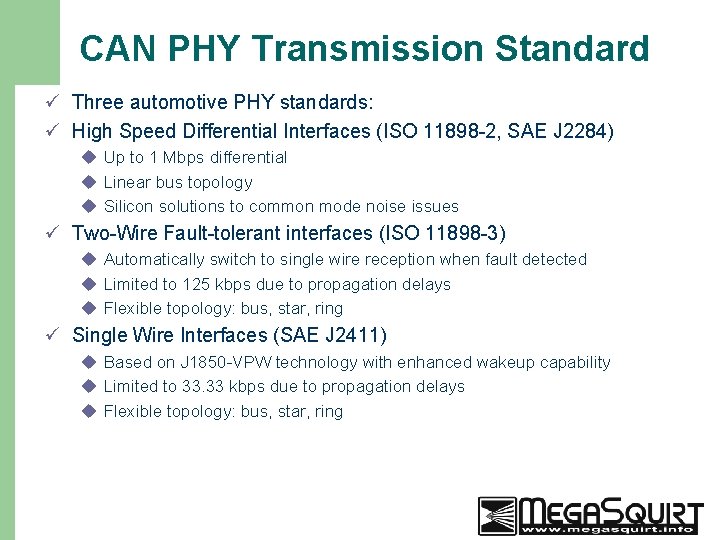

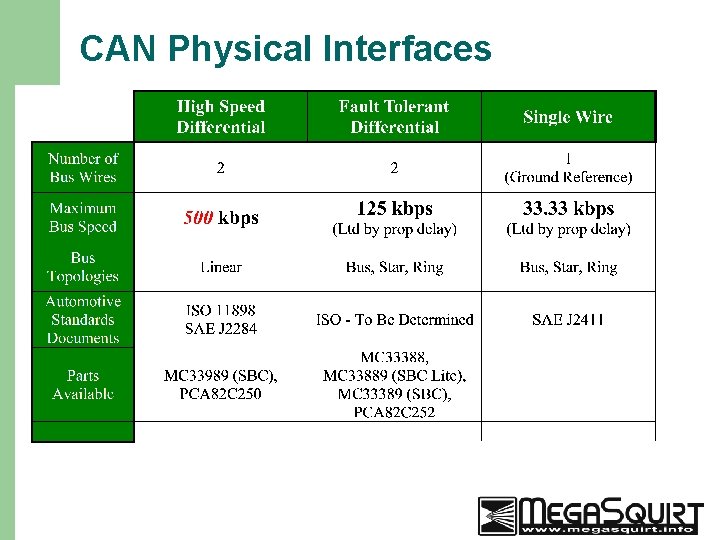

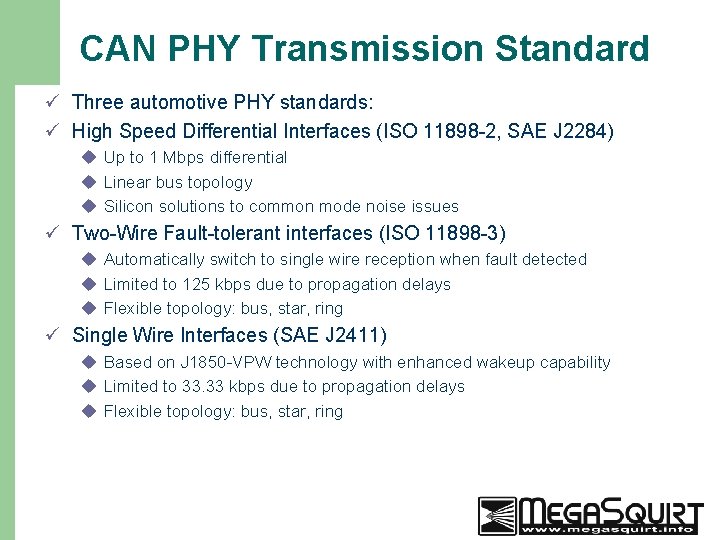

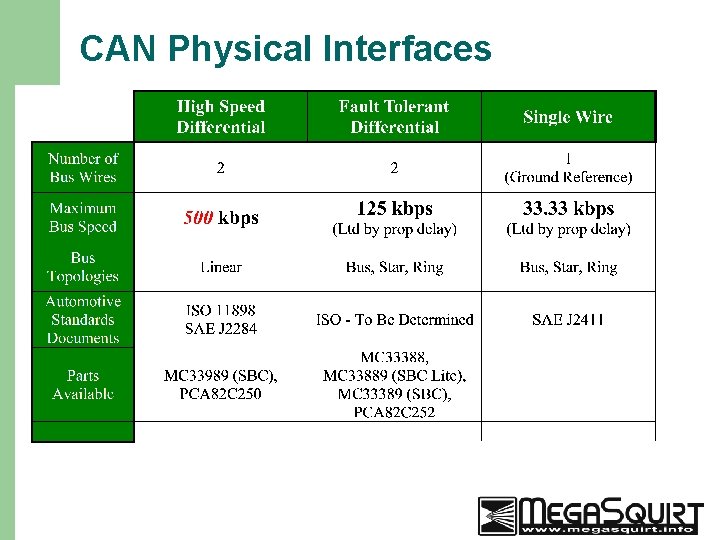

CAN PHY Transmission Standard ü Three automotive PHY standards: ü High Speed Differential Interfaces (ISO 11898 -2, SAE J 2284) u Up to 1 Mbps differential u Linear bus topology u Silicon solutions to common mode noise issues ü Two-Wire Fault-tolerant interfaces (ISO 11898 -3) u Automatically switch to single wire reception when fault detected u Limited to 125 kbps due to propagation delays u Flexible topology: bus, star, ring ü Single Wire Interfaces (SAE J 2411) u Based on J 1850 -VPW technology with enhanced wakeup capability u Limited to 33. 33 kbps due to propagation delays u Flexible topology: bus, star, ring 20

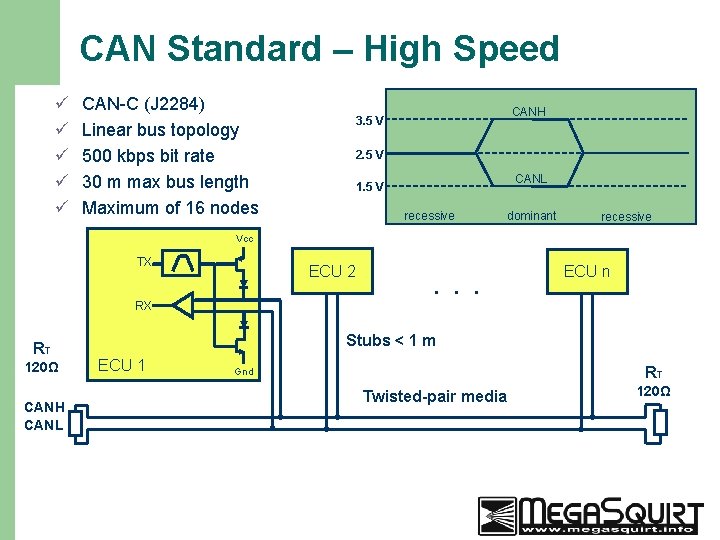

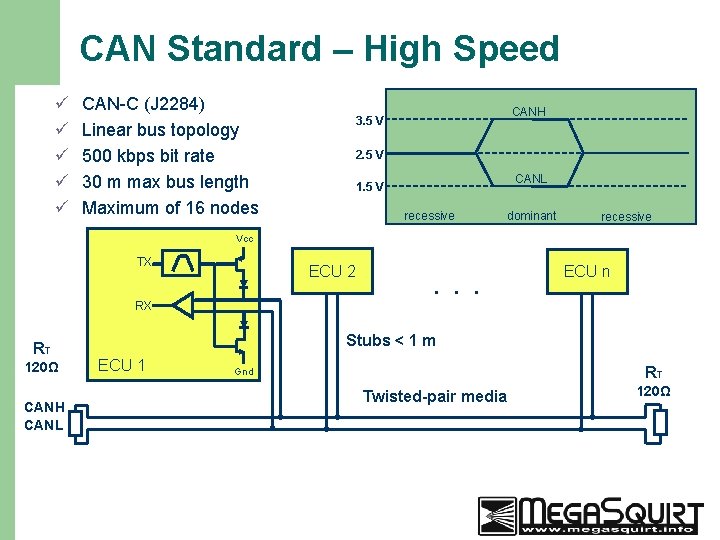

CAN Standard – High Speed ü ü ü CAN-C (J 2284) Linear bus topology 500 kbps bit rate 30 m max bus length Maximum of 16 nodes CANH 3. 5 V 2. 5 V CANL 1. 5 V recessive dominant recessive Vcc TX ECU 2 RX RT 120Ω CANH CANL 21 . . . ECU n Stubs < 1 m ECU 1 RT Gnd Twisted-pair media 120Ω

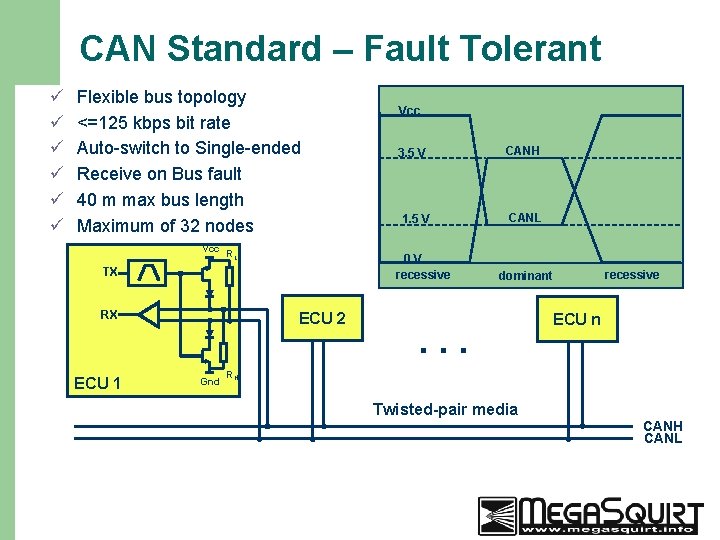

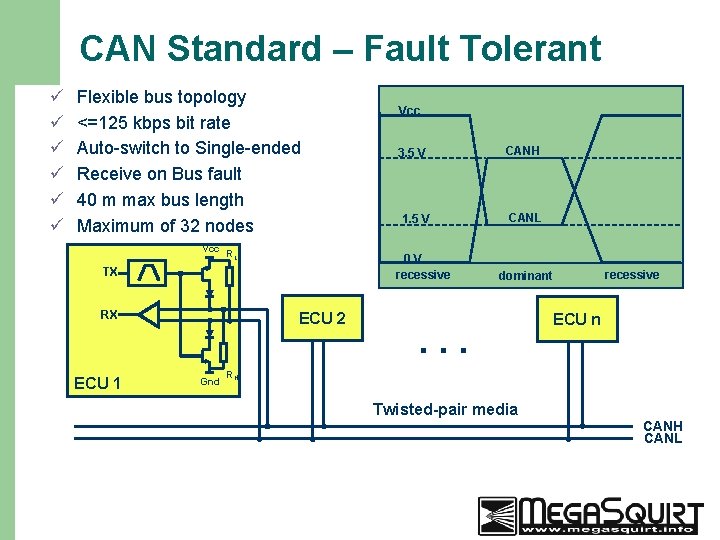

CAN Standard – Fault Tolerant ü ü ü Flexible bus topology <=125 kbps bit rate Auto-switch to Single-ended Receive on Bus fault 40 m max bus length Maximum of 32 nodes Vcc RL ECU 1 ECU 2 Gnd 3. 5 V 1. 5 V 0 V recessive TX RX Vcc CANH CANL recessive dominant . . . ECU n RH Twisted-pair media CANH CANL 22

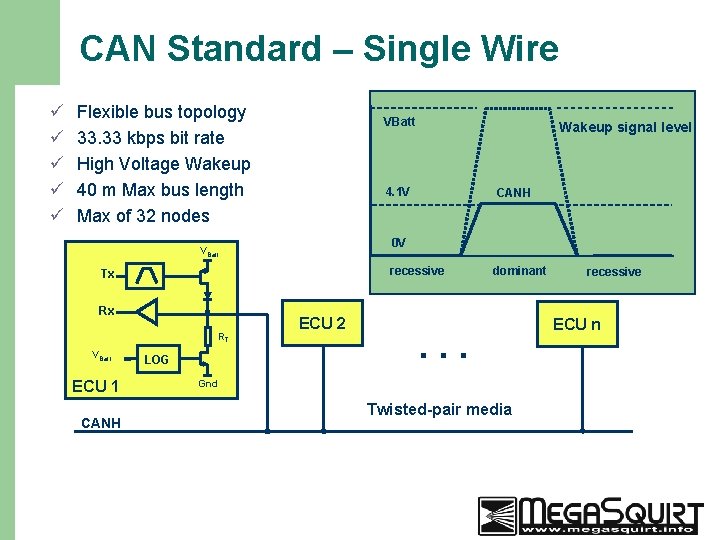

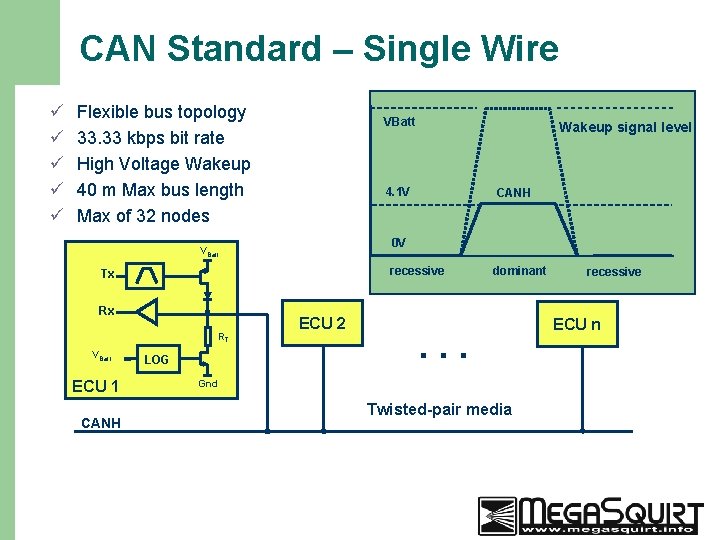

CAN Standard – Single Wire ü ü ü Flexible bus topology 33. 33 kbps bit rate High Voltage Wakeup 40 m Max bus length Max of 32 nodes VBatt 4. 1 V recessive Tx Rx RT ECU 1 CANH 23 CANH 0 V VBatt Wakeup signal level LOG ECU 2 dominant . . . Gnd Twisted-pair media recessive ECU n

CAN Physical Interfaces 24

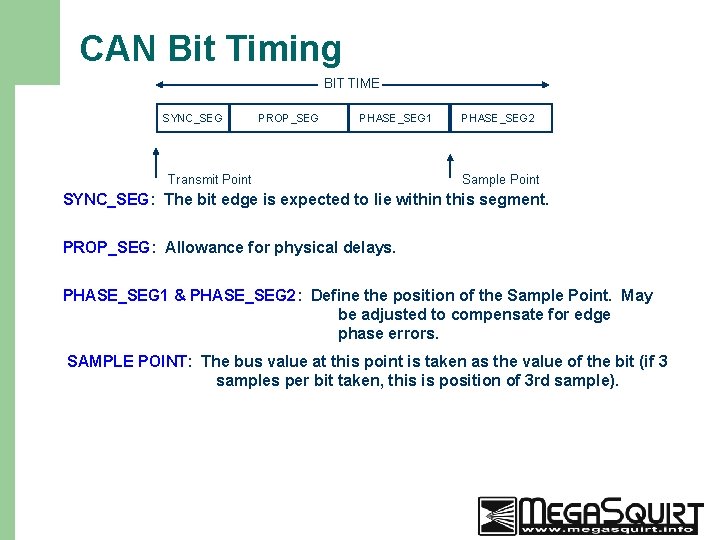

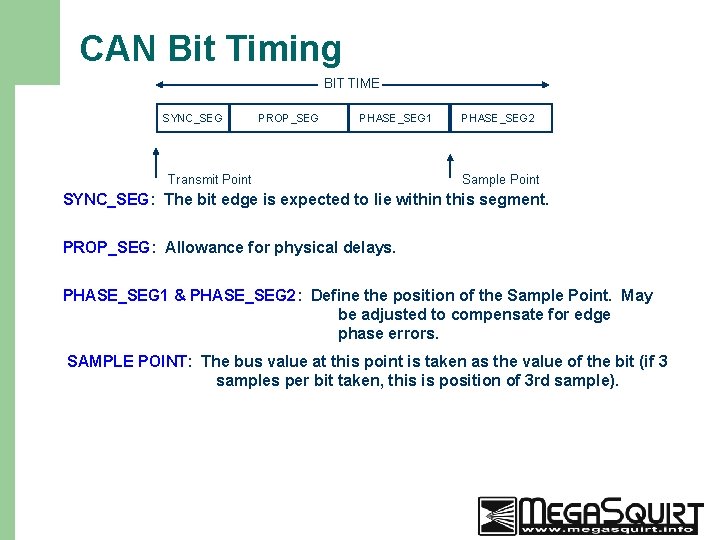

CAN Bit Timing BIT TIME SYNC_SEG PROP_SEG PHASE_SEG 1 Transmit Point PHASE_SEG 2 Sample Point SYNC_SEG: The bit edge is expected to lie within this segment. PROP_SEG: Allowance for physical delays. PHASE_SEG 1 & PHASE_SEG 2: Define the position of the Sample Point. May be adjusted to compensate for edge phase errors. SAMPLE POINT: The bus value at this point is taken as the value of the bit (if 3 samples per bit taken, this is position of 3 rd sample). 25

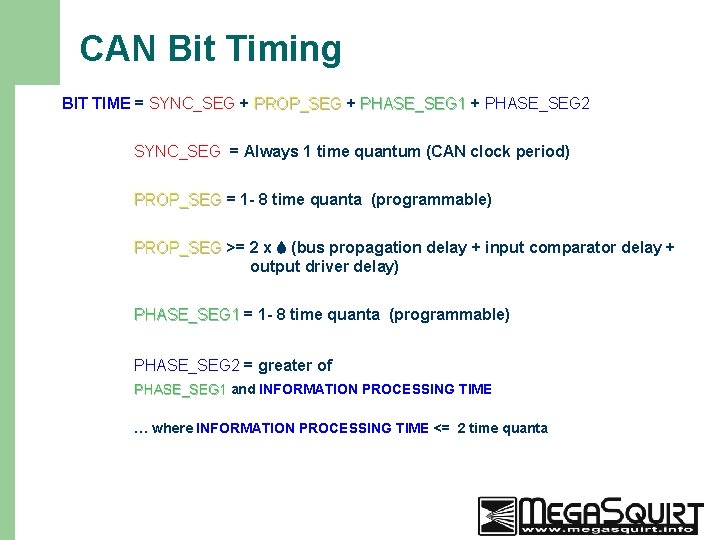

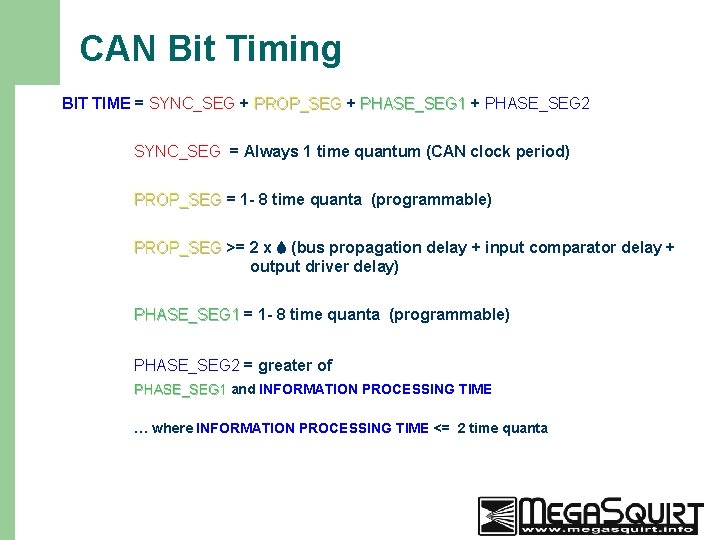

CAN Bit Timing BIT TIME = SYNC_SEG + PROP_SEG + PHASE_SEG 1 + PHASE_SEG 2 SYNC_SEG = Always 1 time quantum (CAN clock period) PROP_SEG = 1 - 8 time quanta (programmable) PROP_SEG >= 2 x (bus propagation delay + input comparator delay + output driver delay) PHASE_SEG 1 = 1 - 8 time quanta (programmable) PHASE_SEG 2 = greater of PHASE_SEG 1 and INFORMATION PROCESSING TIME … where INFORMATION PROCESSING TIME <= 2 time quanta 26

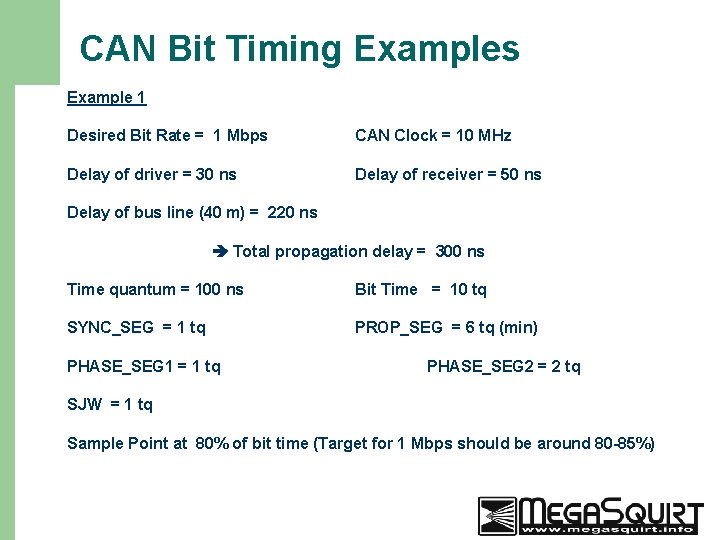

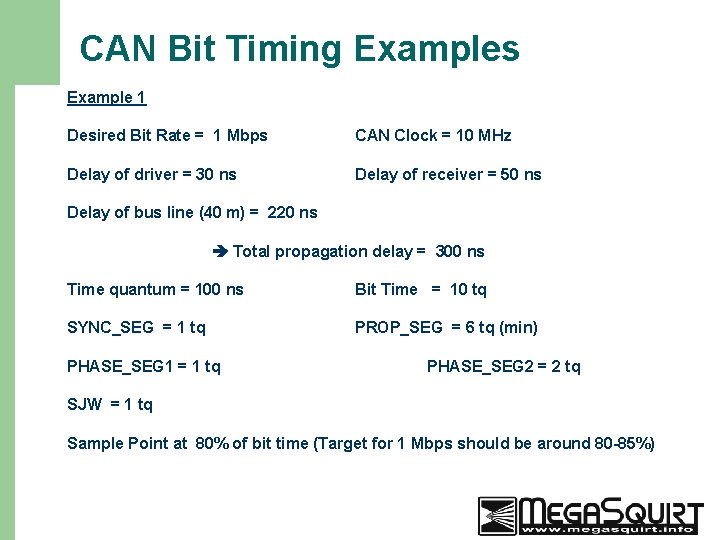

CAN Bit Timing Examples Example 1 Desired Bit Rate = 1 Mbps CAN Clock = 10 MHz Delay of driver = 30 ns Delay of receiver = 50 ns Delay of bus line (40 m) = 220 ns Total propagation delay = 300 ns Time quantum = 100 ns Bit Time = 10 tq SYNC_SEG = 1 tq PROP_SEG = 6 tq (min) PHASE_SEG 1 = 1 tq PHASE_SEG 2 = 2 tq SJW = 1 tq Sample Point at 80% of bit time (Target for 1 Mbps should be around 80 -85%) 27

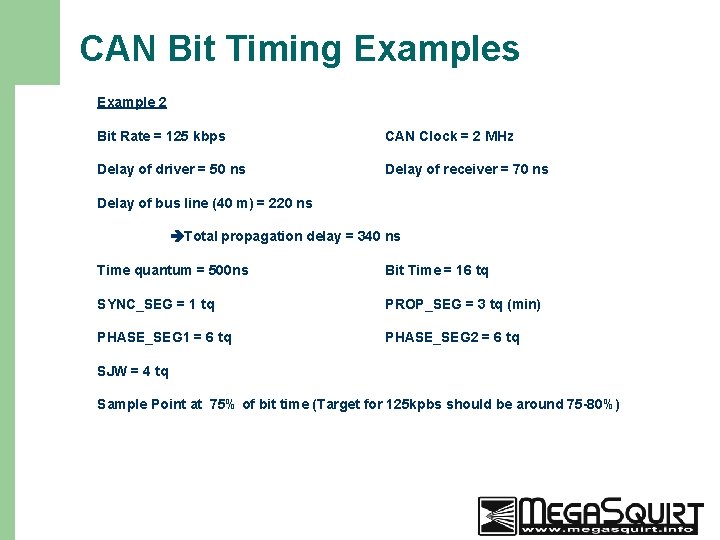

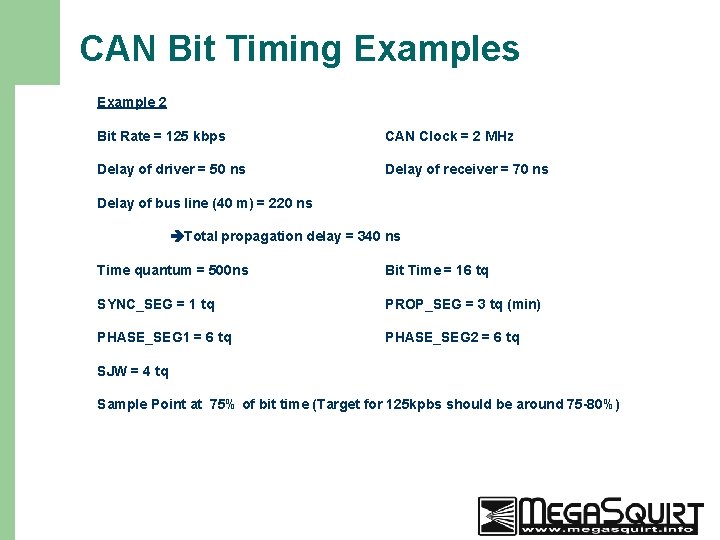

CAN Bit Timing Examples Example 2 Bit Rate = 125 kbps CAN Clock = 2 MHz Delay of driver = 50 ns Delay of receiver = 70 ns Delay of bus line (40 m) = 220 ns Total propagation delay = 340 ns Time quantum = 500 ns Bit Time = 16 tq SYNC_SEG = 1 tq PROP_SEG = 3 tq (min) PHASE_SEG 1 = 6 tq PHASE_SEG 2 = 6 tq SJW = 4 tq Sample Point at 75% of bit time (Target for 125 kpbs should be around 75 -80%) 28

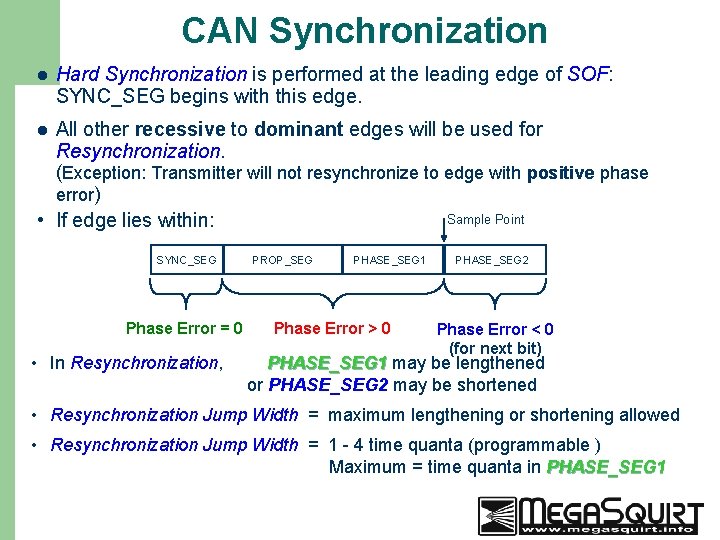

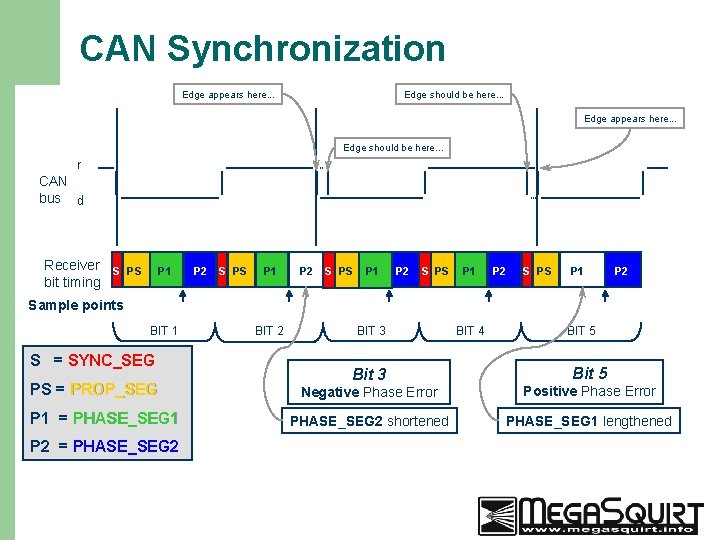

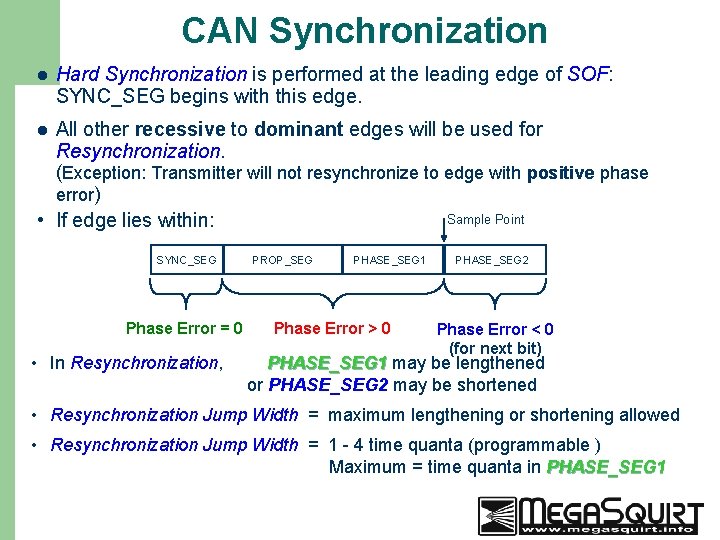

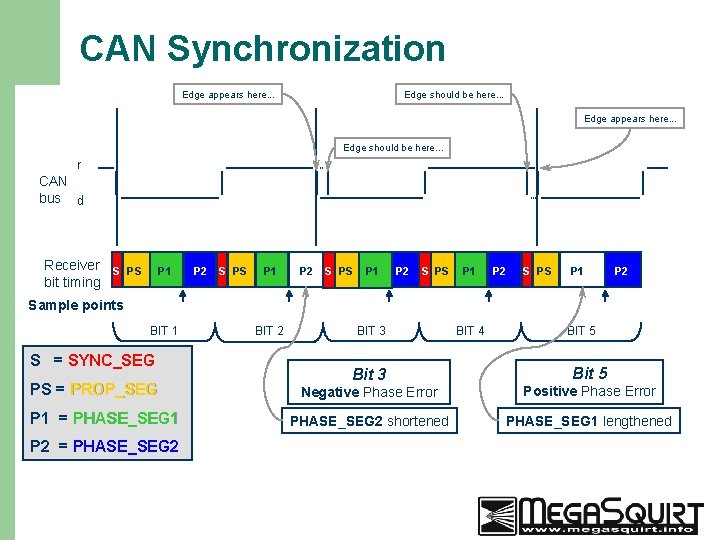

CAN Synchronization l Hard Synchronization is performed at the leading edge of SOF: SYNC_SEG begins with this edge. All other recessive to dominant edges will be used for Resynchronization. (Exception: Transmitter will not resynchronize to edge with positive phase error) Sample Point • If edge lies within: l SYNC_SEG Phase Error = 0 • In Resynchronization, PROP_SEG PHASE_SEG 1 Phase Error > 0 PHASE_SEG 2 Phase Error < 0 (for next bit) PHASE_SEG 1 may be lengthened or PHASE_SEG 2 may be shortened • Resynchronization Jump Width = maximum lengthening or shortening allowed • Resynchronization Jump Width = 1 - 4 time quanta (programmable ) Maximum = time quanta in PHASE_SEG 1 29

CAN Synchronization Edge appears here. . . Edge should be here. . . Edge appears here. . . Edge should be here. . . r CAN bus d Receiver bit timing S PS P 1 P 2 S PS P 1 P 2 Sample points BIT 1 S = SYNC_SEG PS = PROP_SEG P 1 = PHASE_SEG 1 P 2 = PHASE_SEG 2 30 BIT 2 BIT 3 BIT 4 BIT 5 Bit 3 Bit 5 Negative Phase Error Positive Phase Error PHASE_SEG 2 shortened PHASE_SEG 1 lengthened

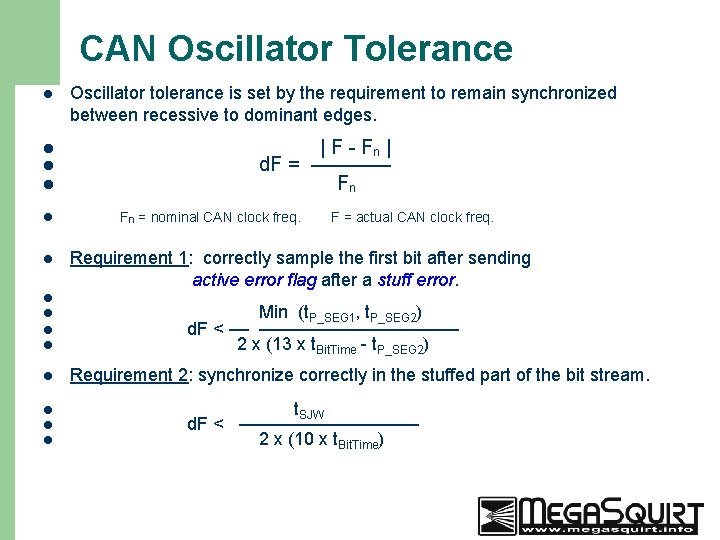

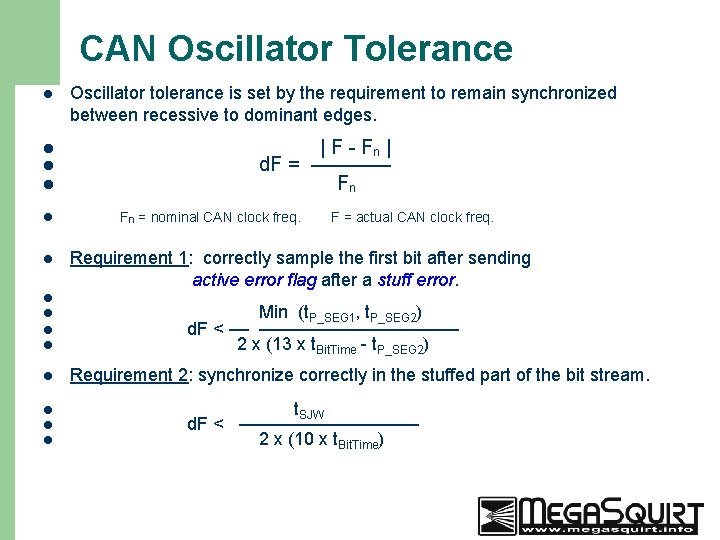

CAN Oscillator Tolerance l l l l 31 Oscillator tolerance is set by the requirement to remain synchronized between recessive to dominant edges. | F - Fn | d. F = ———— Fn Fn = nominal CAN clock freq. F = actual CAN clock freq. Requirement 1: correctly sample the first bit after sending active error flag after a stuff error. Min (t. P_SEG 1, t. P_SEG 2) d. F < — ————— 2 x (13 x t. Bit. Time - t. P_SEG 2) Requirement 2: synchronize correctly in the stuffed part of the bit stream. t. SJW d. F < ————— 2 x (10 x t. Bit. Time)

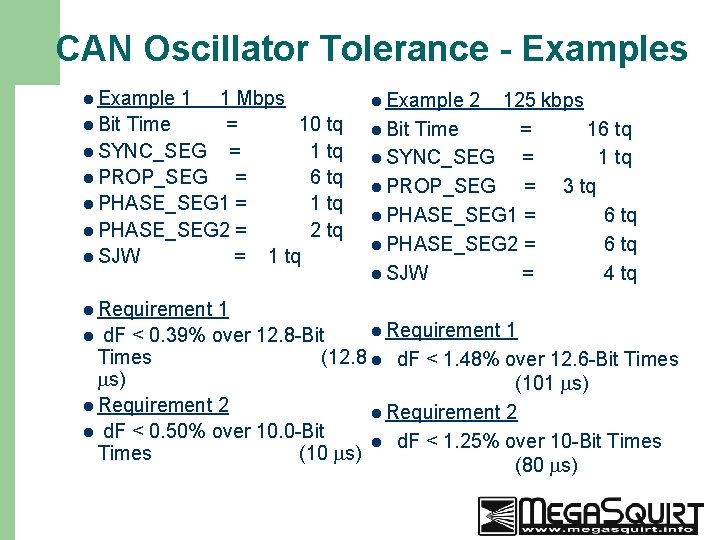

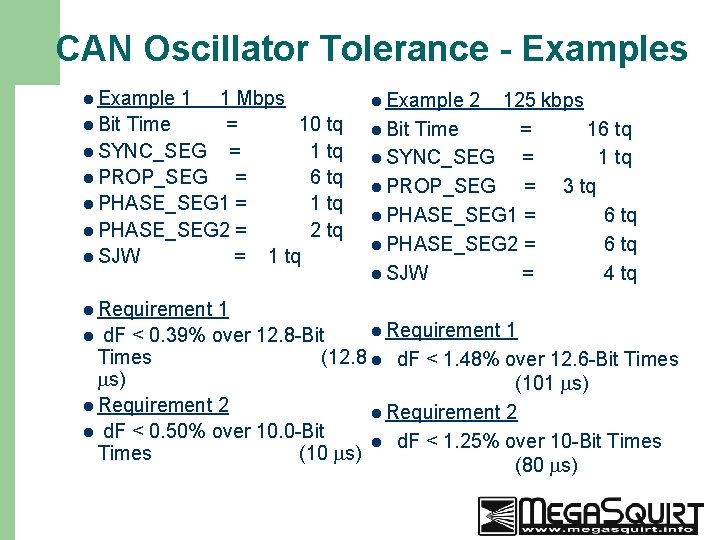

CAN Oscillator Tolerance - Examples l Example 1 1 Mbps l Bit Time = 10 tq l SYNC_SEG = 1 tq l PROP_SEG = 6 tq l PHASE_SEG 1 = 1 tq l PHASE_SEG 2 = 2 tq l SJW = 1 tq l Requirement l Example 2 125 kbps l Bit Time = 16 tq l SYNC_SEG = 1 tq l PROP_SEG = 3 tq l PHASE_SEG 1 = 6 tq l PHASE_SEG 2 = 6 tq l SJW = 4 tq 1 l Requirement 1 l d. F < 0. 39% over 12. 8 -Bit Times (12. 8 l d. F < 1. 48% over 12. 6 -Bit Times ms) (101 ms) l Requirement 2 l d. F < 0. 50% over 10. 0 -Bit l d. F < 1. 25% over 10 -Bit Times (10 ms) (80 ms) 32

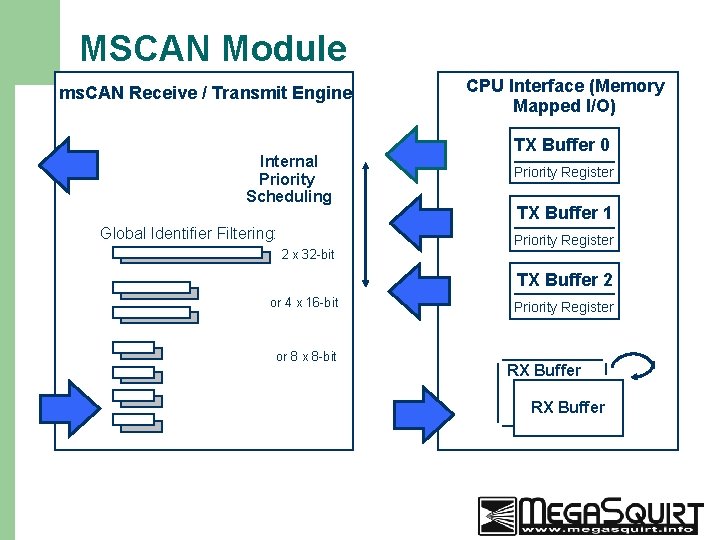

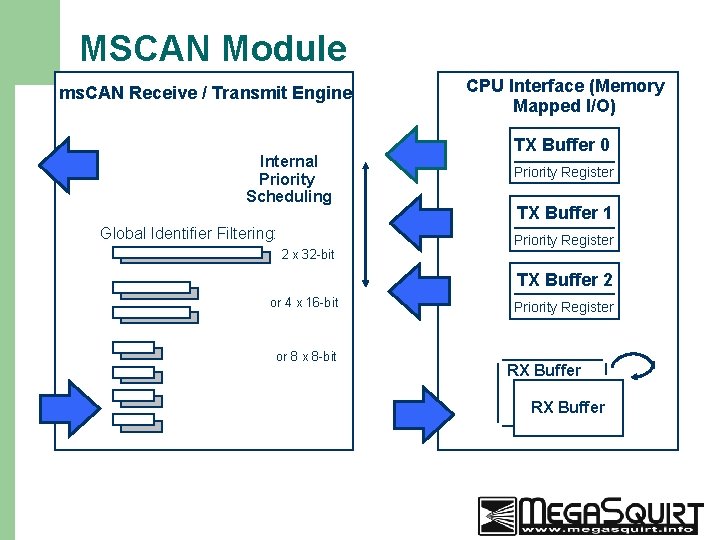

MSCAN Module ms. CAN Receive / Transmit Engine Internal Priority Scheduling Global Identifier Filtering: 2 x 32 -bit CPU Interface (Memory Mapped I/O) TX Buffer 0 Priority Register TX Buffer 1 Priority Register TX Buffer 2 or 4 x 16 -bit or 8 x 8 -bit Priority Register RX Buffer 33

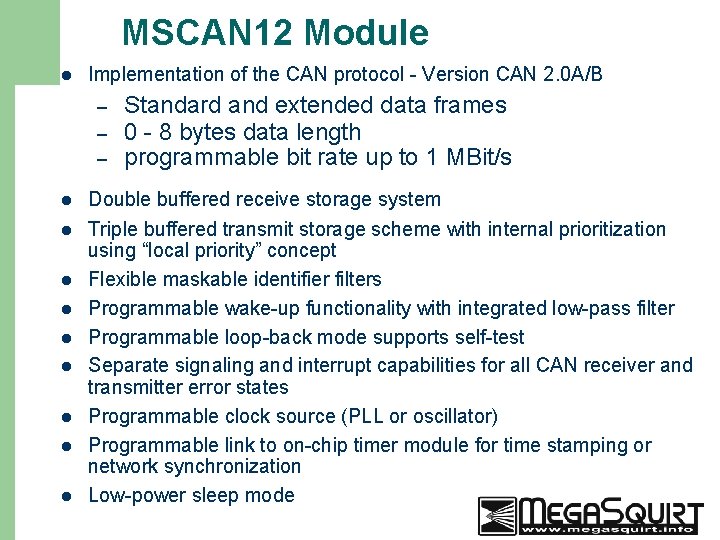

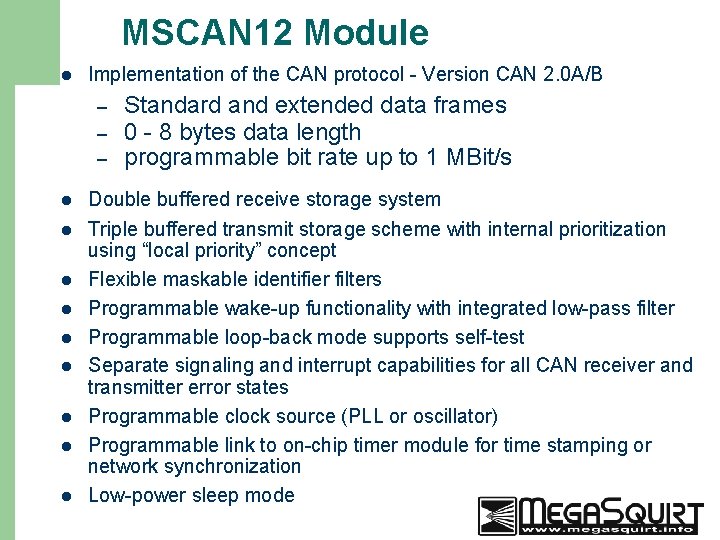

MSCAN 12 Module l Implementation of the CAN protocol - Version CAN 2. 0 A/B – – – l l l l 34 l Standard and extended data frames 0 - 8 bytes data length programmable bit rate up to 1 MBit/s Double buffered receive storage system Triple buffered transmit storage scheme with internal prioritization using “local priority” concept Flexible maskable identifier filters Programmable wake-up functionality with integrated low-pass filter Programmable loop-back mode supports self-test Separate signaling and interrupt capabilities for all CAN receiver and transmitter error states Programmable clock source (PLL or oscillator) Programmable link to on-chip timer module for time stamping or network synchronization Low-power sleep mode

Mega. Squirt CAN Message April 17, 2003 Mega. Squirt and Mega. Squirt Logo are trademarks of BG Soflex, LLC.

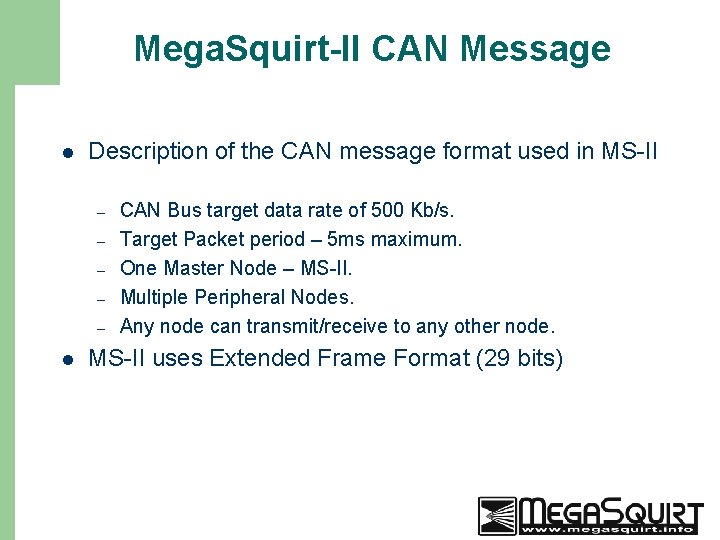

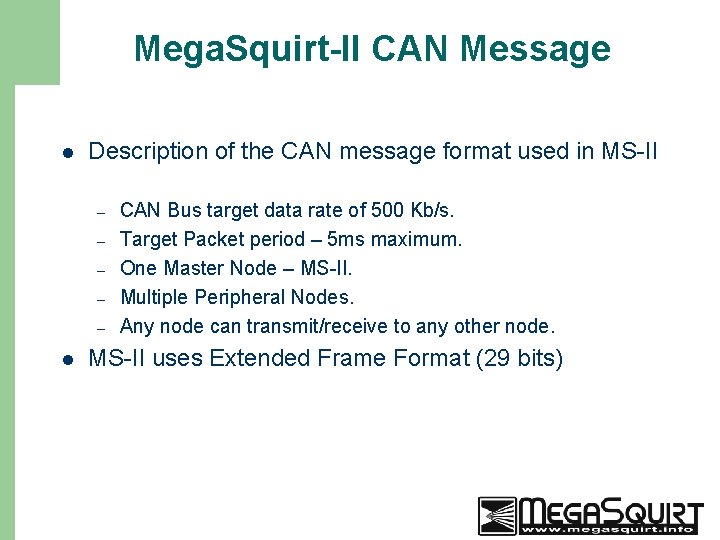

Mega. Squirt-II CAN Message l Description of the CAN message format used in MS-II – – – l 36 CAN Bus target data rate of 500 Kb/s. Target Packet period – 5 ms maximum. One Master Node – MS-II. Multiple Peripheral Nodes. Any node can transmit/receive to any other node. MS-II uses Extended Frame Format (29 bits)

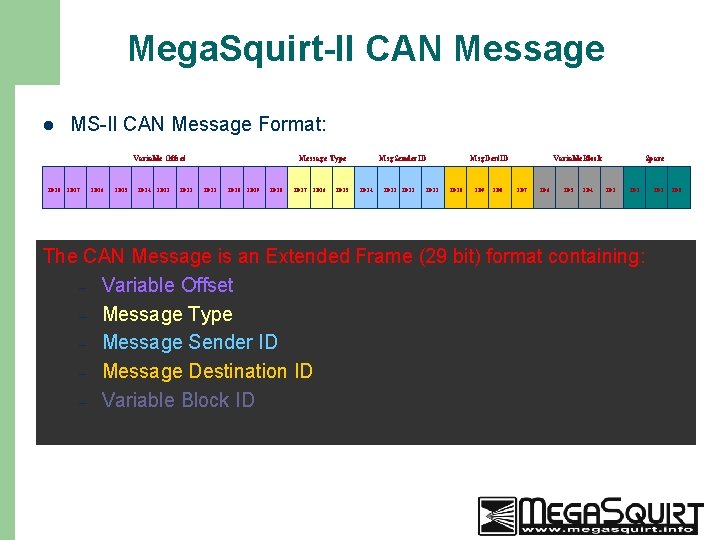

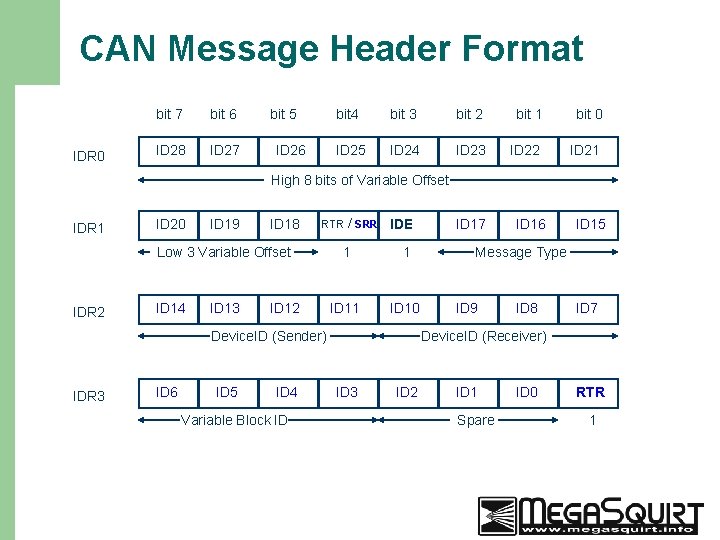

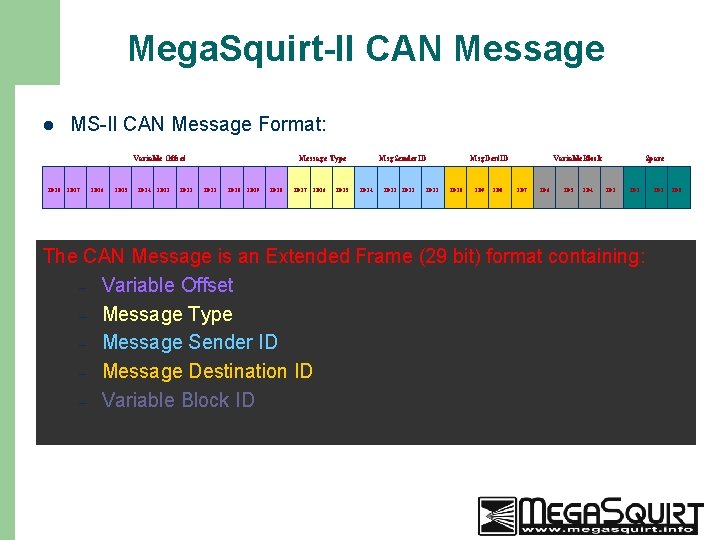

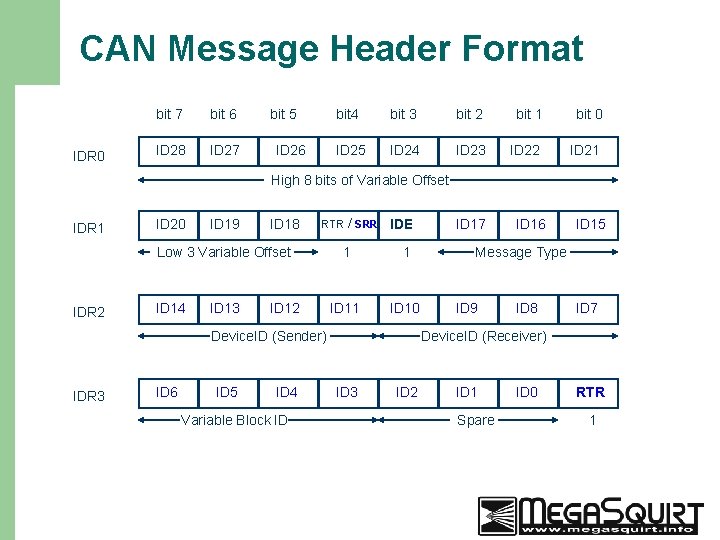

Mega. Squirt-II CAN Message l MS-II CAN Message Format: Variable Offset ID 28 ID 27 ID 26 ID 25 ID 24 ID 23 ID 22 Message Type ID 21 ID 20 ID 19 ID 18 ID 17 ID 16 ID 15 Msg. Sender. ID ID 14 ID 13 ID 12 ID 11 Msg. Dest. ID ID 10 ID 9 ID 8 Variable. Block ID 7 ID 6 ID 5 ID 4 Spare ID 3 ID 2 The CAN Message is an Extended Frame (29 bit) format containing: – Variable Offset – Message Type – Message Sender ID – Message Destination ID – Variable Block ID 37 ID 1 ID 0

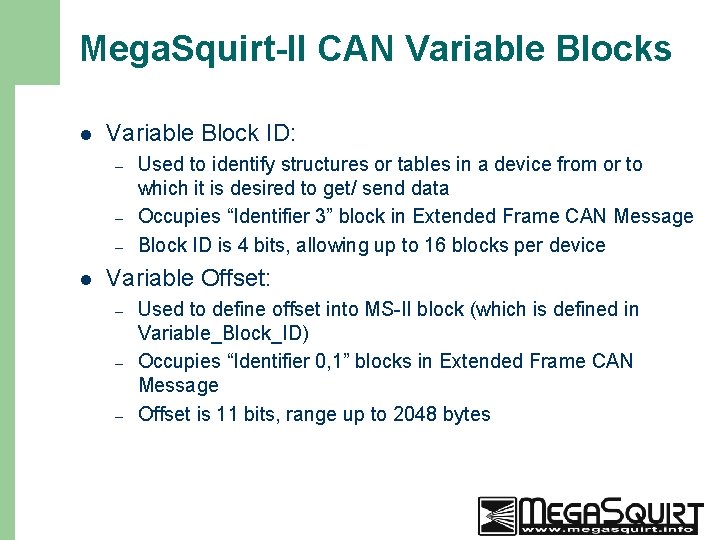

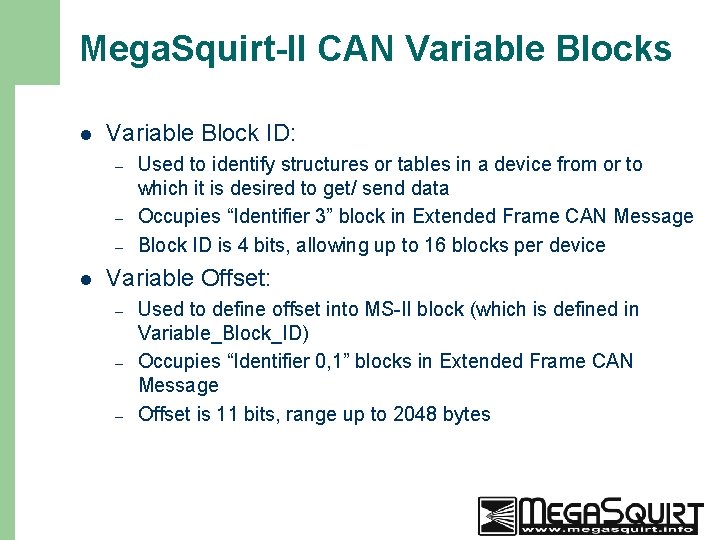

Mega. Squirt-II CAN Variable Blocks l Variable Block ID: – – – l Variable Offset: – – – 38 Used to identify structures or tables in a device from or to which it is desired to get/ send data Occupies “Identifier 3” block in Extended Frame CAN Message Block ID is 4 bits, allowing up to 16 blocks per device Used to define offset into MS-II block (which is defined in Variable_Block_ID) Occupies “Identifier 0, 1” blocks in Extended Frame CAN Message Offset is 11 bits, range up to 2048 bytes

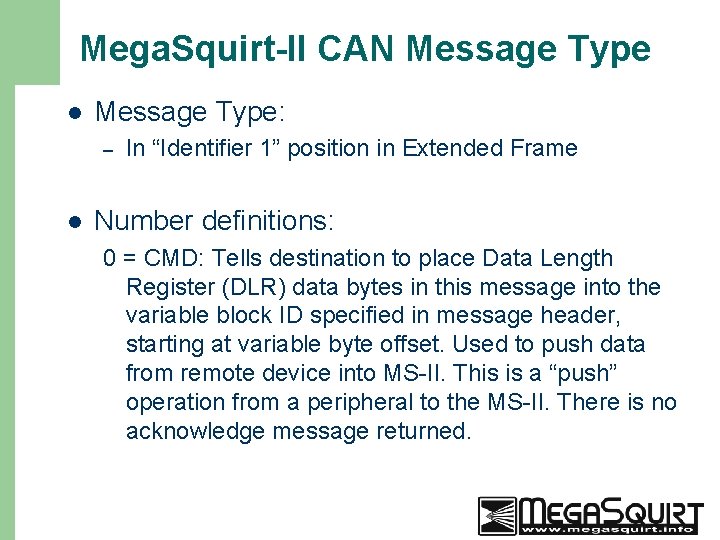

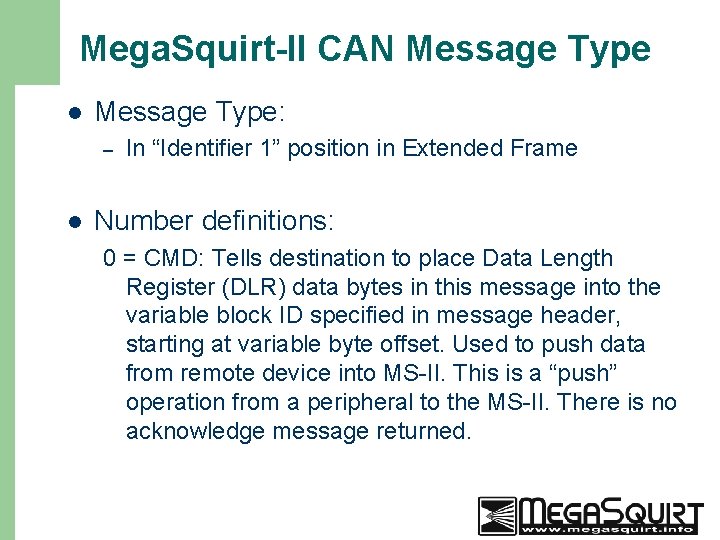

Mega. Squirt-II CAN Message Type l Message Type: – l In “Identifier 1” position in Extended Frame Number definitions: 0 = CMD: Tells destination to place Data Length Register (DLR) data bytes in this message into the variable block ID specified in message header, starting at variable byte offset. Used to push data from remote device into MS-II. This is a “push” operation from a peripheral to the MS-II. There is no acknowledge message returned. 39

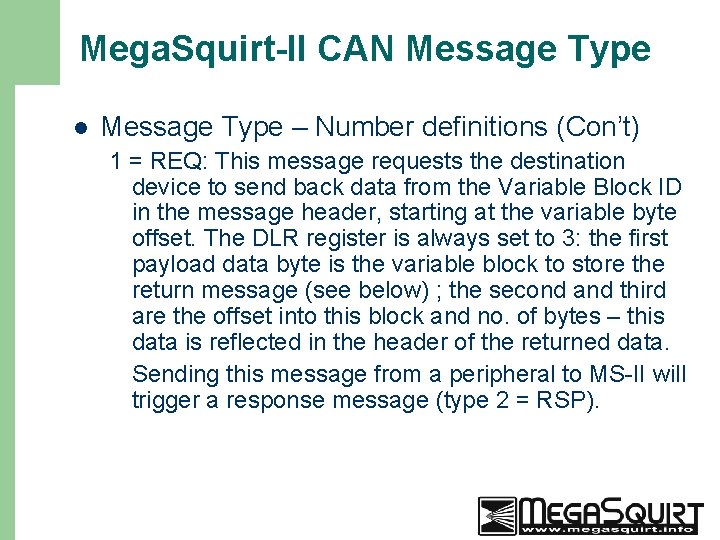

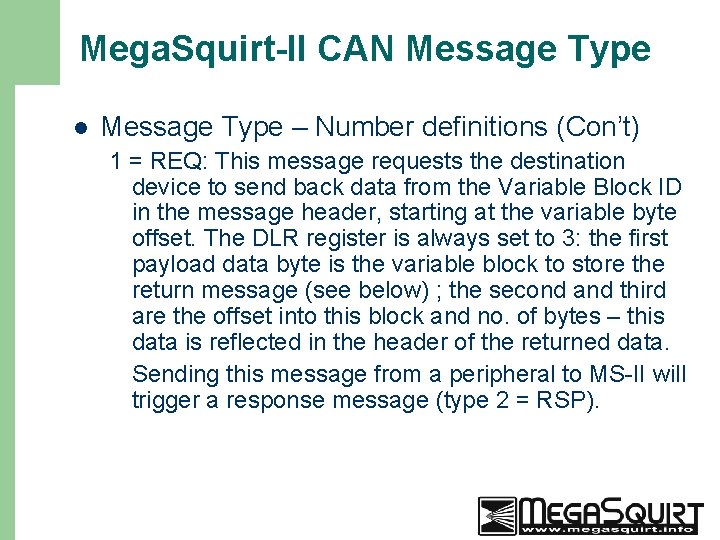

Mega. Squirt-II CAN Message Type l Message Type – Number definitions (Con’t) 1 = REQ: This message requests the destination device to send back data from the Variable Block ID in the message header, starting at the variable byte offset. The DLR register is always set to 3: the first payload data byte is the variable block to store the return message (see below) ; the second and third are the offset into this block and no. of bytes – this data is reflected in the header of the returned data. Sending this message from a peripheral to MS-II will trigger a response message (type 2 = RSP). 40

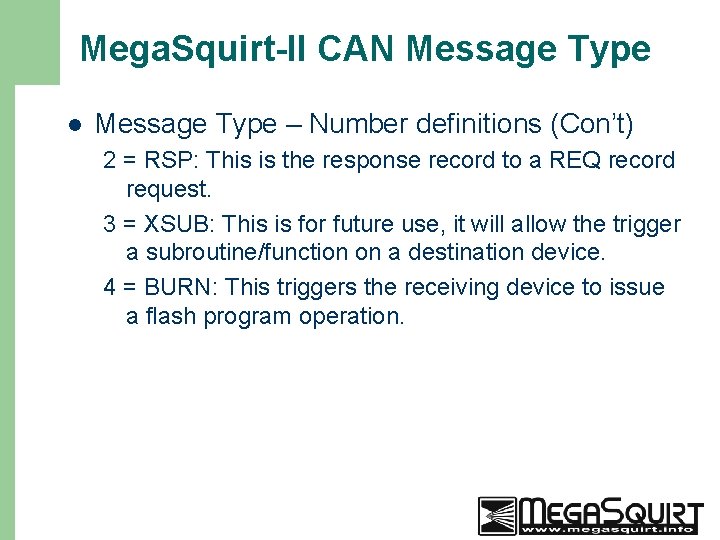

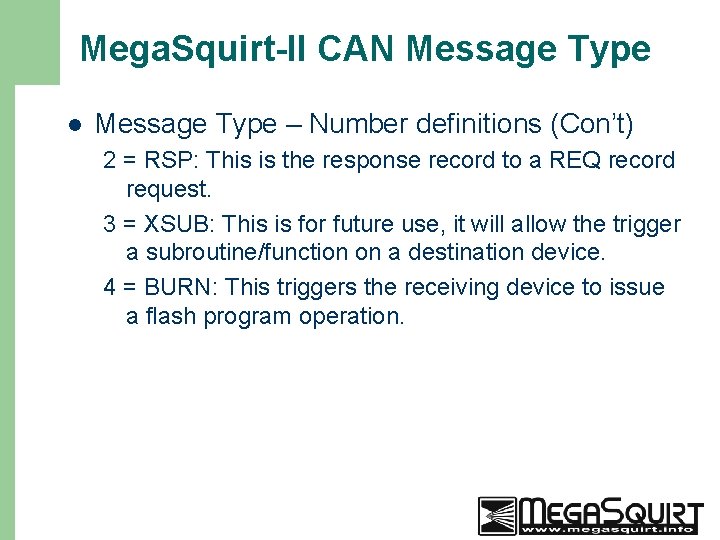

Mega. Squirt-II CAN Message Type l Message Type – Number definitions (Con’t) 2 = RSP: This is the response record to a REQ record request. 3 = XSUB: This is for future use, it will allow the trigger a subroutine/function on a destination device. 4 = BURN: This triggers the receiving device to issue a flash program operation. 41

Mega. Squirt-II CAN Sender/Dest ID l Sender and Destination ID: – – – 42 All devices on the MS CAN network must have a unique CAN ID number. This number defines the Sender and Destination ID. By default, the engine controller board (MS-II) is defined as ID zero. Each ID is defined ahead of time before joining the CAN network.

Other MS-II CAN Parameters l Other CAN-specific bits that are included in message header: – – – l 43 SRR = 1 IDE = 1 RTR = set to 1 if no data is being sent (same as DLR empty) DLR is Data Length Register, defines how many bytes are transmitted in CAN frame (up to 8)

Other MS-II CAN Parameters l l l 44 CAN Data rate is 500 KBPS 16 Time Quanta (including Sync Seg) Tseg 1 = 13 Tseg 2 = 2 Sync Jump Width (SJW) = 4 Note – often these numbers are entered in registers as one less (I. e. 0 to n-1).

CAN Message Header Format IDR 0 bit 7 bit 6 ID 28 ID 27 bit 5 ID 26 bit 4 bit 3 bit 2 bit 1 bit 0 ID 25 ID 24 ID 23 ID 22 ID 21 High 8 bits of Variable Offset IDR 1 ID 20 ID 19 ID 18 RTR / SRR Low 3 Variable Offset IDR 2 ID 14 ID 13 ID 12 IDE 1 1 ID 10 Device. ID (Sender) IDR 3 ID 6 ID 5 ID 4 Variable Block ID 45 ID 17 ID 16 ID 15 Message Type ID 9 ID 8 ID 7 Device. ID (Receiver) ID 3 ID 2 ID 1 Spare ID 0 RTR 1

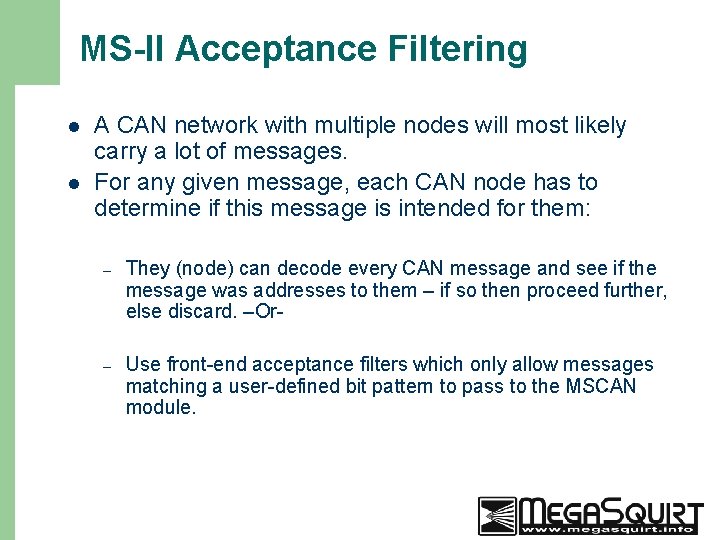

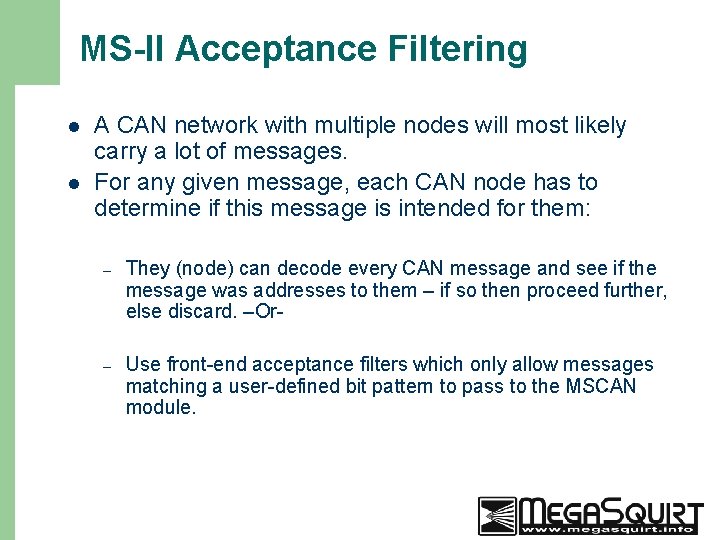

MS-II Acceptance Filtering l l 46 A CAN network with multiple nodes will most likely carry a lot of messages. For any given message, each CAN node has to determine if this message is intended for them: – They (node) can decode every CAN message and see if the message was addresses to them – if so then proceed further, else discard. –Or- – Use front-end acceptance filters which only allow messages matching a user-defined bit pattern to pass to the MSCAN module.

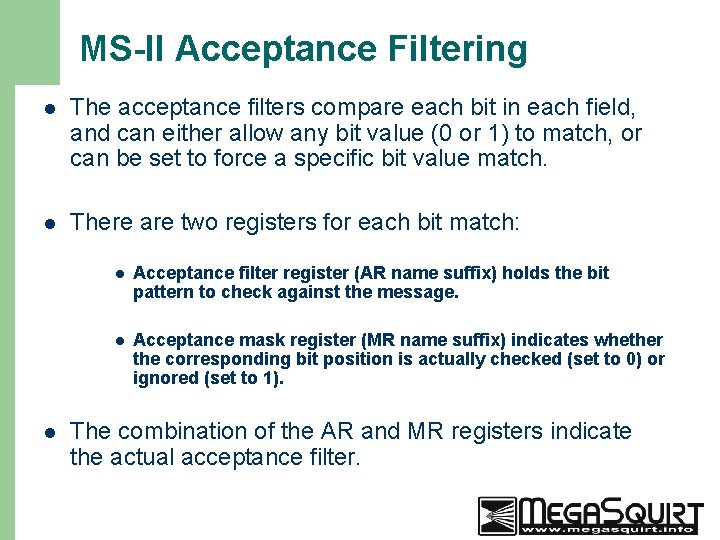

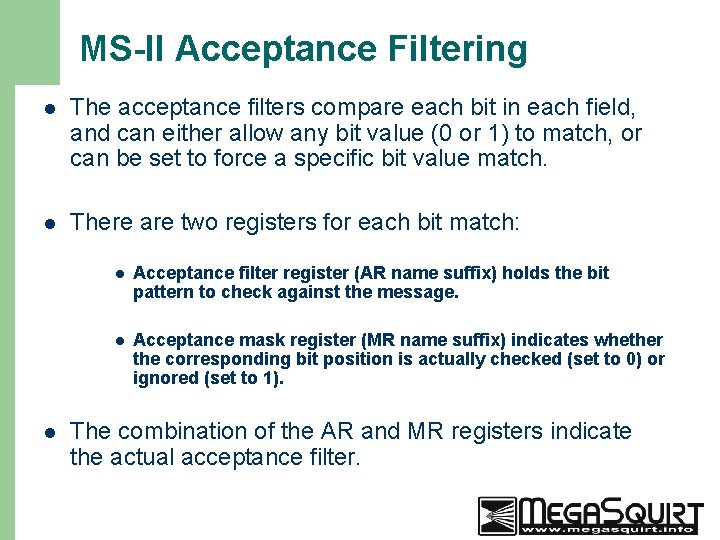

MS-II Acceptance Filtering l The acceptance filters compare each bit in each field, and can either allow any bit value (0 or 1) to match, or can be set to force a specific bit value match. l There are two registers for each bit match: l 47 l Acceptance filter register (AR name suffix) holds the bit pattern to check against the message. l Acceptance mask register (MR name suffix) indicates whether the corresponding bit position is actually checked (set to 0) or ignored (set to 1). The combination of the AR and MR registers indicate the actual acceptance filter.

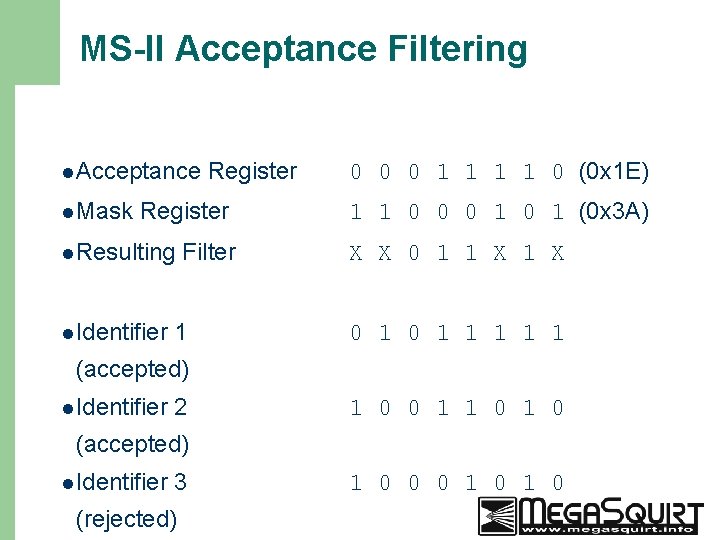

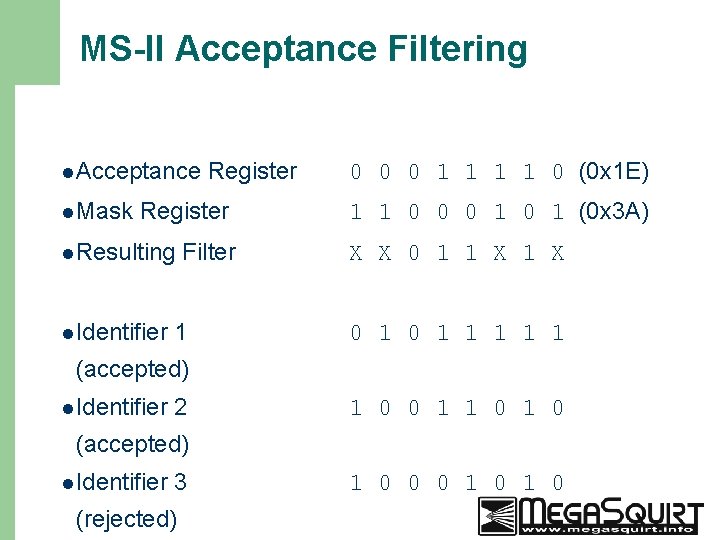

MS-II Acceptance Filtering l Acceptance l Mask Register l Resulting l Identifier Filter 1 0 0 0 1 1 0 (0 x 1 E) 1 1 0 0 0 1 (0 x 3 A) X X 0 1 1 1 (accepted) l Identifier 2 1 0 0 1 1 0 (accepted) l Identifier 48 3 (rejected) 1 0 0 0 1 0

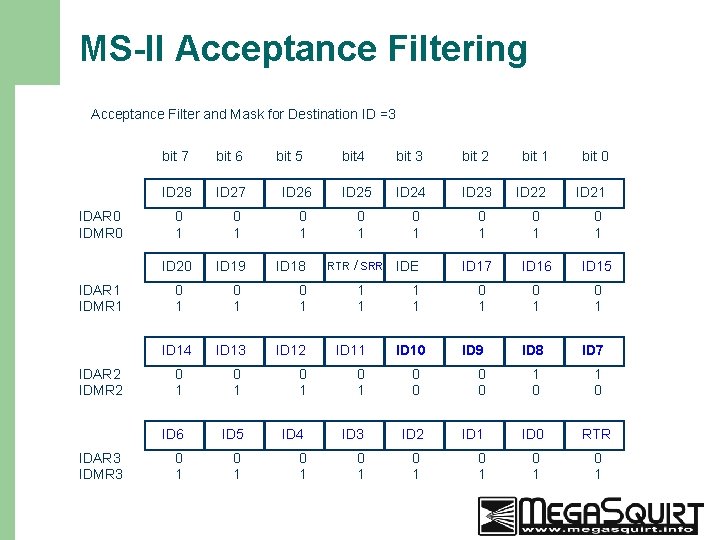

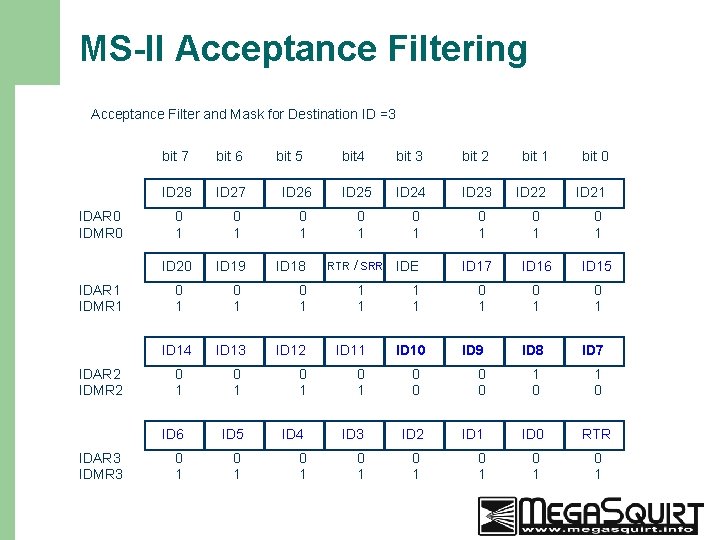

MS-II Acceptance Filtering l 49 Any peripheral on the MS-II CAN bus should set the acceptance filter mask to filter on the destination ID matching the peripheral mask.

MS-II Acceptance Filtering Acceptance Filter and Mask for Destination ID =3 IDAR 0 IDMR 0 bit 7 bit 6 ID 28 ID 27 0 1 ID 20 IDAR 1 IDMR 1 0 1 ID 14 IDAR 2 IDMR 2 IDAR 3 IDMR 3 50 0 1 ID 19 0 1 ID 13 bit 5 ID 26 0 1 ID 18 bit 4 bit 3 bit 2 bit 1 bit 0 ID 25 ID 24 ID 23 ID 22 ID 21 0 1 RTR / SRR 0 1 1 1 ID 12 ID 11 0 1 0 1 ID 6 ID 5 ID 4 ID 3 0 1 0 1 0 1 IDE 1 1 ID 10 0 0 ID 2 0 1 0 1 ID 16 ID 15 0 1 0 1 ID 9 ID 8 ID 7 0 0 1 0 ID 1 ID 0 RTR 0 1 0 1 ID 17

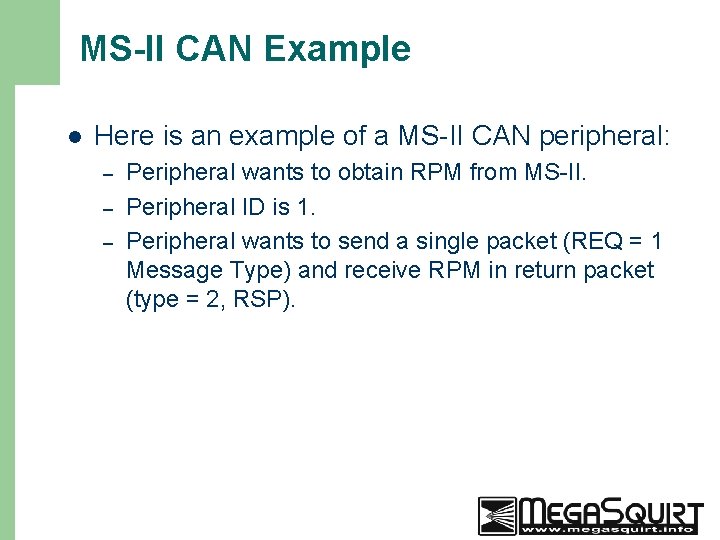

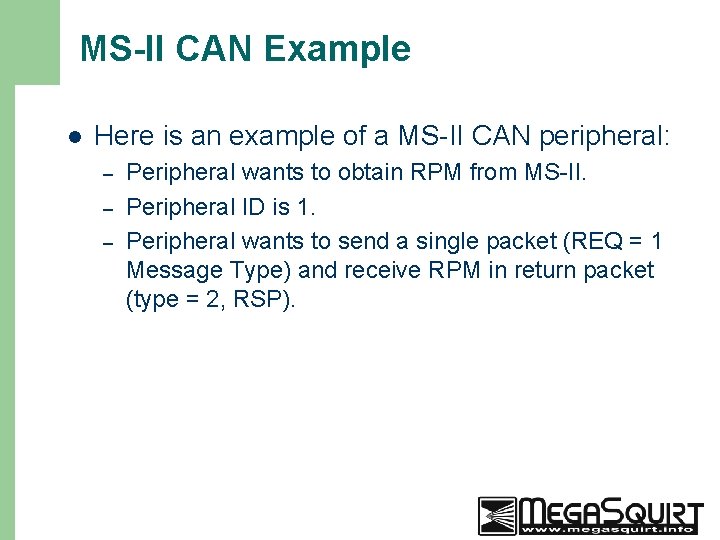

MS-II CAN Example l Here is an example of a MS-II CAN peripheral: – – – 51 Peripheral wants to obtain RPM from MS-II. Peripheral ID is 1. Peripheral wants to send a single packet (REQ = 1 Message Type) and receive RPM in return packet (type = 2, RSP).

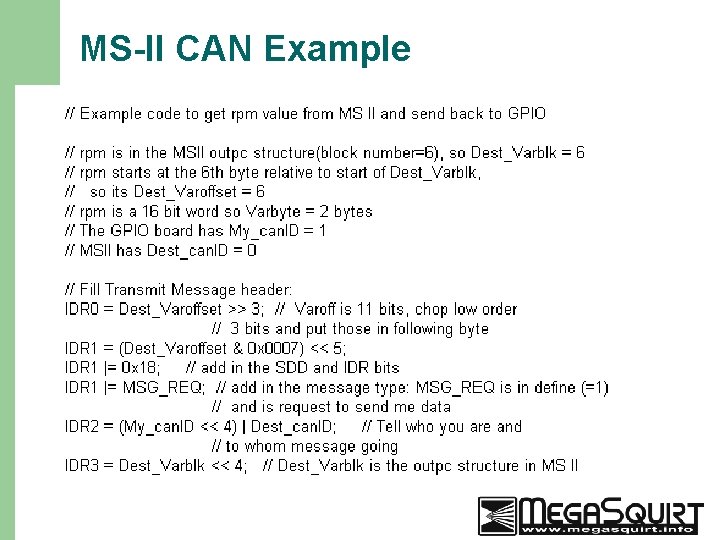

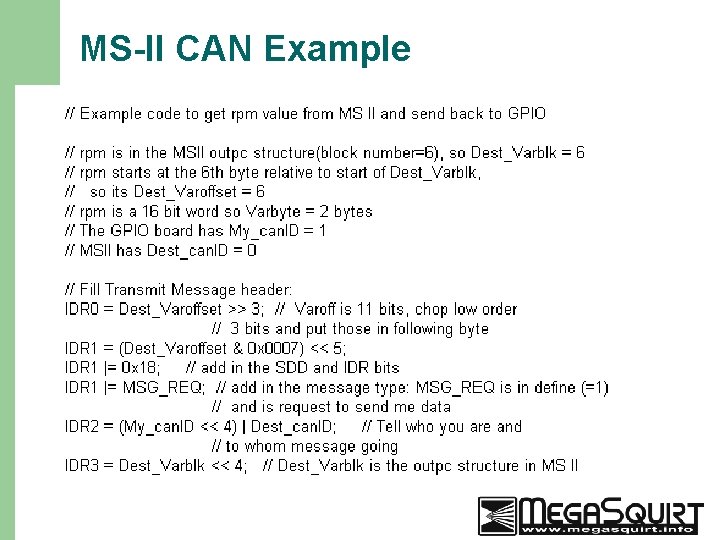

MS-II CAN Example 52

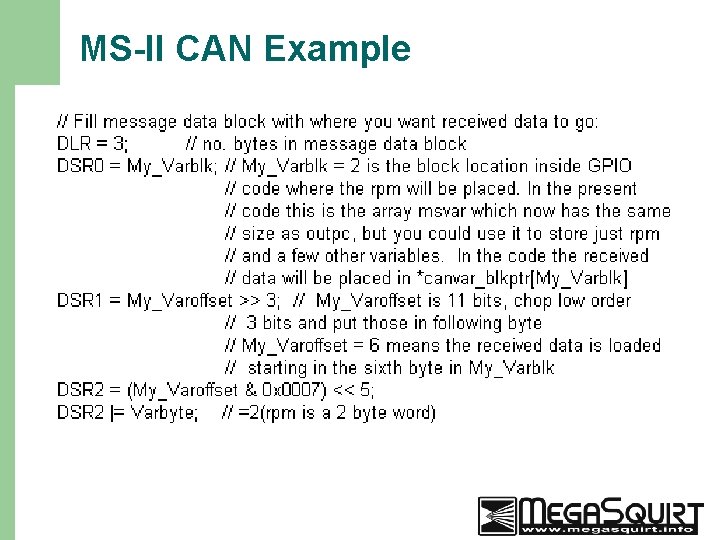

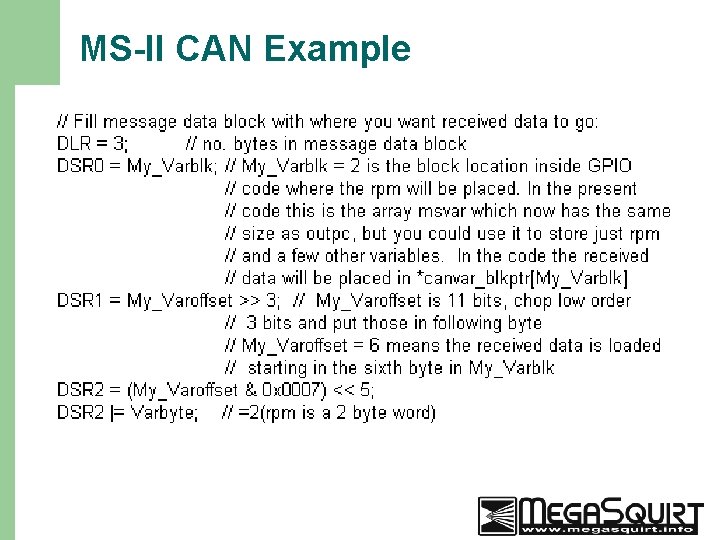

MS-II CAN Example 53

MS-II CAN Example 54