Lecture 21 Today we will n Revisit the

- Slides: 18

Lecture 21 Today we will n Revisit the CMOS inverter, concentrating on logic 0 and logic 1 inputs n Come up with an easy model for MOS transistors involved in CMOS digital computation n Investigate the “complementary” nature of CMOS logic circuits n Introduce CMOS NAND and NOR n Determine the effective R and C for CMOS logic transitions

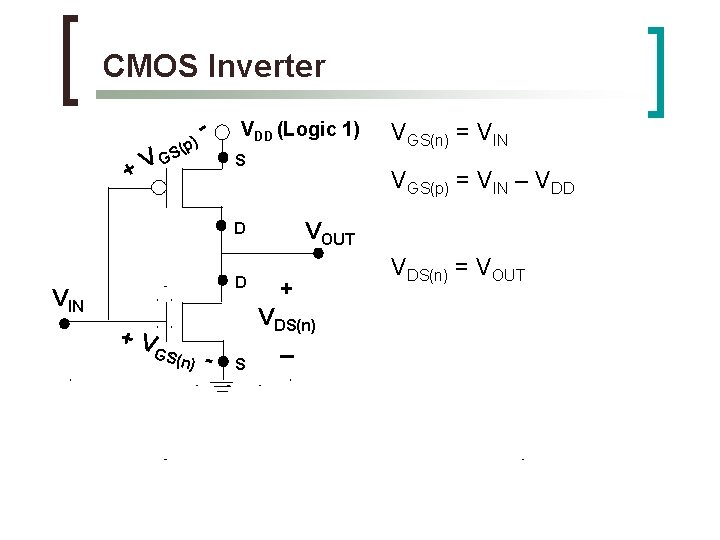

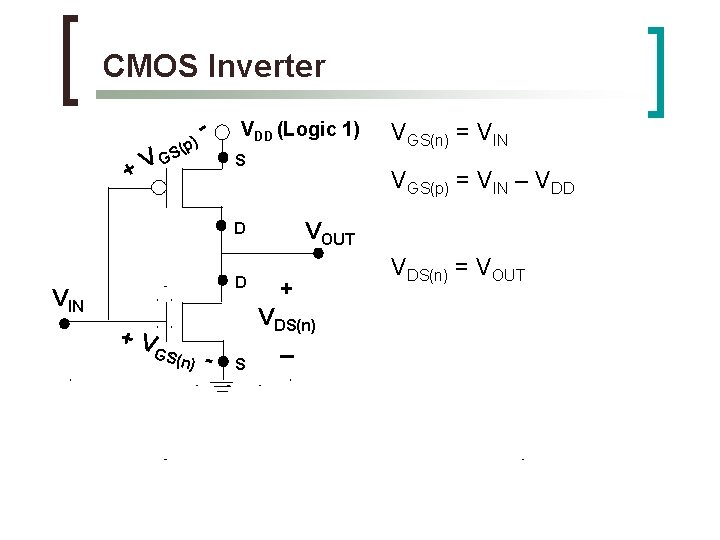

CMOS Inverter GS V + (p) - VDD (Logic 1) S VGS(p) = VIN – VDD VOUT D D VIN +V GS(n ) - S VGS(n) = VIN + VDS(n) _ VDS(n) = VOUT

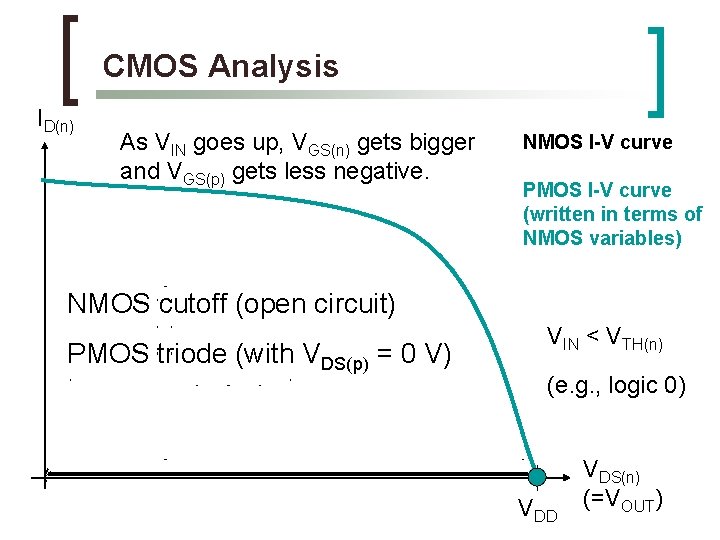

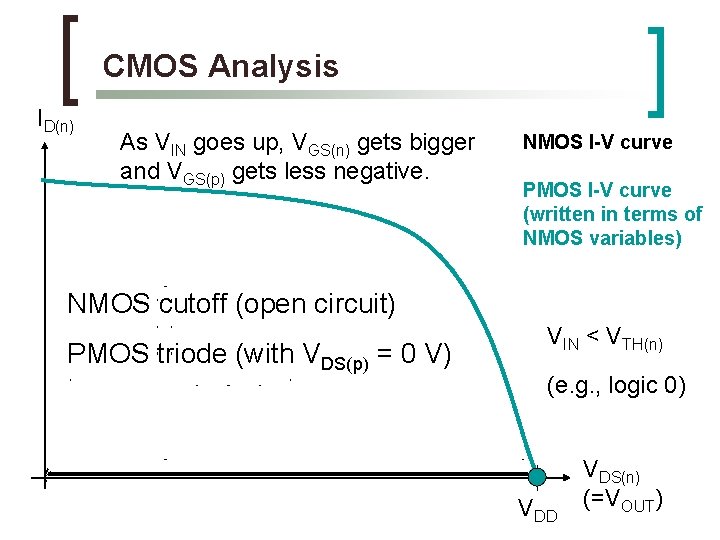

CMOS Analysis ID(n) As VIN goes up, VGS(n) gets bigger and VGS(p) gets less negative. NMOS I-V curve PMOS I-V curve (written in terms of NMOS variables) NMOS cutoff (open circuit) PMOS triode (with VDS(p) = 0 V) VIN < VTH(n) (e. g. , logic 0) VDD VDS(n) (=VOUT)

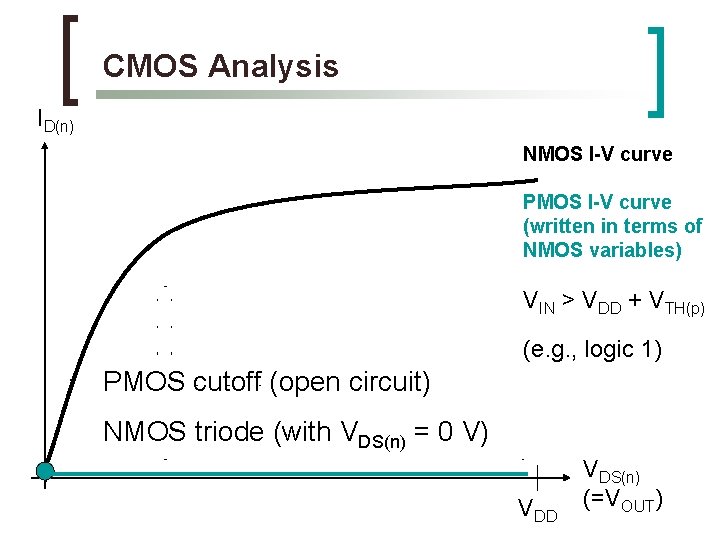

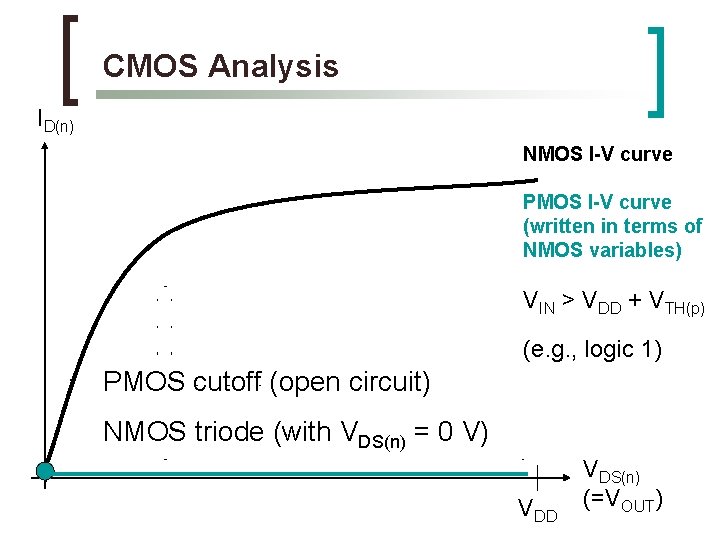

CMOS Analysis ID(n) NMOS I-V curve PMOS I-V curve (written in terms of NMOS variables) VIN > VDD + VTH(p) (e. g. , logic 1) PMOS cutoff (open circuit) NMOS triode (with VDS(n) = 0 V) VDD VDS(n) (=VOUT)

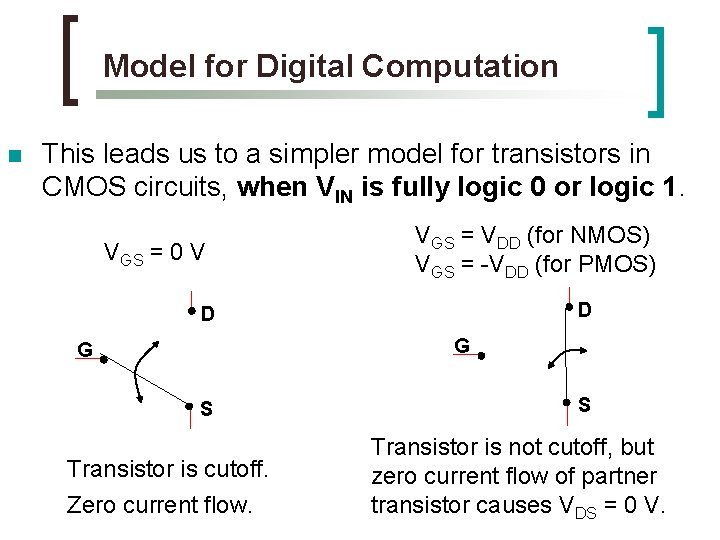

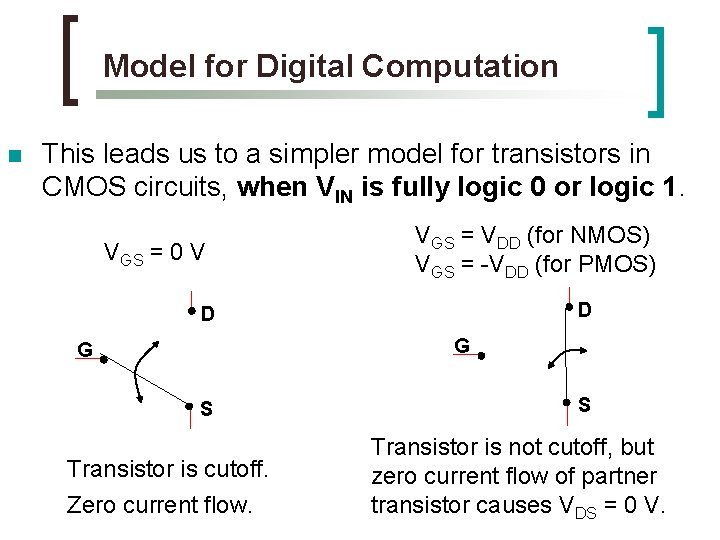

Model for Digital Computation n This leads us to a simpler model for transistors in CMOS circuits, when VIN is fully logic 0 or logic 1. VGS = 0 V VGS = VDD (for NMOS) VGS = -VDD (for PMOS) D D G G S Transistor is cutoff. Zero current flow. S Transistor is not cutoff, but zero current flow of partner transistor causes VDS = 0 V.

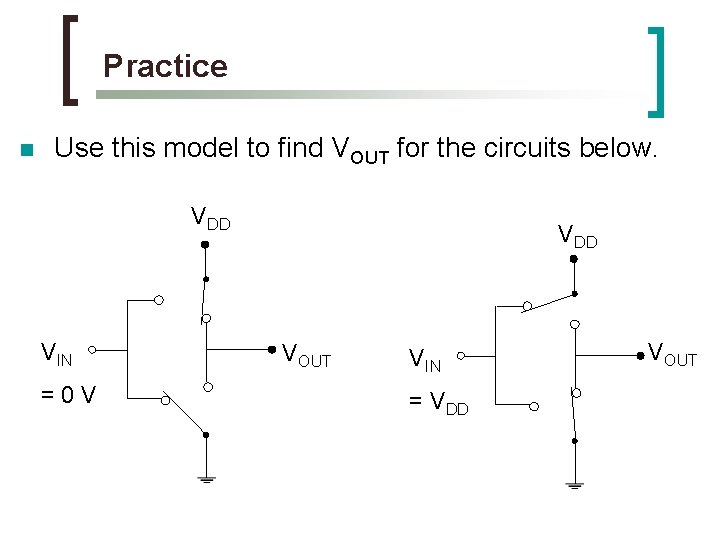

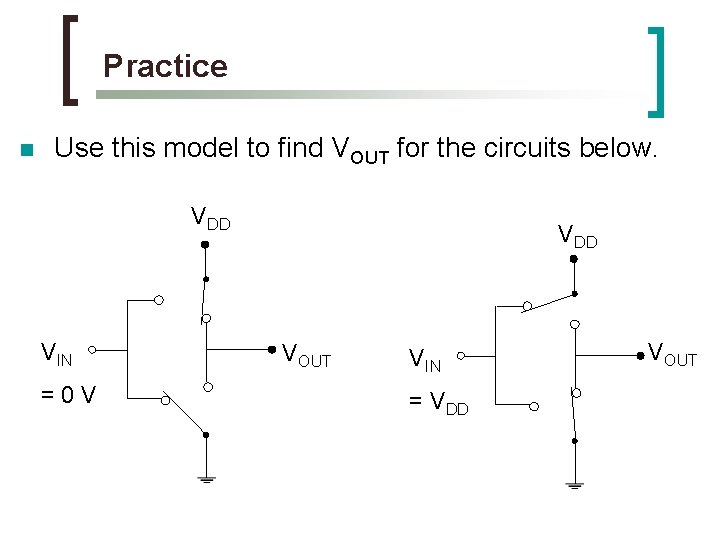

Practice n Use this model to find VOUT for the circuits below. VDD VIN =0 V VDD VOUT VIN = VDD VOUT

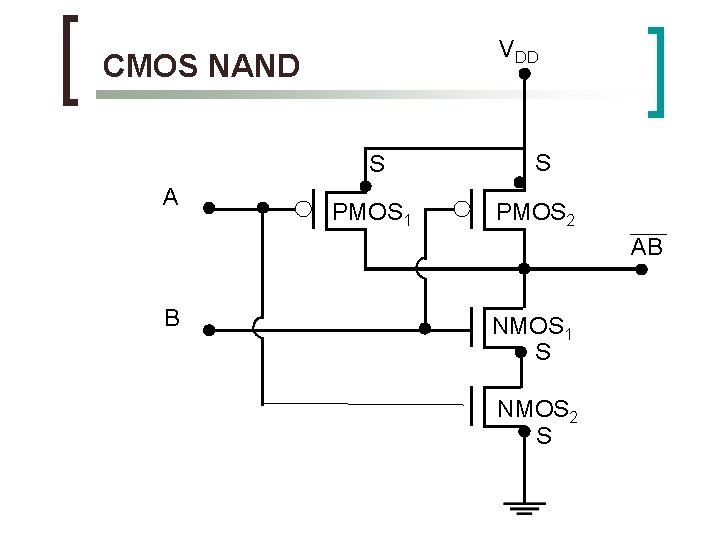

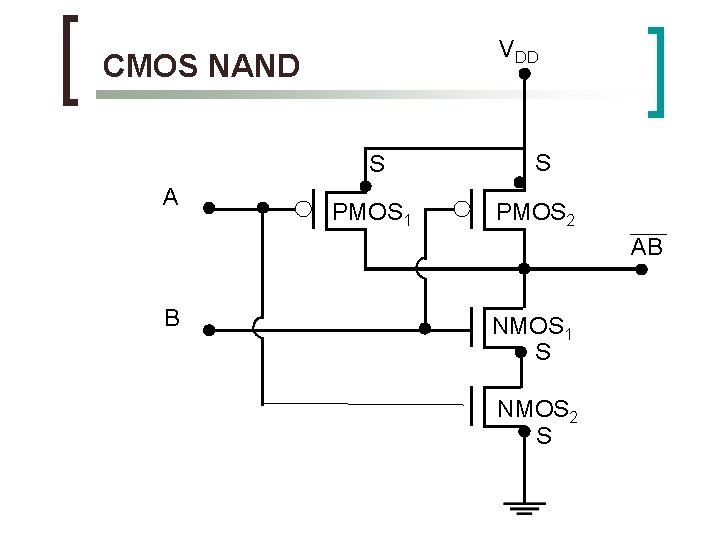

VDD CMOS NAND S A PMOS 1 S PMOS 2 AB B NMOS 1 S NMOS 2 S

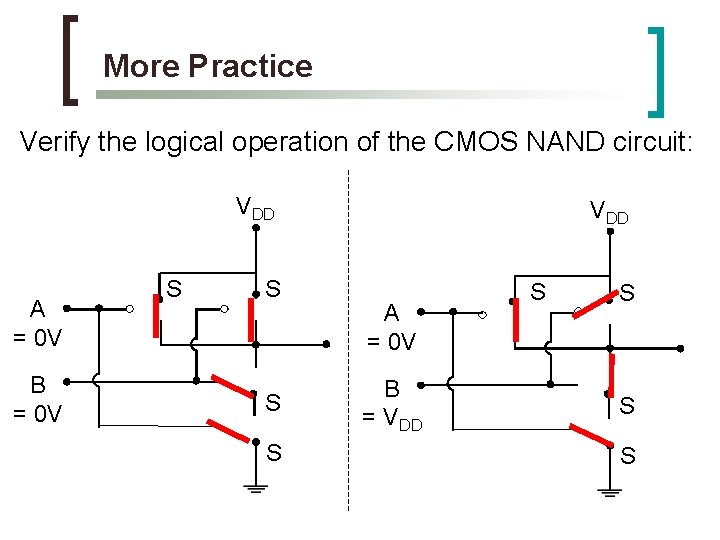

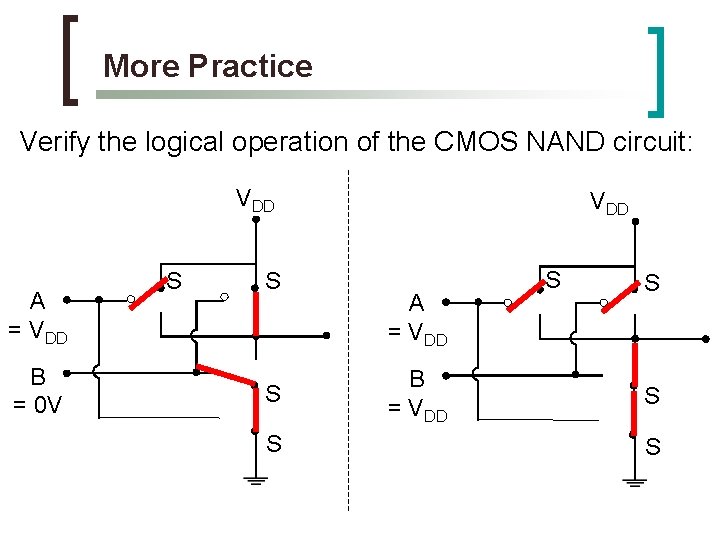

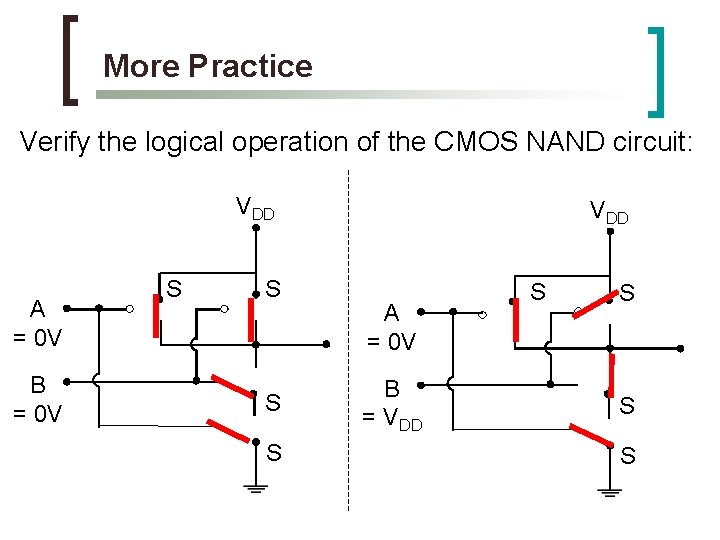

More Practice Verify the logical operation of the CMOS NAND circuit: VDD A = 0 V B = 0 V S S VDD A = 0 V B = VDD S S

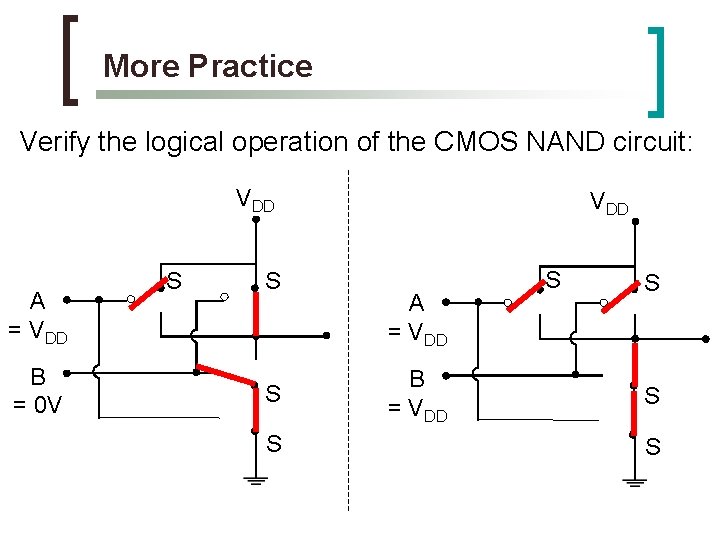

More Practice Verify the logical operation of the CMOS NAND circuit: VDD A = VDD B = 0 V S S VDD A = VDD B = VDD S S

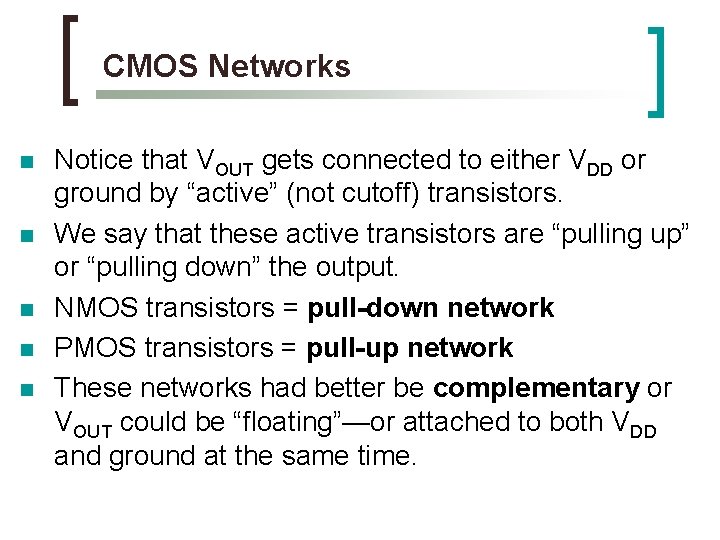

CMOS Networks n n n Notice that VOUT gets connected to either VDD or ground by “active” (not cutoff) transistors. We say that these active transistors are “pulling up” or “pulling down” the output. NMOS transistors = pull-down network PMOS transistors = pull-up network These networks had better be complementary or VOUT could be “floating”—or attached to both VDD and ground at the same time.

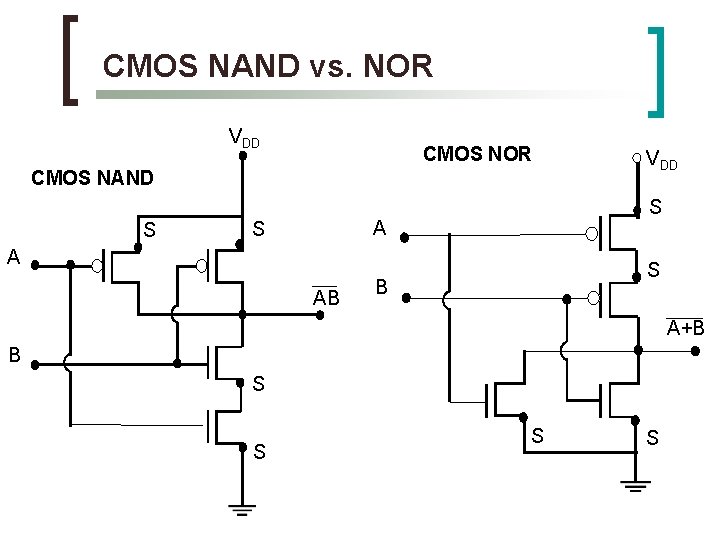

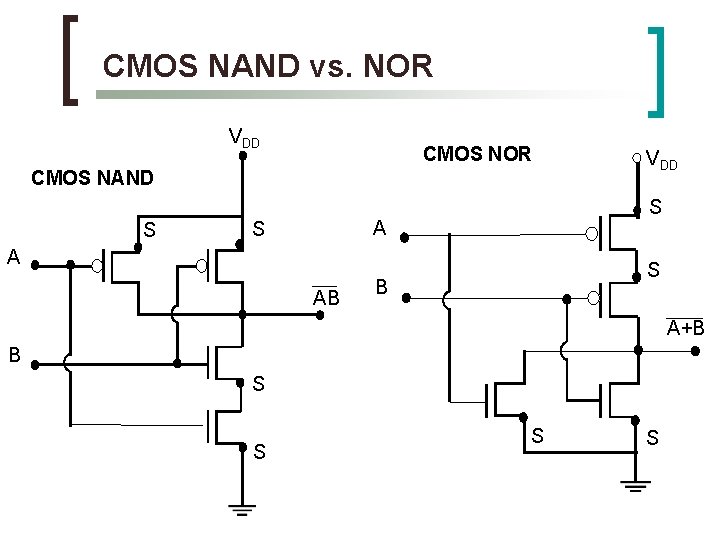

CMOS NAND vs. NOR VDD CMOS NOR CMOS NAND S S A AB VDD S B A+B B S S

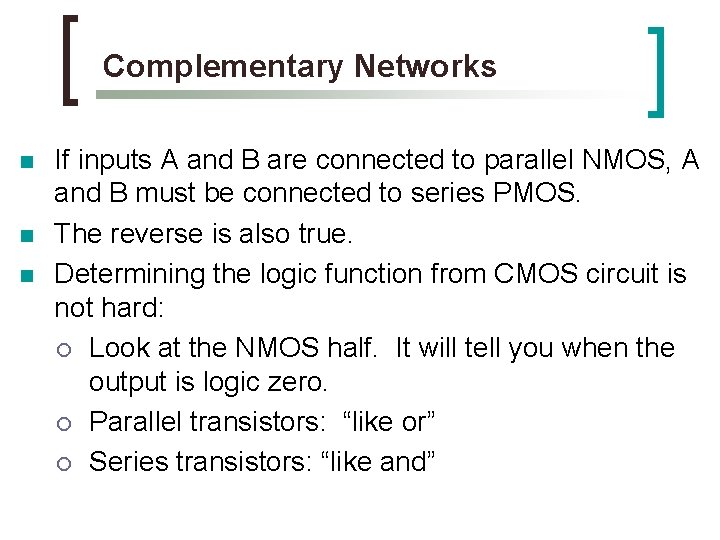

Complementary Networks n n n If inputs A and B are connected to parallel NMOS, A and B must be connected to series PMOS. The reverse is also true. Determining the logic function from CMOS circuit is not hard: ¡ Look at the NMOS half. It will tell you when the output is logic zero. ¡ Parallel transistors: “like or” ¡ Series transistors: “like and”

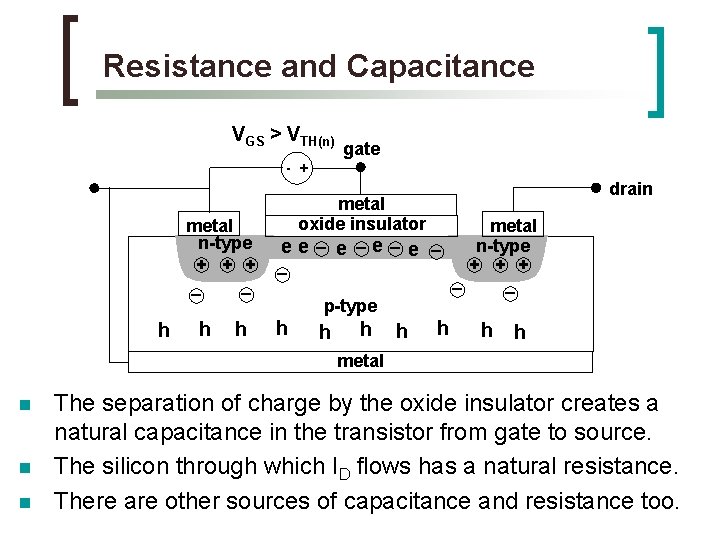

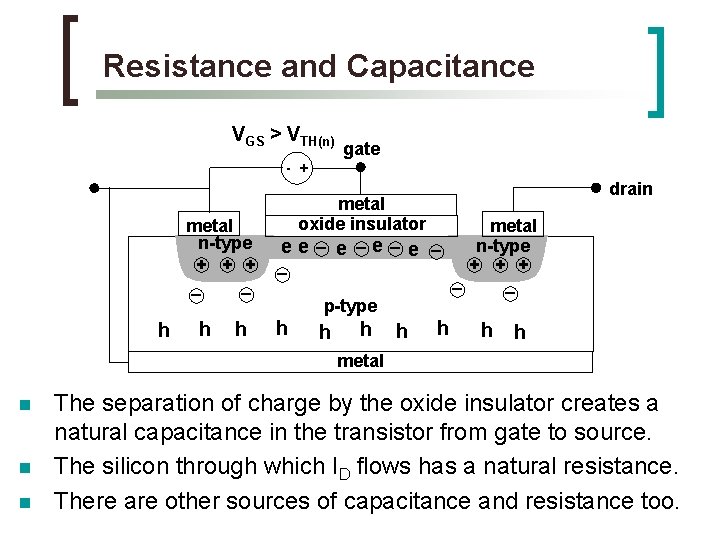

Resistance and Capacitance VGS > VTH(n) gate - + metal n-type + + + _ _ h h h metal oxide insulator ee_ e _ _ drain metal n-type + + + _ _ p-type h h h h metal n n n The separation of charge by the oxide insulator creates a natural capacitance in the transistor from gate to source. The silicon through which ID flows has a natural resistance. There are other sources of capacitance and resistance too.

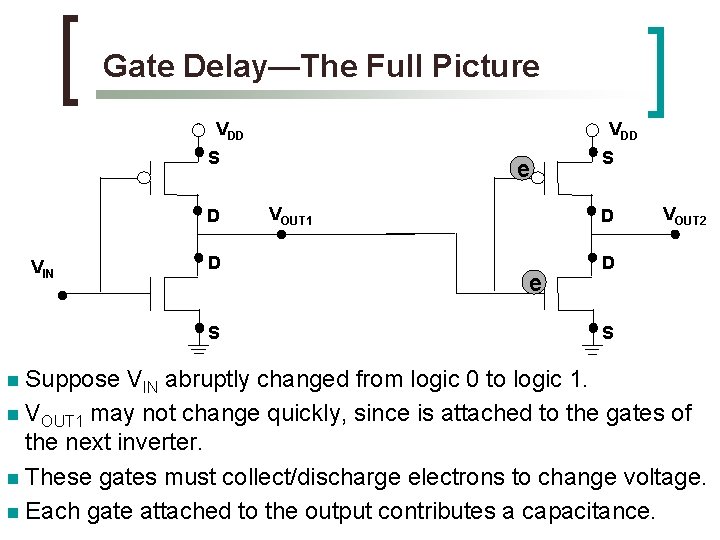

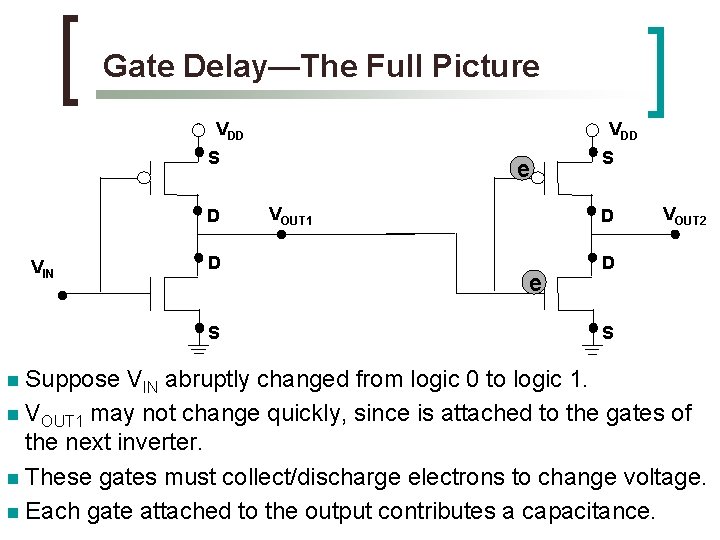

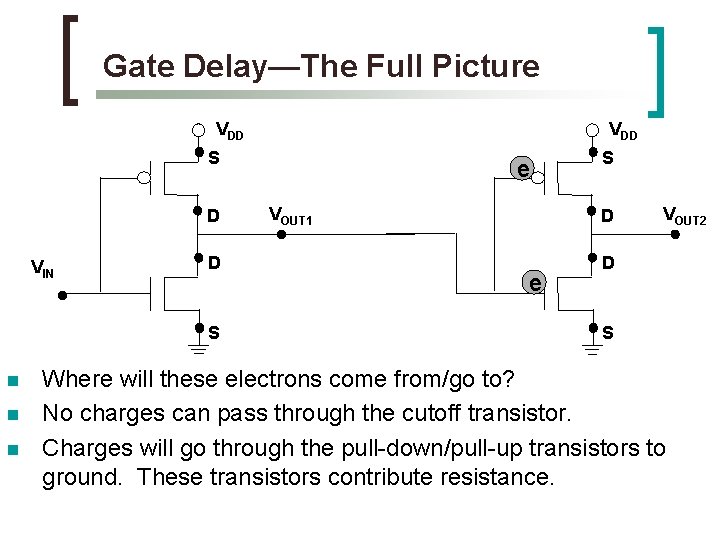

Gate Delay—The Full Picture VDD S D VIN D S n Suppose e VOUT 1 S D e VOUT 2 D S VIN abruptly changed from logic 0 to logic 1. n VOUT 1 may not change quickly, since is attached to the gates of the next inverter. n These gates must collect/discharge electrons to change voltage. n Each gate attached to the output contributes a capacitance.

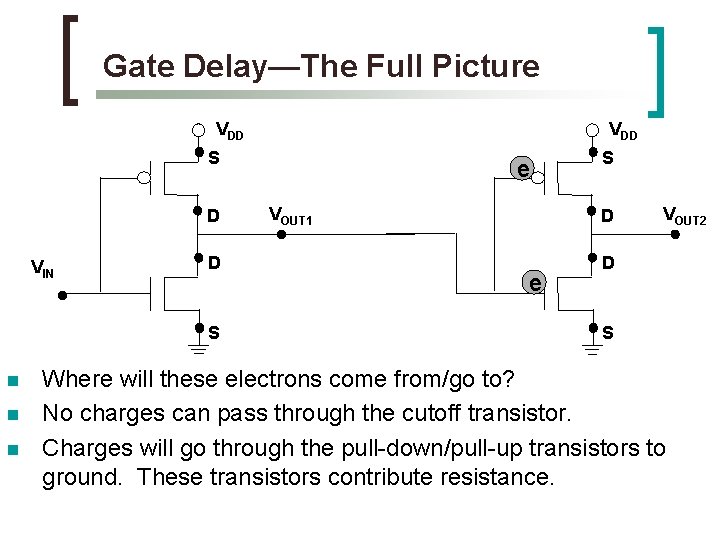

Gate Delay—The Full Picture VDD S D VIN D S n n n e VOUT 1 S D e VOUT 2 D S Where will these electrons come from/go to? No charges can pass through the cutoff transistor. Charges will go through the pull-down/pull-up transistors to ground. These transistors contribute resistance.

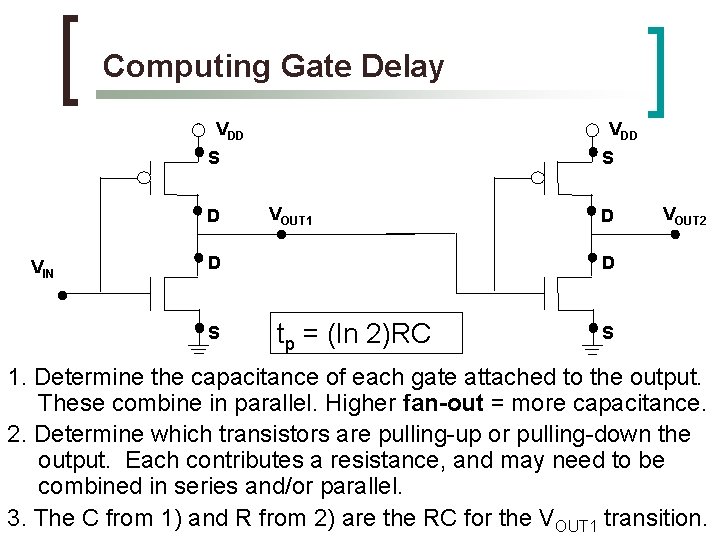

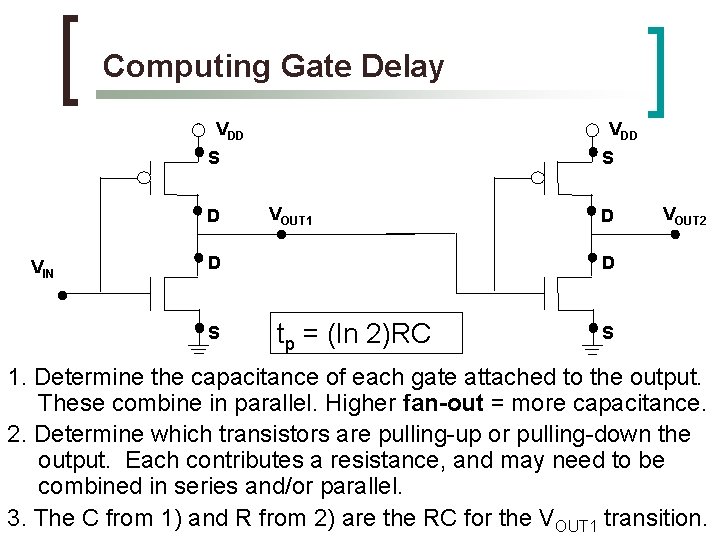

Computing Gate Delay VDD S D VIN S VOUT 1 D S D VOUT 2 D tp = (ln 2)RC S 1. Determine the capacitance of each gate attached to the output. These combine in parallel. Higher fan-out = more capacitance. 2. Determine which transistors are pulling-up or pulling-down the output. Each contributes a resistance, and may need to be combined in series and/or parallel. 3. The C from 1) and R from 2) are the RC for the VOUT 1 transition.

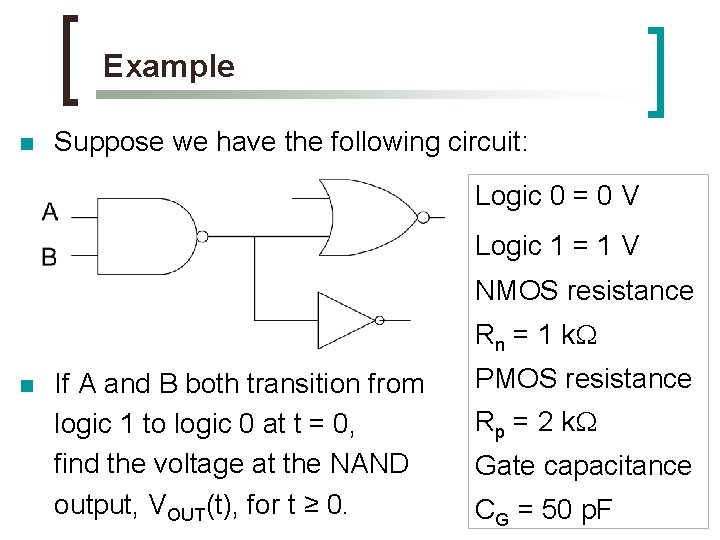

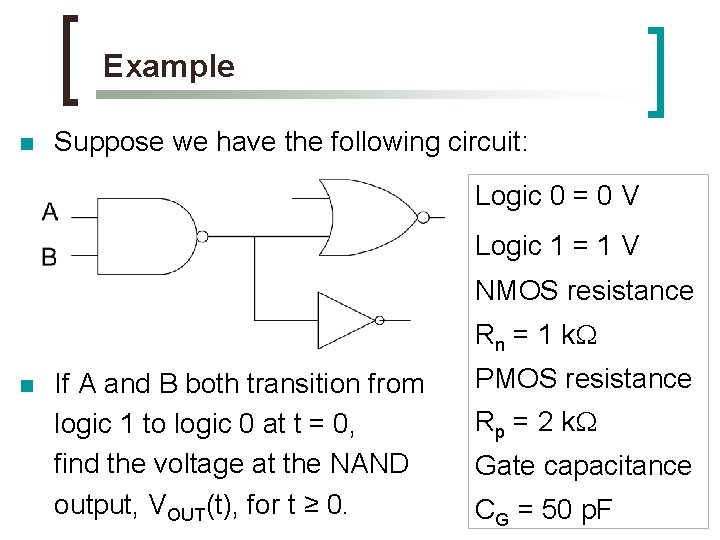

Example n Suppose we have the following circuit: Logic 0 = 0 V Logic 1 = 1 V NMOS resistance Rn = 1 k. W n If A and B both transition from logic 1 to logic 0 at t = 0, find the voltage at the NAND output, VOUT(t), for t ≥ 0. PMOS resistance Rp = 2 k. W Gate capacitance CG = 50 p. F

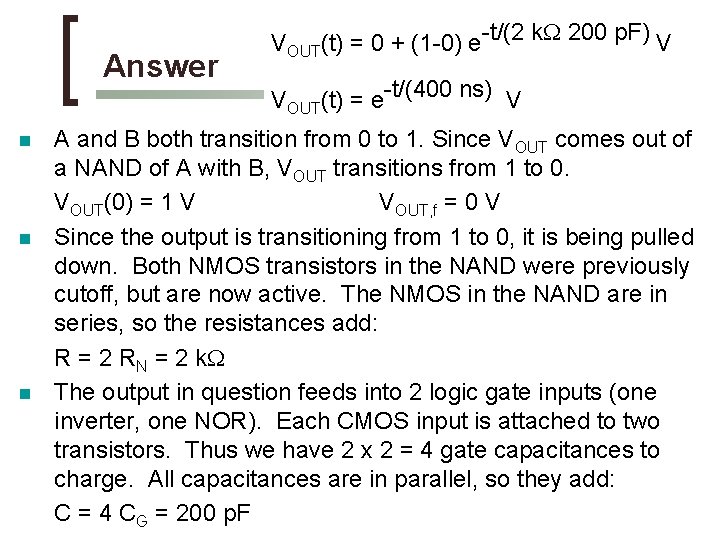

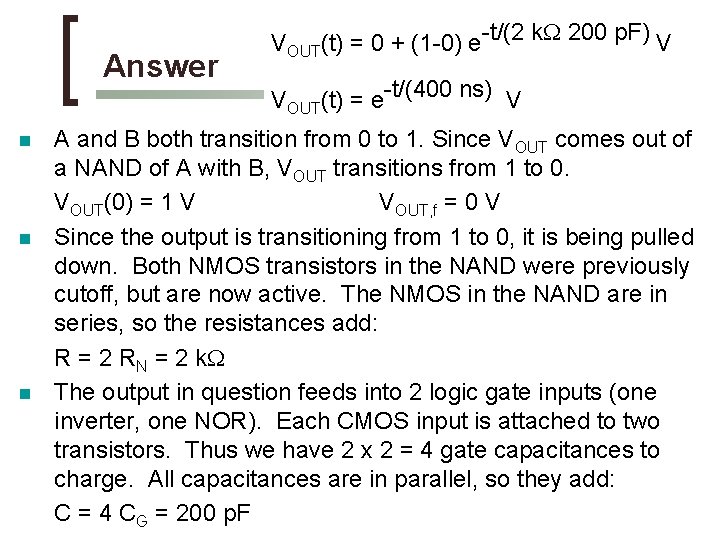

Answer n n n VOUT(t) = 0 + (1 -0) e-t/(2 k. W 200 p. F) V VOUT(t) = e-t/(400 ns) V A and B both transition from 0 to 1. Since VOUT comes out of a NAND of A with B, VOUT transitions from 1 to 0. VOUT(0) = 1 V VOUT, f = 0 V Since the output is transitioning from 1 to 0, it is being pulled down. Both NMOS transistors in the NAND were previously cutoff, but are now active. The NMOS in the NAND are in series, so the resistances add: R = 2 RN = 2 k. W The output in question feeds into 2 logic gate inputs (one inverter, one NOR). Each CMOS input is attached to two transistors. Thus we have 2 x 2 = 4 gate capacitances to charge. All capacitances are in parallel, so they add: C = 4 CG = 200 p. F