DSP Systems Implementation Course Seminar Tehran University Electrical

- Slides: 48

DSP Systems Implementation Course Seminar Tehran University Electrical And Computer Engineering Department Spring 2004 DSP Systems Implementation

A Practical Example Of DSP System Design, ADSL Modem DMT Engine DSP Systems Implementation 2

Outline q A Glance At ADSL Modems Structure q Digital System Design Methodology q Design Flow q Finite Precision Arithmetic Libraries q ADSL Modulator/Demodulator Design q ADSL Time Equalizer Design DSP Systems Implementation 3

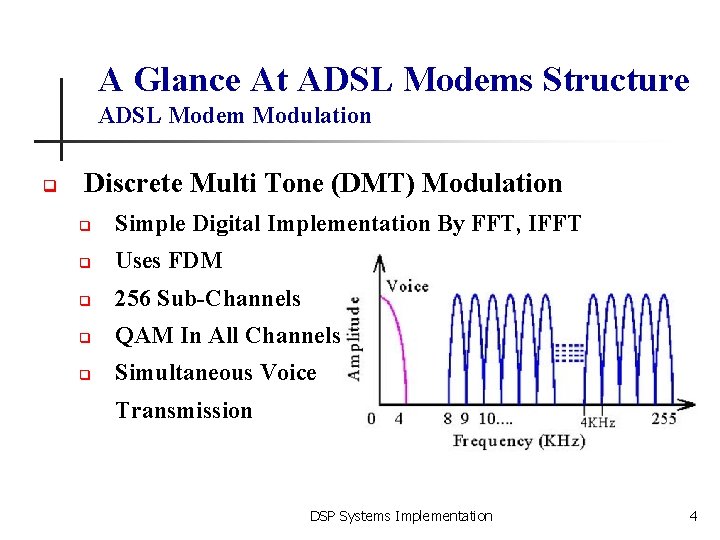

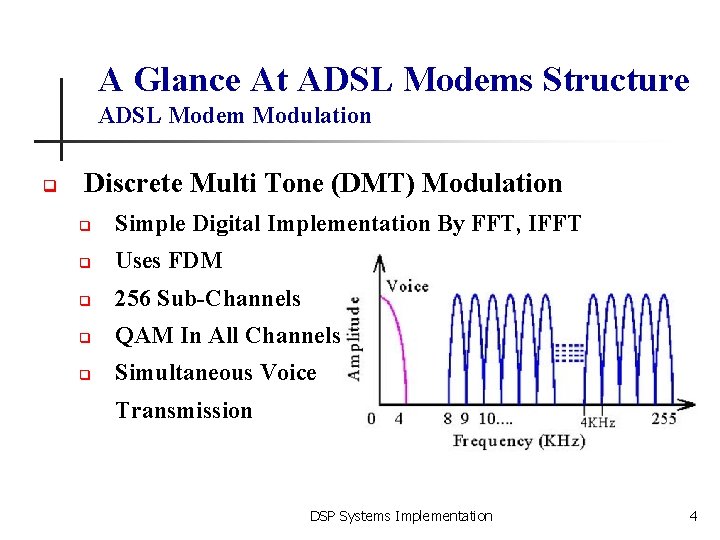

A Glance At ADSL Modems Structure ADSL Modem Modulation q Discrete Multi Tone (DMT) Modulation q Simple Digital Implementation By FFT, IFFT q Uses FDM q 256 Sub-Channels q QAM In All Channels q Simultaneous Voice Transmission DSP Systems Implementation 4

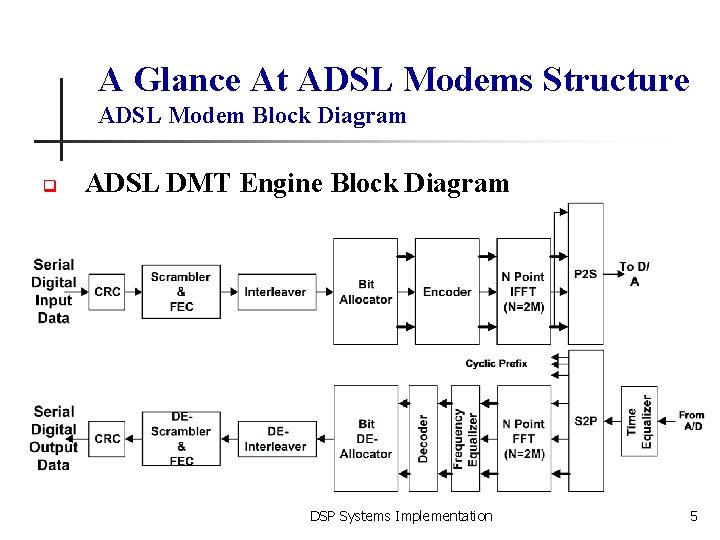

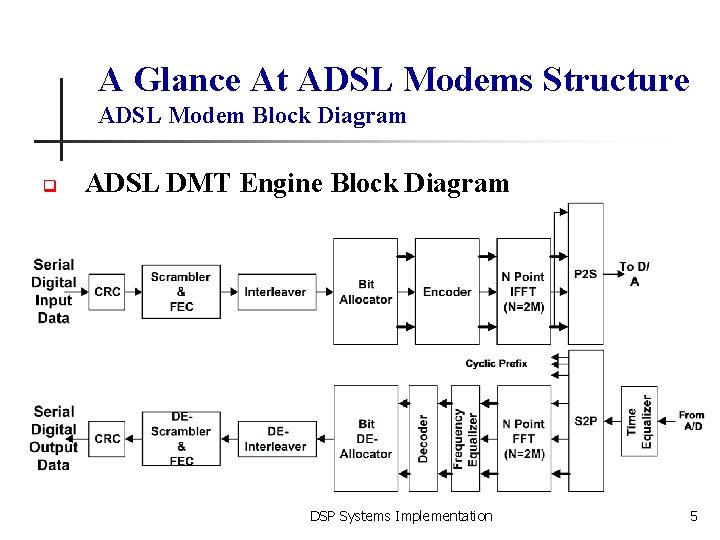

A Glance At ADSL Modems Structure ADSL Modem Block Diagram q ADSL DMT Engine Block Diagram DSP Systems Implementation 5

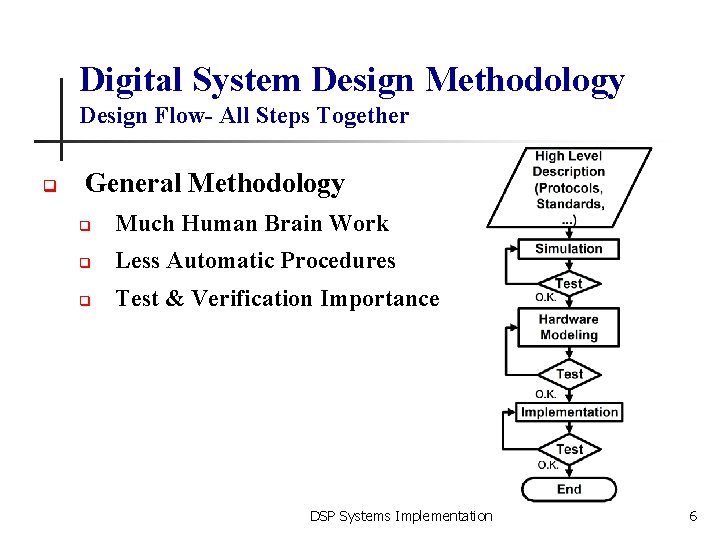

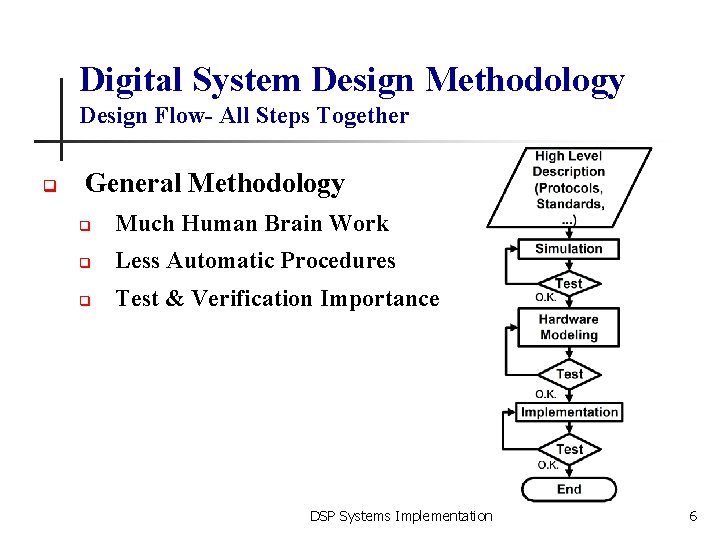

Digital System Design Methodology Design Flow- All Steps Together q General Methodology q Much Human Brain Work q Less Automatic Procedures q Test & Verification Importance DSP Systems Implementation 6

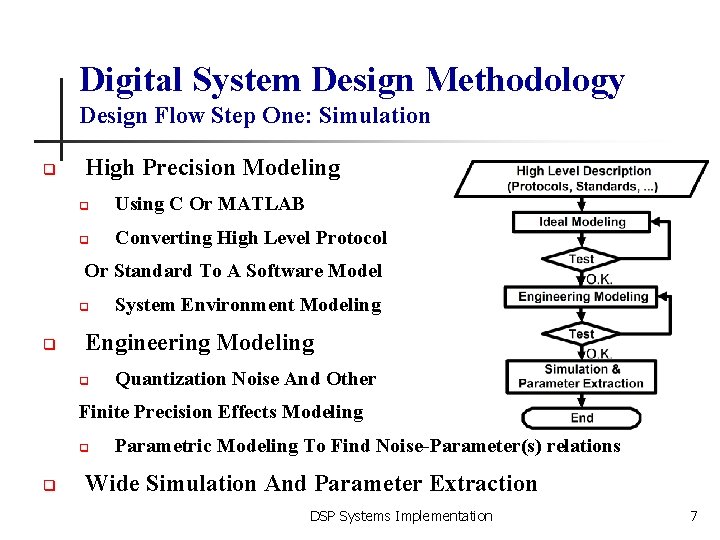

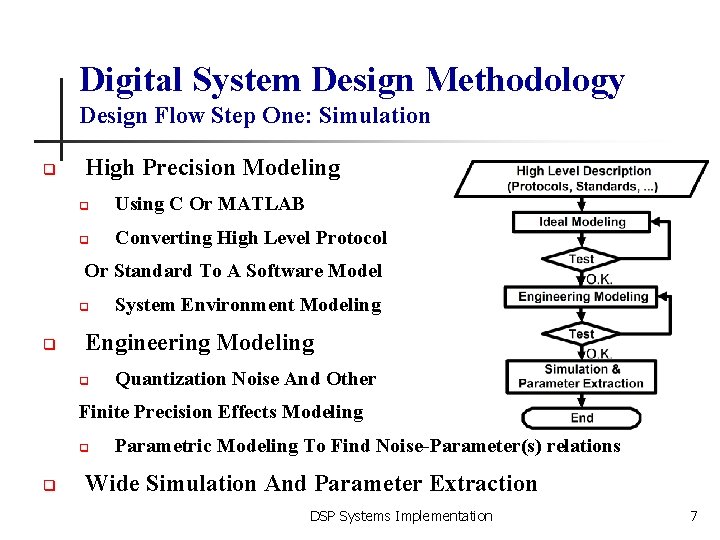

Digital System Design Methodology Design Flow Step One: Simulation q High Precision Modeling q Using C Or MATLAB q Converting High Level Protocol Or Standard To A Software Model q q System Environment Modeling Engineering Modeling q Quantization Noise And Other Finite Precision Effects Modeling q q Parametric Modeling To Find Noise-Parameter(s) relations Wide Simulation And Parameter Extraction DSP Systems Implementation 7

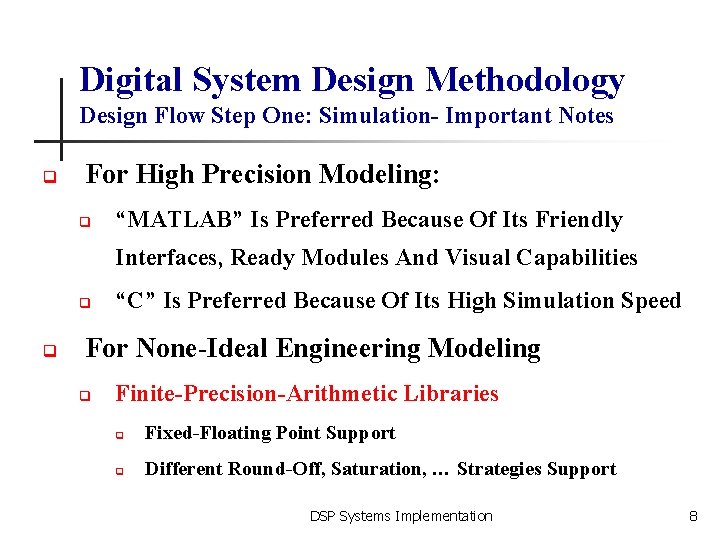

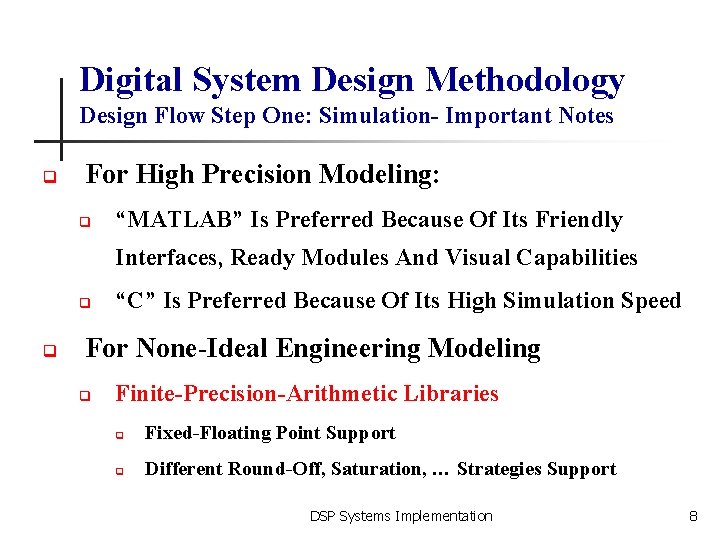

Digital System Design Methodology Design Flow Step One: Simulation- Important Notes q For High Precision Modeling: q “MATLAB” Is Preferred Because Of Its Friendly Interfaces, Ready Modules And Visual Capabilities q q “C” Is Preferred Because Of Its High Simulation Speed For None-Ideal Engineering Modeling q Finite-Precision-Arithmetic Libraries q Fixed-Floating Point Support q Different Round-Off, Saturation, … Strategies Support DSP Systems Implementation 8

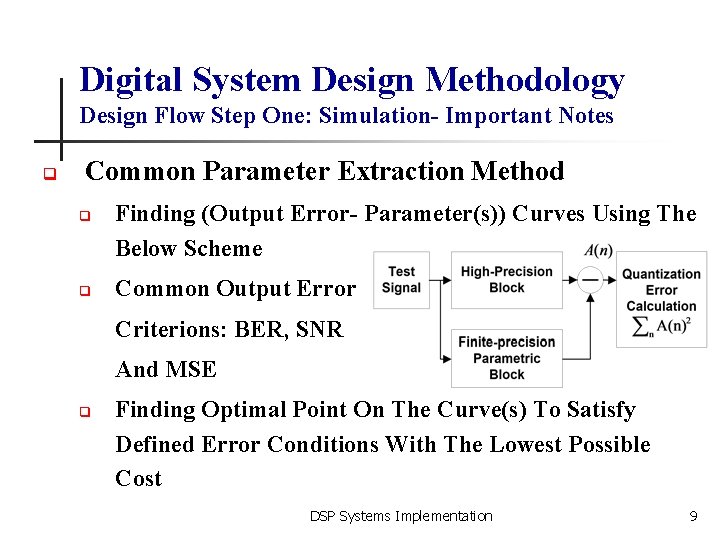

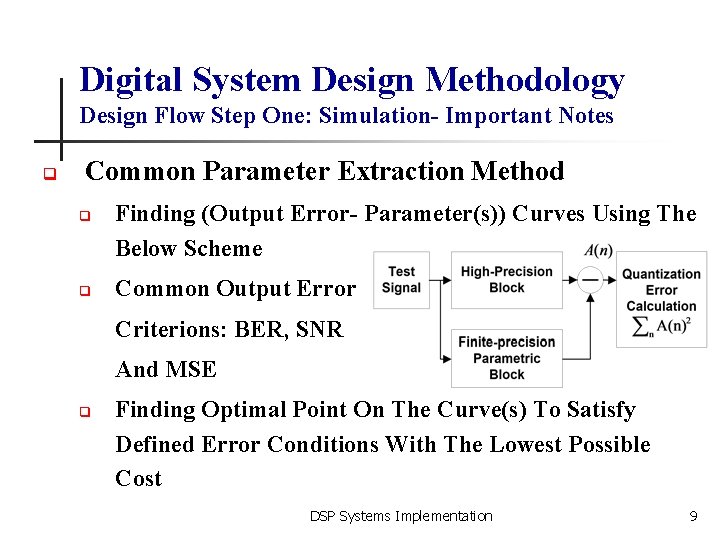

Digital System Design Methodology Design Flow Step One: Simulation- Important Notes q Common Parameter Extraction Method q q Finding (Output Error- Parameter(s)) Curves Using The Below Scheme Common Output Error Criterions: BER, SNR And MSE q Finding Optimal Point On The Curve(s) To Satisfy Defined Error Conditions With The Lowest Possible Cost DSP Systems Implementation 9

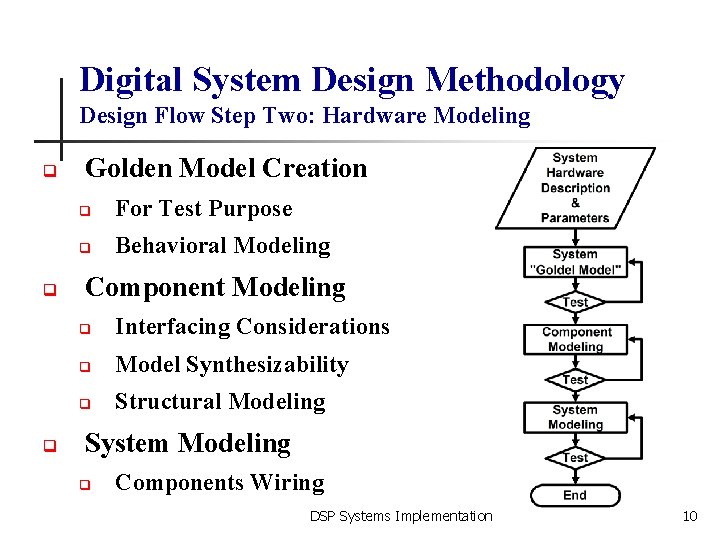

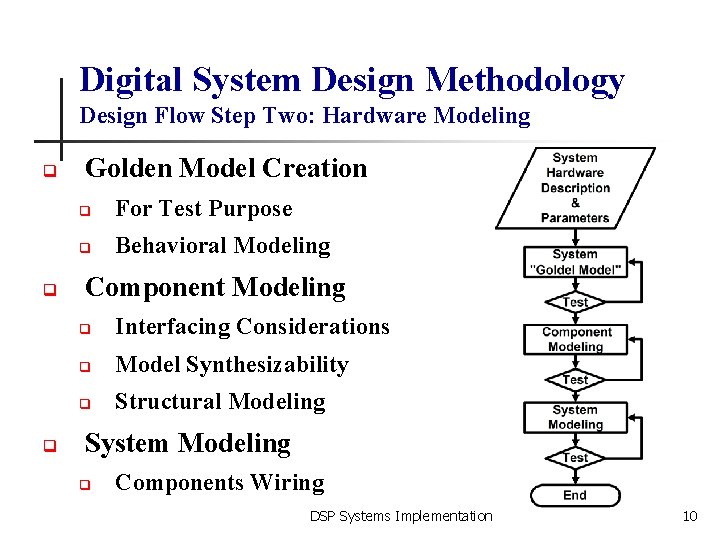

Digital System Design Methodology Design Flow Step Two: Hardware Modeling q q q Golden Model Creation q For Test Purpose q Behavioral Modeling Component Modeling q Interfacing Considerations q Model Synthesizability q Structural Modeling System Modeling q Components Wiring DSP Systems Implementation 10

Digital System Design Methodology Design Flow Step Two: Hardware Modeling- Important Notes q q Golden Model Creation q Simplifies Test Of The Final Model q Functionally Same As C Or MATLAB Model q Not Necessarily Synthesizable Or Efficient Component Modeling q q Common Design Strategy: Top-Down Design, Bottom. Up wiring Extracted Parameters From Simulation Step, Inserted Into Components DSP Systems Implementation 11

Digital System Design Methodology Design Flow Step Three: Implementation q FPGA Implementation q q FPGA Specific HDL Languages Such As AHDL Usually Better Performance When Lower Level Components Described @ RTL Level Hardware Emulation Systems ASIC Implementation DSP Systems Implementation 12

Digital System Design Methodology Finite-Precision-Arithmetic Libraries q q C Does Not Have Sufficient Capabilities Needed For Bit. True Modeling Special Libraries Need To Be Developed That Support q q Different Finite-Length Number Representations (Fixed, Float, …) Different Finite-Length Sign Representations (2’s Complement, Sign And Magnitude, …) q Basic Arithmetic Operations With Finite Precision (Sum, Sub, …) q Different Round-Off Strategies (Truncation, Rounding, …) q Different Overflow Strategies (Maximum Saturation, Zero Saturation, Wrap Around, …) DSP Systems Implementation 13

Digital System Design Methodology Finite-Precision-Arithmetic Libraries q Using The Libraries, The System Should Be Modeled And Simulated With Different Library Options q q All Trade-Offs And Strategies Are Extracted q Number Representation Method (Fixed, Float, …) q Sign Representation q Round-Off Strategy q Overflow Strategy Each Trade-Off Or Strategy Corresponds To A Different Hardware Implementation DSP Systems Implementation 14

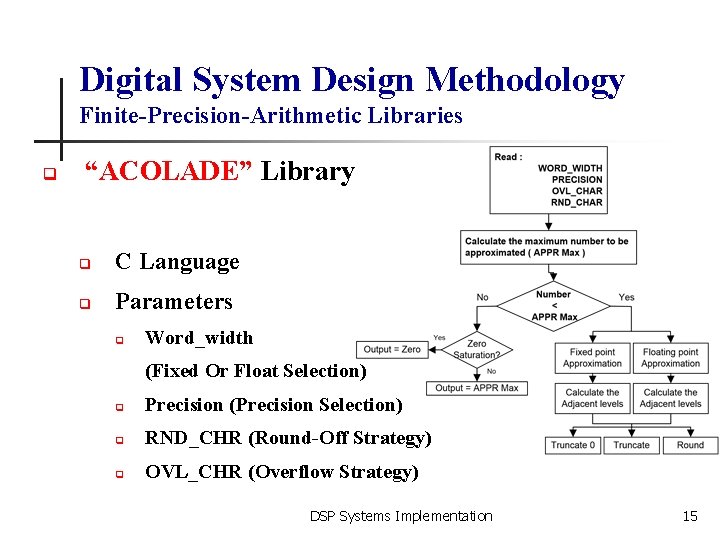

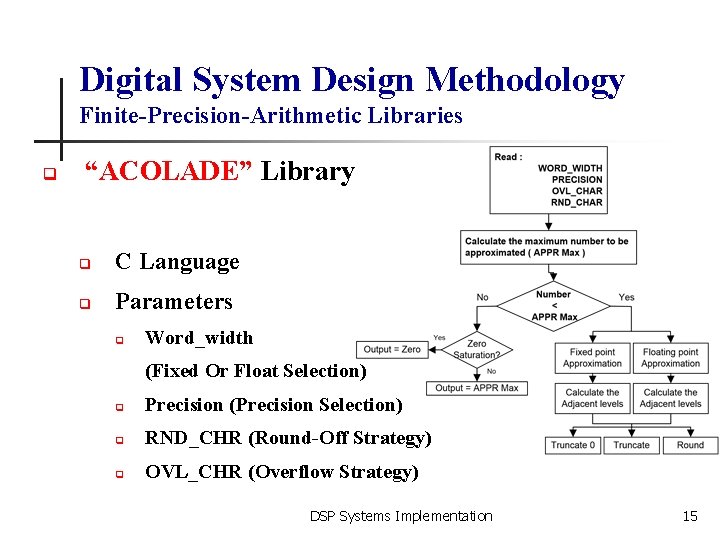

Digital System Design Methodology Finite-Precision-Arithmetic Libraries q “ACOLADE” Library q C Language q Parameters q Word_width (Fixed Or Float Selection) q Precision (Precision Selection) q RND_CHR (Round-Off Strategy) q OVL_CHR (Overflow Strategy) DSP Systems Implementation 15

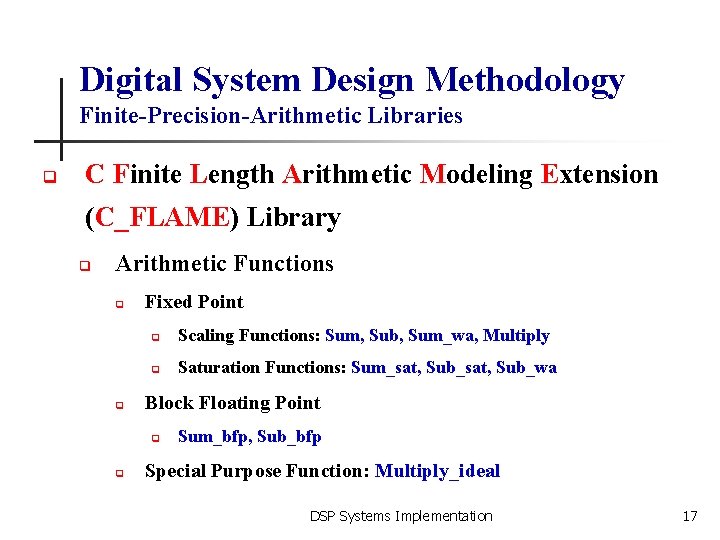

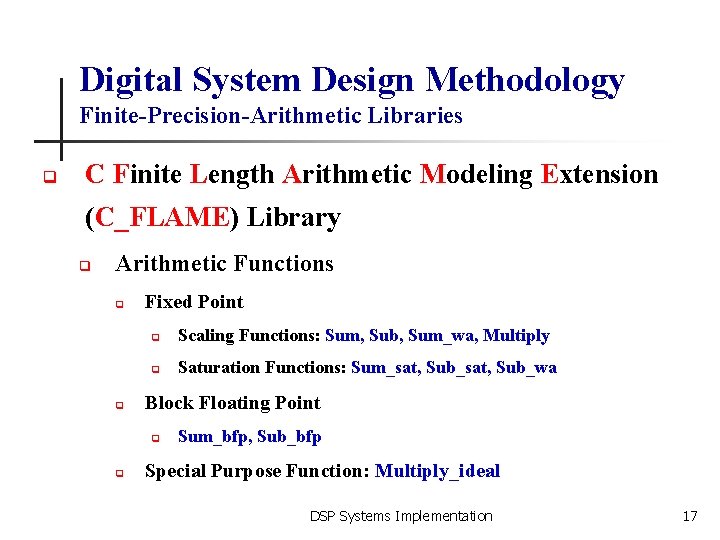

Digital System Design Methodology Finite-Precision-Arithmetic Libraries q C Finite Length Arithmetic Modeling Extension, C_FLAME Library q Developed In UT VLSI Lab q Support Truncation And Rounding Round-Off Strategies q Library Interface Functions: Dec 2 bin, Bin 2 dec q Negation Function: Negate DSP Systems Implementation 16

Digital System Design Methodology Finite-Precision-Arithmetic Libraries q C Finite Length Arithmetic Modeling Extension (C_FLAME) Library q Arithmetic Functions q q Fixed Point q Scaling Functions: Sum, Sub, Sum_wa, Multiply q Saturation Functions: Sum_sat, Sub_wa Block Floating Point q q Sum_bfp, Sub_bfp Special Purpose Function: Multiply_ideal DSP Systems Implementation 17

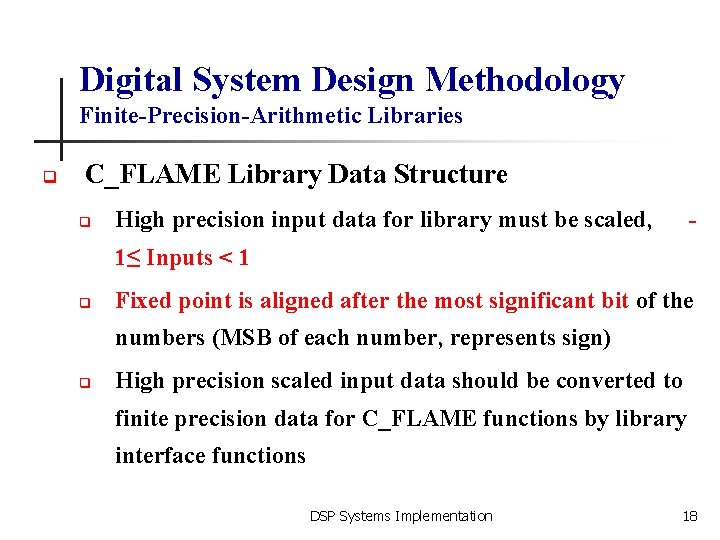

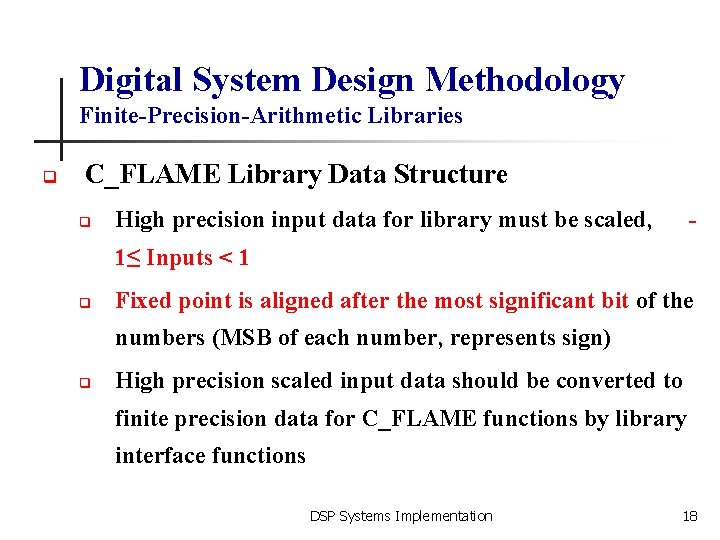

Digital System Design Methodology Finite-Precision-Arithmetic Libraries q C_FLAME Library Data Structure q High precision input data for library must be scaled, - 1≤ Inputs < 1 q Fixed point is aligned after the most significant bit of the numbers (MSB of each number, represents sign) q High precision scaled input data should be converted to finite precision data for C_FLAME functions by library interface functions DSP Systems Implementation 18

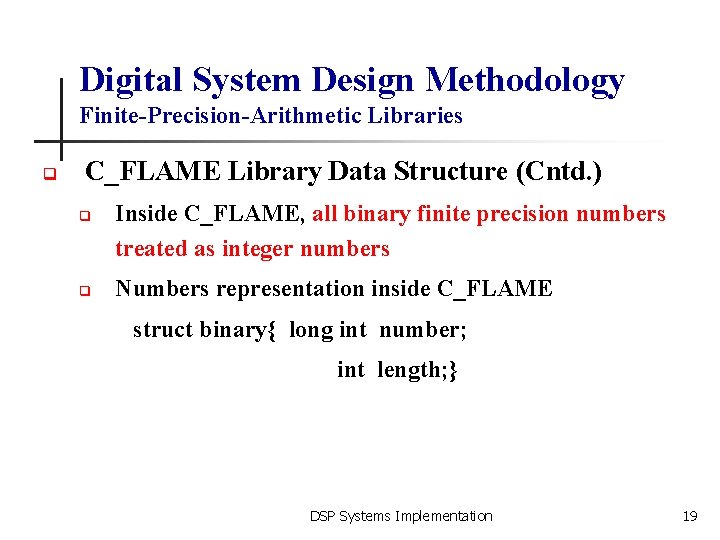

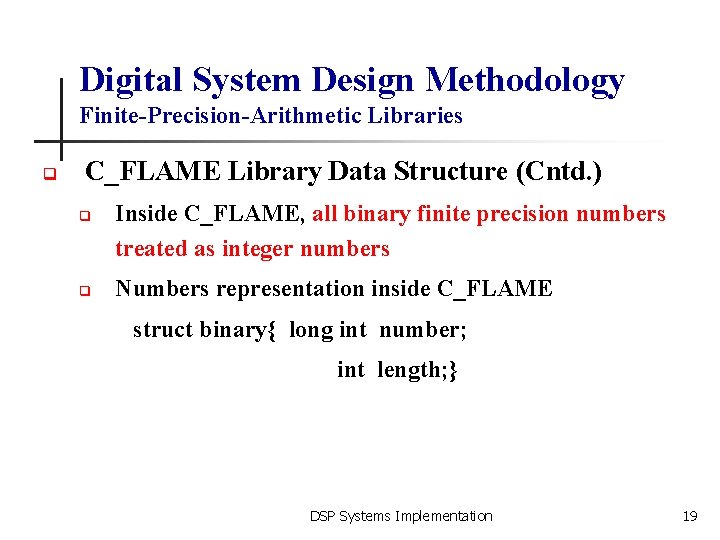

Digital System Design Methodology Finite-Precision-Arithmetic Libraries q C_FLAME Library Data Structure (Cntd. ) q q Inside C_FLAME, all binary finite precision numbers treated as integer numbers Numbers representation inside C_FLAME struct binary{ long int number; int length; } DSP Systems Implementation 19

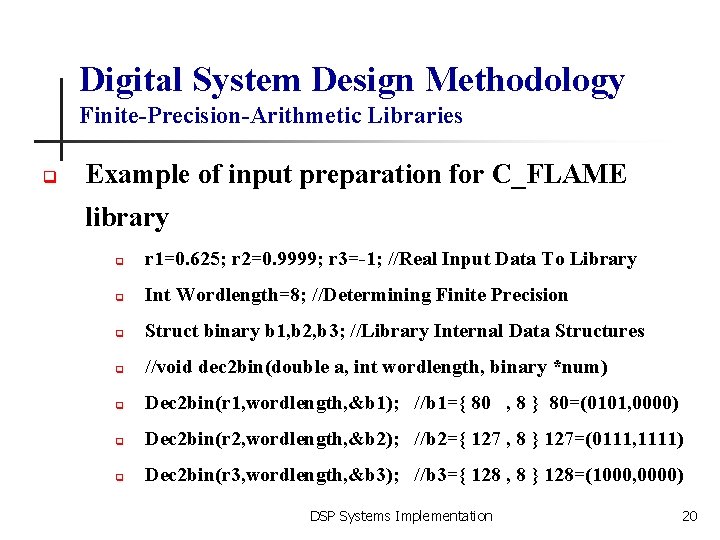

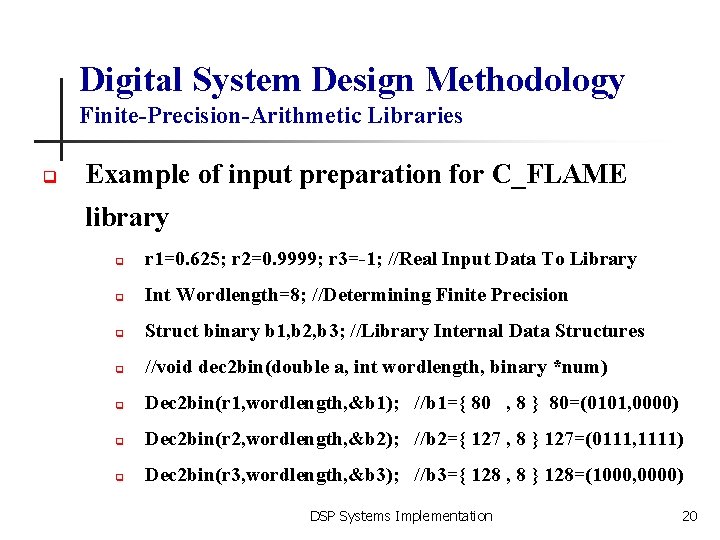

Digital System Design Methodology Finite-Precision-Arithmetic Libraries q Example of input preparation for C_FLAME library q r 1=0. 625; r 2=0. 9999; r 3=-1; //Real Input Data To Library q Int Wordlength=8; //Determining Finite Precision q Struct binary b 1, b 2, b 3; //Library Internal Data Structures q //void dec 2 bin(double a, int wordlength, binary *num) q Dec 2 bin(r 1, wordlength, &b 1); //b 1={ 80 , 8 } 80=(0101, 0000) q Dec 2 bin(r 2, wordlength, &b 2); //b 2={ 127 , 8 } 127=(0111, 1111) q Dec 2 bin(r 3, wordlength, &b 3); //b 3={ 128 , 8 } 128=(1000, 0000) DSP Systems Implementation 20

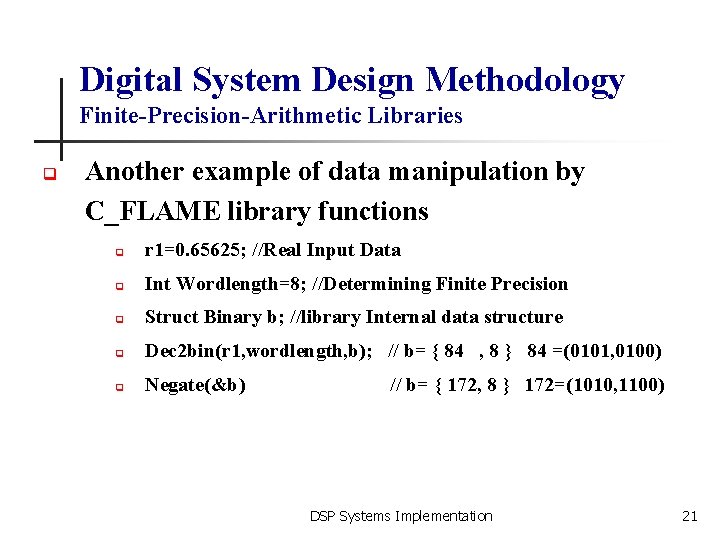

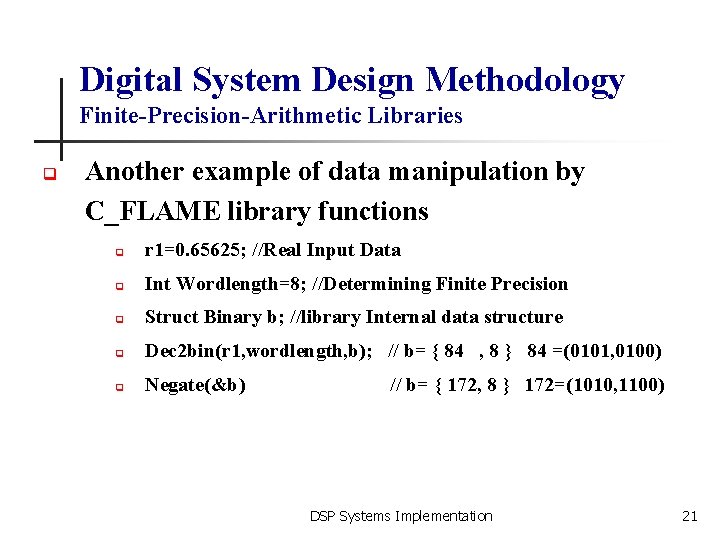

Digital System Design Methodology Finite-Precision-Arithmetic Libraries q Another example of data manipulation by C_FLAME library functions q r 1=0. 65625; //Real Input Data q Int Wordlength=8; //Determining Finite Precision q Struct Binary b; //library Internal data structure q Dec 2 bin(r 1, wordlength, b); // b= { 84 , 8 } 84 =(0101, 0100) q Negate(&b) // b= { 172, 8 } 172=(1010, 1100) DSP Systems Implementation 21

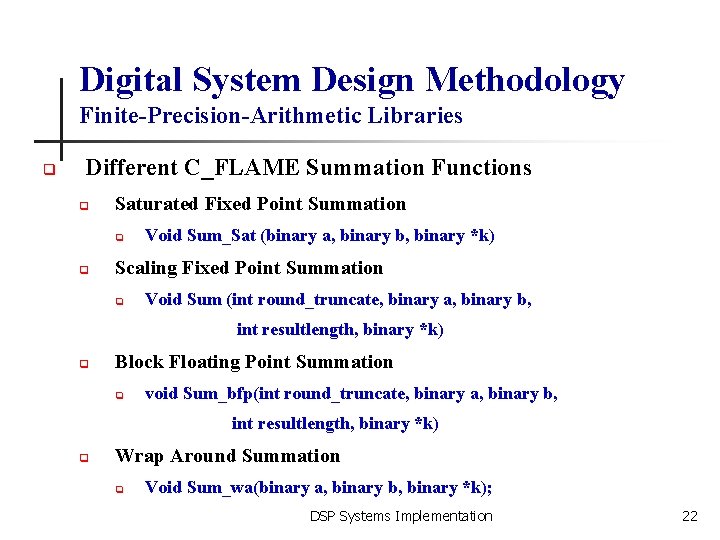

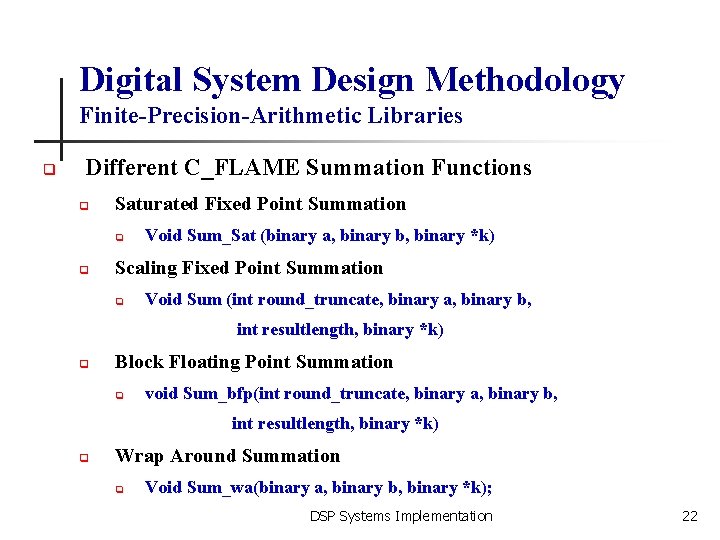

Digital System Design Methodology Finite-Precision-Arithmetic Libraries q Different C_FLAME Summation Functions q Saturated Fixed Point Summation q q Void Sum_Sat (binary a, binary b, binary *k) Scaling Fixed Point Summation q Void Sum (int round_truncate, binary a, binary b, int resultlength, binary *k) q Block Floating Point Summation q void Sum_bfp(int round_truncate, binary a, binary b, int resultlength, binary *k) q Wrap Around Summation q Void Sum_wa(binary a, binary b, binary *k); DSP Systems Implementation 22

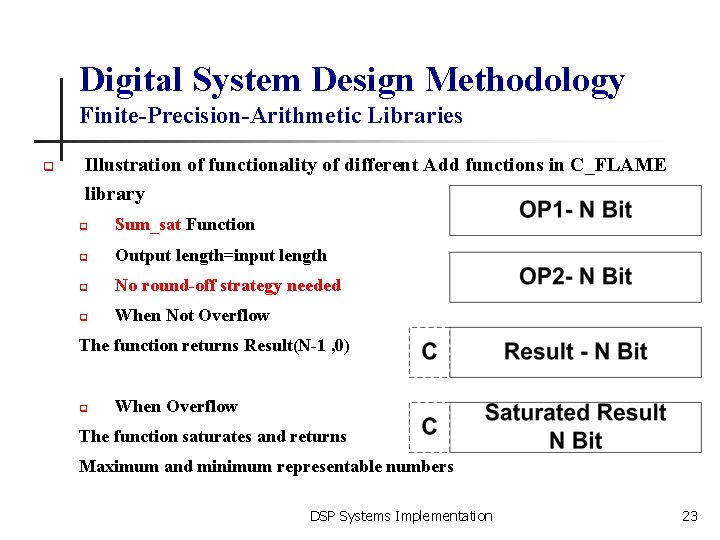

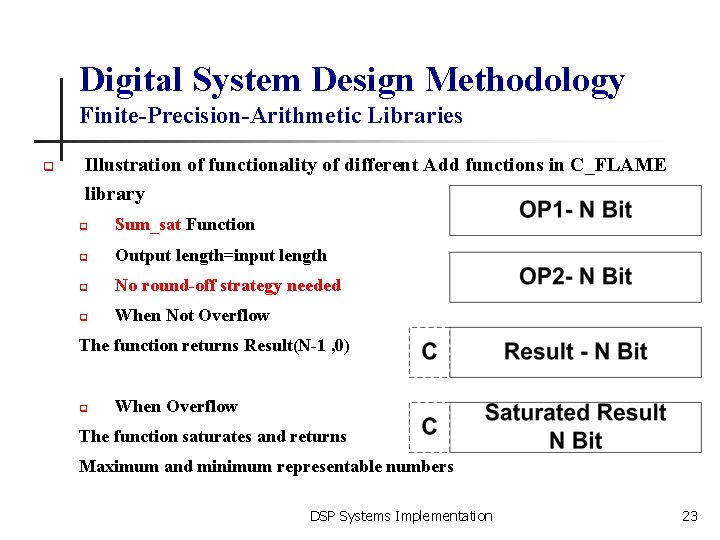

Digital System Design Methodology Finite-Precision-Arithmetic Libraries q Illustration of functionality of different Add functions in C_FLAME library q Sum_sat Function q Output length=input length q No round-off strategy needed q When Not Overflow The function returns Result(N-1 , 0) q When Overflow The function saturates and returns Maximum and minimum representable numbers DSP Systems Implementation 23

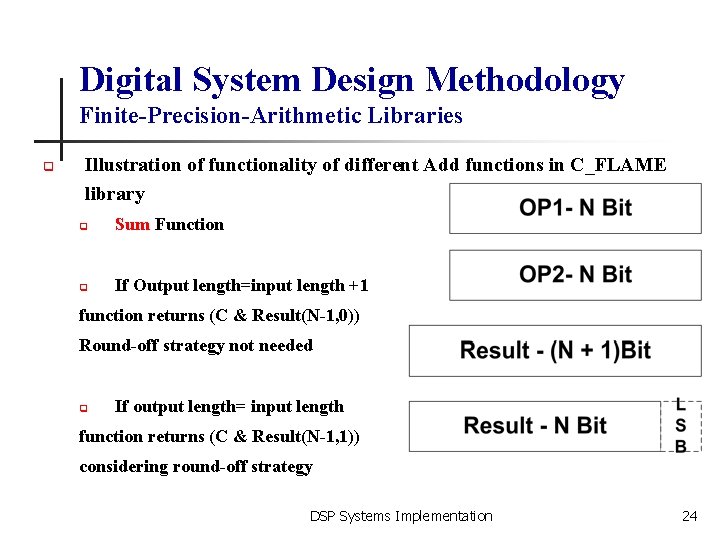

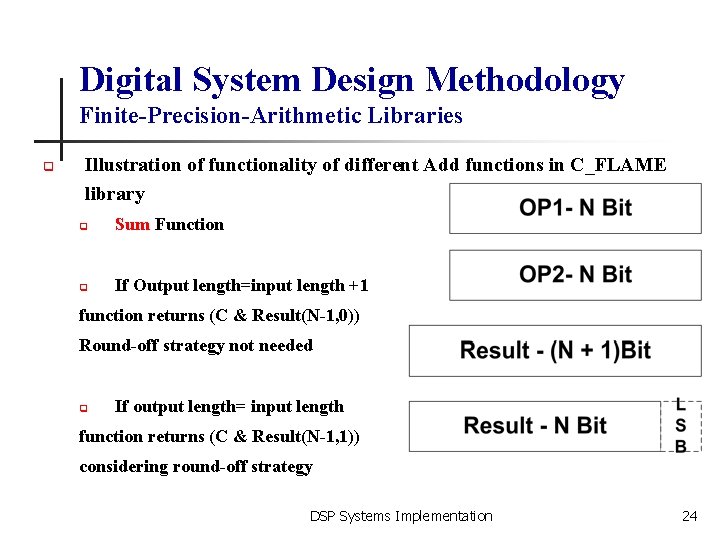

Digital System Design Methodology Finite-Precision-Arithmetic Libraries q Illustration of functionality of different Add functions in C_FLAME library q Sum Function q If Output length=input length +1 function returns (C & Result(N-1, 0)) Round-off strategy not needed q If output length= input length function returns (C & Result(N-1, 1)) considering round-off strategy DSP Systems Implementation 24

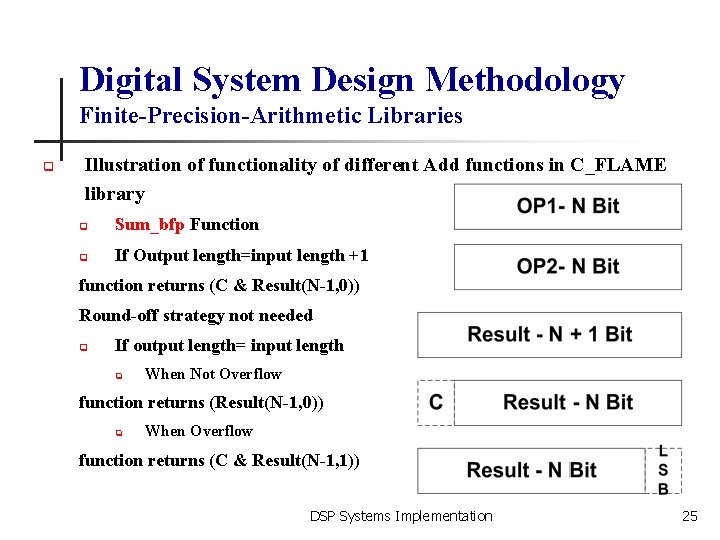

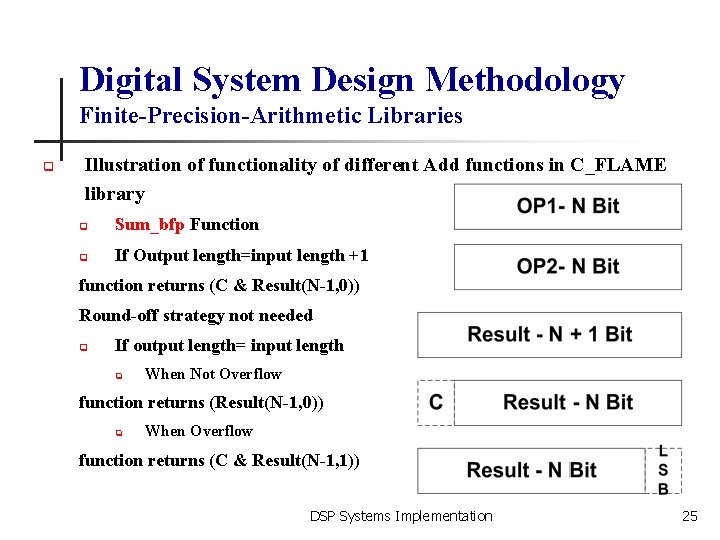

Digital System Design Methodology Finite-Precision-Arithmetic Libraries q Illustration of functionality of different Add functions in C_FLAME library q Sum_bfp Function q If Output length=input length +1 function returns (C & Result(N-1, 0)) Round-off strategy not needed q If output length= input length q When Not Overflow function returns (Result(N-1, 0)) q When Overflow function returns (C & Result(N-1, 1)) DSP Systems Implementation 25

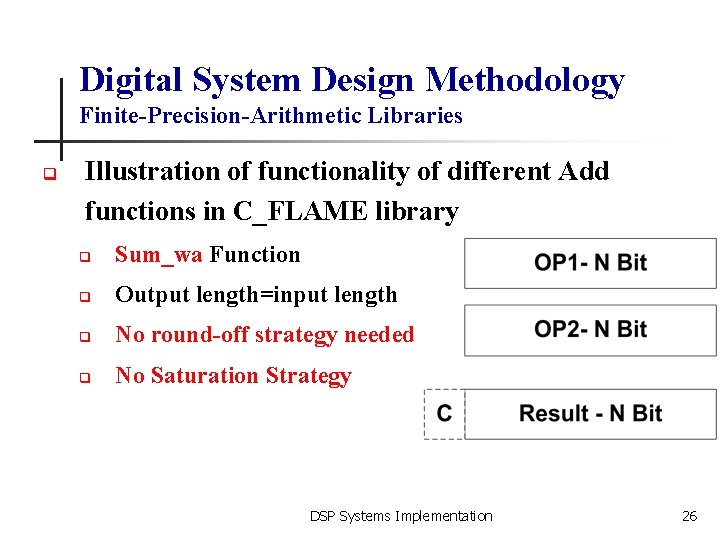

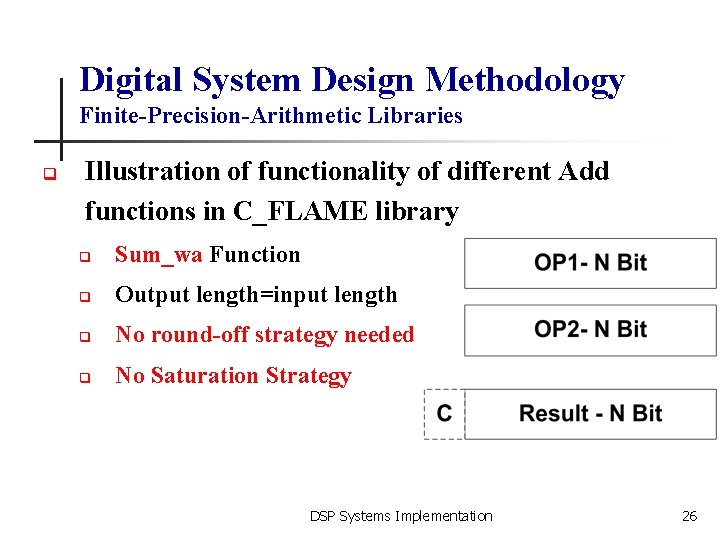

Digital System Design Methodology Finite-Precision-Arithmetic Libraries q Illustration of functionality of different Add functions in C_FLAME library q Sum_wa Function q Output length=input length q No round-off strategy needed q No Saturation Strategy DSP Systems Implementation 26

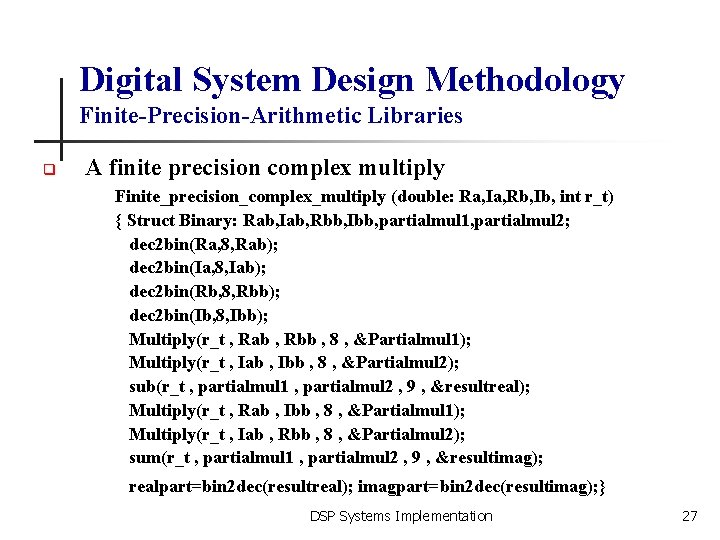

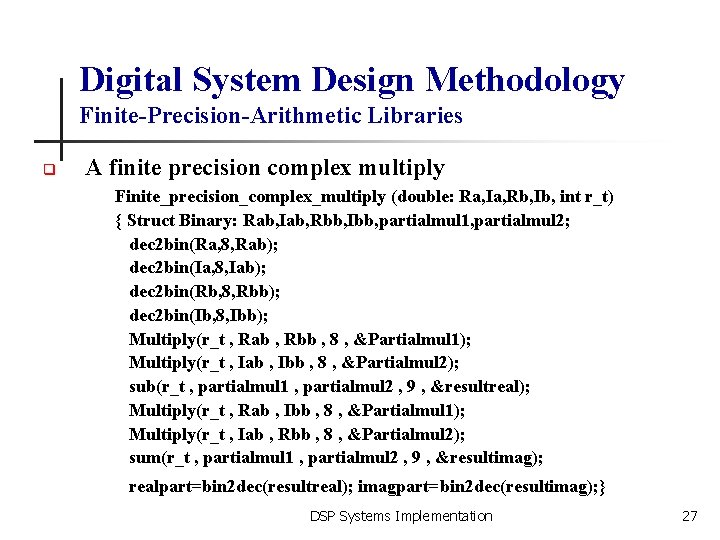

Digital System Design Methodology Finite-Precision-Arithmetic Libraries q A finite precision complex multiply Finite_precision_complex_multiply (double: Ra, Ia, Rb, Ib, int r_t) { Struct Binary: Rab, Iab, Rbb, Ibb, partialmul 1, partialmul 2; dec 2 bin(Ra, 8, Rab); dec 2 bin(Ia, 8, Iab); dec 2 bin(Rb, 8, Rbb); dec 2 bin(Ib, 8, Ibb); Multiply(r_t , Rab , Rbb , 8 , &Partialmul 1); Multiply(r_t , Iab , Ibb , 8 , &Partialmul 2); sub(r_t , partialmul 1 , partialmul 2 , 9 , &resultreal); Multiply(r_t , Rab , Ibb , 8 , &Partialmul 1); Multiply(r_t , Iab , Rbb , 8 , &Partialmul 2); sum(r_t , partialmul 1 , partialmul 2 , 9 , &resultimag); realpart=bin 2 dec(resultreal); imagpart=bin 2 dec(resultimag); } DSP Systems Implementation 27

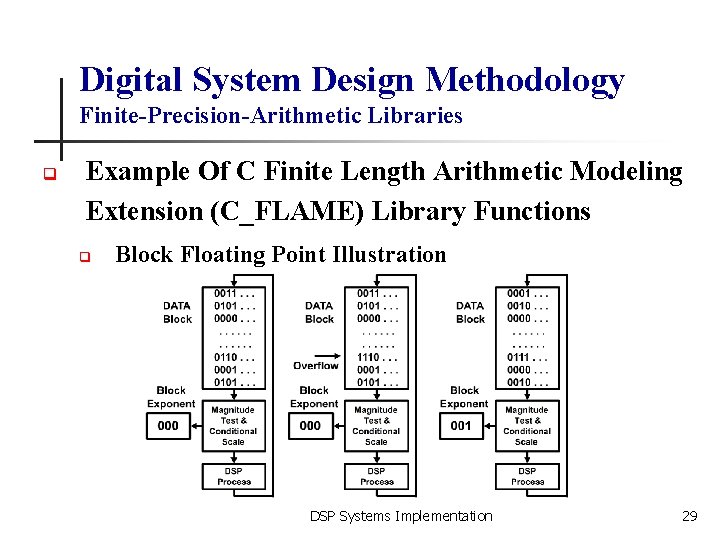

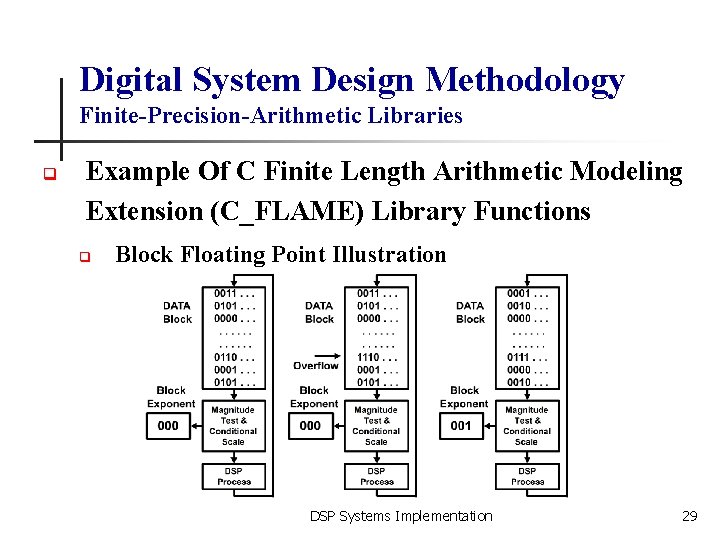

Digital System Design Methodology Finite-Precision-Arithmetic Libraries q Block Floating Point q Extra Hardware q A Solution Between Fixed And Floating Point q Wide range Representation Capability q Simple Hardware Implementation q Low Quantization Noise Sensitivity q Low Delay DSP Systems Implementation 28

Digital System Design Methodology Finite-Precision-Arithmetic Libraries q Example Of C Finite Length Arithmetic Modeling Extension (C_FLAME) Library Functions q Block Floating Point Illustration DSP Systems Implementation 29

Digital System Design Methodology ADSL Modulator/Demodulator Design q q IFFT/FFT Used For Modulation/Demodulation The Most Complicated And Most Important Block Of An ADSL Modem q Hardware Structure q Operation Count q Quantization Noise q Design Constraints (Speed, Area, Power) DSP Systems Implementation 30

Digital System Design Methodology ADSL Mo/Dem- Implementation Method Selection Space q A Multi-Dimensional Space q Different Algorithms q q Different Algorithm Versions q q Decimation In Time (DIT), Decimation In Frequency (DIF) Different Butterfly Structures q q Radix 2, Radix 4, Radix 8, Split Radix, Mixed Radix Symmetric Structures, Asymmetric Structures Different Implementations q Full Parallel Structure, Column Structure, FFT Processor Structure, Pipeline Structure DSP Systems Implementation 31

Digital System Design Methodology ADSL Mo/Dem- Choosing Suitable Structure q Selection Criteria q q Maximum Delay Constraint (250 µs) Hardware Cost (# of Adders, Multipliers, …) Maximum Quantization Noise Acceptable Implementation Complexity (VLSI Layout, …) DSP Systems Implementation 32

Digital System Design Methodology ADSL Mo/Dem- Choosing Suitable Structure q So Many Trade-Offs Must Be Considered And Resolved q q q q q # Of Operations (~Quantization Noise Error) Register Word Lengths Butterfly Hardware Complexity Symmetric Or Asymmetric Butterfly Hardware Delay Hardware Component Count Hardware Utilization Input Output Sequence Final Chip Size DSP Systems Implementation 33

Digital System Design Methodology ADSL Mo/Dem- Choosing Suitable Structure q Important Results Of Browsing Selection Space q q q Result#1: Hardware Complexity Decreases as the Radix Increases ! Result#2: Operations Count Decreases as the Radix Increases! Result#3: Mixed-Radix Algorithms are Hardware Optimized Solutions! Result#4: Implementation Complexity Increases as the Radix Increases (More Than 4 or 8)! Result#5: Hardware Utilization Decreases as the Radix Increases (Generally)! DSP Systems Implementation 34

Digital System Design Methodology ADSL Mo/Dem- The Chosen Algorithm q Mixed-Radix 2^2 +2 Algorithm q Hardware Complexity of Radix-4 Algorithms! q Operation Count of Radix-4 Algorithms! q Mixed-Radix Hardware Optimized With a Very Simple Controller! q Implementation Complexity of Radix-2 Algorithms! q Hardware Utilization of Radix-2 Algorithms! DSP Systems Implementation 35

Digital System Design Methodology ADSL Mo/Dem- The Chosen Algorithm q Mixed-Radix 2^2 +2 Algorithm DFG DSP Systems Implementation 36

Digital System Design Methodology ADSL Mo/Dem- The Selected Implementation Method q q Different Implementations q Fully Parallel FFTs q Column FFTs q Pipeline FFTs q FFT Processors The Selected Implementation Method q Pipeline FFT Implementation DSP Systems Implementation 37

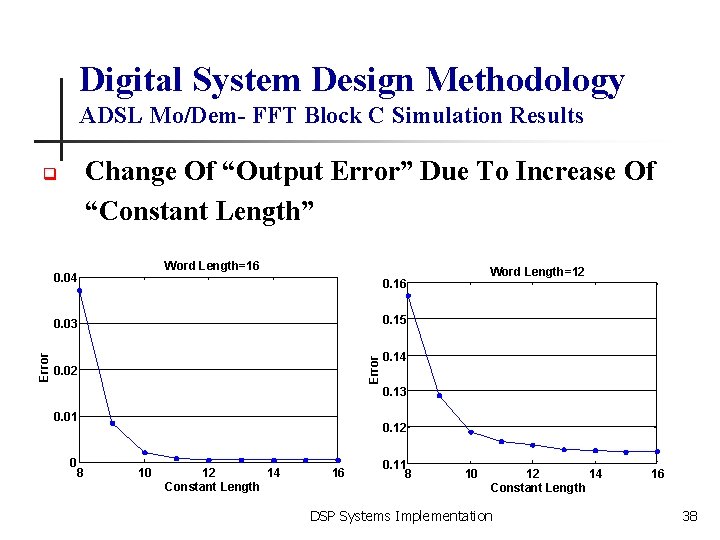

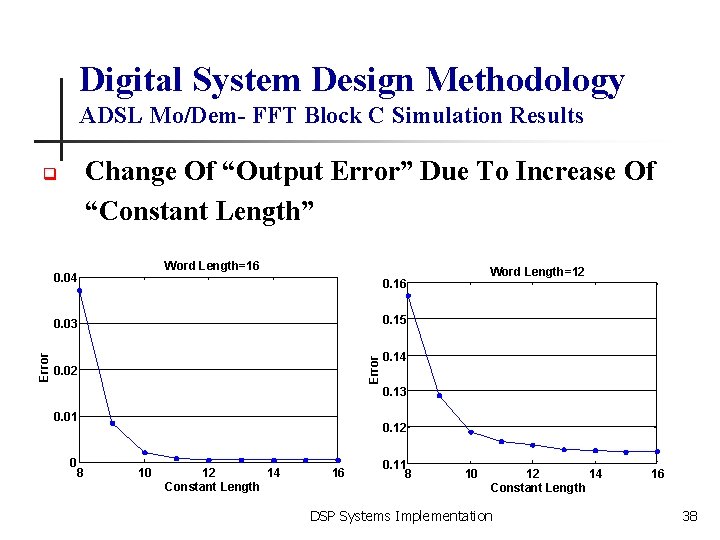

Digital System Design Methodology ADSL Mo/Dem- FFT Block C Simulation Results Change Of “Output Error” Due To Increase Of “Constant Length” q Word Length=16 0. 04 0. 15 Error 0. 03 Error Word Length=12 0. 16 0. 02 0. 14 0. 13 0. 01 0 8 0. 12 10 12 14 Constant Length 16 0. 11 8 10 12 14 Constant Length DSP Systems Implementation 16 38

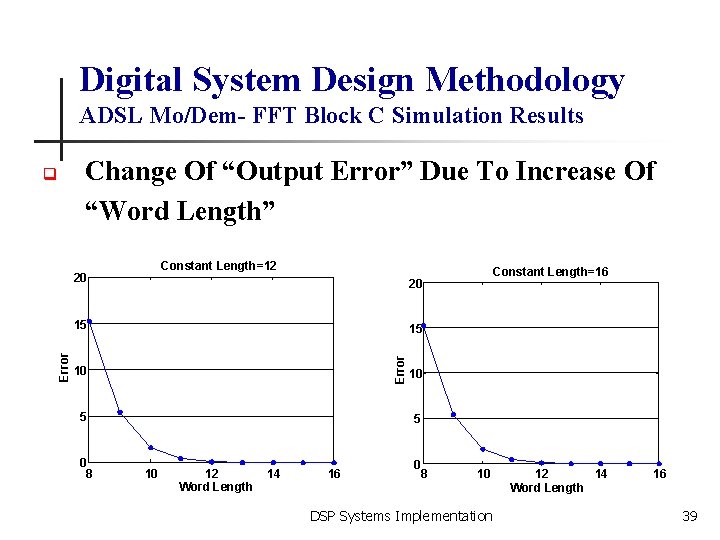

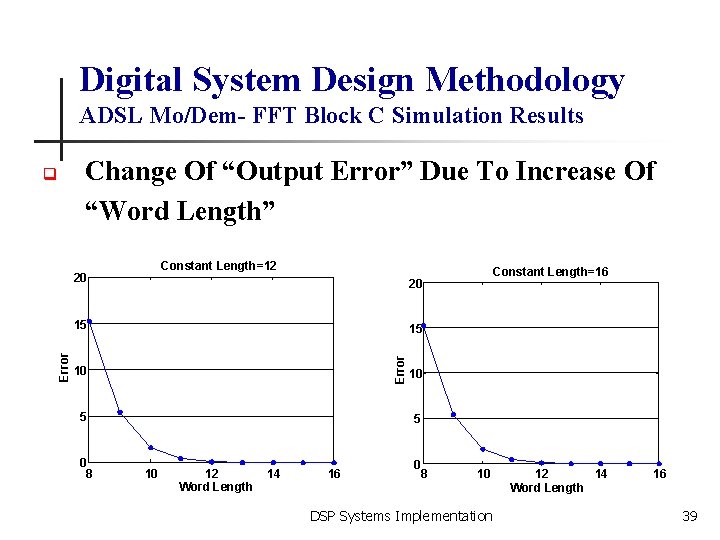

Digital System Design Methodology ADSL Mo/Dem- FFT Block C Simulation Results q Change Of “Output Error” Due To Increase Of “Word Length” Constant Length=12 20 15 Error 15 10 5 0 8 Constant Length=16 20 10 5 10 12 Word Length 14 16 0 8 10 DSP Systems Implementation 12 14 Word Length 16 39

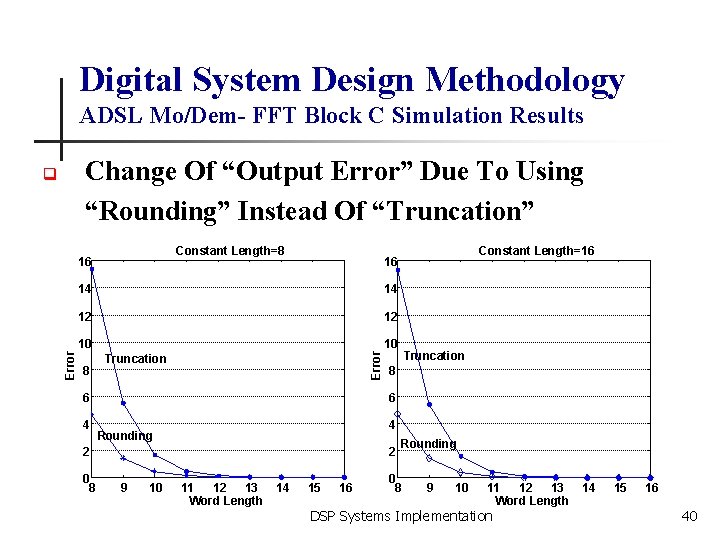

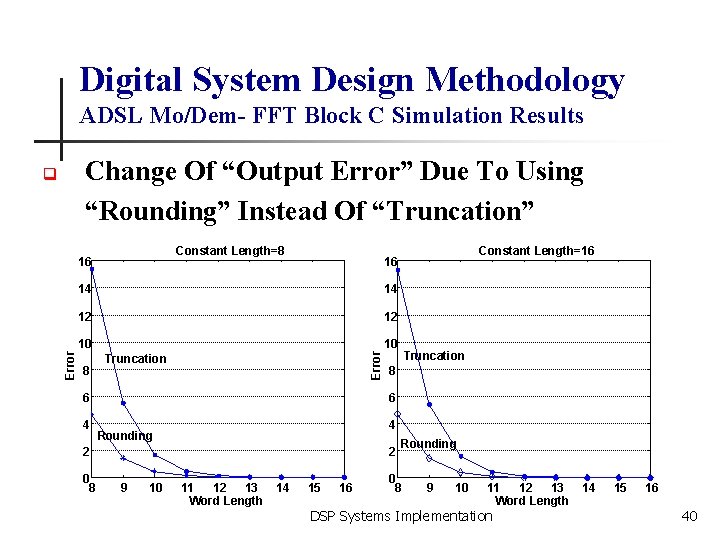

Digital System Design Methodology ADSL Mo/Dem- FFT Block C Simulation Results Change Of “Output Error” Due To Using “Rounding” Instead Of “Truncation” Constant Length=8 Error 16 14 14 12 12 10 10 8 Truncation 4 Rounding 2 0 8 Truncation 8 6 6 4 Constant Length=16 16 Error q 2 9 10 11 12 13 Word Length 14 15 16 Rounding 0 8 9 10 11 12 13 Word Length DSP Systems Implementation 14 15 16 40

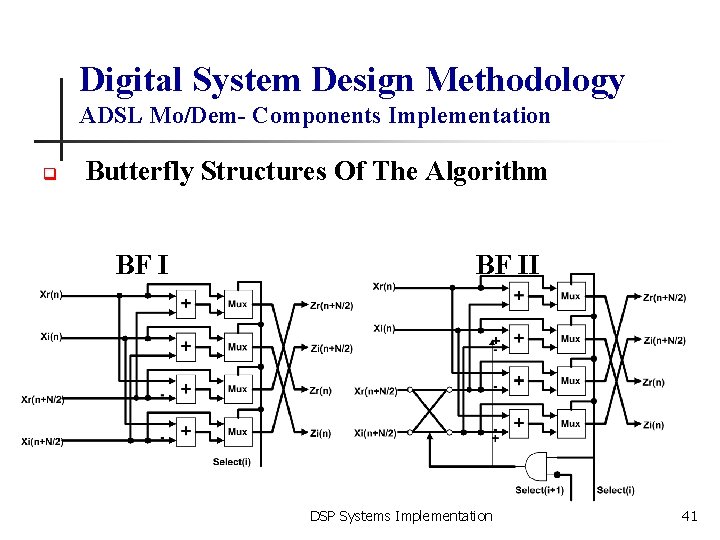

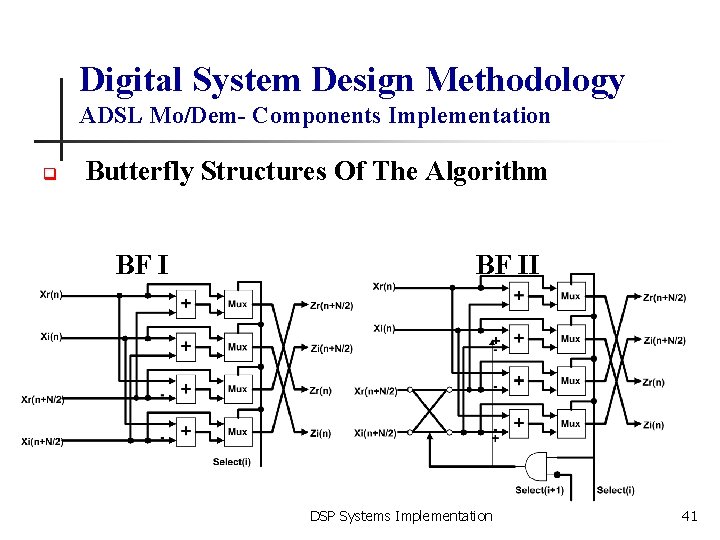

Digital System Design Methodology ADSL Mo/Dem- Components Implementation q Butterfly Structures Of The Algorithm BF II DSP Systems Implementation 41

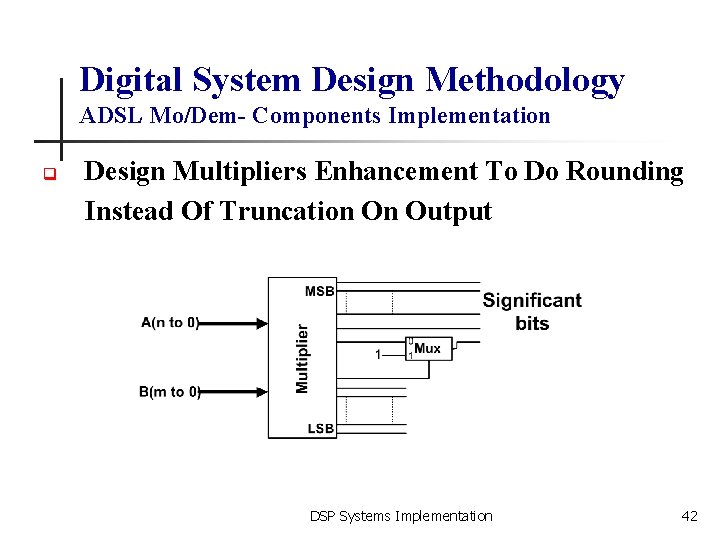

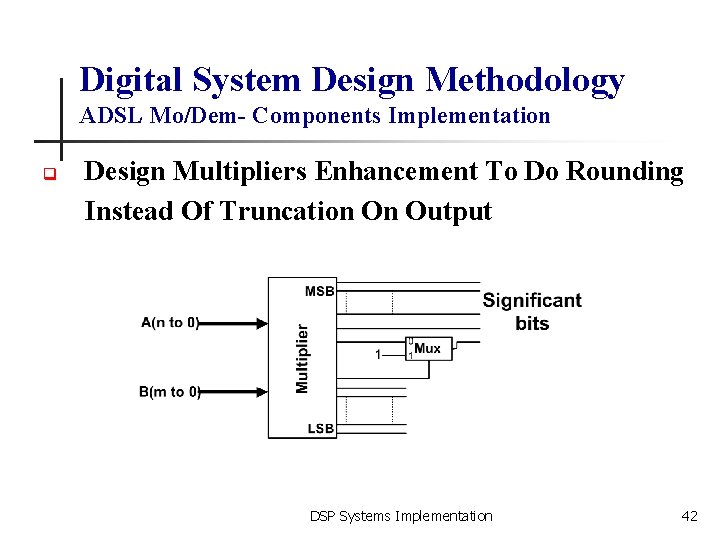

Digital System Design Methodology ADSL Mo/Dem- Components Implementation q Design Multipliers Enhancement To Do Rounding Instead Of Truncation On Output DSP Systems Implementation 42

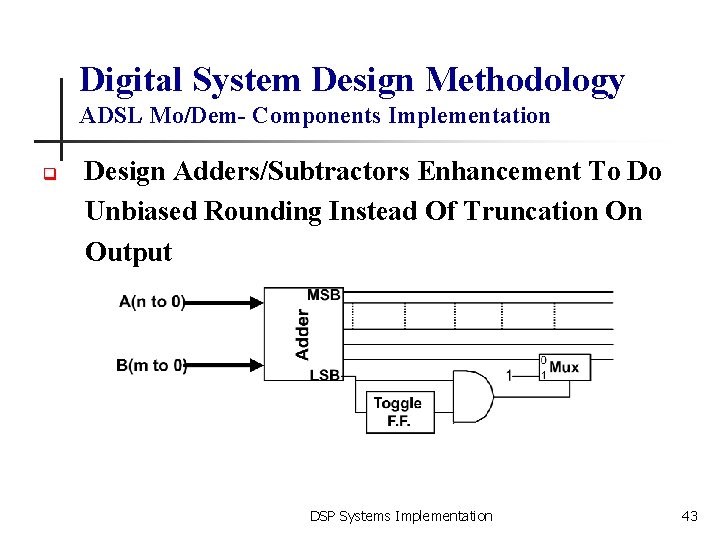

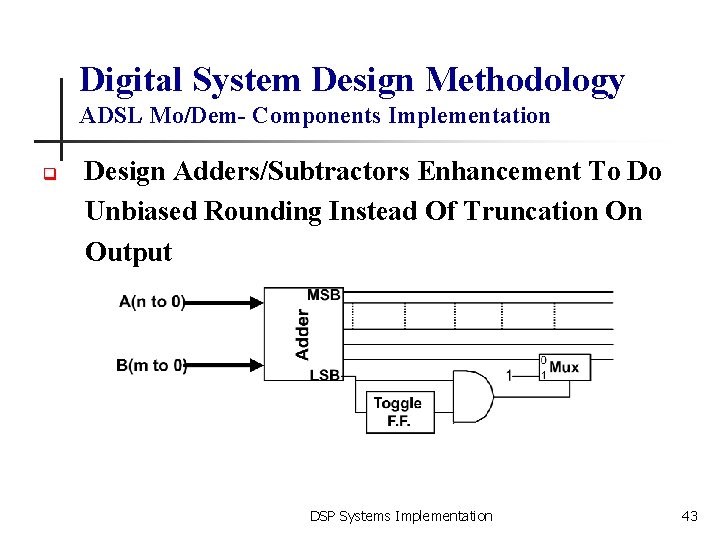

Digital System Design Methodology ADSL Mo/Dem- Components Implementation q Design Adders/Subtractors Enhancement To Do Unbiased Rounding Instead Of Truncation On Output DSP Systems Implementation 43

Digital System Design Methodology ADSL Time Equalizer Design q q A Digital Filter To Cancel Line Distortion Implemented As A 16 Tap Adaptive FIR Filter (Changeable Coefficients) DSP Systems Implementation 44

Digital System Design Methodology ADSL Time Equalizer - Choosing A Suitable Structure q Constant Length = Filter Word Length q Selection Criteria q Maximum Delay Constraint q Hardware Cost (# Of Adders, Multipliers, …) DSP Systems Implementation 45

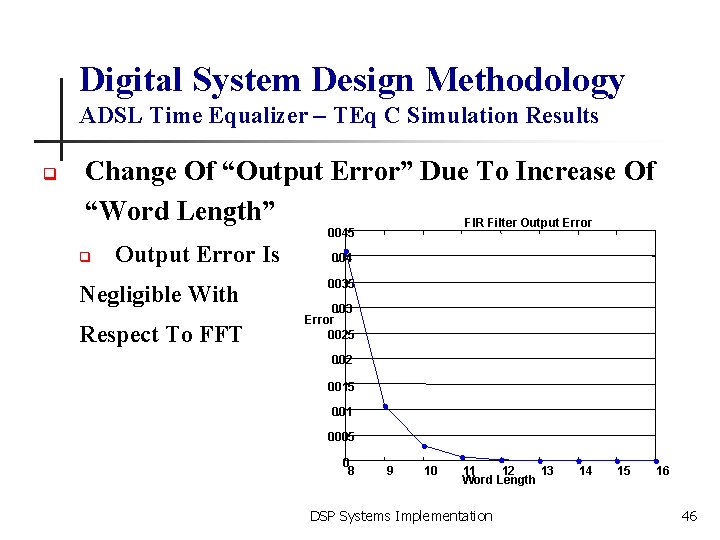

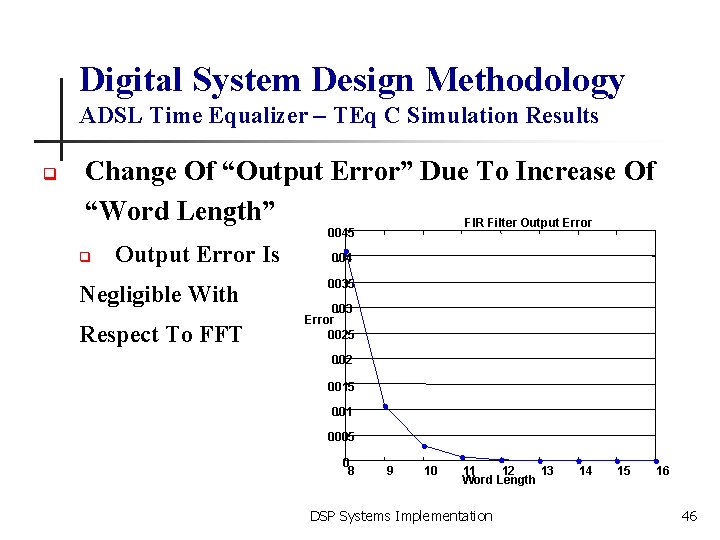

Digital System Design Methodology ADSL Time Equalizer – TEq C Simulation Results q Change Of “Output Error” Due To Increase Of “Word Length” FIR Filter Output Error 0. 045 q Output Error Is Negligible With Respect To FFT 0. 04 0. 035 0. 03 Error 0. 025 0. 02 0. 015 0. 01 0. 005 0 8 9 10 11 12 13 Word Length DSP Systems Implementation 14 15 16 46

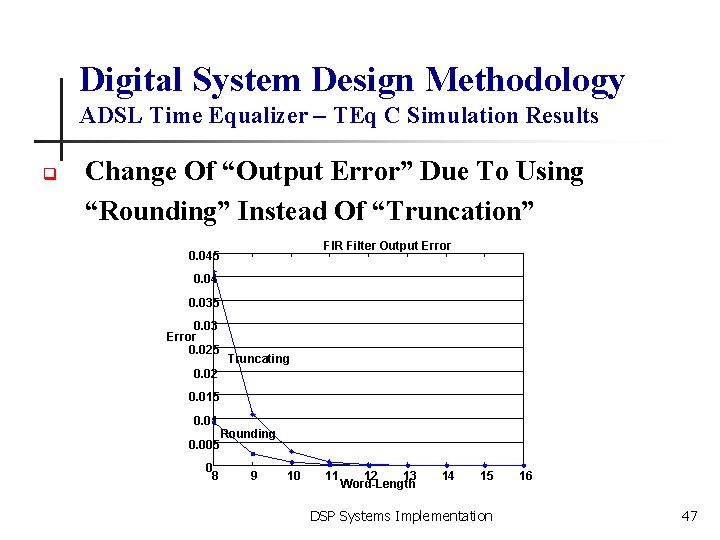

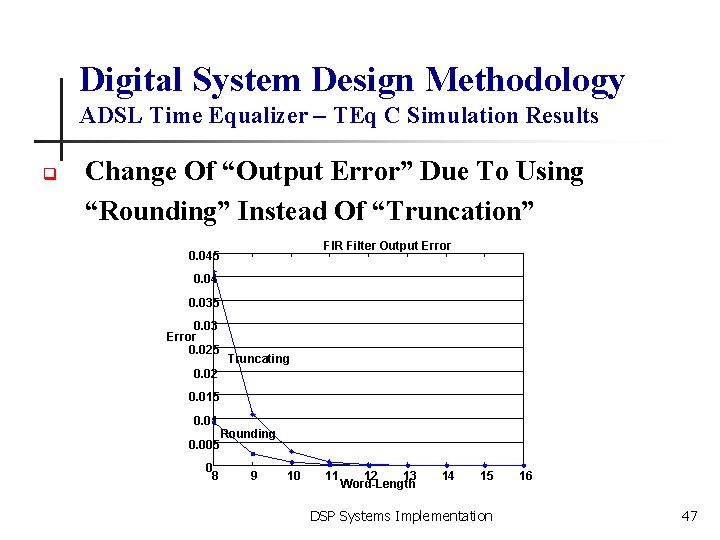

Digital System Design Methodology ADSL Time Equalizer – TEq C Simulation Results q Change Of “Output Error” Due To Using “Rounding” Instead Of “Truncation” FIR Filter Output Error 0. 045 0. 04 0. 035 0. 03 Error 0. 025 Truncating 0. 02 0. 015 0. 01 0. 005 0 8 Rounding 9 10 11 12 13 Word-Length 14 15 DSP Systems Implementation 16 47

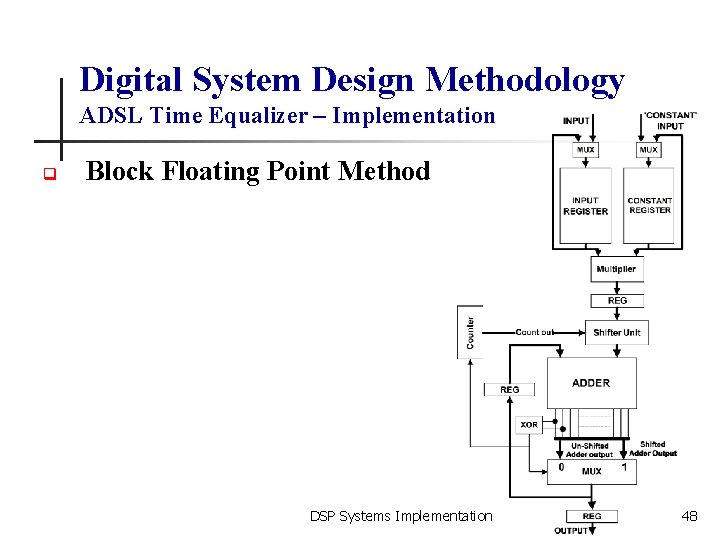

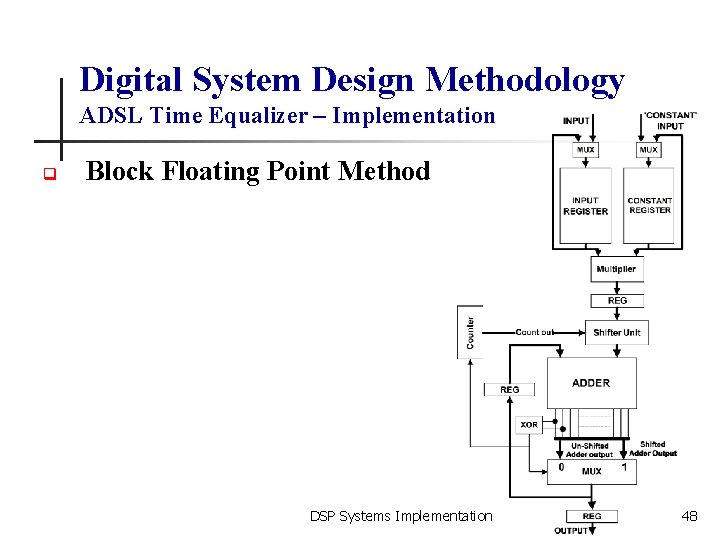

Digital System Design Methodology ADSL Time Equalizer – Implementation q Block Floating Point Method DSP Systems Implementation 48