Introduction to Digital Signal Processors DSPs Dr Konstantinos

- Slides: 24

Introduction to Digital Signal Processors (DSPs) Dr. Konstantinos Tatas

Outline/objectives • Identify the most important DSP processor architecture features and how they relate to DSP applications. ACOE 343 - Embedded Real-Time Processor Systems - Frederick University 2

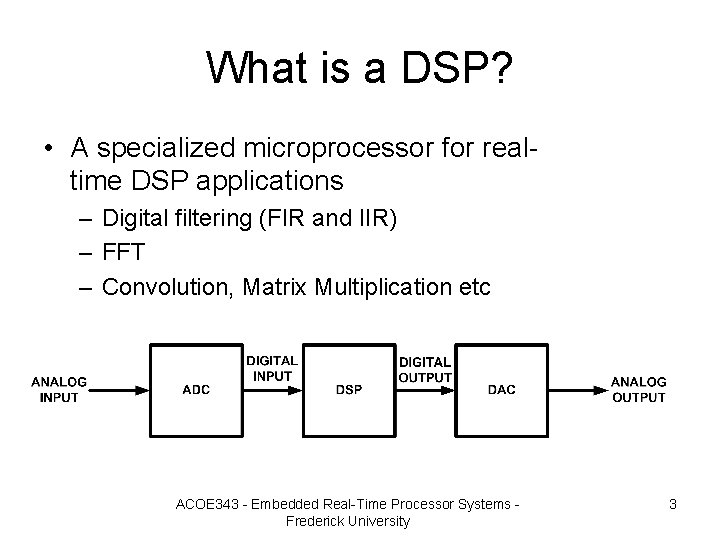

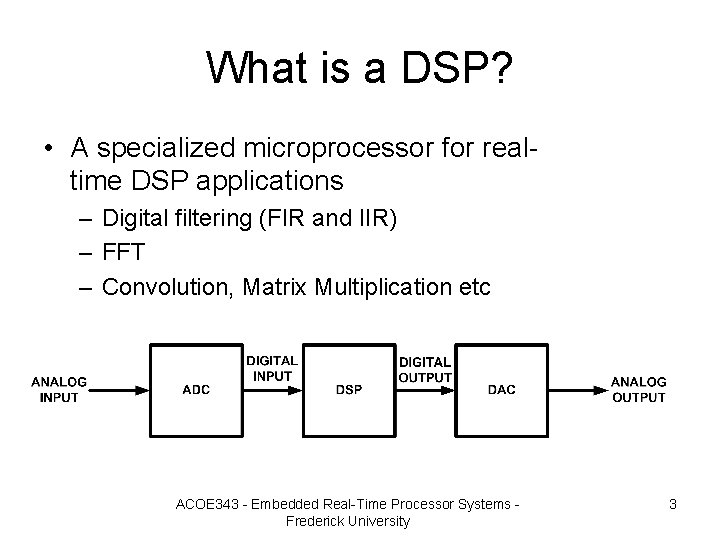

What is a DSP? • A specialized microprocessor for realtime DSP applications – Digital filtering (FIR and IIR) – FFT – Convolution, Matrix Multiplication etc ACOE 343 - Embedded Real-Time Processor Systems - Frederick University 3

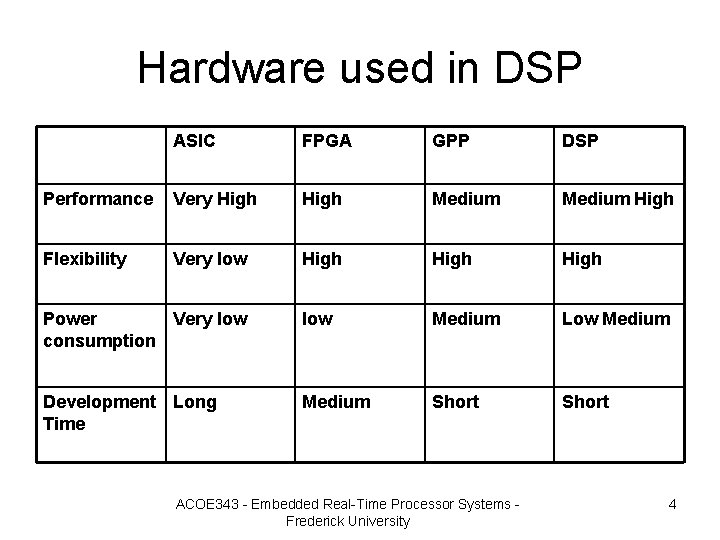

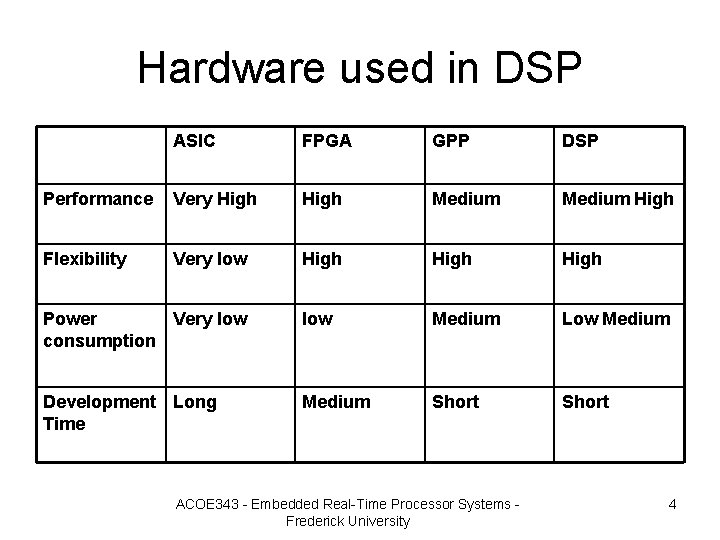

Hardware used in DSP ASIC FPGA GPP DSP Performance Very High Medium High Flexibility Very low High Power Very low consumption low Medium Low Medium Development Long Time Medium Short ACOE 343 - Embedded Real-Time Processor Systems - Frederick University 4

Common DSP features • Harvard architecture • Dedicated single-cycle Multiply-Accumulate (MAC) instruction (hardware MAC units) • Single-Instruction Multiple Data (SIMD) Very Large Instruction Word (VLIW) architecture • Pipelining • Cache • DMA ACOE 343 - Embedded Real-Time Processor Systems - Frederick University 5

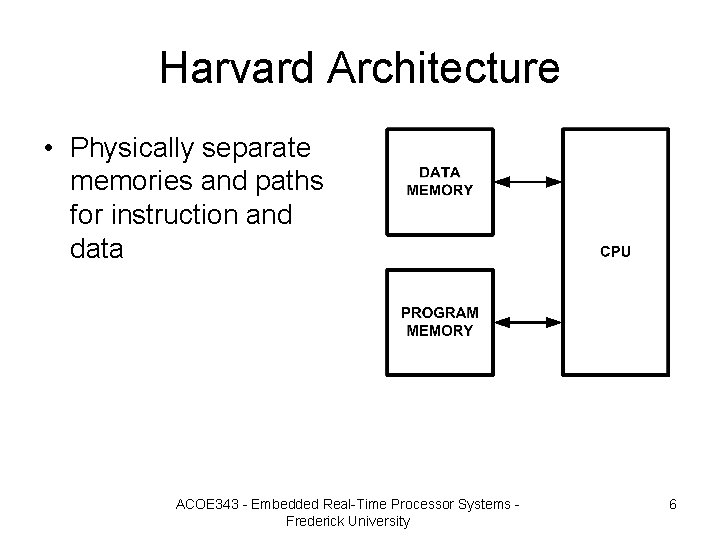

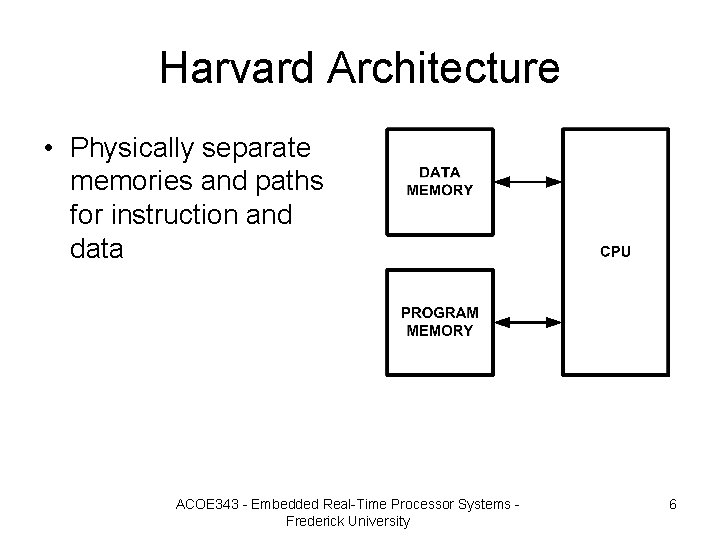

Harvard Architecture • Physically separate memories and paths for instruction and data ACOE 343 - Embedded Real-Time Processor Systems - Frederick University 6

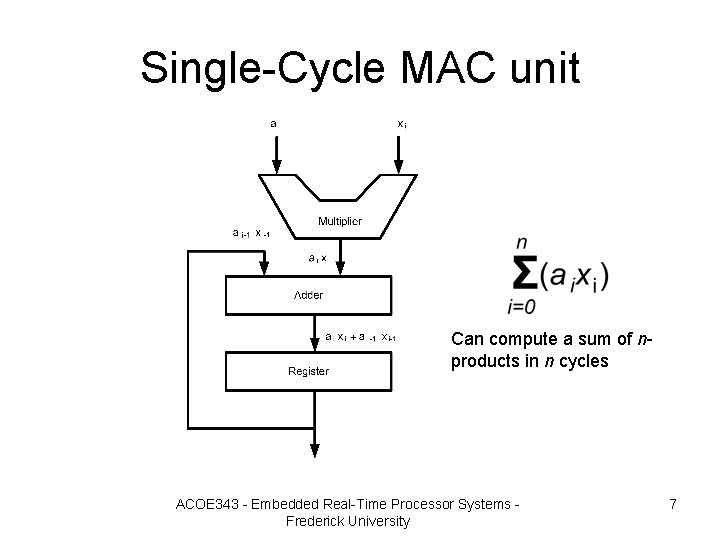

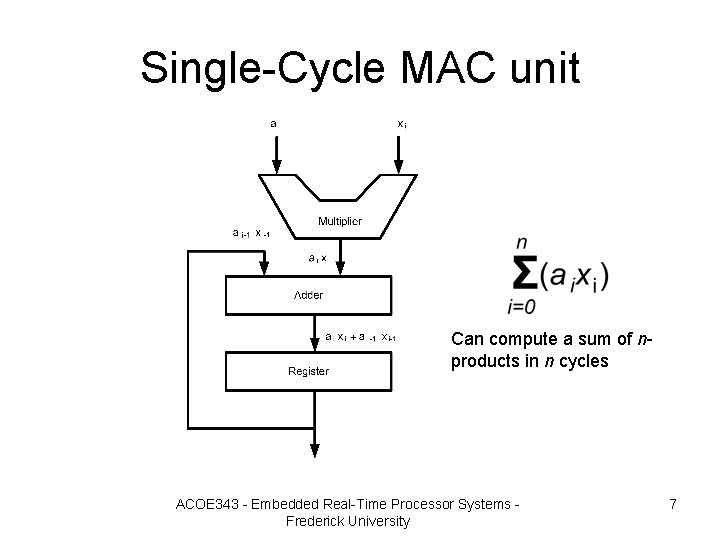

Single-Cycle MAC unit Can compute a sum of nproducts in n cycles ACOE 343 - Embedded Real-Time Processor Systems - Frederick University 7

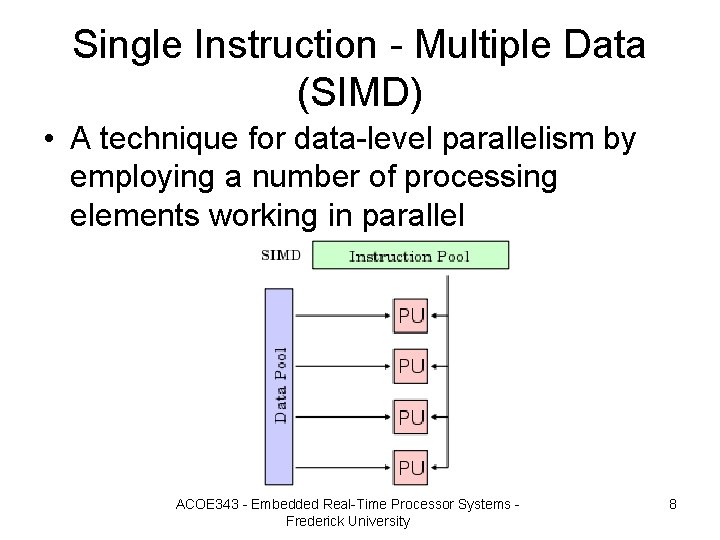

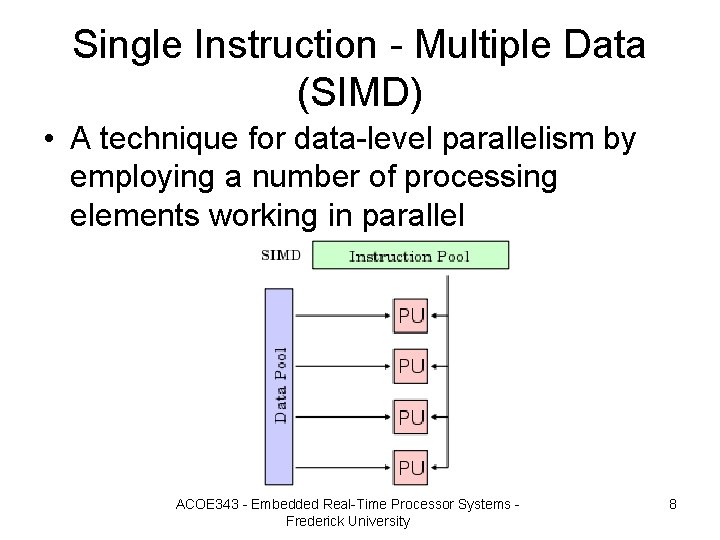

Single Instruction - Multiple Data (SIMD) • A technique for data-level parallelism by employing a number of processing elements working in parallel ACOE 343 - Embedded Real-Time Processor Systems - Frederick University 8

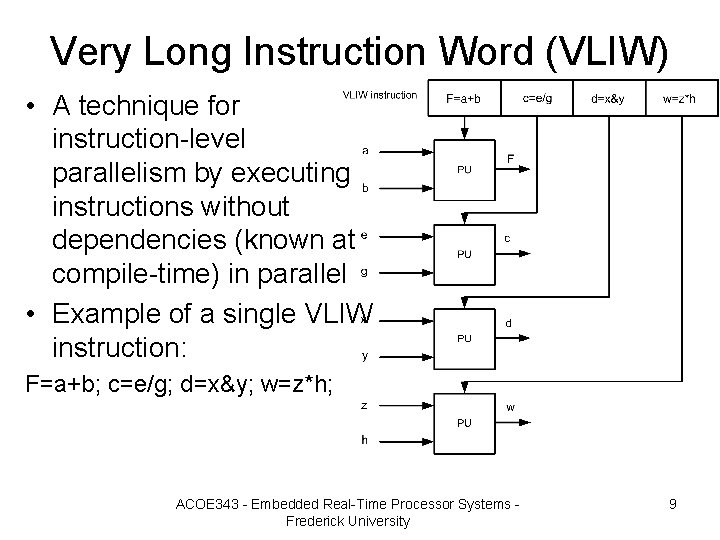

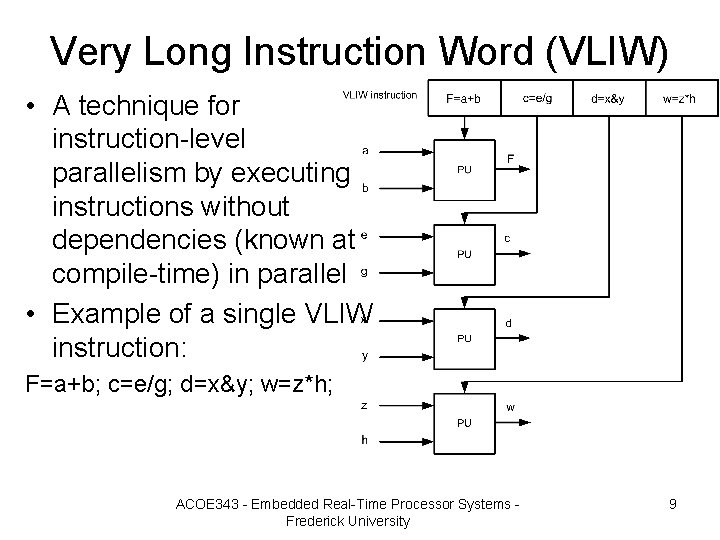

Very Long Instruction Word (VLIW) • A technique for instruction-level parallelism by executing instructions without dependencies (known at compile-time) in parallel • Example of a single VLIW instruction: F=a+b; c=e/g; d=x&y; w=z*h; ACOE 343 - Embedded Real-Time Processor Systems - Frederick University 9

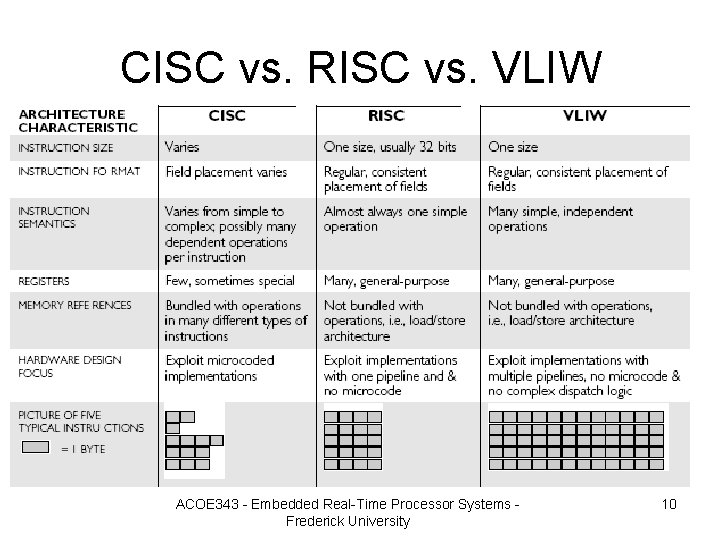

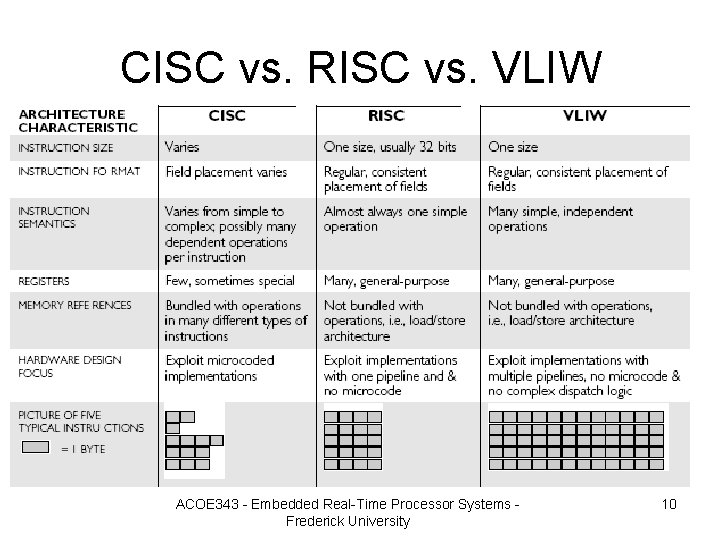

CISC vs. RISC vs. VLIW ACOE 343 - Embedded Real-Time Processor Systems - Frederick University 10

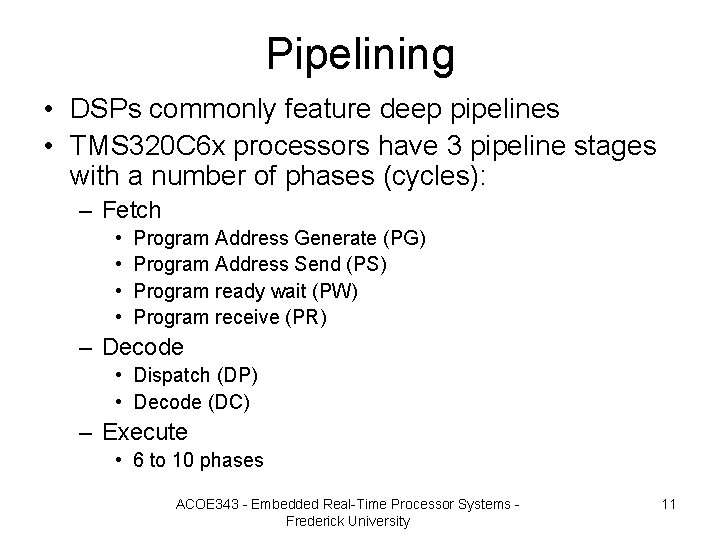

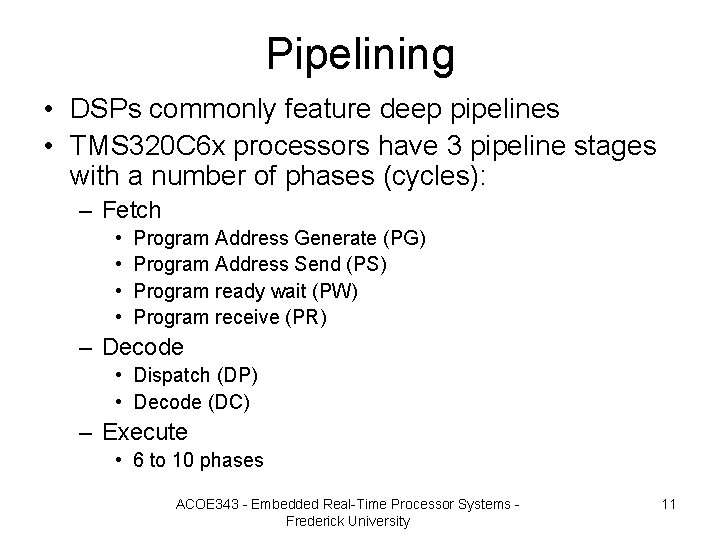

Pipelining • DSPs commonly feature deep pipelines • TMS 320 C 6 x processors have 3 pipeline stages with a number of phases (cycles): – Fetch • • Program Address Generate (PG) Program Address Send (PS) Program ready wait (PW) Program receive (PR) – Decode • Dispatch (DP) • Decode (DC) – Execute • 6 to 10 phases ACOE 343 - Embedded Real-Time Processor Systems - Frederick University 11

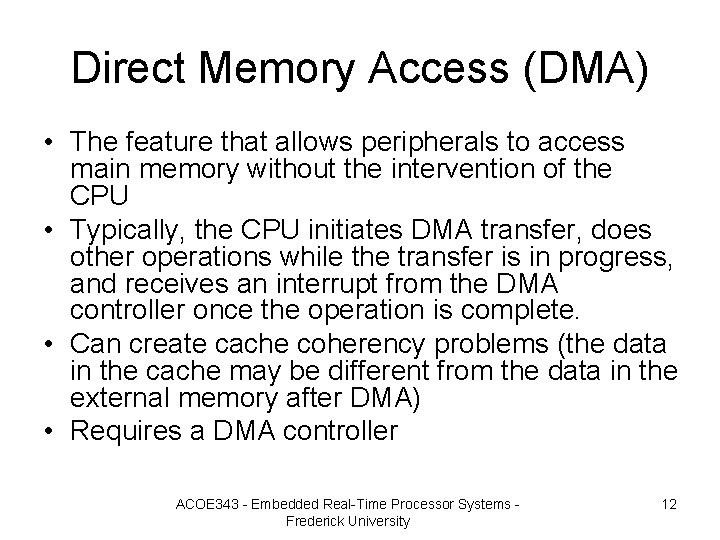

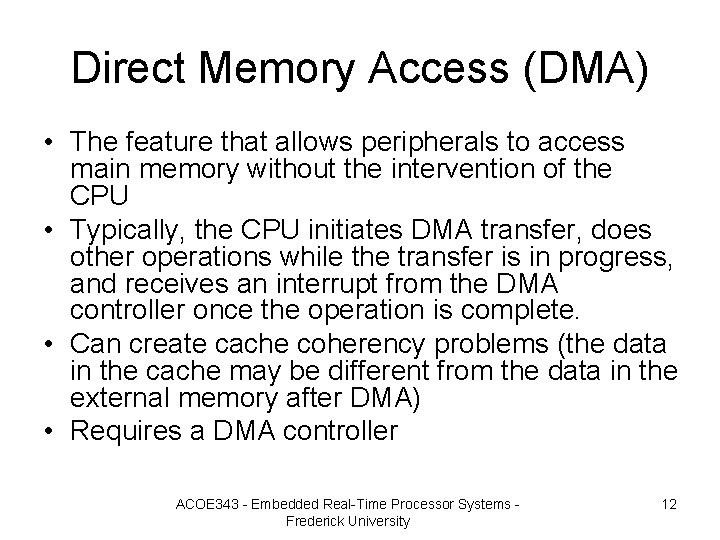

Direct Memory Access (DMA) • The feature that allows peripherals to access main memory without the intervention of the CPU • Typically, the CPU initiates DMA transfer, does other operations while the transfer is in progress, and receives an interrupt from the DMA controller once the operation is complete. • Can create cache coherency problems (the data in the cache may be different from the data in the external memory after DMA) • Requires a DMA controller ACOE 343 - Embedded Real-Time Processor Systems - Frederick University 12

Cache memory • Separate instruction and data L 1 caches (Harvard architecture) • most systems uses DMA ACOE 343 - Embedded Real-Time Processor Systems - Frederick University 13

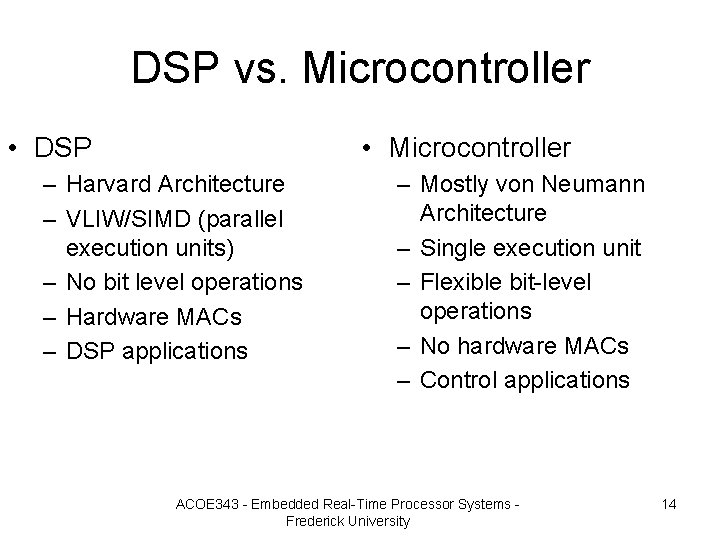

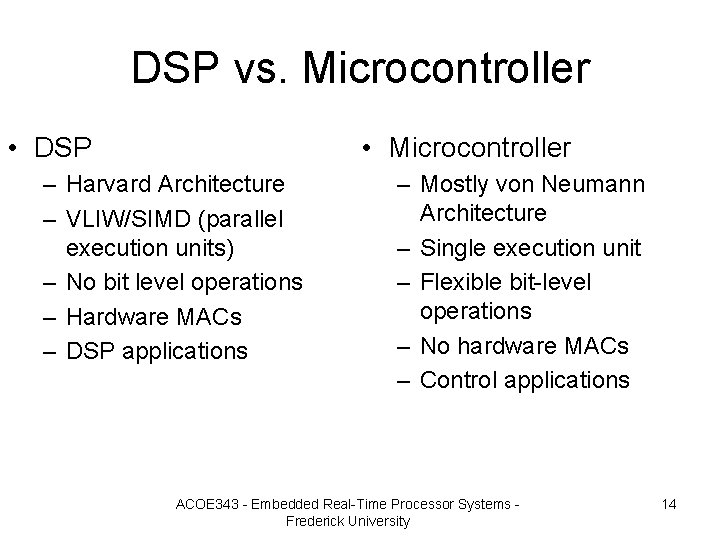

DSP vs. Microcontroller • DSP • Microcontroller – Harvard Architecture – VLIW/SIMD (parallel execution units) – No bit level operations – Hardware MACs – DSP applications – Mostly von Neumann Architecture – Single execution unit – Flexible bit-level operations – No hardware MACs – Control applications ACOE 343 - Embedded Real-Time Processor Systems - Frederick University 14

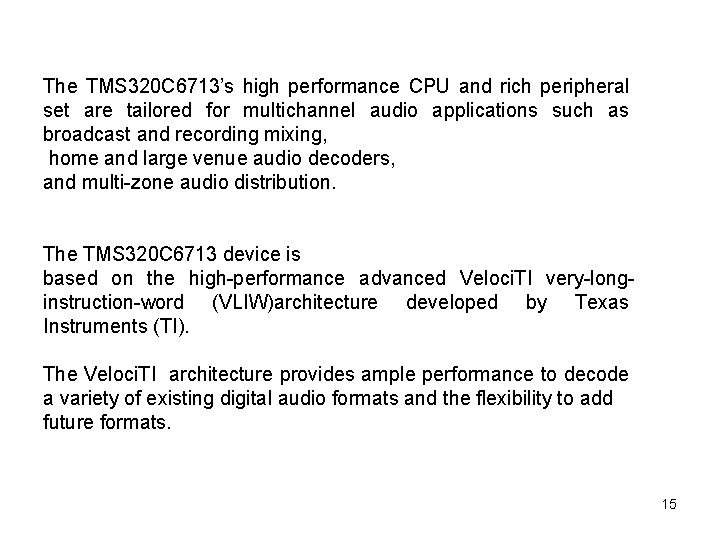

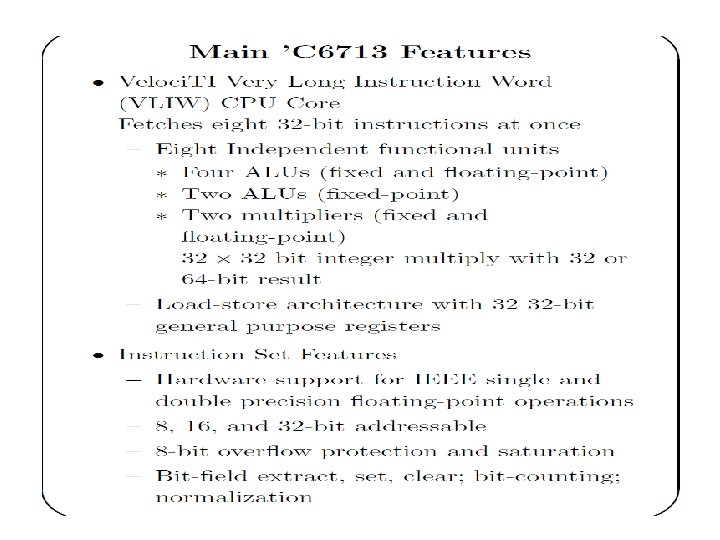

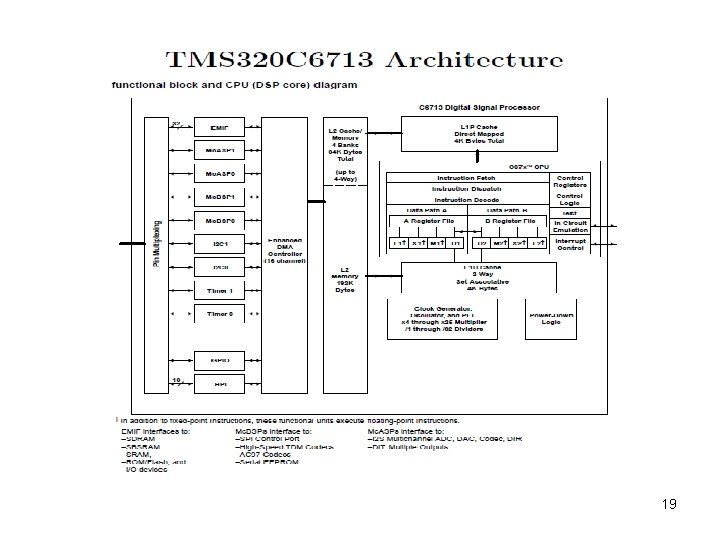

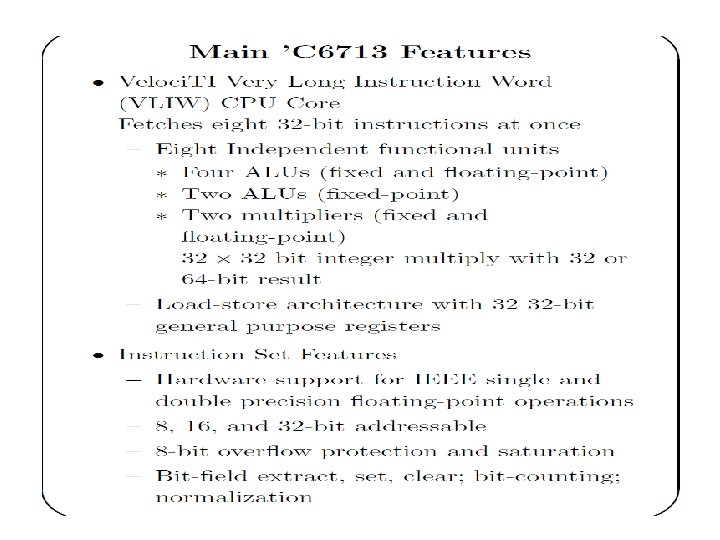

The TMS 320 C 6713’s high performance CPU and rich peripheral set are tailored for multichannel audio applications such as broadcast and recording mixing, home and large venue audio decoders, and multi-zone audio distribution. The TMS 320 C 6713 device is based on the high-performance advanced Veloci. TI very-longinstruction-word (VLIW)architecture developed by Texas Instruments (TI). The Veloci. TI architecture provides ample performance to decode a variety of existing digital audio formats and the flexibility to add future formats. 15

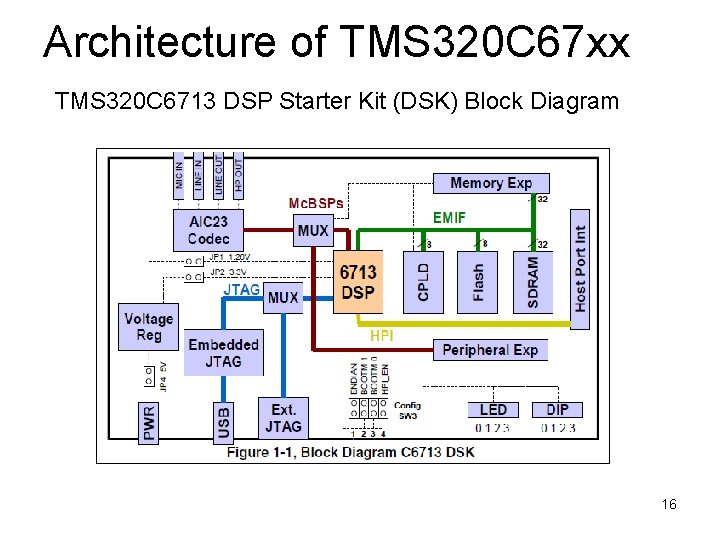

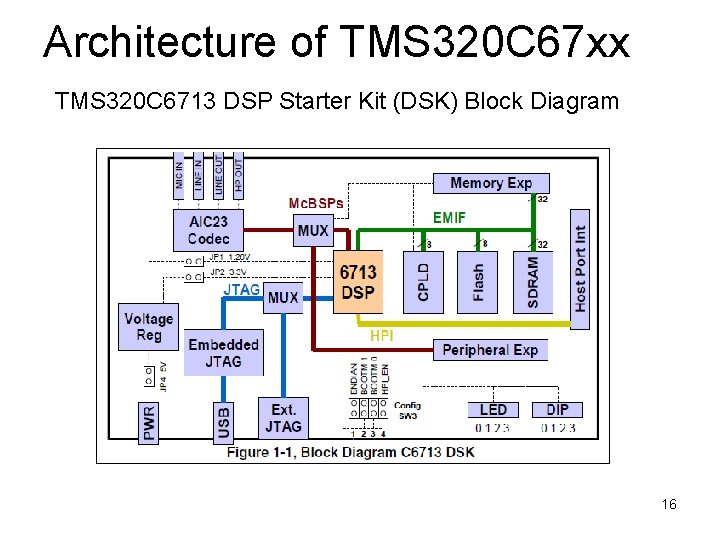

Architecture of TMS 320 C 67 xx TMS 320 C 6713 DSP Starter Kit (DSK) Block Diagram 16

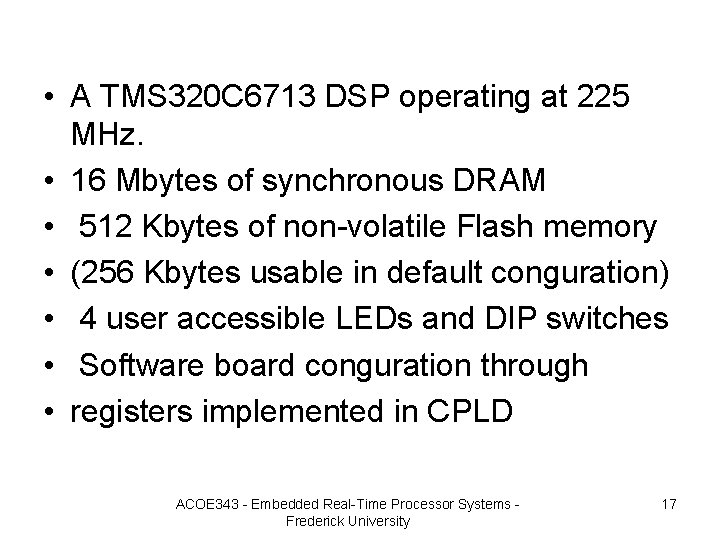

• A TMS 320 C 6713 DSP operating at 225 MHz. • 16 Mbytes of synchronous DRAM • 512 Kbytes of non-volatile Flash memory • (256 Kbytes usable in default conguration) • 4 user accessible LEDs and DIP switches • Software board conguration through • registers implemented in CPLD ACOE 343 - Embedded Real-Time Processor Systems - Frederick University 17

• JTAG emulation through on-board JTAG • emulator with USB host interface or external emulator 18

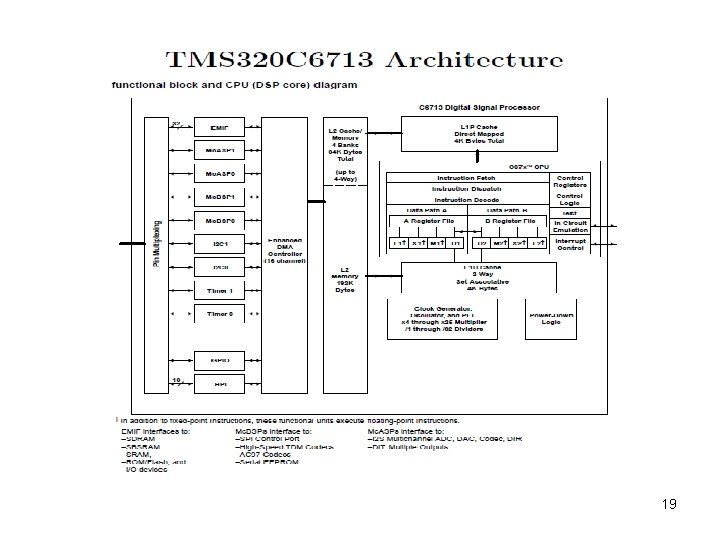

19

20

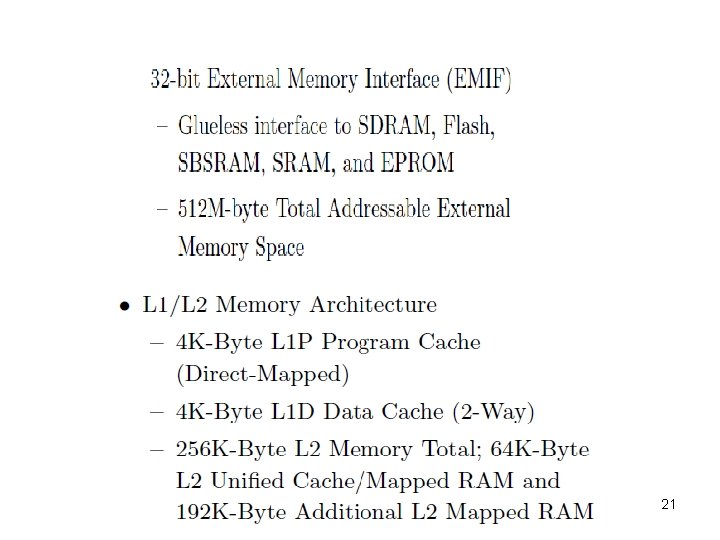

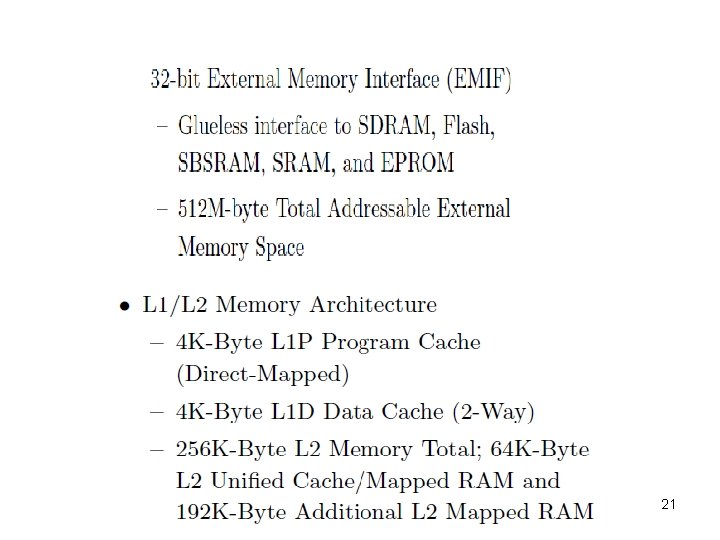

21

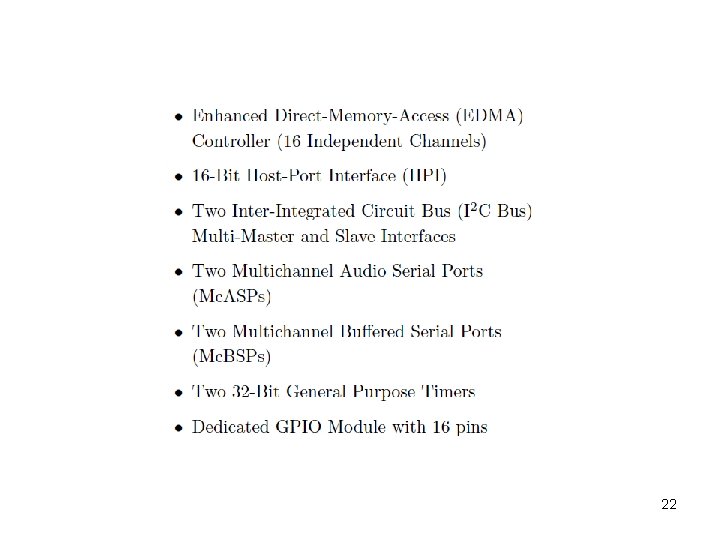

22

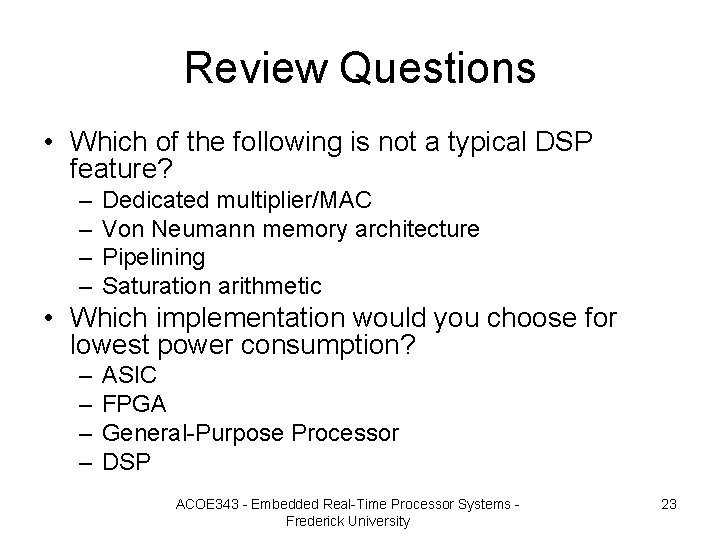

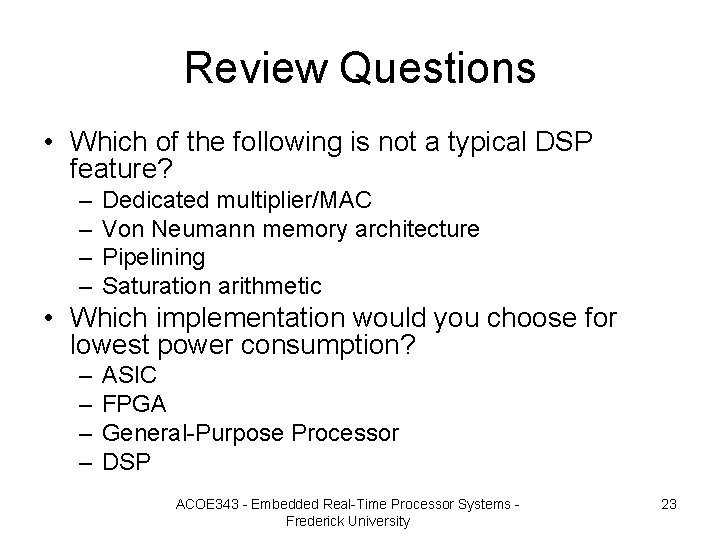

Review Questions • Which of the following is not a typical DSP feature? – – Dedicated multiplier/MAC Von Neumann memory architecture Pipelining Saturation arithmetic • Which implementation would you choose for lowest power consumption? – – ASIC FPGA General-Purpose Processor DSP ACOE 343 - Embedded Real-Time Processor Systems - Frederick University 23

References • DR. Chassaing, “DSP Applications using C and the TMS 320 C 6 x DSK”, Wiley, 2002 • Texas Instruments, TMS 320 C 64 x datasheets • Analog Devices, ADSP-21 xx Processors 24