Academy Xilinx DSP Page 1 Existing DSP Solutions

- Slides: 26

Academy - Xilinx DSP Page 1

Existing DSP Solutions • Fixed function DSP devices • ASICs • Standard DSP processors (only programmable solution) But what do you do when. . . … the fastest DSP Processor Is Not Fast Enough? l Add more DSP processors? l Design a custom gate array? Academy - Xilinx DSP Page 2

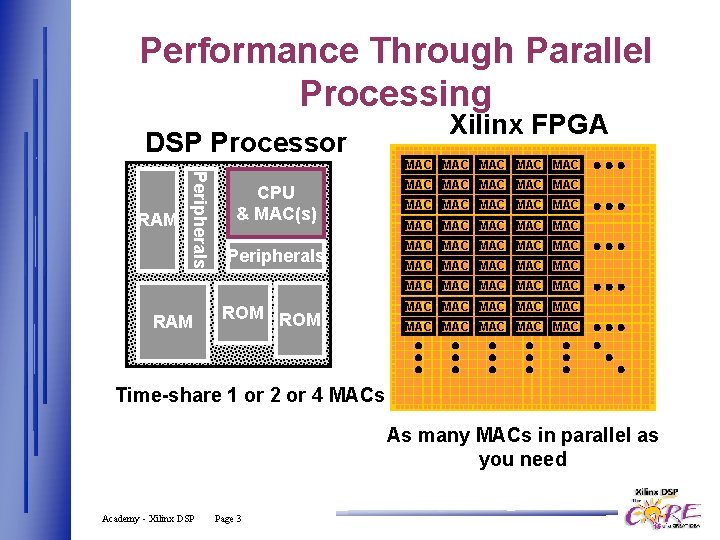

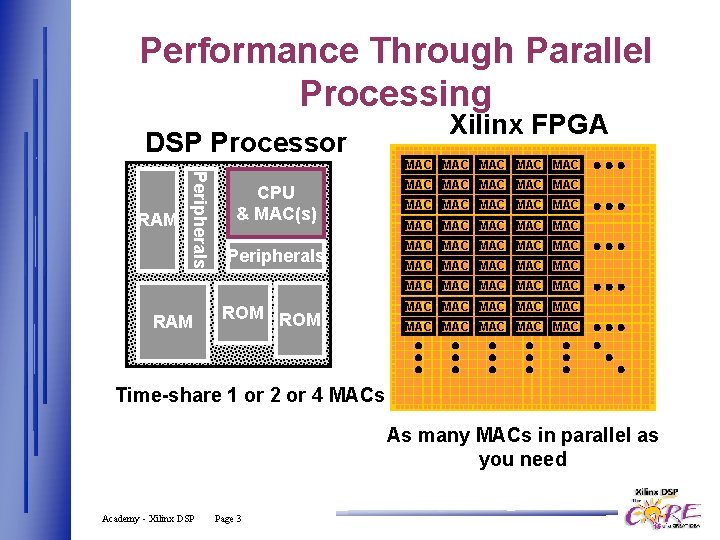

Performance Through Parallel Processing DSP Processor Peripherals RAM Xilinx FPGA MAC MAC MAC CPU & MAC(s) Peripherals MAC MAC MAC MAC MAC MAC MAC MAC RAM ROM MAC MAC MAC Time-share 1 or 2 or 4 MACs As many MACs in parallel as you need Academy - Xilinx DSP Page 3

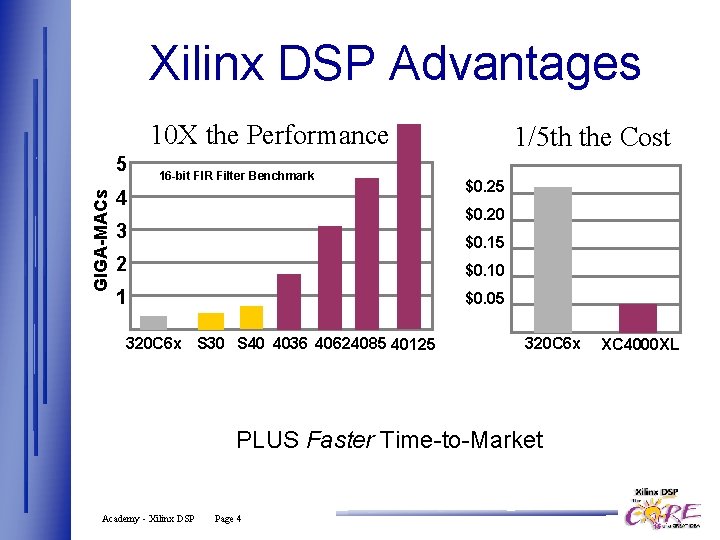

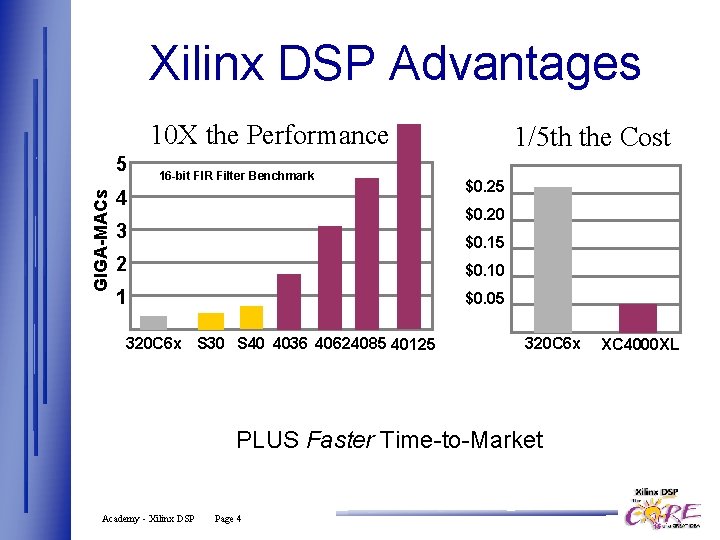

Xilinx DSP Advantages 10 X the Performance GIGA-MACs 5 16 -bit FIR Filter Benchmark 4 1/5 th the Cost $0. 25 $0. 20 3 $0. 15 2 $0. 10 1 $0. 05 320 C 6 x S 30 S 40 4036 40624085 40125 320 C 6 x PLUS Faster Time-to-Market Academy - Xilinx DSP Page 4 XC 4000 XL

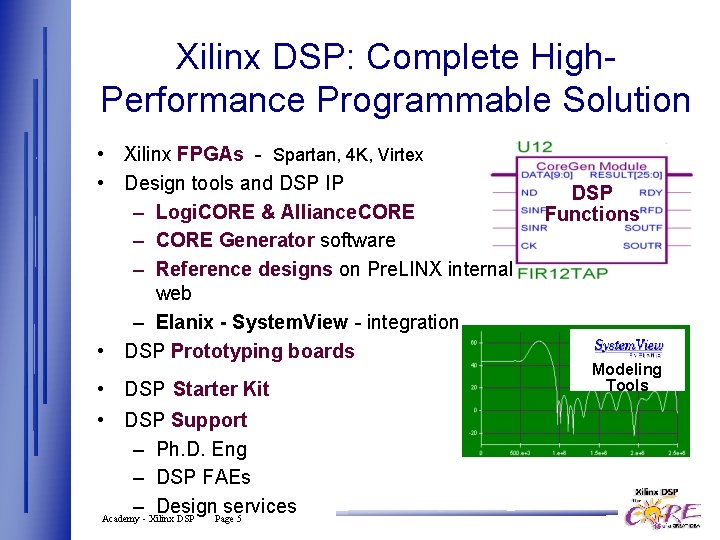

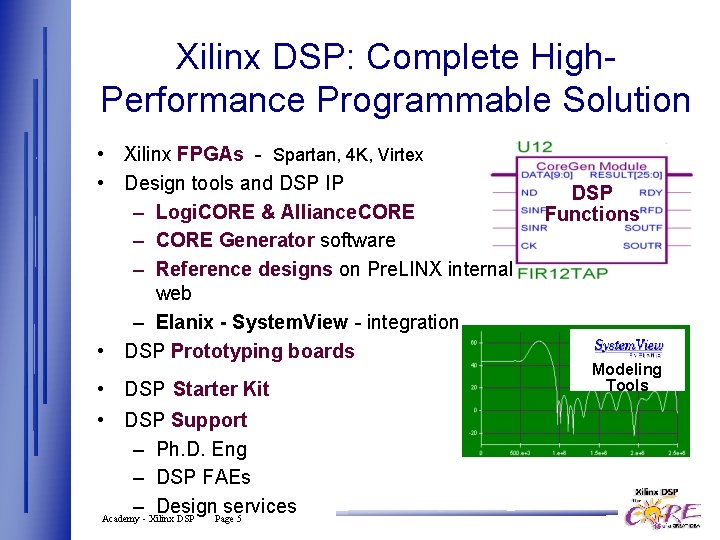

Xilinx DSP: Complete High. Performance Programmable Solution • Xilinx FPGAs - Spartan, 4 K, Virtex • Design tools and DSP IP – Logi. CORE & Alliance. CORE – CORE Generator software – Reference designs on Pre. LINX internal web – Elanix - System. View - integration • DSP Prototyping boards • DSP Starter Kit • DSP Support – Ph. D. Eng – DSP FAEs – Design. Page services Academy - Xilinx DSP 5 DSP Functions Modeling Tools

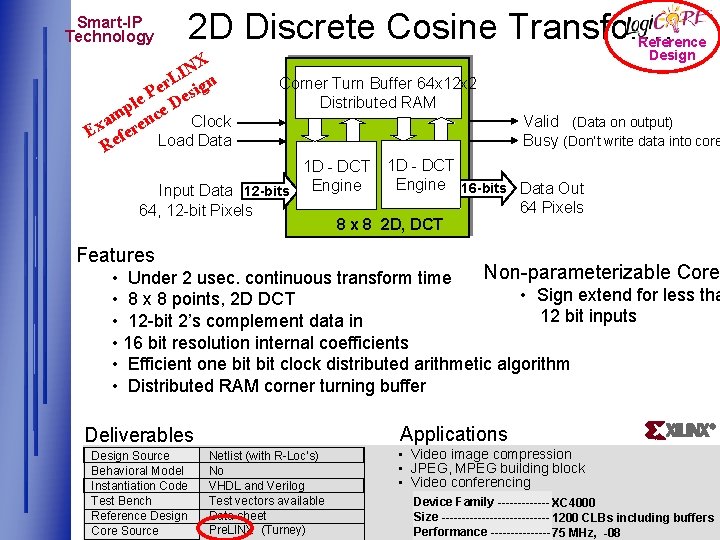

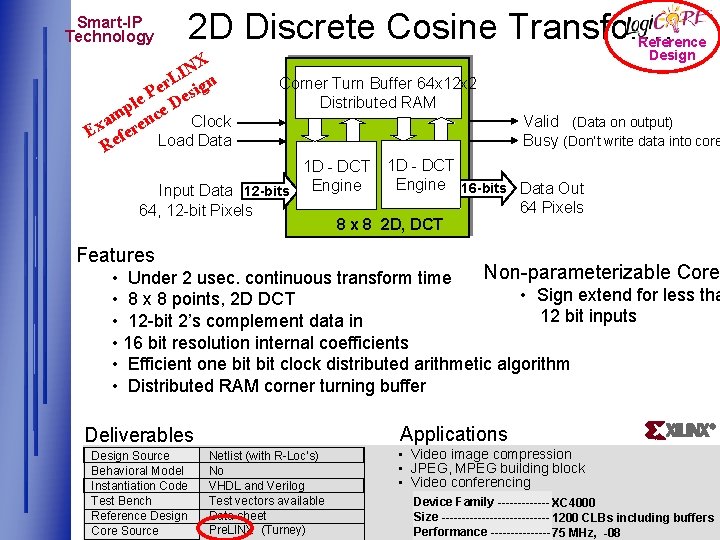

Smart-IP Technology 2 D Discrete Cosine Transform NX I er. L sign P le e De p Clock am renc x E efe Load Data R Reference Design Corner Turn Buffer 64 x 12 x 2 Distributed RAM Valid (Data on output) Busy (Don’t write data into core 1 D - DCT Engine 16 -bits Data Out Input Data 12 -bits Engine 64 Pixels 64, 12 -bit Pixels 8 x 8 2 D, DCT Features Non-parameterizable Core • Under 2 usec. continuous transform time • Sign extend for less tha • 8 x 8 points, 2 D DCT 12 bit inputs • 12 -bit 2’s complement data in • 16 bit resolution internal coefficients • Efficient one bit clock distributed arithmetic algorithm • Distributed RAM corner turning buffer Applications Deliverables Design Source Behavioral Model Instantiation Code Test Bench Reference Design Academy - Xilinx DSP Core Source Netlist (with R-Loc’s) No VHDL and Verilog Test vectors available Data Page 6 sheet Pre. LINX (Turney) • Video image compression • JPEG, MPEG building block • Video conferencing Device Family ------- XC 4000 Size -------------- 1200 CLBs including buffers Performance -------- 75 MHz, -08

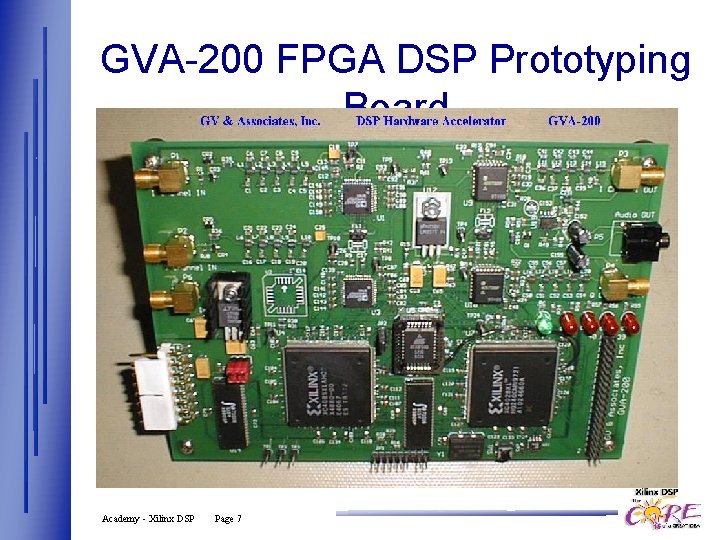

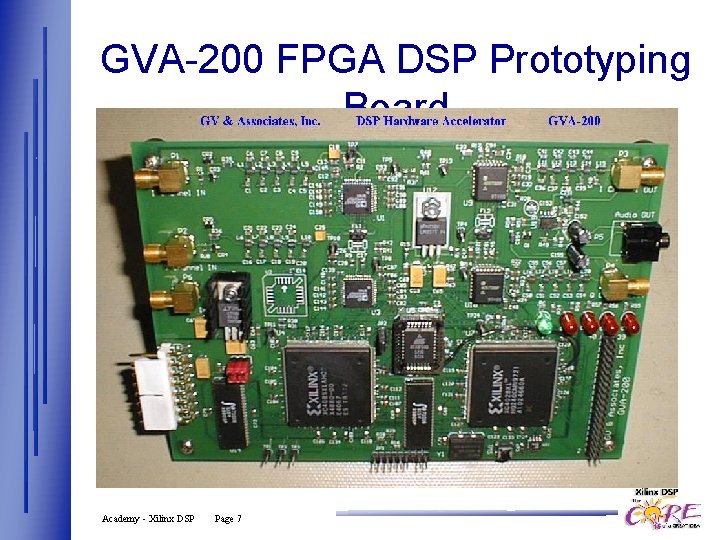

GVA-200 FPGA DSP Prototyping Board Academy - Xilinx DSP Page 7

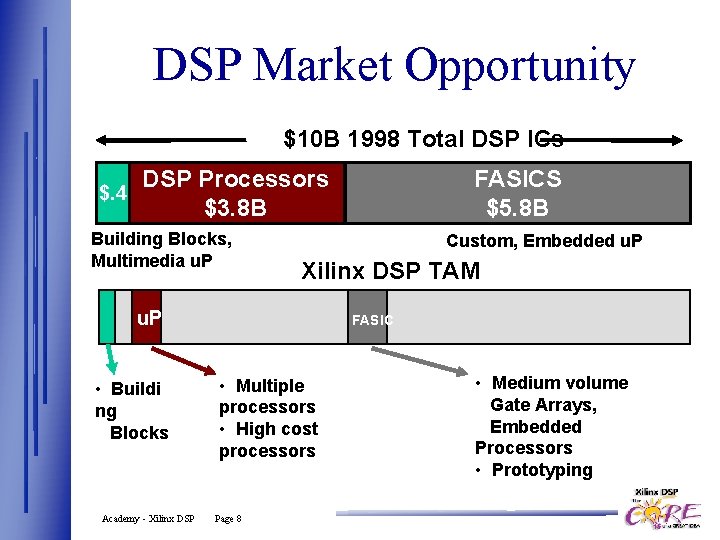

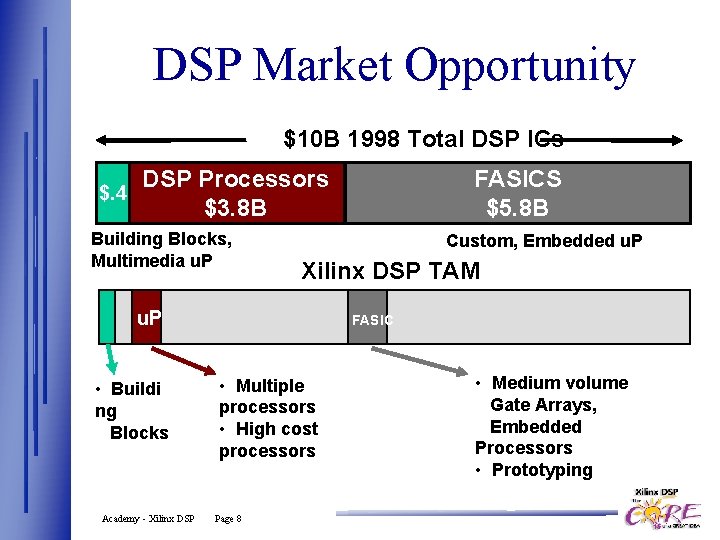

DSP Market Opportunity $10 B 1998 Total DSP ICs DSP Processors $. 4 $3. 8 B Building Blocks, Multimedia u. P Custom, Embedded u. P Xilinx DSP TAM u. P • Buildi ng Blocks Academy - Xilinx DSP FASICS $5. 8 B FASIC • Multiple processors • High cost processors Page 8 • Medium volume Gate Arrays, Embedded Processors • Prototyping

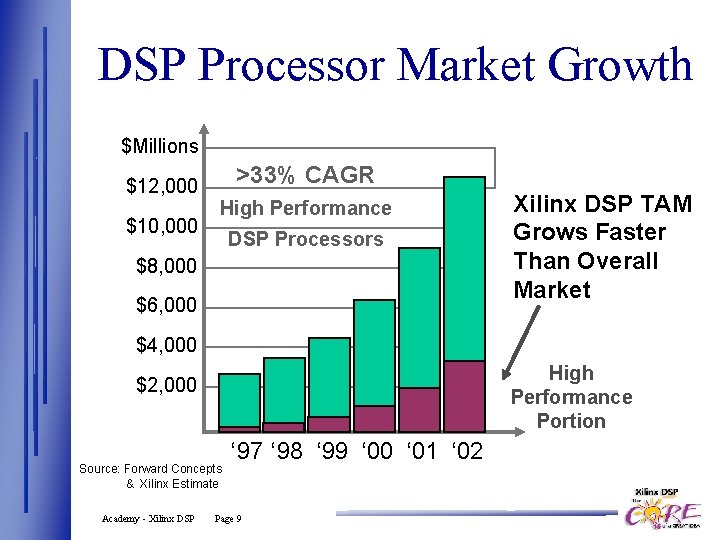

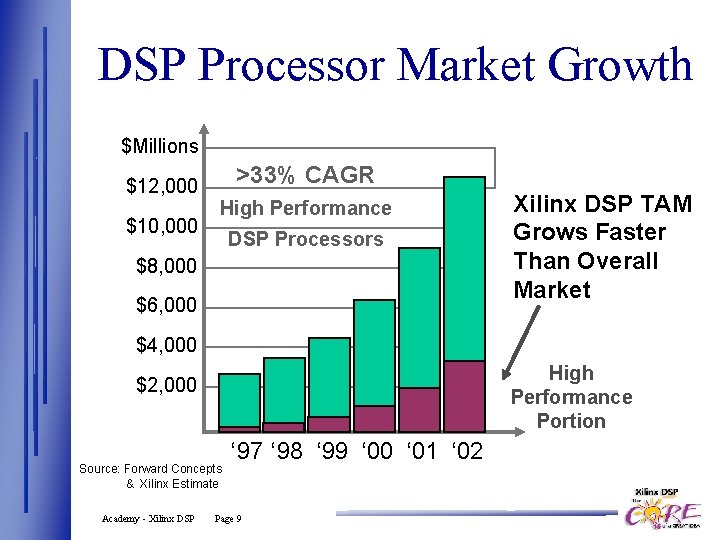

DSP Processor Market Growth $Millions $12, 000 $10, 000 >33% CAGR High Performance DSP Processors $8, 000 $6, 000 Xilinx DSP TAM Grows Faster Than Overall Market $4, 000 High Performance Portion $2, 000 Source: Forward Concepts & Xilinx Estimate Academy - Xilinx DSP ‘ 97 ‘ 98 ‘ 99 ‘ 00 ‘ 01 ‘ 02 Page 9

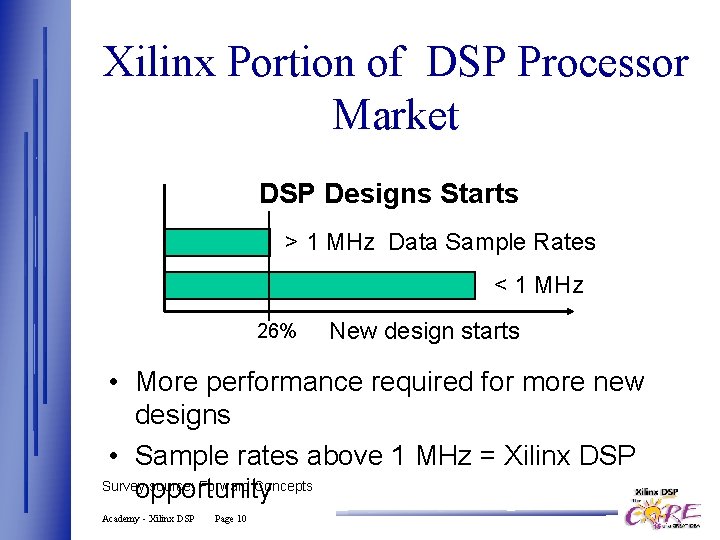

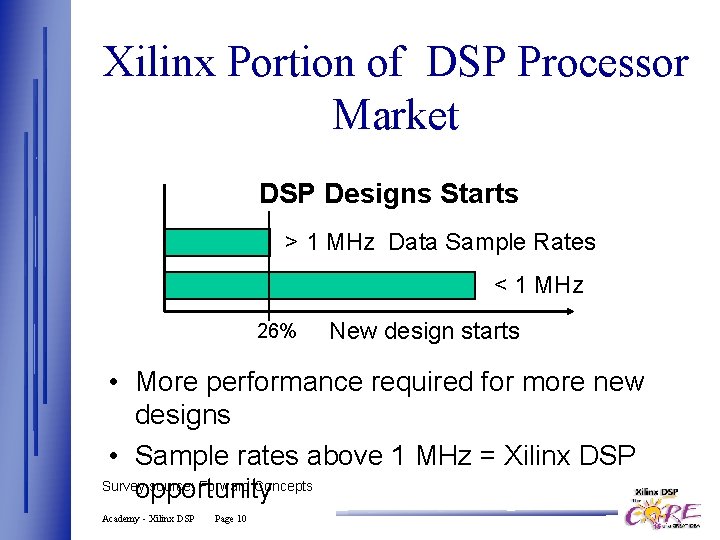

Xilinx Portion of DSP Processor Market DSP Designs Starts > 1 MHz Data Sample Rates < 1 MHz 26% New design starts • More performance required for more new designs • Sample rates above 1 MHz = Xilinx DSP Survey source: Forward Concepts opportunity Academy - Xilinx DSP Page 10

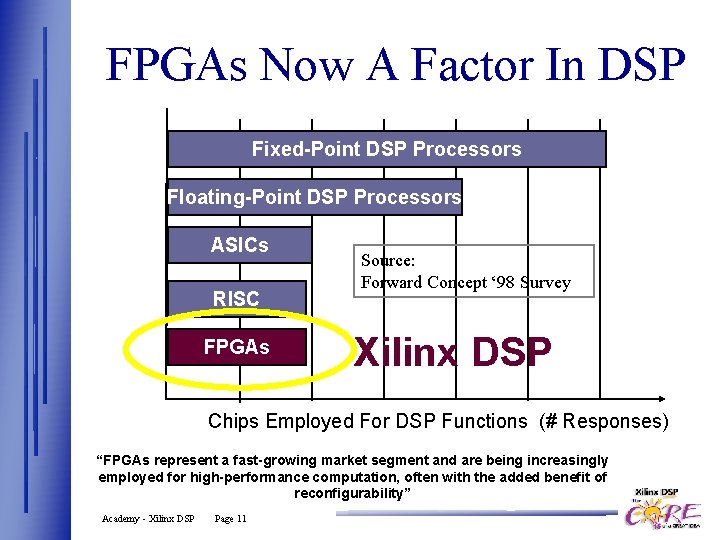

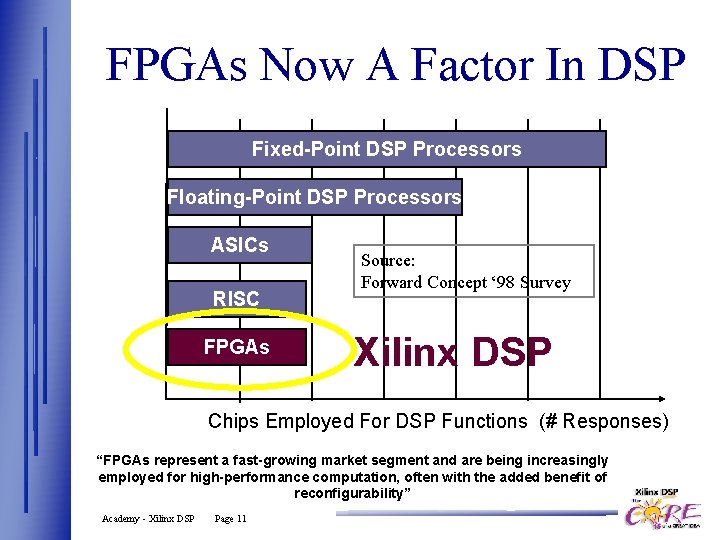

FPGAs Now A Factor In DSP Fixed-Point DSP Processors Floating-Point DSP Processors ASICs RISC FPGAs Source: Forward Concept ‘ 98 Survey Xilinx DSP Chips Employed For DSP Functions (# Responses) “FPGAs represent a fast-growing market segment and are being increasingly employed for high-performance computation, often with the added benefit of reconfigurability” Academy - Xilinx DSP Page 11

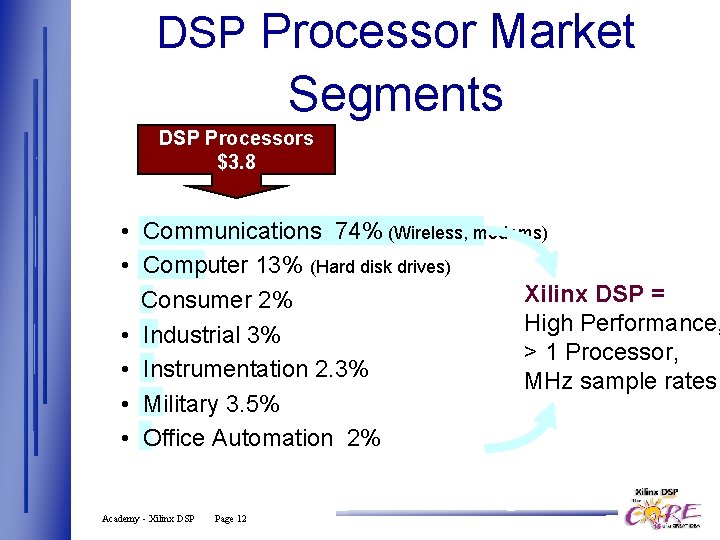

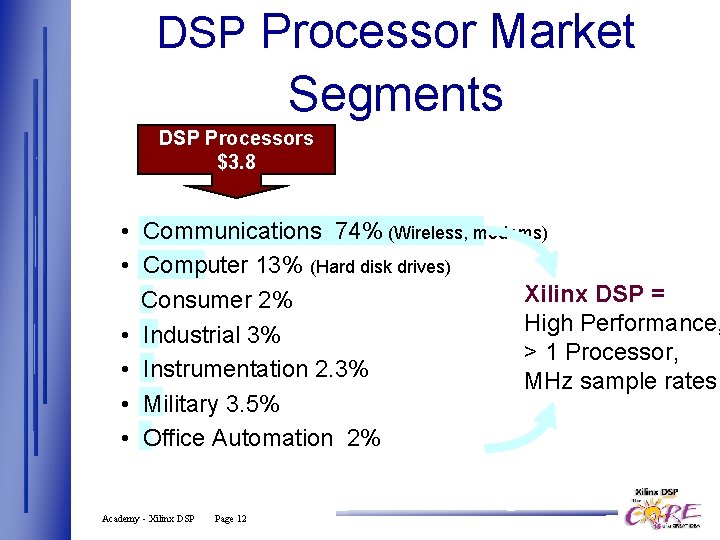

DSP Processor Market Segments DSP Processors $3. 8 • Communications 74% (Wireless, modems) • Computer 13% (Hard disk drives) Xilinx DSP = Consumer 2% High Performance, • Industrial 3% > 1 Processor, • Instrumentation 2. 3% MHz sample rates • Military 3. 5% • Office Automation 2% Academy - Xilinx DSP Page 12

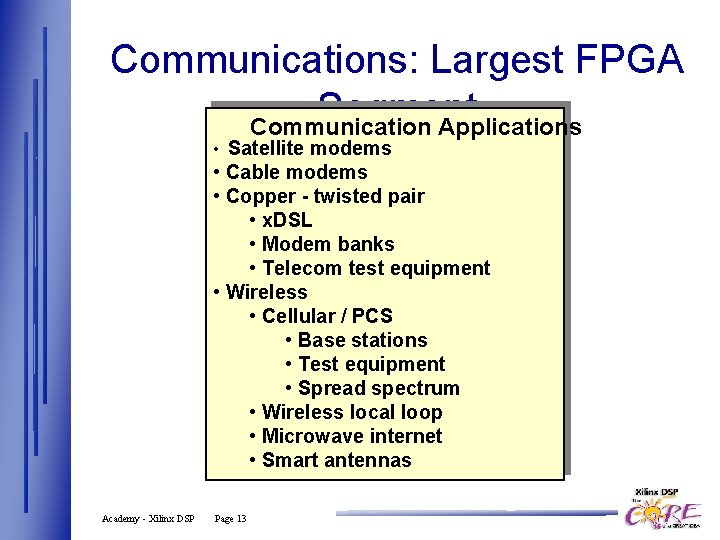

Communications: Largest FPGA Segment Communication Applications Satellite modems • Cable modems • Copper - twisted pair • x. DSL • Modem banks • Telecom test equipment • Wireless • Cellular / PCS • Base stations • Test equipment • Spread spectrum • Wireless local loop • Microwave internet • Smart antennas • Academy - Xilinx DSP Page 13

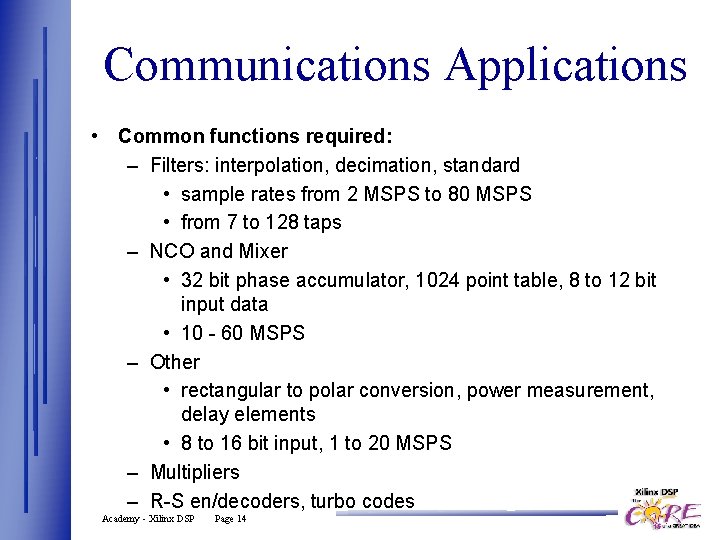

Communications Applications • Common functions required: – Filters: interpolation, decimation, standard • sample rates from 2 MSPS to 80 MSPS • from 7 to 128 taps – NCO and Mixer • 32 bit phase accumulator, 1024 point table, 8 to 12 bit input data • 10 - 60 MSPS – Other • rectangular to polar conversion, power measurement, delay elements • 8 to 16 bit input, 1 to 20 MSPS – Multipliers – R-S en/decoders, turbo codes Academy - Xilinx DSP Page 14

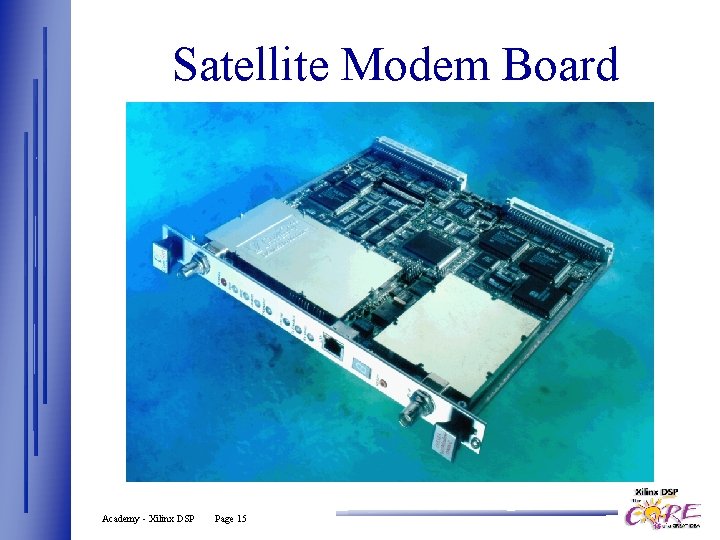

Satellite Modem Board Academy - Xilinx DSP Page 15

Other High Performance Applications • Video and image processing – Medical - Ultrasound, MRI, CT – Industrial - security, manufacturing – Set top boxes – Digital TV broadcast equipment – HDTV • Military - radar, sonar, encryption, guidance, navigation, software radios • Instrumentation • Office automation Academy - Xilinx DSP Page 16

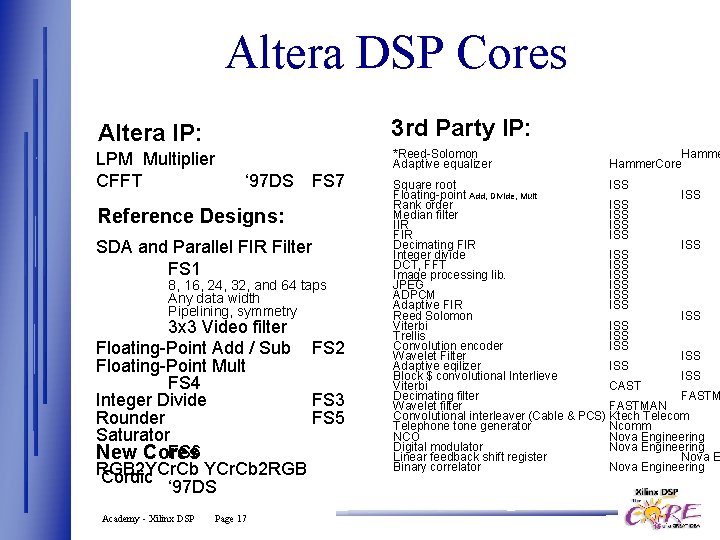

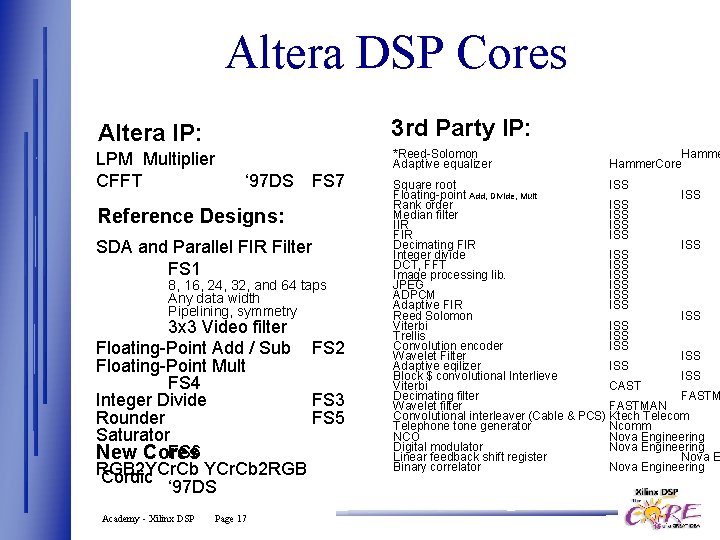

Altera DSP Cores Altera IP: 3 rd Party IP: LPM Multiplier CFFT *Reed-Solomon Adaptive equalizer ‘ 97 DS FS 7 Reference Designs: SDA and Parallel FIR Filter FS 1 8, 16, 24, 32, and 64 taps Any data width Pipelining, symmetry 3 x 3 Video filter Floating-Point Add / Sub FS 2 Floating-Point Mult FS 4 Integer Divide FS 3 Rounder FS 5 Saturator FS 6 New Cores RGB 2 YCr. Cb 2 RGB Cordic ‘ 97 DS Academy - Xilinx DSP Page 17 Hammer. Core Square root ISS Floating-point Add, Divide, Mult ISS Rank order ISS Median filter ISS IIR ISS FIR ISS Decimating FIR ISS Integer divide ISS DCT, FFT ISS Image processing lib. ISS JPEG ISS ADPCM ISS Adaptive FIR ISS Reed Solomon ISS Viterbi ISS Trellis ISS Convolution encoder ISS Wavelet Filter ISS Adaptive eqilizer ISS Block $ convolutional Interlieve ISS Viterbi CAST Decimating filter FASTM Wavelet filter FASTMAN Convolutional interleaver (Cable & PCS) Ktech Telecom Telephone tone generator Ncomm NCO Nova Engineering Digital modulator Nova Engineering Linear feedback shift register Nova E Binary correlator Nova Engineering

Altera Competitive Analysis • Cores – Good Multipliers and Parallel FIR – Inefficient SDA FIR filters – Most Altera reference designs are parameterizable • Easy to do with AHDL code • Not Smart-IP – More 3 rd party DSP IP - but not effective – Little internal DSP IP • Customer 3 rd party IP evaluation capability (security) • No announced DSP system level tools Academy - Xilinx DSP Page 18

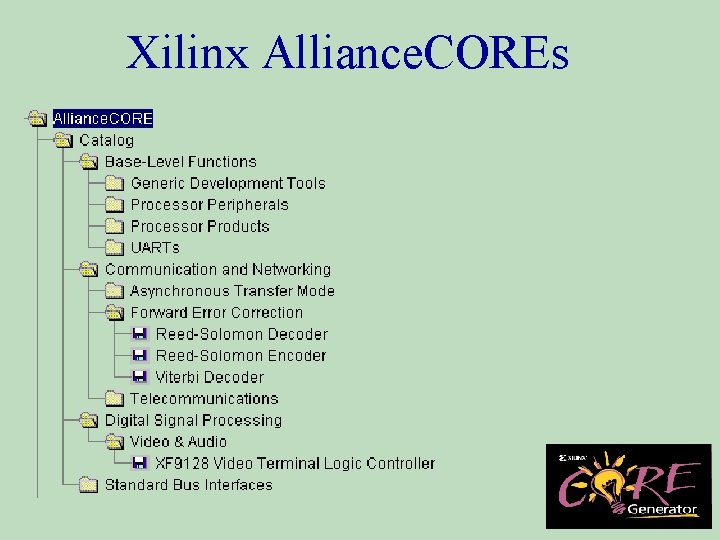

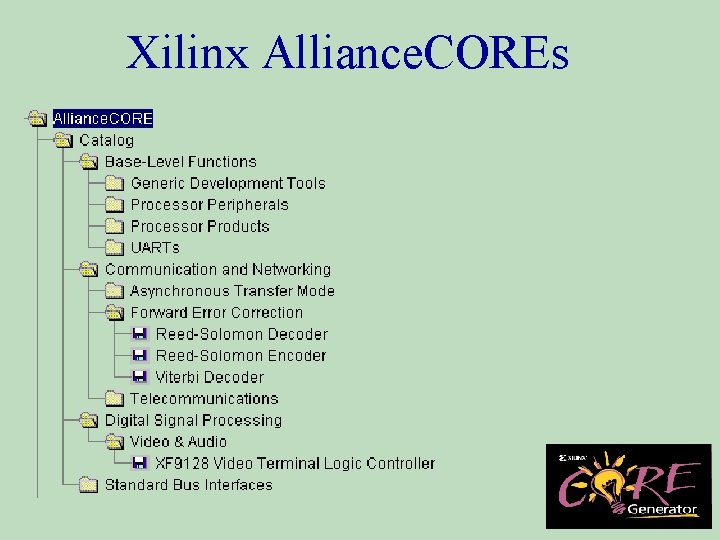

Xilinx Alliance. COREs Academy - Xilinx DSP Page 19

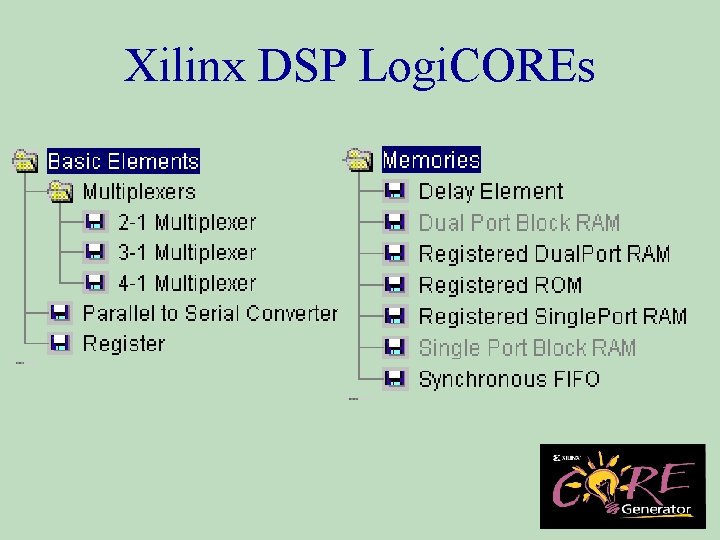

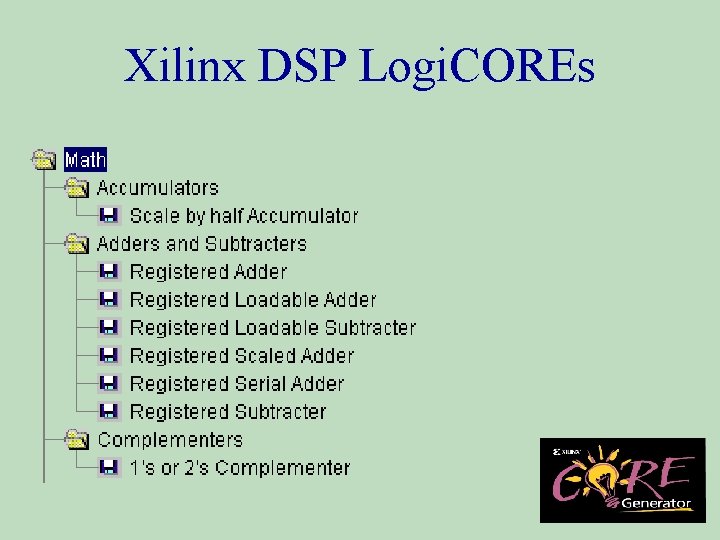

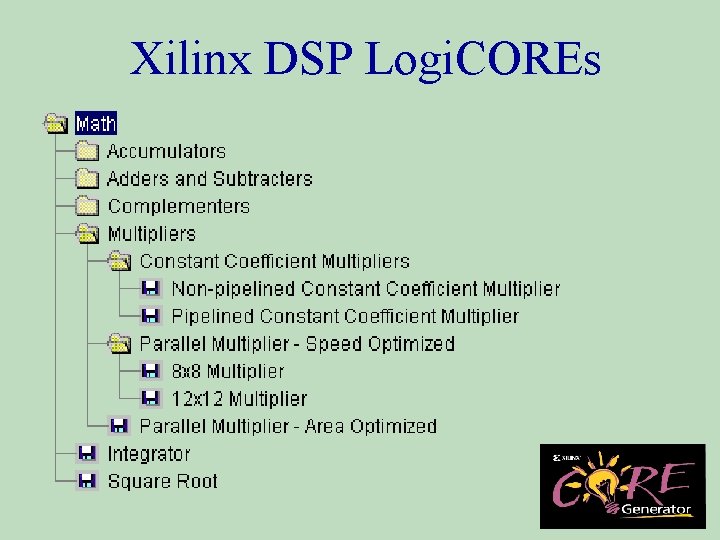

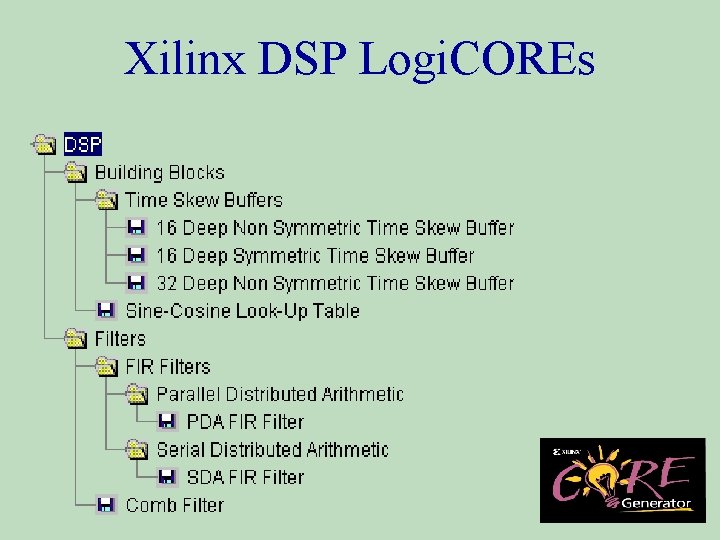

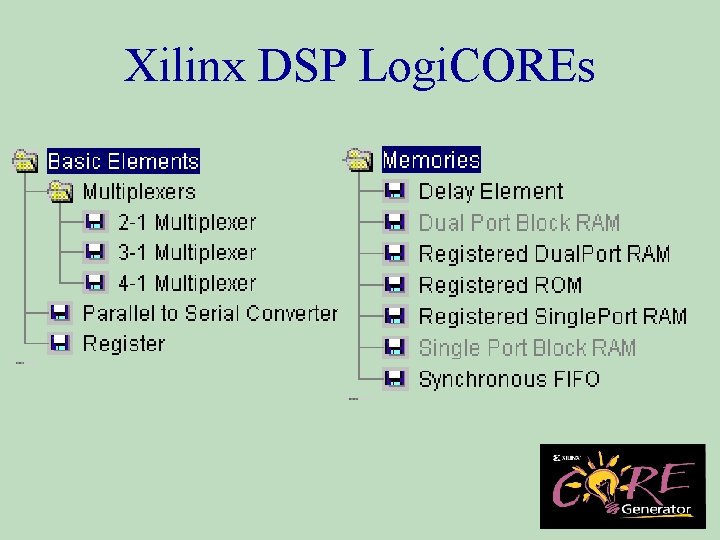

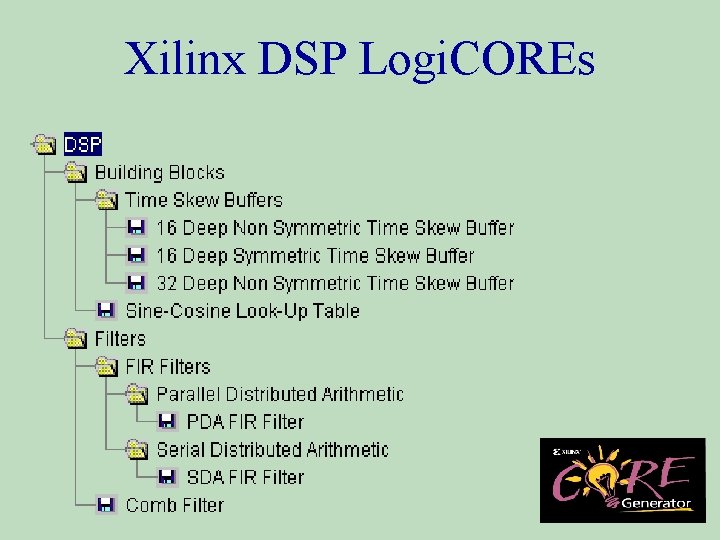

Xilinx DSP Logi. COREs Academy - Xilinx DSP Page 20

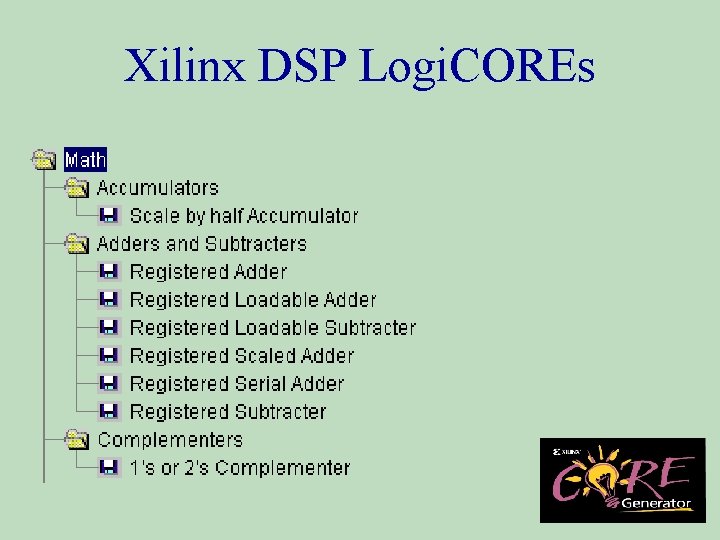

Xilinx DSP Logi. COREs Academy - Xilinx DSP Page 21

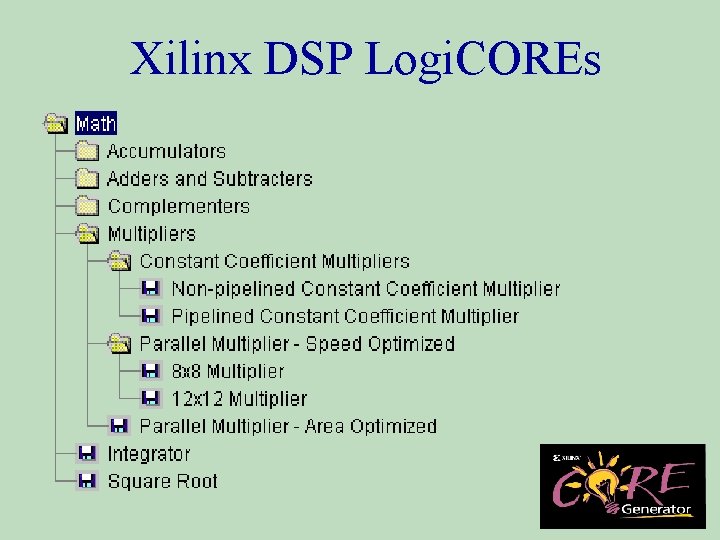

Xilinx DSP Logi. COREs Academy - Xilinx DSP Page 22

Xilinx DSP Logi. COREs Academy - Xilinx DSP Page 23

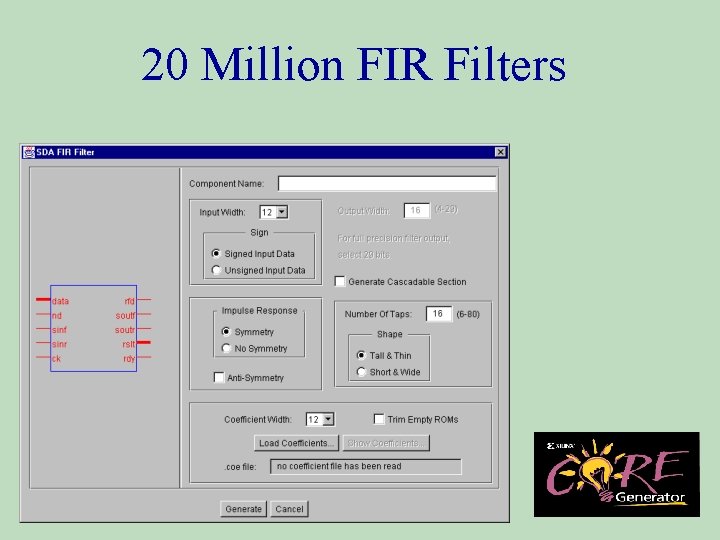

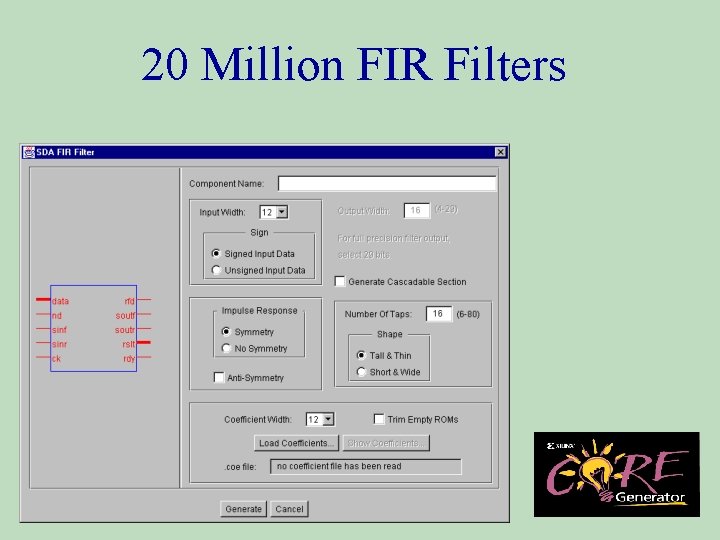

20 Million FIR Filters Academy - Xilinx DSP Page 24

SDA FIR Filter • • • Most commonly used core Parallel In, Parallel Out Bit serial processing All taps processed in parallel Full precession through entire core One clock cycle required for each data bit • One additional clock cycle for symmetric filters Academy - Xilinx DSP Page 25

• The Solution to High Performance DSP Higher performance – 10 X faster, parallel processing • Lower power – 50% to 80% less than DSP processors • Lower price – 1/5 th the cost, Spartan FPGAs at ASIC prices • Faster time to market – Simpler design flow, no real-time software Add a Xilinx FPGA, not more processors Academy - Xilinx DSP Page 26