Enabling HighPrecision HighPerformance DSP VariablePrecision DSP Architecture 2010

Enabling High-Precision, High-Performance DSP Variable-Precision DSP Architecture 2010 Technology Roadshow © 2010 Altera Corporation—Public

Agenda n n n DSP system design trend Altera DSP architecture (28 nm) Summary © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 2

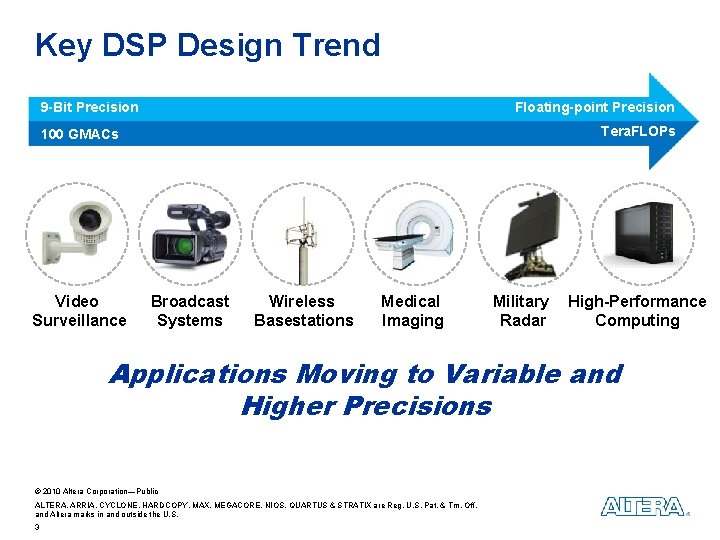

Key DSP Design Trend 9 -Bit Precision Floating-point Precision Tera. FLOPs 100 GMACs Video Surveillance Broadcast Systems Wireless Basestations Medical Imaging Military Radar High-Performance Computing Applications Moving to Variable and Higher Precisions © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 3

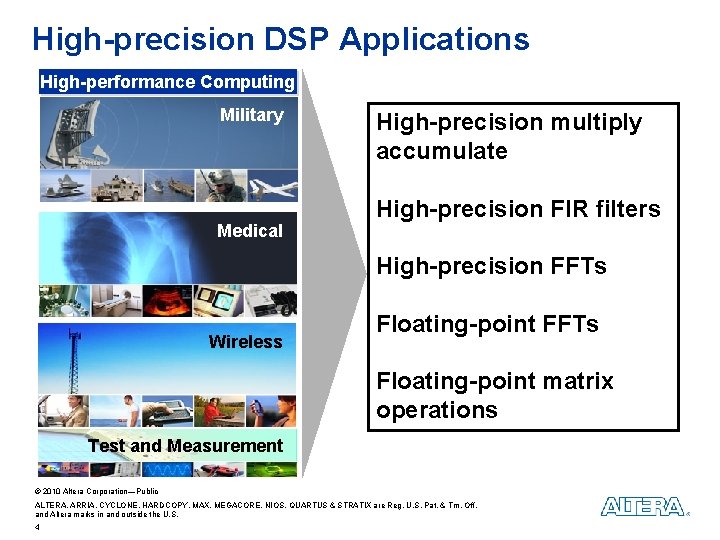

High-precision DSP Applications High-performance Computing Military Medical High-precision multiply accumulate High-precision FIR filters High-precision FFTs Wireless Floating-point FFTs Floating-point matrix operations Test and Measurement © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 4

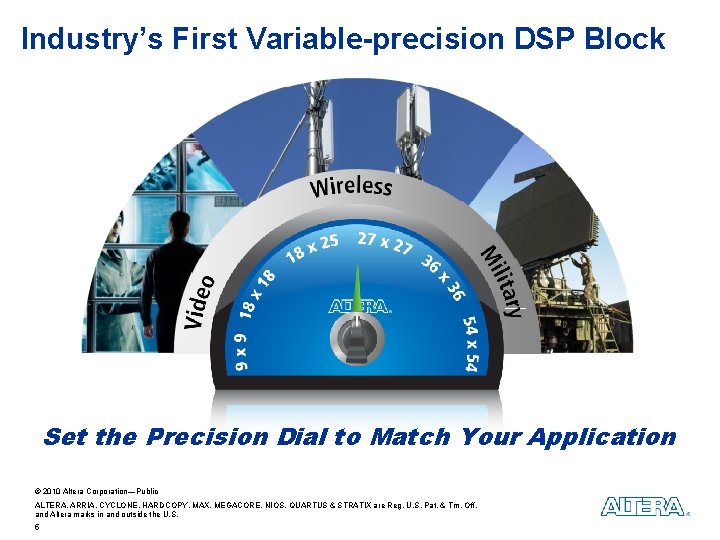

Industry’s First Variable-precision DSP Block Set the Precision Dial to Match Your Application © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 5

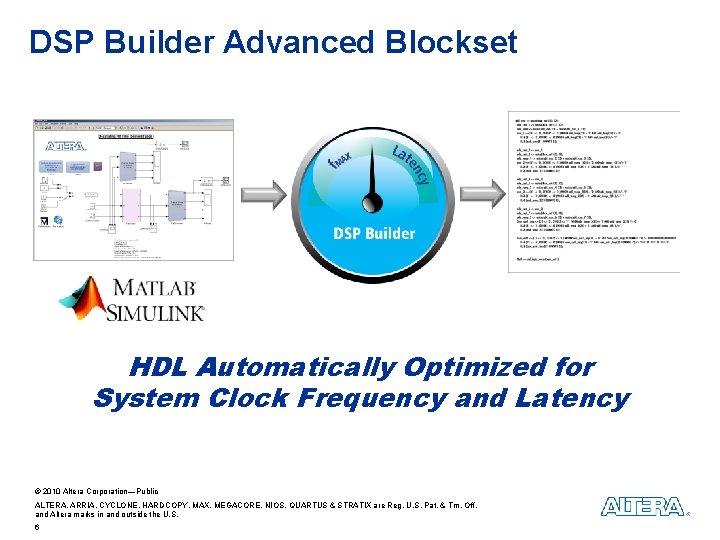

DSP Builder Advanced Blockset HDL Automatically Optimized for System Clock Frequency and Latency © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 6

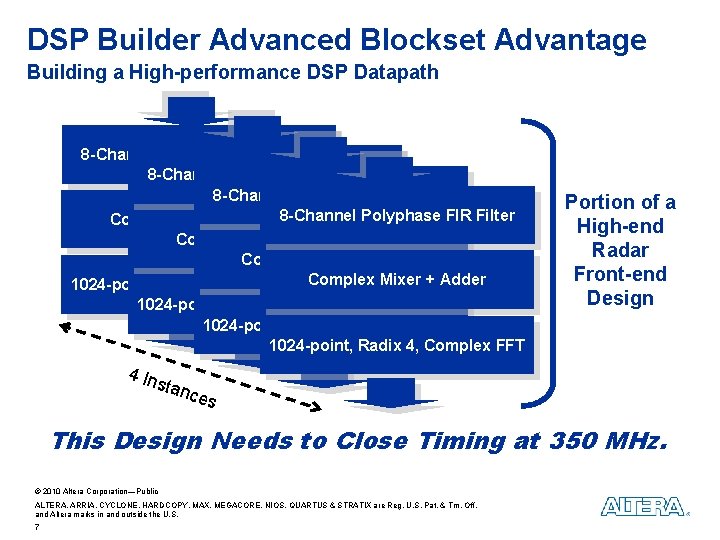

DSP Builder Advanced Blockset Advantage Building a High-performance DSP Datapath 8 -Channel Polyphase FIR Filter Complex Mixer + Adder 1024 -point, Radix 4, Complex FFT 4 In Portion of a High-end Radar Front-end Design stan ces This Design Needs to Close Timing at 350 MHz. © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 7

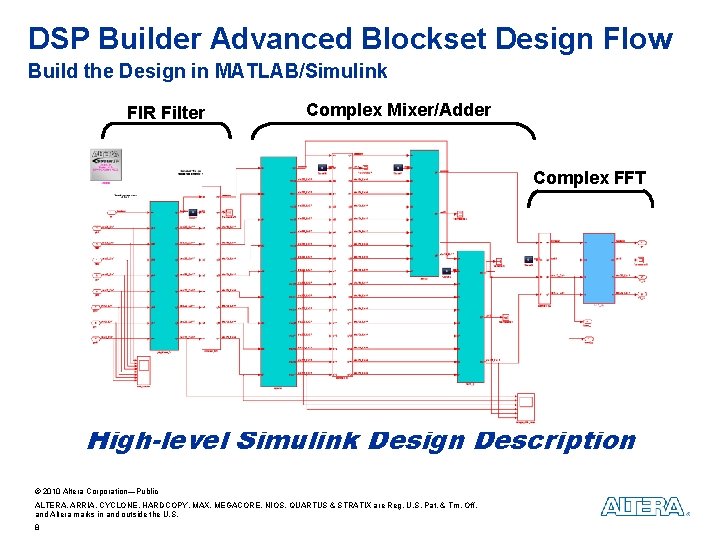

DSP Builder Advanced Blockset Design Flow Build the Design in MATLAB/Simulink FIR Filter Complex Mixer/Adder Complex FFT High-level Simulink Design Description © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 8

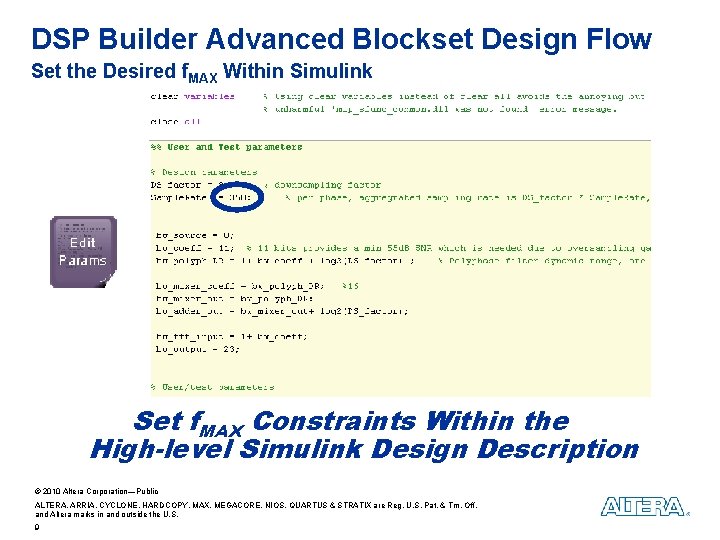

DSP Builder Advanced Blockset Design Flow Set the Desired f. MAX Within Simulink Set f. MAX Constraints Within the High-level Simulink Design Description © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 9

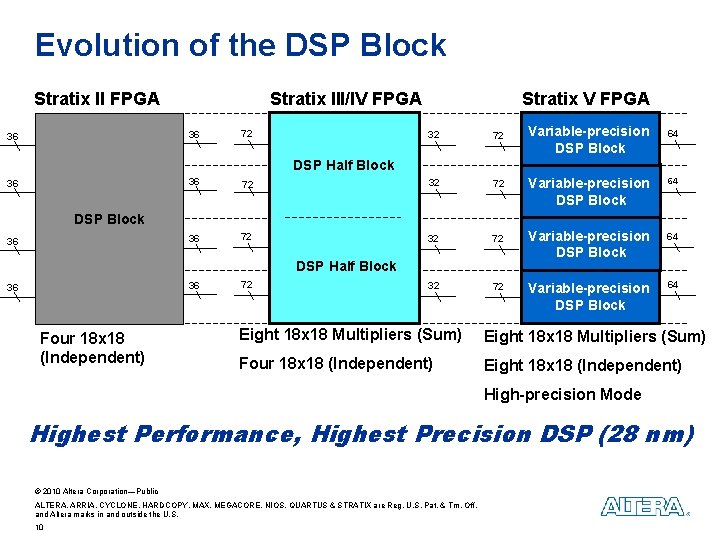

Evolution of the DSP Block Stratix II FPGA Stratix III/IV FPGA 36 36 72 Stratix V FPGA 32 72 Variable-precision DSP Block 64 DSP Half Block 36 36 72 32 72 Variable-precision DSP Block 64 DSP Block 36 DSP Half Block 36 36 Four 18 x 18 (Independent) 72 Eight 18 x 18 Multipliers (Sum) Four 18 x 18 (Independent) Eight 18 x 18 (Independent) High-precision Mode Highest Performance, Highest Precision DSP (28 nm) © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 10

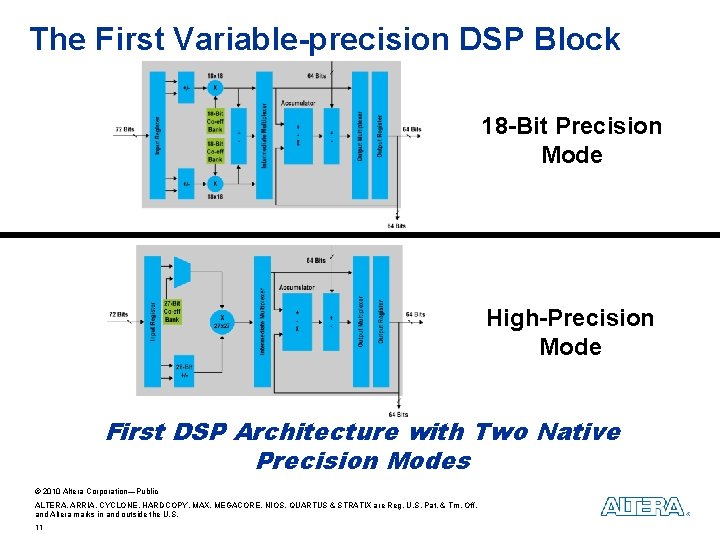

The First Variable-precision DSP Block 18 -Bit Precision Mode High-Precision Mode First DSP Architecture with Two Native Precision Modes © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 11

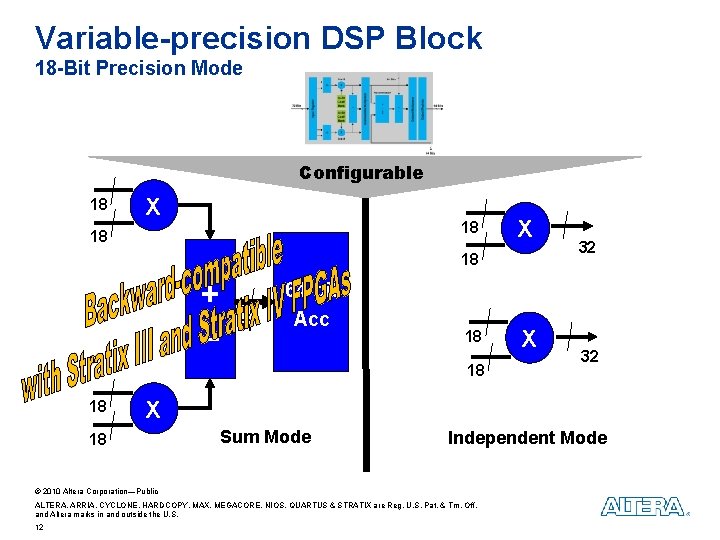

Variable-precision DSP Block 18 -Bit Precision Mode Configurable 18 X 18 + _ 37 64 -bit Acc 18 18 18 32 X 18 Sum Mode Independent Mode © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 12 X 32

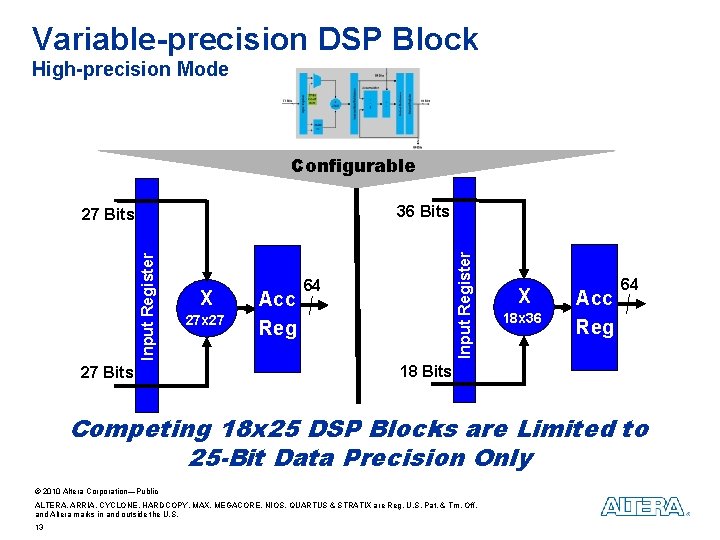

Variable-precision DSP Block High-precision Mode Configurable Input Register 27 Bits X 27 x 27 Acc Reg Input Register 36 Bits 27 Bits 64 X 18 x 36 Acc Reg 64 18 Bits Competing 18 x 25 DSP Blocks are Limited to 25 -Bit Data Precision Only © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 13

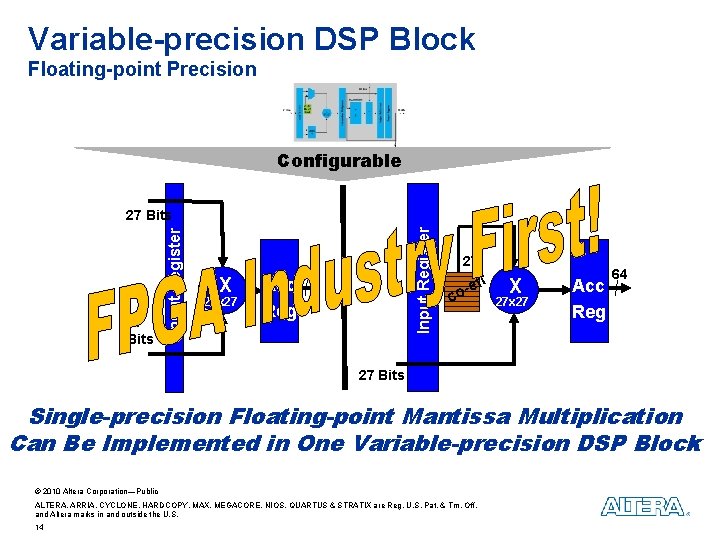

Variable-precision DSP Block Floating-point Precision Configurable X 27 x 27 Acc Reg Input Register 27 Bits 64 27 c ff o-e X 27 x 27 Acc Reg 64 27 Bits Single-precision Floating-point Mantissa Multiplication Can Be Implemented in One Variable-precision DSP Block © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 14

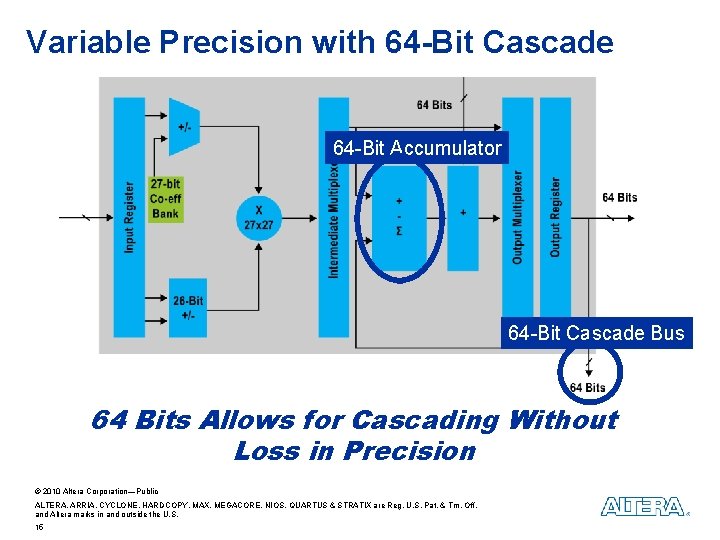

Variable Precision with 64 -Bit Cascade 64 -Bit Accumulator 64 -Bit Cascade Bus 64 Bits Allows for Cascading Without Loss in Precision © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 15

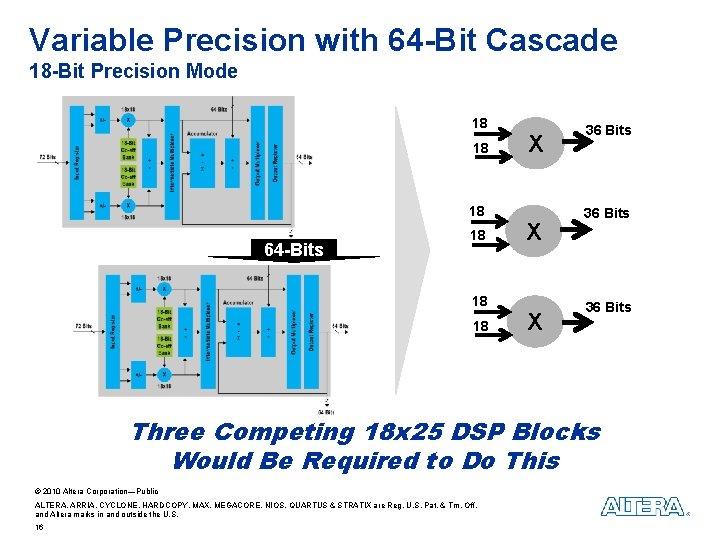

Variable Precision with 64 -Bit Cascade 18 -Bit Precision Mode 18 18 18 64 -Bits 18 18 18 X X X 36 Bits Three Competing 18 x 25 DSP Blocks Would Be Required to Do This © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 16

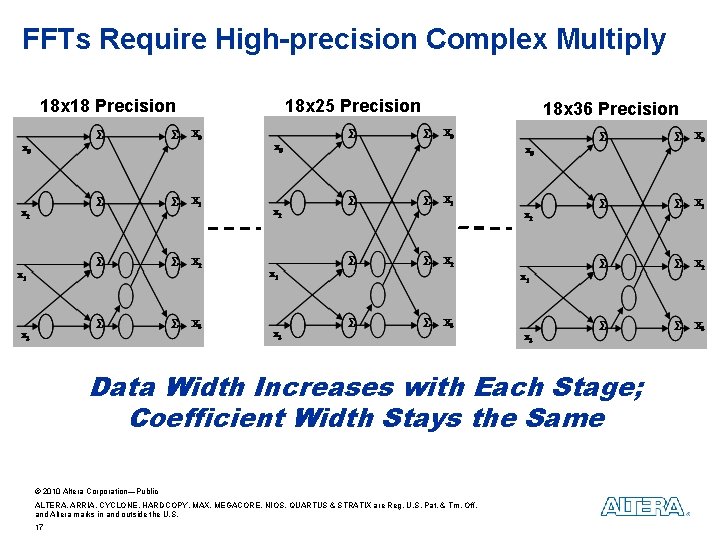

FFTs Require High-precision Complex Multiply 18 x 18 Precision 18 x 25 Precision 18 x 36 Precision Data Width Increases with Each Stage; Coefficient Width Stays the Same © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 17

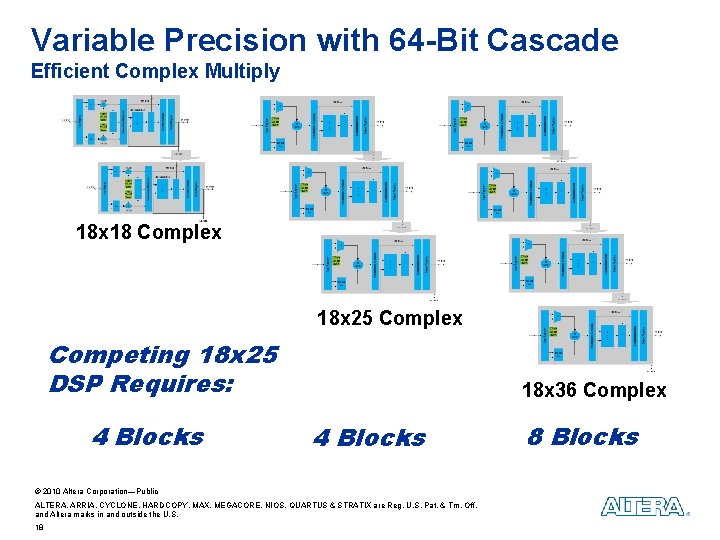

Variable Precision with 64 -Bit Cascade Efficient Complex Multiply 18 x 18 Complex 18 x 25 Complex Competing 18 x 25 DSP Requires: 4 Blocks 18 x 36 Complex 4 Blocks © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 18 8 Blocks

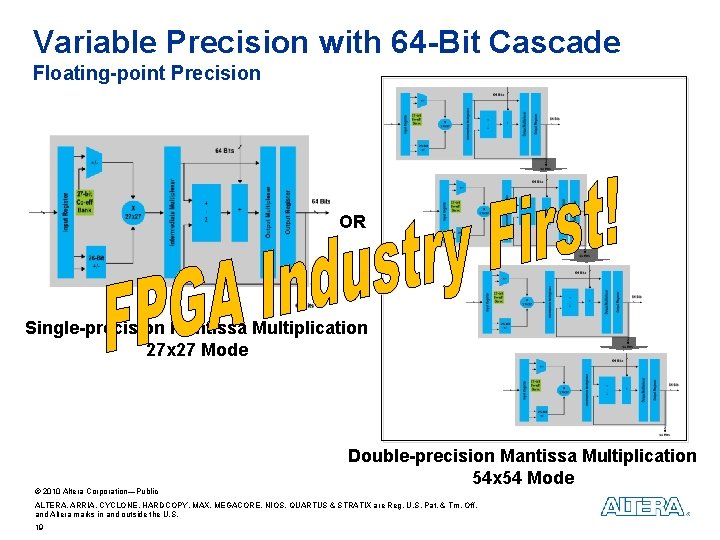

Variable Precision with 64 -Bit Cascade Floating-point Precision OR Single-precision Mantissa Multiplication 27 x 27 Mode © 2010 Altera Corporation—Public Double-precision Mantissa Multiplication 54 x 54 Mode ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 19

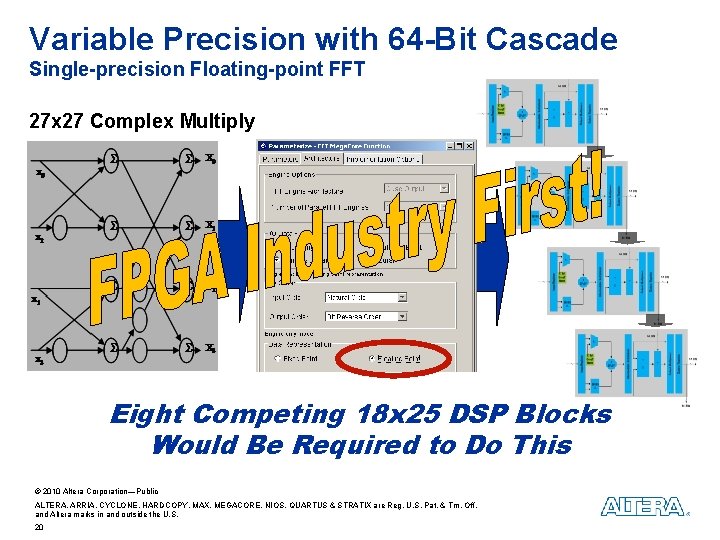

Variable Precision with 64 -Bit Cascade Single-precision Floating-point FFT 27 x 27 Complex Multiply Eight Competing 18 x 25 DSP Blocks Would Be Required to Do This © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 20

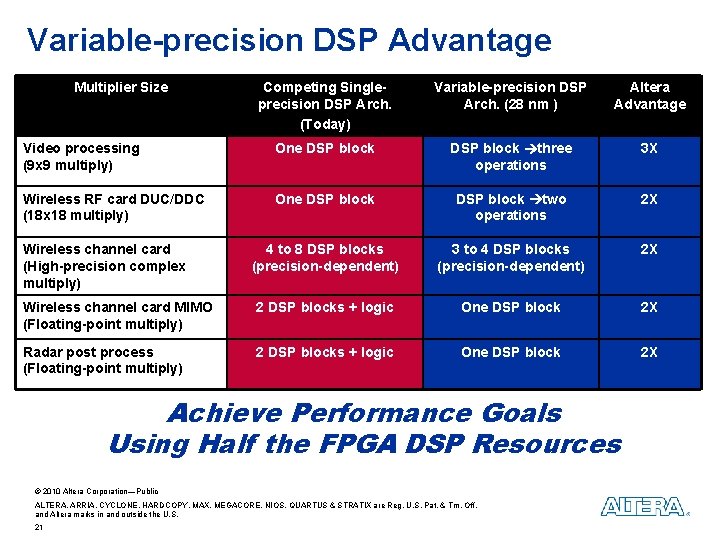

Variable-precision DSP Advantage Multiplier Size Competing Singleprecision DSP Arch. (Today) Variable-precision DSP Arch. (28 nm ) Altera Advantage Video processing (9 x 9 multiply) One DSP block three operations 3 X Wireless RF card DUC/DDC (18 x 18 multiply) One DSP block two operations 2 X 4 to 8 DSP blocks (precision-dependent) 3 to 4 DSP blocks (precision-dependent) 2 X Wireless channel card MIMO (Floating-point multiply) 2 DSP blocks + logic One DSP block 2 X Radar post process (Floating-point multiply) 2 DSP blocks + logic One DSP block 2 X Wireless channel card (High-precision complex multiply) Achieve Performance Goals Using Half the FPGA DSP Resources © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 21

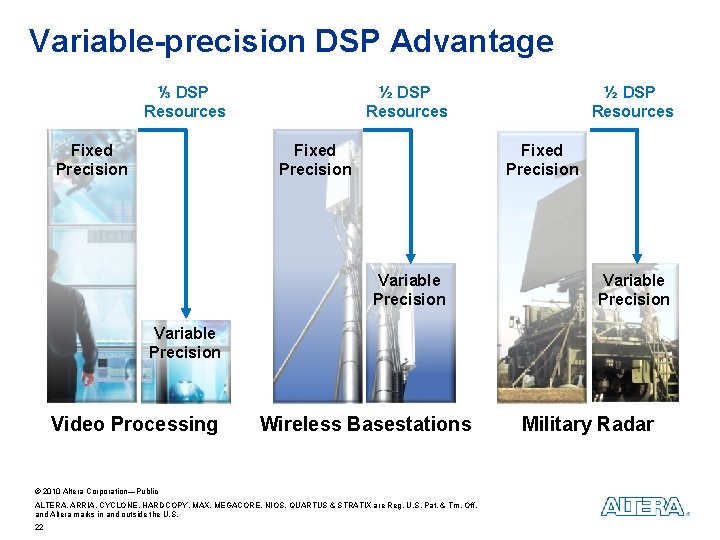

Variable-precision DSP Advantage ⅓ DSP Resources Fixed Precision ½ DSP Resources Fixed Precision Variable Precision Video Processing Wireless Basestations © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 22 Military Radar

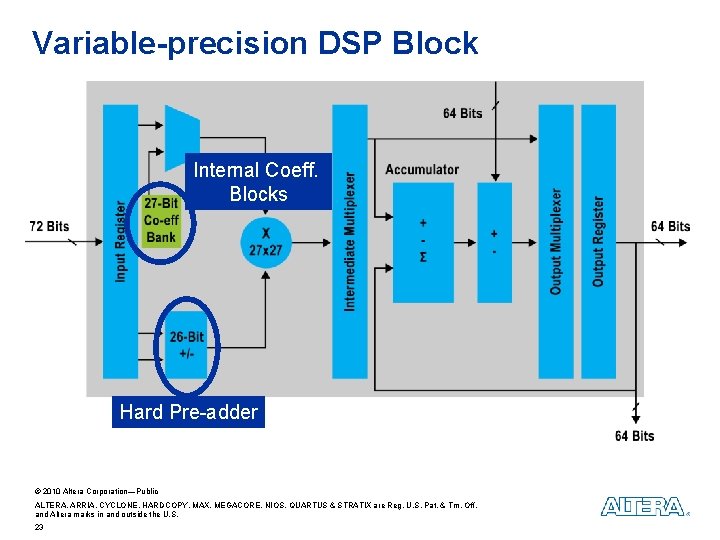

Variable-precision DSP Block Internal Coeff. Blocks Hard Pre-adder © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 23

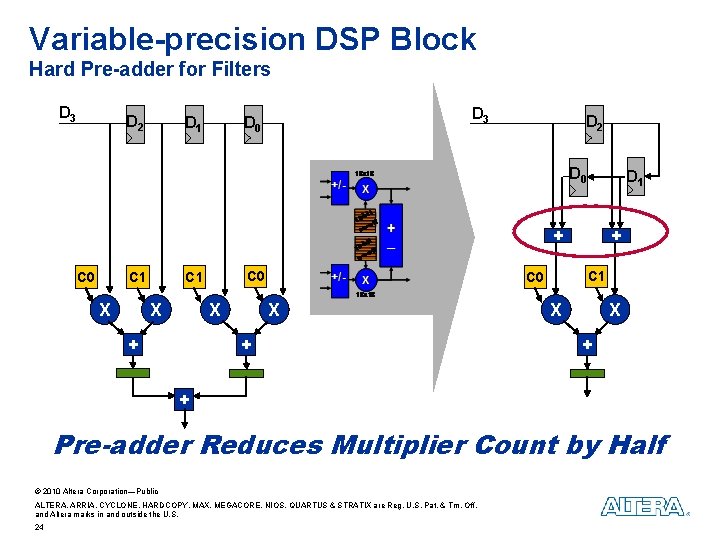

Variable-precision DSP Block Hard Pre-adder for Filters D 3 D 2 D 1 D 3 D 0 D 2 D 0 D 1 + C 0 C 1 X X + + C 1 C 0 X + X X + + Pre-adder Reduces Multiplier Count by Half © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 24

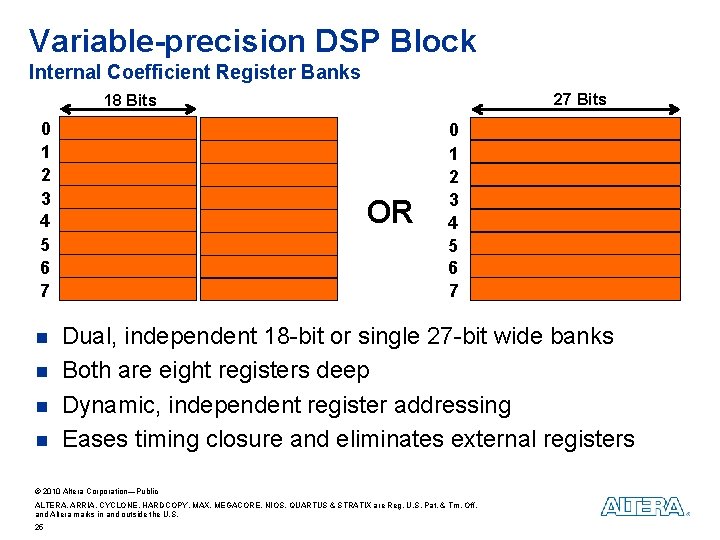

Variable-precision DSP Block Internal Coefficient Register Banks 27 Bits 18 Bits 0 1 2 3 4 5 6 7 n n OR 0 1 2 3 4 5 6 7 Dual, independent 18 -bit or single 27 -bit wide banks Both are eight registers deep Dynamic, independent register addressing Eases timing closure and eliminates external registers © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 25

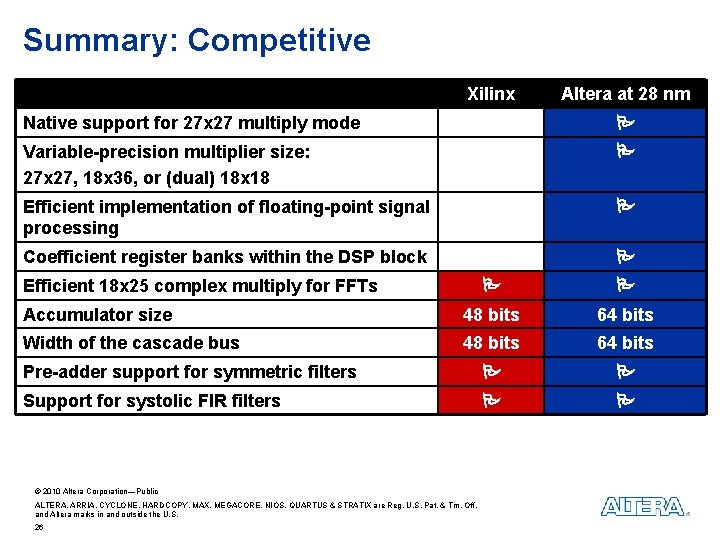

Summary: Competitive Xilinx Altera at 28 nm Native support for 27 x 27 multiply mode Variable-precision multiplier size: 27 x 27, 18 x 36, or (dual) 18 x 18 Efficient implementation of floating-point signal processing Coefficient register banks within the DSP block Efficient 18 x 25 complex multiply for FFTs Accumulator size 48 bits 64 bits Width of the cascade bus 48 bits 64 bits Pre-adder support for symmetric filters Support for systolic FIR filters © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 26

For More Information n Download our DSP architecture whitepaper - FPGA Industry’s first variable precision DSP architecture n Download the Stratix V FPGA handbook © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 27

Thank You! For more information visit: www. altera. com © 2010 Altera Corporation—Public

- Slides: 28