include DSP 281 xDevice h DSP 281 x

- Slides: 10

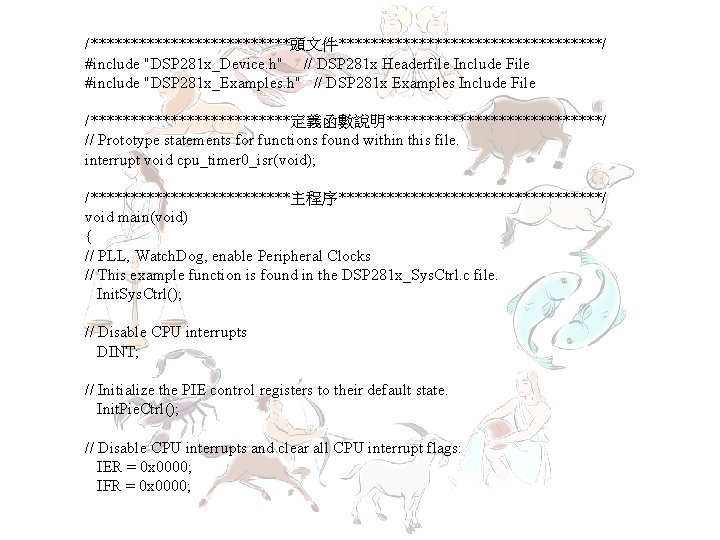

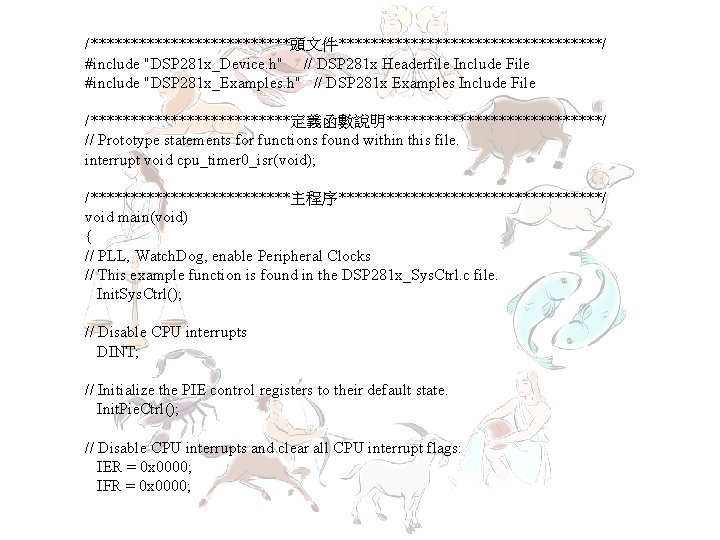

/*************頭文件*****************/ #include "DSP 281 x_Device. h" // DSP 281 x Headerfile Include File #include "DSP 281 x_Examples. h" // DSP 281 x Examples Include File /*************定義函數說明**************/ // Prototype statements for functions found within this file. interrupt void cpu_timer 0_isr(void); /*************主程序*****************/ void main(void) { // PLL, Watch. Dog, enable Peripheral Clocks // This example function is found in the DSP 281 x_Sys. Ctrl. c file. Init. Sys. Ctrl(); // Disable CPU interrupts DINT; // Initialize the PIE control registers to their default state. Init. Pie. Ctrl(); // Disable CPU interrupts and clear all CPU interrupt flags: IER = 0 x 0000; IFR = 0 x 0000;

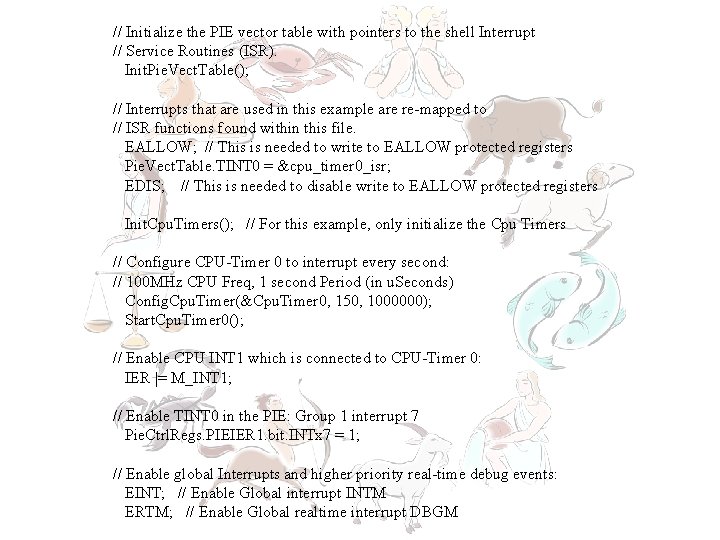

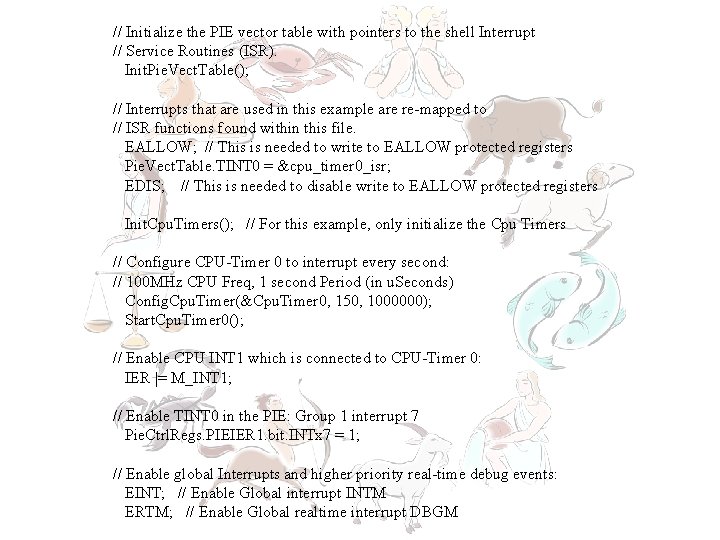

// Initialize the PIE vector table with pointers to the shell Interrupt // Service Routines (ISR). Init. Pie. Vect. Table(); // Interrupts that are used in this example are re-mapped to // ISR functions found within this file. EALLOW; // This is needed to write to EALLOW protected registers Pie. Vect. Table. TINT 0 = &cpu_timer 0_isr; EDIS; // This is needed to disable write to EALLOW protected registers Init. Cpu. Timers(); // For this example, only initialize the Cpu Timers // Configure CPU-Timer 0 to interrupt every second: // 100 MHz CPU Freq, 1 second Period (in u. Seconds) Config. Cpu. Timer(&Cpu. Timer 0, 150, 1000000); Start. Cpu. Timer 0(); // Enable CPU INT 1 which is connected to CPU-Timer 0: IER |= M_INT 1; // Enable TINT 0 in the PIE: Group 1 interrupt 7 Pie. Ctrl. Regs. PIEIER 1. bit. INTx 7 = 1; // Enable global Interrupts and higher priority real-time debug events: EINT; // Enable Global interrupt INTM ERTM; // Enable Global realtime interrupt DBGM

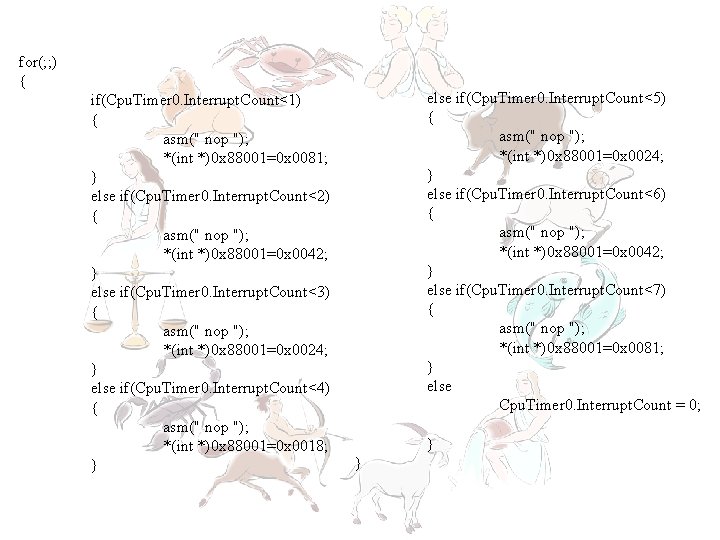

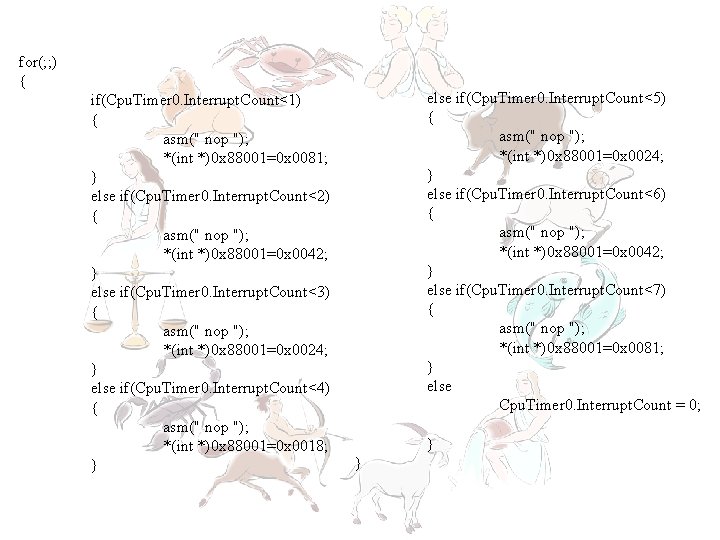

for(; ; ) { if(Cpu. Timer 0. Interrupt. Count<1) { asm(" nop "); *(int *)0 x 88001=0 x 0081; } else if(Cpu. Timer 0. Interrupt. Count<2) { asm(" nop "); *(int *)0 x 88001=0 x 0042; } else if(Cpu. Timer 0. Interrupt. Count<3) { asm(" nop "); *(int *)0 x 88001=0 x 0024; } else if(Cpu. Timer 0. Interrupt. Count<4) { asm(" nop "); *(int *)0 x 88001=0 x 0018; } else if(Cpu. Timer 0. Interrupt. Count<5) { asm(" nop "); *(int *)0 x 88001=0 x 0024; } else if(Cpu. Timer 0. Interrupt. Count<6) { asm(" nop "); *(int *)0 x 88001=0 x 0042; } else if(Cpu. Timer 0. Interrupt. Count<7) { asm(" nop "); *(int *)0 x 88001=0 x 0081; } else Cpu. Timer 0. Interrupt. Count = 0; } }

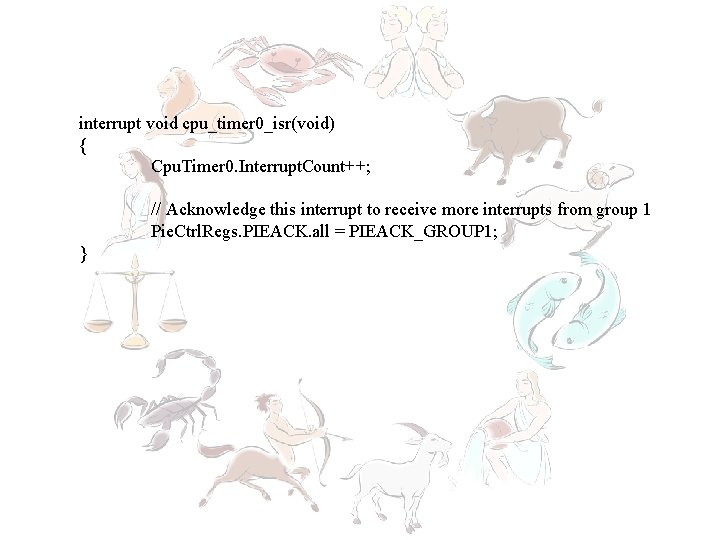

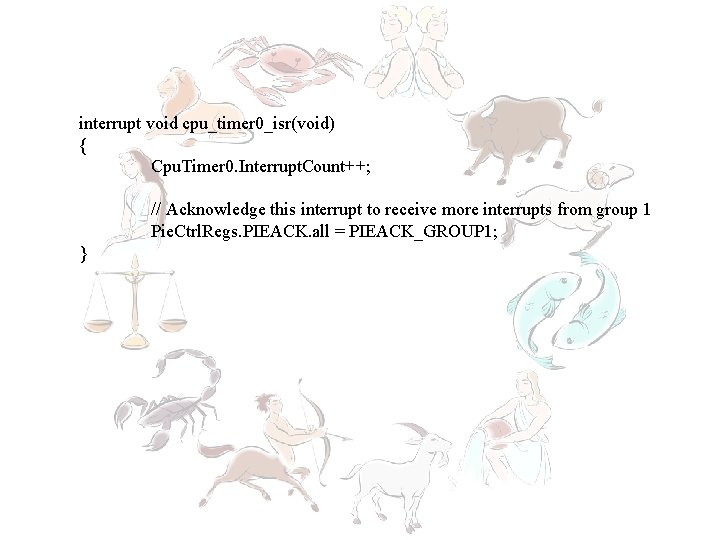

interrupt void cpu_timer 0_isr(void) { Cpu. Timer 0. Interrupt. Count++; // Acknowledge this interrupt to receive more interrupts from group 1 Pie. Ctrl. Regs. PIEACK. all = PIEACK_GROUP 1; }