Transient Analysis of Power System ChungKuan Cheng January

- Slides: 26

Transient Analysis of Power System Chung-Kuan Cheng January 27, 2006 Computer Science & Engineering Department University of California, San Diego

Outline l l l l Statement of the Problem Status of Simulators Solver Engine: Multigrid Review Integration Method Frequency Domain Analysis Experimental Results Conclusion

Statement of Problem l l l Huge RLC linear system with multiple sources Wide spread of natural frequencies (KHz. GHz) Many corners and many modes of operations Packaging and transmission lines Nonlinear devices

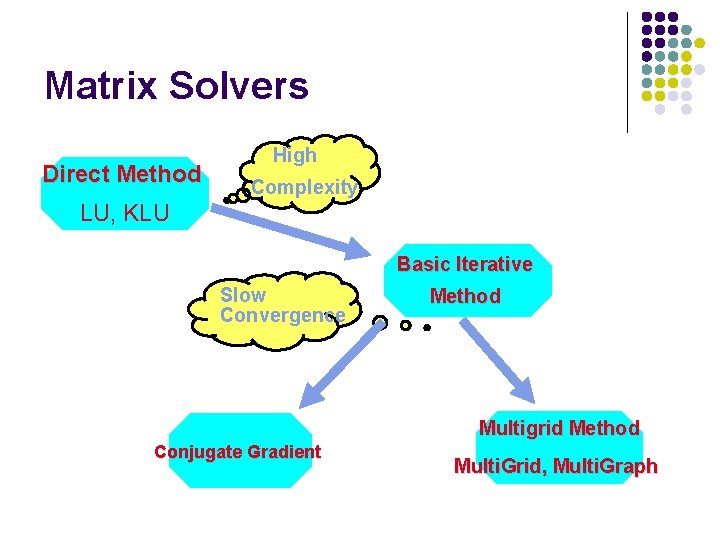

Status of the Simulator l l l Matrix Solvers: Multigrid, Multigraph Integration Method: Operator Splitting Frequency Domain Analysis

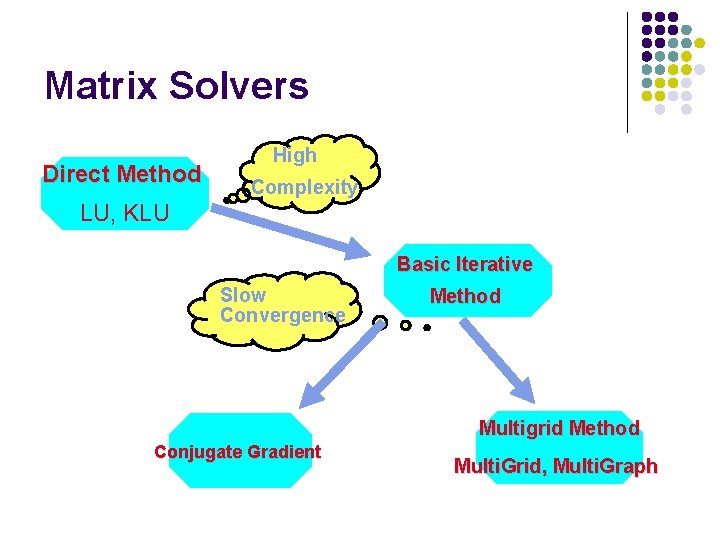

Matrix Solvers Direct Method High Complexity LU, KLU Basic Iterative Slow Convergence Method Multigrid Method Conjugate Gradient Multi. Grid, Multi. Graph

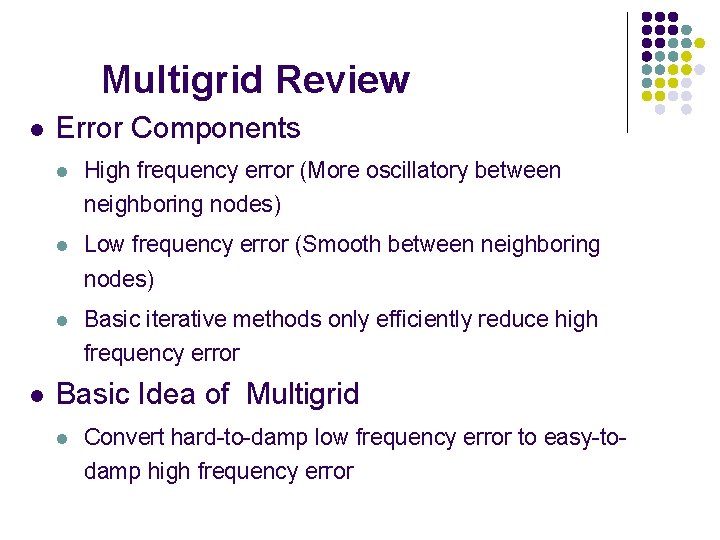

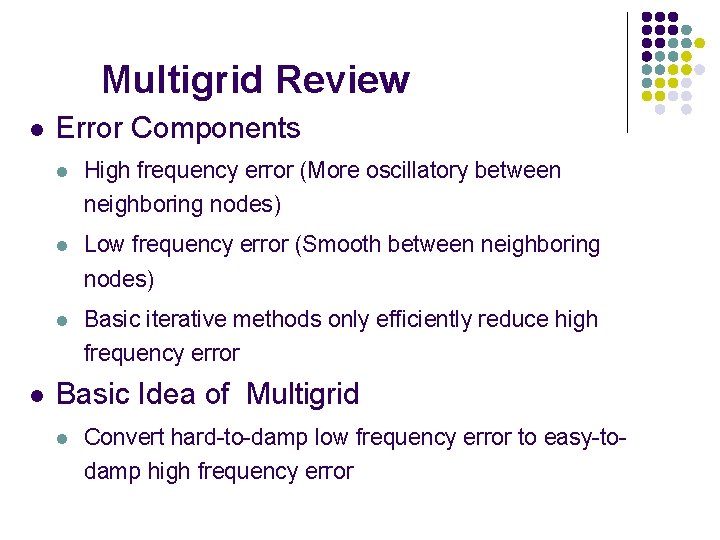

Multigrid Review l l Error Components l High frequency error (More oscillatory between neighboring nodes) l Low frequency error (Smooth between neighboring nodes) l Basic iterative methods only efficiently reduce high frequency error Basic Idea of Multigrid l Convert hard-to-damp low frequency error to easy-todamp high frequency error

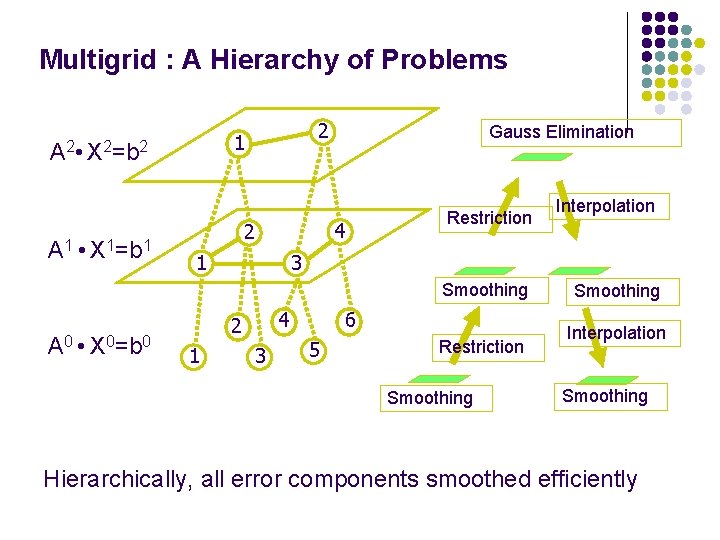

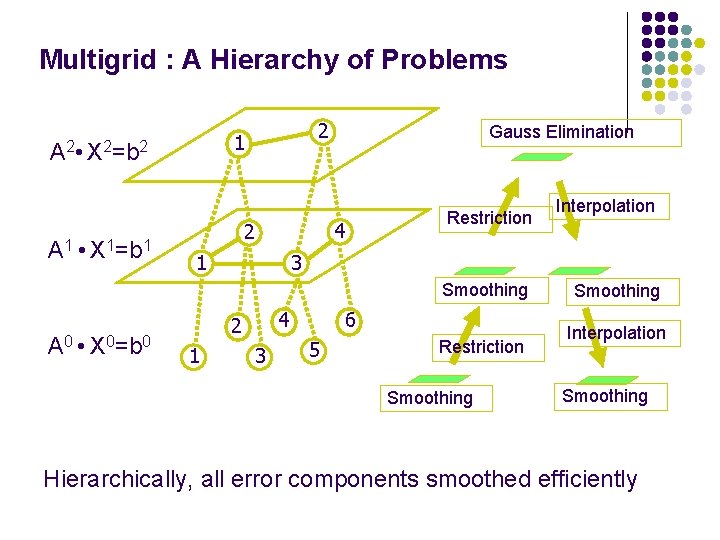

Multigrid : A Hierarchy of Problems A 2 • X 2=b 2 A 1 • X 1=b 1 2 1 Gauss Elimination 4 2 1 Restriction 3 Smoothing A 0 • X 0=b 0 4 2 1 Interpolation 3 6 5 Restriction Smoothing Interpolation Smoothing Hierarchically, all error components smoothed efficiently

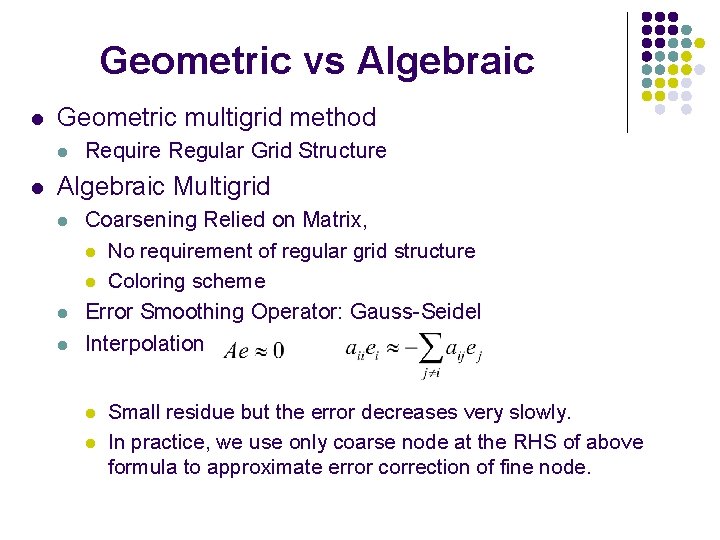

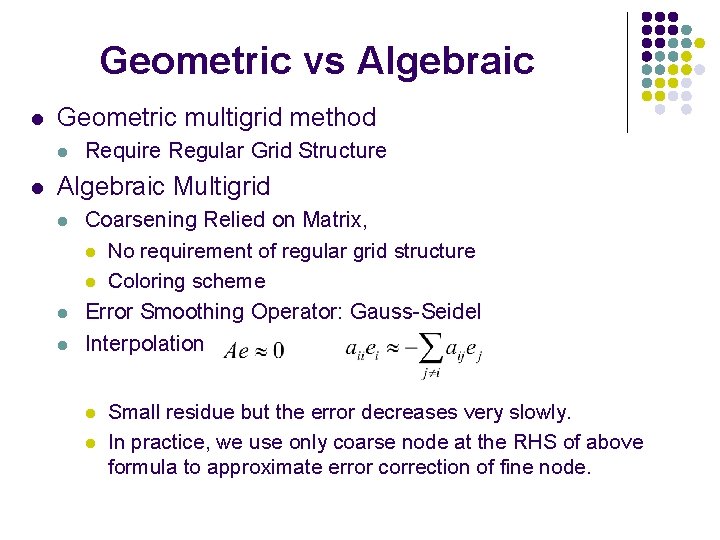

Geometric vs Algebraic l Geometric multigrid method l l Require Regular Grid Structure Algebraic Multigrid l l l Coarsening Relied on Matrix, l No requirement of regular grid structure l Coloring scheme Error Smoothing Operator: Gauss-Seidel Interpolation l l Small residue but the error decreases very slowly. In practice, we use only coarse node at the RHS of above formula to approximate error correction of fine node.

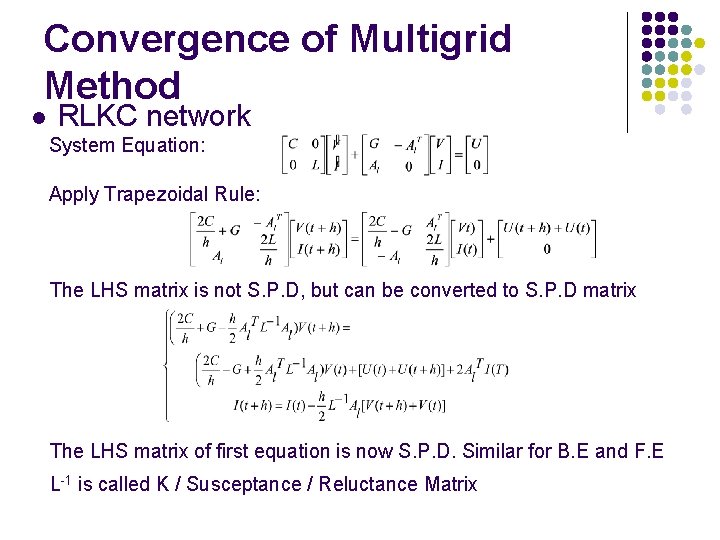

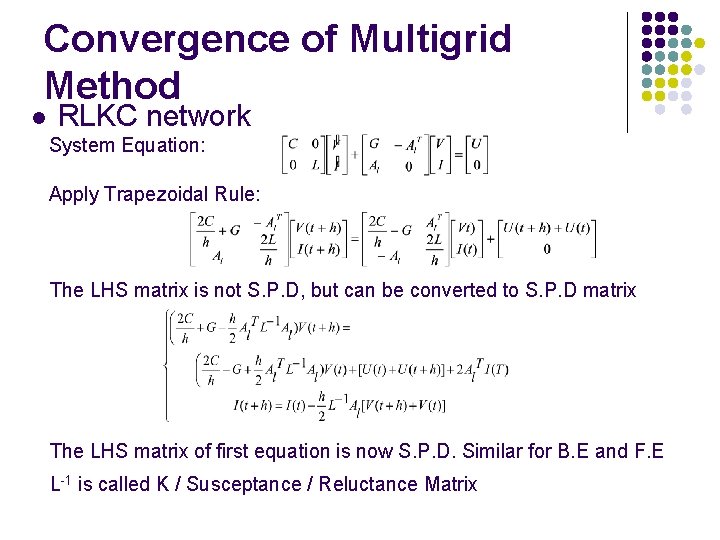

Convergence of Multigrid Method l RLKC network System Equation: Apply Trapezoidal Rule: The LHS matrix is not S. P. D, but can be converted to S. P. D matrix The LHS matrix of first equation is now S. P. D. Similar for B. E and F. E L-1 is called K / Susceptance / Reluctance Matrix

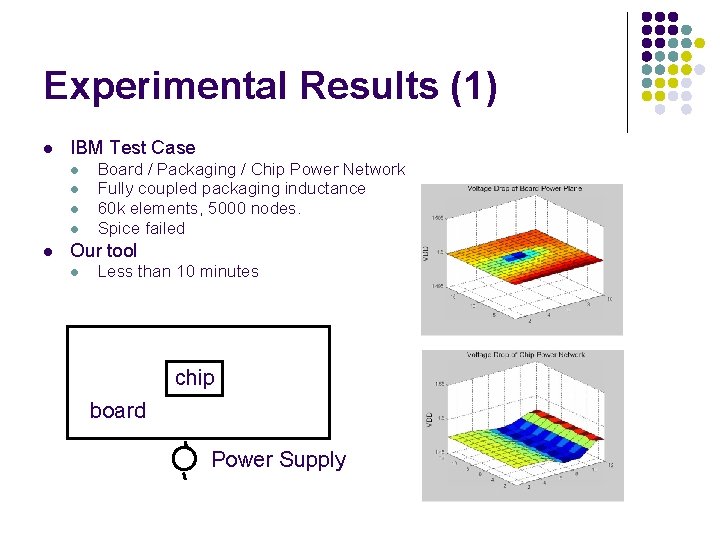

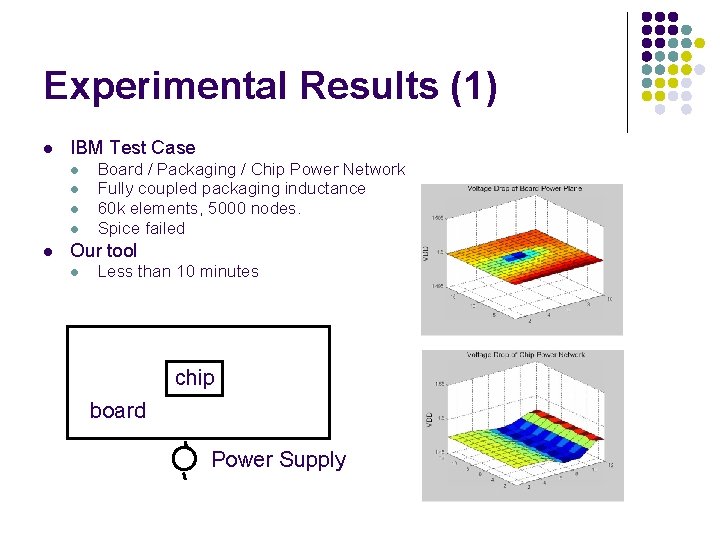

Experimental Results (1) l IBM Test Case l l l Board / Packaging / Chip Power Network Fully coupled packaging inductance 60 k elements, 5000 nodes. Spice failed Our tool l Less than 10 minutes chip board Power Supply

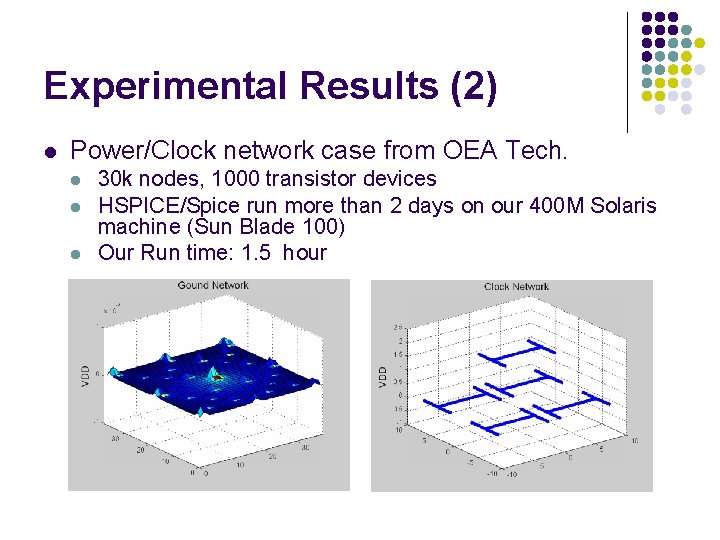

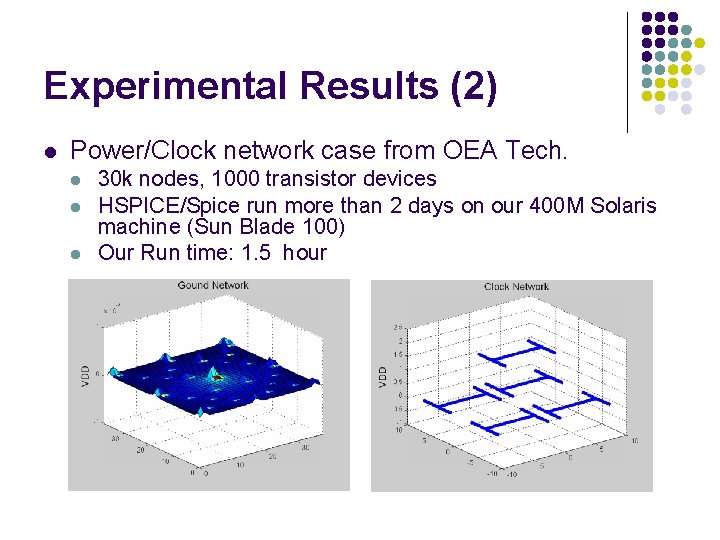

Experimental Results (2) l Power/Clock network case from OEA Tech. l l l 30 k nodes, 1000 transistor devices HSPICE/Spice run more than 2 days on our 400 M Solaris machine (Sun Blade 100) Our Run time: 1. 5 hour

Integration Method: Operator Splitting l l ADI: Two way partitions. Working on time steps. Operator Splitting: Multiway Partitioning. Research + Development.

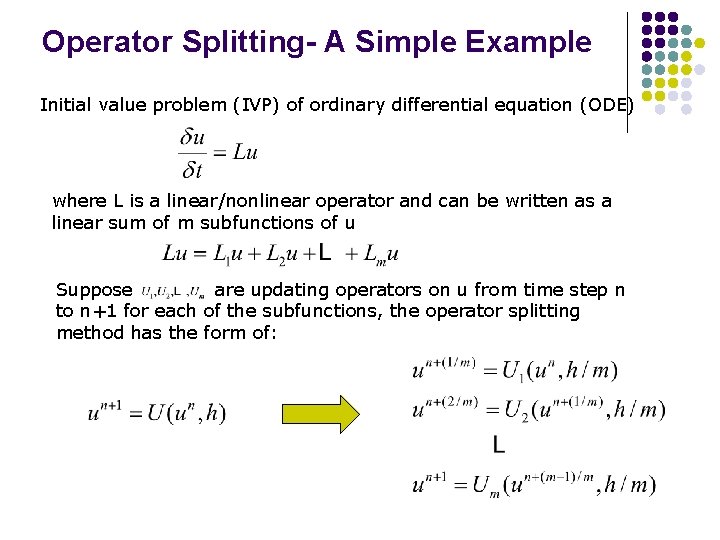

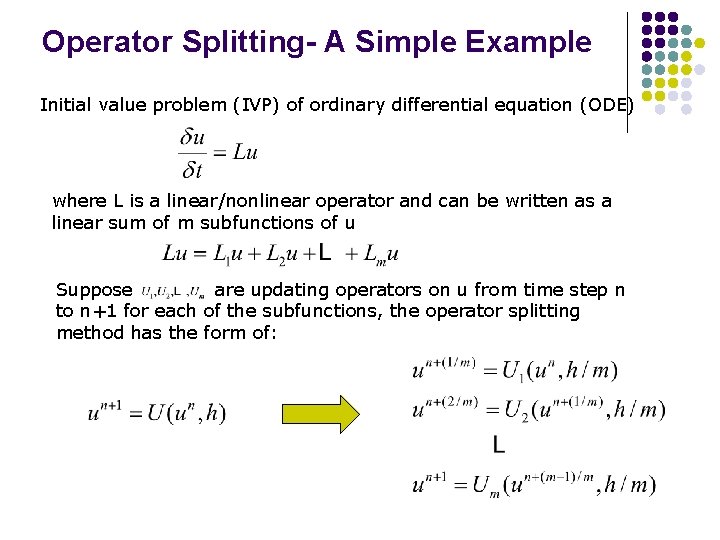

Operator Splitting- A Simple Example Initial value problem (IVP) of ordinary differential equation (ODE) where L is a linear/nonlinear operator and can be written as a linear sum of m subfunctions of u Suppose are updating operators on u from time step n to n+1 for each of the subfunctions, the operator splitting method has the form of:

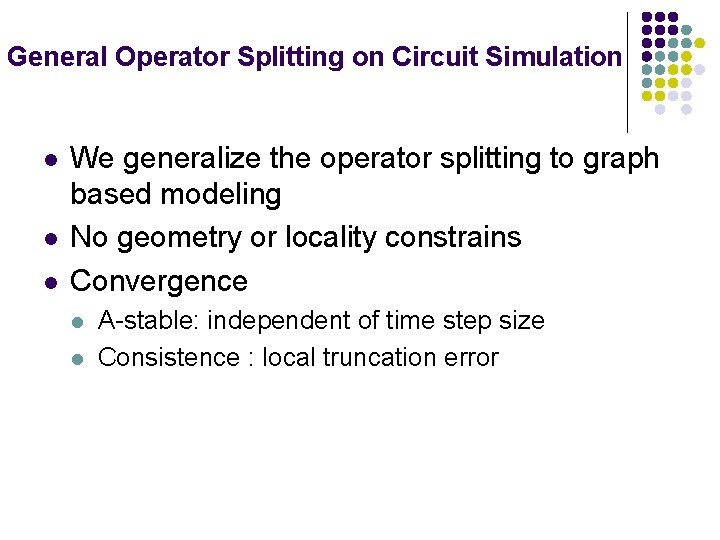

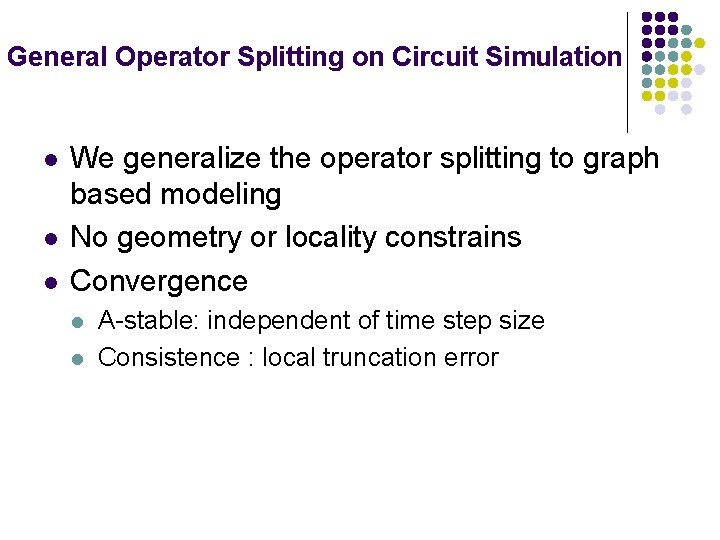

General Operator Splitting on Circuit Simulation l l l We generalize the operator splitting to graph based modeling No geometry or locality constrains Convergence l l A-stable: independent of time step size Consistence : local truncation error

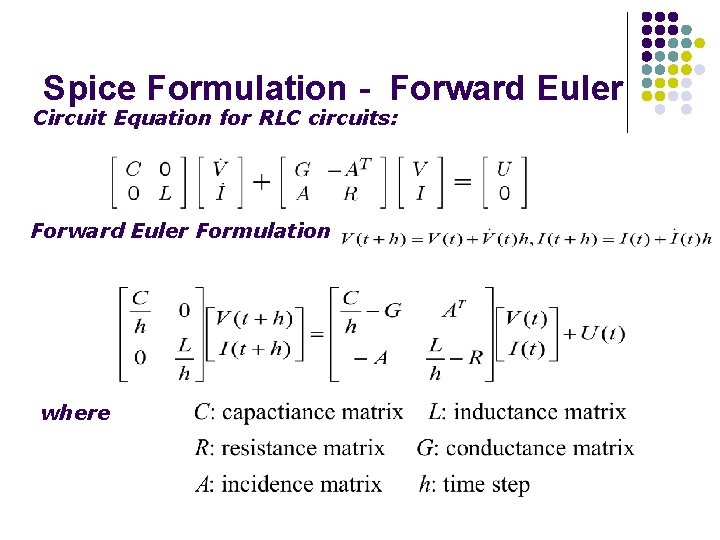

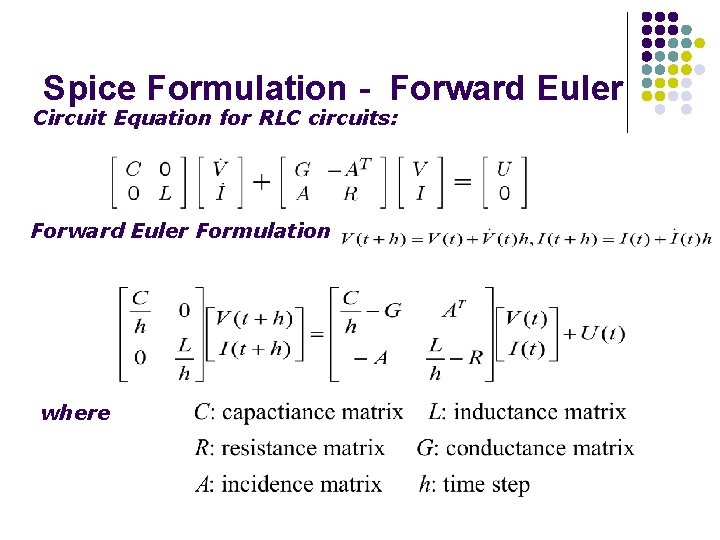

Spice Formulation - Forward Euler Circuit Equation for RLC circuits: Forward Euler Formulation where

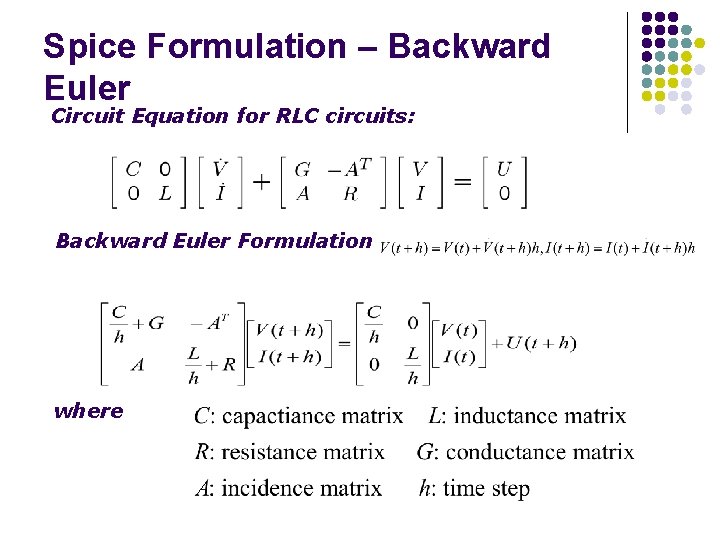

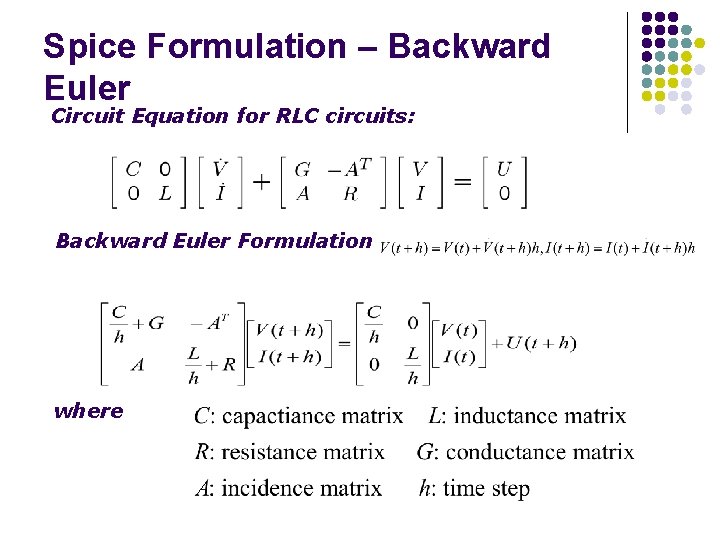

Spice Formulation – Backward Euler Circuit Equation for RLC circuits: Backward Euler Formulation where

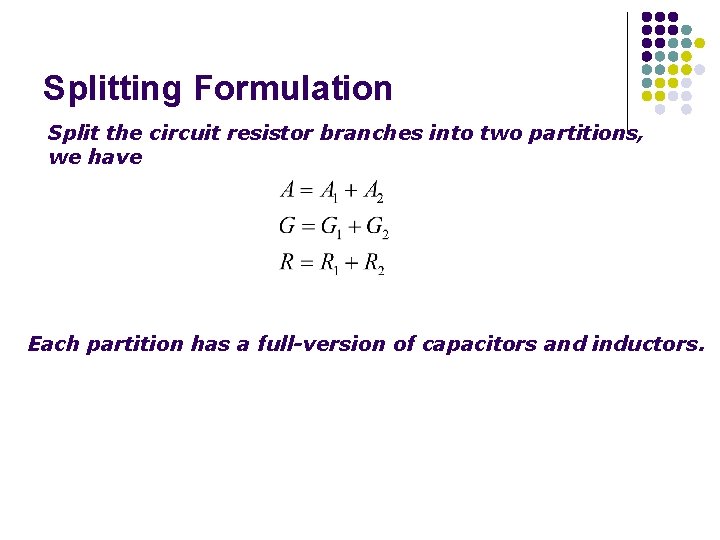

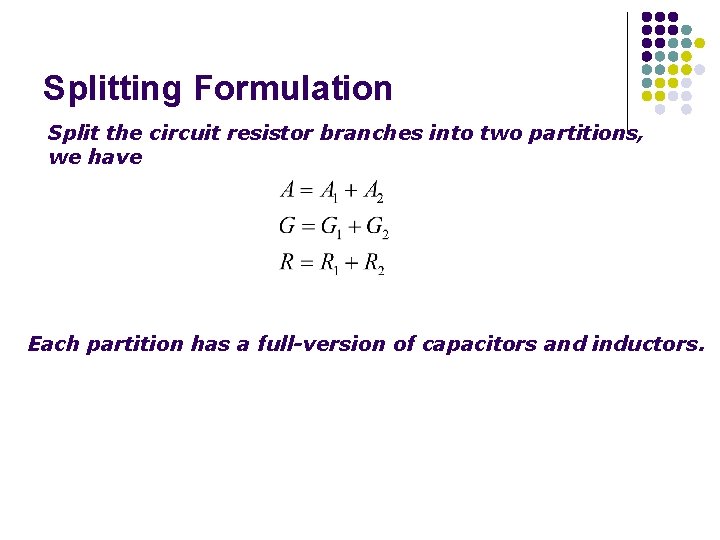

Splitting Formulation Split the circuit resistor branches into two partitions, we have Each partition has a full-version of capacitors and inductors.

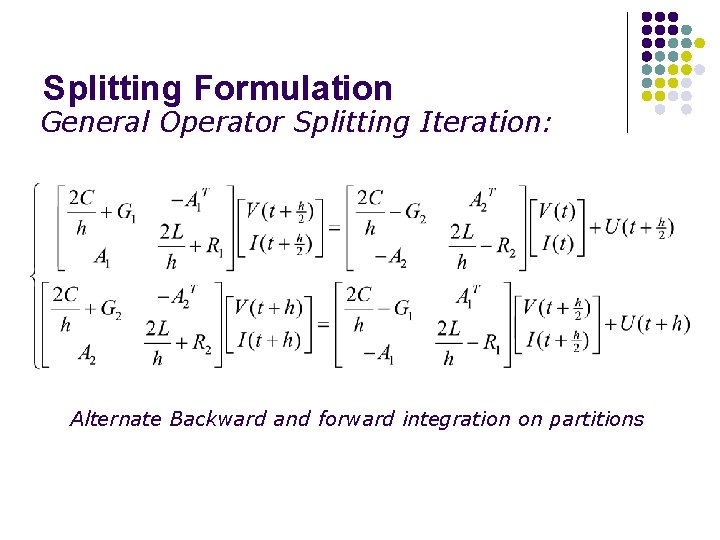

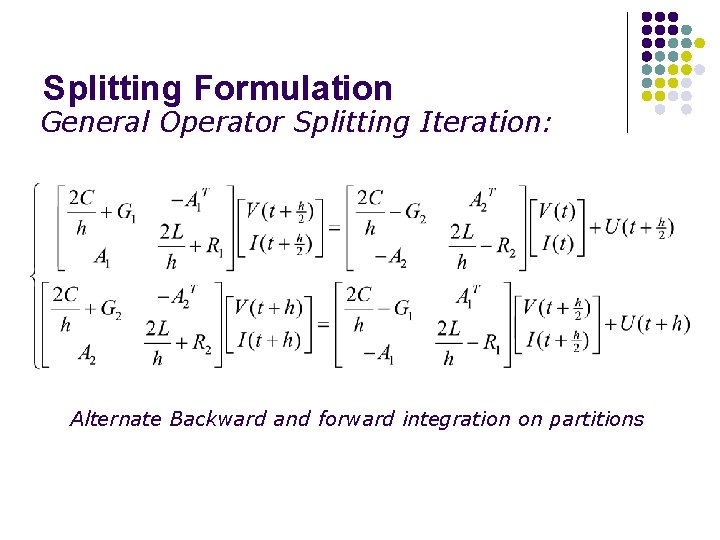

Splitting Formulation General Operator Splitting Iteration: Alternate Backward and forward integration on partitions

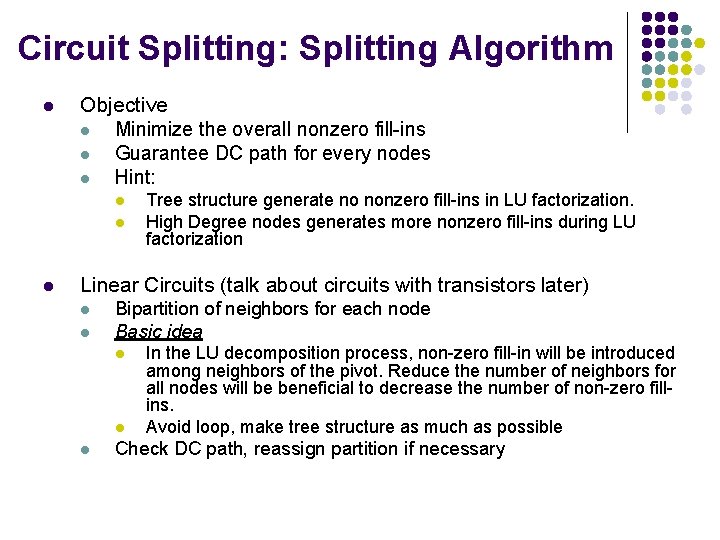

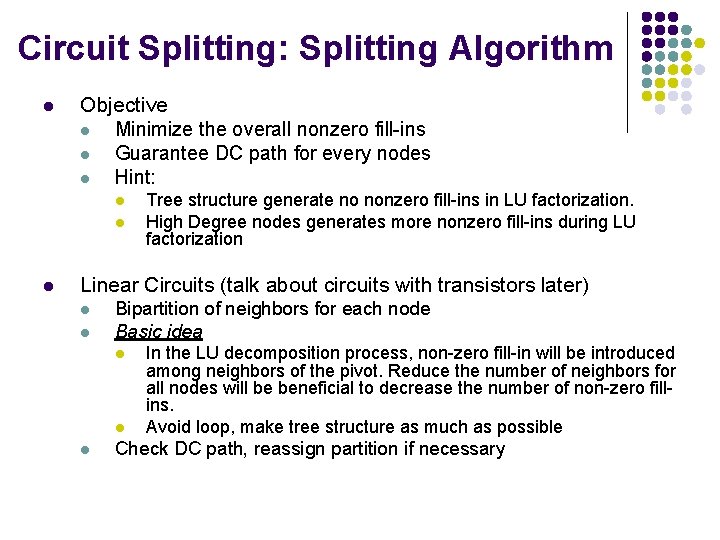

Circuit Splitting: Splitting Algorithm l Objective l Minimize the overall nonzero fill-ins l Guarantee DC path for every nodes l Hint: l l l Tree structure generate no nonzero fill-ins in LU factorization. High Degree nodes generates more nonzero fill-ins during LU factorization Linear Circuits (talk about circuits with transistors later) l l Bipartition of neighbors for each node Basic idea l l l In the LU decomposition process, non-zero fill-in will be introduced among neighbors of the pivot. Reduce the number of neighbors for all nodes will be beneficial to decrease the number of non-zero fillins. Avoid loop, make tree structure as much as possible Check DC path, reassign partition if necessary

Experimental Results-1 Power Network & Gate Sinks Examples Circuit 1 Circuit 2 Circuit 3 Circuit 4 # Nodes 11, 203 41, 321 92, 360 160, 657 # Transistors 74 513 1, 108 2, 130 Simulation Period 10 ns SPICE 3(sec) 602. 44 8268. 92 39612. 32 N/A Operator Splitting 74. 64 305. 38 681. 18 1356. 21 Speedup 8. 1 x 27. 1 x 58. 2 x N/A Voltage Drop of Circuit 3

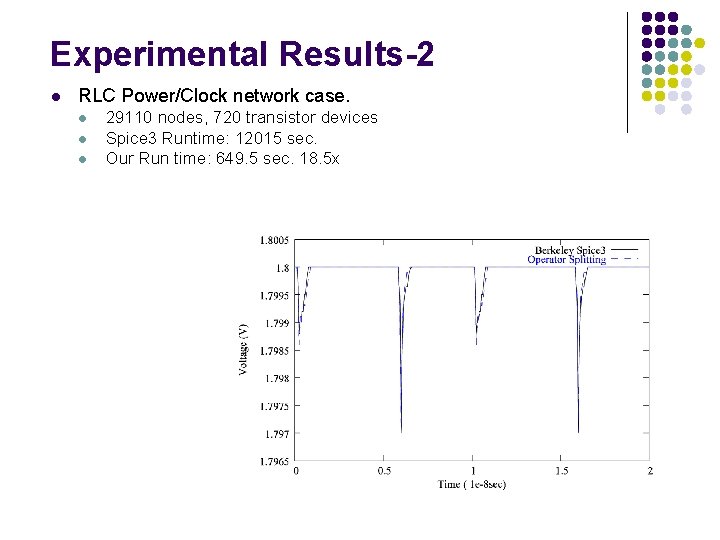

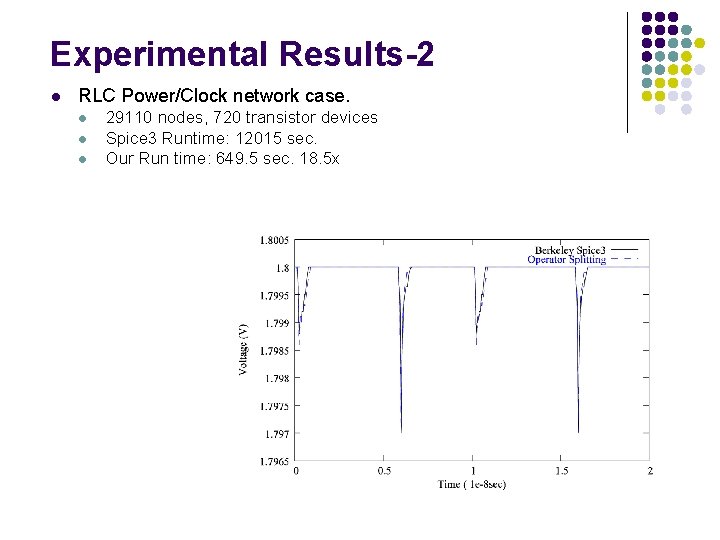

Experimental Results-2 l RLC Power/Clock network case. l l l 29110 nodes, 720 transistor devices Spice 3 Runtime: 12015 sec. Our Run time: 649. 5 sec. 18. 5 x

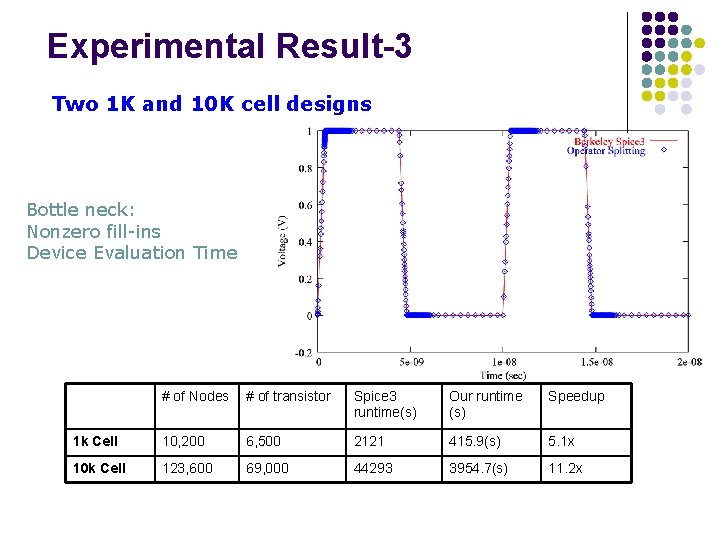

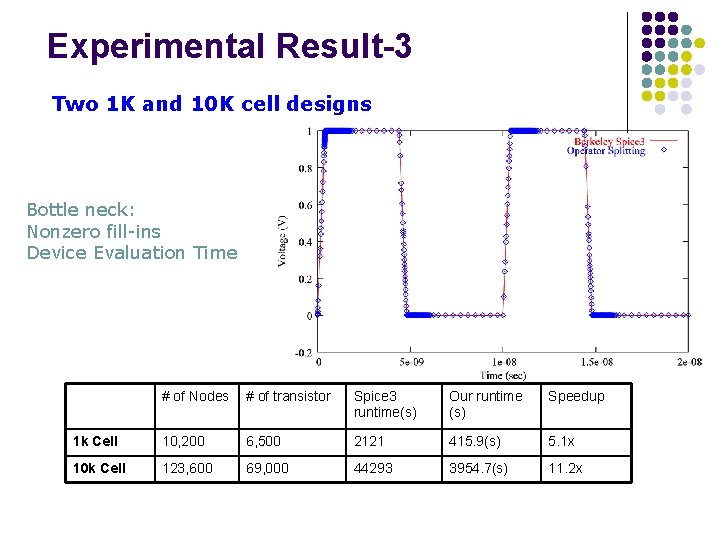

Experimental Result-3 Two 1 K and 10 K cell designs Bottle neck: Nonzero fill-ins Device Evaluation Time # of Nodes # of transistor Spice 3 runtime(s) Our runtime (s) Speedup 1 k Cell 10, 200 6, 500 2121 415. 9(s) 5. 1 x 10 k Cell 123, 600 69, 000 44293 3954. 7(s) 11. 2 x

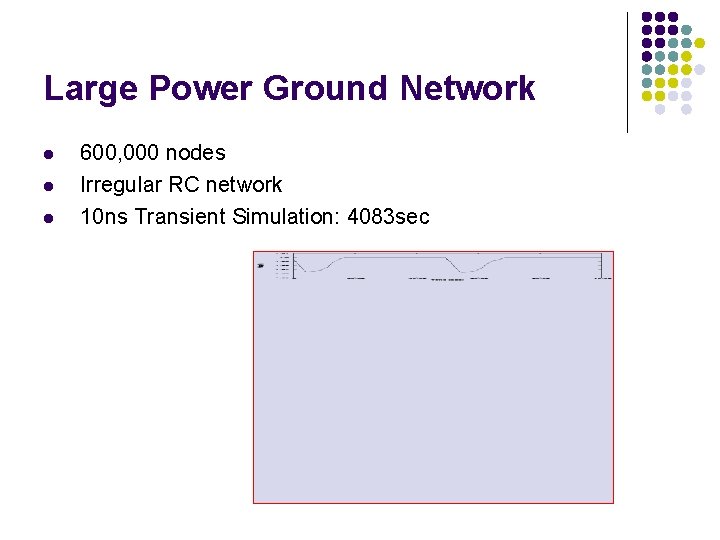

Large Power Ground Network l l l 600, 000 nodes Irregular RC network 10 ns Transient Simulation: 4083 sec

Frequency Domain Analysis l Natural Frequency Extraction l l Complex Matrix Solver Fast Fourier Transformation

Conclusion Transient of Power Analysis: Post Doc. (Sep 05 -Feb 06) l Nonlinear Network: Fastrack Release l Operator Splitting: Rui Shi l Packaging: Vincent Peng l Frequency Domain Analysis: R. Wang l

References l l Efficient Transistor Level Simulation Using Two-Stage Newton. Raphson and Multigrid Method, CK Cheng and Zhengyong Zhu, filed by UCSD, SD 2005 -013. Circuit Splitting in Analysis of Circuits at Transistor Level, C. K. Cheng, R. Shi, and Z. Zhu, filed by UCSD, SD 2005 -129 -PCT, June 7, 2005. Z. Zhu, B. Yao, and C. K. Cheng, "Power Network Analysis Using an Adaptive Algebraic Multigrid Approach, ACM/IEEE Design Automation Conference, pp. 105 -108, June 2003. Z. Zhu, K. Rouz, M. Borah, C. K. Cheng, and E. S. Kuh, "Efficient Transient Simulation for Transistor-Level Analysis, “ Asia and South Pacific Design Automation Conf. , 240 -243, 2005.